Page 1

LG Semicon

8-bit Microcontrollers

GMS81604/08

Revision History

Rev 1.2 (Dec. 1998)

Redraw package dimension on page 5~6.

Rev 1.1 (Nov. 1998)

Operating Voltage, 2.7~5.5V is extended with 2.4~5.5V.

Operating Temperature, -20~80°C is extended wi t h -20~85°C.

Add the "Typical Characteristics" on page 16, 17.

Add the unused port guidance on page 48.

Revision the information for the OTP programming guidance, recommand using "Intelligent Mode" on page 49.

Add the chapter for OTP programming specification as an appendix.

Rev 1.0 (Nov. 1997)

First Edition

Page 2

Second Edition

Published by

MCU Application Team

1998 LG Semicon Co., Ltd. All right reserved.

Additional information of this manual may be served by LG Semicon offices in Korea or Distributors and

Representatives listed at address directory.

LG Semicon reserves the right to make changes to any information here in at any time without notice.

The information, diagrams and other data in this manual are correct and reliable; however, LG Semicon Co,. Ltd.

is in no way responsible for any violations of patents or other rights of the third party generated by the use of this

manual.

Page 3

Table of Contents

OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

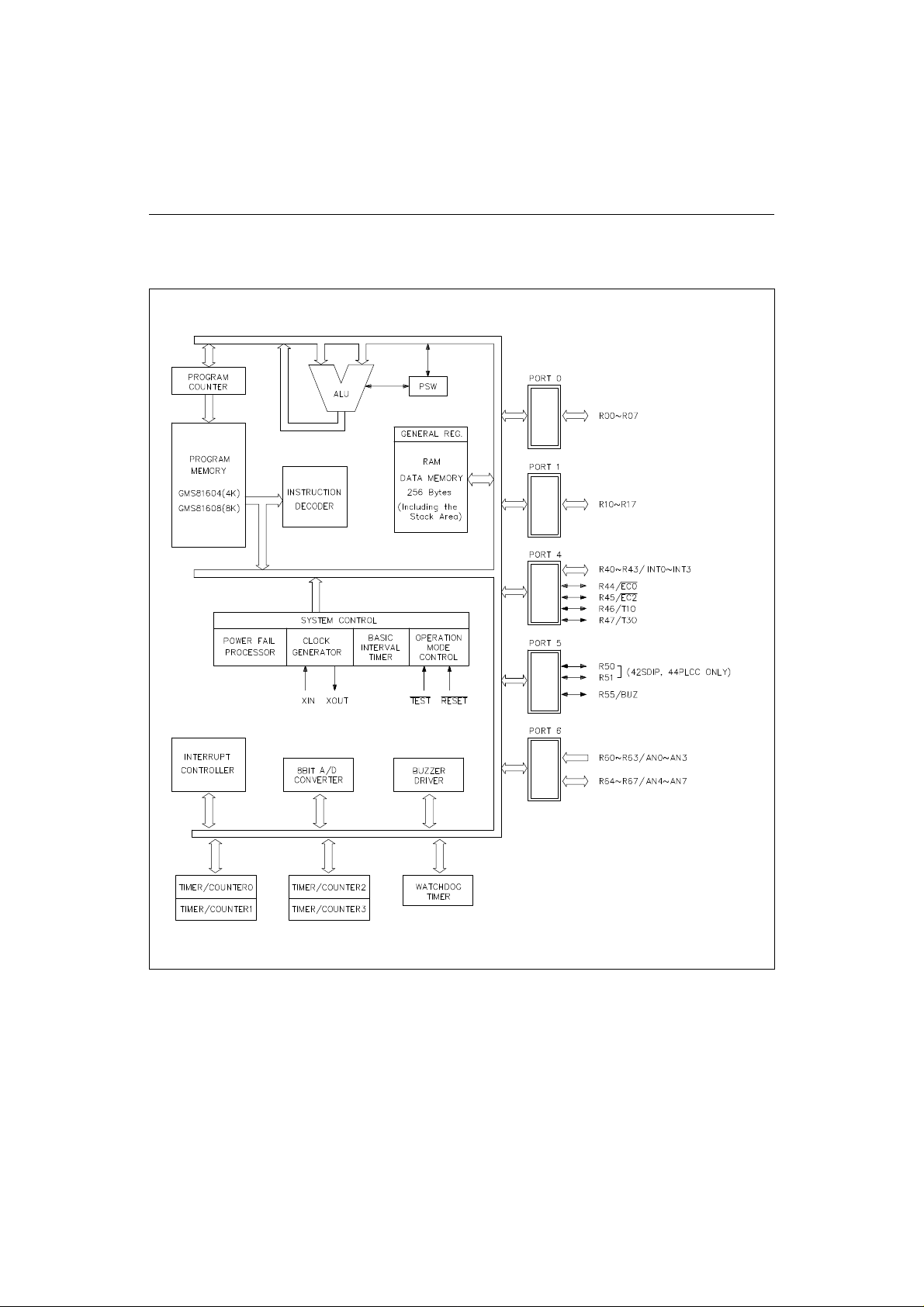

BLOCK DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

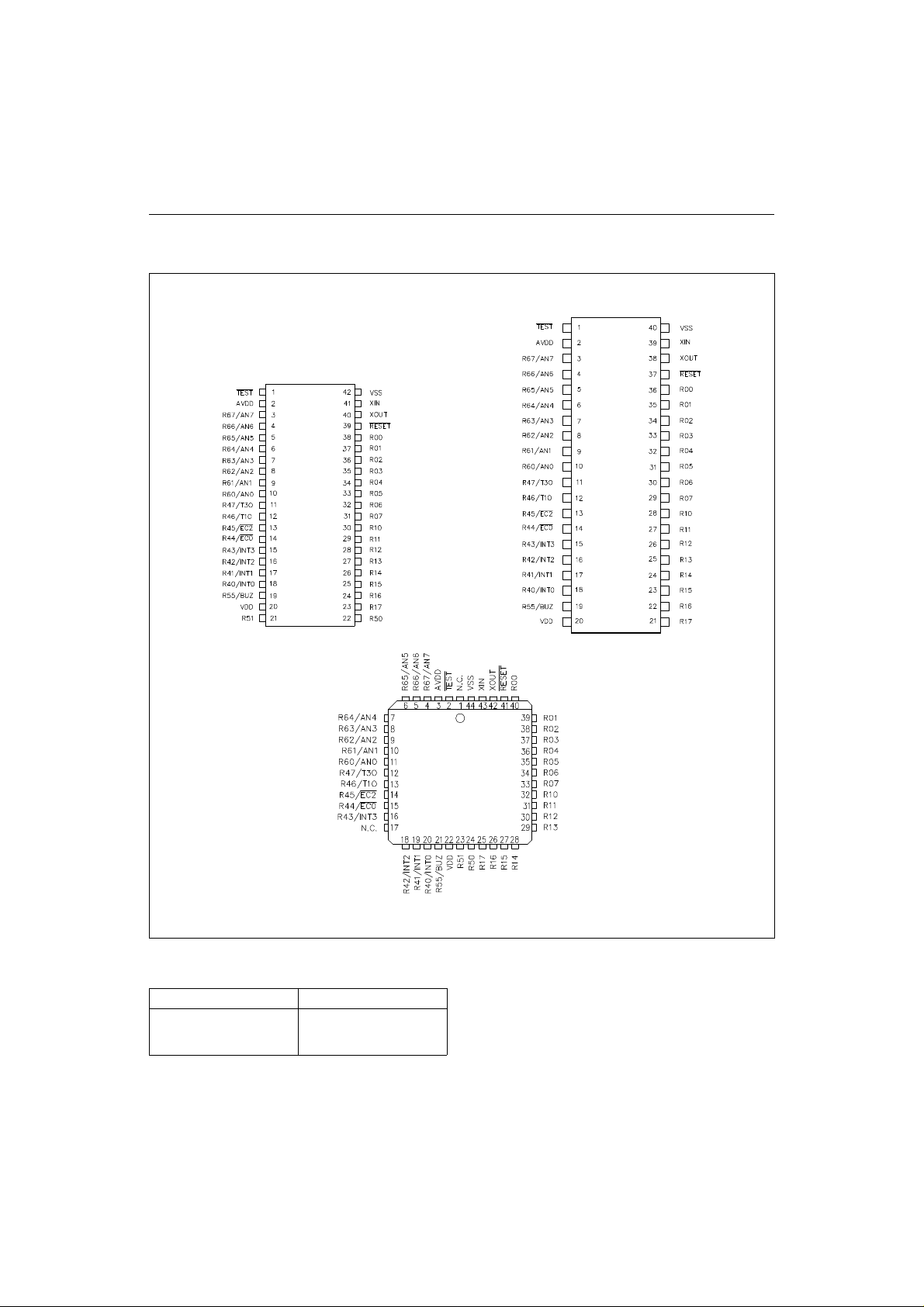

PIN ASSIGNMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

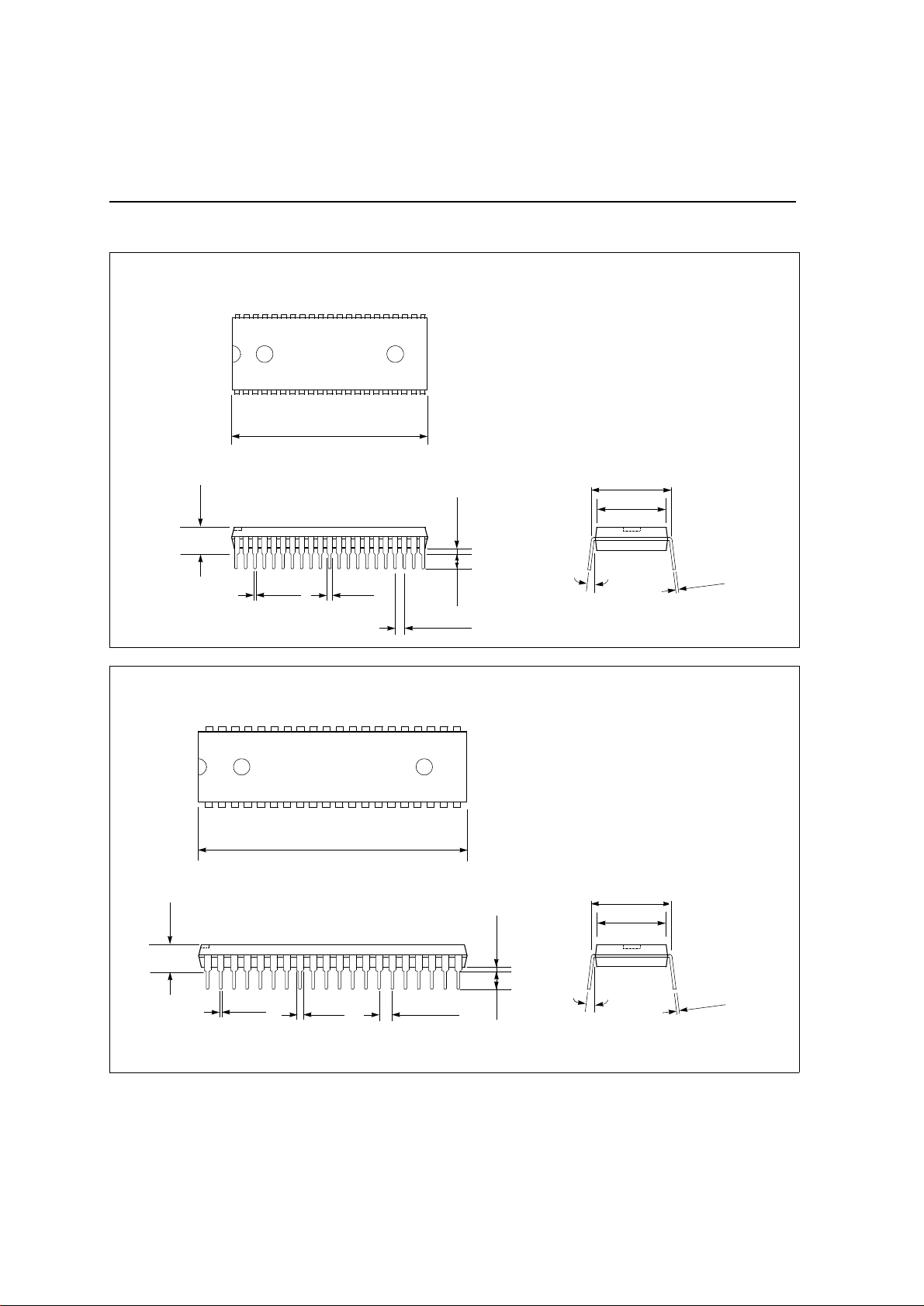

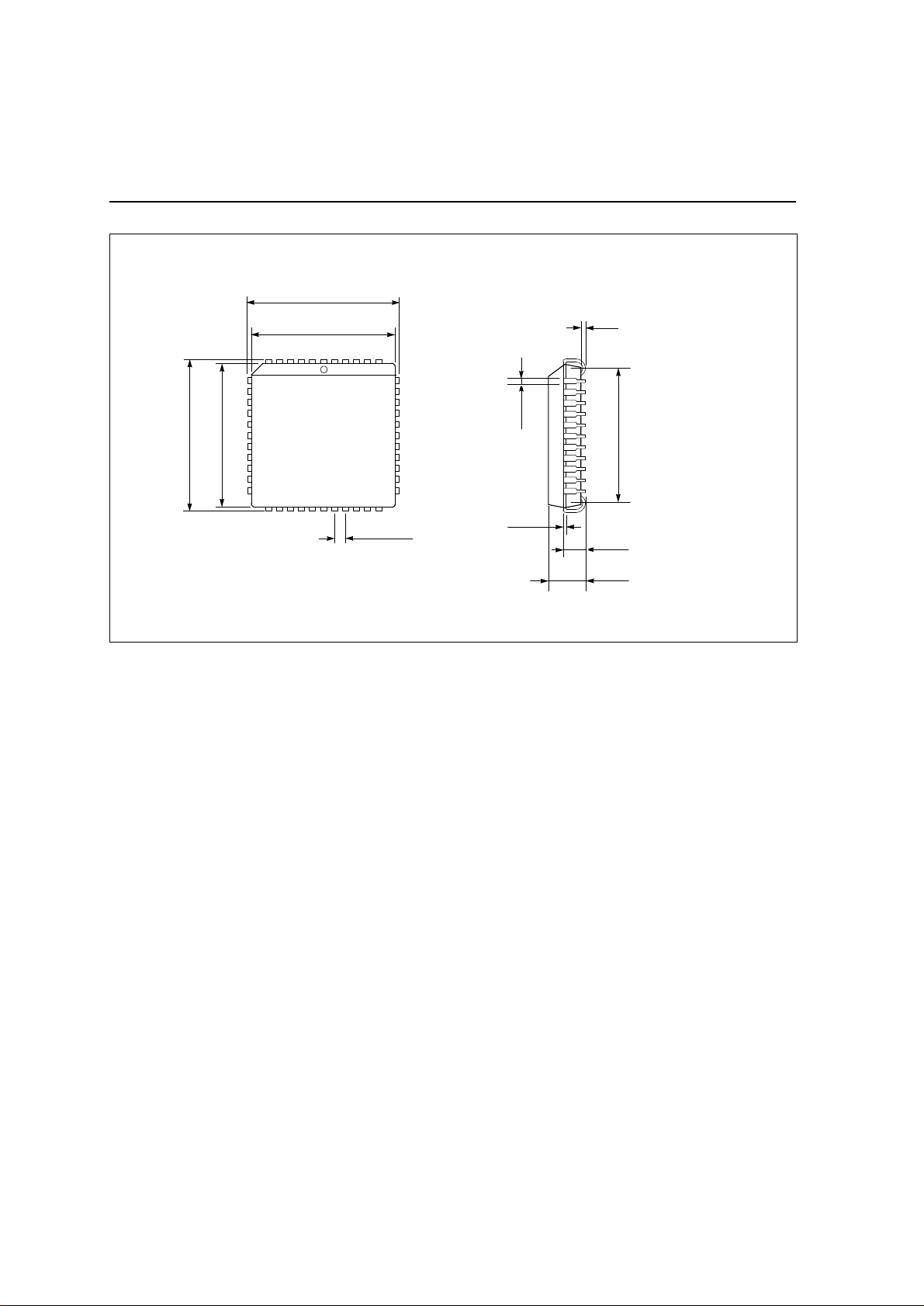

PACKAGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

PIN DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

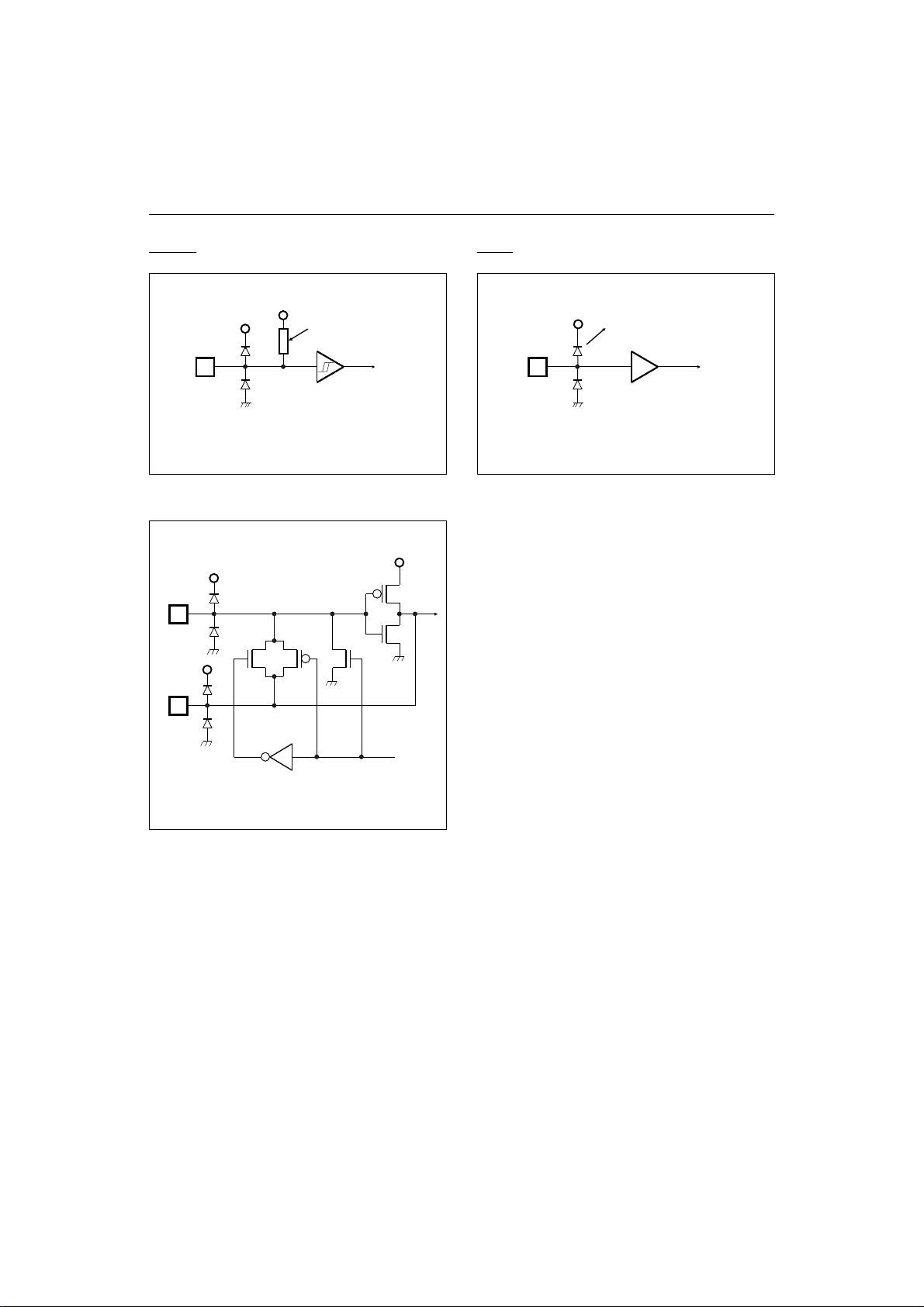

PORT STRUCTURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

MEMORY ORGANIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Program Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Data Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

I/O PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

BASIC INTERVAL TIMER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

TIMER/COUNTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

8-bit Timer/Counter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

16-bit Timer/Counter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

8-bit Capture Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

16-bit Capture Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

ANALOG TO DIGITAL CONVERTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

How to Use A/D Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

BUZZER FUNCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

External Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

BRK Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Multiple Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

WATCHDOG TIMER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Page 4

STOP MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Release Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Minimizing Current Consumption in Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . 43

RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

POWER FAIL PROCESSOR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

OSCILLATOR CIRCUIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

UNUSED PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

GMS81608T (OTP) PROGRAMMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

1. Using the Universal programmer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

2. Using the general EPROM(27C256)

programmer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

GMS81608T PROGRAMMING MANUAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

APPENDIX

A. INSTRUCTION SET

B. MASK ORDER SHEET

Page 5

LG Semicon GMS81604/08

GMS81604 / GMS81608

CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER

OVERVIEW

Description

The GMS81604/08 is a high-performance CMOS 8-bit microcontroller with 4K or 8K bytes of ROM. The device

is one of GMS800 family. The LG Semicon GMS81604/08 is a powerful microcontroller which provides a highly

flexible and cost effective solution to many embedded control applications. The GMS81604/08 provides the

following standard features: 8K bytes of ROM, 256 bytes of RAM, 35 I/O lines(33 lines for 40PDIP), 16-bit or

8-bit timer/counter, a precision analog to digital converter, on-chip oscillator and clock circuitry. In addition, the

GMS81604/08 supports power saving modes to reduce power consumption. The Stop Mode saves the RAM

contents but freezes the oscillator disabling all other chip functions until the next hardware reset or external

interrupt.

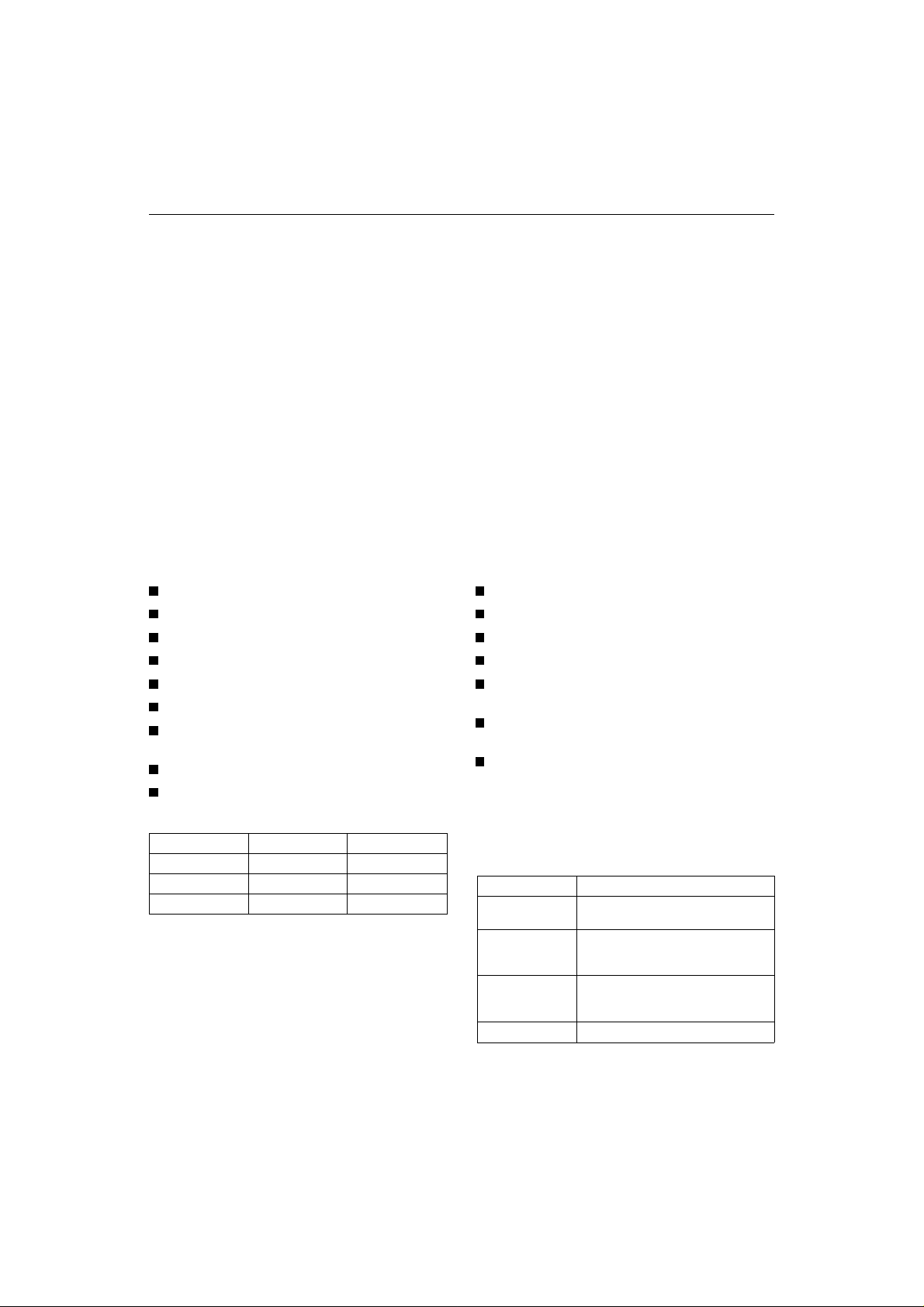

Features

4K/ 8K On-chip Program Memory

256 Bytes of On-Chip Data RAM

Instruction execution time: 0.5us at 8MHz

2.4V to 5.5V Operating Range

1~8 MHz Operating frequency

Basic Interval Timer

Four 8-Bit Timer/ Counters (can be used

as two 16-bit)

Four external interrupt ports

Two Programmable Clock Out

Memory Proliferation

Device ROM Bytes RAM Bytes

GMS81604 4K 256

GMS81608 8K 256

GMS81608T 8K EPROM 256

Development Tools

The GMS800 family is supported by a full-featured

macro assembler, an in-circuit emulators CHOICEJr.TM, socket adapters for OTP device.

The availability of OTP devices are especially useful

for customers expecting frequent code changes and

updates. The OTP devices, packaged in plastic pack-

One Buzzer Driving port

31 Programmable I/O, 4 Input pins,

Twelve Interrupt Sources

All LED Direct Drive Output Ports

8-Channel 8-Bit On-Chip Analog to Digital

Converter

Power Fail Processor

(Noise immunity circuit)

Power Down Mode (Stop Mode)

ages permit the user to program them once. In addition

to the program memory, the configuration fuses must

be programmed.

GMS81604, GMS81608

In-Circuit

Emulators

OTP devices GMS81608T (40 DIP)

Socket

Adapters for

OTP Devices

Assembler LGS Macro Assembler

CHOICE-Jr.

GMS81608T K (42 SDIP)

GMS81608T PL (44 pin PLCC)

OA816A-40PD (40 DIP)

OA816A-42SD (42 SDIP)

OA816A-44PL (44 PLCC)

TM

1

Page 6

GMS81604/08 LG Semicon

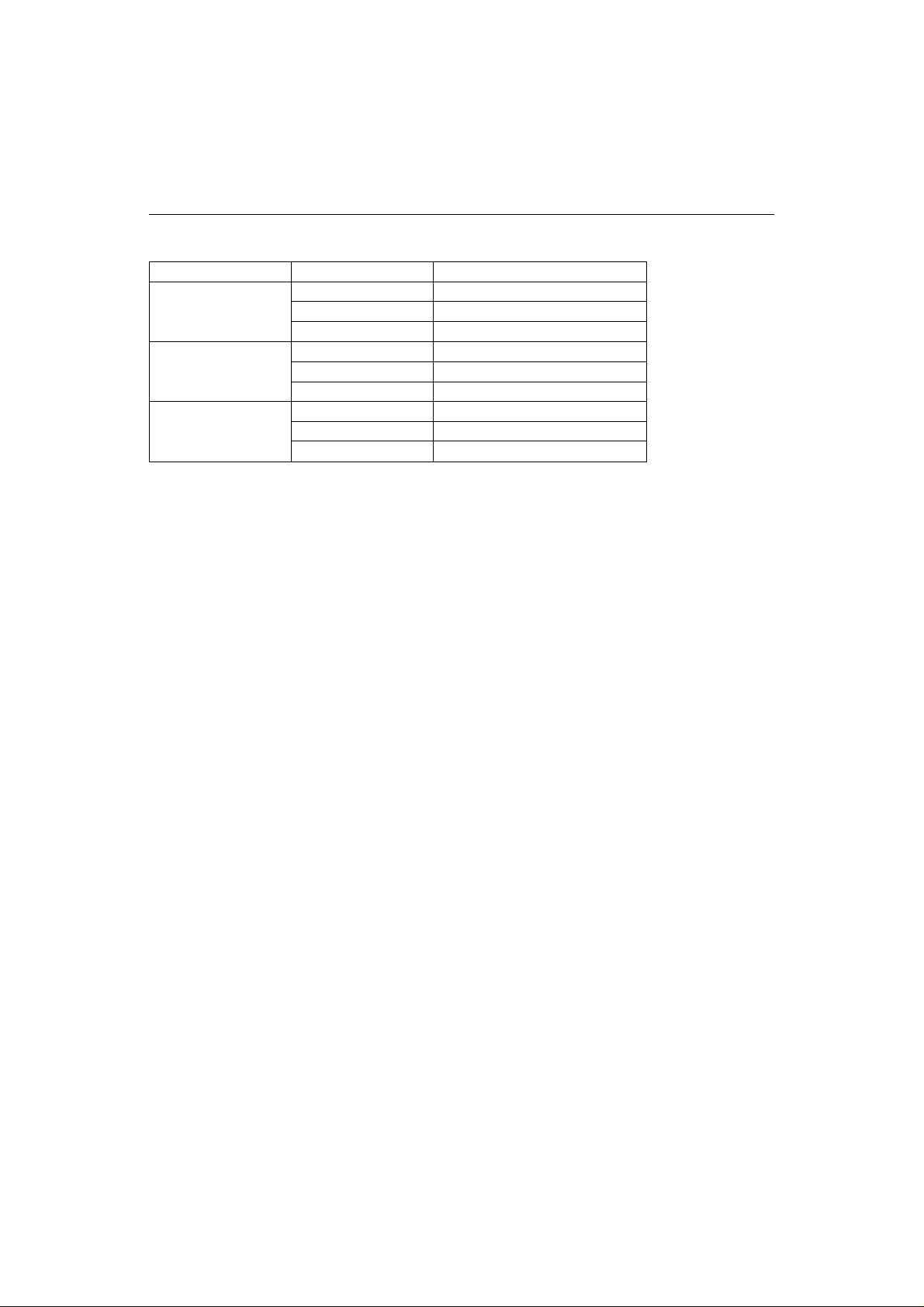

Device Selection Guide

ROM size Package Ordering code

4K bytes 40DIP GMS81604

42SDIP GMS81604 K

44PLCC GMS81604 PL

8K bytes 40DIP GMS81608

42SDIP GMS81608 K

44PLCC GMS81608 PL

8K bytes (OTP) 40DIP GMS81608T

42SDIP GMS81608T K

44PLCC GMS81608T PL

2

Page 7

LG Semicon GMS81604/08

BLOCK DIAGRAM

Figure 1. Block Diagram

3

Page 8

GMS81604/08 LG Semicon

PIN ASSIGNMENT

PACKAGES

Part Package Type

GMS8160X

GMS8160X K

GMS8160X PL

42 SDIP

40DIP

42SDIP

44PLCC

40 PDIP

44 PLCC

Figure 2. Pin Connections

← "X" means 4(4K bytes) or 8(8K bytes).

4

Page 9

LG Semicon GMS81604/08

PACKAGE

42SDIP

UNIT: INCH

1.470

1.450

0.600 BSC

0.550

0-15

0.530

2

1

0

.

0

8

0

0

.

°

0

0.190 max.

min. 0.015

0.020

0.016

0.045

0.035

0.140

0.070 BSC

0.120

40DIP

UNIT: INCH

2.075

2.045

0.600 BSC

0.550

0-15

0.530

2

1

0

.

0

8

0

0

.

°

0

5

0.200 max.

0.022

0.015

0.065

0.045

0.100 BSC

min. 0.015

0.140

0.120

Page 10

GMS81604/08 LG Semicon

44PLCC

UNIT: INCH

0.695

0.685

min. 0.020

0.630

0.590

0.695

0.685

0.656

0.650

0.656

0.650

0.032

0.026

0.050 BSC

0.012

0.0075

0.120

0.090

0.180

0.165

6

Page 11

LG Semicon GMS81604/08

PIN DESCRIPTIONS

V

: Supply voltage.

DD

V

: Circuit Ground.

SS

TEST: For test purposes only. Connect it to V

DD

.

RESET: Reset the MCU.

X

: Input to the inverting oscillator amplifier and

IN

input to the internal clock operating circuit.

X

: Output from the inverting oscillator amplifier.

OUT

R00~R07: R0 is an 8-bit, CMOS, bidirectional I/O

port. As an output port each pin can sink several LS

TTL inputs. R0 pins that have 1 or 0 written to their

Port Direction Mode Register, can be used as outputs

or inputs.

R10~R17: R1 is an 8-bit, CMOS, bidirectional I/O

port. As an output port each pin can sink several LS

TTL inputs. R1 pins that have 1 or 0 written to their

Port Direction Mode Register, can be used as outputs

or inputs.

R40~R47: R4 is an 8-bit, CMOS, bidirectional I/O

port. As an output port each pin can sink several LS

TTL inputs. R4 pins that have 1 or 0 written to their

Port Direction Mode Register, can be used as outputs

or inputs.

In addition, Port 4 serves the functions of the various

following special features.

Port Pin Alternate Function

R40 INT0 (External Interrupt 0)

R41 INT1 (External Interrupt 1)

R42

R43

R44

R45

R46

R47

INT2 (External Interrupt 2)

INT3 (External Interrupt 3)

EC0 (External Count Input to Timer/

Counter 0)

EC2 (External Count Input to Timer/

Counter 2)

T1O (Timer 1 Clock-Out)

T3O (Timer 3 Clock-Out)

R50, R51, R55: R5 is a 3-bit, CMOS, bidirectional I/O

port. As an output port each pin can sink several LS

TTL inputs. R5 pins that have 1 or 0 written to their

Port Direction Mode Register, can be used as outputs

or inputs. R50 and R51 differs in having internal

pull-ups.

Port R55 serves the functions of special features.

Port Pin Alternate Function

R55 BUZ (Square wave output for Buzzer

driving)

R60~R67: R6 is an 8-bit, CMOS, I/O port. R60~R63

can be used as only input, can not be output, R64~R67

are bidirectional I/O port. As an output port each pin

can sink several LS TTL inputs. R64~R67 pins that

have 1 or 0 written to their Port Direction Mode

Register, can be used as outputs or inputs.

R6 serves the functions of following special features.

Port Pin Alternate Function

R60

R61

R62

R63

R64

R65

R66

R67

AV

: Supply voltage to the ladder resistor of ADC

DD

AN0 (ADC input 0)

AN1 (ADC input 1)

AN2 (ADC input 2)

AN3 (ADC input 3)

AN4 (ADC input 4)

AN5 (ADC input 5)

AN6 (ADC input 6)

AN7 (ADC input 7)

circuit. To enhance the resolution of analog to digital

converter, use independent power source as well as

possible, other than digital power source.

7

Page 12

GMS81604/08 LG Semicon

Port Pin I/O

V

DD

V

SS

AV

DD

Descriptions

Primary Functions Secondary Functions

- Power supply to MCU - - - -

- Ground - - - -

- Power supply for ADC - - - -

Pull-up/

Pull-down

RESET

STOP

Mode

TEST I Test mode - - - RESET I Reset the MCU - Pull-up Low Last state

X

IN

X

OUT

R00~R07 I/O General I/O - - Input

R10~R17 I/O General I/O - - Input

R40/INT0

R41/INT1

R42/INT2

R43/INT3

R44/EC0

R45/EC2

R46/T1O

R47/T3O

1)

R50

1)

R51

R55/BUZ

R60/AN0

R61/AN1

R62/AN2

R63/AN3

R64/AN4

R65/AN5

R66/AN6

R67/AN7

I Oscillation input - - Oscillation Low

O Oscillation output - - Oscillation High

3)

Last state

3)

Last state

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

I

I/O

I/O

I/O

I/O

General I/O

"

"

"

"

"

"

"

General I/O

"

"

General Input

"

"

"

General I/O

"

"

"

External interrupt 0

External interrupt 1

External interrupt 2

External interrupt 3

External count input 0

External count input 2

Timer 1 output

Timer 3 output

-

Buzzer driving output

Analog input 0

Analog input 1

Analog input 2

Analog input 3

Analog input 4

Analog input 5

Analog input 6

Analog input 7

- Input

2)

Pull-up

2)

Pull-up

-

- Input

Input

3)

3)

3)

Last state

Last state

Last state

NOTES:

1. R50 and R51 are not physically served on 40 pin package.

2. When input mode is selected, pull-up is activated. In output mode, pull-up is de-activated.

3. In reset status, status of R50,R51 are weak high (Typ. impedance 50~100kΩ). Other pin impedance is very high(High-Z).

8

Page 13

LG Semicon GMS81604/08

PORT STRUCTURES

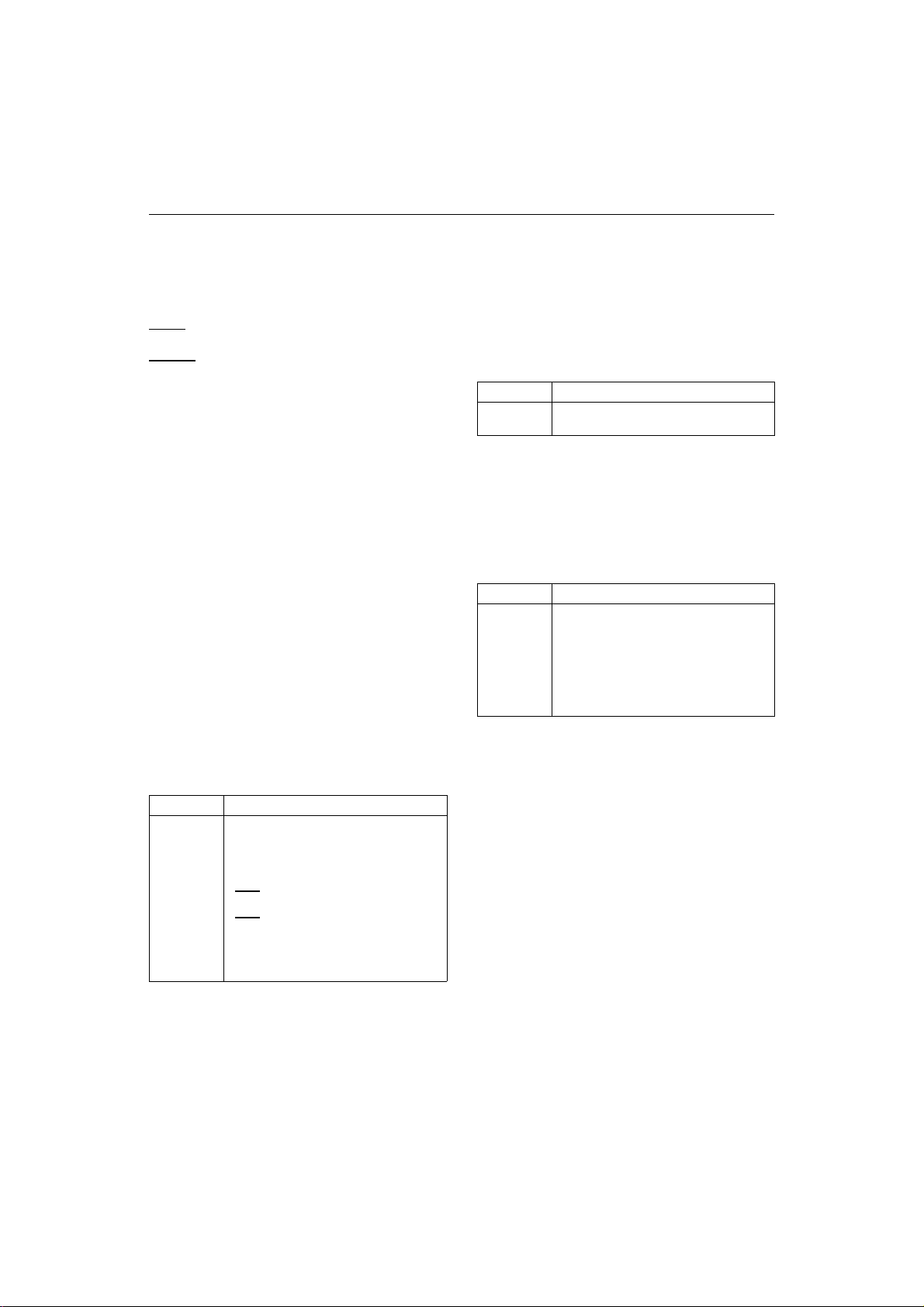

R00~R07, R10~R17

V

DATA BUS

DATA BUS

DATA BUS

DATA REG.

DIRECTION REG.

Rd.

MUX

DD

V

SS

PROTECT DIODE

PROTECT DIODE

R40/INT0, R41/INT1, R42/INT2, R43/INT3, R44/EC0, R45/EC2

PMR4

DATA REG.

DATA BUS

DATA BUS

DIRECTION REG.

DATA BUS

ALTERNATE FUNCTION

EX) INT0

R46/T1O, R47/T3O, R55/BUZ

Selection (PMR4 or PMR5)

ALTERNATE FUNCTION

EX) T1O

DATA BUS

DATA BUS

DATA BUS

MUX

Rd.

MUX

DATA REG.

DIRECTION REG.

MUX

Rd.

9

Page 14

GMS81604/08 LG Semicon

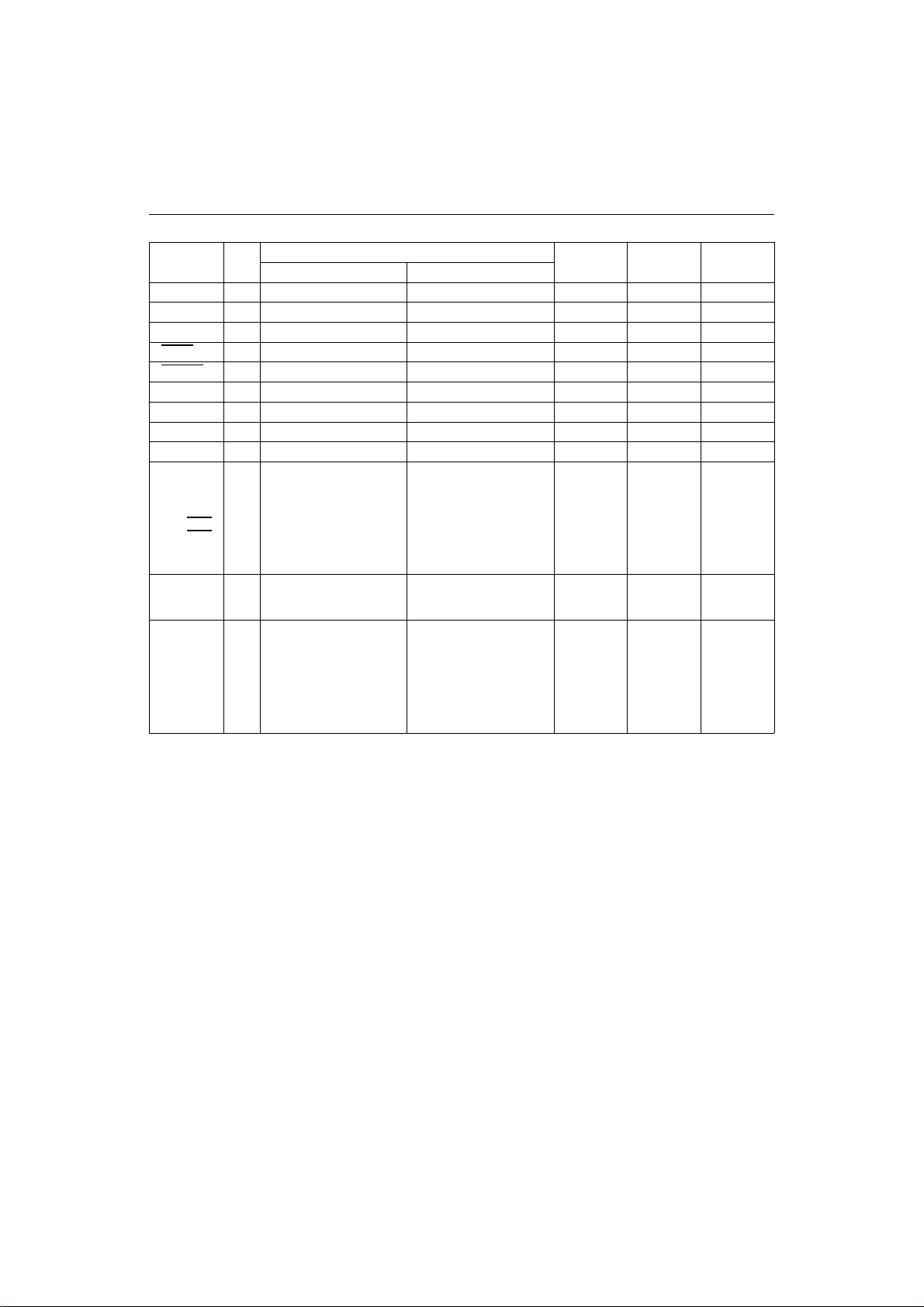

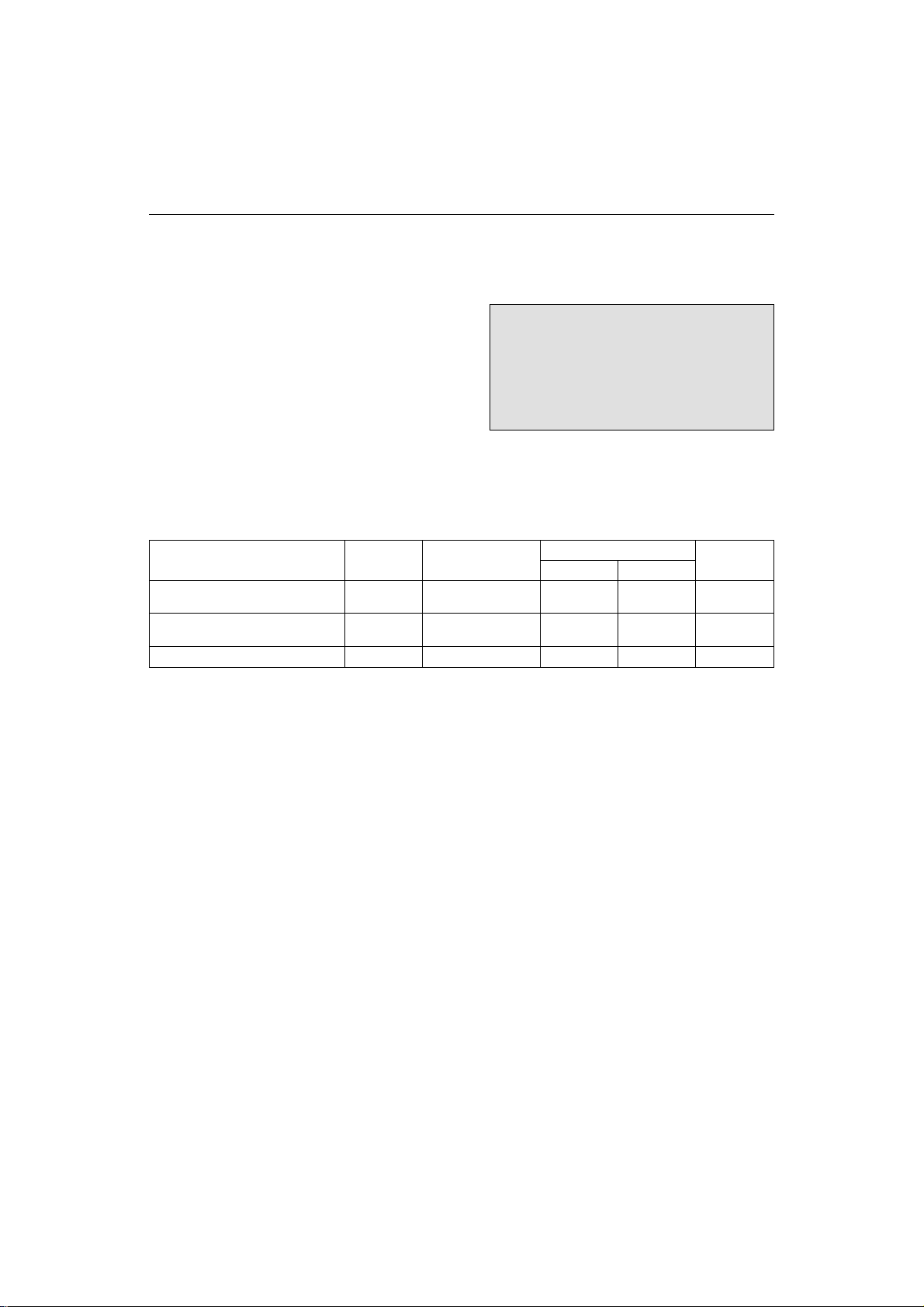

R50, R51

DATA REG.

DATA BUS

DIRECTION REG.

DATA BUS

DATA BUS

Rd.

R60/AN0, R61/AN1, R62/AN2, R63/AN3

DATA BUS

TO A/D Converter

Ch. Select

Rd.

MUX

PULL-UP RESISTOR

INPUT MODE: PULL-UP RESISTOR IS ACTIVATED.

OUTPUT MODE: PULL-UP RESISTOR IS DE-ACTIVATED.

Rd.

R64/AN4, R65/AN5, R66/AN6, R67/AN7

DATA BUS

DATA BUS

DATA BUS

TO A/D Converter

Ch. Select

DATA REG.

DIRECTION REG.

Rd.

10

MUX

0: Output

Rd.

1: Reset, Input, AD ch. select

Page 15

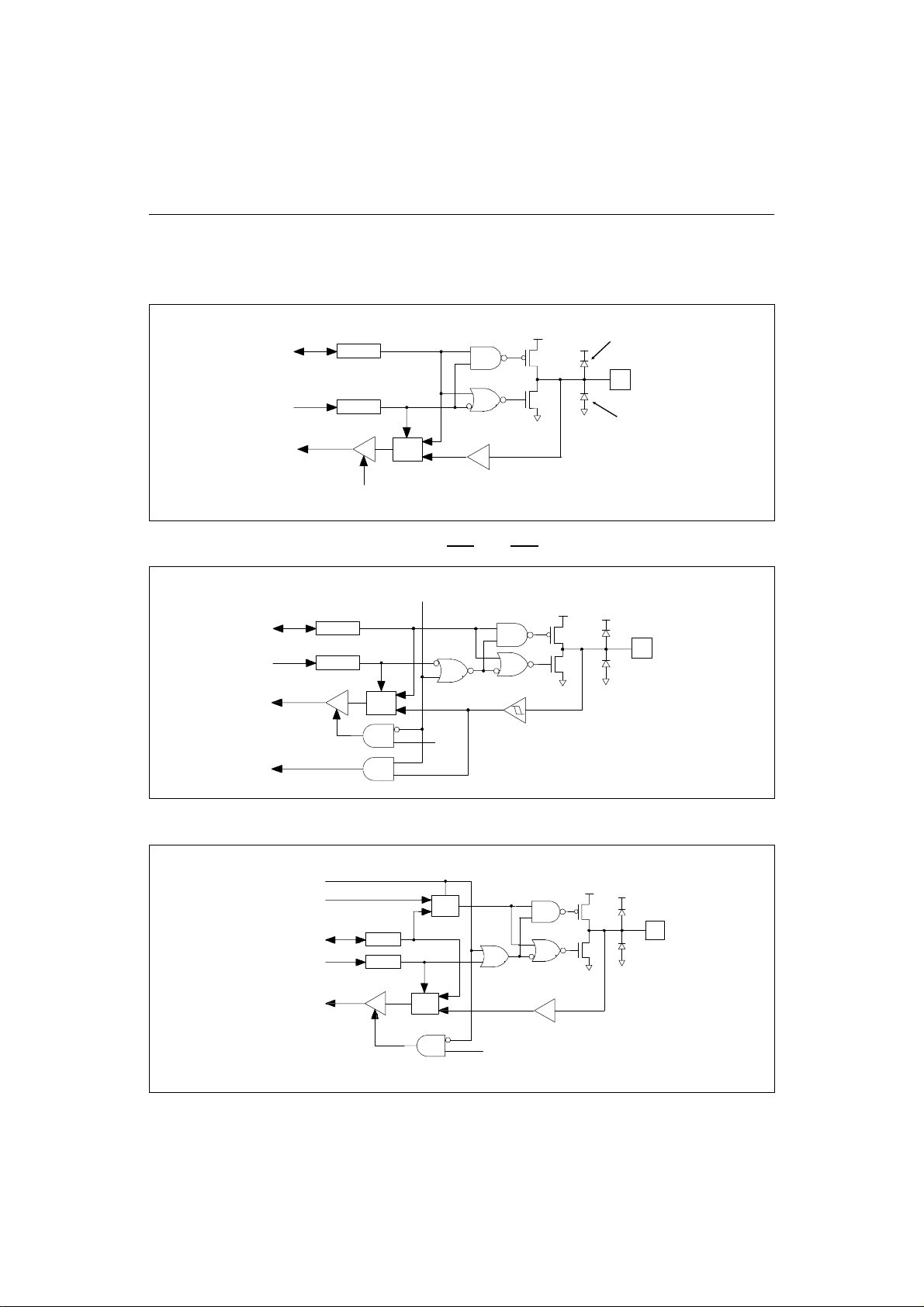

LG Semicon GMS81604/08

RESET

XIN, X

X

IN

X

OUT

OUT

Pull-up Resister

TEST

OTP: No P-Ch diode

STOP

11

Page 16

GMS81604/08 LG Semicon

ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings

Supply Voltage . . . . . . . . . . . . . . . -0.3 to +6.0 V

Storage Temperature . . . . . . . . . . . . -40 to +125 °C

Voltage on any pin with

respect to Ground (VSS) . . . . . . -0.3 to VDD+0.3 V

Maximum current out of VSS pin . . . . . . . . . 150 mA

Maximum current into VDD pin . . . . . . . . . 100 mA

Maximum current sunk by (IOL per I/O Pin) . . . . 20 mA

Maximum output current sourced

by (IOH per I/O Pin) . . . . . . . . . . . . . . . 8 mA

Maximum current (Σ IOL) . . . . . . . . . . . . 120 mA

Maximum current (Σ IOH) . . . . . . . . . . . . . 50 mA

Notice:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to

the device. This is a stress rating only and functional operation of the device at these of any

other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device

reliability.

Recommended Operating Conditions

Parameter Symbol Condition

Supply Voltage V

Operating Frequency f

Operating Temperature T

DD

XIN

OPR

f

= 8 MHz

XIN

f

= 4 MHz

XIN

VDD = 4.5~5.5V

VDD = 2.4~5.5V

Specifications

Min. Max.

4.5

2.4

1

1

5.5

5.5

8

4.2

-20 85

Unit

V

MHz

°C

12

Page 17

LG Semicon GMS81604/08

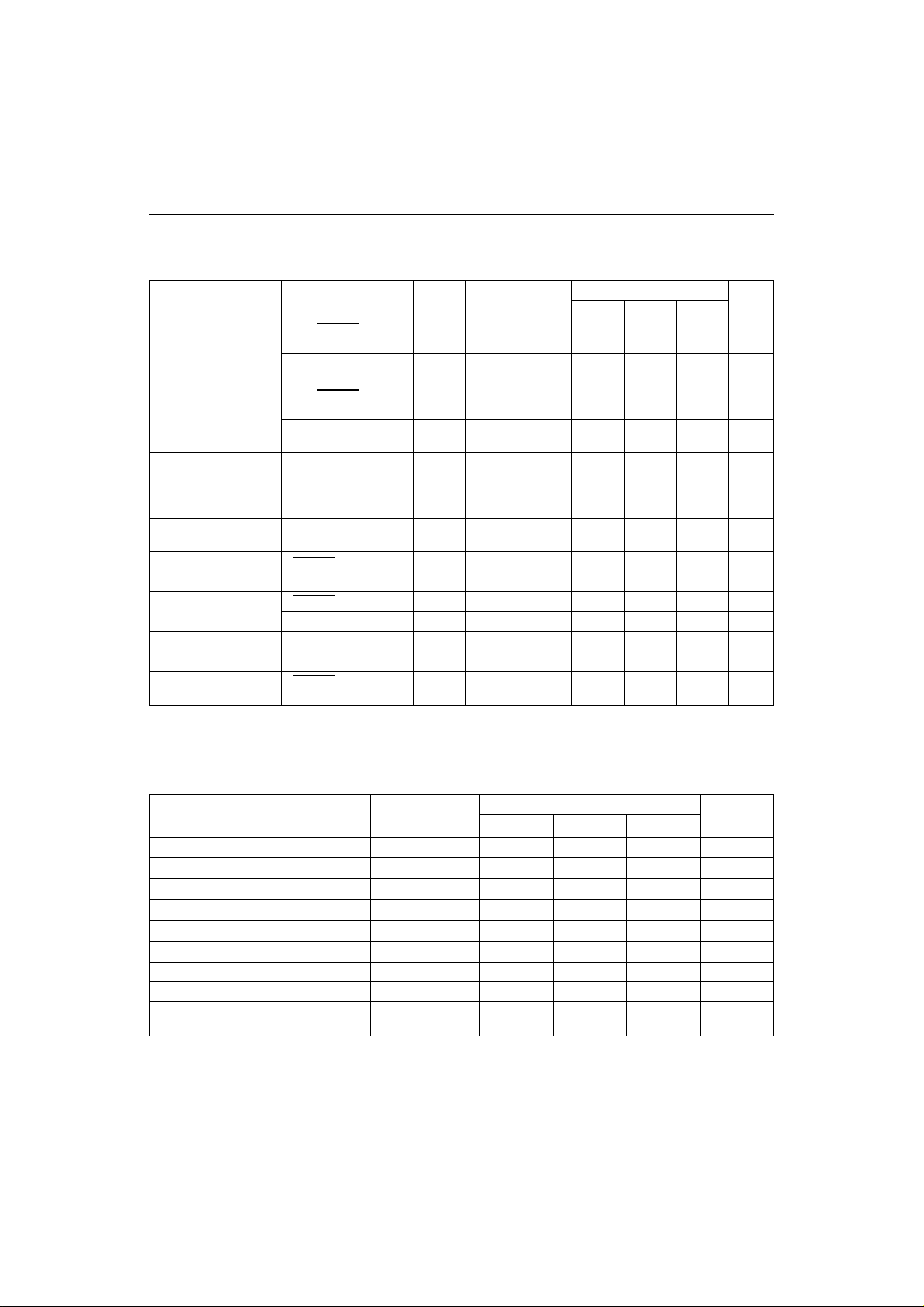

DC Characteristics ( 5V )

(VDD = 5.0V± 10%, VSS = 0V, TA = -20 ~ 85 °C, f

Parameter Pin Symbol Test Condition

XIN, RESET,

Input High Voltage

R40~R45

R0,R1,R46,R47

R5,R6

X

RESET,

IN,

Input Low Voltage

R40~R45

R0,R1,R46,R47

R5,R6

Output High Voltage R0,R1,R4,R5,R6 V

Output Low Voltage R0,R1,R4,R5,R6 V

Power Fail Detect

Voltage

Input Leakage

Current

Input Pull-up Current

Power Current

V

DD

RESET, R0, R1,

R4, R5, R6

RESET I

R50, R51 I

Operating mode I

STOP mode I

Hysteresis

* : Data in "Typ" column is at 5 V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

RESET,

R40~R45

= 8 MHz)

XIN

V

V

V

V

V

PFD

I

I

P1

P2

DD

STOP

VT+

~VT-

Specifications

Min. Typ.* Max.

IH1

IH2

IL1

IL2

OH

OL

- 0.8V

- 0.7V

- 0 - 0.2V

- 0 - 0.3V

VDD = 5V

IOH = -2mA

VDD = 5V

IOL = 10mA

VDD -1.0 VDD -0.4 - V

- 0.6 1.0 V

DD

DD

- V

- V

VDD=3~4V 3.0 - 4.0 V

VI = V

IH

IL

DD

VI = 0V -5.0 - 5.0 uA

-5.0 - 5.0 uA

VDD = 5V -180 -120 -30 uA

VDD = 5V -90 -60 -15 uA

f

XIN

f

XIN

=4MHz

=8MHz

4.5

8

VDD = 5V - 2 20 uA

VDD = 5V 0.5 0.8 - V

15

DD

DD

8

DD

DD

Unit

V

V

V

V

mA

A/D Converter Characteristics ( 5V )

(VDD = 5.0V± 10%, V

Parameter Symbol

Analog Input Range V

Non-linearity Error N

Differential Non-linearity Error N

Zero Offset Error N

Full Scale Error N

Accuracy A

AVDD Input Current I

Conversion Time T

Analog power supply Input

Range

* : Data in "Typ" column is at 5 V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

= 5.0V, VSS = 0V, TA = 25 °C)

AIN

AVDD

V

AIN

LE

DIF

OFF

FS

CC

CONV

AVDD

Specifications

Min. Typ.* Max.

V

SS

- 0.7

- 0.1

- 1.5

- 1.0

- 2.0

- V

AVDD

± 1.5

± 0.5

± 2.5

± 1.5

± 3.0

- 0.5 1.0 mA

- - 40 uS

4.5 5.0 5.5

Unit

V

LSB

LSB

LSB

LSB

LSB

V

13

Page 18

GMS81604/08 LG Semicon

DC Characteristics ( 3V )

(VDD = 3.0V± 10%, VSS = 0V, TA = -20 ~ 85 °C, f

Parameter Pin Symbol Test Condition

XIN, RESET,

Input High Voltage

R40~R45

R0,R1,R46,R47

R5,R6

XIN, RESET,

Input Low Voltage

R40~R45

R0,R1,R46,R47

R5,R6

Output High Voltage R0,R1,R4,R5,R6 V

Output Low Voltage R0,R1,R4,R5,R6 V

Power Fail Detect

Voltage**

Input Leakage

Current

Input Pull-up

Current

Power Current

Hysteresis

* : Data in "Typ" column is at 3 V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**: Power Fail Detection function is not available on 3V operation.

- - - - - - V

RESET, R0, R1,

R4, R5, R6

RESET I

R50, R51 I

Operating mode I

STOP mode I

RESET,

R40~R45

= 4 MHz)

XIN

V

V

V

V

I

I

P1

P2

DD

STOP

VT+

~VT-

Specifications

Min. Typ.* Max.

IH1

IH2

IL1

IL2

OH

OL

IH

IL

- 0.8V

- 0.7V

- 0 - 0.2V

- 0 - 0.3V

VDD = 3V

IOH = -1mA

VDD = 3V

IOL = 5mA

VI = V

DD

VDD -0.5 VDD -0.3 - V

- 0.5 0.7 V

-3.0 - 3.0 uA

VI = 0V -3.0 - 3.0 uA

DD

DD

- V

- V

VDD = 3V -60 -40 -15 uA

VDD = 3V -30 -20 -7.5 uA

f

=4MHz - 2 5 mA

XIN

VDD = 3V - 1 10 uA

VDD = 3V 0.3 0.6 - V

DD

DD

DD

DD

Unit

V

V

V

V

A/D Converter Characteristics ( 3V )

(VDD = 3.0V± 10%, V

Parameter Symbol

Analog Input Range V

Non-linearity Error N

Differential Non-linearity Error N

Zero Offset Error N

Full Scale Error N

Accuracy A

AVDD Input Current I

Conversion Time T

Analog power supply Input

Range

* : Data in "Typ" column is at 3 V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

= 3.0V, VSS = 0V, TA = 25 °C)

AIN

AVDD

V

AIN

LE

DIF

OFF

FS

CC

CONV

AVDD

Specifications

Min. Typ.* Max.

V

SS

- 0.2

- 0.1

- 2.0

- 1.0

- 2.0

- V

AVDD

± 1.0

± 0.5

± 2.5

± 1.5

± 3.0

- 0.3 0.5 mA

- - 40 uS

2.7 3.0 3.3

Unit

V

LSB

LSB

LSB

LSB

LSB

V

14

Page 19

LG Semicon GMS81604/08

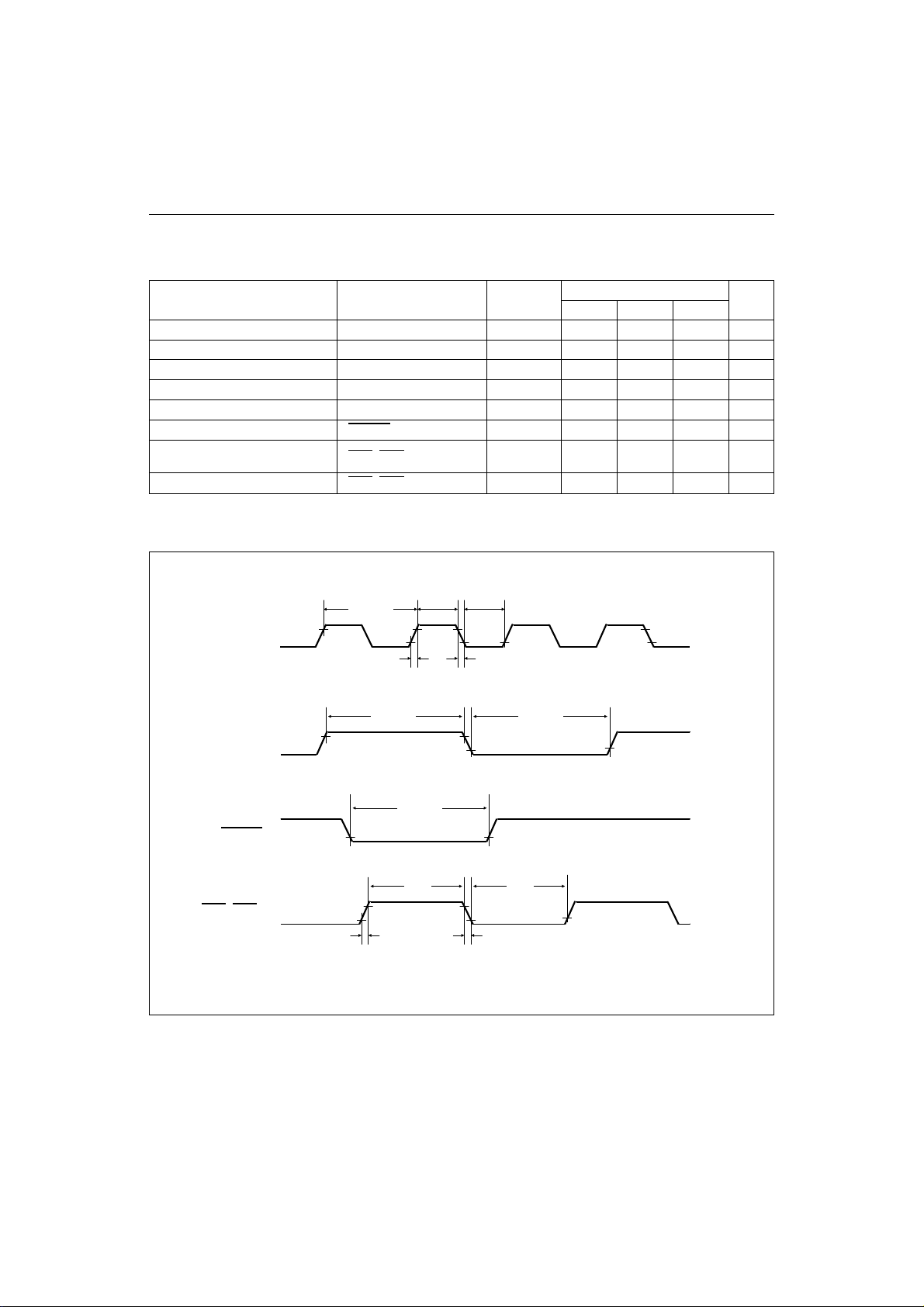

AC Characteristics

(VDD = 2.7~5.5V, VSS = 0V, TA = -20 ~ 85 °C)

Parameter Pin Symbol

Main clock frequency X

Oscillation stabilization Time XIN, X

External Clock Pulse Width X

External Clock Transition Time X

IN

OUT

IN

IN

Interrupt Pulse Width INT0, INT1, INT2, INT3 t

RESET Input Low Width RESET t

Event Counter Input Pulse

Width

EC0, EC2 t

Event Counter Transition Time EC0, EC2 t

*: t

is 2/f

XIN

.

SYS

t

RCP

REC

f

t

t

CPW

RST

ECW

XIN

ST

, t

IW

, t

FCP

FEC

Specifications

Min. Typ. Max.

1 - 8 MHz

20 - - ms

80 - - ns

- - 20 ns

2 - - t

8 - - t

2 - - t

- - 20 ns

Unit

SYS

SYS

SYS

*

*

*

Timing Chart

t

1 / f

XIN

X

IN

CPWtCPW

0.9V

0.1V

DD

DD

INT0, INT1

INT2, INT3

RESET

EC0, EC2

0.8V

t

RCPtFCP

t

IW

DD

0.8V

t

REC

0.2V

DD

t

RST

t

ECW

DD

t

0.2V

FEC

DD

0.2V

t

ECW

t

IW

DD

15

Page 20

GMS81604/08 LG Semicon

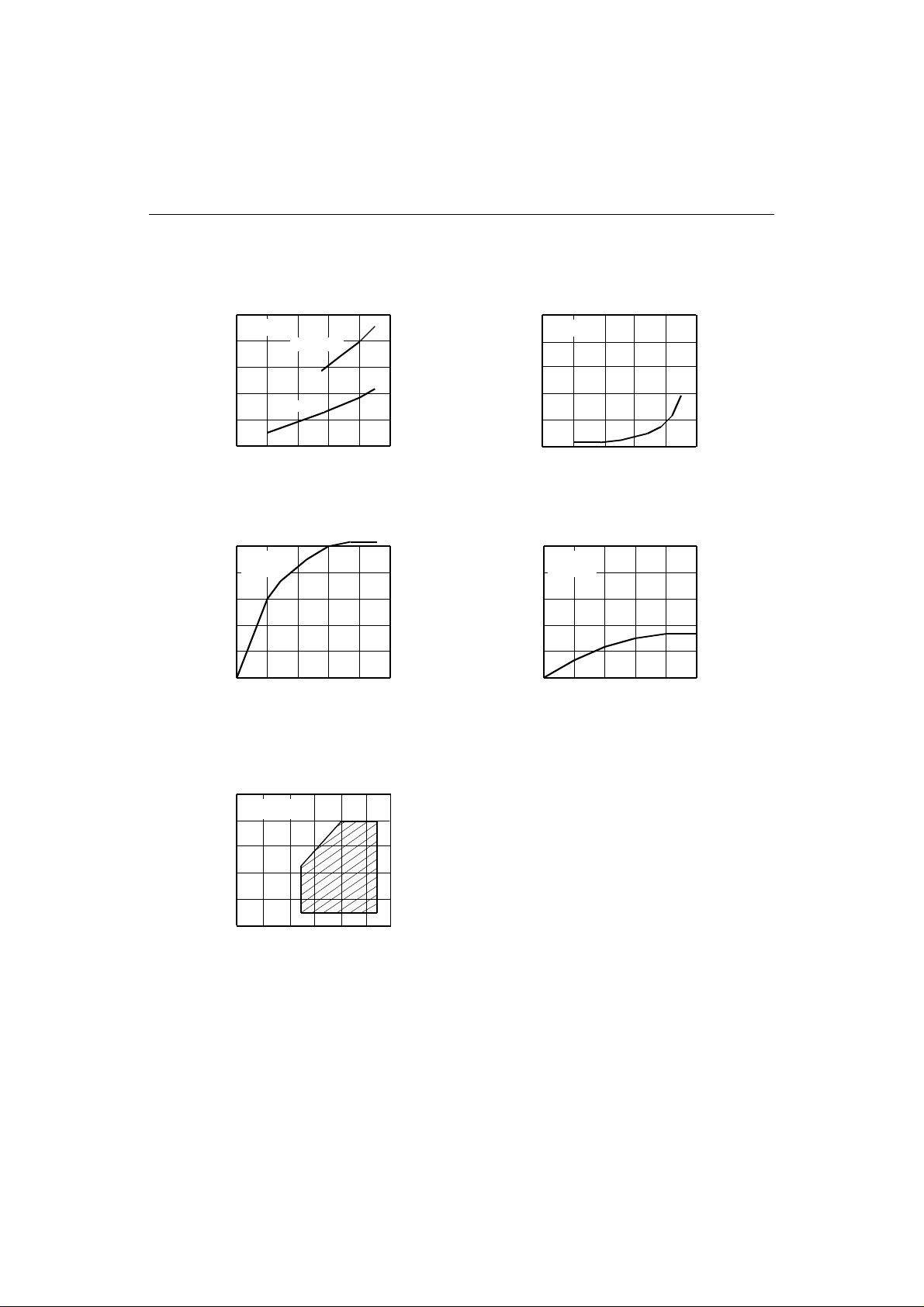

TYPICAL CHARACTERISTICS

These parameters are for design guidance only and are not tested.

VDD=5V

I

DD

(mA)

I

OL

(mA)

IDD - V

DD

TA=25°C

8

6

4

2

IOL - V

VDD=5.0V

24

18

12

6

0

f

XIN

f

= 4MHz

XIN

2 3 4 506 (V)

OL

TA=25°C

1 2 3 4

= 8MHz

I

STOP

I

STOP

(uA)

TA=25°C

8

6

4

2

V

DD

I

(mA)

V

OL

(V)

2 3 4 506 (V)

IOH - V

OH

24

18

12

6

0

OH

VDD=5.0V

TA=25°C

1 2 3 4

VDD-V

(V)

V

DD

OH

16

Operating area

f

XIN

(MHz)

TA = -20~80°C

8

6

4

2

0

1

2 3 4 5

V

DD

(V)

Page 21

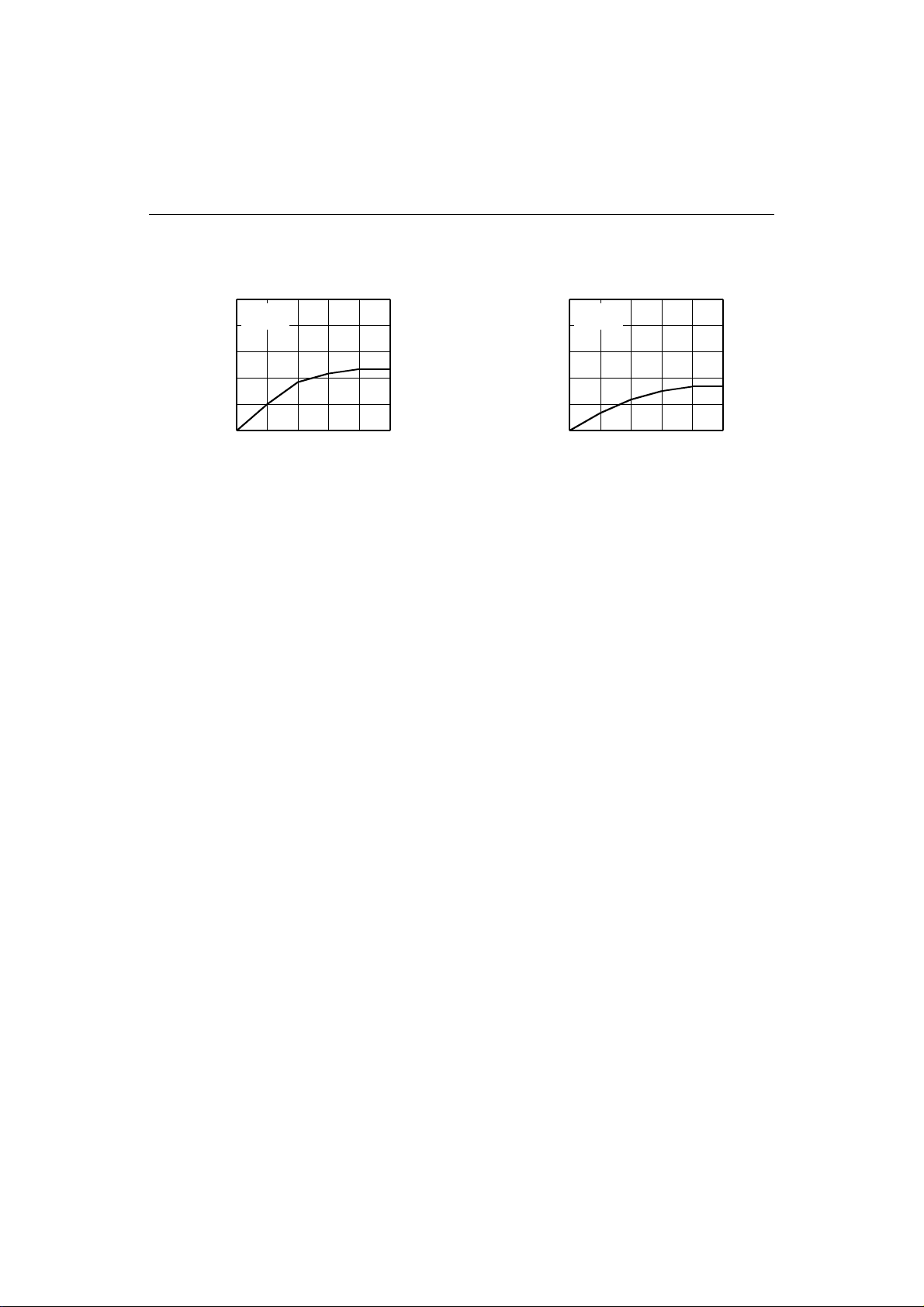

LG Semicon GMS81604/08

VDD=3.0V

I

OL

(mA)

20

IOL - V

VDD=3.0V

TA=25°C

OL

I

OH

(mA)

-8

IOH - V

VDD=3.0V

TA=25°C

OH

15

10

5

0

0.5 1.0 1.5 2.0

-6

-4

-2

VDD-V

V

OL

(V)

0

0.5 1.0 1.5 2.0

OH

(V)

17

Page 22

GMS81604/08 LG Semicon

MEMORY ORGANIZATION

The GMS81604 has separate address spaces for Program and Data Memory. Program memory can only be

read, not written to. It can be up to 4K (8K for

GMS81608) bytes of Program Memory. Data memory can be read and written to up to 256 bytes including

the stack area.

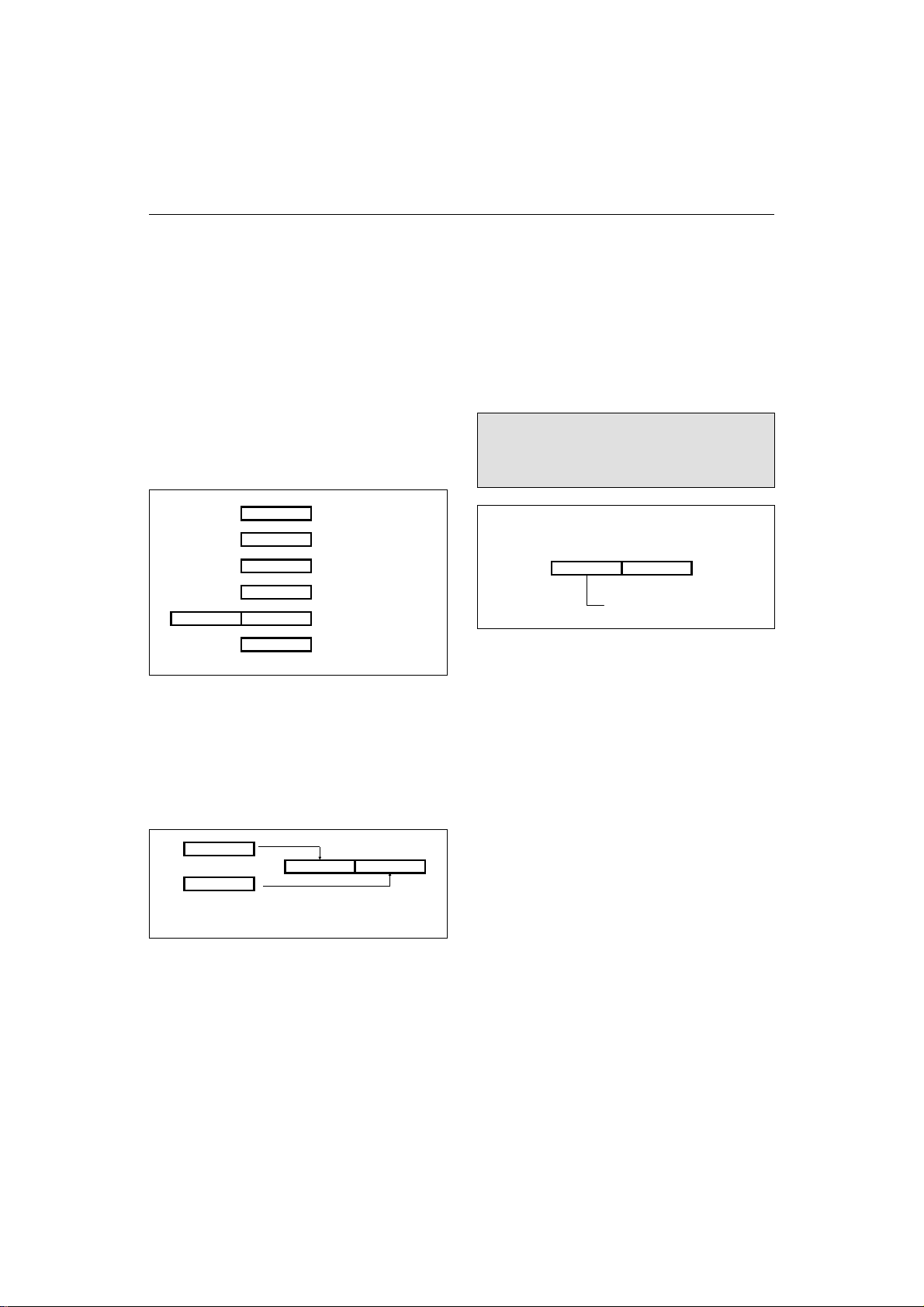

Registers

This device has six registers that are the Program

Counter (PC), a Accumulator (A), two Index registers

(X,Y), the Stack Pointer (SP) and the Program Status

Word (PSW). The Program Counter consists of 16-bit

register.

A

X

Y

SP

PCH PCL

PSW

ACCUMULATOR

X REGISTER

Y REGISTER

STACK POINTER

PROGRAM COUNTER

PROGRAM STATUS

WORD

Figure 3. Configuration of Registers

Accumulator: The accumulator is the 8-bit general

purpose register, used for data operation such as transfer, temporary saving and conditional judgment, etc.

The accumulator can be used as a 16-bit register with

Y register as shown below.

Y

Y A

A

TWO 8-BIT REGISTERS ONE "YA" 16-BIT REGISTER

Figure 4. Configuration of YA 16-bit register

X register, Y register: In the addressing modes which

use these index registers, the register contents are

added to the specified address and this becomes the

actual address. These modes are extremely effective

for referencing subroutine tables and memory tables.

The index registers also have increment, decrement,

compare and data transfer functions and they can be

used as simple accumulators.

Stack Pointer: The stack pointer is an 8-bit register

used for occurrence interrupts and calling out subroutines. The stack can be located at any position within

100H to 13FH of the internal data memory. Data store

and restore sequence to(from) stack area is shown in

Figure 0.

Caution:

The stack pointer must be initialized by software

because its value is undefined after reset.

Ex) LDX #03FH

TXSP ; SP ← 3F

Stack Address (100H~13FH)

15 8 7 0

1 SP

Hardware fixed.

H

Figure 5. Stack Pointer

Program Counter: The program counter is a 16-bit

wide which consists of two 8-bit registers, PCH, PCL.

This counter indicates the address of the next instruction to be executed. In reset state, the program counter

has reset routine address (PCH: FFH, PCL: FEH). .

Program Status Word : The Program Status Word

(PSW) contains several status bits that reflect the current state of the CPU. The PSW shown in Figure 6. It

contains the Negative flag, the Overflow flag, the

Direct page flag, the Break flag, the Half Carry (for

BCD operations), the Interrupt enable flag, the Zero

flag and the Carry bit.

[Carry flag C]

This flag stores any carry or borrow from the ALU of

CPU after an arithmetic operation and is also changed

by the Shift instruction or rotate instruction.

[Zero flag Z]

This flag is set when the result of an arithmetic operation or data transfer is "0" and is cleared by any other

result.

[Interrupt disable flag I] This flag enables/disables all

interrupts except interrupt caused by Reset or software

18

Page 23

LG Semicon GMS81604/08

MSB LSB

PSW

NEGATIVE FLAG

OVERFLOW FLAG

N

V G B H I Z C

RESET VALUE: 00H

CARRY FLAG RECEIVES

CARRY OUT

ZERO FLAG

G FLAG TO SELECT DIRECT PAGE

BRK FLAG

Figure 6. PSW (Program Status Word) Register

BRK instruction. All interrupts are disabled when

cleared to "0". This flag immediately becomes "0"

when an interrupt is served. It is set by the EI instruction, cleared by the DI instruction.

[Half carry flag H]

After operation, set when there is a carry from bit 3 of

ALU or there is not a borrow from bit 4 of ALU. This

bit can not be set or cleared except CLRV instruction,

clearing with Overflow flag (V).

[Break flag B]

This flag set by software BRK instruction to distinguish BRK from TCALL instruction which as the

same vector address.

[Direct page flag G]

This flag assign direct page for direct addressing mode.

In the direct addressing mode, addressing area is

INTERRUPT ENABLE

FLAG

HALF CARRY FLAG RECEIVES

CARRY OUT FROM BIT 1 OF

ADDITION OPERANDS

within zero page 00H to FFH when this flag is "0". If it

is set to "1", addressing area is 100H to 1FFH.

It is set by SETG instruction, and cleared by CLRG.

[Overflow flag V]

This flag is set to "1" when an overflow occurs in the

result of an arithmetic operation involving signs. An

overflow occurs when the result of an addition or

subtraction exceeds +127(7FH) or -128(80H).

The CLRV instruction clears the overflow flag. There

is no set instruction. When the BIT instruction is

executed, for other than the above, bit 6 of memory is

copy to this flag.

[Negative flag N]

This flag is set to match the sign bit (bit 7) status of the

result of a data or arithmetic operation. When the BIT

instruction is executed, bit 7 of memory is copy to this

flag.

1) INTERRUPT

M(SP) ← (PCH)

SP ← SP - 1

M(SP) ← (PCL)

SP ← SP - 1

M(SP) ← (PSW)

SP ← SP - 1 (PCH) ← M(SP)

2) RETI

SP ← SP + 1

(PSW) ← M(SP)

SP ← SP + 1

(PCL) ← M(SP)

SP ← SP + 1

3) CALL

M(SP) ← (PCH)

SP ← SP - 1

M(SP) ← (PCL)

SP ← SP - 1

Figure 7. Stack Operation

4) RET

SP ← SP + 1

(PCL) ← M(SP)

SP ← SP + 1

(PCH) ← M(SP)

5) PUSH A (X,Y,PSW)

M(SP) ← ACC.

SP ← SP - 1

6) POP A (X,Y,PSW)

SP ← SP + 1

M(SP) ← (PCH)

19

Page 24

GMS81604/08 LG Semicon

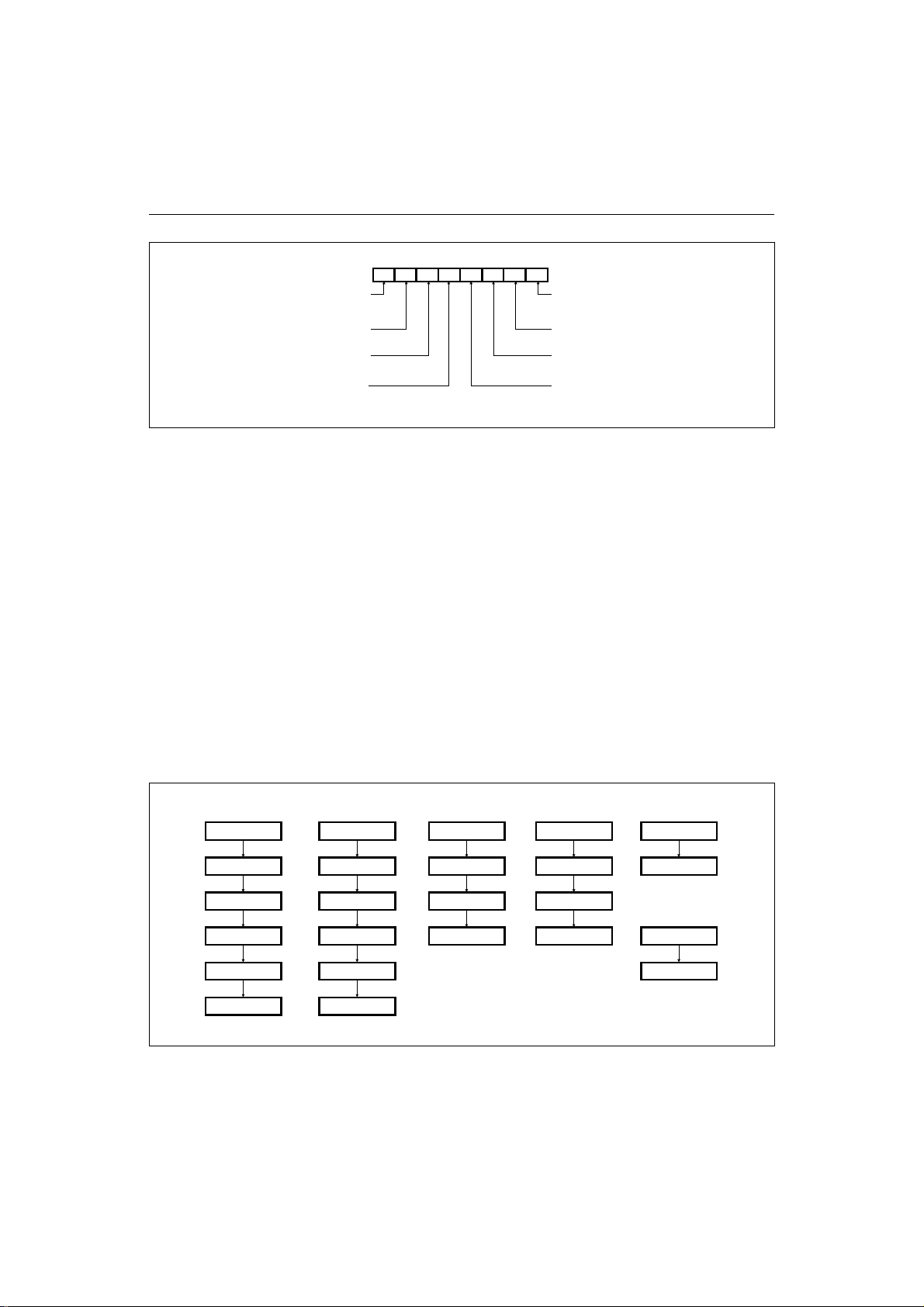

Program Memory

A 16-bit program counter is capable of addressing up

to 64K bytes, but this devices have 4K bytes (8K for

GMS81608) program memory space only the physically implemented. Accessing a location above FFFF

will cause a wrap-around to 0000H.

Figure 8, shows a map of the upper part of the Program

Memory. After reset, the CPU begins execution from

reset vector which is stored in address FFFEH, FFFFH.

As shown in Figure 8, each area is assigned a fixed

location in Program Memory. Program Memory area

contains the user program, Page Call (PCALL) area

contains subroutine program, to reduce program byte

length because of using by 2 bytes PCALL instead of

3 bytes CALL instruction. If it is frequently called,

more useful to save program byte length.

E000H

F000H

PROGRAM

MEMORY

FEFFH

FF00H

FFBFH

FFC0H

FFDFH

FFE0H

FFFFH

PCALL

AREA

TCALL

AREA

INTERRUPT

VECTOR

AREA

GMS81608

GMS81604

Figure 8. Program Memory

Table Call (TCALL) causes the CPU to jump to each

TCALL address, where it commences execution of the

service routine. The Table Call service locations are

spaced at 2-byte interval : FFC0H for TCALL15,

FFC2H for TCALL14, etc.

Address TCALL Name

FFC0H

FFC2H

FFC4H

H

FFC6H

FFC8H

FFCAH

FFCCH

FFCEH

FFD0H

FFD2H

FFD4H

FFD6H

FFD8H

FFDAH

FFDCH

FFDEH

1) The BRK software interrupt is using same address with

TCALL0.

TCALL15

TCALL14

TCALL13

TCALL12

TCALL11

TCALL10

TCALL9

TCALL8

TCALL7

TCALL6

TCALL5

TCALL4

TCALL3

TCALL2

TCALL1

TCALL0/ BRK

1)

The interrupt causes the CPU to jump to specific

location, where it commences execution of the service

routine. The External interrupt 0, for example, is assigned to location FFFAH. The interrupt service locations are spaced at 2-byte interval : FFF8H for External

Interrupt 1, FFFAH for External Interrupt 0, etc.

Any area from FF00H to FFFFH, if it not going to be

used, its service location is available as general purpose Program Memory.

Address Vector Name

FFE0H

FFE2H

FFE4H

FFE6H

FFE8H

FFEAH

FFECH

FFEEH

FFF0H

FFF2H

FFF4H

FFF6H

FFF8H

FFFAH

FFFCH

FFFEH

-

-

Basic Interval Timer

Watch Dog Timer

Analog to Digital Converter

Timer/ Counter 3

Timer/ Counter 2

Timer/ Counter 1

Timer/ Counter 0

External Interrupt 3

External Interrupt 2

External Interrupt 1

External Interrupt 0

RESET

20

Page 25

LG Semicon GMS81604/08

Data Memory

Figure 9 shows the internal Data Memory space available. Data Memory are divided into three groups, a

user RAM, control registers and Stack.

00

H

DATA

MEMORY

(RAM)

BF

C0

100

13F

FF

H

H

CONTROL

REGISTERS

H

H

STACK

H

AREA

256 BYTES

Figure 9. Data Memory

Internal Data Memory addresses are always one byte

wide, which implies an address space of 256 bytes

including the stack area. To access above FFH, G-flag

should be set to "1" before, because after MCU reset,

G-flag is "0".

The stack pointer should be initialized within 00H to

3FH by software because of implemented area of

internal data memory.

The control registers are used by the CPU and Peripheral functions for controlling the desired operation of

the device.

Therefore these registers contain control and status

bits for the interrupt system, the timer/ counters, analog

to digital converters, I/O ports. The control registers

are in address C0H to FFH.

Note that unoccupied addresses may not be implemented on the chip. Read accesses to these addresses

will in general return random data, and write accesses

will have an indeterminate effect.

More detail informations of each register are explained

in each peripheral sections.

Caution:

Write only registers can not be accessed by bit

manipulation instruction.

Address Symbol R/W

C0

C1

C2

C3

C8

C9

CA

CB

CC

CD

D0

D1

D3

D3

E0

E2

E3

E4

E5

E6

E7

E8

E9

EC

ED

F4

F5

F6

F7

F8

Legend - = Unimplemented locations.

X= Undefined value.

NOTES:

1) The all write only registers can not be accessed by bit

manipulation instruction.

2) The register BITR and CKCTLR are located at same address.

Address D3H is read as BITR, as written to CKCTLR.

3) Several names are given at same address. Refer to below

table.

Address

E4H

E5H

E6H

E7H

4) Only bit 0 of ADCM can be read.

R0

H

R0DD

H

R1

H

R1DD

H

R4

H

R4DD

H

R5

H

R5DD

H

R6

H

R6DD

H

PMR4

H

PMR5

H

2)

BITR

H

2)

CKCTLR

H

WDTR

H

TM0

H

TM2

H

H

H

H

H

H

H

H

H

H

H

H

H

H

Note 3

+

Note 3

+

Note 3

+

Note 3

+

ADCM

ADR

BUR

PFDR

IENL

IRQL

IENH

IRQH

IEDS

Timer mode Capture Mode

T0

T1

T2

T3

When read

R/W

1)

W

R/W

W

R/W

W

R/W

W

R/W

W

W

W

R

W

W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

W

R/W

R/W

R/W

R/W

R/W

W

CDR0

CDR1

CDR2

CDR3

1)

1)

1)

1)

1)

1)

1)

1)

1)

1)

Reset Value

4)

Power-on

X

00000000

X

00000000

X

00000000

X

--0---00

X

00000000

00000000

--0-----

00000000

--010111

-0111111

00000000

00000000

X

X

X

X

--000001

X

X

-----100

000----000----00000000

00000000

00000000

When write

TDR0

TDR1

TDR2

TDR3

21

Page 26

GMS81604/08 LG Semicon

Control Registers for the GMS81604/08

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

C0

C1

C2

C3

C8

C9

CA

CB

CC

CD

D0

D1

D3

D3

E0

E2

E3

E4

E5

E6

E7

E8

E9

EC

ED

F4

F5

F6

F7

F8

Legend - = Unimplemented locations.

R0 R0 port data register

H

R0DD R0 port direction register

H

R1 R1 port data register

H

R1DD R1 port direction register

H

R4 R4 port data register

H

R4DD R4 port direction register

H

R5 R5 port data register

H

R5DD R5 port direction register

H

R6 R6 port data register

H

R6DD R6 port direction register

H

PMR4 T3S T1S EC2S EC0S INT3S INT2S INT1S INT0S

H

PMR5 - - BUZS - - - - -

H

1)

BITR Basic Interval Timer data register

H

1)

CKCTLR - - WDTON ENPCK BTCL BTS2 BTS1 BTS0

H

WDTR - WDTCL 6-bit Watch Dog Counter register

H

TM0 CAP0 T1ST T1SL1 T1SL0 T0ST T0CN T0SL1 T0SL0

H

TM2 CAP2 T3ST T3SL1 T3SL0 T2ST T2CN T2SL1 T2SL0

H

T0/ TDR0/ CDR0 Timer 0 register/ Timer data register 0/ Capture data register 0

H

T1/ TDR1/ CDR1 Timer 1 register/ Timer data register 1/ Capture data register 1

H

T2/ TDR2/ CDR2 Timer 2 register/ Timer data register 2/ Capture data register 2

H

T3/ TDR3/ CDR3 Timer 3 register/ Timer data register 3/ Capture data register 3

H

ADCM - - ADEN ADS2 ADS1 ADS0 ADST ADSF

H

ADR ADC result data register

H

BUR BUCK1 BUCK0 BU5 BU4 BU3 BU2 BU1 BU0

H

2)

PFDR - - - - - PFD PFR PFS

H

IENL AE WDTE BITE - - - - -

H

IRQL AIF WDTIF BITIF - - - - -

H

IENH INT0E INT1E INT2E INT3E T0E T1E T2E T3E

H

IRQH INT0IF INT1IF INT2IF INT3IF T0IF T1IF T2IF T3IF

H

IEDS IED3H IED3L IED2H IED2L IED1H IED1L IED0H IED0L

H

NOTES:

1) The register BITR and CKCTLR are located at same address. Address D3H is read as BITR, written to CKCTLR.

2) The register PFDR only be implemented on device, not on In-circuit Emulator.

22

Page 27

LG Semicon GMS81604/08

I/O PORTS

The GMS81604/08 have five ports, R0, R1, R4, R5,

R6. These ports pins may be multiplexed with an

alternate function for the peripheral features on the

device. In general, when a initial reset state, all ports

are used as a general purpose input port.

All pins have data direction registers which can configure these pins as output or input.

A "1" in the port direction register configures the

corresponding port pin as output. Conversely, write

"0" to the corresponding bit to specify as an input pin.

For example, to use the even numbered bit of R1 as

output ports and the odd numbered bits as input ports,

write "55H" to address C1H (R0 direction register)

during initial setting as shown in Figure 10.

WRITE "55H" TO PORT R0 DIRECTION REGISTER

C0H

C1H

C2H

C3H

R0 DATA

R0 DIRECTION

R1 DATA

R1 DIRECTION

0 1 0 1 0 1 0 1

7 6 5 4 3 2 1 0 BIT

I I O I O I OO

7 6 5 4 3 2 1 0 PORT

I: INPUT PORT

O: OUTPUT PORT

Figure 10. Example port I/O assignment

Reading data register reads the status of the pins

whereas writing to it will write to the port latch.

R0 and R0DD registers: R0 is a 8-bit bidirectional

I/O port (address C0H). Each pin is individually configurable as input and output through the R0DD register (address C1H).

Port 0 Data Register

R07 R06 R05 R04 R03 R02 R01 R00

R0

Port 0 Direction Register

R07 R06 R05 R04 R03 R02 R01 R00

R0DD

ADDRESS: C0

RESET VALUE: Undefined

Input/ Output data

ADDRESS: C1

RESET VALUE: 00000000

Direction select

0: Input

1: Output

H

H

R1 and R1DD registers: R1 is an 8-bit bidirectional

I/O port (address C2H). Each pin is individually configurable as input and output through the R1DD register (address C3H).

Port 1 Data Register

R17 R16 R15 R14 R13 R12 R11 R10

R1

Port 1 Direction Register

R17 R16 R15 R14 R13 R12 R11 R10

R1DD

ADDRESS: C2

RESET VALUE: Undefined

Input/ Output data

ADDRESS: C3

RESET VALUE: 00000000

Direction select

0: Input

1: Output

H

H

R4 and R4DD registers: R4 is an 8-bit bidirectional

I/O port (address C8H). Each pin is individually configurable as input and output through the R4DD register (address C9H).

In addition, Port R4 is multiplexed with various special

features. The control register PMR4 (address D0H)

controls to select alternate function. After reset, this

value is "0", port may be used as general I/O ports. To

select alternate function such as External interrupt or

External counter or Timer clock out, write "1" to the

corresponding bit of PMR4.

Port Pin Alternate Function

R40

R41

R42

R43

R44

INT0 (External Interrupt 0)

INT1 (External Interrupt 1)

INT2 (External Interrupt 2)

INT3 (External Interrupt 3)

EC0 (External Count Input to Timer/

Counter 0)

R45

EC2 (External Count Input to Timer/

Counter 2)

R46

R47

T1O (Timer 1 Clock-Out)

T3O (Timer 3 Clock-Out)

Regardless of the direction register R4DD, PMR4 is

selected to use as alternate functions, port pin can be

used as a corresponding alternate features.

23

Page 28

GMS81604/08 LG Semicon

R5 and R5DD registers: R5 is a 3-bit bidirectional

Port 4 Data Register

R47 R46 R45 R44 R43 R42 R41 R40

R4

ADDRESS: C8

RESET VALUE: Undefined

H

I/O port (address CAH). R50, R51 and R55 only are

physically implemented on this device.

R50, R51 have internal pullups which is activated on

input but deactivated on output. As input, these pins

Input/ Output data

that are externally pull low will source current (IP2 on

the DC characteristics) because of the internal pullups.

Port 4 Direction Register

R47 R46 R45 R44 R43 R42 R41 R40

R4DD

Port 4 Mode Register

T3S T1S EC2S EC0S INT3S INT2S INT1S INT0S

PMR4

0: R46

1: T1O

0: R47

1: T3O

Edge Selection Register

MSB LSB

IEDS

INT3 INT2 INT1 INT0

External Interrupt Edge select

00: Reserved

01: Falling (1-to-0 transition)

10: Rising (0-to-1 transition)

11: Both (Rising & Falling)

ADDRESS: C9

RESET VALUE: 00000000

Direction select

0: Input

1: Output

ADDRESS: D0

RESET VALUE: 00000000

0: R44

1: EC0

0: R45

1: EC2

ADDRESS: F8

RESET VALUE: 00000000

0: R43

1: INT3

H

H

0: R42

1: INT2

H

0: R41

1: INT1

0: R40

1: INT0

Caution:

Pins R50, R51 are present on 42SDIP, 44PLCC

package only, but not on 40DIP . Refer to Pin assignment.

Each pin is individually configurable as input and

output through the R5DD register (address CBH).

Port Pin Alternate Function

R55 BUZ (Square-wave output for

Buzzer driving)

The control register PMR5 (address D1H) controls the

selection alternate function. After reset, this value is

"0", port may be used as general I/O ports. To use

buzzer function, write "1" to the PMR5.

Port 5 Data Register

- - R55 - - - R51 R50

R5

Port 5 Direction Register

R5DD

- - R55 - - - R51 R50

Port 5 Mode Register

PMR5

- - BUZS - - - - -

ADDRESS: CA

RESET VALUE: Undefined

Input/ Output data

ADDRESS: CB

RESET VALUE: --0---00

Direction select

0: Input

1: Output

ADDRESS: D1

RESET VALUE: --0-----

H

H

H

24

0: R55

1: BUZ (Buzzer Port)

Page 29

LG Semicon GMS81604/08

R6 and R6DD registers: R6 is an 8-bit port (address

CCH). Pins R64~R67 are indiv idual ly confi gurabl e as

input and output th rough the R6DD registe r (address

CDH), but pins R60~R63 are input only.

Port Pin Alternate Function

R60

R61

R62

R63

R64

R65

R66

R67

AN0 (ADC input 0)

AN1 (ADC input 1)

AN2 (ADC input 2)

AN3 (ADC input 3)

AN4 (ADC input 4)

AN5 (ADC input 5)

AN6 (ADC input 6)

AN7 (ADC input 7)

R6DD (address CDH) controls the direction of the R6

pins, even when they are being used as analog inputs.

The user must make sure to keep the pins configured

as inputs when using them as analog inputs.

On the initial RESET, R60 can not be used digital

input port, because this port is selected as an analog input port by ADCM register. To use this port as

a digital I/O port, change the value of lower 4 bits of

ADCM (address 0E8

On the other hand, R6 port, all eight pins can not be

used as digital I/O port simultaneousely. At least

one pin is used as an analog input.

).

H

Port 6 Data Register

R67 R66 R65 R64 R63 R62 R61 R60

R6

Port 6 Direction Register

R67 R66 R65 R64 R63 R62 R61 R60

R6DD

ADDRESS: CC

RESET VALUE: Undefined

Input/ Output data

ADDRESS: CD

RESET VALUE: 0000----

H

H

Fixed as Input.

Can not write.

Direction select

0: Input

1: Output

25

Page 30

GMS81604/08 LG Semicon

BASIC INTERVAL TIMER

The GMS81604 has one 8-bit Basic Interval Timer that

is free-run, can not stop. Block diagram is shown in

Figure 11.

The 8-bit Basic interval timer register (BITR) is incremented every internal count pulse which is divided by

prescaler. Since prescaler has divided ratio by 16 to

2048, the count rate is 1/16 to 1/2048 of the oscillator

frequency. As the count overflows from FFH to 00H,

this overflow causes to generate the Basic interval

timer interrupt. The BITR is interrupt request flag of

BTS[2:0]

3

8

MUX

XIN PIN

÷16

÷32

÷64

÷128

÷256

÷512

÷1024

÷2048

PRESCALER

Figure 11. Block Diagram of The Basic Interval Timer

CKCTLR

WDTON- ENPCK BTCL BTS1BTS2 BTS0-

Basic interval timer.

Caution:

All control bits of Basic interval timer are in

CKCTLR register which is located at same address of BITR (address D3H). Address D3H is

read as BITR, written to CKCTLR.

When write "1" to bit BTCL of CKCTLR, data register

is cleared to "0" and restart to count-up. It becomes "0"

after one machine cycle by hardware.

BTCL

CLEAR

BITR (8 BITS)

BITIF

BASIC INTERVAL TIMER

INTERRUPT

ADDRESS: D3

RESET VALUE: --010111

H

26

Symbol Position Name and Significance

WDTON CKCTLR.5

ENPCK CKCTLR.4 Enable Peripheral clock.

BTCL CKCTLR.3

BASIC INTERVAL TIMER CLOCK SELECTION

BTS2 BTS1 BTS0 Prescale value

0

0

0

0

0

1

0

1

1

0

1

0

1

1

1

1

WDTON=1, enables Watch Dog Timer operation,

WDTON=0, operates as a 6-bit timer

BTCL is set to "1", BITR is cleared. BTCL becomes "0" automatically

after one machine cycle, and starts counting.

0

1

0

1

0

1

0

1

16

32

64

128

256

512

1024

2048

Figure 12. CKCTLR: Control Clock Register

Page 31

LG Semicon GMS81604/08

TIMER/COUNTER

The GMS81604 has four Timer/Counter registers.

Each module can generate an interrupt to indicate that

an event has occurred (i.e. timer match).

Timer 0 and Timer 1 are can be used either the two

8-bit Timer/Counter or one 16-bit Timer/Counter to

combine them. Also Timer 2 and Timer 3 are same.

In the "timer" function, the register is incremented

every internal clock input. Thus, one can think of it as

counting internal clock input. Since a least clock consists of 4 and most clock consists of 64 oscillator

periods, the count rate is 1/4 to 1/64 of the oscillator

frequency.

In the "counter" function, the register is incremented

in response to a 1-to-0 (falling edge) transition at its

corresponding external input pin, EC0 or EC2.

In addition the "capture" function, the register is incremented in response external or internal clock sources

same with timer or counter function. When external

clock edge input, the count register is captured into

Timer data register correspondingly.

It has four operating modes: "8-bit timer/counter",

"16-bit timer/counter", "8-bit capture", "16-bit capture" which are selected by bit in Timer mode register

TM0 and TM2 as shown in right Table.

In operation of Timer 2, Timer 3, their operations are

same with Timer 0, Timer 1, respectively.

TM0 FOR TIMER 0, TIMER 1

CAP0 T1SL1 T1SL0 Timer 0 Timer 1

0 0 0 16-bit Timer/Counter

1 0 0 16-bit Capture

0 X X 8-bit Timer 8-bit Timer

1 X X 8-bit Capture 8-bit Timer

TM2 FOR TIMER 2, TIMER 3

CAP2 T3SL1 T3SL0 Timer 2 Timer 3

0 0 0 16-bit Timer/Counter

1 0 0 16-bit Capture

0 X X 8-bit Timer 8-bit Timer

1 X X 8-bit Capture 8-bit Timer

LSBMSB

TM0

TM2 is in Figure 14.

Capture mode selection flag, When set, timer

CAP0

operate as one 16-bit capture timer combine

two 8-bit timers.

When set, Timer 1 count register is cleared

T1ST Start/Stop control for Timer 0. A logic 1

and start again.

When cleared, stop the counting.

TIMER 1 TIMER 0

T1SL1 T1SL0

0

0

1

1

NOTE:

If this mode selected, the Timer 0 are used as a 16-bit timer mode. The Timer 1 is engaged to the Timer 0.

The source clock is selected by bits T0SL1 and T0SL0.

INPUT CLOCK

0

16-BIT TIMER MODE (NOTE 1)

1

8-BIT TIMER, ÷ 4 ← PRESCALER

0

8-BIT TIMER, ÷ 16

1

8-BIT TIMER, ÷ 64

T1SL1T1ST T1SL0 T0ST T0SL1T0CN T0SL0CAP0

TIMER 1 TIMER 0

When set, The Timer 0 Count Register is

T0ST

cleared and start again.

When cleared, stop the counting.

T0CN

starts the timer.

T0SL1 T0SL0

0

0

0

1

1

0

1

1

INPUT CLOCK

Timer or Counter select

÷ 4 ← PRESCALER

÷ 16

÷ 64

ADDRESS: E2

RESET VALUE: 00H

Figure 13. TM0: Timer 0, Timer 1 Mode Register

H

27

Page 32

GMS81604/08 LG Semicon

MSB

TM2

Capture mode selection flag, When set, timer

CAP2

operate as one 16-bit timer combine two 8-bit

timers. See Figure 21 and Figure 22.

When set, Timer 3 count register is cleared

T3ST Start/Stop control for Timer 2. A logic 1

and start again.

When cleared, stop the counting.

TIMER 3 TIMER 2

T3SL1 T3SL0

0

0

1

1

NOTE:

If this mode selected, the Timer 2 and Timer 3 are used as a 16-bit timer mode. The Timer 3 is engaged to

the Timer 2. The source clock is selected by bits T2SL1 and T2SL0.

INPUT CLOCK

0

16-BIT TIMER MODE (NOTE 1)

1

8-BIT TIMER, ÷ 4 ←PRESCALER

0

8-BIT TIMER, ÷ 16

1

8-BIT TIMER, ÷ 64

T3SL1T3ST T3SL0 T2ST T2SL1T2CN T2SL0CAP2

TIMER 3 TIMER 2

When set, Timer 2 count register is cleared

T2ST

and start again.

When cleared, stop the counting.

T2CN

starts the timer.

T2SL1 T2SL0

0

0

1

1

LSB

INPUT CLOCK

0

Timer or Counter select

1

÷ 4 ← PRESCALER

0

÷ 16

1

÷ 64

ADDRESS: E3

RESET VALUE: 00

Figure 14. TM2: Timer 2, Timer 3 Mode Register

ADDRESS: E4

RESET VALUE: 00

ADDRESS: E5

RESET VALUE: 00

ADDRESS: E6

RESET VALUE: 00

ADDRESS: E7

RESET VALUE: 00

TDR0

TDR1

TDR2

TDR3

MSB

LSB

H

H

H

H

H

H

H

H

H

H

28

Figure 15. TDRx : Timer x Data Register

Page 33

LG Semicon GMS81604/08

8-bit Timer/Counter Mode

The GMS81604 has four 8-bit Timer/Counters, Timer

0, Timer 1, Timer 2, Timer 3. The Timer 0, Timer 1

only as shown in Figure 16. because other timer/counters are same with Timer 0 and Timer 1.

The "timer" or "counter" function is selected by control

registers TM0, TM2 as shown in Figure 13 and Figure

14. To use as an 8-bit timer/counter mode, bit CAP0

of TM0 is cleared to "0" and bits T1SL1, T1SL0 of

TM0 or bits T3SL1, T3SL0 of TM2 should not set to

zero (Figure 16).

These timers have each 8-bit count register and data

register. The count register is incremented by every

internal or external clock input. The internal clock has

a prescaler divide ratio option of 4, 16, 64 (selected by

control bits TxSL1, TxSL0 of register TMx).

In the Timer 0, timer register T0 increments from 00

MSB LSB

CAP0 T1ST T1SL1 T1SL0 T0ST T0CN T0SL1 T0SL0

TM0

0 X ≠ 0 ≠ 0 X X X X

T0SL[1:0]

EC0 PIN

XIN PIN

EDGE DETECTOR

÷ 4

÷ 16

÷ 64

PRESCALER

MUX

TIMER 0

0

1

T0CN

until it matches TDR0 and then reset to 00H. The match

output of Timer 0 generates Timer 0 interrupt (latched

in T0IF bit)

As TDRx and Tx register are in same address, when

reading it as a Tx, written to TDRx.

Caution:

The contents of Timer data register TDRx should

be initialized 1H~FFH except 0H, because it is undefined after reset.

In counter function, the counter is incremented every

1-to 0 (falling edge) transition of EC0 or EC2 pin. In

order to use counter function, the bit EC0S, EC2S of

the Port mode register PMR4 are set to "1". The Timer

0 can be used as a counter by pin EC0 input, but Timer

1 can not. Similarly, Timer 2 can be used by pin EC2

input but Timer 3 can not.

H

T0ST

0: Stop

1: Clear and Start

T0 (8-BITS)

TDR0 (8-BITS)

CLEAR

COMPARATOR

ADDRESS: E2

RESET VALUE: 00

T0IF

H

TIMER 0

INTERRUPT

H

T1SL[1:0]

MUX

TIMER 1

T1ST

0: Stop

1: Clear and Start

T1 (8-BITS)

TDR1 (8-BITS)

COMPARATOR

Figure 16. 8-bit Timer/Counter Mode

CLEAR

T1IF

F/F

TIMER 1

INTERRUPT

T1O PIN

29

Page 34

GMS81604/08 LG Semicon

To pulse out, the timer match can goes to port pin as

shown in Figure 16. Thus, pulse out is generated by

the timer match. These operation is implemented to

pin, T1O and T3O. The pin T1O is output from Timer

1, the T3O is from Timer 3. Operation of T3O is

omitted in this document, but still presents and same

architecture with T1O.

PMR4

T3S 0: R47

1: T3O (TIMER 3 OUTPUT)

T1S 0: R46

1: T1O (TIMER 1 OUTPUT)

EC2S 0: R45

1: EC2 (EXTERNAL INPUT PIN FOR

TIMER 2

EC0S 0: R44

1: EC0 (EXTERNAL INPUT PIN FOR

TIMER 0

EC2ST1S EC0S INT3S INT1SINT2S INT0ST3S

Figure 17. PMR4: R4 Port Mode Register

When TM0: 00110111 (PRESCALER= 16)

EX)

TDR0

00

TDR0: F9H = 249

OSCILLATOR FREQ.= 4MHz

INTERRUPT PERIOD =

H

1

MATCH

(TDR0 = T0)

F1

F0

3

2

D

1

4 × 106 Hz

F5

F4

F3

F2

× 16 × (249 + 1) = 1ms

F7

F6

f

TxO

INT3S 0: R43

INT2S 0: R42

INT1S 0: R41

INT0S 0: R40

F9

F8

Oscillator Frequency

(Hz) =

2 ⋅ Prescaler ⋅ TDR

LSBMSB

1: INT3 (EXTERNAL INTERRUPT 3)

1: INT2 (EXTERNAL INTERRUPT 2)

1: INT1 (EXTERNAL INTERRUPT 1)

1: INT0 (EXTERNAL INTERRUPT 0)

COUNT PULSE

PERIOD

4 us

CLEAR

ADDRESS: D0

RESET VALUE: 00

H

H

TIMECLEAR CLEAR

30

TIMER 0

INTERRUPT

OCCUR INTERRUPT

INTERRUPT

PERIOD

Figure 18. Timer Count Example

OCCUR INTERRUPT

OCCUR INTERRUPT

Page 35

LG Semicon GMS81604/08

16-bit Timer/Counter Mode

The Timer register is being run with all 16 bits. A 16-bit

timer/counter register T0, T1 are incremented from

0000H until it matches TDR0, TDR1 and then resets

to 0000H. The match output generates Timer 0 interrupt.

The clock source of the Timer 0 is selected either

internal or external clock by bit T0SL1, T0SL0.

MSB

CAP0 T1ST T1SL1 T1SL0 T0ST T0CN T0SL1 T0SL0

TM0

0 X 0 0 X X X X

T0SL[1:0]

EDGE DETECTOR

EC0 PIN

MUX

XIN PIN

THIS FIGURE IS A EXAMPLE OF THE TIMER 0 AND

TIMER 1.

IN THE TIMER 2, EACH REGISTERS AND FLAGS MAY BE

CHANGED CORRESPONDINGLY.

÷ 4

÷ 16

÷ 64

PRESCALER

DO NOT CARE

0

1

T0CN

TIMER 0

(+TIMER1)

Figure 19. 16-bit Timer/Counter Mode

Even if the Timer 0 (including the Timer 1) is used as

a 16-bit timer, the Timer 2 and Timer 3 can still be used

as either two 8-bit timer or one 16-bit timer by setting

the TM2. Reversely, even if the Timer 2 (including the

Timer 3) is used as a 16-bit timer, the Timer 0 and

Timer 1 can still be used as 8-bit timer independently.

T0ST

0: Stop

1: Clear and Start

T1

(8-BITS)

TDR1

(8-BITS)

HIGHER LOWER

T0

(8-BITS)

TDR0

(8-BITS)

LSB

CLEAR

COMPARATOR

ADDRESS: E2

RESET VALUE: 00

T0IF

(NOT TIMER 1 INTERRUPT)

H

H

TIMER 0

INTERRUPT

TDR0

00

TIMER

INTERRUPT

TxST

TxCN

MATCH

Clear and Start

Stop

H

HIGH

LOW

HIGH

LOW

Stop

Restart

MATCH

Count Up

TIMECLEAR CLEAR CLEAR

OCCUR INTERRUPTOCCUR INTERRUPT

Figure 20. Timer Count Operation

31

Page 36

GMS81604/08 LG Semicon

8-bit Capture Mode

The Timer 0 capture mode is set by bit CAP0 of timer

mode register TM0 (bit CAP2 of timer mode register

TM2 for Timer 2) as shown in Figure 21. In this mode,

Timer 1 still operates as an 8-bit timer/counter.

As mentioned above, not only Timer 0 but Timer 2 can

also be used as a capture mode.

In 8-bit capture mode, Timer 1 and Timer 3 are can not

be used as a capture mode.

The Timer/Counter register is incremented in response

internal or external input. This counting function is

same with normal timer mode, but Timer interrupt is

not generated. Timer/Counter still does the above, but

with the added feature that a edge transition at external

MSB LSB

CAP0 T1ST T1SL1 T1SL0 T0ST T0CN T0SL1 T0SL0

TM0

1 X ≠ 0 ≠ 0 X X X X

T0SL[1:0]

EC0 PIN

XIN PIN

EDGE DETECTOR

÷ 4

÷ 16

÷ 64

PRESCALER

IEDS[1:0]

MUX

0

1

T0CN

input INTx pin causes the current value in the Timer x

register (T0,T2), to be captured into registers CDRx

(CDR0, CDR2), respectively. After captured, Timer

x register is cleared and restarts by hardware.

Caution:

The CDRx and TDRx are in same address.

In the capture mode, reading operation is read the

CDRx, not TDRx because path is opened to the

CDRx.

It has three transition modes: "falling edge", "rising

edge", "both edge" which are selected by interrupt

edge selection register IEDS (Refer to External interrupt section). In addition, the transition at INTx pin

generate an interrupt.

T0 (8-BITS)

CAPTURE

CDR0 (8-BITS)

T0ST

0: Stop

1: Clear and Start

ADDRESS: E2

RESET VALUE: 00

THIS FIGURE IS A EXAMPLE OF THE TIMER 0.

IN THE TIMER 2, EACH REGISTERS AND FLAGS

MAY BE CHANGED CORRESPONDINGLY.

H

H

32

INT0 PIN

Figure 21. 8-bit Capture Mode

INT0IF

INT0

INTERRUPT

Page 37

LG Semicon GMS81604/08

16-bit Capture Mode

16-bit capture mode is the same as 8-bit capture, except

that the Timer register is being run will 16 bits.

EC0 PIN

XIN PIN

INT0 PIN

EDGE DETECTOR

÷ 4

÷ 16

÷ 64

PRESCALER

IEDS[1:0]

MSB LSB

CAP0 T1ST T1SL1 T1SL0 T0ST T0CN T0SL1 T0SL0

TM0

1 X 0 0 X X X X

T0SL[1:0]

MUX

DO NOT CARE

T0CN

TIMER 0

+

TIMER 1

0

1

T0ST

0: Stop

1: Clear and Start

T1

(8-BITS)

CDR1

(8-BITS)

HIGHER LOWER

T0

(8-BITS)

CDR0

(8-BITS)

THIS FIGURE IS A EXAMPLE OF USING TIMER 0

AND TIMER 1.

IN THE TIMER 2 AND TIMER 3 EACH

REGISTERS AND FLAGS MAY BE CHANGED.

Figure 22. 16-bit Capture Mode

ADDRESS: E2

RESET VALUE: 00

INT0IF

H

INT 0

INTERRUPT

H

33

Page 38

GMS81604/08 LG Semicon

ANALOG TO DIGITAL CONVERTER

The analog-to-digital converter (A/D) allows conversion of an analog input signal to a corresponding 8-bit

digital value. The A/D module has eight analog inputs,

which are multiplexed into one sample and hold. The

output of the sample and hold is the input into the

converter, which generates the result via successive

approximation. The analog supply voltage is connected to AVDD of ladder resistance of A/D module.

The A/D module has two registers which are the control register ADCM and A/D result register ADR. The

register ADCM, shown in Figure 24, controls the

operation of the A/D converter module. The port pins

can be configured as analog inputs or digital I/O. To

use analog inputs, I/O is selected input mode by R6DD

ADEN

AVDD PIN

R60/AN0

R61/AN1

R62/AN2

R63/AN3

R64/AN4

R65/AN5

R66/AN6

R67/AN7

"0"

"1"

ADS[2:0]

3

000

001

010

011

100

101

110

111

INPUT CHANNEL SELECTION

V

IN

S/H

SAMPLE & HOLD

LADDER

RESISTOR

DECODER

direction register.

How to Use A/D Converter

The processing of conversion is start when the start bit

ADST is set to "1". After one cycle, it is cleared by

hardware. The register ADR contains the results of the

A/D conversion. When the conversion is completed,

the result is loaded into the ADR, the A/D conversion

status bit ADSF is set to "1", and the A/D interrupt flag

AIF is set. The block diagram of the A/D module is

shown in Figure 23. The A/D status bit ADSF is set

automatically when A/D conversion is completed,

cleared when A/D conversion is in process. The conversion time takes maximum 40 uS (at f

SUCCESSIVE

APPROXIMATION

CIRCUIT

ADR

A/D RESULT REGISTER

AIF

ADDRESS: E9

RESET VALUE: Undefined

H

=4 MHz).

XIN

A/D

INTERRUPT

34

Figure 23. A/D Block Diagram

Page 39

LG Semicon GMS81604/08

ADCM

R/W R/W R/W R/W R/W R

LSBMSB

ADEN- ADS2 ADS1 ADSTADS0 ADSF-

RESERVED

Figure 24. ADCM: A/D Converter Control Register

ADDRESS: E8

RESET VALUE: --00001

A/D status bit

0: A/D conversion is in process.

1: A/D conversion is completed, not in

process.

A/D start bit

1: Setting this bit starts an A/D conversion.

After one cycle, bit is cleared to "0".

0: Bit force to zero.

Analog channel select

000: channel 0 (R60/AN0)

001: channel 1 (R61/AN1)

010: channel 2 (R62/AN2)

011: channel 3 (R63/AN3)

100: channel 4 (R64/AN4)

101: channel 5 (R65/AN5)

110: channel 6 (R66/AN6)

111: channel 7 (R67/AN7)

A/D converter Enable bit

0: A/D converter module shut off and

consumes no operating current.

1: Enable A/D converter

H

35

Page 40

GMS81604/08 LG Semicon

BUZZER FUNCTION

The buzzer driver consists of 6-bit binary counter, the

XIN PIN

÷ 16

÷ 32

÷ 64

÷ 128

PRESCALER

MUX

BUR[7:6]

COUNTER

(6 BIT)

BUR[5:0]

(6 BIT)

BUR REGISTER

F/F

BUZ PIN

buzzer register BUR and the clock selector. It generates square-wave which is very wide range frequency

(250 Hz~125 kHz at f

=4 MHz) by user program-

XIN

mable counter.

Pin R55 is assigned for output port of Buzzer driver by

setting the bit 5 of PMR5 (address D1H) to "1". At this

time, the pin R55 must be defined as output mode (the

bit 5 of R5DD=1)

The bit 0 to 5 of BUR determines output frequency for

buzzer driving.

Frequency calculation is following below.

f

f

f

f

Prescaler: Prescaler divide ratio by BUCK1, BUCK0

BUR:Lower 6-bit of BUR. Buzzer period data value

(Hz) =

BUZ

: Buzzer frequency

BUZ

: Min oscillator frequency

XIN

2 ⋅ Prescaler ratio ⋅ BUR value

XIN

The bits BUCK1, BUCK0 of BUR selects the source

clock from prescaler output.

BUR

BU5BUCK0 BU4 BU3 BU1BU2 BU0BUCK1

Buzzer Source Clock Selection

00: fXIN ÷ 16

01: fXIN ÷ 32

10: fXIN ÷ 64

11: fXIN ÷ 128

Figure 26. BUR: Buzzer Period Data Register

Figure 25. Buzzer Driver

The 6-bit buzzer counter is cleared and start the counting by writing signal to the register BUR. It is increment from 00H until it matches 6-bit register BUR.

Caution:

The register BUR contains undefined value after

reset. It must be initialized none 0H(1H~3FH).

LSBMSB

Buzzer Period Data

ADDRESS: EC

RESET VALUE: Undefined

H

36

PMR5

LSBMSB

BUZS- - - -- --

R55/ BUZ Port Selection

0: R55

1: BUZ

Figure 27. PMR5: Port 5 Mode Register

ADDRESS: D1

RESET VALUE: --0-----

H

Page 41

LG Semicon GMS81604/08

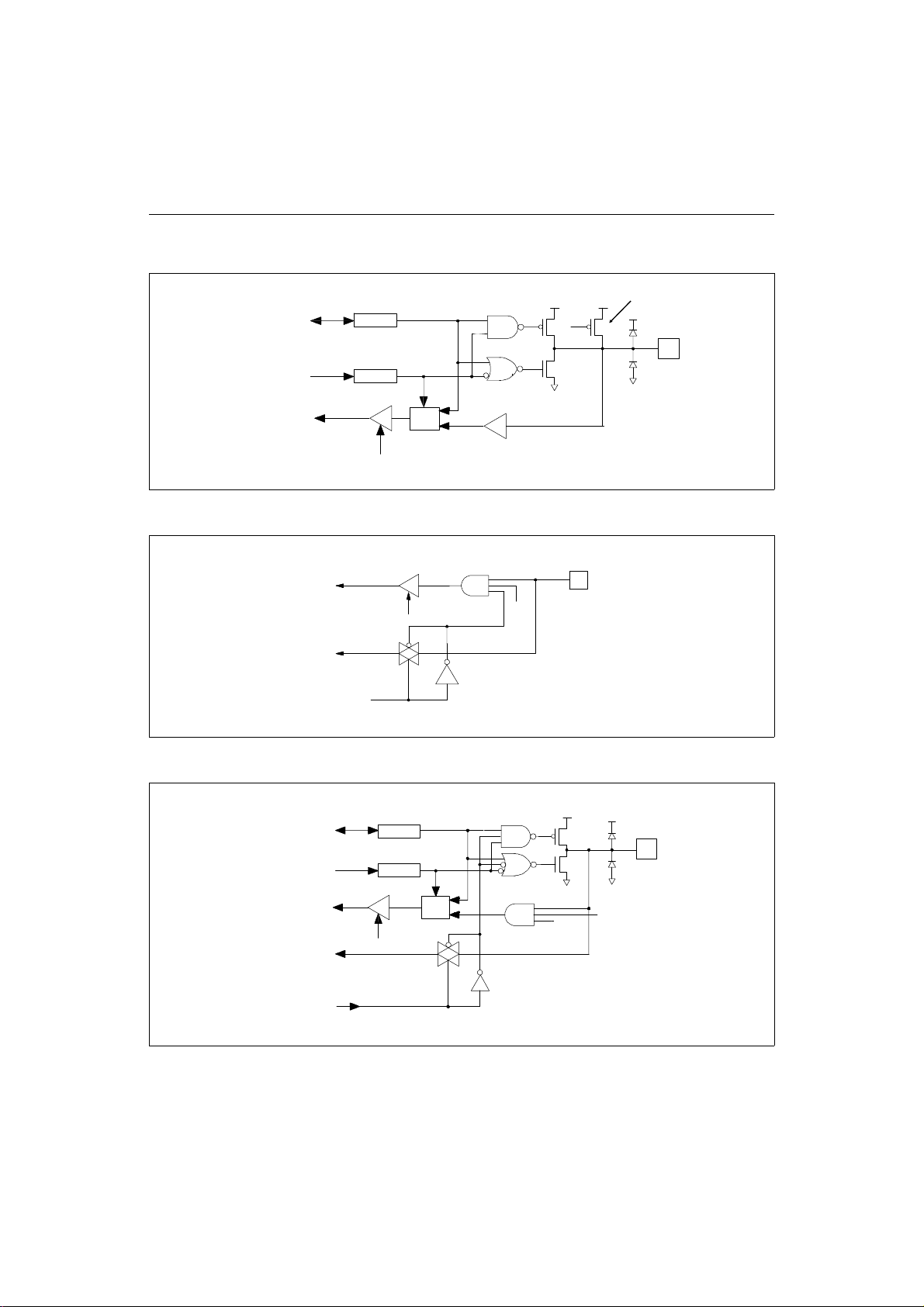

INTERRUPTS

The GMS81604/08 interrupt circuits consist of Interrupt enable register (IENH, IENL), Interrupt request

flags of IRQH, IRQL, priority circuit and Master enable flag(I flag of PSW). The configuration of interrupt

circuit is shown in Figure 28.

12 interrupt sources are provided including the Reset.

Interrupt source Symbol Priority

Hardware RESET

External Interrupt 0

External Interrupt 1

External Interrupt 2

External Interrupt 3

Timer/Counter 0

Timer/Counter 1

Timer/Counter 2

Timer/Counter 3

AD Converter

Watch dog timer

Basic interval timer

*Vector addresses are shown in Program Memory

section.

INT0

INT1

INT2

INT3

TIMER 0

TIMER 1

TIMER 2

TIMER 3

ADC

WDT

BASIC INTERVAL

TIMER

IRQH

INT0IF

INT1IF

INT2IF

INT3IF

T0IF

T1IF

T2IF

T3IF

IRQL

WDTIF

BITIF

RST

INT0IF

INT1IF

INT2IF

INT3IF

T0IF

T1IF

T2IF

T3IF

AIF

WDTIF

BITIF

AIF

MSB

LSB

BIT 7

BIT 6

BIT 5

IENH

IENL

10

11

12

1

2

3

4

5

6

7

8

9

0

1

The External Interrupts INT0~INT3 can each be transition-activated, depending on interrupt edge selection

register.

The Timer 0~Timer 3 Interrupts are generated by T0IF

~T3IF, which are set by a match in their respective

timer/counter register.

The AD converter Interrupt is generated by AIF which

is set by finishing the analog to digital conversion.

The Watch dog timer Interrupt is generated by WDTIF

which set by a match in Watch dog timer register.

The Basic Interval Timer Interrupt is generated by

BITIF which are set by a overflow in the timer/counter

register.

The interrupts are controlled by the interrupt master

enable flag I-flag (bit 2 of PSW), the interrupt enable

register (IENH, IENL) and the interrupt request flags

(in IRQH, IRQL) except Power-on reset and software

BRK interrupt.

Interrupt enable registers are shown in Figure 29.

These registers are composed of interrupt enable flags

of each interrupt source, these flags determines

I-flag is in PSW, it is cleared by "DI", set by "EI"

instruction.

When it goes interrupt service, I-flag is cleared by

hardware, thus any other interrupt are inhibited.

When interrupt service is completed by "RETI"

instruction, I-flag is set to "1" by hardware.

BRK (Software Interrupt)

PRIORITY

CONTROL

0

1

I-FLAG

Master Enable Flag

RELEASE THE STOP

(IF IN STOP MODE)

TO CPU

RESET

Figure 28. Block Diagram of Interrupt Function

37

Page 42

GMS81604/08 LG Semicon

LSBMSB

IENH

INT2EINT1E INT3E T0E T2ET1E T3EINT0E

ADDRESS: F6

RESET VALUE: 00

H

H

MSB LSB

IENL

BITEWDTE - - -- -AE

Enables or disables the interrupt individually.

If flag is cleared, the interrupt is disabled.

0: Disable

1: Enable

Figure 29. IENH, IENL: Interrupt Enable Registers

whether an interrupt will be accepted or not. When

enable flag is "0", a corresponding interrupt source is

prohibited. Note that PSW contains also a master enable bit, I-flag, which disables all interrupts at once.

When an interrupt is responded to, the I-flag is cleared

to disable any further interrupt, the return address is

pushed into the stack and the PC is vectored to. Once

in the interrupt service routine the source(s) of the

interrupt can be determined by polling the interrupt

flag bits.

The interrupt flag bit(s) must be cleared in software

before reenabling interrupts to avoid recursive interrupts. The Interrupt Request flags are able to be read

and write.

External Interrupt

External interrupt on INT0~INT3 pins are edge triggered depending the edge selection register IEDS.

The edge detection of external interrupt has three

transition activated mode: rising edge, falling edge,

both edge. INT0~INT3 are multiplexed with general

I/O ports (R40~R43). To use external interrupt pin, set

ADDRESS: F4

RESET VALUE: 000-----

H

bit 0 to bit 3 of the port mode register PMR4.

The PMR4 and IEDS registers are shown in Figure

32.

EDGE DETECTOR

IEDS[1:0]

INT0

INT1

INT2

INT3

IEDS[3:2]

IEDS[5:4]

IEDS[7:6]

INT0IF

INT1IF

INT2IF

INT3IF

INT0 INTERRUPT

INT1 INTERRUPT

INT2 INTERRUPT

INT3 INTERRUPT

Figure 30. External Interrupt

38

Page 43

LG Semicon GMS81604/08

MAX. 13 f

f

XIN

INTERRUPT

ACTIVE

INSTRUCTION EXECUTION

(INTERRUPT HOLDING)

PMR4

Relation with Timer/Counter Function

T3S 0: R47

1: T3O (TIMER/COUNTER 3 OUTPUT)

T1S 0: R46

1: T1O (TIMER/COUNTER 1 OUTPUT)

EC2S 0: R45

1: EC2 (EXTERNAL INPUT PIN FOR

TIMER/COUNTER 2

EC0S 0: R44

1: EC0 (EXTERNAL INPUT PIN FOR

TIMER/COUNTER 0

IEDS

8 f

OSC

OSC

INTERRUPT

PROCESSING

Figure 31. INT Pin Interrupt Timing

EC2ST1S EC0S INT3S INT1SINT2S INT0ST3S

IED2HIED3L IED2L IED1H IED0HIED1L IED0LIED3H

INT3 INT2 INT1 INT0

INTERRUPT

ROUTINE

LSBMSB

Relation with External Interrupt function

INT3S 0: R43

1: INT3 (EXTERNAL INTERRUPT 3)

INT2S 0: R42

1: INT2 (EXTERNAL INTERRUPT 2)

INT1S 0: R41

1: INT1 (EXTERNAL INTERRUPT 1)

INT0S 0: R40

1: INT0 (EXTERNAL INTERRUPT 0)

LSBMSB

ADDRESS: D0

RESET VALUE: 00

ADDRESS: F8

RESET VALUE: 00

H

H

H

H

Edge selection register

00: Reserved

01: Falling (1-to-0 transition)

10: Rising (0-to-1 transition)

11: Both (Rising & Falling)

Figure 32. PMR4 and IEDS Registers

39

Page 44

GMS81604/08 LG Semicon

BRK Interrupt

Software interrupt can be invoked by BRK instruction,

which is the lowest priority order.

Interrupt vector address of BRK is shared with the

vector of TCALL0 (Refer to Program Memory Section). When BRK interrupt is generated, B-flag of

PSW is set to distinguish BRK from TCALL0.

Each processing step is determined by B-flag as shown

below.

= 0

B-FLAG

BRK or

TCALL0

= 1

BRK

INTERRUPT