Page 1

G-LINK

GLT6400M08

Ultra Low Power 512k x 8 CMOS SRAM

Nov 2000(Rev. 2.0)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 1 -

Features : Description :

∗ Low-power consumption.

-active: 30mA at 120ns.

-stand by :

20 µA (CMOS input / output)

5 µA (CMOS input / output, SL)

∗ Single +2.3 to 2.7V power supply.

∗ Equal access and cycle time.

∗ 120 ns access time.

∗ 1.0V data retention mode.

∗ TTL compatible, tri-state input/output.

∗ Automatic power-down when deselected.

∗ Industrial grade (-40°C ~ 85°C)

availabel.

∗ Package available: sTSOP.

The GLT6400M08 is a low power CMOS Static

RAM organized as 524,288 x 8 bits. Easy memory

expansion is provided by an active LOW CE1 an

active LOW OE , and Tri-state I/O’s. This device has

an automatic power-down mode feature when

deselected.

Writing to the device is accomplished by taking

chip Enable 1 ( CE1 ) with Write Enable ( WE ) LOW.

Reading from the device is performed by taking Chip

Enable 1 ( CE1 ) with Output Enable ( OE ) LOW

while Write Enable ( WE ) and Chip Enable 2 (CE2)

is HIGH. The I/O pins are placed in a high-impedance

state when the device is deselected : the outputs are

disabled during a write cycle.

The GLT6400M08 comes with a 1V data retention

feature and Lower Standby Power. The

GLT6400M08 is available in a 32-pin sTSOP

packages.

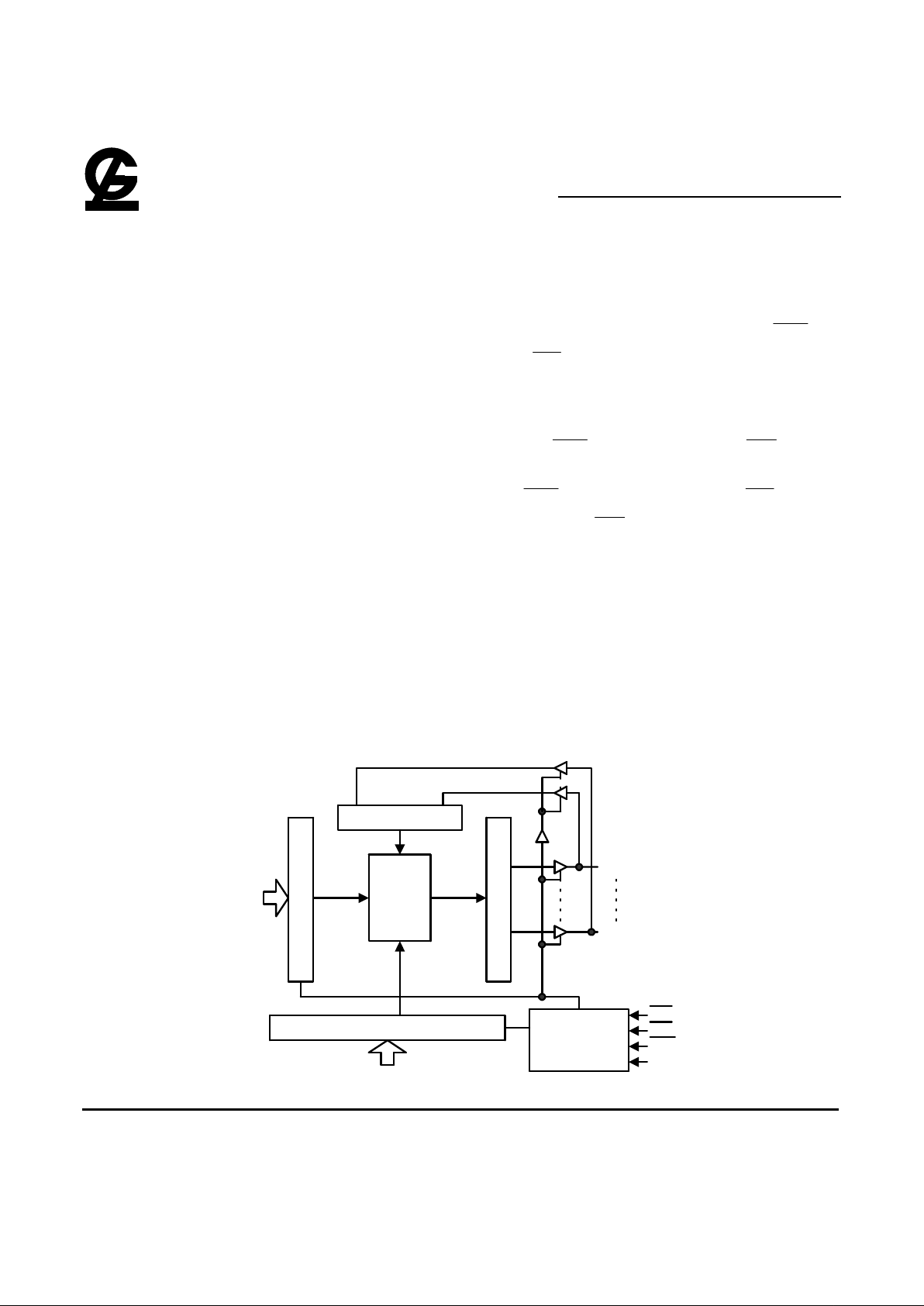

Function Block Diagram :

ROW DECODER

Cell

Array

SENSE AMP

INPUT BUFFER

COLUMN DECODER

CONTROL

CIRCUIT

OE

WE

CE1

CE2

I/O7

I/O1

Column Address

Row Address

Page 2

G-LINK

GLT6400M08

Ultra Low Power 512k x 8 CMOS SRAM

Nov 2000(Rev. 2.0)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 2 -

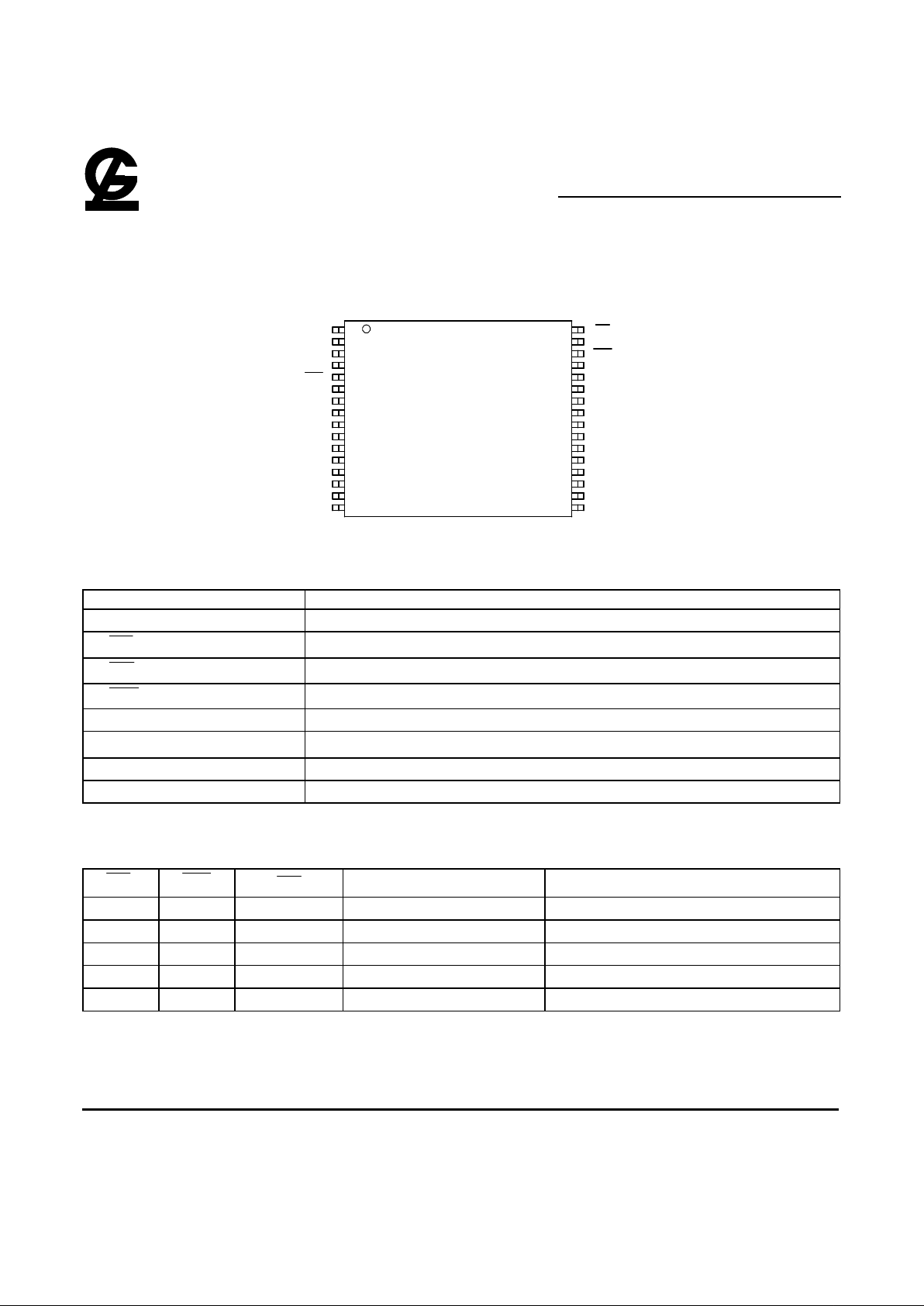

Pin Configurations :

sTSOPI

GLT6400M08

A

16

A

7

1

2

3

4

5

6

8

9

10

11

12

13

22

21

19

18

17

26

25

2423GND

OE

A

10

14

27

28

I/O

7

I/O

6

20 A

0

7

WE

V

CC

15

16

29

30

31

32A

11

A

9

A

8

A

13

A

17

A

15

A

14

A

12

A

6

A

5

A

4

A

3

A

2

A

1

I/O

0

I/O

1

I/O

2

I/O

3

I/O

4

I/O

5

CE

1

A

18

Pin Descriptions:

Name

Function

A0 – A

18

Address Inputs

CE

1

Chip Enable Input

OE

Output Enable Input

WE

Write Enable Input

I/O0 – I/O

7

Data Input and Data Output

V

CC

2.5V Power Supply

GND Ground

NC No Connection

Truth Table:

CE

1

WE

OE

Data Mode

HXX

High-Z

Standby

XXX

High-Z

Standby

LHL

Data Out

Active, Read

LHH

High-Z

Active, Output Disable

LLX

Data Out

Active, Write

*Key : X = Don’t Care, L = Low, H = High

Page 3

G-LINK

GLT6400M08

Ultra Low Power 512k x 8 CMOS SRAM

Nov 2000(Rev. 2.0)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 3 -

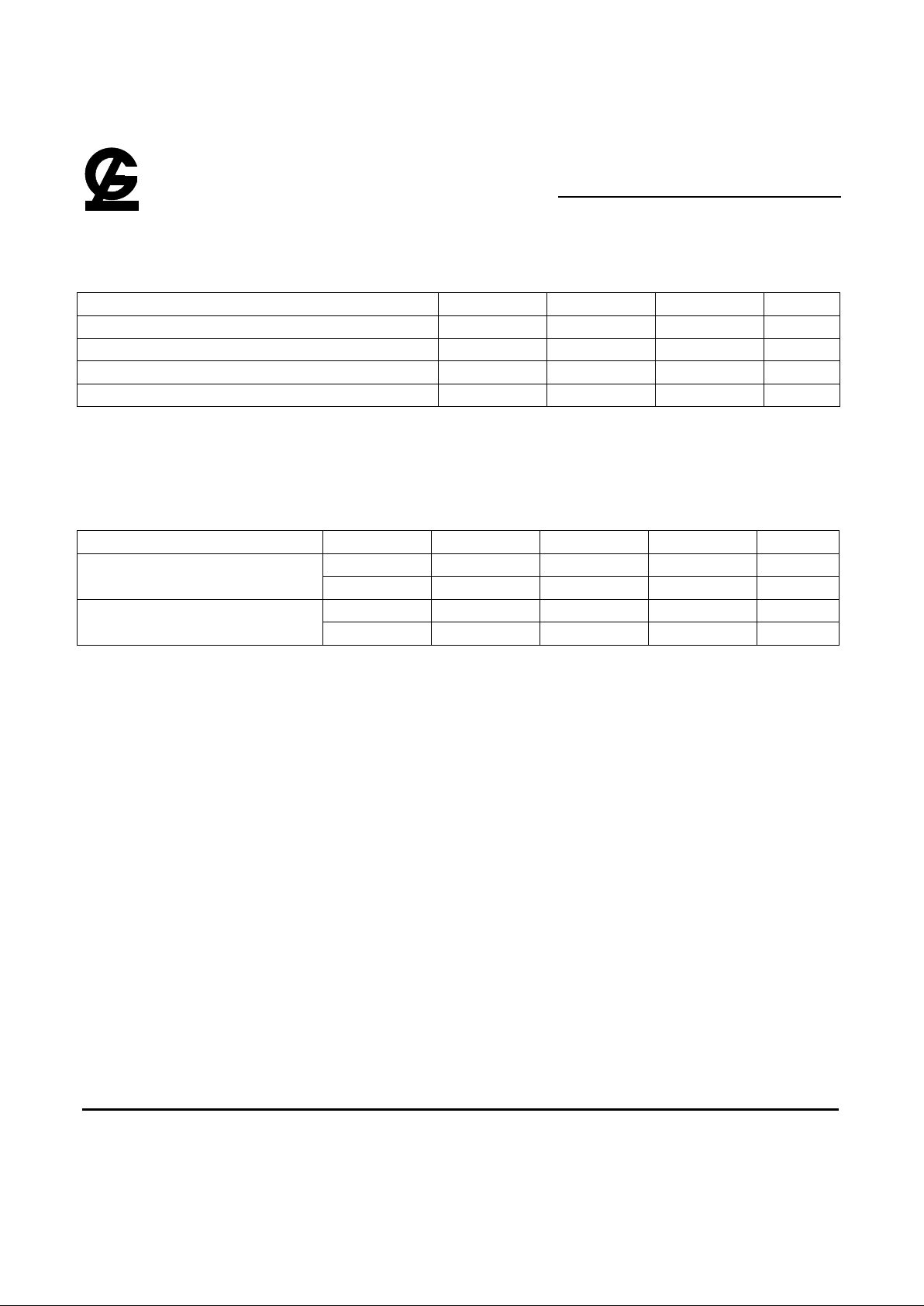

Absolute Maximum Ratings*

Parameter Symbol Minimum Maximum Unit

Voltage on Any Pin Relative to Gnd Vt -0.5 Vcc+0.3 V

Power Dissipation P

T

- 1.0 W

Storage Temperature (Plastic) Tstg -55 +150

°C

Temperature Under Bias Tbias -40 +85

°C

*Note : Stresses greater than those listed above Absolute Maximum Ratings may cause permanent damage to the device.

This is a stress rating only and functional operation of the device at these or any conditions outside those indicated

in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect reliability.

Recommended Operating Conditions ( TA = -25°C to + 85°C)

Parameter Symbol Min Typ Max Unit

V

CC

2.3 2.5 2.7 V

Supply Voltage

Gnd 0.0 0.0 0.0 V

V

IH

2.0 - VCC+0.2 V

Input Voltage

V

IL

-0.5* - 0.6 V

* VIL min = -1.0V for pulse width less than tRC/2.

Page 4

G-LINK

GLT6400M08

Ultra Low Power 512k x 8 CMOS SRAM

Nov 2000(Rev. 2.0)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 4 -

DC Operating Characteristics ( Vcc=2.3V to 2.7V, T

A

=-25°C to + 85°C)

120

Parameter Sym. Test Conditions

Min Max

Unit

Input Leakage Current

I

LI

VCC = Max,

Vin = Gnd to V

CC

- 1

µA

Output Leakage

Current

I

LO

CE

1

=V

IH

VCC = Max, V

OUT

= Gnd to V

CC

- 1

µA

Operating Power

Supply Current

I

CC

CE

1

=VIL ,

VIN=VIH or VIL, I

OUT

=0mA

- 5 mA

I

CC1

CE

1

=VIL ,

I

OUT

= 0mA,

Min Cycle, 100% Duty

- 30 mA

Average Operating

Current

I

CC2

CE

1

=0.2V

I

OUT

= 0mA,

Cycle Time=1µs, 100% Duty

- 3 mA

Standby Power Supply

Current(TTL Level)

I

SB

CE

1

=V

IH

- 0.3 mA

GLT6400M

08LL

20

µA

Standby Power Supply

Current (CMOS Level)

I

SB1

CE

1

≥ VCC-0.2V

or f=0

VIN ≤ 0.2V or V

IN

≥ VCC-0.2V

GLT6400M

08SL

5

µA

Output Low Voltage V

OLIOL

= 2 mA - 0.4 V

Output High Voltage V

OHIOH

= -1 mA 2.0 - V

Data Retention

Parameter Sym. Test Conditions Min. Max. Unit

VCC for Data retention

V

DR

1.0 - V

Data Retention Current

I

CCDR

- 4

µA

Chip Deselect to Data Retention Time

t

CDR

0 - ns

Operating Recovery Time

(2)

t

R

CE

1

≥

VCC -0.2V or

V

IN

≥

VCC -0.2V or

V

IN

≤ 0.2V

t

RC

- ns

Page 5

G-LINK

GLT6400M08

Ultra Low Power 512k x 8 CMOS SRAM

Nov 2000(Rev. 2.0)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 5 -

Data Retention Waveform (TA = -25°C to + 85°C)

Data Retention Mode

Vcc

CE

VDR

VDR >= 1.0V

tRtCDR

2.7V

2.7V

VIH

V

IH

AC Test Conditions AC Test Loads and Waveforms

CL*

TTL

Output Load Condition *Including Scope and Jig Capacitance

CL = 30pf + 1TTL Load

Read Cycle

(3,9)

( Vcc=2.3V to 2.7V, TA =-25°C to + 85°C)

120

Unit NoteParameter Symbol

Min Max

Read Cycle Time t

RC

120 ns

Address Access Time t

AA

120 ns

Chip Enable Access Time t

ACE

120 ns

Output Enable Access Time t

OE

60 ns

Output Hold from address Change t

OH

15 ns

Chip Enable to Output in Low-Z t

CLZ

10 ns 4,5

Chip Disable to Output in High-Z t

CHZ

0 35 ns 4,5

Output Enable to Output in Low-Z t

OLZ

5 ns 4,5

Output Disable to Output in High-Z t

OHZ

0 35 ns 4,5

Power-Up Time t

PU

0 ns 5

Power-Down Time t

PD

120 ns 5

Input Pulse Levels 0.4V to 2.2V

Input Rise and Fall Time

Input and Output Timing

Reference Level

5 ns

1.1V

Page 6

G-LINK

GLT6400M08

Ultra Low Power 512k x 8 CMOS SRAM

Nov 2000(Rev. 2.0)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 6 -

Timing Waveform of Read Cycle 1

(3,6,7,9)

(Address Controlled)

DOUT

tAA tOH

tRC

Data Valid

Address

Timing Waveform of Read Cycle 2

(5,6,8,9)

( CE1 Controlled)

t

OE

t

RC

Data Valid

CE1

t

OHZ

t

CHZ

t

PD

50%

50%

t

OLZ

t

ACE

t

CLZ

t

PU

Supply Current

OE

D

OUT

I

CC

I

SB

Write Cycle

(3,11)

( Vcc=2.3V to 2.7V, TA =-25°C to + 85°C)

120

Parameter Symbol

Min Max

Unit Note

Write Cycle Time t

WC

120 ns

Chip Enable to Write End t

CW

100 ns

Address Setup to Write End t

AW

100 ns

Address Setup Time t

AS

0 ns

Write Pulse Width t

WP

80 ns

Write Recovering Time t

WR

0 ns

Data Valid to Write End t

DW

50 ns

Data Hold Time t

DH

0 ns

Write Enable to Output in High-Z t

WZ

0 35 ns 4,5

Output Active from Write End t

OW

5 ns 4,5

Page 7

G-LINK

GLT6400M08

Ultra Low Power 512k x 8 CMOS SRAM

Nov 2000(Rev. 2.0)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 7 -

Timing Waveform of Write Cycle 1

(10,11)

( WE Controlled)

tWP

tAW

WE

tWC

tWR

tAS

tDW tDH

tOW

tWZ

Data Valid

Address

DIN

DOUT

Timing Waveform of Write Cycle 2

(10,11)

( CE1 Controlled)

tAW

WE

tWC

tWR

tDW tDH

Data Valid

Address

DIN

tAS tCW

t

WP

tWZ

CE1

DOUT

Page 8

G-LINK

GLT6400M08

Ultra Low Power 512k x 8 CMOS SRAM

Nov 2000(Rev. 2.0)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 8 -

Notes :

1. L-version includes this feature.

2. This Parameter is samples and not 100% tested.

3. For test conditions, see AC Test Condition.

4. This parameter is tested with CL = 5pF. Transition is measured ± 500mV from steady – state voltage.

5. This parameter is guaranteed, but is not tested.

6. WE is HIGH for read cycle.

7. CE1 and OE are LOW and for read cycle.

8. Address valid prior to or coincident with CE1 transition LOW .

9. All read cycle timings are referenced from the last valid address to the first transition address.

10. CE1 or WE must be HIGH during address transition.

11. All write cycle timings are referenced from the last valid address to the first transition address.

Page 9

G-LINK

GLT6400M08

Ultra Low Power 512k x 8 CMOS SRAM

Nov 2000(Rev. 2.0)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 9 -

Ordering Information

GLT6400M08LL-120 ST

120ns

Normal

sTSOPI 32L

GLT6400M08SL-120 ST

120ns

Normal

sTSOPI 32L

GLT6400M08SLI-120 ST

120ns

Normal

sTSOPI 32L

GLT6400M08SLI-120 ST

120ns

Normal

sTSOPI 32L

Parts Numbers (Top Mark) Definition :

GLT 6 400 M 08 LL I - 120 TC

4 : DRAM

6 : Standard

SRAM

7 : Cache SRAM

8 : Synchronous

Burst SRAM

-SRAM

064 : 64K

256 : 256K

512 : 512K

100 : 1M

-DRAM

10 : 1M(C/EDO)*

11 : 1M(C/FPM)*

12 : 1M(H/EDO)*

13 : 1M(H/FPM)*

20 : 2M(EDO)

21 : 2M(FPM)

40 : 4M(EDO)

41 : 4M(FPM)

80 : 8M(EDO)

81 : 8M(FPM)

*See note

VOLTAGE

Blank : 5V

L : 3.3V

M : 2.5V

N : 2.1V

CONFIG.

04 : x04

08 : x08

16 : x16

32 : x32

SPEED

-SRAM

10 : 10ns

12 : 12ns

15 : 15ns

20 : 20ns

70 : 70ns

-DRAM

35 : 35ns

40 : 40ns

45 : 45ns

50 : 50ns

60 : 60ns

PACKAGE

T : PDIP(300mil)

TS : TSOP(Type I)

ST : sTSOP (Type I)

TC : TSOP(Type ll)

PL : PLCC

FA : 300mil SOP

FB : 330mil SOP

FC : 445mil SOP

J3 : 300mil SOJ

J4 : 400mil SOJ

P : PDIP(600mil)

Q : PQFP

TQ : TQFP

FG : 48-fpBGA

LL : Low Low power

L : Low power

SL : Super Low power

I : Industrial Temperature

Page 10

G-LINK

GLT6400M08

Ultra Low Power 512k x 8 CMOS SRAM

Nov 2000(Rev. 2.0)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 10 -

Package Information

32 pin 8x13.4mm Small Outline J-form Package (sTSOP)

Loading...

Loading...