Datasheet DS1340Z-33, DS1340Z-3, DS1340Z-18, DS1340U-33, DS1340U-3 Datasheet (Dallas Semiconductor)

...Page 1

General Description

The DS1340 is a real-time clock (RTC)/calendar that is

pin compatible and functionally equivalent to the ST

M41T00, including the software clock calibration. The

device additionally provides trickle-charge capability

on the V

BACKUP

pin, a lower timekeeping voltage, and

an oscillator STOP flag. Block access of the register

map is identical to the ST device. Two additional registers, which are accessed individually, are required for

the trickle charger and flag. The clock/calendar provides seconds, minutes, hours, day, date, month, and

year information. A built-in power-sense circuit detects

power failures and automatically switches to the backup supply. The device is programmed serially through

a 2-wire bidirectional bus.

Applications

Portable Instruments

Point-of-Sale Equipment

Medical Equipment

Telecommunications

Features

♦ Enhanced Second Source for the ST M41T00

♦ Fast (400kHz) 2-Wire Interface

♦ Software Clock Calibration

♦ RTC Counts Seconds, Minutes, Hours, Day, Date,

Month, and Year

♦ Automatic Power-Fail Detect and Switch Circuitry

♦ Trickle-Charge Capability

♦ Low Timekeeping Voltage Down to 1.3V

♦ Three Operating Voltage Ranges (1.8V, 3V, and

3.3V)

♦ Oscillator Stop Flag

♦ Available in 8-Pin µSOP or SO Packages

DS1340

2-Wire RTC with Trickle Charger

______________________________________________ Maxim Integrated Products 1

1

2

3

4

8

7

6

5

V

CC

FT/OUT

SCL

SDA

V

BACKUP

GND

X2

X1

TOP VIEW

DS1340

SO,

µSOP

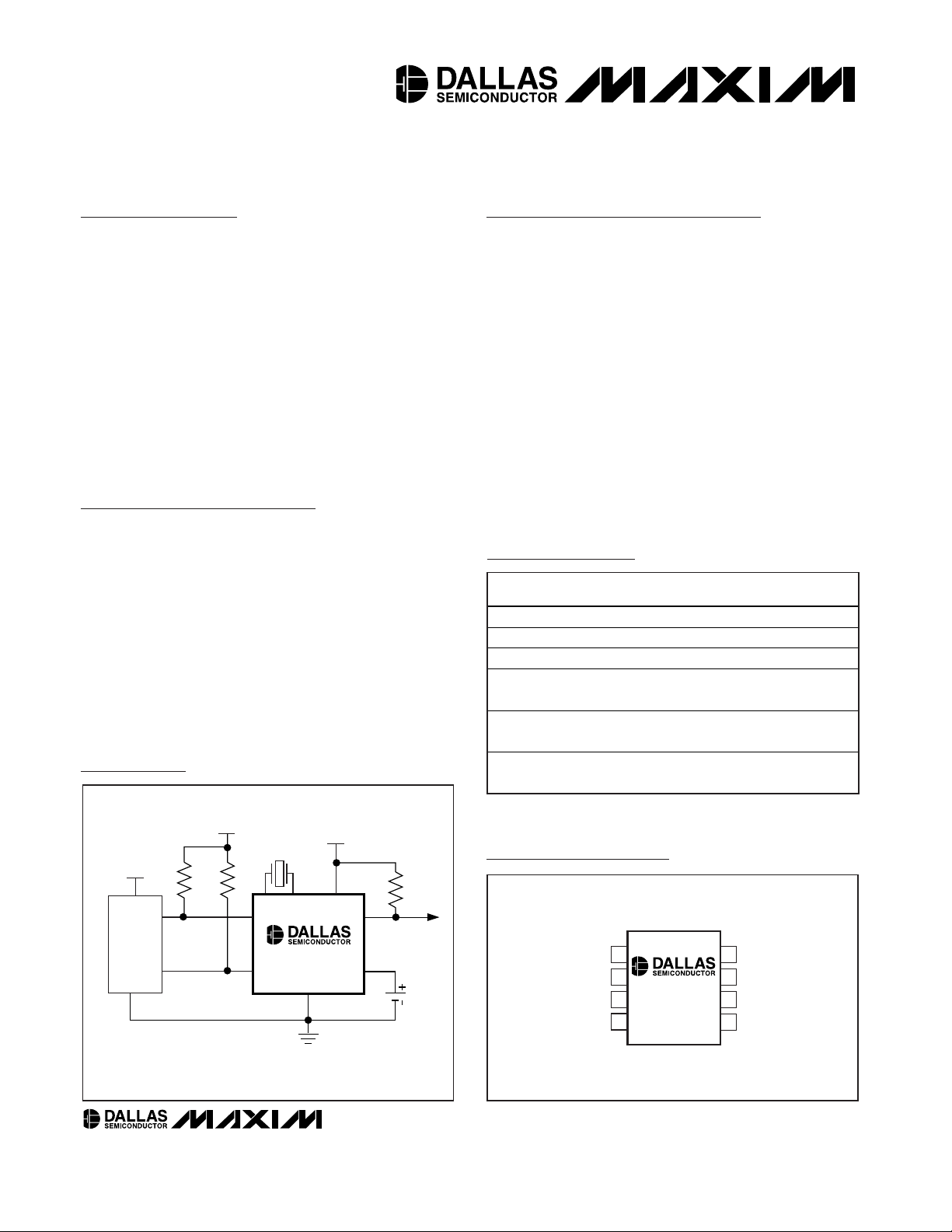

Pin Configuration

Ordering Information

4

CPU

V

CC

V

CC

V

CC

5

6

8

12

SDA

SCL

GND

X2X1

V

CC

RPU RPU

CRYSTAL

FT/OUT

V

BACKUP

3

7

RPU = t

R

/ CB

DS1340

Typical Operating Circuit

Rev 0; 6/03

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

PART

TEMP RANGE

PINPACKAGE

TOP

MARK

DS1340Z-18

D1340-18

DS1340Z-3

DS1340-3

DS1340Z-33

D1340-33

DS1340U-18

8 µSOP

1340

A1-18

DS1340U-3

8 µSOP

1340

A1-3

DS1340U-33

8 µSOP

1340

A1-33

-40°C to +85°C 8 SO (0.150in)

-40°C to +85°C 8 SO (0.150in)

-40°C to +85°C 8 SO (0.150in)

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

Page 2

DS1340

2-Wire RTC with Trickle Charger

2 _____________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

Voltage Range on VCCPin Relative to Ground .....-0.3V to +6.0V

Voltage Range on SDA, SCL, and FT/OUT

Relative to Ground..................................-0.3V to (V

CC

+ 0.3V)

Operating Temperature Range ...........................-40°C to +85°C

Storage Temperature Range .............................-55°C to +125°C

Soldering Temperature Range ..................................See JEDEC

J-STD-020A Specification

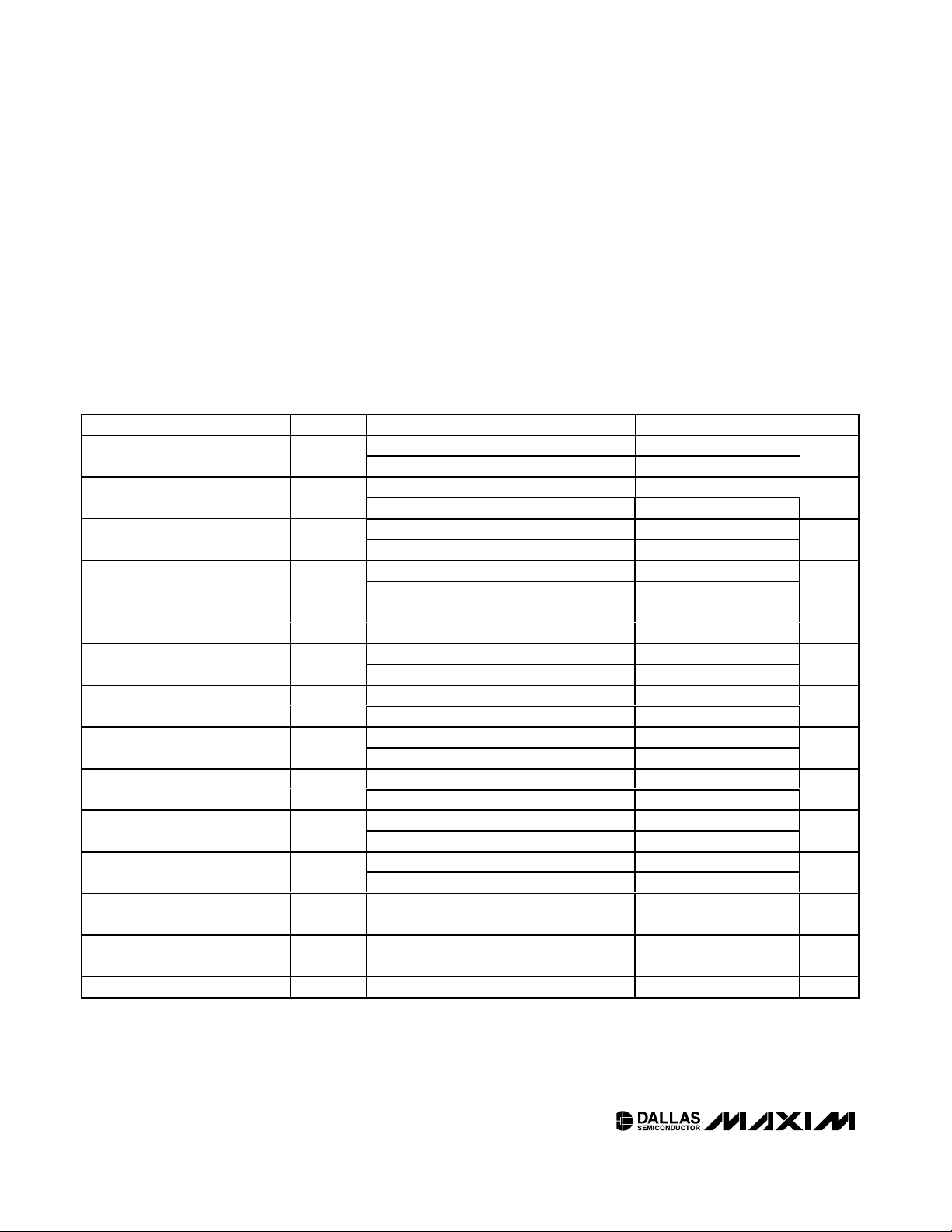

AC ELECTRICAL CHARACTERISTICS

(VCC= V

CC MIN

to V

CC MAX

, TA= -40°C to +85°C, unless otherwise noted.) (Note 1, Figure 1)

PARAMETER

CONDITIONS

UNITS

Standard mode 0

SCL Clock Frequency f

SCL

Fast mode

kHz

Standard mode 4.7

Bus Free Time Between STOP

and START Conditions

t

BUF

Fast mode 1.3

µs

Standard mode 4.0

Hold Time (Repeated) START

Condition (Note 2)

Fast mode 0.6

µs

Standard mode 4.7

Low Period of SCL Clock t

LOW

Fast mode 1.3

µs

Standard mode 4.0

High Period of SCL Clock t

HIGH

Fast mode 0.6

µs

Standard mode 0

Data Hold Time (Notes 3, 4)

Fast mode 0

µs

Standard mode

Data Setup Time (Note 5)

Fast mode

ns

Standard mode 4.7

START Setup Time

Fast mode 0.6

µs

Standard mode

Rise Time of SDA and SCL

Signals (Note 6)

t

R

Fast mode

ns

Standard mode

Fall Time of SDA and SCL Signals

(Note 6)

t

F

Fast mode

ns

Standard mode 4.7

Setup Time for STOP Condition

Fast mode 0.6

µs

Capacitive Load for Each Bus

Line

C

B

(Note 6)

pF

Pulse Width of Spikes that Must

be Suppressed by the Input Filter

t

SP

Fast mode 30 ns

Oscillator Stop Flag (OSF) Delay

t

OSF

(Note 7) 100 ms

SYMBOL

t

HD:STA

MIN TYP MAX

100

100 400

t

HD:DAT

t

SU:DAT

t

SU:STA

t

SU:STO

250

100

20 + 0.1C

20 + 0.1C

20 + 0.1C

20 + 0.1C

B

B

B

B

0.9

0.9

1000

300

300

300

400

Page 3

DS1340

2-Wire RTC with Trickle Charger

_____________________________________________________________________ 3

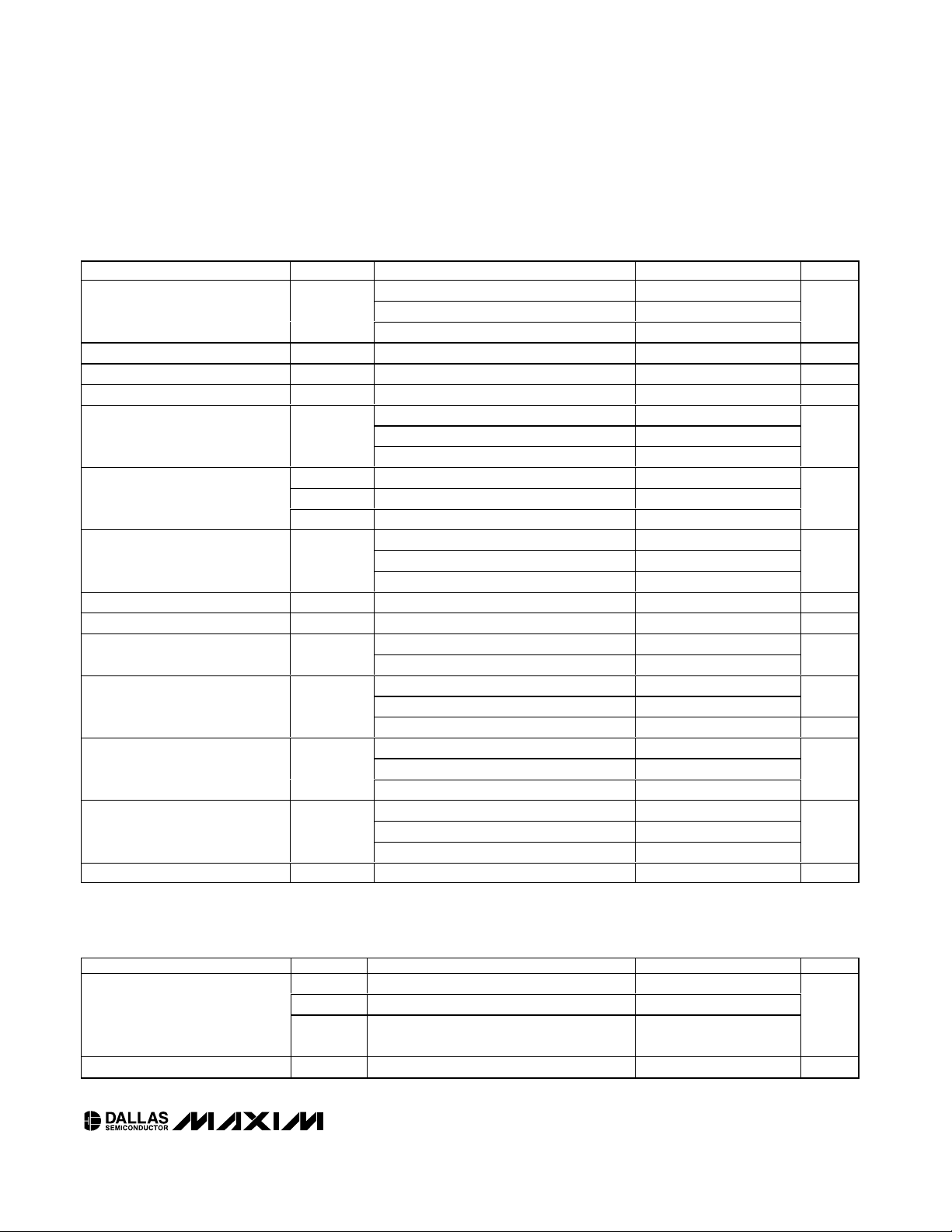

RECOMMENDED DC OPERATING CONDITIONS

(VCC= V

CC MIN

to V

CC MAX

, TA= -40°C to +85°C, unless otherwise noted. Typical values are at VCC= 3.3V, TA= +25°C, unless

otherwise noted.) (Note 1)

PARAMETER

CONDITIONS

UNITS

DS1340-18

1.8

DS1340-3 2.7 3.0 3.3

Supply Voltage (Note 8) V

CC

DS1340-33

3.3 5.5

V

Input Logic 1 (SDA, SCL) V

IH

(Note 8)

V

Input Logic 0 (SDA, SCL) V

IL

(Note 8)

V

Supply Voltage, Pullup (FT/OUT)

V

IH

(Note 8) 5.5 V

DS1340-18 1.3 3.7

DS1340-3 1.3 3.7

Backup Supply Voltage (Note 8)

DS1340-33 1.3 5.5

V

R1 (Notes 9, 10)

R2 (Note 11)

Trickle-Charge Current-Limiting

Resistors

R3 (Note 12)

Ω

DS1340-18

1.6

DS1340-3

2.6 2.7Power-Fail Voltage (Note 8) V

PF

DS1340-33

V

Input Leakage (SCL, CLK) I

LI

-1 +1 µA

I/O Leakage (SDA, FT/OUT) I

LO

-1 +1 µA

VCC > 2V; V

OL

= 0.4V 3.0

SDA Logic 0 Output I

OLSDA

1.7V < VCC < 2V; VOL = 0.2 x V

CC

3.0

mA

VCC > 2V; VOL = 0.4V 3.0

1.7V < VCC < 2V; VOL = 0.2 x V

CC

3.0

mA

FT/OUT Logic 0 Output I

OLSQW

1.3V < VCC < 1.7V; VOL = 0.2x V

CC

250 µA

DS1340-18 72 150

DS1340-3

200

Active Supply Current (Note 13) I

CCA

DS1340-33

300

µA

DS1340-18 60 100

DS1340-3 81 125Standby Current (Note 14) I

CCS

DS1340-33

150

µA

V

BACKUP

Leakage Current

V

BACKUP

= 3.7V 100 nA

DC ELECTRICAL CHARACTERISTICS

(VCC= 0V, V

BACKUP

= 3.7V, TA= -40°C to +85°C, unless otherwise noted.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

OSC ON, FT = 0 (Note 15)

OSC ON, FT = 1 (Note 15)

Oscillator Current

OSC ON, FT = 0, V

BACKUP

= 3.0V,

T

A

= +25°C (Notes 15, 16)

nA

V

BACKUP

Data-Retention Current

OSC OFF

100 nA

SYMBOL

V

BACKUP

I

BACKUPLKG

I

BACKUP1

I

BACKUP2

I

BACKUP3

I

BACKUPDR

MIN TYP MAX

1.71

2.97

0.7 x V

-0.3 +0.3 x V

1.51

2.45

2.70 2.88 2.97

CC

V

250

2000

4000

108

192

100

800 1150

850 1250

800 1000

25.0

CC

1.89

+ 0.3

CC

1.71

Page 4

DS1340

2-Wire RTC with Trickle Charger

4 _____________________________________________________________________

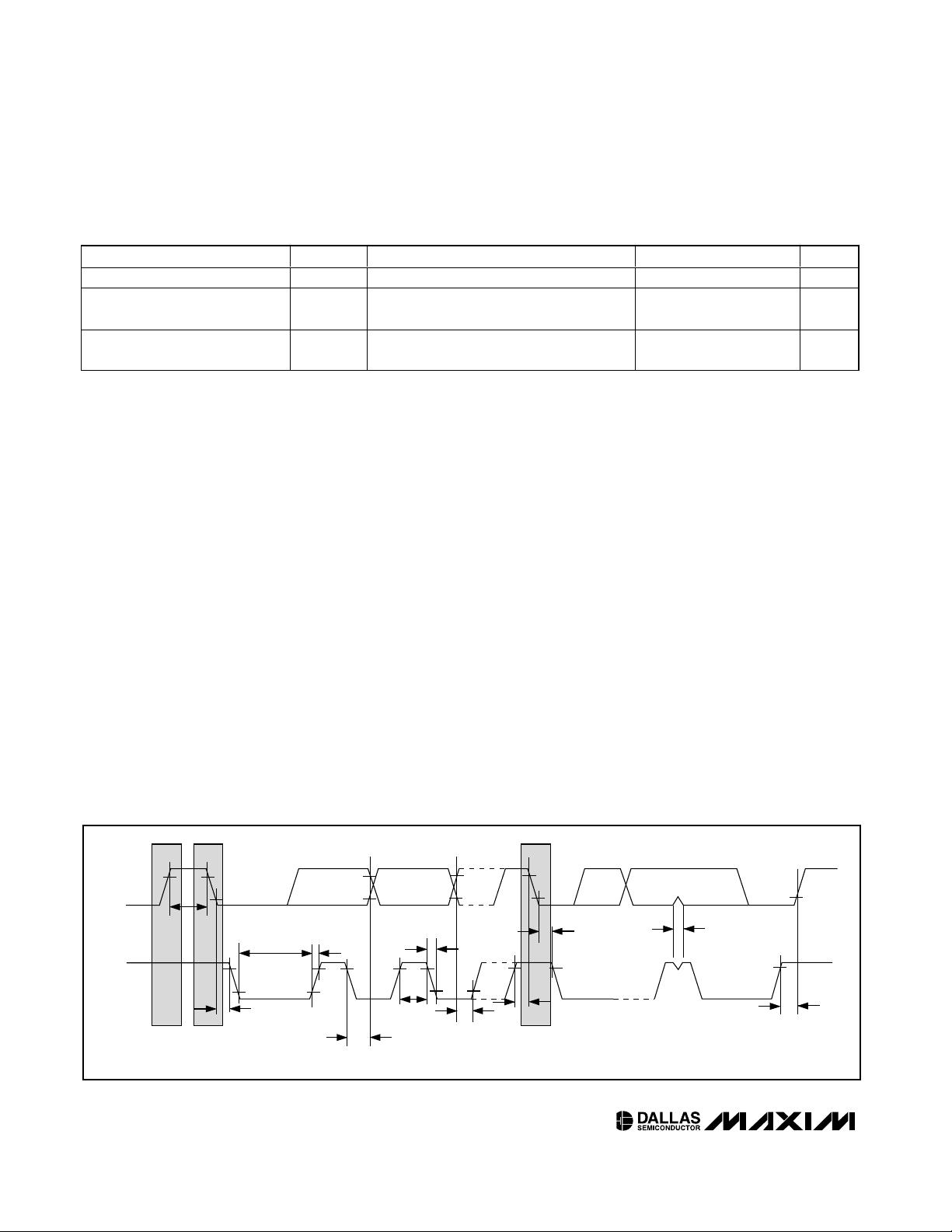

POWER-UP/POWER-DOWN CHARACTERISTICS

(TA= -40°C to +85°C) (Figure 2)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Recovery at Power-Up t

REC

(Note 17) 2 ms

VCC Fall Time; V

PF(MAX)

to

V

PF(MIN)

t

VCCF

µs

VCC Rise Time; V

PF(MIN)

to

V

PF(MAX)

t

VCCR

0µs

WARNING: Under no circumstances are negative undershoots, of any amplitude, allowed when device is in battery-backup mode.

Note 1: Limits at -40°C are guaranteed by design and not production tested.

Note 2: After this period, the first clock pulse is generated.

Note 3: A device must internally provide a hold time of at least 300ns for the SDA signal (referred to as the V

IH(MIN)

of the SCL

signal) to bridge the undefined region of the falling edge of SCL.

Note 4: The maximum t

HD:DAT

only has to be met if the device does not stretch the low period (t

LOW

) of the SCL signal.

Note 5: A fast-mode device can be used in a standard-mode system, but the requirement t

SU:DAT

≥ to 250ns must be met. This

is automatically the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the

low period of the SCL signal, it must output the next data bit to the SDA line t

R MAX

+ t

SU:DAT

= 1000 + 250 = 1250ns

before the SCL line is released.

Note 6: C

B

—total capacitance of one bus line in pF.

Note 7: The parameter t

OSF

is the period of time the oscillator must be stopped for the OSF flag to be set over the 0V ≤ VCC≤

V

CCMAX

and 1.3V ≤ V

BAT

≤ 3.7V range.

Note 8: All voltages are referenced to ground.

Note 9: Measured at V

CC

= typ, V

BACKUP

= 0V, register 08h = A5h.

Note 10: The use of the 250Ω trickle-charge resistor is not allowed at V

CC

> 3.63V and should not be enabled.

Note 11: Measured at V

CC

= typ, V

BACKUP

= 0V, register 08h = A6h.

Note 12: Measured at V

CC

= typ, V

BACKUP

= 0V, register 08h = A7h.

Note 13: I

CCA

—SCL clocking at max frequency = 400kHz.

Note 14: Specified with 2-wire bus inactive.

Note 15: Measured with a 32.768kHz crystal attached to the X1 and X2 pins.

Note 16: Limits at +25°C are guaranteed by design and not production tested.

Note 17: This delay applies only if the oscillator is enabled and running. If the oscillator is disabled or stopped, no power-up delay

occurs.

SDA

SCL

t

HD:STA

t

LOW

t

HIGH

t

R

t

F

t

BUF

t

HD:DAT

t

SU:DAT

REPEATED

START

t

SU:STA

t

HD:STA

t

SU:STO

t

SP

STOP START

Figure 1. Data Transfer on 2-Wire Serial Bus

300

Page 5

DS1340

2-Wire RTC with Trickle Charger

_____________________________________________________________________ 5

OUTPUTS

V

CC

V

PF(MAX)

INPUTS

HIGH-Z

RST

DON'T CARE

VALID

RECOGNIZED

RECOGNIZED

VALID

V

PF(MIN)

t

RST

t

RPU

t

R

t

F

V

PF

V

PF

Figure 2. Power-Up/Power-Down Timing

I

CCSA

vs. VCC FT = 0

DS1340 toc01

VCC (V)

SUPPLY CURRENT (µA)

5.04.54.03.53.02.52.01.5

50

100

150

200

250

0

1.0 5.5

25

50

75

100

125

150

0

I

CCS

vs. VCC FT = 0

DS1340 toc02

VCC (V)

SUPPLY CURRENT (µA)

5.04.54.03.53.02.52.01.51.0 5.5

-1.8V

-3.0V

-3.3V

I

BACKUP1

(FT = 0) vs. V

BACKUP

DS1340 toc03

450

500

550

600

650

700

750

800

850

400

V

BACKUP

(V)

SUPPLY CURRENT (nA)

5.04.54.03.53.02.52.01.51.0 5.5

Typical Operating Characteristics

(VCC= +3.3V, TA= +25°C, unless otherwise noted.)

I

BACKUP2

(FT = 1) vs. V

BACKUP

DS1340 toc04

450

500

550

600

650

700

750

800

850

400

V

BACKUP

(V)

SUPPLY CURRENT (nA)

5.04.54.03.53.02.52.01.51.0 5.5

FT vs. V

BACKUP

DS1340 toc06

V

BACKUP

(V)

FREQUENCY (Hz)

5.04.51.5 2.0 2.5 3.53.0 4.0

511.9965

511.9970

511.9975

511.9980

511.9985

511.9990

511.9995

512.0000

511.9960

1.0 5.5

I

BACKUP3

vs. TEMPERATURE

DS1340 toc05

TEMPERATURE (°C)

SUPPLY CURRENT (nA)

6040-20 0 20

500

550

600

650

700

750

800

850

-40 80

V

BACKUP

= 3.0V

Page 6

DS1340

Detailed Description

The DS1340 is a low-power clock/calendar with a trickle

charger. Address and data are transferred serially

through a 2-wire bidirectional bus. The clock/calendar

provides seconds, minutes, hours, day, date, month, and

year information. The date at the end of the month is

automatically adjusted for months with fewer than 31

days, including corrections for leap year. The DS1340

has a built-in power-sense circuit that detects power failures and automatically switches to the backup supply.

Oscillator Circuit

The DS1340 uses an external 32.768kHz crystal. The

oscillator circuit does not require any external resistors

or capacitors to operate. Table 1 specifies several crystal parameters for the external crystal. Figure 3 shows a

functional schematic of the oscillator circuit. If using a

crystal with the specified characteristics, the startup

time is usually less than one second.

Clock Accuracy

The initial clock accuracy depends on the accuracy of

the crystal and the accuracy of the match between the

capacitive load of the oscillator circuit and the capacitive load for which the crystal was trimmed. Additional

error is added by crystal frequency drift caused by

2-Wire RTC with Trickle Charger

6 _____________________________________________________________________

Pin Description

PIN NAME FUNCTION

1X1

2X2

Connections for a Standard 32.768kHz Quartz Crystal. The internal oscillator circuitry is designed for

operation with a crystal having a specified load capacitance (C

L

) of 12.5pF. X1 is the input to the

oscillator and can optionally be connected to an external 32.768kHz oscillator. The output of the

internal oscillator, X2, is floated if an external oscillator is connected to X1.

3

Connection for a Secondary Power Supply. For the 1.8V and 3V devices, V

BACKUP

must be held

between 1.3V and 3.7V for proper operation. V

BACKUP

can be as high as 5.5V on the 3.3V device.

This pin can be connected to a primary cell such as a lithium coin cell. Additionally, this pin can be

connected to a rechargeable cell or a super cap when used with the trickle-charge feature.

4 GND Ground

5 SDA

Serial Data Input/Output. SDA is the data input/output for the 2-wire serial interface. The SDA pin is

open drain and requires an external pullup resistor.

6 SCL

Serial Clock Input. SCL is the clock input for the 2-wire interface and is used to synchronize data

movement on the serial interface.

7 FT/OUT

Frequency Test/Output. This pin is used to output either a 512Hz signal or the value of the OUT bit.

When the FT bit is logic 1, the FT/OUT pin toggles at a 512Hz rate. When the FT bit is logic 0, the

FT/OUT pin reflects the value of the OUT bit. This open-drain pin requires an external pullup resistor,

and operates with either V

CC

or V

BACKUP

applied.

8VCCDC Power for Primary Power Supply

Table 1. Crystal Specifications*

*The crystal, traces, and crystal input pins should be isolated

from RF generating signals. Refer to Application Note 58:

Crystal Considerations for Dallas Real-Time Clocks for additional specifications.

COUNTDOWN

CHAIN

RTC

X1

X2

C

L

1

C

L

2

CRYSTAL

RTC

REGISTERS

Figure 3. Oscillator Circuit Showing Internal Bias Network

V

BACKUP

PARAMETER SYMBOL MIN TYP MAX UNITS

Nominal

Frequency

Series Resistance ESR 45 kΩ

Load Capacitance C

f

O

L

32.768 kHz

12.5 pF

Page 7

temperature shifts. External circuit noise coupled into

the oscillator circuit can result in the clock running fast.

Figure 4 shows a typical PC board layout for isolating

the crystal and oscillator from noise. Refer to

Application Note 58: Crystal Considerations with Dallas

Real-Time Clocks (www.maxim-ic.com/RTCapps) for

detailed information.

Operation

The DS1340 operates as a slave device on the serial

bus. Access is obtained by implementing a START

condition and providing a device identification code followed by data. Subsequent registers can be accessed

sequentially until a STOP condition is executed. The

device is fully accessible and data can be written and

read when V

CC

is greater than VPF. However, when

VCCfalls below VPF, the internal clock registers are

blocked from any access. If VPFis less than V

BACKUP

,

the device power is switched from VCCto V

BACKUP

when VCCdrops below VPF. If VPFis greater than

V

BACKUP

, the device power is switched from VCCto

V

BACKUP

when VCCdrops below V

BACKUP

. The regis-

ters are maintained from the V

BACKUP

source until V

CC

is returned to nominal levels. The functional diagram

(Figure 5) shows the main elements of the serial RTC.

Address Map

Table 2 shows the DS1340 address map. The RTC registers are located in address locations 00h to 06h, and

DS1340

2-Wire RTC with Trickle Charger

_____________________________________________________________________ 7

CRYSTAL

X1

X2

GND

LOCAL GROUND PLANE (LAYER 2)

Figure 4. Layout Example

SERIAL BUS

INTERFACE

AND ADDRESS

REGISTER

OSCILLATOR

CONTROL

LOGIC

X2

SCL

SDA

512Hz

MUX/BUFFER

FT/OUT

USER BUFFER

(7 BYTES)

CLOCK AND

CALENDAR

REGISTERS

32,768Hz

1Hz

X1

POWER

CONTROL

V

CC

V

BACKUP

DIVIDER AND

CALIBRATION

CIRCUIT

DS1340

Figure 5. Functional Diagram

ADDRESS

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2 BIT 1

BIT 0

FUNCTION

RANGE

00H

10 Seconds Seconds Seconds 00–59

01H X 10 Minutes Minutes Minutes 00–59

02H CEB CB 10 Hours Hours

Century/

Hours

0–1; 00–23

03H X X X X X Day Day 01–07

04H X X 10 Date Date Date 01–31

05H X X X

Month Month 01–12

06H 10 Year Year Year 00–99

07H OUT FT S CAL4

CAL2 CAL1

Control —

08H

TCS0

DS0

Trickle

Charger

—

09H OSF 0 0 0 0 0 0 0 Flag —

Table 2. Address Map

X = Read/Write bit

Note: Unless otherwise specified, the state of the registers is not defined when power is first applied.

EOSC

10 Month

TCS3 TCS2 TCS1

CAL3

DS1

ROUT1 ROUT0

CAL0

Page 8

DS1340

the control register is located at 07h. The trickle-charge

and flag registers are located in address locations 08h

to 09h. During a multibyte access of the timekeeping

registers, when the address pointer reaches 07h—the

end of the clock and control register space—it wraps

around to location 00h. Writing the address pointer to

the corresponding location accesses address locations

08h and 09h. After accessing location 09h, the address

pointer wraps around to location 00h. On a 2-wire

START, STOP, or address pointer incrementing to location 00h, the current time is transferred to a second set

of registers. The time information is read from these

secondary registers, while the clock may continue to

run. This eliminates the need to reread the registers in

case the main registers update during a read.

Clock and Calendar

The time and calendar information is obtained by reading the appropriate register bytes. Table 2 shows the

RTC registers. The time and calendar data are set or

initialized by writing the appropriate register bytes. The

contents of the time and calendar registers are in the

binary-coded decimal (BCD) format. The day-of-week

register increments at midnight. Values that correspond

to the day of week are user-defined but must be

sequential (i.e., if 1 equals Sunday, then 2 equals

Monday, and so on). Illogical time and date entries

result in undefined operation. Bit 7 of register 0 is the

enable oscillator (EOSC) bit. When this bit is set to 1, the

oscillator is disabled. When cleared to 0, the oscillator is

enabled. The initial power-up value of EOSC is 0.

Location 02h is the century/hours register. Bit 7 and bit

6 of the century/hours register are the century-enable

bit (CEB) and the century bit (CB). Setting CEB to logic

1 causes the CB bit to toggle, either from a logic 0 to a

logic 1, or from a logic 1 to a logic 0, when the years

register rolls over from 99 to 00. If CEB is set to logic 0,

CB does not toggle.

When reading or writing the time and date registers,

secondary (user) buffers are used to prevent errors

when the internal registers update. When reading the

time and date registers, the user buffers are synchronized to the internal registers on any START or STOP

and when the register pointer rolls over to zero. The

time information is read from these secondary registers

while the clock continues to run. This eliminates the

need to reread the registers in case the internal registers update during a read.

The divider chain is reset whenever the seconds register is written. Write transfers occur on the acknowledge

from the DS1340. Once the divider chain is reset, to

avoid rollover issues, the remaining time and date registers must be written within one second.

Special-Purpose Registers

The DS1340 has three additional registers (control,

trickle charger, and flag) that control the RTC, trickle

charger, and oscillator flag output.

Control Register (07h)

Bit 7: Output Control (OUT). This bit controls the output level of the FT/OUT pin when the FT bit is set to 0. If

FT = 0, the logic level on the FT/OUT pin is 1 if OUT = 1

and 0 if OUT = 0. The initial power-up OUT value is 1.

2-Wire RTC with Trickle Charger

8 _____________________________________________________________________

BIT 7

TCS3

1 OF 16 SELECT

NOTE: ONLY 1010b

ENABLES CHARGER

1 OF 2

SELECT

V

CC

V

BACKUP

R1

250Ω

TCS

0-3

= TRICKLE-CHARGER SELECT

DS

0-1

= DIODE SELECT

TOUT

0-1

= RESISTOR SELECT

R2

2kΩ

R3

4kΩ

1 OF 3

SELECT

BIT 6

TCS2

BIT 5

TCS1

BIT 4

TCS0

BIT 3

DS1

BIT 2

DS0

BIT 1

ROUT1

BIT 0

ROUT0

Figure 6. Trickle Charger Functional Diagram

Page 9

Bit 6: Frequency Test (FT). When this bit is 1, the

FT/OUT pin toggles at a 512Hz rate. When FT is written

to 0, the OUT bit controls the state of the FT/OUT pin.

The initial power-up value of FT is 0.

Bit 5: Calibration Sign Bit (S). A logic 1 in this bit indicates positive calibration for the RTC. A 0 indicates

negative calibration for the clock. See the Clock

Calibration section for a detailed description of the bit

operation. The initial power-up value of S is 0.

Bits 4 to 0: Calibration Bits (CAL4 to CAL0). These

bits can be set to any value between 0 and 31 in binary

form. See the Clock Calibration section for a detailed

description of the bit operation. The initial power-up

value of CAL0–CAL4 is 0.

Trickle-Charger Register (08h)

The simplified schematic in Figure 6 shows the basic

components of the trickle charger. The trickle-charge

select (TCS) bits (bits 4–7) control the selection of the

trickle charger. To prevent accidental enabling, only a

pattern on 1010 enables the trickle charger. All other

patterns disable the trickle charger. The trickle charger

is disabled when power is first applied. The diodeselect (DS) bits (bits 2, 3) select whether or not a diode

is connected between V

CC

and V

BACKUP

. If DS is 01,

no diode is selected; if DS is 10, a diode is selected.

The ROUT bits (bits 0, 1) select the value of the resistor

connected between VCCand V

BACKUP

. Table 3 shows

the resistor selected by the resistor select (ROUT) bits

and the diode selected by the diode select (DS) bits.

Warning: The ROUT value of 250Ω must not be select-

ed whenever V

CC

is greater than 3.63V.

The user determines diode and resistor selection

according to the maximum current desired for battery

or super cap charging (Table 3). The maximum charg-

ing current can be calculated as illustrated in the following example.

Assume that a 3.3V system power supply is applied to

V

CC

and a super cap is connected to V

BACKUP

. Also

assume that the trickle charger has been enabled with

a diode and resistor R2 between V

CC

and V

BACKUP

.

The maximum current I

MAX

would therefore be calculat-

ed as follows:

I

MAX

= (3.3V - diode drop) / R2 ≈ (3.3V - 0.7V) /

2kΩ≈1.3mA

As the super cap charges, the voltage drop between

VCCand V

BACKUP

decreases and therefore the charge

current decreases.

Flag Register (09h)

Bit 7: Oscillator Stop Flag (OSF). A logic 1 in this bit

indicates that the oscillator has stopped or was

stopped for some time period and may be used to

judge the validity of the clock and calendar data. This

bit is edge triggered and is set to logic 1 when the

internal circuitry senses that the oscillator has transitioned from a normal run state to a STOP condition. The

following are examples of conditions that can cause the

OSF bit to be set:

1) The first time power is applied.

2) The voltages present on VCCand V

BACKUP

are insufficient to support oscillation.

3) The EOSC bit is set to 1, disabling the

oscillator.

4) External influences on the crystal (e.g., noise,

leakage).

The OSF bit remains at logic 1 until written to logic 0. It

can only be written to logic 0. Attempting to write OSF

to logic 1 leaves the value unchanged.

DS1340

2-Wire RTC with Trickle Charger

_____________________________________________________________________ 9

TCS3 TCS2 TCS1 TCS0 DS1 DS0

FUNCTION

XXXX00XXDisabled

XXXX11XXDisabled

XXXXXX00Disabled

10100101No diode, 250Ω resistor

10101001One diode, 250Ω resistor

10100110No diode, 2kΩ resistor

10101010One diode, 2kΩ resistor

10100111No diode, 4kΩ resistor

10101011One diode, 4kΩ resistor

00000000Power-on reset value

Table 3. Trickle-Charge Register

ROUT1 ROUT0

Page 10

DS1340

Bits 6 to 0: All other bits in the flag register read as 0

and cannot be written.

Clock Calibration

The DS1340 provides a digital clock calibration feature

to allow compensation for crystal and temperature variations. The calibration circuit adds or subtracts counts

from the oscillator divider chain at the divide-by-256

stage. The number of pulses blanked (subtracted for

negative calibration) or inserted (added for positive calibration) depends upon the value loaded into the five

calibration bits (CAL4–CAL0) located in the control register. Adding counts speeds the clock up and subtracting counts slows the clock down.

The calibration bits can be set to any value between 0

and 31 in binary form. Bit 5 of the control register, S, is

the sign bit. A value of 1 for the S bit indicates positive

calibration, while a value of 0 represents negative calibration. Calibration occurs within a 64-minute cycle.

The first 62 minutes in the cycle can, once per minute,

have a one-second interval where the calibration is performed. Negative calibration blanks 128 cycles of the

32,768Hz oscillator, slowing the clock down. Positive

calibration inserts 256 cycles of the 32,768Hz oscillator,

speeding the clock up. If a binary 1 is loaded into the

calibration bits, only the first two minutes in the 64minute cycle are modified. If a binary 6 is loaded, the

first 12 minutes are affected, and so on. Therefore,

each calibration step either adds 512 or subtracts 256

oscillator cycles for every 125,829,120 actual 32,678Hz

oscillator cycles (64 minutes). This equates to

+4.068ppm or -2.034ppm of adjustment per calibration

step. If the oscillator runs at exactly 32,768Hz, each of

the 31 increments of the calibration bits would repre-

sent +10.7 or -5.35 seconds per month, corresponding

to +5.5 or -2.75 minutes per month.

For example, if using the FT function, a reading of

512.01024Hz would indicate a +20ppm oscillator frequency error, requiring a -10(00 1010) value to be

loaded in the S bit and the five calibration bits.

Note: Setting the calibration bits does not affect the frequency test output frequency. Also note that writing to

the control register resets the divider chain.

2-Wire Serial Data Bus

The DS1340 supports a bidirectional 2-wire bus and

data transmission protocol. A device that sends data

onto the bus is defined as a transmitter and a device

receiving data as a receiver. The device that controls

the message is called a master. The devices that are

controlled by the master are slaves. A master device

that generates the serial clock (SCL), controls the bus

access, and generates the START and STOP conditions must control the bus. The DS1340 operates as a

slave on the 2-wire bus. Connections to the bus are

made through the open-drain I/O lines SDA and SCL.

Within the bus specifications a standard mode (100kHz

max clock rate) and a fast mode (400kHz max clock

rate) are defined. The DS1340 works in both modes.

The following bus protocol has been defined (Figure 7):

• Data transfer can be initiated only when the bus is

not busy.

• During data transfer, the data line must remain

stable whenever the clock line is high. Changes in

the data line while the clock line is high are interpreted as control signals.

2-Wire RTC with Trickle Charger

10 ____________________________________________________________________

STOP

CONDITION

OR REPEATED

START

CONDITION

REPEATED IF MORE BYTES

ARE TRANSFERED

ACK

START

CONDITION

ACK

ACKNOWLEDGEMENT

SIGNAL FROM RECEIVER

ACKNOWLEDGEMENT

SIGNAL FROM RECEIVER

SLAVE ADDRESS

MSB

SCL

SDA

R/W

DIRECTION

BIT

12 678 9 12 893–7

Figure 7. 2-Wire Data Transfer Overview

Page 11

Accordingly, the following bus conditions have been

defined:

Bus not busy: Both data and clock lines remain

high.

START data transfer: A change in the data line’s

state from high to low, while the clock line is high,

defines a START condition.

STOP data transfer: A change in the data line’s

state from low to high, while the clock line is high,

defines a STOP condition.

Data valid: The data line’s state represents valid

data when, after a START condition, the data line is

stable for the duration of the high period of the

clock signal. The data on the line must be changed

during the low period of the clock signal. There is

one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The

number of data bytes transferred between the

START and STOP conditions is not limited, and is

determined by the master device. The information

is transferred byte-wise and each receiver

acknowledges with a ninth bit.

Acknowledge: Each receiving device, when

addressed, is obliged to generate an acknowledge after the reception of each byte. The master

device must generate an extra clock pulse that is

associated with this acknowledge bit.

A device that acknowledges must pull down the

SDA line during the acknowledge clock pulse in

such a way that the SDA line is stable low during

the high period of the acknowledge-related clock

pulse. Setup and hold times must be taken into

account. A master must signal an end of data to

the slave by not generating an acknowledge bit on

the last byte that has been clocked out of the

slave. In this case, the slave must leave the data

line high to enable the master to generate the

STOP condition.

Figures 8 and 9 detail how data transfer is accomplished on the 2-wire bus. Depending upon the state of

the R/W bit, two types of data transfer are possible:

Data transfer from a master transmitter to a

slave receiver. The first byte transmitted by the

master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte.

Data transfer from a slave transmitter to a master receiver. The master transmits the first byte (the

slave address). The slave then returns an acknowledge bit. Next follows a number of data bytes transmitted by the slave to the master. The master

returns an acknowledge bit after all received bytes

other than the last byte. At the end of the last

received byte, a not acknowledge is returned.

The master device generates all the serial clock

pulses and the START and STOP conditions. A

transfer is ended with a STOP condition or with a

repeated START condition. Since a repeated

START condition is also the beginning of the next

serial transfer, the bus is not released.

The DS1340 can operate in the following two modes:

Slave Receiver Mode (Write Mode): Serial data

and clock are received through SDA and SCL.

After each byte is received, an acknowledge bit is

transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Hardware performs address recognition after

reception of the slave address and direction bit.

The slave address byte is the first byte received

after the master generates the START condition.

The slave address byte contains the 7-bit DS1340

address, which is 1101000, followed by the direction bit (R/W), which is 0 for a write. After receiving

and decoding the slave address byte, the DS1340

outputs an acknowledge on SDA. After the DS1340

acknowledges the slave address + write bit, the

master transmits a word address to the DS1340.

This sets the register pointer on the DS1340, with

the DS1340 acknowledging the transfer. The master can then transmit zero or more bytes of data,

DS1340

2-Wire RTC with Trickle Charger

____________________________________________________________________ 11

AXXXXXXXXA1101000S 0 XXXXXXXX A XXXXXXXX A XXXXXXXX A P

<SLAVE

ADDRESS>

S — START

A — ACKNOWLEDGE

P — STOP

R/W — READ/WRITE OR DIRECTION BIT ADDRESS = D0H

<RW>

DATA TRANSFERRED

(X + 1 BYTES + ACKNOWLEDGE)

<DATA (n + X)><DATA (n + 1)><DATA (n)>

<WORD

ADDRESS (n)>

Figure 8. Slave Receiver Mode (Write Mode)

AXXXXXXXXA1101000S 1 XXXXXXXX A XXXXXXXX A XXXXXXXX A P

<SLAVE

ADDRESS>

S — START

A — ACKNOWLEDGE

P — STOP

A — NOT ACKNOWLEDGE

R/W — READ/WRITE OR DIRECTION BIT ADDRESS = D0H

<RW>

DATA TRANSFERRED

(X + 1 BYTES + ACKNOWLEDGE)

NOTE: LAST DATA BYTE IS FOLLOWED BY

A NOT ACKNOWLEDGE (A) SIGNAL

<DATA (n + X)><DATA (n + 2)><DATA (n + 1)>

<DATA (n)>

Figure 9. Slave Transmitter Mode (Read Mode)

Page 12

DS1340

2-Wire RTC with Trickle Charger

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are

implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12 Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2003 Maxim Integrated Products Printed USA is a registered trademark of Maxim Integrated Products.

with the DS1340 acknowledging each byte

received. The register pointer increments after

each data byte is transferred. The master generates a STOP condition to terminate the data write.

Slave Transmitter Mode (Read Mode): The first

byte is received and handled as in the slave

receiver mode. However, in this mode, the direction bit indicates that the transfer direction is

reversed. The DS1340 transmits serial data on

SDA while the serial clock is input on SCL. START

and STOP conditions are recognized as the beginning and end of a serial transfer. Hardware performs address recognition after reception of the

slave address and direction bit. The slave address

byte is the first byte received after the master generates the START condition. The slave address

byte contains the 7-bit DS1340 address, which is

1101000, followed by the direction bit (R/W),

which is 1 for a read. After receiving and decoding

the slave address byte, the DS1340 outputs an

acknowledge on SDA. The DS1340 then begins to

transmit data starting with the register address

pointed to by the register pointer. If the register

pointer is not written to before the initiation of a

read mode, the first address that is read is the last

one stored in the register pointer. The DS1340

must receive a not acknowledge to end a read.

Chip Information

TRANSISTOR COUNT: 10,930

PROCESS: CMOS

SUBSTRATE CONNECTED TO GROUND

Thermal Information

Theta-JA: +170°C/W (0.150in SO)

Theta-JC: +40°C/W (0.150in SO)

Theta-JA: +221°C/W (µSOP)

Theta-JC: +39°C/W (µSOP)

Package Information

For the latest package outline information, go to

www.maxim-ic.com/DallasPackInfo

.

Loading...

Loading...