Page 1

September 1195

Revised March 1999

CGS3321 • CGS3322 CMOS Crystal Clock Generators

© 1999 Fairchild Semiconductor Corporation DS011503.prf www.fairchildsemi.com

CGS3321 • CGS3322

CMOS Crystal Clock Generators

General Description

The CGS3321 and CGS3322 devices are designed for

Clock Generation and Support (CGS) application s up to

110 MHz. The CGS332x series of devices are crystal controlled CMOS oscillators requiring a minimum of external

components. The 332x dev ices provide selectable output

divide ratio. The c ircuit is designed to operat e over a wide

frequency range using fundamental mode or overtone crystals.

Features

■ Fairchild’s CGS family of devices for high frequency

clock source applications

■ Crystal frequency operation range:

fundamental: 10 MHz to 100 MHz typical

3rd or 5th overtone: 10 MHz to 95 MHz

■ 1000V ESD protection on OC S_IN an d OSC_O UT pins .

2000V ESD protection on all other pins

■ Output current drive of 48 mA for I

OL/IOH

■ FACT CMOS output levels

■ Output has high speed short circuit protection

■ Intended for Pierce oscillator applications

■ Hysteresis inputs to improve noise margin

■ CGS3321 has duty cycle adjust

■ CGS3322 has 1, 2, 4 divide ratio

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering cod e.

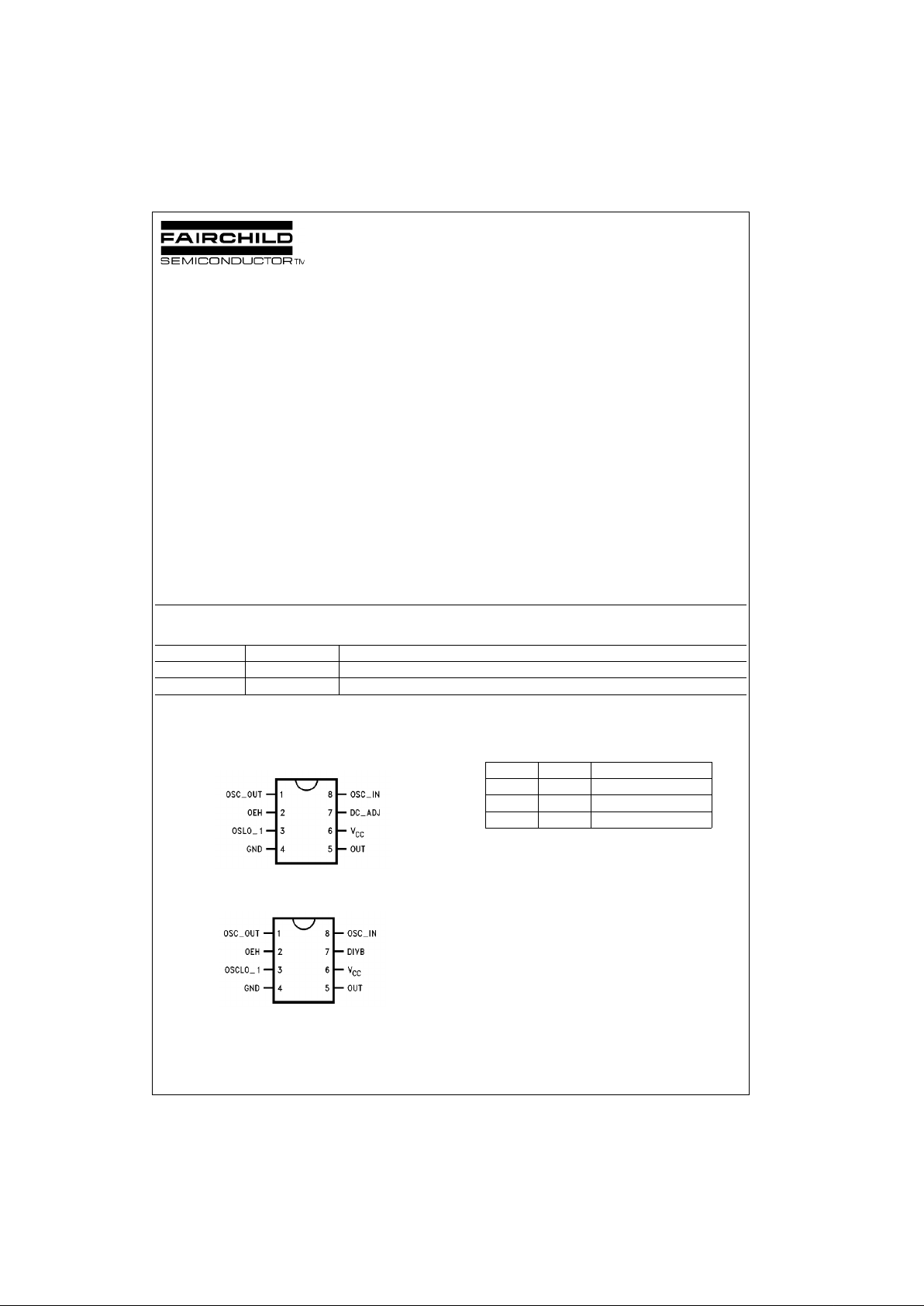

Connection Diagrams

CGS3321

CGS3322

Truth Table

Division Selection

Note: Actual value of the float ing DIVB input is V

CC/2

FACT is a trade m ark of F airchild Semiconductor Corporation.

Order Number Package Number Package Description

CGS3321M M08A 8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body

CGS3322M M08A 8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body

DIVB OEH Divider Output

F X Divide-by 1

1 1 Divide-by 2

0 1 Divide-by 4

Page 2

www.fairchildsemi.com 2

CGS3321 • CGS3322

Pin Descriptions

Note: Pin out varies for each device.

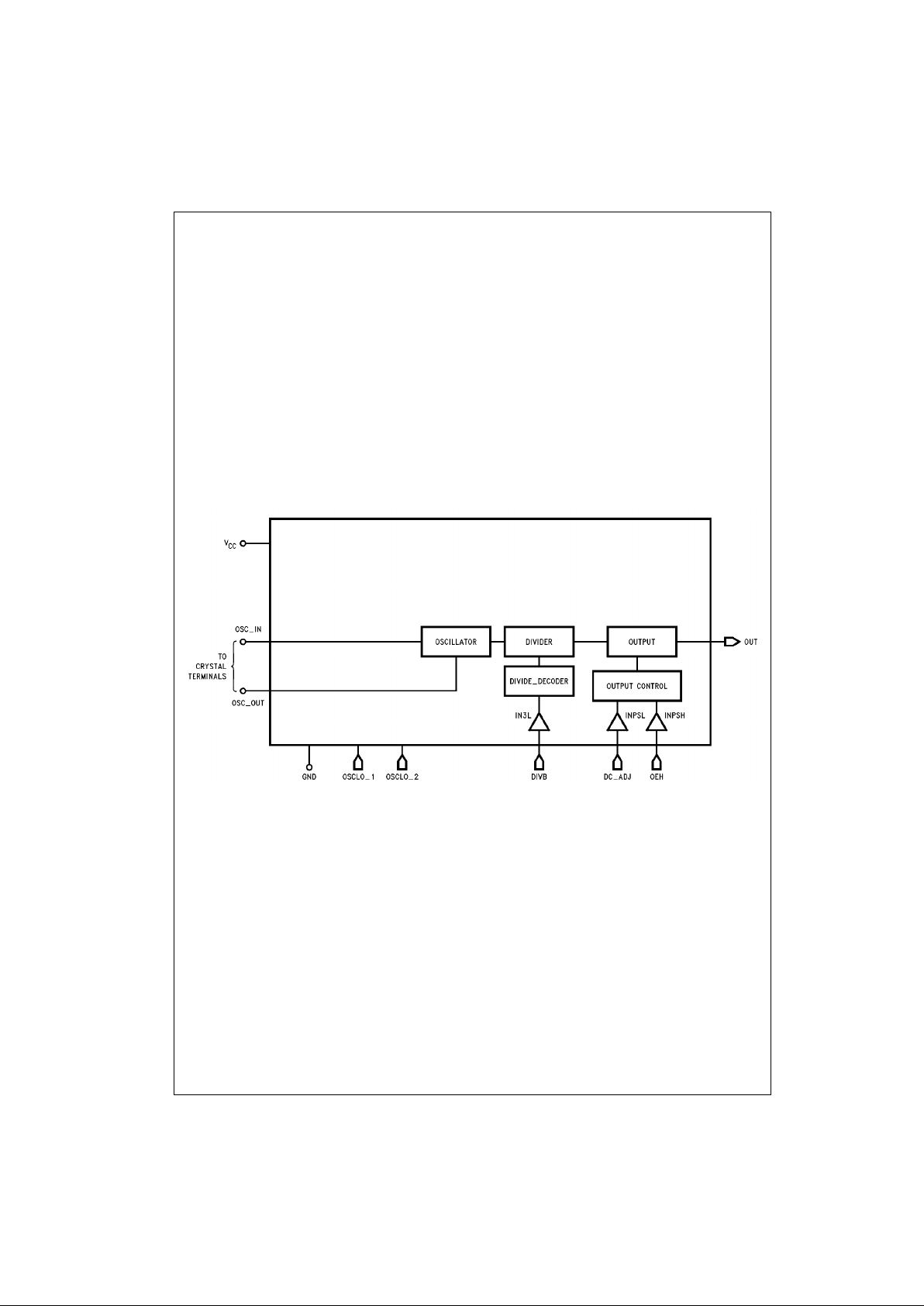

Block Diagrams

Note: Pin numbers vary for each device

Note: Pin out varies for each device.

OSC_IN Input to Oscillator Inverter. The output of the

crystal would be connected here.

OEH Active HIGH 3-STATE enable pin. This pin pulls

to a HIGH value when left floating and 3STATEs the output when forced LOW. This pin

has TTL compatible input levels.

OSC_OUT Resistive Buffered Output of the Oscillator

Inverter

OUT This pin is the main clock output on the device.

DIVB (CGS3322 only)

3-Level input used to select Binary Divide-by

value of output frequency.

OSCLO_1 The Oscillator LOW pin is the ground for the

Oscillator.

DC_ADJ (CGS3321 only)

Active high input that controls output duty

cycle. Logic high level will delay the HL transition edge approximately 0.3 ns.

V

CC

The power pin for the chip.

GND The ground pin for all sections of the circuitry

except the oscillator and oscillator related

circuitry.

Page 3

3 www.fairchildsemi.com

CGS3321 • CGS3322

Oscillator Stage

Output Stage

Page 4

www.fairchildsemi.com 4

CGS3321 • CGS3322

Absolute Maximum Ratings(Note 1) Recommended Operating

Conditions

Note 1: The Absolute Maximum Ratings are those values beyond which

the safety of the dev ice cannot be guaranteed. T he device sh ould not be

operated at thes e lim its. The para metric values defined in th e DC and AC

Electrical Characte ristics tables are not gu aranteed at the absolu te maximum ratings. The R ec ommended Operat ing Conditions will d ef ine the conditions for actual dev ic e operation.

DC Electrical Characteristics

Supply Voltage (VCC) −0.5V to 7.0V

DC Input Voltage Diode Current (I

IK

) ±9 mA

DC Input Voltage (V

I

) −0.5V to 7.0V

DC Output Diode Current (I

OK

) ±20 mA

DC Output Voltage (V

O

) -0.5V to VCC + 0.5V

DC Output Source

or Sink Current (I

O

) ±70 mA

Storage Temperature (T

STG

) −55°C to 150°C

Junction Temperature (T

J

)

SOIC 140°C/W

Supply Voltage (V

CC

) 4.5V to 5.5V

Input Voltage (V

I

) 0V to 5.5V

Output Voltage (V

O

) 0V to VCC V

Operating Temperature (T

A

) −40° to +85°C

Symbol Parameter

TA = +25°CT

A

= −40° C to +85°C

Units Conditions

V

CC

Typ

Guaranteed Limits

(V) Min Max Min Max

V

IHTTL

Minimum HIGH Level

Input Voltage,

TTL Level Inputs (OEH, OEL)

4.5 2.0 2.0 V

5.5 2.0 2.0

V

ILTTL

Maximum LOW Level

Input Voltage, TTL Level

Inputs (OEH, OEL)

4.5 0.8 0.8 V

5.5 0.8 0.8

V

IHCMOS

Minimum HIGH Level

Input Voltage. CMOS

Level Inputs (DC_ADJ)

4.5 3.15 3.15 V

5.5 3.85 3.85

V

ILCMOS

Maximum LOW Level

Input voltage. CMOS

Level Inputs (DC_ADJ)

4.5 1.35 1.35 V

5.5 1.65 1.65

V

IN3L_H

Minimum Logic 1 Input

for Three Level Input

(DIVB)

4.5 4.05 4.05 V

5.5 4.95 4.95

V

IN3L_1/2

Minimum Logic 1/2 Input

for Three Level Input

(DIVB)

4.5 1.8 2.7 1.8 2.7 V

5.5 2.2 3.3 2.2 3.3

V

IN3L_L

Maximum Logic 0 Input

Level Three Level Input

(DIVB)

4.5 0.45 0.45 V

5.5 0.45 0.45

V

OH

Minimum HIGH Level

Output Voltage

4.5 4.49 4.40 4.40 V I

OUT

= −50µA

5.5 5.49 5.40 5.40

4.5 3.86 3.76 IOH = −48 mA

5.5 4.86 4.76 VIN = VIH or V

IH

V

OL

Minimum LOW Level

Output Voltage

4.5 0.001 0.1 0.1 V I

OUT

= 50µA

5.5 0.001 0.1 0.1

4.5 0.44 0.44 IOL = +48mA

5.5 0.44 0.44 VIN = VIL or V

IH

I

IHRES

Input Current for Pins DIVB 5.5 220 360 200 380 µAVIN = 5.5V

I

ILRES

Input Current for Pins DIVB 5.5 −220 −360 −200 −380 µAVIN = 0.0V

I

IHENAB

Input Current for

Enable Pin OEL

5.5 90 160 85 175 µAVIN = 5.5V

I

ILENAB

Input Current for

Enable Pin OEH

5.5 −90 −160 −85 −175 µAVIN = 0.0V

I

IHOSC

Input Current for OSC_IN Pin

(Indicates Bias Resistance)

5.5 20 100 20 125 µAV

IN

= 5.5V

I

ILOSC

Input Current for OSC_IN Pin

(Indicates Bias Resistance)

5.5 −20 −100 −20 −125 µAVIN = 0.0V

I

OZH

Output Disabled Current 4.5 3.0 5.0 µAV

OUT

= V

CC

(Output HIGH) 5.5 3.0 5.0

I

OZL

Output Disabled Current 4.5 −140 −150 µAV

OUT

= 0.0V

(Output LOW) 5.5 −170 −180

Page 5

5 www.fairchildsemi.com

CGS3321 • CGS3322

DC Electrical Characteristics (Continued)

AC Electrical Characteristics

Over recommended operating free air temperature range. All typical values are measured at V

CC

= 5V, T

A

= 25°C.

Note 2: Voltage Range 5.0 is 5.0V ± 0.5V

Symbol Parameter

TA = +25°CT

A

= −40° C to +85°C

Units Conditions

V

CC

Typ

Guaranteed Limits

(V) Min Max Min Max

I

OLD

Minimum Dynamic

Output Current

5.57575mAV

OLD

= 1.65V

I

OHD

Minimum Dynamic

Output Current

5.5 −75 −75 mA V

OHD

= 3.85V

I

CCT

Additional Maximum ICC

per Input

(OEH, OEL Pins)

5.5 1.5 1.5 mA VIN = VCC − 2.1V

I

CC3L

Additional Maximum ICC

per Input

(DIVB)

5.5 1.5 1.5 mA DIVB, OSC_DR

Inputs Equal to V

CC/2

Symbol Parameter

V

CC

TA = −40°C to + 85°C

Units

(V)

CL = 50 pF

(Note 2) Min Type Max

f

MAX

Frequency Maximum 5.0 95 110 ns

t

PZH

Output HIGH Enable Time 5.0 1.0 31.5 ns

t

PZL

Output LOW Enable Time 5.0 1.0 28.0 ns

t

PHZ

Output HIGH Disable Time 5.0 1.0 21.5 ns

t

PLZ

Output LOW Disable Time 5.0 1.0 16.0 ns

t

RISE

Rise/Fall Time 5.0 1.0 ns

t

FALL

30 pF (20% to 80%)

Page 6

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

CGS3321 • CGS3322 CMOS Crystal Clock Generators

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or syste ms

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be reasonably expected to result in a significant inju ry to the

user.

2. A critical component in any com ponen t of a life su pport

device or system whose failu re to perform can be reasonably expected to ca use the fa i lure of the life su pp ort

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

Physical Dimensions inches (millimeters) unless otherwise noted

8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body

Package Number M08A

Loading...

Loading...