Page 1

October 1987

Revised January 1999

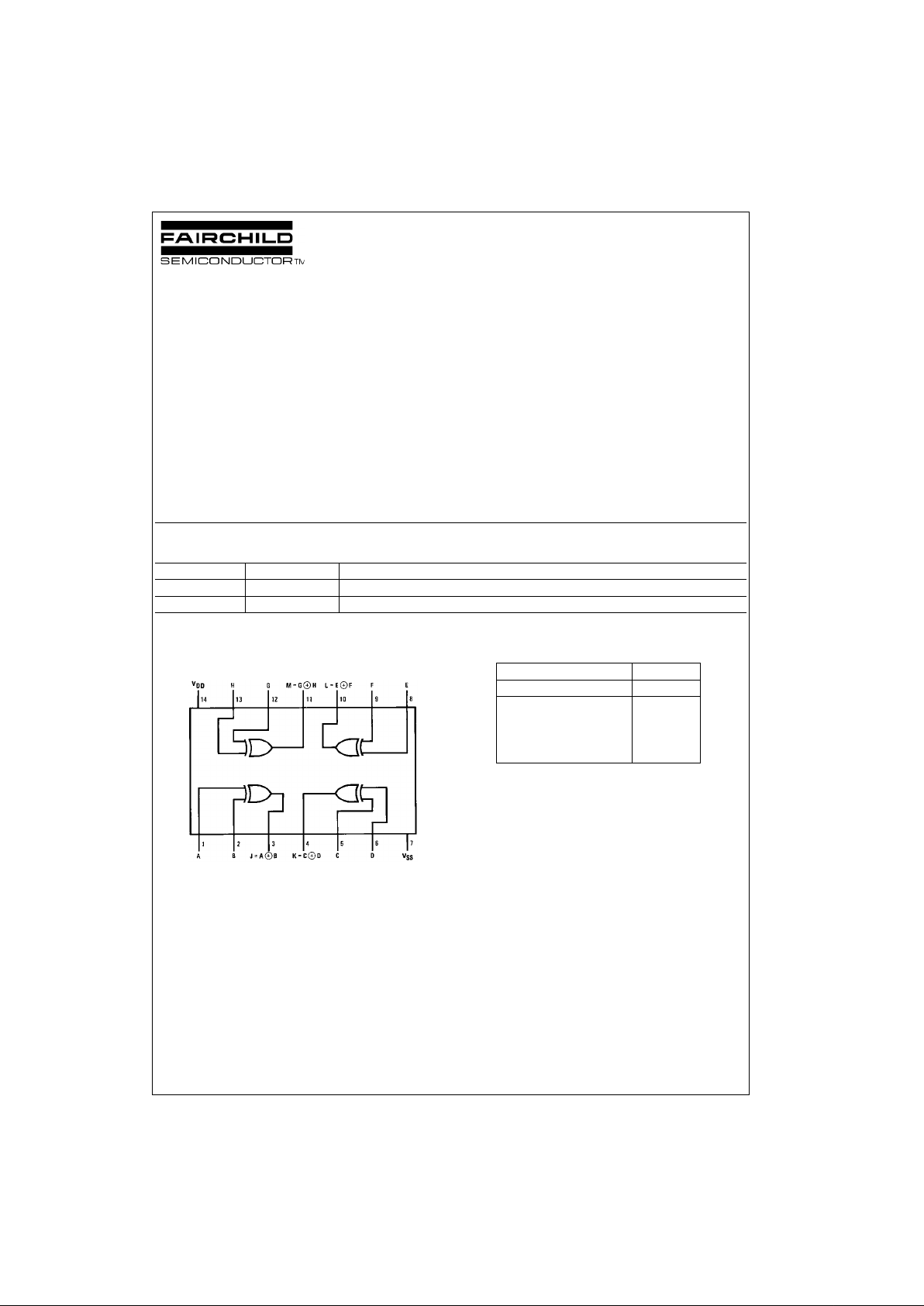

CD4070BC Quad 2-Input EXCLUSIVE-OR Gate

© 1999 Fairchild Semiconductor Corporation DS005976.prf www.fairchildsemi.com

CD4070BC

Quad 2-Input EXCLUSIVE-OR Gate

General Description

The CD4070BC employs complementary MOS (CMOS)

transistors to achieve wide power supply operatin g range,

low power consumption, and high noise margin, the

CD4070BC provide basic func tions used in the imple mentation of digital integrated circuit system s. The N- and Pchannel enhancement mode transistors provide a symmetrical circuit with output swing essentially equal to the supply

voltage. No DC power other than that caused by leakage

current is consumed during static condition. All inputs are

protected from damag e due to static discharge by diode

clamps to V

DD

and VSS.

Features

■ Wide supply voltage range: 3.0V to 15V

■ High noise immunity: 0.45 V

DD

typ.

■ Low power TTL compatibility:

Fan out of 2 driving 74L or 1 driving 74LS

■ Pin compatible to CD4030A

Equivalent to MM74C86 and MC14070B

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Connection Diagram

Pin Assignments for SOIC and DIP

Top View

Truth Table

Order Number Package Number Package Description

CD4070BCM M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” Narrow Body

CD4070BCN N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

Inputs Outputs

ABY

LLL

LHH

HLH

HHL

Page 2

www.fairchildsemi.com 2

CD4070BC

Absolute Maximum Ratings(Note 1)

(Note 2)

Recommended Operating

Conditions

(Note 2)

Note 1: “Absolute Maxi mum Ratings” are those valu es beyond which the

safety of the device cannot be guaranteed. They are not meant to imply

that the devices should be ope rated at these limi ts. The table of “Recommended Operating Conditions” and “Electrical Characteristics” provides

conditions for actual device op eration.

Note 2: V

SS

= 0V unless otherw is e s pecified.

DC Electrical Characteristics (Note 3)

Note 3: “Absolute Maximum Ratin gs” are those values beyond which t he safety of the device canno t be gua ranteed . They are not mea nt to im ply that the

devices should be operated at these limits. The table of “Recommended Operating Conditions” and “Electrical Characteristics” provides conditions for actual

device operation.

DC Supply Voltage (VDD) −0.5 to +18 V

DC

Input Voltage (VIN) −0.5toVDD+0.5 V

DC

Storage Temperature Range (TS) −65°C to +150°C

Power Dissipation (P

D

)

Dual-In-Line 700 mW

Small Outline 500 mW

Lead Temperature (T

L

)

(Soldering, 10 seconds) 260°C

DC Supply Voltage (V

DD

) 3V to 15 V

DC

Input Voltage (VIN)0 to V

DD VDC

Operating Temperature Range (TA) −40°C to +85°C

Symbol Parameter Conditions

−40°C +25°C +85°C

Units

Min Max Min Typ Max Min Max

I

DD

Quiescent Device VDD = 5V, 1.0 1.0 7.5 µA

Current VIN = VDD or V

SS

VDD = 10V, 2.0 2.0 15 µA

VIN = VDD or V

SS

VDD = 15V, 4.0 4.0 30 µA

VIN = VDD or V

SS

V

OL

LOW Level |IO| < 1 µA

Output Voltage VDD = 5V 0.05 0 0.05 0.05 V

VDD = 10V 0.05 0 0.05 0.05 V

VDD = 15V 0.05 0 0.05 0.05 V

V

OH

HIGH Level |IO| < 1 µA

Output Voltage VDD = 5V 4.95 4.95 5 4.95 V

VDD = 10V 9.95 9.95 10 9.95 V

VDD = 15V 14.95 14.95 15 14.95 V

V

IL

LOW Level |IO| < 1 µA

Input Voltage VDD = 5V, VO = 4.5V or 0.5V 1.5 1.5 1.5 V

VDD = 10V, VO = 9V or 1.0V 3.0 3.0 3.0 V

VDD = 15V, VO = 13.5V or 1.5V 4.0 4.0 4.0 V

V

IH

HIGH Level |IO| < 1 µA

Input Voltage VDD = 5V, VO = 0.5V or 4.5V 3.5 3.5 3.5 V

VDD = 10V, VO = 1V or 9.0V 7.0 7.0 7.0 V

VDD = 15V, VO = 1.5V or 13.5V 11.0 11.0 11.0 V

I

OL

LOW Level Output VDD = 5V, VO = 0.4V 0.52 0.44 0.88 0.36 mA

Current VDD = 10V, VO = 0.5V 1.3 1.1 2.25 0.9 mA

VDD = 15V, VO = 1.5V 3.6 3.0 8.8 2.4 mA

I

OH

HIGH Level Output VDD = 5V, VO = 4.6V −0.52 −0.44 −0.88 −0.36 mA

Current VDD = 10V, VO = 9.5V −1.3 −1.1 −2.25 −0.9 mA

VDD = 15V, VO = 13.5V −3.6 −3.0 −8.8 −2.4 mA

I

IN

Input Current VDD = 15V, VIN = 0V −0.3 −10−5−0.3 −1.0 µA

VDD = 15V, VIN = 15V 0.3 10−50.3 1.0 µA

Page 3

3 www.fairchildsemi.com

CD4070BC

AC Electrical Characteristics (Note 4)

TA = 25°C, CL = 50 pF, RL = 200k, tr and tf ≤ 20 ns, unless otherwise specified

Note 4: AC Parameters are guaranteed by DC correlated testin g.

Note 5: C

PD

determines t he no load AC power cons umption of any CMO S device. For compl ete explanatio n, see 74C Family Charac teristics Application

Note—AN-90.

Typical PerformanceCharacteristics

Propagation Delay Time

vs Load Capacitance

AC Test Circuit and Switching Time Waveforms

Note: Delays measured with input tr, tf = 20 ns.

t

r

= tf = 20 ns

Symbol Parameter Conditions Min Typ Max Units

t

PHL

or Propagation Delay Time VDD = 5V 110 185 ns

t

PLH

from Input to Output VDD = 10V 50 90 ns

VDD = 15V 40 75 ns

t

THL

or Transition Time VDD = 5V 100 200 ns

t

TLH

VDD = 10V 50 100 ns

VDD = 15V 40 80 ns

C

IN

Average Input Capacitance Any Input 5 7.5 pF

C

PD

Power Dissipation Capacitance Any Input (Note 5) 20 pF

Page 4

www.fairchildsemi.com 4

CD4070BC

Physical Dimensions inches (millimeters) unless otherwise noted

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” Narrow Body

Package Number M14A

Page 5

Fairchild does not assume any responsibility for use of any circuitry descri bed, no circuit patent licenses are implied and Fairchil d reser ves the right at any time without notice to change said circuitr y and specifications.

CD4070BC Quad 2-Input EXCLUSIVE-OR Gate

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or system s a re devices or syste ms

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be reasonably expected to result in a significant injur y to the

user.

2. A critical compon ent in any com ponent of a li fe support

device or system whose failure to p erform can be r easonably expected to cause the failure of the life suppor t

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

14-Lead Plastic Dual-In-Package (PDIP), JEDEC MS-001, 0.300” Wide

Package Number N14A

Loading...

Loading...