Page 1

1

Video ICs

SECAM chroma signal processor for

VHS VCRs

BA7207AS / BA7207AK

The BA7207AS and BA7207AK are LSI components that incorporate the contain circuitry required for SECAM chroma signal processing. The ICs have both recording and playback systems and each includes a bell filter, a bandpass filter, a limiter amplifier, a multiply-by-four circuit, a divide-by-four circuit, and a sync-gate circuit.

•

Applications

SECAM and VHS format video cassette recorders and

camcorders

•

Features

1) All filters required for SECAM chroma signal pro-

cessing are provided.

2) Built-in chroma killer circuit.

3) Built-in switch circuit for selecting PAL chroma or

SECAM chroma for the PB / REC system output.

•

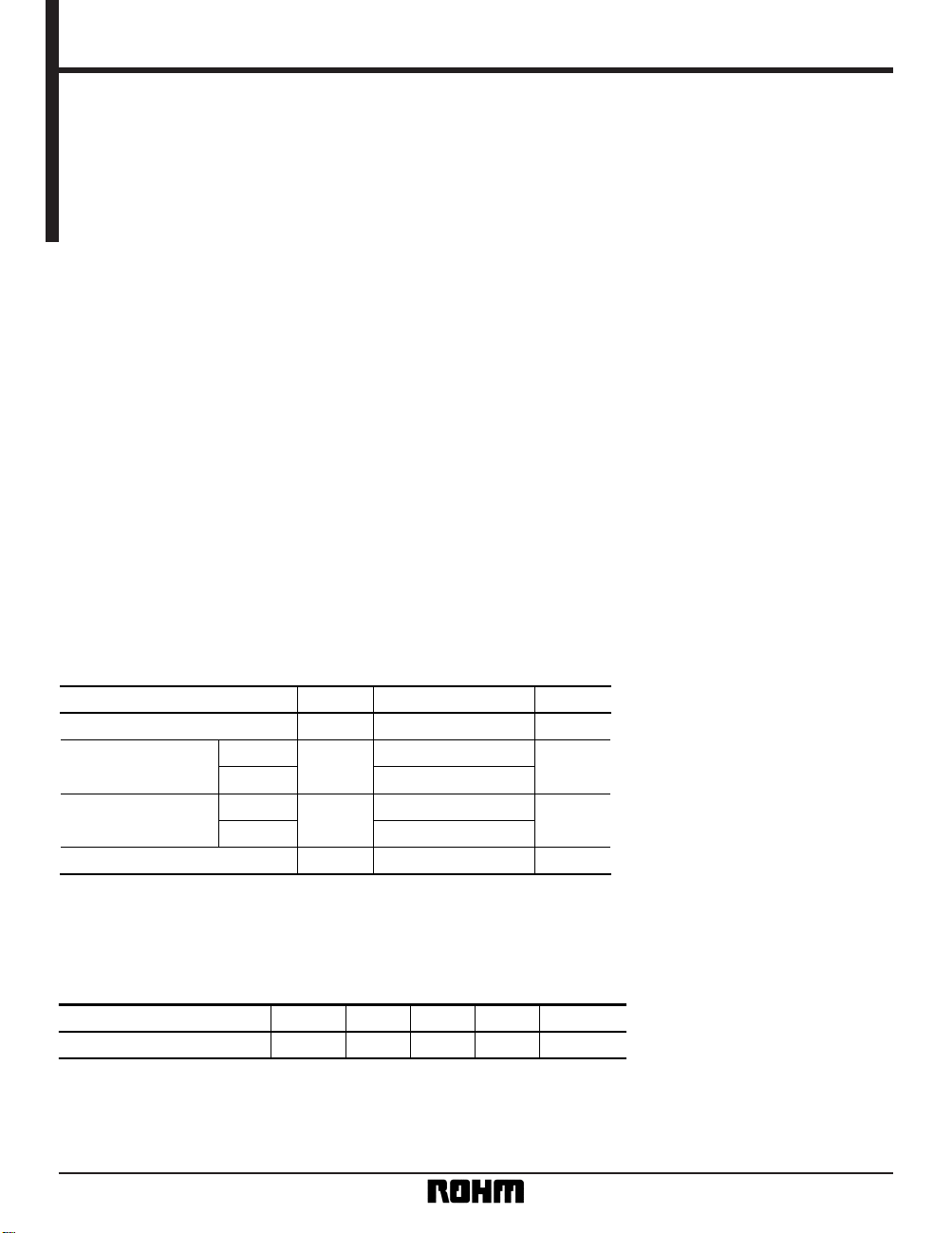

Absolute maximum ratings (Ta = 25°C)

•

Recommended operating conditions (Ta = 25°C)

Parameter Symbol Limits Unit

Power supply voltage

Power dissipation

Storage temperature

V

CC

7V

BA7207AS

BA7207AK

BA7207AS

BA7207AK

mWPd

Topr °C

Tstg

°C

1400 (SDIP32)

∗

1

– 25 ~ + 75

850 (QFP44)

∗

2

– 25 ~ + 65

– 55 ~ + 125

∗

1 Reduced by 14mW for each increase in Ta of 1°C over 25°C .

∗

2 When mounted on a 70mm × 70mm, t = 1.6mm glass epoxy board, reduced by 8.5W for each

increase in Ta of 1°C over 25°C.

Operating temperature

Parameter Symbol Min. Typ. Max. Unit

Operating power supply voltage

V

CC

4.5 5.0 5.5 V

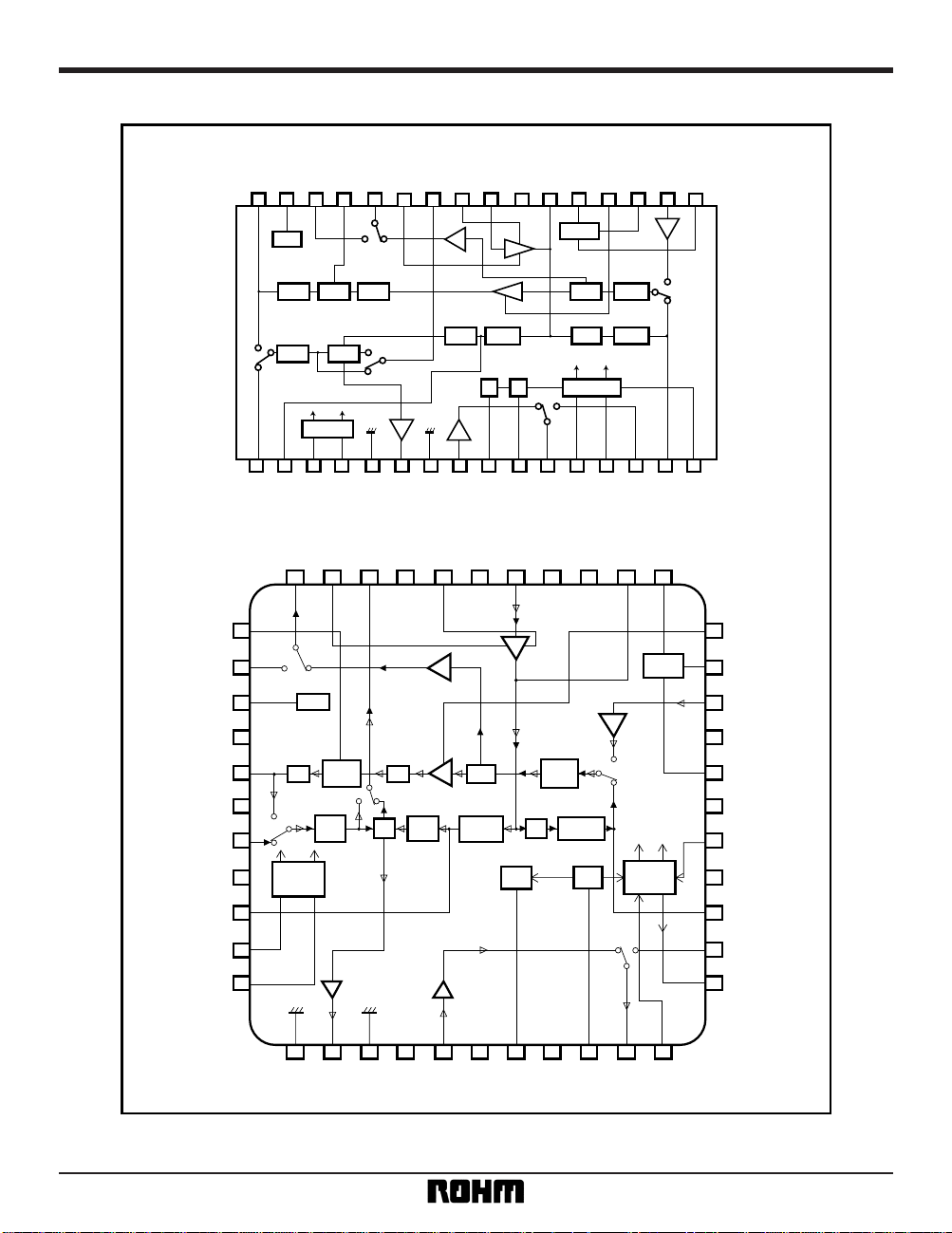

Page 2

2

Video ICs BA7207AS / BA7207AK

•

Block diagram

30 29 28

27

26

25

24

23 22

21

20

19

18

17

32 31

3 4 5 6 7 8 9 1011121314151612

VREG

×

2

×

2

2.2MHz

BPF

PAL SCM

R

R

P

P

P

R

RP

P

P

R

R

4.3MHz

BPF

—

A

4.3MHz

BPF - B

PB

SYNC GATE

1.1MHz

BPF

MODE

CONTOROL

REC

SYNC GATE

SYNC GATE TIMING

GENERATOR

BELL

DET

VCO

SCM

PAL

÷ 4

EQ

LIM

LIM

SYNCIN

DIV

PALPIN

SGC

SGADJ

PBOUT

VCO

DET

SCMPIN

GND

AMPOUT

GND1

FADJ2

FADJ1

MUL

RECIN

BWL

PBIN

RECH

CREF3

CTL

LAO

V

CC

LAIN

CREF1

ABELO

CREF2

RECOUT

TRAP

PALRIN

VREG

×

4O

FREQUENCY

ADJUSTER

BA7207AS (SDIP32)

BA7207AK (SQFP44)

PAL SCM

VREG

×

2

×

2

÷ 4

LIM

LIM

V

CC

CREF3

RECH

PBIN

N.C.

BWL

N.C.

SYNCIN

N.C.

DIV

PALPIN

SGC

TRAP

PALRIN

VREG

N.C.

×

4O

N.C.

RECIN

N.C.

MUL

FADJ1

FADJ2

P

P

P

R

P

P

R

R

P

R

R

EQ

DET VCO

SCM PAL

BELL

FREQUENCY

ADJUSTER

SYNC GATE

TIMING

GENERATOR

1.1MHz

BPF

2.2MHz

BPF

4.3MHz

BPF—A

4.3MHz

BPF—BPBSYNC GATE

REC

SYNC GATE

R

MODE

CONTROL

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

23

24

25

2627

28

29

30

31

32

33

1110987654321

GND

AMPOUT

GND1

N.C.

SCMPIN

N.C.

DET

N.C.

VCO

PBOUT

SGADJ

ABELO

CREF2

RECOUT

N.C.

CREF1

N.C.

LAIN

N.C.

VCC

LAO

CTL

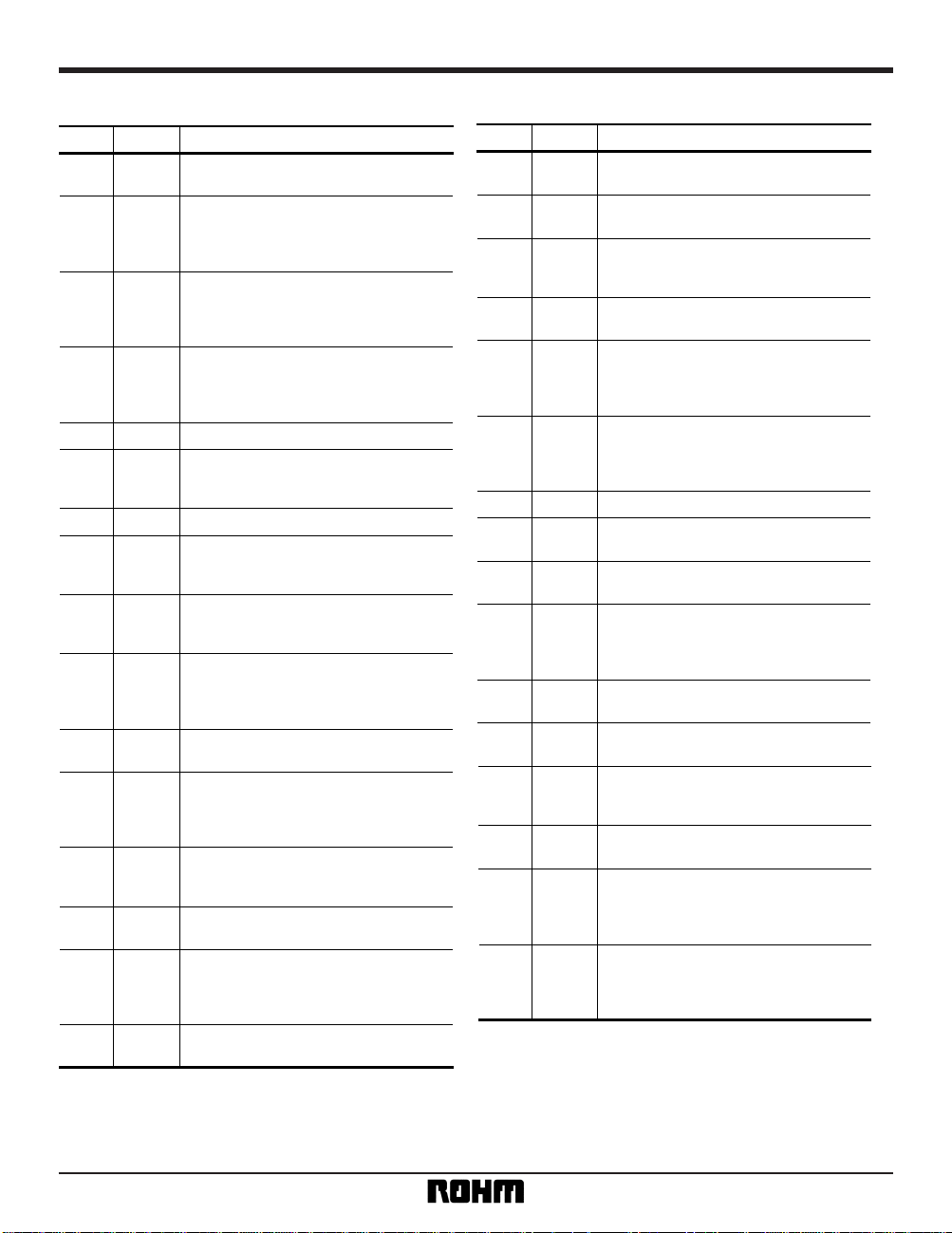

Page 3

3

Video ICs BA7207AS / BA7207AK

•

Pin descriptions

Pin name

1 (40) RECIN

2 (42) MUL

3 (43) FADJ1

4 (44) FADJ2

5 (1) GND1

6 (2) AMPOUT

7 (3) GND

8 (5) SCMPIN

9 (7) DET

10 (9) VCO

11 (10) PBOUT

12 (11) SGADJ

13 (12) SGC

Pin No. Function

Recording system input.

Input the REC system chroma signal.

PB sync gate output.

Test pin. Outputs the chroma signal after it is

multiplied by four and passed through the sync

gate. Normally connected to V

CC to prevent

interference.

Filter fo adjustment pin 1.

Used to adjust fo for the equalizer, 1.1MHz BPF

and 2.2MHz BPF. Connect a resistor and variable

resistor from this pin to GND.

Filter fo adjustment pin 2.

Used to adjust fo for the bell filter, 4.3MHz BPF-A

and 4.3MHz BPF-B. Connect a resistor and

variable resistor from this pin to GND.

Ground.

PB system preamplifier output.

Connect to GND via a variable resistor to adjust

the level, and input to pin 8.

Ground.

PB system output amplifier input.

Input the level-adjusted PB system SECAM

chroma signal.

Phase comparator output.

Connect to GND via a RC LPF to obtain the error

voltage.

VCO oscillator frequency control pin.

The error voltage is input via a resistor.

Connected to GND via free-running frequency

setting resistor.

PB system output.

Outputs the PB system chroma signal.

Fine adjustment for the sync gate phase.

The voltage from a resistor divider is used for fine

adjustment of the gate phase of the sync gate.

Normally open.

Sync gate timing output.

Test pin. Outputs the REC sync gate timing.

Normally open.

14 (13) PALPIN

15 (14) DIV

16 SYNCIN

PAL PB system input.

Input chroma signal for the PAL PB system.

Divide-by-four divider output.

Test pin. Outputs the chroma signal after it has

been divided by four. Normally connected to V

CC

to prevent interference.

Delayed sync signal input.

Input the synchronously-separated composite

17 (18) BWL

18 (20) PBIN

19 (21) RECH

20 (22) CREF3

21 (23) CTL

22 (24) LAO

23 (25)

24 (27) LAIN

25 (29) CREF1

26 (31) ABELO

27 (32) CREF2

BA7207AK pin numbers are given in brackets.

Pin namePin No. Function

V

CC

Chroma killer mode setting . "L" sets the IC in

chroma killer mode.

PB system input .

Input chroma signal for the PB system.

REC / PB mode switch.

Set to open or "H" for REC mode, "L" for PB

mode.

Bias terminal for the limiter amplifier before × 2.

Connect to GND via a capacitor.

SECAM / PAL output switch.

Selects the signal output for the REC / PB

terminal. Set to open or "H" for SECAM output

mode, "L" for PAL mode.

Limiter amplifier output.

Test pin. Outputs the amplitude-limited chroma

signal. Normally connected to V

CC to prevent

interference.

Power supply.

Limiter amplifier input.

Input the de-emphasised chroma signal.

Limiter amplifier bias pin 1.

Connect to GND via a capacitor.

REC BELL output. When in REC mode,

de-emphasised chroma signal is output via REC

BELL. When in PB mode, the PB system chroma

signal is output after being multiplied by four.

Limiter amplifier bias pin 2.

Connect to GND via a capacitor.

28 (33) RECOUT

29 (34) TRAP

30 (35) PALRIN

REC system output.

REC system chroma signal output.

TRAP connection.

Connect TRAP that rejects spurious signal

component after × 2 multiplication.

PAL REC system input.

PAL REC system chroma signal input.

31 (36) VREG

32 (38) ×

40

Regulated voltage output.

Output for the regulated 2.5V reference voltage

used for internal biasing. Connect to GND via a

bypass capacitor.

× 4 multiply output.

Test pin. Outputs the chroma signal after it is

multiplied by four. Normally connected to V

CC to

prevent interference.

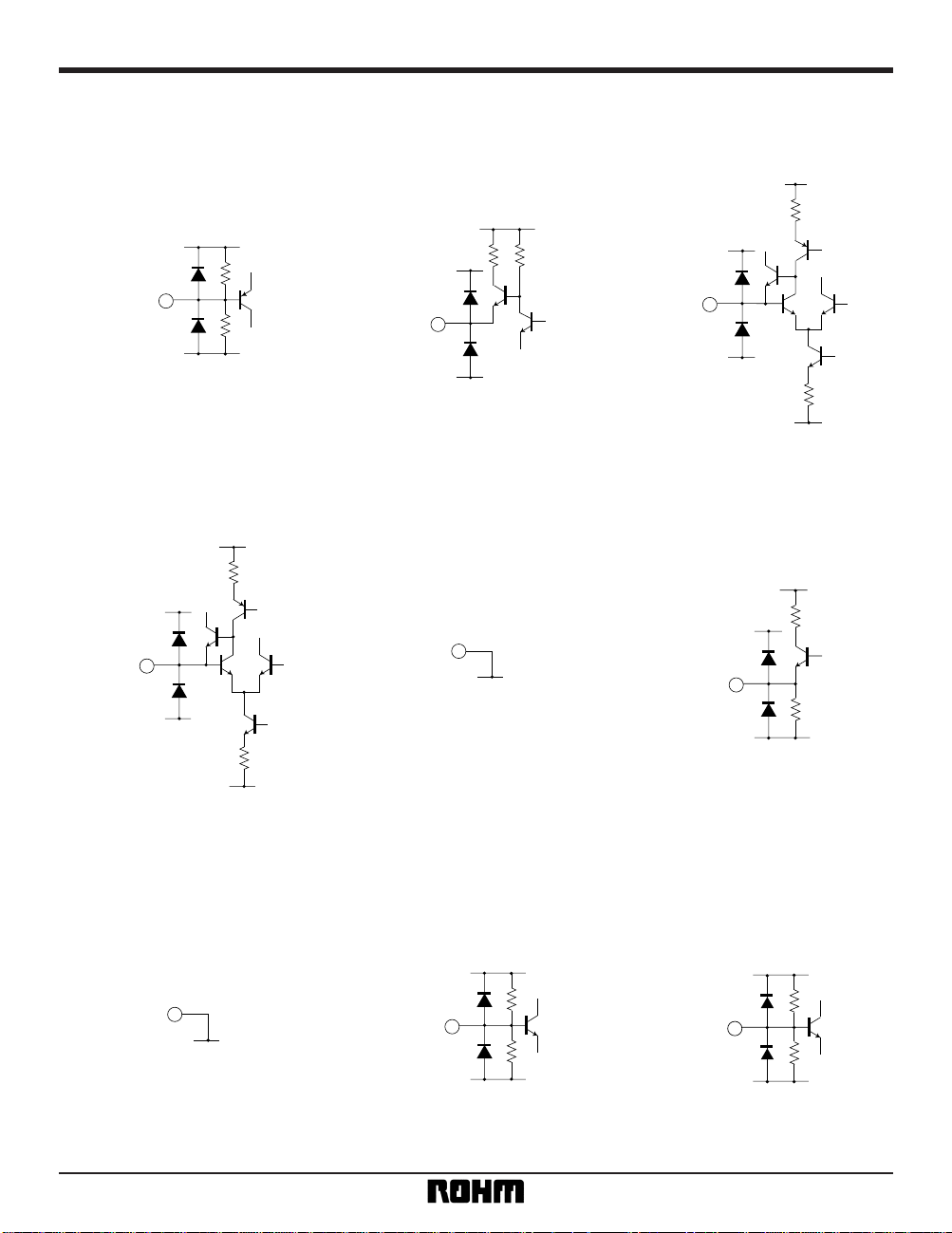

Page 4

4

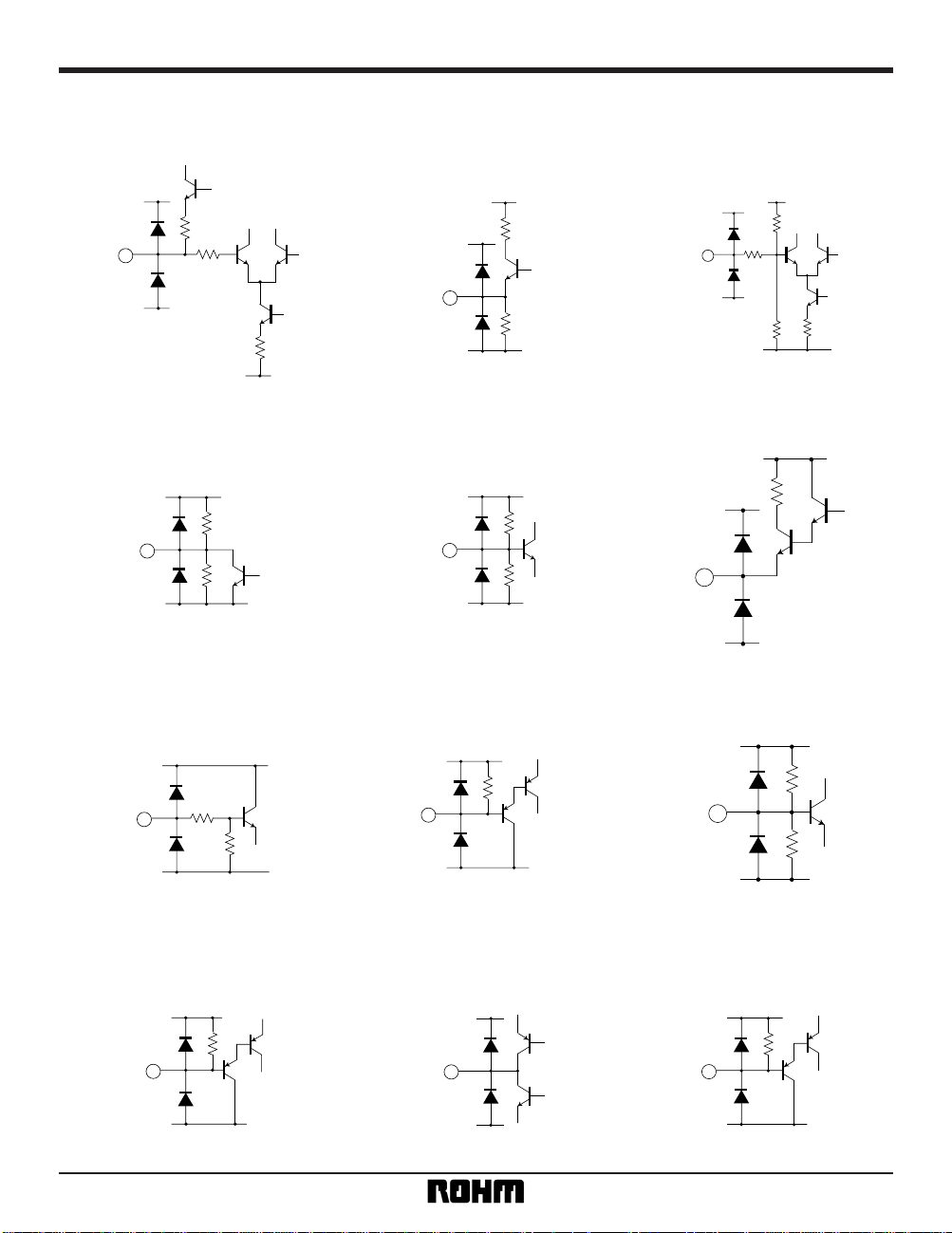

Video ICs BA7207AS / BA7207AK

•

Input / output circuits

RECIN

V

CC

40k

40k

GND

1pin

(40pin)

MUL

V

CC

VCC

GND

2pin

(42pin)

FADJ1

V

CC

VCC

GND

GND

3pin

(43pin)

FADJ2

V

CC

VCC

GND

GND

4pin

(44pin)

GND

GND1

5pin

(1pin)

AMPOUT

V

CC

VCC

5k

GND

6pin

(2pin)

GND

GND

7pin

(3pin)

SCMPIN

V

CC

20k

30k

GND

8pin

(5pin)

SCMPIN

V

CC

20k

30k

GND

9pin

(7pin)

Page 5

5

Video ICs BA7207AS / BA7207AK

VCO

V

CC

GND

GND

12k

5k

10pin

(9pin)

PBOUT

V

CC

VCC

GND

2.2k

11pin

(10pin)

SGADJ

V

CC

VCC

GND

GND

50k

50k

100k

12pin

(11pin)

SGC

V

CC

10k

10k

GND

13pin

(12pin)

PALPIN

V

CC

20k

30k

GND

14pin

(13pin)

DIV

V

CC

VCC

GND

15pin

(14pin)

SYNCIN

V

CC

15k

35k

GND

16pin

BWL

V

CC

50k

GND

17pin

(18pin)

PBIN

V

CC

20k

20k

GND

18pin

(20pin)

RECH

V

CC

GND

50k

19pin

(21pin)

CREF3

GND

V

CC

20pin

(22pin)

CTL

V

CC

50k

GND

21pin

(23pin)

Page 6

6

Video ICs BA7207AS / BA7207AK

LAO

VCC

VCC

GND

22pin

(24pin)

VCC

VCC

23pin

(25pin)

LAIN

V

CC

GND

GND

2k

24pin

(27pin)

CREF1

V

CC

30k

2k

GND

GND

25pin

(29pin)

ABELO

V

CC

VCC

GND

1.8k

26pin

(31pin)

CREF2

V

CC

GND

GND

2k

30k

27pin

(32pin)

RECOUT

V

CC

VCC

GND

1.8k

28pin

(33pin)

TRAP

V

CC

GND

560

200

29pin

(34pin)

PALRIN

V

CC

20k

30k

GND

30pin

(35pin)

VREG

V

CC

5.3k

GND

VCC

3k 3k

31pin

(36pin)

× 4O

VCC

VCC

GND

32pin

(38pin)

Pin numbers in parentheses are for the BA7207AK.

Page 7

7

Video ICs BA7207AS / BA7207AK

•

Electrical characteristics (unless otherwise noted, Ta = 25°C, VCC = 5.0V)

Parameter Symbol Min. Typ. Max. Unit Conditions

Measurement

circuit

IREC

39.2 56.0 72.8 mA REC mode Fig.1

I

PB

46.9 67.0 87.1 mA PB mode

V

REG

2.38 2.53 2.68 V Fig.1

fosc

13.8 15.625 17.4 Fig.1

CR

H

1.8 ——kHz Fig.1

CR

L

— — – 1.8 kHz Fig.1

LR

H

2.2 ——kHz Fig.1

LR

L

— — – 2.2 kHz Fig.1

V

REC

mVP-P Cyan level (cyan frequency) Fig.1

HD

R4 — — – 25 Fig.1

HD

R3 — — – 25 dB Fig.1

HD

R2 — — – 25 dB Fig.1

G

RS – 1 0 1 dB Fig.1

f

RS – 1 0 1 dB Fig.1

CT

R1 — – 60 — dB Fig.1

CT

R2 — – 60 — dB Fig.1

V

PB Cyan level (cyan frequency) Fig.1

HD

P3

— — – 35 dB Fig.1

HD

P2

— — – 35 dB Fig.1

HD

P1

— — – 35 dB Fig.1

G

P1

5 6 7 dB Fig.1

f

P1

– 1 0 1 dB Fig.1

CT

P1

— – 60 — dB Fig.1

G

P2

– 1 0 1 dB Fig.1

– 1 0 1 dB Fig.1

CT

P2

— – 60 — dB V14 = 0.3VP-P, 4.43MHz Fig.1

CT

RIN

— – 40 – 30 dB Fig.1

2.5 ——V Fig.1

V

L

——1.5 V Fig.1

f

P2

VH

Pins 14, 17, 19, 21 and 30

(Pins 13,18,21,23 and 35)

∗

Pins 14, 17, 19, 21 and 30

(Pins 13,18,21,23 and 35)

∗

V1 = 0.5VP-P, 4.286MHz

V

14 = 0.3VP-P, 5MHz / 100kHz

V

8 = 0.3VP-P, 4.3MHz

V

8 = 0.3VP-P, 5MHz / 100kHz

V

8 = 0.3VP-P, 4.3MHz

mV

P-P

V30 = 0.3VP-P, 627kHz

V

18 = 25mVP-P, 1.0715MHz

V

30 = 0.3VP-P, 5MHz / 100kHz

V

30 = 0.3VP-P, 627kHz

V

14 = 0.3VP-P, 4.43MHz

Fig.1

kHz

Delayed sync input

Delayed sync input

Delayed sync input

Delayed sync input

V

1 = 170mVP-P, 4.286MHz

V

1 = 170mVP-P, 4.286MHz

V

1 = 170mVP-P, 4.286MHz

dB

V

18 = 25mVP-P, 1.0715MHz

V

18 = 25mVP-P, 1.0715MHz

V

18 = 25mVP-P, 1.0715MHz

187.5 250.0 312.5

202.5 270.0 337.5

[Total device]

REC mode supply current

PB mode supply current

Regulator voltage

[Sync-gate block]

VCO free-running frequency

Capture range "H"

Capture range "L"

Lock range "H"

Lock range "L"

[REC system]

RECOUT output amplitude

Unwanted spectrum rejection

4MHz component

3MHz component

2MHz component

Output switch voltage gain

Output switch frequency characteristic

Output switch crosstalk 1

Output switch crosstalk 2

[PB system]

PB output amplitude

Unwanted spectrum rejection

3MHz component

2MHz component

1MHz component

Output switch voltage gain 1

Output switch frequency characteristic 1

Output switch crosstalk 1

Output switch voltage gain 2

Output switch frequency characteristic 2

Output switch crosstalk 2

RECIN crosstalk

[Control system]

High level voltage

Low level voltage

∗

BA7207AK pin numbers are given in brackets.

Page 8

8

Video ICs BA7207AS / BA7207AK

Parameter Symbol Unit ConditionsMax.Min. Typ.

– 2.8 0.7 4.2 dB Fig.1

– 6.5 – 3.0 0.5 dB Fig.1

—

– 35.0 – 26.0

dB Fig.1

– 11.3

dB Fig.1

dB Fig.1

dB Fig.1

G

RB1

dB Fig.1

G

RB2

dB Fig.1

G

RB3

dB Fig.1

G

PB1

dB Fig.1

G

PB2

dB Fig.1

G

PB3

dB Fig.1

G

RE1

dB Fig.1

G

RE2

dB Fig.1

G

RE3

dB Fig.1

G

PE1

dB Fig.1

G

PE2

– 5.1 – 1.6 1.9 dB Fig.1

G

PE3

dB Fig.1

G

F11

GF12

GF13

GF31

GF32

GF33

V18 = 25mVP-P, 1.0715MHz

V

18 = 25mVP-P, 0.5MHz

V

18 = 25mVP-P, 3.2145MHz

V

1 = 500mVP-P, 4.286MHz

V

1 = 500mVP-P, 3.2MHz

V

1 = 500mVP-P, 5.5MHz

V

1 = 170mVP-P, 4.286MHz

V

1 = 170mVP-P, 4.1MHz

V

1 = 170mVP-P, 4.5MHz

V

1 = 800mVP-P, 4.286MHz

V

1 = 800mVP-P, 4.1MHz

V

1 = 800mVP-P, 4.5MHz

V

18 = 95mVP-P, 1.0715MHz

V

18 = 95mVP-P, 1.0MHz

V

18 = 25mVP-P, 1.0715MHz

V

18 = 25mVP-P, 1.0MHz

V

18 = 25mVP-P, 1.2MHz

V

18 = 95mVP-P, 1.2MHz

– 16.1

– 14.0

– 7.8

– 12.6

– 10.5

– 4.3

– 9.1

– 7.0

6.3

0

– 0.2 – 3.7

– 3.5

2.8

– 7.2

– 7.0

– 0.7

– 20.9

– 16.2

– 15.3

– 17.4

– 12.7

– 11.8

– 13.9

– 9.2

– 8.3

– 4.0 – 0.5 3.0

11.1

13.7

7.6

10.26.7

4.1

2.5

– 8.9

6.0

– 5.4

9.5

– 1.9

[Filter block]

〈1.1MHz BPF characteristic〉

1.1MHz voltage gain

0.5MHz voltage gain

3.2MHz voltage gain

〈4.3MHz BPF - A characteristic〉

4.3MHz voltage gain

3.2MHz voltage gain

5.5MHz voltage gain

〈REC BELL + 4.3MHz BPF - A characteristic〉

4.3MHz voltage gain

4.1MHz voltage gain

4.5MHz voltage gain

〈PB BELL + 4.3MHz BPF - A characteristic〉

4.3MHz voltage gain

4.1MHz voltage gain

4.5MHz voltage gain

〈REC EQ + 1.1MHz BPF characteristic〉

1.1MHz voltage gain

1.0MHz voltage gain

1.2MHz voltage gain

〈PB EQ + 1.1MHz BPF characteristic〉

1.1MHz voltage gain

1.0MHz voltage gain

1.2MHz voltage gain

Measurement

circuit

•

Guaranteed design parameters (unless otherwise noted, Ta = 25°C, VCC = 5.0V, delayed sync input)

Parameter Symbol Unit ConditionsMin. Typ. Max.

REC sync-gate phase

PB sync-gate phase

REC sync-gate amplitude

PB sync-gate amplitude

T

DR

2.4 µs

T

DP

1.6 µs

T

WR

4.9 5.2 5.5 µs

T

WP

6.1 6.4 6.7 µs

DIV (pin 14 / pin 15), REC mode

MUL (pin 2 / pin 42), PB mode

DIV (pin 15 / pin 14), REC mode

MUL (pin 2 / pin 42), PB mode

The pin numbers in brackets are for the BA7207AS and the BA7207AK respectively.

1.3

0.5

3.5

2.7

Page 9

9

Video ICs BA7207AS / BA7207AK

•

Reference design data

(unless otherwise noted, Ta = 25°C, V

CC = 5.0V, fo (REC BELL) = 4.286MHz, fo (PB EQ) = 1.0715MHz)

Parameter Symbol Unit ConditionsMin. Typ. Max.

1.1MHz gain

0.5MHz suppression ratio

3.2MHz suppression ratio

Groupe delay time

2.2MHz gain

1.1MHz suppression ratio

3.2MHz suppression ratio

Groupe delay time

4.3MHz gain

3.2MHz suppression ratio

5.5MHz suppression ratio

Groupe delay time

4.3MHz gain

3.5MHz suppression ratio

5.2MHz suppression ratio

Groupe delay time

4.3MHz gain

4.1MHz suppression ratio

4.5MHz suppression ratio

4.3MHz gain

4.1MHz gain

4.5MHz gain

Center frequency ratio

1.1MHz gain

1.0MHz suppression ratio

1.2MHz suppression ratio

1.1MHz gain

1.0MHz gain

1.2MHz gain

Center frequency ratio

G

F11

— 1.0 — dB

G

F12

— – 4.0 — dB

G

F13

— – 30.0 — dB

370 420 470 nS

G

F21

— – 6.0 — dB

G

F22

——dB

G

F23

—

– 25.0

– 25.0 — dB

D

F2

180 230 280 ns

G

F31

— 7.0 — dB

G

F32

— – 3.0 — dB

G

F33

— – 3.0 — dB

D

F3

160 210 260 nS

G

F41

— 9.0 — dB

G

F42

— – 3.0 — dB

G

F43

— – 3.0 — dB

D

F4

250 300 350 nS

G

RB1

——dB

G

RB2

——dB

G

RB3

——dB

G

PB1

——dB

G

PB2

——dB

G

PB3

——dB

– 101%

G

RE1

——dB

G

RE2

——dB

G

RE3

——dB

G

PE1

——dB

G

PE2

——dB

G

PE3

——dB

df

OE – 101%

df

OB

19.5

– 5.0

– 5.5

– 19.5

5.0

5.5

19.5

– 8.0

– 11.0

– 19.5

8.0

11.0

V

IN = 0.3VP-P, 1.0715MHz

V

IN = 0.3VP-P, 0.5MHz

V

IN = 0.3VP-P, 3.2145MHz

V

IN = 0.3VP-P, 1.0715MHz

V

IN = 0.3VP-P, 2.143MHz

V

IN = 0.3VP-P, 1.0715MHz

V

IN = 0.3VP-P, 3.2145MHz

V

IN = 0.3VP-P, 2.143MHz

V

IN = 0.1VP-P, 4.286MHz

V

IN = 0.1VP-P, 3.2MHz

V

IN = 0.1VP-P, 5.5MHz

V

IN = 0.1VP-P, 4.286MHz

V

IN = 0.1VP-P, 4.286MHz

V

IN = 0.1VP-P, 3.5MHz

V

IN = 0.1VP-P, 5.2MHz

V

IN = 0.1VP-P, 4.286MHz

V

IN = 0.3VP-P, 4.286MHz

V

IN = 0.3VP-P, 4.1MHz

V

IN = 0.3VP-P, 4.5MHz

V

IN = 0.3VP-P, 4.286MHz

V

IN = 0.3VP-P, 4.1MHz

V

IN = 0.3VP-P, 4.5MHz

V

IN = 0.3VP-P, 1.0715MHz

V

IN = 0.3VP-P, 1.0MHz

V

IN = 0.3VP-P, 1.2MHz

V

IN = 0.3VP-P, 1.0715MHz

V

IN = 0.3VP-P, 1.0MHz

V

IN = 0.3VP-P, 1.2MHz

df

OE = (fO (REC) – fO (PB) ) / fO (PB)

dfOB = (fO (PB) – fO (REC) ) / fO (REC)

DF1

〈

1.1MHzBPF

〉

〈

2.2MHzBPF

〉

〈

4.3MHz BPF - A

〉

〈

4.3MHz BPF - B

〉

〈

REC BELL

〉

〈

PB BELL

〉

〈

PB EQ

〉

〈

REC EQ

〉

Page 10

10

Video ICs BA7207AS / BA7207AK

Vreg

× 2 × 2

2.2MHz

BPF

PAL SCM

R

R

P

P

P

P

P

R

RR

R

4.3MHz

BPF - A

4.3MHz

BPF - B

PB

SYNC GATE

1.1MHz

BPF

MODE

CONTOROL

REC

SYNC GATE

SYNC GATE TIMING

GENERATOR

BELL

DET

VCO

SCM

PAL

÷ 4

EQ

LIM

LIM

V

2.5V1.5V

SGCPBOUT

1N2

1

1

1 2 12 12

23

2

12

Vcc

33k

3.3k

0.01

µ

2

SG16

1

SW16

SW15

SW14a

OSC14

SW14b

100k

10k

4700p

0.01µ

0.47µ

12µ

560p

OSC8

AMPOUT

SW8

470

470

SW2 SW3 SW4

Vcc

7.5k

7.5k

8.5k 8.5k

3.9k

2k

VR2

2k

VR1

0.01µ

OSC1

FREQUENCY

ADJUSTER

CTL

BWL

RECH

A

Vcc

Vcc

47µ

0.01µ

0.01µ

0.01µ

0.1µ0.1µ0.1µ0.1µ

47µ

0.1µ

27p

RECOUT

Vcc

VREG

12

12

SW30b

OSC30

SW30a

1

1

1

2

2

2

N

N

N

SW21 SW19

SW18

OSC18

I23

100P

V

Fig. 1

BA7207AS (SDIP32)

32 31 30 28 27 26 25 24 23 22 21 20 19 18 1729

1 2 3 5 6 7 8 9 10 11 12 13 14 15 164

+

+

•

Measurement circuits

Page 11

11

Video ICs BA7207AS / BA7207AK

A

~

~

~

~

~

33 32 31 30 29 28 27 26 25 24 23

1 2 3 4 5 6 7 8 9 10 11

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

+

+

PAL

0.1µ 0.1µ

0.1µ

V

CC

VCC

I23

47µ

0.1µ

0.01µ

100p

SG16

SW16

21

OSC18

SW18

21

OSC14

VCC

SW14a

2

1

SW15

REC SG OUTSGCPB OUTAMP OUT

PB SG OUT

2

3.3k

1

0.01µ

0.47µ

0.01µ

12µ

0.01µ

0.1µ

0.01µ

47µ

27p

OSC30

VCC

VREG

SW30a

SW30b

REC OUT

1N2

12

OSC1

560p

470

470

SW8

OSC8

100k

33k

10k

123

4700p

0.01µ

SCM

VREG

× 2 × 2

÷ 4

LIM

LIM

VCC

P

P

P

R

P

P

R

R

P

R

R

EQ

DET VCO

SCM PAL

BELL

FREQUENCY

ADJUSTER

SYNC GATE

TIMING

GENERATOR

1.1MHz

BPF

2.2MHz

BPF

4.3MHz

BPF

—

A

4.3MHz

BPF—B

PB

SYNC GATE

REC

SYNC GATE

R

MODE

CONTROL

SW3 SW4

2k2k

7.5k7.5k

8.5k

3.9k

8.5k

VR1 VR2

1212

SW2

12

V

CC

SW21

1N2

SW19

1N2

SW4b

1.5V

2.5V

1N2

Fig. 2

BA7207AK (QFP44)

Page 12

12

Video ICs BA7207AS / BA7207AK

•

Circuit operation

(1) Recording system (REC)

The input to REC IN is passed through the 4.3MHz BPF-A to remove unwanted frequency components, and is flattened by REC BELL which has an anti-bell characteristic. The flattened signal is wave-shaped by the limiter amplifer,

and processed by the divide-by-four and sync gate circuits. Finally, unwanted frequency components are removed

by the 1.1MHz BPF and the REC EQ prepares the signal for recording playback and the signal is output on REC

OUT. Refer to Fig. 3.

1

26

24

( )

( )

( )

( )

28

4.3MHz

BPF - A

REC

BELL

LIMAMP

1.1MHz

BPF

÷ 4

REC

SYNC

GATE

REC

EQ

AMP

RECOUT

BA7207AS

(BA7207AK)

100pF

Composite video signal

Fig. 3

33

27

31

40

(2) Playback system (PB)

The input to PB IN is passed through the 1.1MHz BPF to remove unwanted frequency components, and is flattened

by the PB EQ circuit. The amplitude of the flattened signal fixed by the 1st-stage limiter amplifier, and the frequency

is multiplied by four by the multiplier circuit. Unwanted frequency components generated by the multiplier circuit are

removed by the 2.2MHz BPF and 4.3MHz BPF-A. The signal is wave-shaped by the limiter amplifier, and has gate

applied to it by the sync gate circuit then is passed through the 4.3MHz BPF-B to remove unwanted frequency components. The PB BELL circuit restores the original bell characteristic and the signal is output on PB OUT. Refer to

Fig. 4.

18

1.1MHz

BPF

PB

EQ

LPF

LIMAMP

2.2MHz

BPF

4.3MHz

BPF - A

× 2

× 2

AMP

BA7207AS

(BA7207AK)

RF chroma signal

24

26

6 8

11

PB

SYNC

GATE

AMP AMP

PBOUT

LIMAMP

4.3MHz

BPF - B

PB

BELL

TRAP

fcⱌ2.2MHz

Fig. 4

2

5

10

31

27

20

( ) ( )

( )

( )

( )

( )

(3) Sync gate timing circuit

REC and PB SYNC gate operation is as follows. The gate closes closes in synchronous with the SYNC IN input

pulse during the synchronous signal pulse (SYNC) horizontal scan interval (64µs period). During vertical retrace

(32µS period), the input pulse period becomes shorter than the horizontal scan interval. This is detected by the builtin vertical synchronous detector circuit which closes the gate. Refer to Fig. 5.

,

,

,

,

,

,

,

,

,

,

,

,

,

,

,

,

,

,

,

,

Horizontal scan interval Vertical retrace interval

4

µs

64

µs

32µs

SYNCIN

REC / PBOUT

Fig. 5

,,,,

,,,,

,,,,

,,,,

,,,,

,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,

,,,,,,,,

,,,,,,,,

,,,,,,,,

,,,,,,,,

,,,,,,,,

Page 13

13

Video ICs BA7207AS / BA7207AK

•

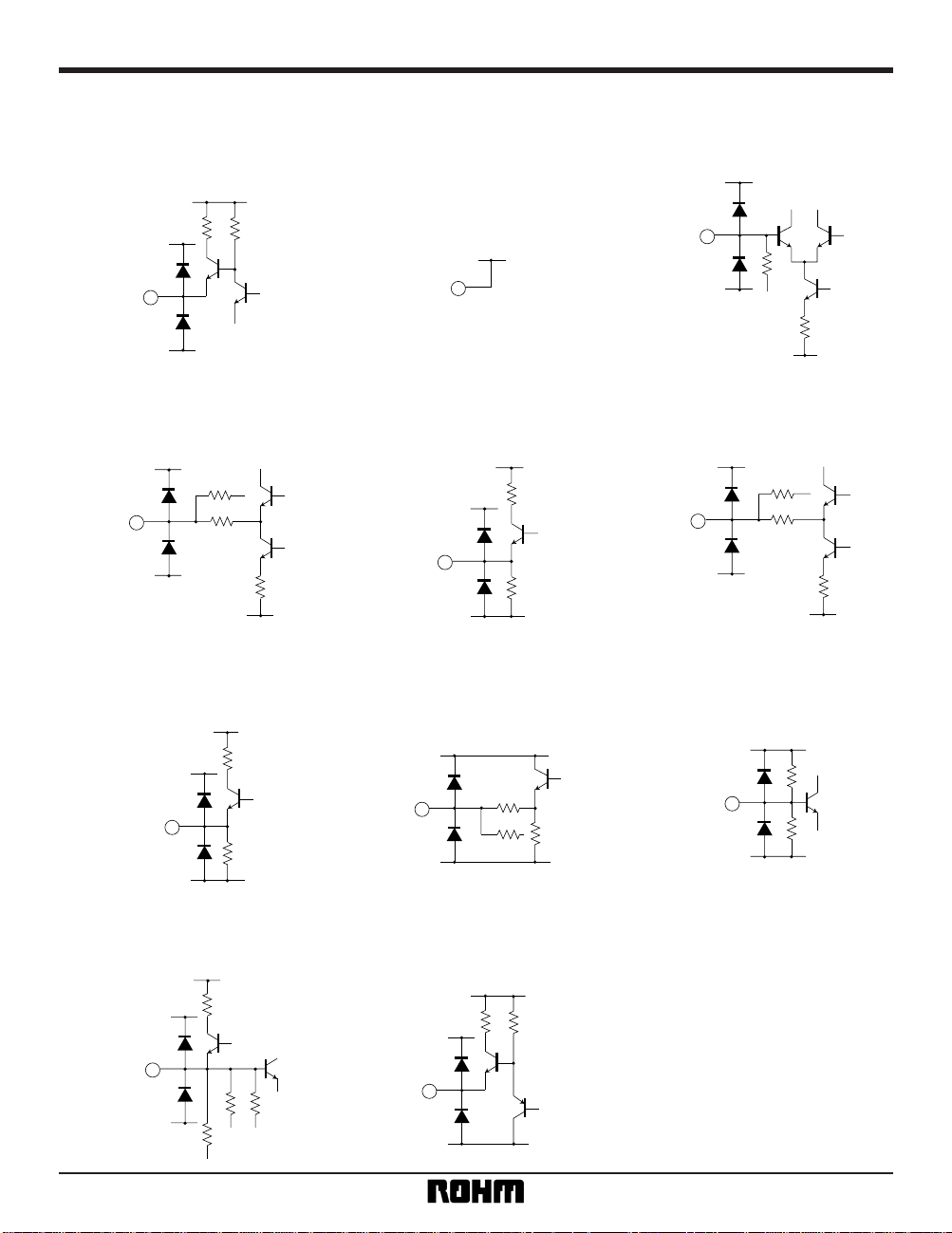

Application examples

BA7207AS (SDIP32)

To cancel the temperature characteristic of the ID, the resistors marked with asterisks should be of the metal film, and have a

temperature coefficient ± 100ppm / °C.

∆: Test pin. Connect to V

CC if unused.

The 100pF capacitor connected to pin 16 is intended to reduce temperature disper of the gate phase.It should have a static

capacitance tolerance of ± 10% or Ic and a temperature coefficient of ± 30ppm / °C ( – 55°C to + 125°C) A (CG).

∗

Vreg

× 2 × 2

2.2MHz

BPF

PAL

SCM

R

R

P

P

P

P

P

R

RR

R

4.3MHz

BPF - A

4.3MHz

BPF - B

PB

SYNC GATE

1.1MHz

BPF

MODE

CONTOROL

REC

SYNC GATE

SYNC GATE TIMING

GENERATOR

BELL

DET

VCO

SCM PAL

÷ 4

EQ

LIM

LIM

33k

0.01

0.01

100k

10k

4700p

0.01

0.47

7.5k

7.5k

FREQUENCY

ADJUSTER

∆

47

0.01

0.01

0.01

0.01

0.1

0.1

0.10.01

47

0.1µ

27p

∆

100

LPF

PAL REC C.

REC C OUT

V

CC

SCM / PAL

REC / PB

PBIN

B / W

SYNC IN

PALPB C

PB C OUT

RECIN

∆

100p

EQ fo ADJ

BELL fo ADJ

PBOUT LEVEL

∗ ∗

∗ ∗

∗

VR1 VR2 VR3

2KVR × 2

∆

1k

12

560p

100p

Fig. 6

32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17

3 4 5 6 7 8 9 10 11 12 13 14 15 1612

+

Page 14

14

Video ICs BA7207AS / BA7207AK

Fig. 7

∗

∗

∗

∗

∗

33 32 31 2930 28 27 25 24 23

22

21

20

18

16

13

12

15

17

19

34

35

36

38

40

42

43

44

41

39

37

26

1 2 3 54 6 10 11

BA7207AK (QFP44)

PAL

0.1µ

0.01µ0.01µ

0.1µ

0.01µ

100µ

47µ

0.01µ

0.01µ

0.1µ

LPF

100p

∆

∆

∆

0.47µ

0.01µ

0.01µ

12µ

580p

0.1µ

1k

VR3

VR2

100k

33k

10k

4700p

0.01µ

SCM

Vreg

× 2 × 2

÷ 4

LIM

LIM

VCC

P

P

P

R

P

P

R

R

P

R

R

EQ

DET VCO

SCM PAL

BELL

FREQUENCY

ADJUSTER

SYNC GATE

TIMING

GENERATOR

1.1MHz

BPF

2.2MHz

BPF

4.3MHz

BPF

—

A

4.3MHz

BPF—B

PB

SYNC GATE

REC

SYNC GATE

R

MODE

CONTROL

2k

BELL of ADJ

PBOUT LEVEL

EQ of ADJ

7.5k

VR

VR1

2k

7.5k

VR

100p

47µ

27p

PAL REC C.

REC C OUT.

VCC

SCM/PAL

REC/PB

PBIN

B/W

SYNC IN

PALPB C.

PB C OUT

RECIN

∆

+

+

To cancel the temperature characteristic of the ID, the resistors marked with asterisks should be of the metal film, and have a

temperature coefficient ± 100ppm / °C.

∆: Test pin. Connect to V

CC if unused.

The 100pF capacitor connected to pin 16 is intended to reduce temperature disper of the gate phase.It should have a static

capacitance tolerance of ± 10% or Ic and a temperature coefficient of ± 30ppm / °C ( – 55°C to + 125°C) A (CG).

∗

14

7 98

•

Control pin logic

Pin Low High (Open)

REC / PB setting switch

Output select switch

Chroma killer switch

RECH (19pin / 21pin) PB REC

CTL (21pin / 23pin) PAL SECAM

BWL (17pin / 18pin)

(BA7207AS / BA7207AK)

Chroma killer NORMAL

Page 15

15

Video ICs BA7207AS / BA7207AK

•

Operation notes

(1) Equalizer fo adjustment

Set to PB mode and input a 25mV

P-P, 1.0715MHz sine

wave to PBIN. Adjust the variable resistor connected

between FADJ1 and GND to maximize the REC OUT

output. This adjustment also adjusts the 1.1MHz and

2.2MHz band-pass filters. The value of the variable

resistor must be at least 2kΩ. If it is less than this,

adjustment may not be possible.

(2) Bell filter fo adjustment

Set to REC mode and input a 170mV

P-P, 4.286MHz

sine wave to RECIN. Adjust the variable resistor connected between FADJ2 and GND to maximize the

AMP OUT output. This adjustment also adjusts the

4.3MHz and 4.3MHz A and B band-pass filters. The

value of the variable resistor must be at least 2kΩ. If it

is less than this, adjustment may not be possible.

(3) Test pins

The MUL, DIV, LAO and 4XO pins are test terminals.

By connecting these pins to GND via a 3.6kΩ resistor,

it is possible to monitor there waveforms. When

unused, connect these pins to V

CC to prevent interfer-

ence.

(4) REC / PB input levels

The frequency characteristics of the built-in filters can

change. For this reason use the following input signal

levels:

RECIN: 540mV

P-P + / – 6dB (cyan level)

PBIN: 75mV

P-P + / – 6dB (cyan level)

(5) Capacitor connected to VREG

Use a ceramic with a static capacitance of 0.1µF. The

filter may not operate correctly with other capacitance

values.

(6) PBIN input

If there is a chroma component imposed on the FM

brightness signal, use a low-pass filter (with an fc of

about 2.2MHz) to remove the FM brightness signal

component, and ensure that only the chroma component is input to PBIN.

(7) RECIN input

In the case of composite video input, connect a 100pF

capacitor to ensure that only the chroma component is

input to RECIN.

(8) Sync-gate phase adjustment

Perform fine adjustment of the sync-gate phase by

applying a voltage to the SGADJ terminal, or using a

resistor divider connected between V

CC and GND. The

adjustment sensitivity is shown in Fig. 6.

SGADJ pin voltage when open: V

SGADJ = 2.5V

Input impedance Z = 125kΩ

1.5 2.5 3.5

+ 3.2

0

– 3.2

0.32µS / 0.1V

SGADJ PIN APPLY VOLTAGE: V

SGADJ (V)

GATE PHASE ADJUSTMENT: TDR (µS)

Fig. 8 Sync-gate phase

Page 16

16

Video ICs BA7207AS / BA7207AK

REC / PB EQ FREQUENCY: fo (MHz)

FADJ1 RESISTANCE VALUE: RADJ1 (kΩ)

7.5 8.0 8.5 9.0 9.5

1.3

1.2

1.1

1.0

0.9

Fig. 9 REC / PB EQ fO

frequency adjustment

range

•

Electrical characteristic curves

6PIN REC BELL FREQUENCY: fo (MHz)

1PIN REC IN LEVEL: VIREC (mVP-P)

fo

Conditions

V

CC = 5.0V

fo = 4.286MHz

V = 170mV

P-P

0

4.15

4.20

4.25

4.30

4.35

4.40

100 200 300 400 500

Fig. 11 REC / BELL fO

frequency variation

REC / PB BELL FREQUENCY: fo (MHz)

FADJ2 RESISTANCE VALUE: RADJ2 (kΩ)

7.5 8.0 8.5 9.0 9.5

5.5

5.0

4.5

4.0

3.5

Fig. 10 REC / PB BELL fO

frequency adjustment

range

28PIN PB EQ FREQUENCY: fo (MHz)

18PIN PB IN LEVEL: VIPB (mVP-P)

fo

Conditions

V

CC = 5.0V

fo = 1.0715MHz

V = 25mV

P-P

1.04

1.05

1.06

1.07

1.08

1.09

0 20 40 60 80 100

Fig. 12 PB EQ fO frequency

variation characteristics

PB OUT LEVEL: VOPB (dBm)

FREQUENCY: f (MHz)

2MHz component

1MHz

component

3MHz

component

6MHz component

8MHz component

7MHz

component

5MHz

component

Fundamental frequency

component

PB IN

f = 1.0715MHz

V = 25mV

P-P

02 4 6 81013 57 9

– 110

– 100

– 90

– 80

– 70

– 60

– 50

– 40

– 30

– 20

– 10

Fig. 14 PB OUT spurious

characteristics

REC OUT LEVEL: VOREC (dBm)

FREQUENCY: f (MHz)

Fundamental

frequency

component

2MHz

component

3MHz

component

4MHz

component

RECIN

f = 4.286MHz

V = 170mV

P-P

– 10

– 20

– 30

– 40

– 50

– 60

– 70

– 80

– 90

– 100

– 110

0 1.0 2.0 3.0 4.0 5.0

Fig. 13 REC OUT spurious

characteristics

Page 17

17

Video ICs BA7207AS / BA7207AK

SDIP32

BA7207AS BA7207AK

4.7 ± 0.3

0.51Min.

8.4 ± 0.3

3.2 ± 0.2

32

116

17

0.5 ± 0.1

0.3

± 0.1

28.0 ± 0.3

0° ~ 15°

10.16

1.778

QFP44

33 23

22

12

1

34

44

10.0 ± 0.2

14.0 ± 0.3

0.35 ± 0.1

10.0 ± 0.2

14.0 ± 0.3

1.2

0.05

2.15 ± 0.1

0.15 ± 0.1

0.8

11

0.15

•

External dimensions (Units: mm)

Loading...

Loading...