Datasheet 74LVXC3245TTR, 74LVXC3245MTR, 74LVXC3245M Datasheet (SGS Thomson Microelectronics)

Page 1

1/12July 2001

■ HIGH SPEED :

t

PD

= 8ns (MAX.) at TA=25°C

V

CCA

= 3.3V, V

CCB

= 5.0V

■ LOW POWER DISSIPATION:

I

CCA

= I

CCB

= 5µA(MAX.) at TA=25°C

■ LOW NOISE: V

OLP

=0.3V (TYP.) at

V

CCA

=3.3V

■ SYMMETRICAL OUTPUT IMPEDANCE:

|I

OH

| = IOL = 24mA (MIN)

■ BALANCED PROPAGATION DELAYS:

t

PLH

≅ t

PHL

■ OPERATING VOLTAGE R ANGE:

V

CCA

(OPR) = 2.7V to 3.6V (1.2V Data Retention)

V

CCB

(OPR) = 2.7V to 5.5V (1.2V Data Retention)

PIN AND FUNCTION COMPATIBLE WITH

74 SERIES C3245

■ IMPROVED LATCH-UP IMMUNITY

DESCRIPTION

The 74LVXC3245 is a dual supply 8 bit

configurable low voltage CMOS OCTAL BUS

TRANSCEIVER fabricated with sub-micron silicon

gate and double-layer metal wiring C

2

MOS

technology. Designed for use as an interface

between a 3.3V bus and a 3.3V to 5V bus in a

mixed 3.3V/5V supply systems, it achieves high

speed operation while m aintaini ng the CMOS low

power dissipation.

This IC is intended for two-way asynchronous

communication between data buses and the

direction of data transmission is determined by

DIR input. The enable input G

can be used to

disable the device so that the buses are effectively

isolated.

The A-port interfaces with the 3V bus, the B-port

with the 5V bus.

All inputs are equipped with protection circuits

against static discharge, giving them 2KV ESD

immunity and transient excess voltage.

74LVXC3245

OCTAL DUAL SUPPLY BUS TRANSCEIVER

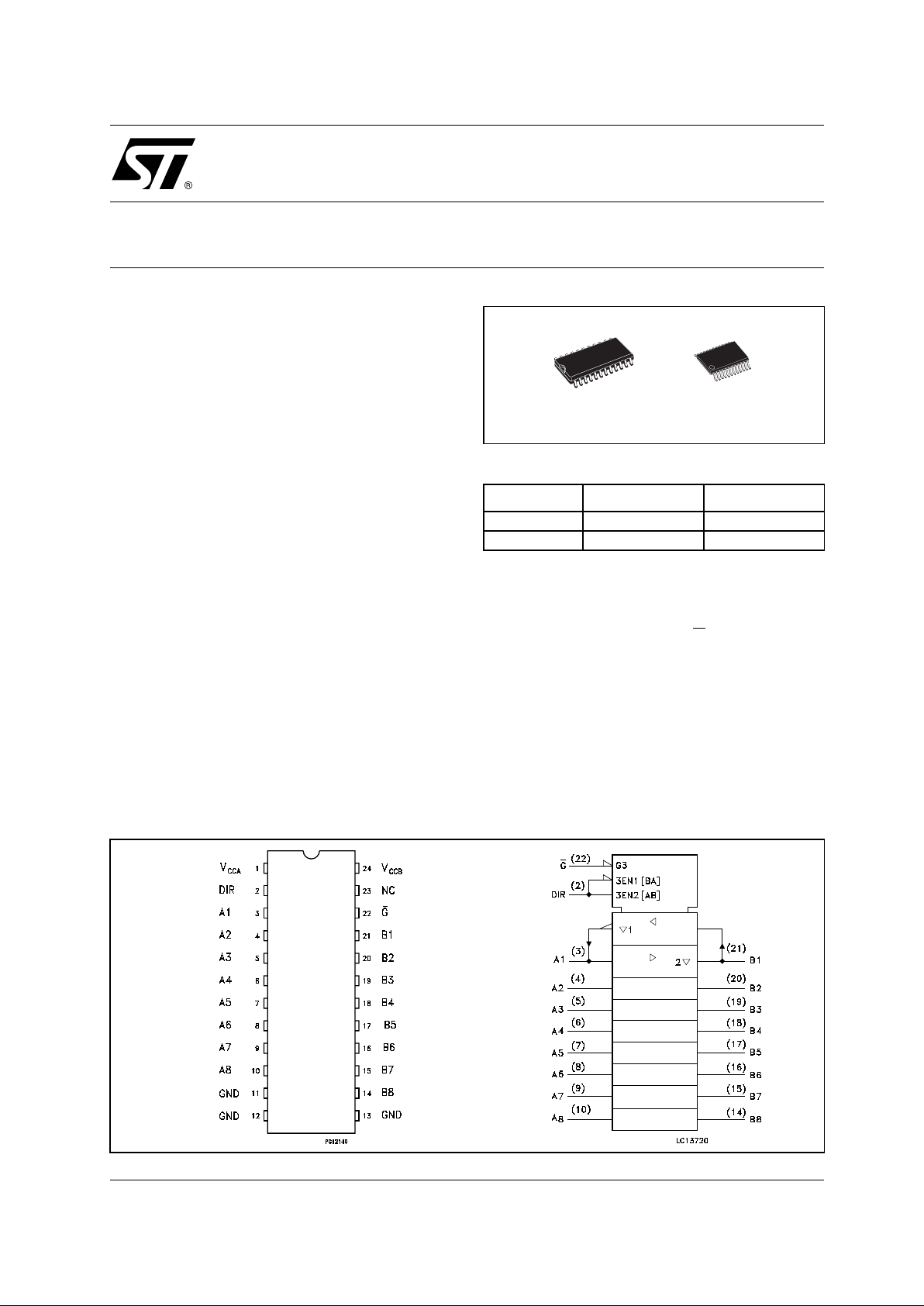

PIN CONNECTION AND IEC LOGIC SYMBOLS

ORDER CODES

PACKAGE TUBE T & R

SOP 74LVXC3245M 74LVXC3245MTR

TSSOP 74LVXC3245TTR

TSSOPSOP

Page 2

74LVXC3245

2/12

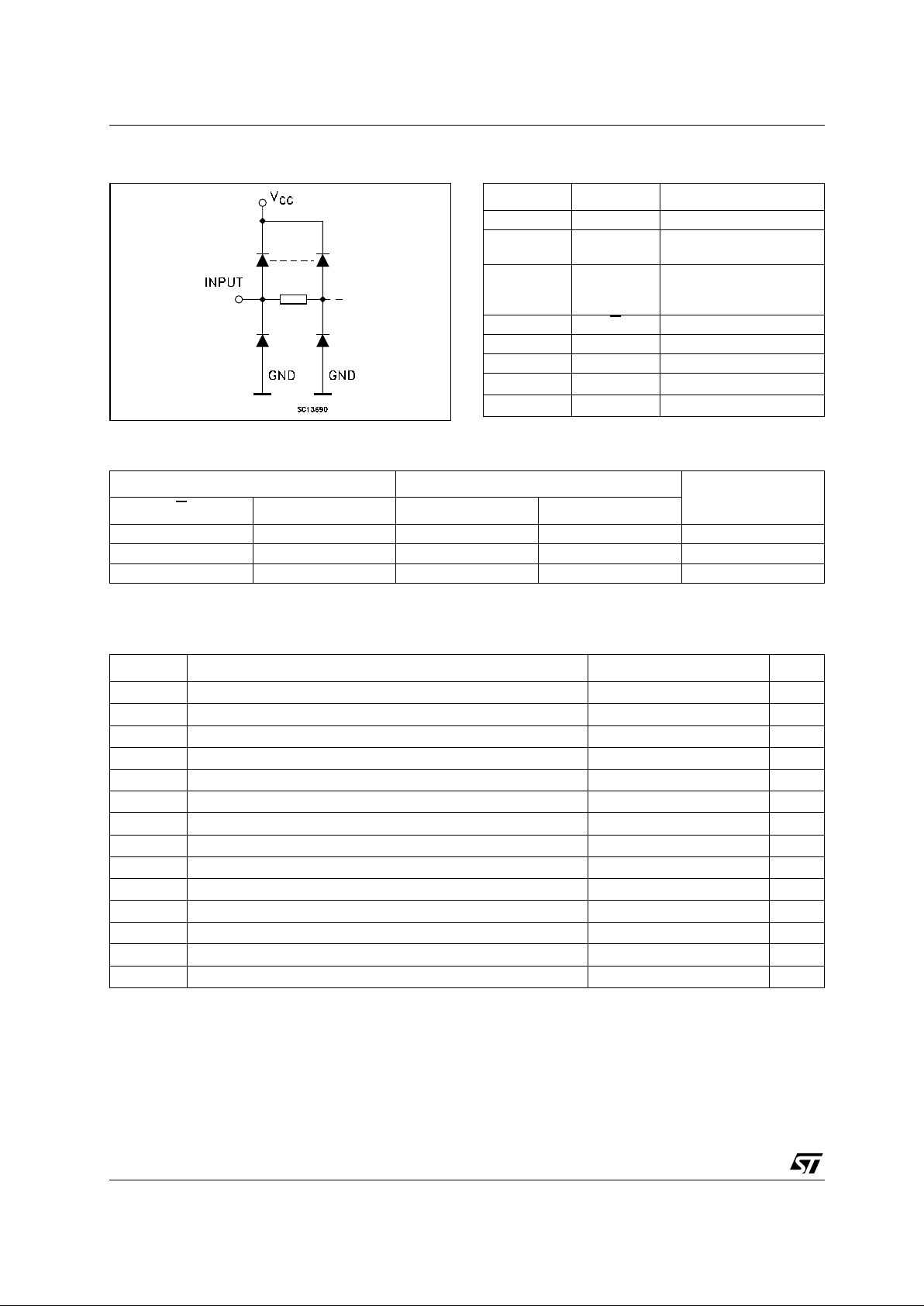

INPUT AND OUTPUT EQUIVALENT CIRCUIT PIN DESCRIPTION

TRUTH TABLE

X : Don’t Care

Z : High Impedance

ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is

not implied

PIN No SYMBOL NAME AND FUNCTION

2 DIR Directional Control

3, 4, 5, 6, 7,

8, 9, 10

A1 to A8 Data Inputs/Outputs

21, 20, 19,

18, 17, 16,

15, 14

B1 to B8 Data Inputs/Outputs

22 G

Output Enable Input

11, 12, 13 GND Ground (0V)

23 NC Not Connected

1V

CCA

Positive Supply Voltage

24 V

CCB

Positive Supply Voltage

INPUTS FUNCTION

OUTPUT

G

DIR A BUS B BUS

L L OUTPUT INPUT A = B

L H INPUT OUTPUT B = A

HXZZZ

Symbol Parameter Value Unit

V

CCA

Supply Voltage

-0.5 to +7.0 V

V

CCB

Supply Voltage

-0.5 to +7.0 V

V

I

DC Input Voltage -0.5 to V

CCA

+ 0.5

V

V

I/OA

DC I/O Voltage -0.5 to V

CCA

+ 0.5

V

V

I/OB

DC I/O Voltage -0.5 to V

CCB

+ 0.5

V

I

IK

DC Input Diode Current

± 20 mA

I

OK

DC Output Diode Current

± 50 mA

I

OA

DC Output Current

± 50 mA

I

OB

DC Output Current

± 50 mA

I

CCA

DC VCC or Ground Current

± 200 mA

I

CCB

DC VCC or Ground Current

± 100 mA

P

d

Power Dissipation

180 mW

T

stg

Storage Temperature

-65 to +150 °C

T

L

Lead Temperature (10 sec)

300 °C

Page 3

74LVXC3245

3/12

RECOMMENDED OPERATING CONDITIONS

1) VIN from 30 % to 70% of V

CC

2) V

CCA

= 2.7 to 3.6V; V

CCB

= 2.7 to 5.5V;

Symbol Parameter Value Unit

V

CCA

Supply Voltage (note 1)

2.7 to 3.6 V

V

CCB

Supply Voltage (note 1)

2.7 to 5.5 V

V

I

Input Voltage 0 to V

CCA

V

V

I/OA

I/O Voltage 0 to V

CCA

V

V

I/OB

I/O Voltage 0 to V

CCB

V

T

op

Operating Temperature

-55 to 125 °C

dt/dv Input Rise and Fall Time (note 2) 0 to 10 ns/V

Page 4

74LVXC3245

4/12

DC SPECIFICATIONS FOR V

CCA

Symbol Parameter

Test Condition Value

Unit

V

CCA

(V)

V

CCB

(V)

T

A

= 25 °C

-40 to 85 °C -55 to 125°C

Min. Typ. Max. Min. Max. Min. Max.

V

IHA

High Level Input

Voltage

2.7 3.0 2.0 2.0 2.0

V3.0 3.6 2.0 2.0 2.0

3.6 5.5 2.0 2.0 2.0

V

ILA

Low Level Input

Voltage

2.7 3.0 0.8 0.8 0.8

V3.0 3.6 0.8 0.8 0.8

3.6 5.5 0.8 0.8 0.8

V

OHA

High Level

Output Voltage

3.0 3.0

IO=-100 µA

2.9 2.99 2.9 2.9

V

3.0 3.0

I

O

=-12 mA

2.56 2.85 2.46 2.46

3.0 3.0

I

O

=-24 mA

2.35 2.65 2.25 2.25

2.7 3.0

I

O

=-12 mA

2.3 2.5 2.2 2.2

2.7 4.5

I

O

=-24 mA

2.1 2.3 2.0 2.0

V

OLA

Low Level Output

Voltage

3.0 3.0

IO=100 µA

0.0 0.1 0.1 0.1

V

3.0 3.0

I

O

=24 mA

0.21 0.36 0.44 0.44

2.7 3.0

I

O

=12 mA

0.11 0.36 0.44 0.44

2.7 4.5

I

O

=24 mA

0.22 0.42 0.5 0.5

I

IA

Input Leakage

Current

3.6 5.5

V

I

= VCC or GND

± 0.1 ± 1 ± 1 µA

I

OZA

High Impedance

Output Leakage

Current

3.6 5.5 VIA = V

IHA

or V

ILA

VIB = V

IHB

or V

ILB

V

I/OA

= V

CCA

or

GND

± 0.5 ± 5 ± 5 µA

I

CCtA

Quiescent Supply

Current

3.6 5.5 VIA = V

CCA

or

GND

V

IB

= V

CCB

or

GND

55050µA

I

CCtAF

Quiescent V

CCA

Supply Current

as B Port Floats

3.6 Open VIA = V

CCA

or

GND G

= DIR =

V

CCA

VIB = Open

55050µA

∆I

CCtA

Maximum

Quiescent Supply

Current / Input

(An, DIR, G

)

3.6 5.5 V

IA

= V

CCA

- 0.6V

V

IB

= V

CCB

or

GND

0.35 0.5 0.5 mA

Page 5

74LVXC3245

5/12

DC SPECIFICATIONS FOR V

CCB

Symbol Parameter

Test Condition Value

Unit

V

CCA

(V)

V

CCB

(V)

T

A

= 25 °C

-40 to 85 °C -55 to 125°C

Min. Typ. Max. Min. Max. Min. Max.

V

IHB

High Level Input

Voltage

2.7 3.0 2.0 2.0 2.0

V3.0 3.6 2.0 2.0 2.0

3.6 5.5 3.85 3.85 3.85

V

ILB

Low Level Input

Voltage

2.7 3.0 0.8 0.8 0.8

V3.0 3.6 0.8 0.8 0.8

3.6 5.5 1.65 1.65 1.65

V

OHB

High Level

Output Voltage

3.0 3.0

IO=-100 µA

2.9 3.0 2.9 2.9

V

3.0 3.0

I

O

=-12 mA

2.56 2.85 2.46 2.46

3.0 3.0

I

O

=-24 mA

2.35 2.65 2.25 2.25

3.0 4.5

I

O

=-24 mA

3.86 4.25 3.76 3.76

V

OLB

Low Level Output

Voltage

3.0 3.0

IO=100 µA

0.00 0.1 0.1 0.1

V3.0 3.0

I

O

=24 mA

0.21 0.36 0.44 0.44

3.0 4.5

I

O

=24 mA

0.18 0.36 0.44 0.44

I

IB

Input Leakage

Current

3.6 5.5

V

I

= V

CCA

or GND

± 0.1 ± 1 ± 1 µA

I

OZB

High Impedance

Output Leakage

Current

3.6 5.5 VIA = V

IHA

or V

ILA

V

I/OB

= V

CCB

or

GND

± 0.5 ± 5 ± 5 µA

I

CCtB

Quiescent Supply

Current

3.6 5.5 VIA = V

CCA

or

GND

V

IB

= V

CCB

or

GND

55050µA

∆I

CCtB

Maximum

Quiescent Supply

Current / Input

3.6 5.5 VIA = V

CCA

or

GND

V

IB

= V

CCB

- 2.1V

1.35 1.5 1.5 mA

Page 6

74LVXC3245

6/12

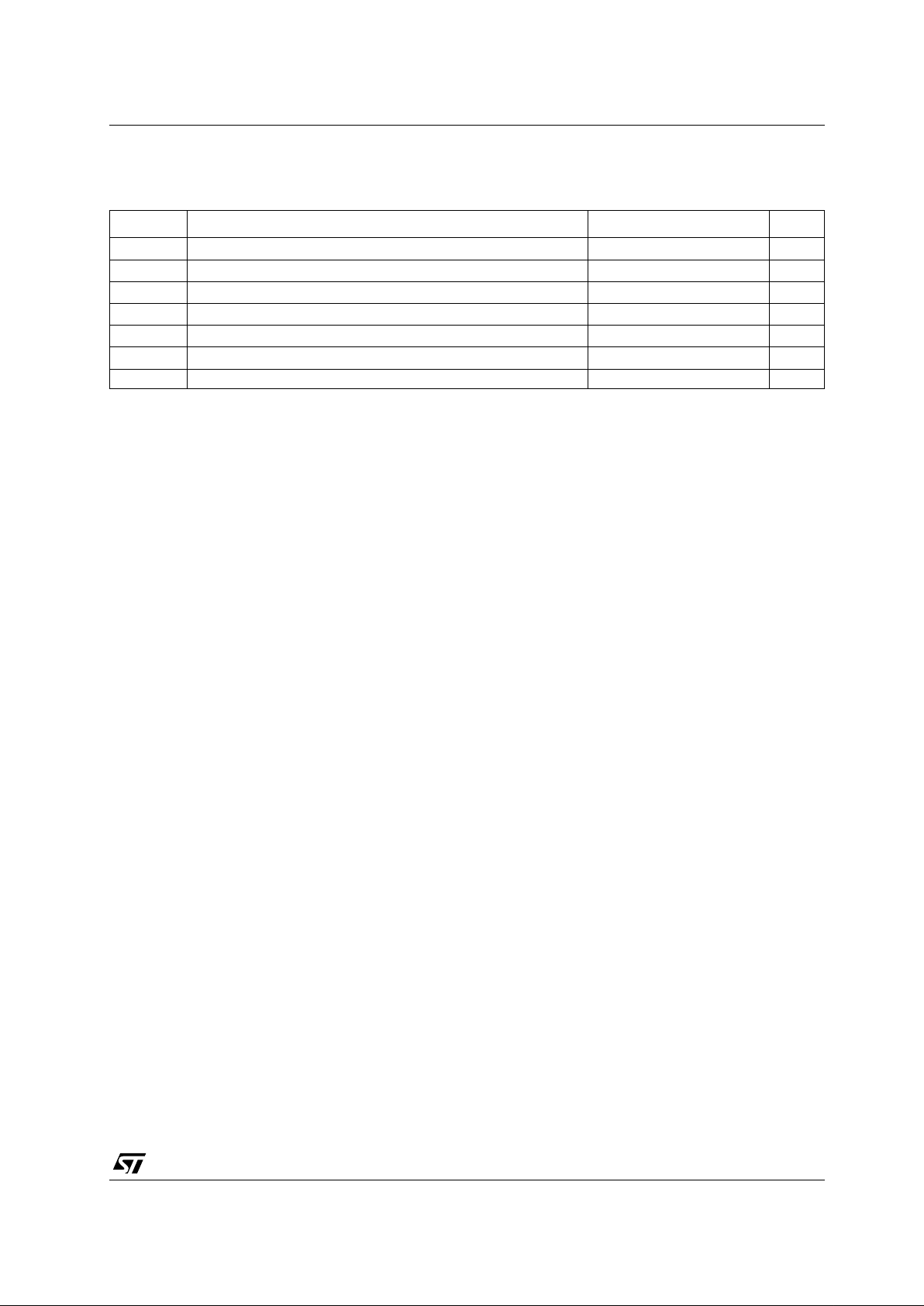

DINAMIC SWITCHING CHARACTERISTICS

1) Worst c ase package

2) Max number of output defined as ( n). Data input s are driven 0V to 3.3V, (n-1) outputs swit ching and one output at GND

3) Max number of data inputs (n) switching. (n -1) switching 0V to 3.3V. Inputs und er test switc hi ng: 3V to threshold (V

ILD

). 0V to threshold

(V

IHD

) f = 1MHz

Symbol Parameter

Test Condition Value

Unit

V

CCA

(V)

V

CCB

(V)

T

A

= 25 °C

-40 to 85 °C -55 to 125°C

Min. Typ. Max. Min. Max. Min. Max.

V

OLPA

Dynamic Low

Level Quiet

Output (note 1, 2)

3.3 5.5 1.0 1.5

V

3.3 5.5 -1.2 -0.6

V

OLPB

Dynamic Low

Level Quiet

Output (note 1, 2)

3.3 5.5 0.8 1.2

V

3.3 5.5 -0.8 -0.5

V

IHDA

Dynamic High

Voltage Input

(note 1, 3)

3.3 5.5 2 V

V

ILDA

Dynamic Low

Voltage Input

(note 1, 3)

3.3 5.5 0.8 V

V

IHDB

Dynamic High

Voltage Input

(note 1, 3)

3.3 5.5 2 V

V

ILDB

Dynamic Low

Voltage Input

(note 1, 3)

3.3 5.5 0.8 V

Page 7

74LVXC3245

7/12

AC ELECTRICAL CHARACTERISTICS (CL = 50pF, Input tr = tf = 3ns)

1) Skew is defined as the absolute value of the difference between the actual propagation delay for any two outputs of the same device switching in the same direction, either H IGH or LOW (t

OSLH

= | t

PLHm

- t

PLHn

|, t

OSHL

= | t

PHLm

- t

PHLn

|

2) Param eter guaran teed by design

3) Typical values ref erred at V

CCA

= 3.3V, V

CCB

= 5.0V or V

CCA

= 3.3V, V

CCB

= 3.3V

(*) Volt age Range is 3.0V ± 0.3

(**) Voltage Range is 5.0V ± 0.5

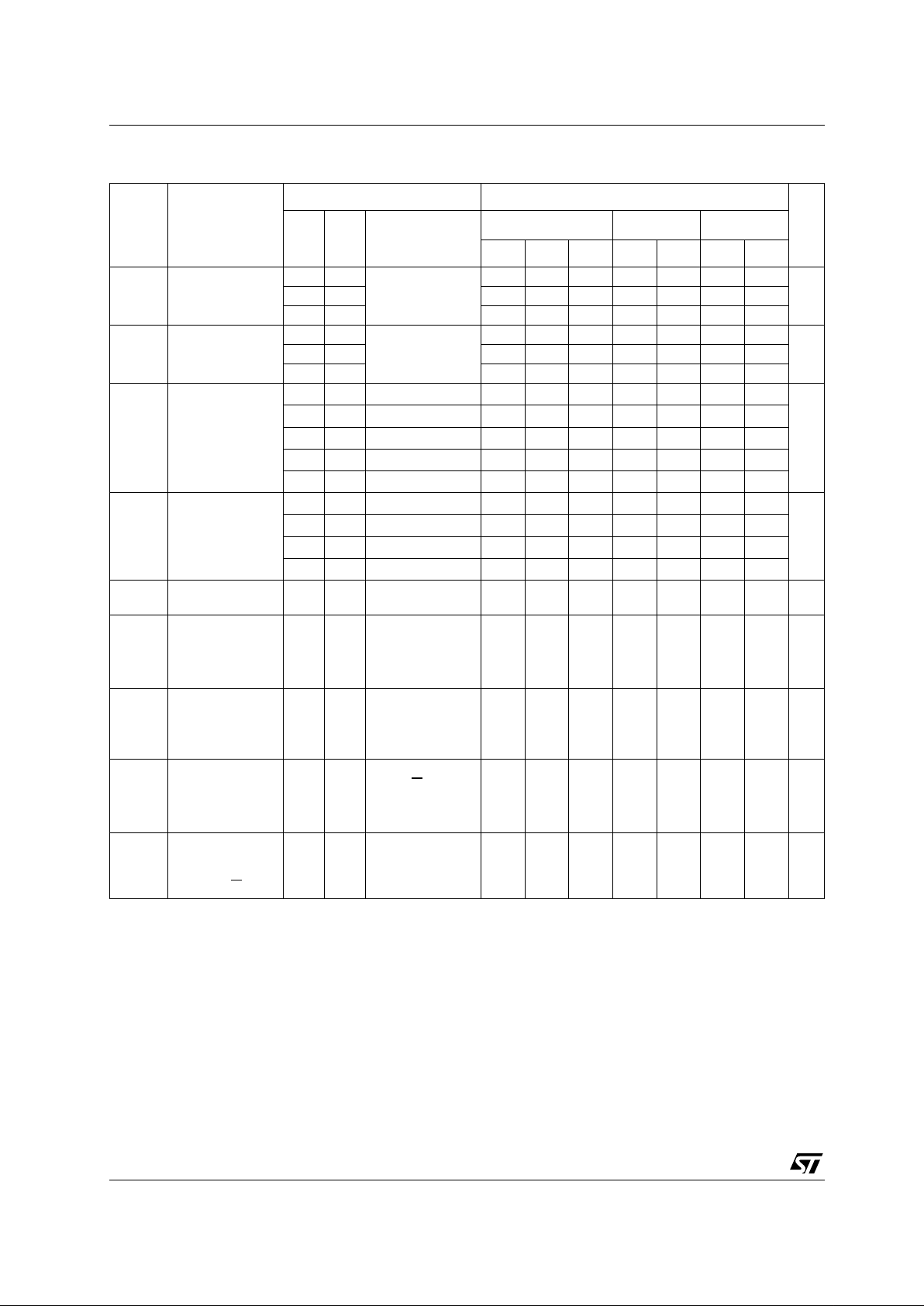

Symbol Parameter

Test Condition

Value

(3)

Unit

V

CCB

(V)

T

A

= 25°C

-40 to 85°C -55 to 125°C

Min. Typ. Max. Min. Max. Min. Max.

t

PLH

Propagation Delay

Time (An to Bn)

3.0(*) 1.0 5.5 8.5 1.0 9.0 1.0 9.5

ns

5.0(**) 1.0 4.8 8.0 1.0 8.5 1.0 9.

t

PHL

Propagation Delay

Time (An to Bn)

3.0(*) 1.0 5.2 8.0 1.0 8.5 1.0 9.0

5.0(**) 1.0 3.9 6.5 1.0 7.0 1.0 7.5

t

PZL

Output Enable

Time (G

to Bn)

3.0(*) 1.0 6.0 9.0 1.0 9.5 1.0 9.5

ns

5.0(**) 1.0 4.7 8.0 1.0 8.5 1.0 8.5

t

PZH

Output Enable

Time (G

to Bn)

3.0(*) 1.0 6.1 9.5 1.0 10.0 1.0 10.5

5.0(**) 1.0 4.8 8.5 1.0 9.0 1.0 9.5

t

PLZ

Output Disable

Time (G

to Bn)

3.0(*) 1.0 6.3 9.5 1.0 10.0 1.0 10.5

ns

5.0(**) 1.0 4.0 8.0 1.0 8.5 1.0 8.5

t

PHZ

Output Disable

Time (G

to Bn)

3.0(*) 1.0 4.5 8.0 1.0 8.5 1.0 8.5

5.0(**)

1.0 3.8 7.5 1.0 8.0 1.0 8.5

t

PLH

Propagation Delay

Time (Bn to An)

3.0(*) 1.0 4.4 7.0 1.0 7.5 1.0 7.5

ns

5.0(**) 1.0 3.8 6.5 1.0 7.0 1.0 7.5

t

PHL

Propagation Delay

Time (Bn to An)

3.0(*) 1.0 5.1 7.5 1.0 8.0 1.0 8.5

5.0(**) 1.0 4.3 7.5 1.0 8.0 1.0 8.5

t

PZL

Output Enable

Time (G

to An)

3.0(*) 1.0 6.4 10.0 1.0 10.5 1.0 10.5

ns

5.0(**) 1.0 5.9 9.5 1.0 10.0 1.0 10.5

t

PZH

Output Enable

Time (G

to An)

3.0(*) 1.0 5.8 9.0 1.0 9.5 1.0 9.5

5.0(**) 1.0 5.4 9.0 1.0 9.5 1.0 9.5

t

PLZ

Output Disable

Time (G

to An)

3.0(*) 1.0 5.2 9.5 1.0 10.0 1.0 10.5

ns

5.0(**) 1.0 4.6 9.5 1.0 10.0 1.0 10.5

t

PHZ

Output Disable

Time (G

to An)

3.0(*) 1.0 3.4 6.5 1.0 7.0 1.0 7.5

5.0(**) 1.0 3.1 6.5 1.0 7.0 1.0 7.5

t

OSLH

t

OSHL

Output To Output

Skew Time (note1,

2)

3.0(*) 0.5 1.0 1.5 1.5

ns

5.0(**) 0.5 1.0 1.5 1.5

Page 8

74LVXC3245

8/12

CAPACITIVE CHARACTERISTICS

1) CPD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without

load. (R efer to Test Ci rcuit). Average curre nt can be obta i ned by the following equ ation. I

CC(opr)

= CPD x VCC x fIN + ICC/8 (per circuit)

TEST CIRCUIT

CL = 50pF or equivalent (incl udes jig and p robe capacit ance)

R

L

= R1 = 500Ω or equivalent

R

T

= Z

OUT

of pulse generator (typically 50Ω)

Symbol Parameter

Test Condition Value

Unit

V

CCA

(V)

V

CCB

(V)

T

A

= 25 °C

-40 to 85 °C -55 to 125°C

Min. Typ. Max. Min. Max. Min. Max.

C

INA

Input

Capacitance

open open 4.5 10 10 10 V

C

I/O

Input/Output

Capacitance

3.3 5.0 10 V

C

PD

Dynamic Low

Level Quiet

Output (note 1)

A to B

3.3 5.0 55 V

C

PD

Dynamic Low

Level Quiet

Output (note 1)

B to A

3.3 5.0 40 V

TEST SWITCH

t

PLH

, t

PHL

Open

t

PZLH

, t

PLZ

2V

CC

t

PZH

, t

PHZ

Open

Page 9

74LVXC3245

9/12

WAVEFORM 1: PROPAGATION DELAYS (f=1MHz; 50% duty cycle)

WAVEFORM 2: OUTPUT ENABLE AND DISABLE TIME (f=1MHz; 50% duty cycle)

Page 10

74LVXC3245

10/12

DIM.

mm. inch

MIN. TYP MAX. MIN. TYP. MAX.

A 2.65 0.104

a1 0.1 0.2 0.004 0.008

a2 2.45 0.096

b 0.35 0.49 0.014 0.019

b1 0.23 0.32 0.009 0.012

C 0.5 0.020

c1 45° (typ.)

D 15.20 15.60 0.598 0.614

E 10.00 10.65 0.393 0.419

e 1.27 0.050

e3 13.97 0.550

F 7.40 7.60 0.291 0.300

L 0.50 1.27 0.020 0.050

S8° (max.)

SO-24 MECHANICAL DATA

PO13T

F

C

L

E

a1

b1

A

e

D

e3

b

24 13

112

c1

s

a2

Page 11

74LVXC3245

11/12

DIM.

mm. inch

MIN. TYP MAX. MIN. TYP. MAX.

A 1.1 0.043

A1 0.05 0.15 0.002 0.006

A2 0.9 0.035

b 0.19 0.30 0.0075 0.0118

c 0.09 0.20 0.0035 0.0079

D 7.7 7.9 0.303 0.311

E 6.25 6.5 0.246 0.256

E1 4.3 4.5 0.169 0.177

e 0.65 BSC 0.0256 BSC

K0° 8°0° 8°

L 0.50 0.70 0.020 0.028

TSSOP24 MECHANICAL DATA

c

E

b

A2

A

E1

D

1

PIN 1 IDENTIFICATION

A1

L

K

e

7047476A

Page 12

74LVXC3245

12/12

Information furnished is bel ieved to be accurate and reliable. However, STMicroe lectronics assumes no responsibility for the

consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from

its use. No li cense is granted by imp lica tion or otherwise under a ny patent or patent rig hts of STMicroelectronics. Sp ec ificat ions

mentioned in this publication ar e subject to change without notice. This publication supersedes and replaces all information

previously supplied. S TMicroelectronics products are not authorized for use as critica l components in life suppo rt devices or

systems without express written approval of STMicroelectronics.

© The ST logo is a registered trademark of STMicroelectronics

© 2001 STM icroelectronics - Printed in Italy - All Rights Reserv ed

STMicr o el ectronics G ROU P OF COMPANIES

Australi a - Brazil - Chi na - Finland - F rance - Germ any - Hong Kon g - India - Italy - Japan - Malaysia - Malta - Mo rocco

Singapo re - Spain - Sweden - Swit zerland - Uni ted Kingdom

© http://www.st.com

Loading...

Loading...