Datasheet 74ABT16541CSSCX, 74ABT16541CSSC, 74ABT16541CMTDX, 74ABT16541CMTD Datasheet (Fairchild Semiconductor)

Page 1

© 1999 Fairchild Semiconductor Corporation DS012149 www.fairchildsemi.com

July 1996

Revised November 1999

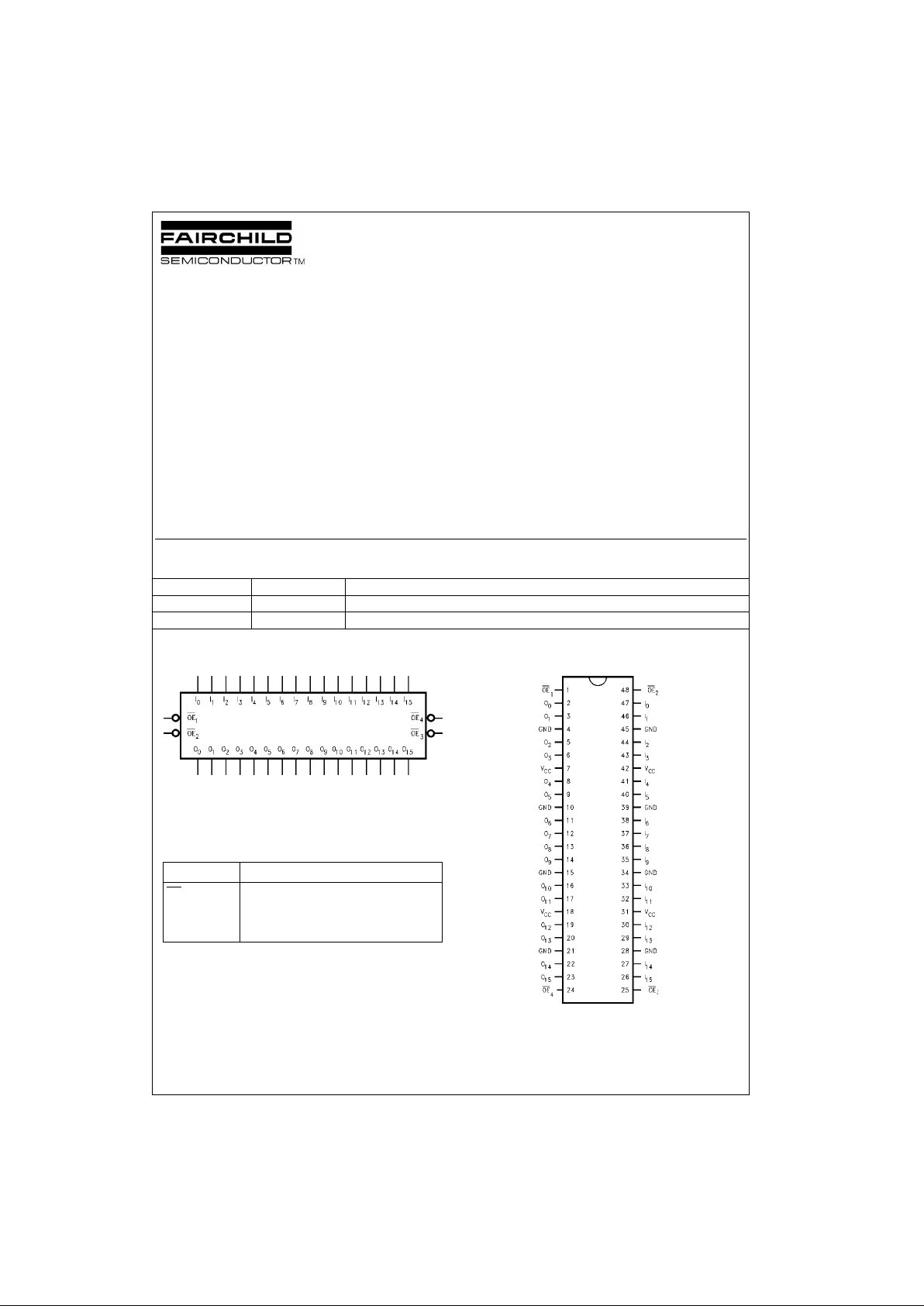

74ABT16541 16-Bit Buffer/Line Driver with 3-STATE Outputs

74ABT16541

16-Bit Buffer/Line Driver with 3-STATE Outputs

General Description

The ABT16541 contai ns sixteen n on-invertin g buffers with

3-STATE ou tputs designed to be employed as a memo ry

and address driver, clock driver, or bus oriented transmitter/receiver. The device is byte controlled. Individual 3STATE contro l inputs can be shorted t ogether for 8-bit or

16-bit operation.

Features

■ Separate control logic for each nibble

■ 16-bit version of the ABT541

■ Outputs sink capability of 64 mA, source capability of

32 mA

■ Guaranteed simultaneous switching noise level and

dynamic threshold performan ce

■ Guarante ed latchup protection

■ High impedance glitch free bus loading during entire

power up and power down cycle

■ Non-destructive hot insertion capability

Ordering Code:

Device also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Logic Symbol

Pin Descriptions

Connection Diagram

Order Number Package Number Package Description

74ABT16541CSSC MS48A 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300” Wide

74ABT16541CMTD MTD48 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Pin Names Description

OE

n

Output Enable Inputs (Active Low)

I

0–I15

Inputs

O

0–O15

Outputs

Page 2

www.fairchildsemi.com 2

74ABT16541

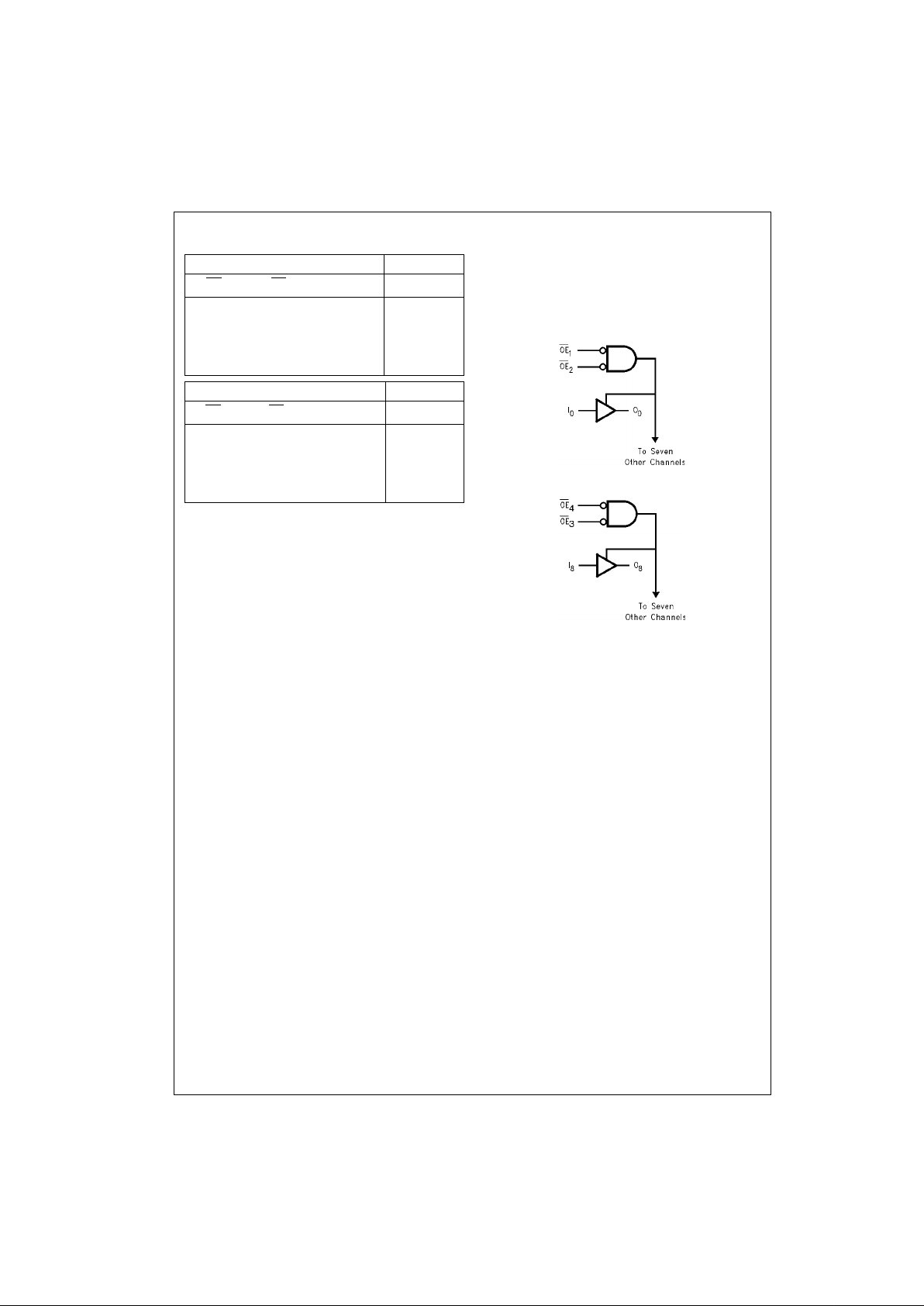

Truth Tables

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

Functional Description

The ABT16541 contains sixtee n non-inverting buffers with

3-STATE outputs. The device is byte (8 bits) controlled with

each byte functioning identically, but independent of the

other. The control pins can be shorted tog ether to obtain

full 16-bit operation.

Logic Diagrams

Inputs Outputs

OE

1

OE

2

I0–I

7

O0–O

7

LL L L

LLH H

HX X Z

XH X Z

Inputs Outputs

OE

4

OE

3

I8–I

15

O8–O

15

LL L L

LL H H

HX X Z

XH X Z

Page 3

3 www.fairchildsemi.com

74ABT16541

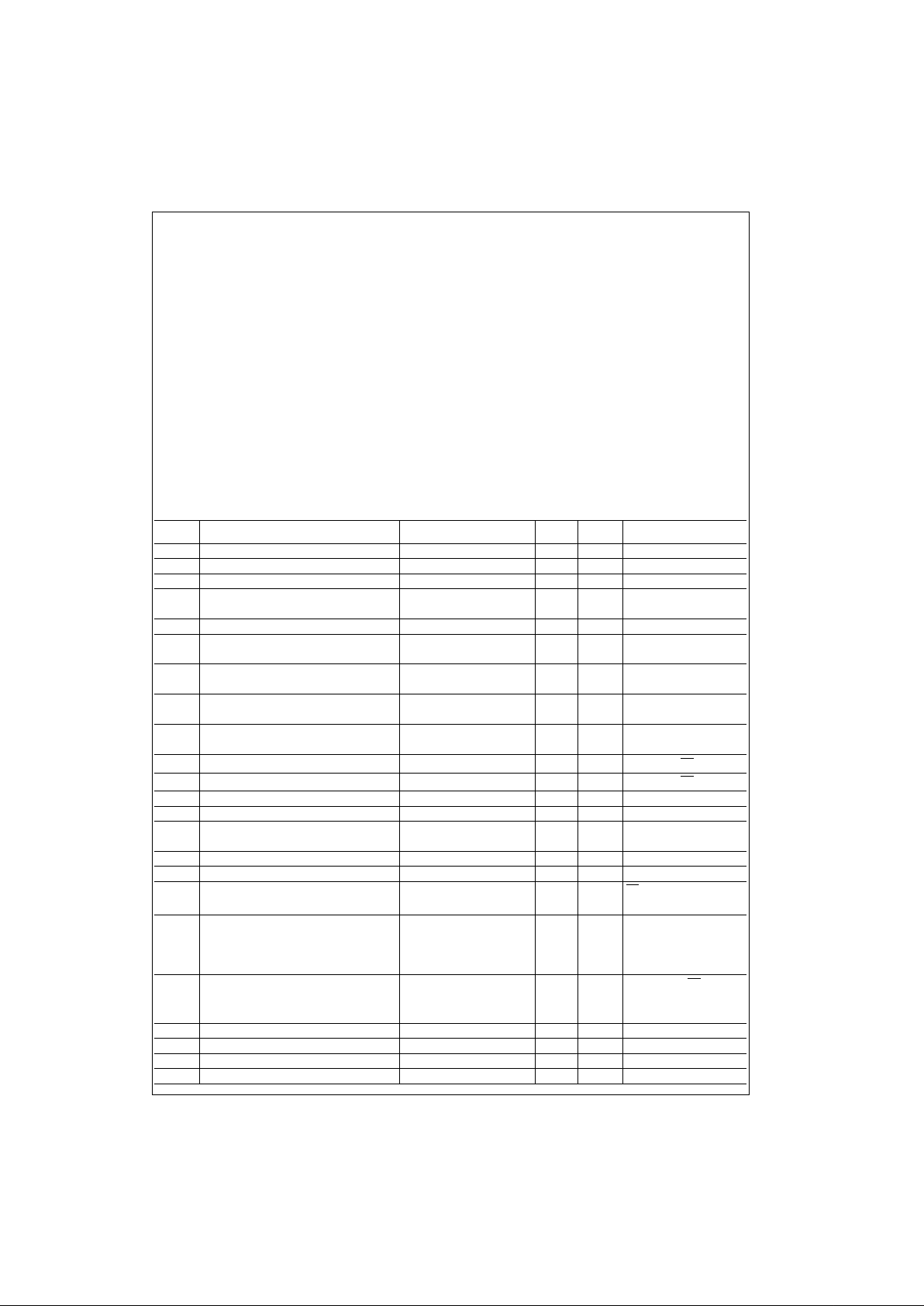

Absolute Maximum Ratings(Note 1) Recommended Operating

Conditions

Note 1: Absolute maximum ratings are values beyond which the device

may be damaged or have its useful life impaired . Functional operation

under these conditions is not implied.

Note 2: Either voltage lim it or c urrent limit is sufficient to pro te c t in puts.

DC Electrical Characteristics

Storage Temperature −65°C to +150°C

Ambient Temperature under Bias −55°C to +125°C

Junction Temperature under Bias −55°C to +150°C

V

CC

Pin Potential to Ground Pin −0.5V to +7.0V

Input Voltage (Note 2) −0.5V to +7.0V

Input Current (Note 2) −30 mA to +5.0 mA

Voltage Applied to Any Output

in the Disabled or

Power-Off State −0.5V to 5.5V

in the HIGH State −0.5V to V

CC

Current Applied to Output

in LOW State (Max) twice the rated I

OL

(mA)

DC Latchup Source Current −500 mA

Over Voltage Latchup (I/O) 10V

Free Air Ambient Temperature −40°C to +85°C

Supply Voltage +4.5V to +5.5V

Minimum Input Edge Rate (∆V/∆t)

Data Input 50 mV/ns

Enable Input 20 mV/ns

Symbol Parameter Min Typ Max Units

V

CC

Conditions

V

IH

Input HIGH Voltage 2.0 V Recognized HIGH Signal

V

IL

Input LOW Voltage 0.8 V Recognized LOW Signal

V

CD

Input Clamp Diode Voltage −1.2 V Min IIN = −18 mA

V

OH

Output HIGH 2.5 V Min IOH = −3 mA

Voltage 2.0 V Min IOH = −32 mA

V

OL

Output LOW Voltage 0.55 V Min IOL = 64 mA

I

IH

Input HIGH Current 1

µAMax

VIN = 2.7V (Note 3)

1V

IN

= V

CC

I

BVI

Input HIGH Current 7

µAMax

VIN = 7.0V

Breakdown Test

I

IL

Input LOW Current −1

µAMax

VIN = 0.5V (Note 3)

−1V

IN

= 0.0V

V

ID

Input Leakage Test 4.75 V 0.0 IID = 1.9 µA

All Other Pins Grounded

I

OZH

Output Leakage Current 10 µA0–5.5V

V

OUT

= 2.7V; OEn = 2.0V

I

OZL

Output Leakage Current −10 µA0–5.5V

V

OUT

= 0.5V; OEn = 2.0V

I

OS

Output Short-Circuit Current −100 −275 mA Max V

OUT

= 0.0V

I

CEX

Output HIGH Leakage Current 50 µAMaxV

OUT

= V

CC

I

ZZ

Bus Drainage Test 100 µA0.0V

OUT

= 5.5V

All Other Pins GND

I

CCH

Power Supply Current 100 µA Max All Outputs HIGH

I

CCL

Power Supply Current 60 mA Max All Outputs LOW

I

CCZ

Power Supply Current

100 µAMax

OEn = V

CC

All Others at VCC or GND

I

CCT

Additional ICC/Input Outputs Enabled 2.5 mA VI = VCC − 2.1V

Outputs 3-STATE 2.5 mA Max Enable Input VI = VCC − 2.1V

Outputs 3-STATE 50 µA Data Input VI = VCC − 2.1V

All Others at VCC or GND

I

CCD

Dynamic I

CC

No Load

mA/

Outputs Open, OEn = GND

(Note 3) 0.1 MHz Max One Bit Toggling,

50% Duty Cycle

V

OLP

Quiet Output Maximum Dynamic V

OL

0.4 0.7 V 5.0 TA = 25°C (Note 4)

V

OLV

Quiet Output Minimum Dynamic V

OL

−1.3 −1.0 V 5.0 TA = 25°C (Note 4)

V

OHV

Minimum HIGH Level Dynamic Output Voltage 2.7 3.0 V 5.0 TA = 25°C (Note 6)

V

IHD

Minimum HIGH Level Dynamic Input Voltage 2.0 1.4 V 5.0 TA = 25°C (Note 5)

Page 4

www.fairchildsemi.com 4

74ABT16541

DC Electrical Characteristics (Continued)

Note 3: Guaranteed but not tested.

Note 4: Max number of outputs defined as (n). n-1 data inputs are driven 0V to 3V. One output at LOW. Guaranteed, but not tested.

Note 5: Max number of data inputs (n) switching. n-1 inputs switching 0V to 3V. Input-under-test switching: 3V to threshold (V

ILD

), 0V to threshold (V

IHD

).

Guaranteed, but not tested.

Note 6: Max number of output s d ef ined as (n). n − 1 data inputs are driven 0V to 3V. One output HIGH. Guaranteed, but not tested.

AC Electrical Characteristics

Extended AC Electrical Characteristics

Note 7: This specification is gu aranteed but not tested . The limits apply to propagation delays for all paths described switching in ph ase

(i.e., all LOW-to-HIGH, HIGH-to-LOW, etc.).

Note 8: This specification is guaranteed but not tested. The limits represent propagation delay with 250 pF load capacitors in place of the 50 pF load ca pac -

itors in the standard AC load. This specifica ti on pertains to single output switching only.

Note 9: This specification is gu aranteed but not tested . The limits represent propagation delays for all pa t hs des c ribed switching in phase

(i.e., all LOW-to-HIGH, HIGH-to-LOW, etc.) with 250 pF load capacitors in place of the 50 pF lo ad capacitors in the standard AC load.

Note 10: The 3-STATE delay times are dominated by the RC network (500Ω, 250 pF) on the output and have been ex c luded from the datasheet.

Symbol Parameter Min Typ Max Units

V

CC

Conditions

V

ILD

Maximum LOW Level Dynamic Input Voltage 1.2 0.8 V 5.0 TA = 25°C (Note 5)

Symbol Parameter

TA=+25°CT

A

= −40°C to +85°C

Units

V

CC

=+5V VCC = 4.5V–5.5V

C

L

= 50 pF CL = 50 pF

Min Typ Max Min Max

t

PLH

Propagation 1.0 2.3 3.4 1.0 3.4

ns

t

PHL

Delay Data to Outputs 1.0 2.7 3.9 1.0 3.9

t

PZH

Output Enable 1.5 3.5 5.2 1.5 5.2

ns

t

PZL

Time 1.5 3.5 6.0 1.5 6.0

t

PHZ

Output Disable 1.0 4.2 5.1 1.0 5.1

ns

t

PLZ

Time 1.0 3.2 5.1 1.0 5.1

Symbol Parameter

−40°C to +85°C

TA = −40°C to +85°CTA = −40°C to +85°C

Units

V

CC

= 4.5V–5.5V VCC = 4.5V–5.5V VCC = 4.5V–5.5V

C

L

= 50 pF CL = 250 pF CL = 250 pF

16 Outputs Switching 1 Output Switching 16 Outputs Switching

(Note 7) (Note 8) (Note 9)

Min Typ Max Min Max Min Max

f

TOGGLE

Maximum Toggle Frequency 100 MHz

t

PLH

Propagation Delay 1.5 5.0 1.5 6.0 2.5 8.0

ns

t

PHL

Data to Outputs 1.5 5.3 1.5 6.0 2.5 8.0

t

PZH

Output Enable 1.5 6.5 2.5 7.8 2.5 9.5

ns

t

PZL

Time 1.5 6.5 2.5 7.8 2.5 8.5

t

PHZ

Output Disable 1.0 6.7 (Note 10) (Note 10) ns

t

PLZ

Time 1.0 6.7

Page 5

5 www.fairchildsemi.com

74ABT16541

Skew

Note 11: This specification is guaranteed but not tested. The limits apply t o propagation delays for all paths described switc hing in phase

(i.e., all LOW-to-HIGH, HIGH-to -LOW, etc.)

Note 12: These specific ations gua ranteed b ut not tes ted. The limits repr esent propa gation de lays with 250 pF lo ad capacit ors in pla ce of the 50 pF load

capacitors in the standard AC load.

Note 13: Skew is def ined as the absolu te valu e of the differ ence be tween the actu al propag ation de lays f or any tw o separ ate outpu ts of the sam e devi ce.

The specification appli es t o an y ou tput s sw itchi ng HIGH -to -LO W (t

OSHL

), LOW-to-HIGH (t

OSLH

), or any combination switching LOW-to-HIGH and/or HIGH-

to-LOW (t

OST

). The specification is guaranteed but not test ed.

Note 14: This describ es th e d ifferenc e b etw een t he del ay o f t he LO W-to -HIGH an d the HIGH -to -LOW tra nsitio n on t he s ame p in. It is mea sure d across all

the outputs (drivers) on t he same chip, the worst (la rgest delta) number is the guaranteed specificat ion. This specification is guaranteed but not tested.

Note 15: Propagation delay variation for a given set of conditions (i.e., temperature and V

CC

) from device to device. This specification is guaranteed but not

tested.

Capacitance

Note 16: C

OUT

is measured at frequency f = 1 MHz; per MIL STD -883, Method 3012.

Symbol Parameter

TA = −40°C to +85°CT

A

= −40°C to +85°C

Units

V

CC

= 4.5V–5.5V VCC = 4.5V–5.5V

C

L

= 50 pF CL = 250 pF

16 Outputs Switching 16 Outputs Switching

(Note 11) (Note 12)

Max Max

t

OSHL

Pin to Pin Skew

1.0 1.5 ns

(Note 13) HL Transitions

t

OSLH

Pin to Pin Skew

1.0 1.5 ns

(Note 13) LH Transitions

t

PS

Duty Cycle

1.5 1.5 ns

(Note 14) LH–HL Skew

t

OST

Pin to Pin Skew

1.7 2.0 ns

(Note 13) LH/HL Transitions

t

PV

Device to Device Skew

2.0 2.5 ns

(Note 15) LH/HL Transitions

Symbol Parameter Typ Units

Conditions

T

A

= 25°C

C

IN

Input Capacitance 5.0 pF VCC = 5.0V

C

OUT

(Note 16) Output Capacitance 9.0 pF VCC = 5.0V

Page 6

www.fairchildsemi.com 6

74ABT16541

AC Loading

* Includes jig and pro be capacitance

FIGURE 1. Standard AC Test Load

FIGURE 2. Test Input Pulse Requirements

FIGURE 3. Test Input Signal Requirements

AC Waveforms

FIGURE 4. Propagation Delay Waveforms for Inverting

and Non-Inverting Functions

FIGURE 5. Propagation Delay, Pulse Width Waveforms

FIGURE 6. 3-STATE Output HIGH and LOW Enable and

Disable Times

FIGURE 7. Setup Time, Hold Time and Recovery Time

Waveforms

Amplitude Rep Rate t

W

t

r

t

f

3.0V 1 MHz 500 ns 2.5 ns 2.5 ns

Page 7

7 www.fairchildsemi.com

74ABT16541

Physical Dimensions inches (millimeters) unless otherwise noted

48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300” Wi d e

Package Num b er MS48A

Page 8

www.fairchildsemi.com 8

74ABT16541 16-Bit Buffer/Line Driver with 3-STATE Outputs

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Package Number MTD48

Fairchild does not assume any responsibility for use of any circuitr y described, no circuit patent licenses are implied and

Fairchild reserves the right at any time without notice to change said circuitry and specifications.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or syste ms

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be reasonably expected to result in a significant inju ry to the

user.

2. A critical component in any compon ent of a lif e supp ort

device or system whose failure t o perform can be reasonably expected to ca use the failure of the life supp ort

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

Loading...

Loading...