Page 1

73S1210F

Self-Contained Smart Card Reader

with PINpad and Power Management

Simplifying System Integration™

DATA SHEET

May 2009

GENERAL DESCRIPTION

The 73S1210F is a versatile and economical CMOS

System-on-Chip device intended for smart card reader

applications. The circuit is built around an 80515 highperformance core; it features primarily an ISO-7816 / EMV

interface and a generic asynchronous serial interface.

Delivered with turnkey Teridian embedded firmware, it

forms a ready-to-use smart card reader solution that can be

seamlessly incorporated into any microprocessor-based

system where a serial line is available.

The solution is scalable, thanks to a built-in I

that allows to drive external electrical smart card interfaces

such as Teridian 73S8010 ICs. This makes the so l ution

immediately able to support multi-card slots or multi-SAM

architectures.

In addition, the 73S1210 features a 5x6 PINpad interface, 8

user I/Os, multiple interrupt options and an analog volt age

input (for DC voltage monitoring such as battery level

detection) that make it suitable for low-cost PINpad reader

devices.

The 80515 CPU core instruction set is compatible with the

industry standard 8051, while offering one clock-cycle per

instruction processing power (most instructions). Wit h a

CPU clock running up to 24MHz, it results in up to 24MIPS

available that meets the requirements of various encryption

needs such as AES, DES / 3-DES and even RSA (for PIN

encryption for instance).

The circuit requires a single 6MHz to 12MHz crystal.

The respective 73S1210F embedded memories are 32KB

Flash program memory, 2KB user XRAM memory, and

256B IRAM memory. Dedicated FIFOs for the IS O 7816

UART are independent from the user XRAM and IRAM.

Alternatively to the turnkey firmware offered by Teridian,

customers can develop their own embedded firmware

directly within their application or using Teridian 73S1210F

Evaluation Board through a JTAG-like interface .

The chip incorporates an inductor-based DC-DC convert er

that generates all the necessary voltages to the various

73S1210F function blocks (smart card interface, digital

core, etc.) from any of two distinct power supply sources:

the +5V bus (V

4.0V to 6.5V). The chip automatically powers-up the DCDC converter with V

supply input if V

can support a wider power supply input range (2.7V to

6.5V), when using a single system supply source.

, 4.4 to 6.5V), or a main battery (V

BUS

if it is present, or uses V

BUS

is not present. Alternatively, the pin VPC

BUS

2

C interface

BAT

as the

BAT

,

In addition, the circuit features an ON/OF F mode which

operates directly with an ON/OFF system switch: Any

activity on the ON/OFF button is debounced internally

and controls the power generation circuit accordingly,

under the supervision of the firmware (OFF request /

OFF acknowledgement at firmware level). The OFF

mode can be alternatively initiated from the controller

(firmware action instead of ON/OFF switch).

In OFF mode, the circuit typically draws less than 1µA,

which makes it ideal for applications where battery life

must be maximized.

Embedded Flash memory is in-system programmable

and lockable by means of on-silicon fuses. This makes

the 73S1210F suitable for both development and

production phases.

Teridian Semiconductor Corporation offers with its

73S1210F a very comprehensive set of software

libraries for EMV. Refer to the 73S12xxF Sof tware

User’s Guide for a complete description of the

Application Programming Interface (API Libraries) and

related software modules.

A complete array of development and programming

tools, libraries and demonstration boards enable rapid

development and certification of readers that meet

most demanding smart card standards.

APPLICATIONS

• PINpad smart card readers:

o With serial connectivity

o Ideal for low-cost POS Terminals and Digital

Identification (Secure Login, Gov’t ID, ...)

• SIM Readers in Personal Wireless devices

• Payphones & Vending machines

• General purpose smart card readers

ADVANTAGES

• Reduced BOM

• Versatile power supply options

o 2.7V to 6.5V ranges

• Higher performance CPU core (up to 24MIPS)

• Built-in EMV/ISO slot, expandable to multi-slots

• Flexible power supply options

o On-chip DC-DC converter

o CMOS switches between supply inputs

• Sub-µA Power Down mode with ON/OFF switch

• Powerful In-Circuit Emulation and Programming

• A complete set of EMV4.1 / ISO7816 libraries

• Turnkey PC/SC firmware and host drivers

o Multiple OS supported

Rev. 1.4 © 2009 Teridian Semiconductor Corporation 1

Page 2

73S1210F Data Sheet DS_1210F_001

FEATURES

80515 Core:

• 1 clock cycle per instruction (most instructions)

• CPU clocked up to 24MHz

• 32KB Flash memory (lockable)

• 2kB XRAM (User Data Memory)

• 256 byte IRAM

• Hardware watchdog timer

Oscillators:

• Single low-cost 6MHz to 12MHz crystal

• An Internal PLL provides all the necessary clocks to

each block of the system

Interrupts:

• Standard 80C515 4-priority level structure

• 9 different sources of interrupt to the core

Power Down Modes:

• 2 standard 80C515 Power Down and IDLE modes

• Sub-µA OFF mode

• ON/OFF Main System Power Switch:

• Input for an SPST momentary switch to ground

Timers:

• (2) Standard 80C52 timers T0 and T1

• (1) 16-bit timer

Built-in ISO-7816 Card Interface:

• Linear regulator produces VCC for the card

(1.8V, 3V or 5V)

• Full compliance with EMV 4.1

• Activation/Deactivation sequencers

• Auxiliary I/O lines (C4 and C8 signals)

• 7kV ESD protection on all interface pins

Communication with Smart Cards:

• ISO 7816 UART 9600 to 115kbps for T=0, T=1

• (2) 2-Byte FIFOs for transmit and receive

• Configured to drive multiple external Teridian

73S8010x interfaces (for multi-SAM architectures)

Voltage Detection:

• Analog Input (detection range: 1.0V to 2.5V)

Communication Interfaces:

• Full-duplex serial interface (1200 to 115kbps

UART)

2

C Master Interface (400kbps)

• I

• Man-Machine Interface and I/Os:

• 6x5 Keyboard (hardware scanning, debouncing

and scrambling)

• (8) User I/Os

• Single programmable current output (LED)

• Operating Voltage:

• Single supply 2.7V to 6.5V operation (VPC)

• 5V supply (VBUS 4.4V to 5.5V) with or without

battery back up operation (VBAT 4.0V to 6.5V)

• Automated detection of voltage presence - Priority

on VBUS over VBAT

DC-DC Converter:

• Requires a single 10µH Inductor

• 3.3V / 20mA supply available for external circuits

Operating Temperature:

• -40°C to 85°C

Package:

• 68-pin QFN, 44 pin QFN

Turnkey Firmware:

• Compliant with PC/SC, ISO7816 and EMV4.1

specifications

• Features a Power Down mode accessible from the

host

• Supports Plug & Play over serial interface

®

• Windows

• Windows CE / Mobile driver available (*)

• Linux and other OS: Upon request

• Or for custom developments:

o A complete set of ISO-7816, EMV4.1 and

o Two-level Application Pr ogr amming Interface

XP driver available (*)

low-level libraries are available for T=0 / T=1

(ANSI C-language libraries)

(*) Contact Teridian Semiconductor for condit i ons and

availability.

2 Rev. 1.4

Page 3

DS_1210F_001 73S1210F Data Sheet

Table of Contents

1 Hardware Description ......................................................................................................................... 8

1.1

Pin Description ............................................................................................................................. 8

Hardware Overview ................................................................................................................... 11

1.2

80515 MPU Core ....................................................................................................................... 11

1.3

80515 Overview ............................................................................................................. 11

1.3.1

Memory Organization .................................................................................................... 11

1.3.2

Program Security ....................................................................................................................... 16

1.4

Special Function Registers (SFRs) ........................................................................................... 18

1.5

Internal Data Special Function Registers (SFRs) .......................................................... 18

1.5.1

IRAM Special Function Registers (Generic 80515 SFRs) ............................................ 19

1.5.2

External Data Special Function Registers (SFRs) ........................................................ 20

1.5.3

Instruction Set ............................................................................................................................ 22

1.6

Peripheral Descriptions .............................................................................................................. 22

1.7

Oscillator and Clock Generation .................................................................................... 22

1.7.1

Power Supply Management .......................................................................................... 25

1.7.2

Power ON/OFF .............................................................................................................. 26

1.7.3

Power Control Modes .................................................................................................... 27

1.7.4

Interrupts ........................................................................................................................ 33

1.7.5

UART ............................................................................................................................. 40

1.7.6

Timers and Counters ..................................................................................................... 45

1.7.7

WD Timer (Software Watchdog Timer) ......................................................................... 47

1.7.8

User (USR) Ports ........................................................................................................... 49

1.7.9

Analog Voltage Comparator .......................................................................................... 51

1.7.10

LED Driver ..................................................................................................................... 53

1.7.11

1.7.12

1.7.13

1.7.14

1.7.15

1.7.16

Typical Application Schematic ...................................................................................................... 104

2

2

I

Keypad Interface ............................................................................................................ 61

Emulator Port ................................................................................................................. 68

Smart Card Interface Function ...................................................................................... 69

VDD Fault Detect Function .......................................................................................... 103

C Master Interface ....................................................................................................... 54

3

Electrical Specification ................................................................................................................... 105

3.1

Absolute Maximum Ratings ..................................................................................................... 105

Recommended Operating Conditions ..................................................................................... 105

3.2

Digital IO Characteristics ......................................................................................................... 106

3.3

Oscillator Interface Requirements ........................................................................................... 107

3.4

DC Characteristics: Analog Input ............................................................................................. 107

3.5

Smart Card Interface Requirements ........................................................................................ 108

3.6

DC Characteristics ................................................................................................................... 110

3.7

Current Fault Detection Circuits ............................................................................................... 111

3.8

Equivalent Circuits ......................................................................................................................... 112

4

5

Package Pin Designation ............................................................................................................... 120

5.1

68-pin QFN Pinout ................................................................................................................... 120

44-pin QFN Pinout ................................................................................................................... 121

5.2

Packaging Information ................................................................................................................... 122

6

6.1

68-Pin QFN Package Outline .................................................................................................. 122

44-Pin QFN Package Outline .................................................................................................. 123

6.2

Ordering Information ...................................................................................................................... 124

7

8

Related Documentation .................................................................................................................. 124

9

Contact Information ........................................................................................................................ 124

Revision History

Rev. 1.4 3

...................................................................................................................................... 125

Page 4

73S1210F Data Sheet DS_1210F_001

Figures

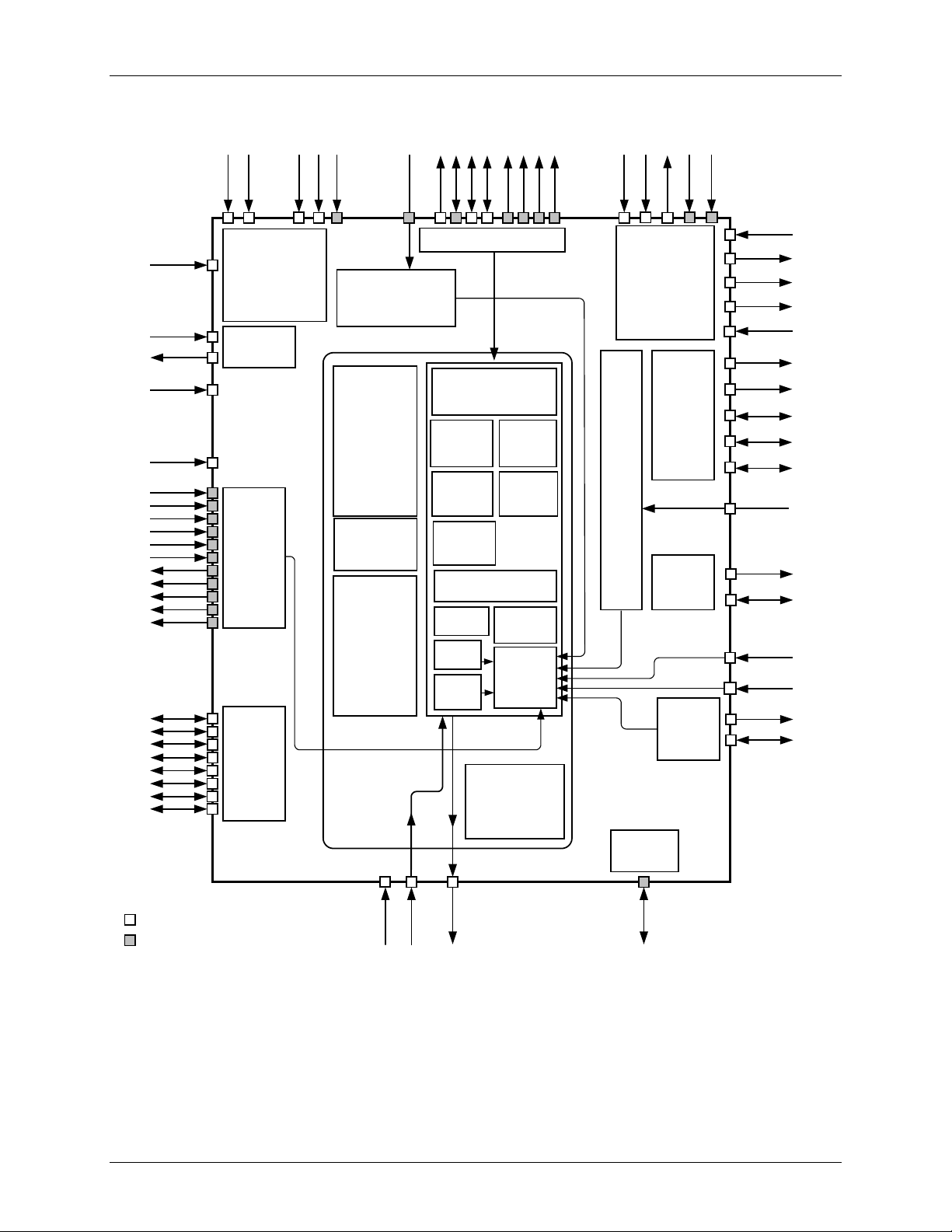

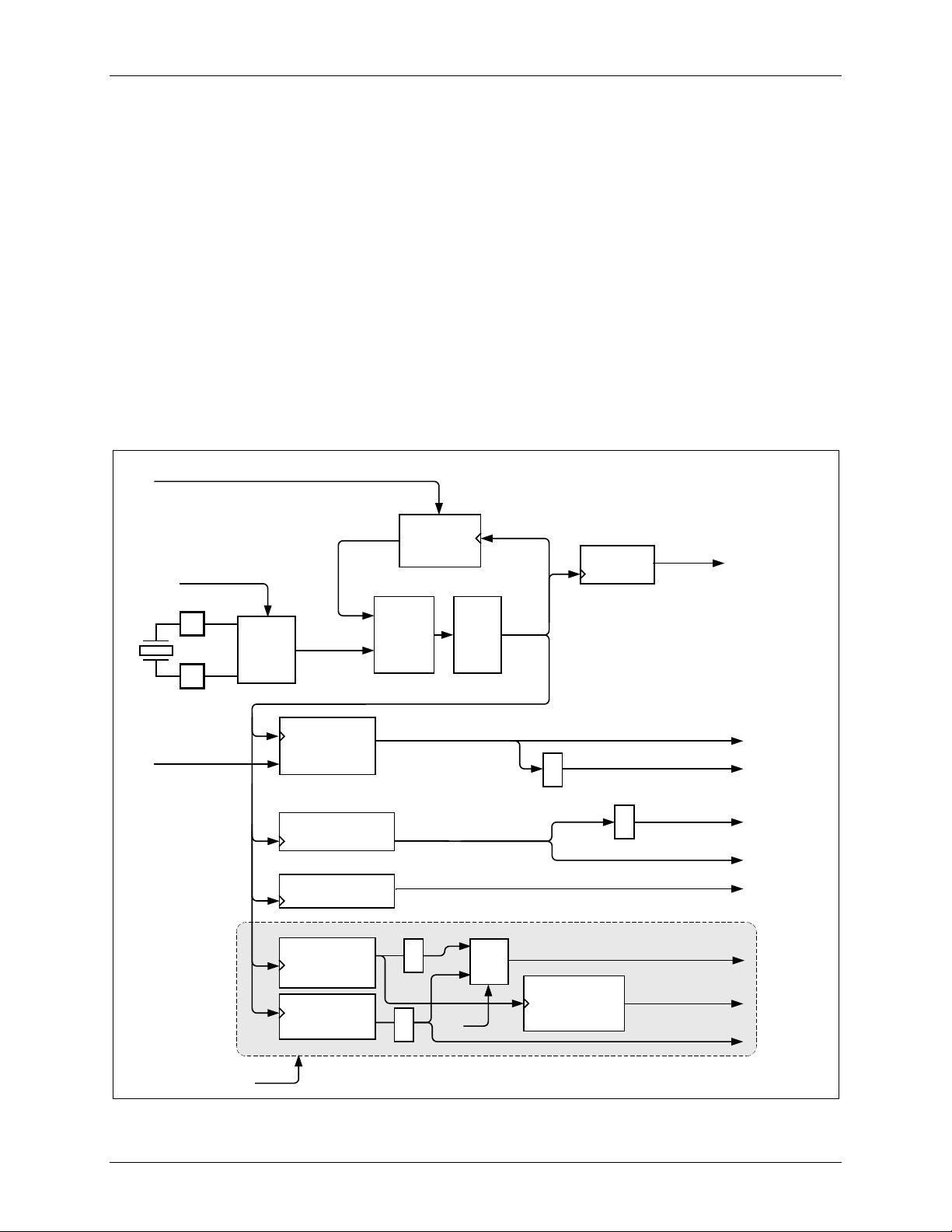

Figure 1: IC Functional Block Diagram ......................................................................................................... 7

Figure 2: Memory Map

Figure 3: Clock Generation and Control Circuits

Figure 4: Oscillator Circuit

Figure 5: Detailed Power Management Logic Block Diagram

Figure 6: Power Down Control

Figure 7: Detail of Power Down Interrupt Logic

Figure 8: Power Down Sequencing

Figure 9: External Interrupt Configuration

Figure 10: I

Figure 11: I

Figure 12: Simplified Keypad Block Diagram

Figure 13: Keypad Interface Flow Chart

Figure 14: Smart Card Interface Block Diagram

Figure 15: External Smart Card Interface Block Diagram

Figure 16: Asynchronous Activation Sequence Timing

Figure 17: Deactivation Sequence

Figure 18: Smart Card CLK and ETU Generation

Figure 19: Guard, Block, Wait and ATR Time Definitions

Figure 20: Synchronous Activation

Figure 21: Example of Sync Mode Operation: Generating/Reading ATR Signals

Figure 22: Creation of Synchronous Clock Start/Stop Mode Start Bit in S ync Mode

Figure 23: Creation of Synchronous Clock Start/Stop Mode Stop Bit in Sync Mode

Figure 24: Operation of 9-bit Mode in Sync Mode

Figure 25: 73S1210F Typical Application Schematic

Figure 26: 12 MHz Oscillator Circuit

Figure 27: 32KHz Oscillator Circuit

Figure 28: Digital I/O Circuit

Figure 29: Digital Output Circuit

Figure 30: Digital I/O with Pull Up Circuit

Figure 31: Digital I/O with Pull Down Circuit

Figure 32: Digital Input Circuit

Figure 33: OFF_REQ Interface Circuit

Figure 34: Keypad Row Circuit

Figure 35: Keypad Column Circuit

Figure 36: LED Circuit

Figure 37: Test and Security Pin Circuit

Figure 38: Analog Input Circuit

Figure 39: Smart Card Output Circuit

Figure 40: Smart Card I/O Circuit

Figure 41: PRES Input Circuit

Figure 42: PRESB Input Circuit

Figure 43: ON_OFF Input Circuit

Figure 44: 73S1210F 68 QFN Pinout

Figure 45: 73S1210F 44 QFN Pinout

Figure 46: 73S1210F 68 QFN Mechanical Drawing

Figure 47: 73S1210F 44 QFN Package Drawing

2

2

................................................................................................................................ 15

........................................................................................ 22

........................................................................................................................... 24

.................................................................... 25

.................................................................................................................... 27

.......................................................................................... 28

............................................................................................................ 29

................................................................................................... 33

C Write Mode Operation .......................................................................................................... 55

C Read Operation ................................................................................................................... 56

............................................................................................. 61

..................................................................................................... 63

......................................................................................... 69

.......................................................................... 70

.............................................................................. 73

.............................................................................................................. 73

...................................................................................... 74

.......................................................................... 75

............................................................................................................. 77

..................................... 77

................................. 78

................................. 78

...................................................................................... 79

............................................................................... 104

......................................................................................................... 112

........................................................................................................... 112

...................................................................................................................... 113

................................................................................................................ 113

.................................................................................................. 114

............................................................................................. 114

................................................................................................................... 115

..................................................................................................... 115

................................................................................................................. 115

............................................................................................................ 116

............................................................................................................................... 116

................................................................................................... 117

................................................................................................................. 117

....................................................................................................... 117

............................................................................................................. 118

................................................................................................................... 118

................................................................................................................ 118

.............................................................................................................. 119

....................................................................................................... 120

....................................................................................................... 121

................................................................................. 122

..................................................................................... 123

4 Rev. 1.4

Page 5

DS_1210F_001 73S1210F Data Sheet

Tables

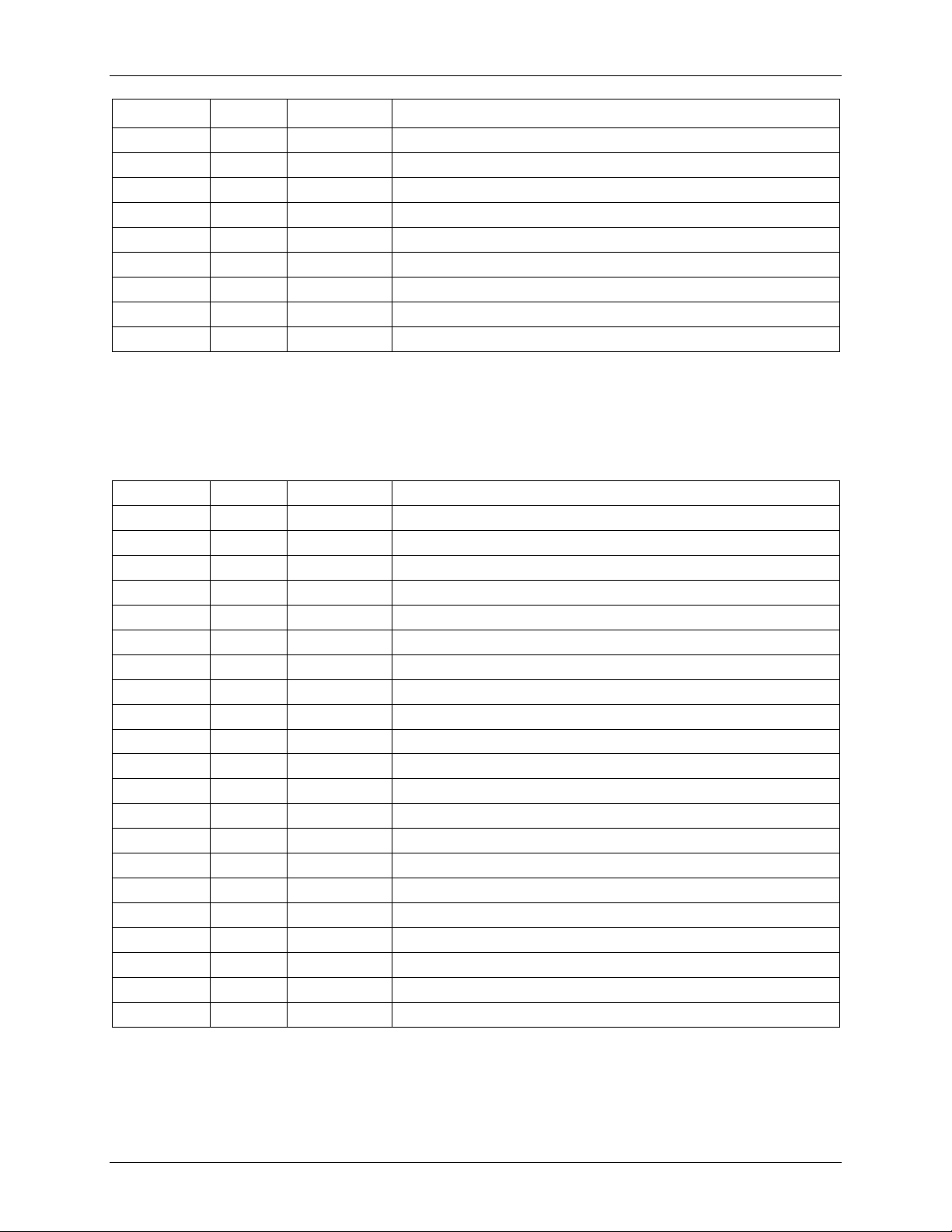

Table 1: 73S1210 Pinout Description ........................................................................................................... 8

Table 2: MPU Data Memory Map

Table 3: Flash Special Function Registers

Table 4: Internal Data Memory Map

Table 5: Program Security Registers

Table 6: IRAM Special Function Registers Locations

Table 7: IRAM Special Function Registers Reset Values

Table 8: XRAM Special Function Registers Reset Values

Table 9: PSW Register

Table 10: Port Registers

Table 11: Frequencies and Mcount Values for MCLK = 96MHz

Table 12: The MCLKCtl Register

Table 13: The TCON Register

Table 14: The INT5Ctl Register

Table 15: The MISCtl0 Register

Table 16: The MISCtl1 Register

Table 17: The MCLKCtl Register

Table 18: The PCON Register

Table 19: The IEN0 Register

Table 20: The IEN1 Register

Table 21: The IEN2 Register

Table 22: The TCON Register

Table 23: The T2CON Register

Table 24: The IRCON Register

Table 25: External MPU Interrupts

Table 26: Control Bits for External Interrupts

Table 27: Priority Level Groups

Table 28: The IP0 Register

Table 29: The IP1 Register

Table 30: Priority Levels

Table 31: Interrupt Polling Sequence

Table 32: Interrupt Vectors

Table 33: UART Modes

Table 34: Baud Rate Generation

Table 35: The PCON Register

Table 36: The BRCON Register

Table 37: The MISCtl0 Register

Table 38: The S0CON Register

Table 39: The S1CON Register

Table 40: The TMOD Register

Table 41: Timers/Counters Mode Description

Table 42: The TCON Register

Table 43: The IEN0 Register

Table 44: The IEN1 Register

Table 45: The IP0 Register

Table 46: The WDTREL Register

Table 47: Direction Registers and Internal Resources for DIO Pin Groups

Table 48: UDIR Control Bit

Table 49: Selectable Controls Using the UxIS Bits

Table 50: The USRIntCtl1 Register

Table 51: The USRIntCtl2 Register

Table 52: The USRIntCtl3 Register

Table 53: The USRIntCtl4 Register

Table 54: The ACOMP Register ................................................................................................................. 51

Table 55: The INT6Ctl Register

Table 56: The LEDCtl Register

Rev. 1.4 5

............................................................................................................... 11

................................................................................................. 13

........................................................................................................... 14

.......................................................................................................... 17

................................................................................ 18

.......................................................................... 19

......................................................................... 20

................................................................................................................................ 21

............................................................................................................................. 21

................................................................ 23

................................................................................................................ 23

.................................................................................................................... 24

.................................................................................................................. 30

.................................................................................................................. 30

.................................................................................................................. 31

................................................................................................................ 31

.................................................................................................................... 32

...................................................................................................................... 34

...................................................................................................................... 35

...................................................................................................................... 35

.................................................................................................................... 36

.................................................................................................................. 36

................................................................................................................... 37

.............................................................................................................. 37

.............................................................................................. 38

.................................................................................................................. 38

......................................................................................................................... 38

......................................................................................................................... 39

.............................................................................................................................. 39

.......................................................................................................... 39

......................................................................................................................... 39

.............................................................................................................................. 40

................................................................................................................ 40

.................................................................................................................... 41

................................................................................................................. 41

.................................................................................................................. 42

.................................................................................................................. 43

.................................................................................................................. 44

.................................................................................................................... 45

............................................................................................ 45

.................................................................................................................... 46

...................................................................................................................... 47

...................................................................................................................... 48

......................................................................................................................... 48

............................................................................................................... 48

............................................... 49

......................................................................................................................... 49

..................................................................................... 49

............................................................................................................ 50

............................................................................................................ 50

............................................................................................................ 50

............................................................................................................ 50

.................................................................................................................. 52

................................................................................................................... 53

Page 6

73S1210F Data Sheet DS_1210F_001

Table 57: The DAR Register ....................................................................................................................... 57

Table 58: The WDR Register

Table 59: The SWDR Register

Table 60: The RDR Register

Table 61: The SRDR Register

Table 62: The CSR Register

Table 63: The INT6Ctl Register

Table 64: The KCOL Register

Table 65: The KROW Register

Table 66: The KSCAN Register

Table 67: The KSTAT Register

Table 68: The KSIZE Register

Table 69: The KORDERL Register

Table 70: The KORDERH Register

Table 71: The INT5Ctl Register

Table 72: The SCSel Register

Table 73: The SCInt Register

Table 74: The SCIE Register

Table 75: The VccCtl Register

Table 76: The VccTmr Register

Table 77: The CRDCtl Register

Table 78: The STXCtl Register

Table 79: The STXData Register

Table 80: The SRXCtl Register

Table 81: The SRXData Register

Table 82: The SCCtl Register

Table 83: The SCECtl Register

Table 84: The SCDIR Register

Table 85: The SPrtcol Register

Table 86: The SCCLK Register

Table 87: The SCECLK Register

Table 88: The SParCtl Register

Table 89: The SByteCtl Register

Table 90: The FDReg Register

Table 91: The FDReg Bit Functions

Table 92: Divider Ratios Provided by the ETU Counter

Table 93: Divider Values for the ETU Clock

Table 94: The CRCMsB Register

Table 95: The BGT Register

Table 96: The EGT Register

Table 97: The BWTB0 Register

Table 98: The BWTB1 Register

Table 99: The BWTB2 Register

Table 100: The BWTB3 Register

Table 101: The CWTB0 Register

Table 102: The CWTB1 Register

Table 103: The ATRLsB Register

Table 104: The ATRMsB Register

Table 105: The STSTO Register

Table 106: The RLength Register

Table 107: Smart Card SFR Table

Table 108: The VDDFCtl Register

Table 109: Order Numbers and Packaging Marks

...................................................................................................................... 57

................................................................................................................... 58

....................................................................................................................... 58

.................................................................................................................... 59

....................................................................................................................... 59

.................................................................................................................. 60

..................................................................................................................... 64

................................................................................................................... 64

.................................................................................................................. 65

................................................................................................................... 65

.................................................................................................................... 66

............................................................................................................. 67

............................................................................................................ 67

.................................................................................................................. 68

.................................................................................................................... 80

..................................................................................................................... 81

...................................................................................................................... 82

.................................................................................................................... 83

.................................................................................................................. 84

.................................................................................................................. 85

................................................................................................................... 86

................................................................................................................ 87

................................................................................................................... 87

............................................................................................................... 88

..................................................................................................................... 89

................................................................................................................... 90

................................................................................................................... 91

................................................................................................................... 92

.................................................................................................................. 93

................................................................................................................ 93

.................................................................................................................. 94

................................................................................................................ 95

................................................................................................................... 96

............................................................................................................ 96

............................................................................. 96

............................................................................................... 97

............................................................................................................... 98

....................................................................................................................... 99

....................................................................................................................... 99

................................................................................................................ 100

................................................................................................................ 100

................................................................................................................ 100

.............................................................................................................. 100

.............................................................................................................. 100

.............................................................................................................. 100

............................................................................................................. 101

............................................................................................................ 101

.............................................................................................................. 101

............................................................................................................. 101

........................................................................................................... 102

............................................................................................................ 103

................................................................................... 124

6 Rev. 1.4

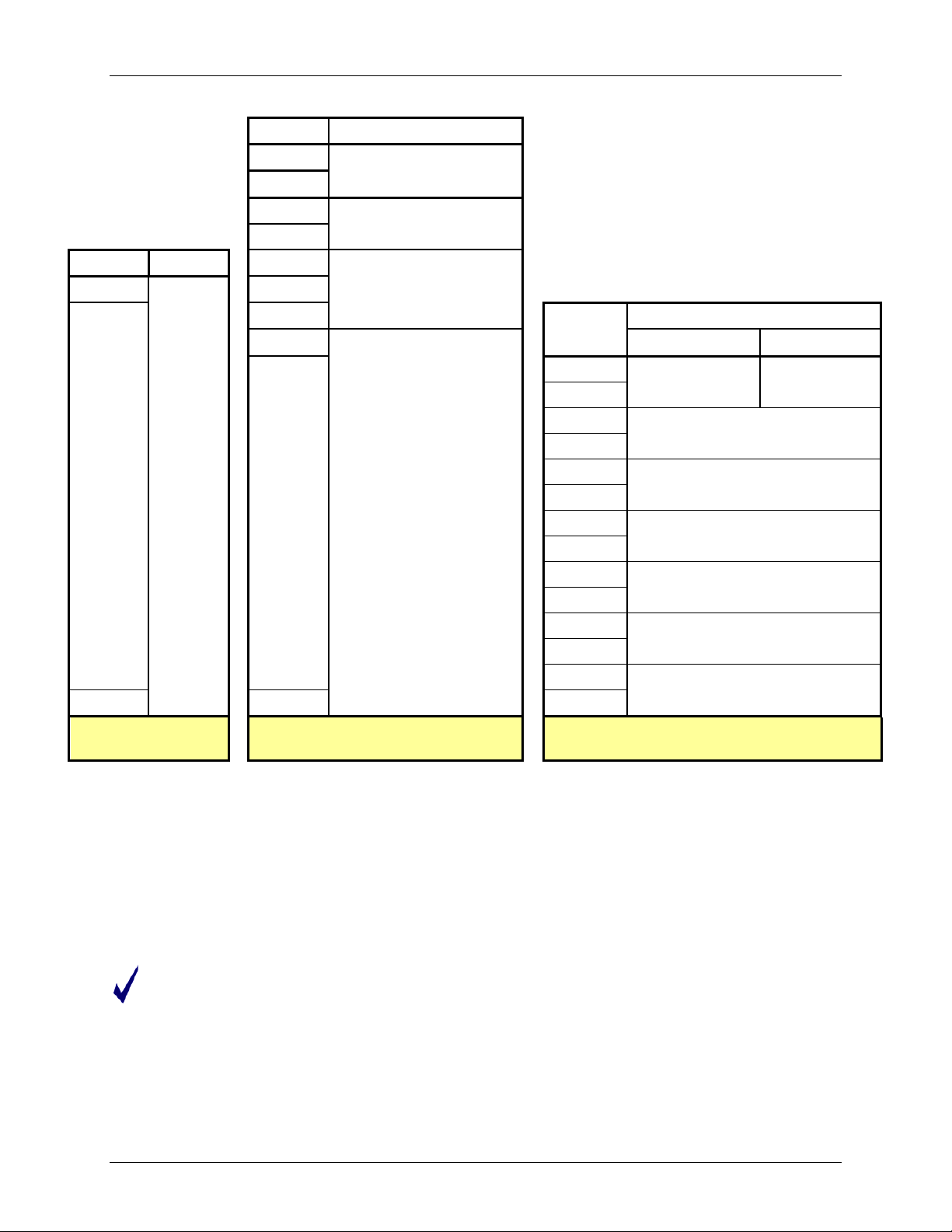

Page 7

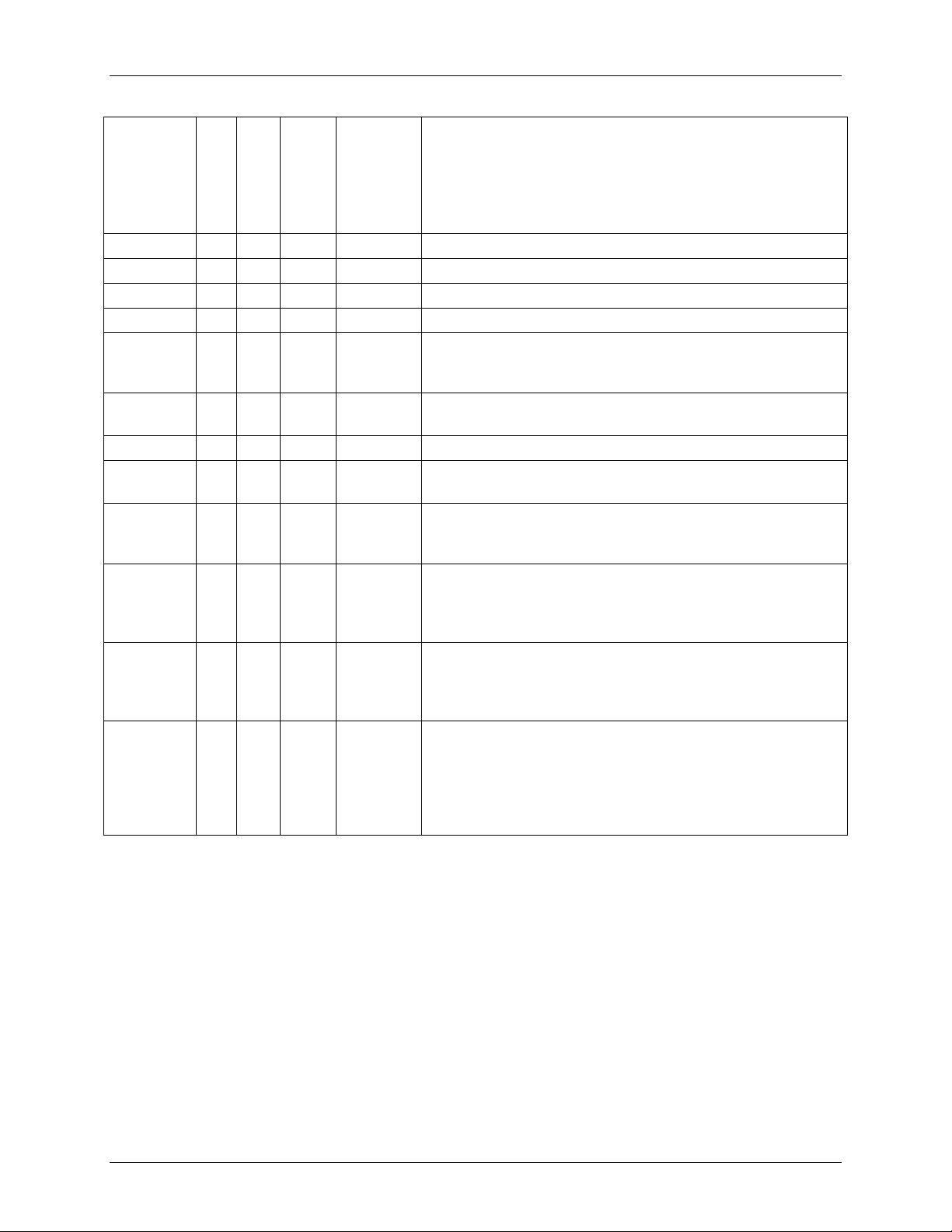

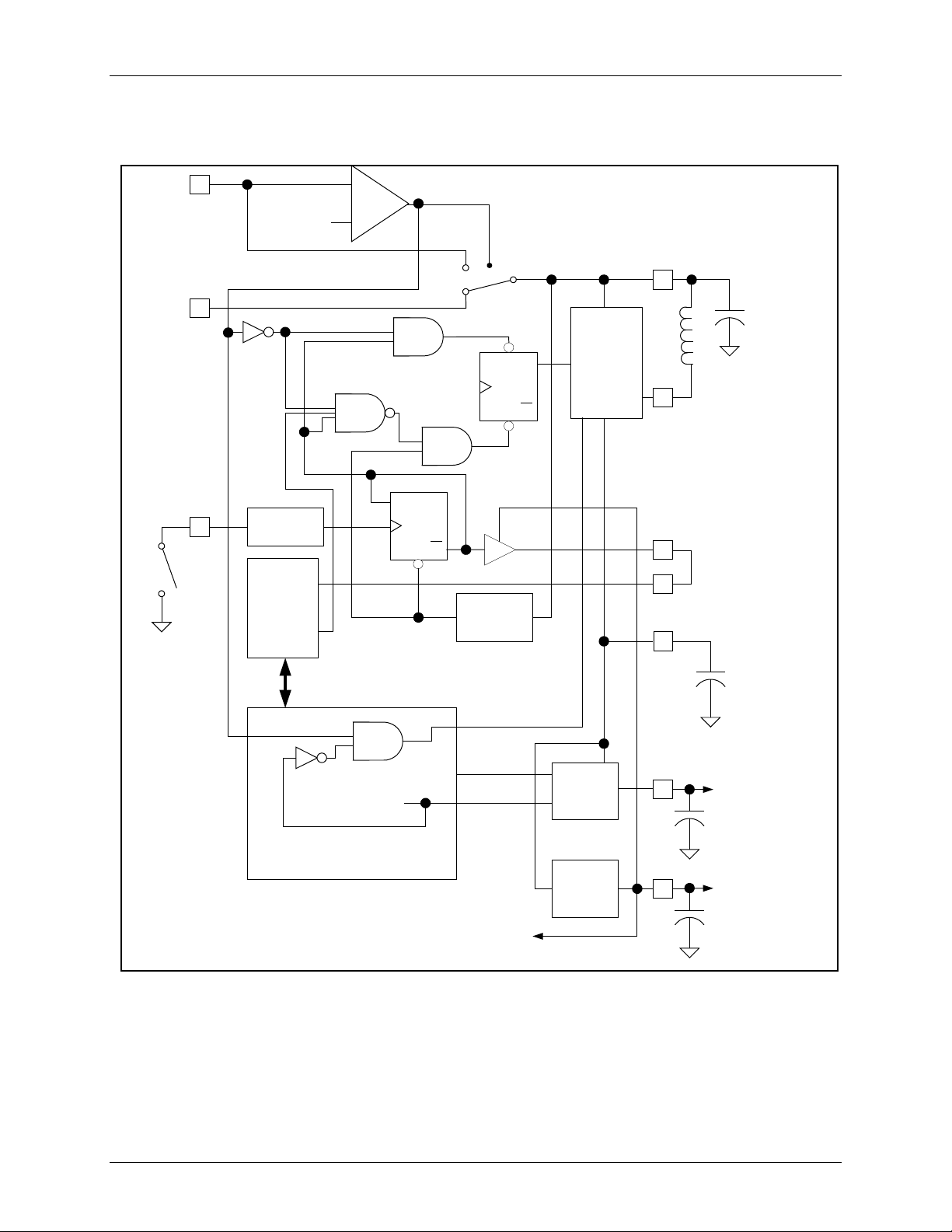

SMART

CARD

ISO

INTERFACE

SCLK

SIO

EXTERNAL

SMART

CARD

INTERFACE

POWER

REGULATION

AND VCC

CONTROL

LOGIC

GND

VDD

TBUS1

TBUS2

TBUS3

TBUS0

RXTX

ERST

ISBR

TCLK

TXD

RXD

ICE INTERFACE

SEC

SMART CARD LOGIC

ISO UART and CLOCK GENERATOR

FLASH/ROM

PROGRAM

MEMORY

32KB

DATA

XRAM

2KB

CORE

SERIAL

INT2

INT3

GND

GND

PERIPHERAL

INTERFACE

and SFR LOGIC

FLASH

INTERFACE

TEST

OCDSI

ISR

WATCH-

DOG

TIMER

PMU

PORTS

TIMER_0_1

MEMORY_

CONTROL

CONTROL

UNIT

RAM_

SFR_

CONTROL

ALU

RESET

VOLTAGE REFERENCE

AND FUSE TRIM

CIRCUITRY

VPD REGULATOR

ANA_IN

PLL

and

TIMEBASES

VDD

SCRATCH

IRAM

256B

12MHz

OSCILLATOR

X12OUT

X12IN

COL4

COL3

COL2

COL1

COL0

ROW5

ROW4

ROW3

ROW2

ROW1

ROW0

KEYPAD

INTERFACE

I

2

C

MASTER

INT.

SDA

SCL

USR(8:0)

DRIVERS

USR7

USR6

USR5

USR4

USR3

USR1

USR2

USR0

VCC

RST

CLK

I/O

AUX2

AUX1

PRES

VPC

GND

VBUS

VP

VBAT

VDD

LIN

OFF_REQ

ON_OFF

GND

LED

DRIVER

LED0

Pins available on both 68 and 44-pin packages.

Pins only available on 68-pin package.

DS_1210F_001 73S1210F Data Sheet

Figure 1: IC Functional Block Diagram

Rev. 1.4 7

Page 8

73S1210F Data Sheet DS_1210F_001

4

19

13

2

1 Hardware Description

1.1 Pin Description

Table 1: 73S1210 Pinout Description

Pin Name

Pin (68 QFN)

Pin (44 QFN)

X12IN 10 9 I Figure 26 MPU clock crystal oscillator input pin. A 1MΩ resistor is

X12OUT 11 10 O Figure 26 MPU clock crystal oscillator output pin.

ROW(5:0)

0

1

2

3

4

5

COL(4:0)

0

1

2

3

USR(7:0)

0

1

2

3

4

5

6

7

SCL 5 6 O Figure 29 I2C (master mode) compatible Clock signal. Note: the pin

SDA 6 7 IO Figure 28 I

RXD 17 11 I Figure 32 Serial UART Receive data pin.

TXD 18 12 O Figure 29 Serial UART Transmit data pin.

INT3 48 30 I Figure 32 General purpose interrupt input.

INT2 49 31 I Figure 32 General purpose interrupt input.

SIO 47 29 IO Figure 28 IO data signal for use with external Smart Card interface

SCLK 45 28 O Figure 29 Clock signal for use with external Smart Card interface

21

22

24

33

36

37

12

13

14

16

35

34

32

31

30

29

23

20

I Figure 34 Keypad row input sense.

O Figure 35 Keypad column output scan pins.

22

21

20

19

18

17

14

Type

IO Figure 30 General-purpose user pins, individually configurable as

Equivalent

Description

Circuit*

required between pins X12IN and X12OUT.

inputs or outputs or as external input interrupt ports.

is configured as an open drain output. When the I2C

interface is being used, an external pull up resistor is

required. A value of 3K is recommended.

C (master mode) compatible data I/O. Note: this pin is bidirectional. When the pin is configured as output, it is an

open drain output. When the I2C interface is being used,

an external pull up resistor is required. A value of 3K is

recommended.

circuit such as 73S8010.

circuit.

8 Rev. 1.4

Page 9

DS_1210F_001 73S1210F Data Sheet

Pin Name

Pin (68 QFN)

Pin (44 QFN)

Type

Equivalent

Description

Circuit*

PRES 53 34 I Figure 41 Smart Card presence. Active high. Note: the pin has a

very weak pull down resistor. In noisy environments, an

external pull down may be desired to insure against a

false card event.

CLK 55 36 O Figure 39 Smart Card clock signal.

RST 57 38 O Figure 39 Smart Card reset signal.

IO 61 42 IO Figure 40 Smart Card Data IO signal.

AUX1 60 41 IO Figure 40 Auxiliary Smart Card IO signal (C4).

AUX2 59 40 IO Figure 40 Auxiliary Smart Card IO signal (C8).

VCC 58 39 PSO

Smart Card VCC supply voltage output. A 0.47µF

capacitor is required and should be located at the smart

card connector. The capacitor should be a ceramic type

with low ESR.

GND 56 37 GND Smart Card Ground.

VPC 65 44 PSI Power supply source for main voltage converter circuit. A

10µF and a 0.1µF capacitor are required at the VPC input.

The 10µF capacitor should be a ceramic type with low

ESR.

VBUS 62 PSI Alternate power source input from external power supply.

VBAT 64 PSI Alternate power source input, typically from two series

cells, V > 4V.

VP 54 35 PSO Intermediate output of main converter circuit. Requires an

external 4.7µF low ESR filter capacitor to GND.

LIN 66 1 PSI

Connection to 10µH inductor for internal step up

converter. Note: inductor must be rated for 400 mA

maximum peak current.

ON_OFF 63 43 I Figure 43 Power control pin. Connected to normally open SPST

switch to ground. Closing switch for duration greater than

debounce period will turn 73S1210F on. If 73S1210F is

on, closing switch will flag the 73S1210F to go to the off

state. Firmware will control when the power is shut down.

OFF_REQ 52 33 O Figure 33 Digital output. If ON_OFF switch is closed (to ground) for

debounce duration and circuit is “on,” OFF_REQ will go

high (Request to turn OFF). This output should be

connected to an interrupt pin to signal the CPU core that a

request to shut down power has been initiated. The

firmware can then perform all of its shut down

DD

.

TBUS(3:0)

0

1

2

3

50

46

44

41

IO

housekeeping duties before shutting down V

Trace bus signals for ICE.

Rev. 1.4 9

Page 10

73S1210F Data Sheet DS_1210F_001

GND

Pin Name

Pin (68 Qfn)

Pin (44 QFN)

Type

Equivalent

Description

Circuit*

RXTX 43 27 IO ICE control.

ERST 38 23 IO ICE control.

ISBR 3 IO ICE control.

TCLK 39 24 I ICE control.

ANA_IN 15 AI Figure 38 Analog input pin. This signal goes to a programmable

comparator and is used to sense the value of an external

voltage.

SEC 2 I Figure 37 Input pin for use in programming security fuse. It should be

connected to ground when not in use.

TEST 51 32 DI Figure 37 Test pin, should be connected to ground

LED0 4 5 IO Figure 36 Special output driver, programmable pull-down current to

drive LED. May also be used as an input.

VDD 68

N/C 7

28

40

3

16

25

PSO

VDD supply output pin. A 0.1µF capacitor is recommended

at each VDD pin.

No connect.

8

26

27

9

25

42

67

2

8

15

26

GND

General ground supply pins for all IO and logic circuits.

RESET 1 4 I Figure 32 Reset input, positive assertion. Resets logic and registers

to default condition. Note: to insure proper reset operation

after V

is turned on by application of V

DD

power or

BUS

activation of the ON/OFF switch, external reset circuitry

must generate a proper reset signal to the 73S1210F. This

can be accomplished via a simple RC network.

* See the figures in the Equivalent Circuits section.

10 Rev. 1.4

Page 11

DS_1210F_001 73S1210F Data Sheet

1.2 Hardware Overview

The 73S1210F single smart card controller integrates all primary functional blocks required to implement

a smart card reader. Included on chip are an 8051-compatible microprocessor (MPU) which executes up

to one instruction per clock cycle (80515), a fully integrated IS0 7816 compliant smart card interface,

expansion smart card interface, serial interface, I2C interface, 6 x 5 keypad interface, RAM , FLASH

memory, and a variety of I/O pins.

The power management circuitry provides a 3.3V voltage output (VDD, pin #68) that must be connected

to the power supply inputs of the digital core of the circuit, pins # 28 and 40 (these are not internally

connected). Should external circuitry require a 3.3V digital power supply, the VDD output i s capable of

supplying additional current.

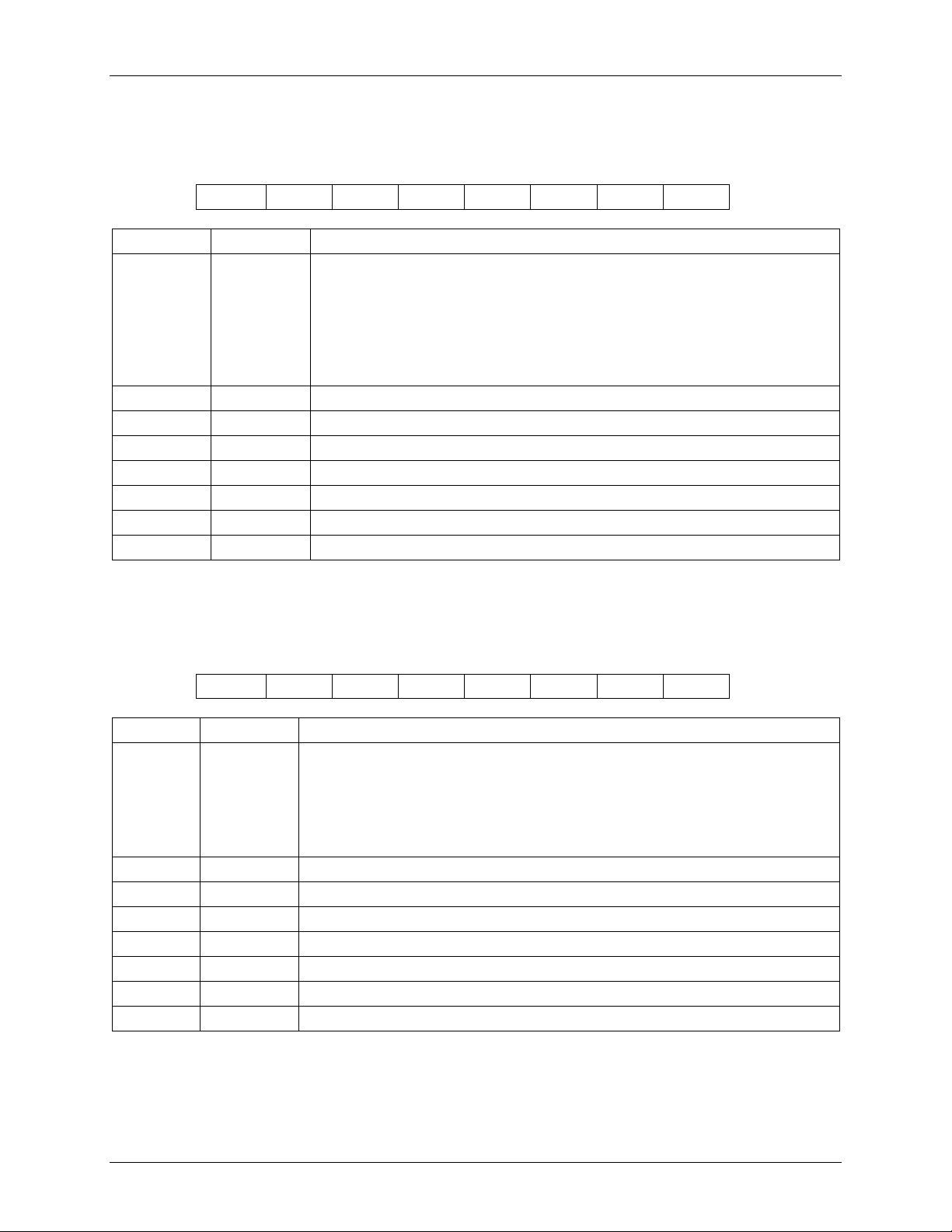

Figure 1 shows a functional block diagram of the 73S1210F.

1.3 80515 MPU Core

1.3.1 80515 Overview

The 73S1210F includes an 80515 MPU (8-bit, 8051-compatible) that performs most instructions in one

clock cycle. The 80515 architecture eliminates redundant bus states and implements parallel execution

of fetch and execution phases. Normally a machine cycle is aligned with a memory fetch, therefore, most

of the 1-byte instructions are performed in a single cycle. This leads to an 8x performance (average)

improvement (in terms of MIPS) over the Intel 8051 device running at the same clock frequency.

Actual processor clocking speed can be adjusted to the total processing demand of the application

(cryptographic calculations, key management, memory management, and I/O management) using the

XRAM special function register MPUCKCtl.

Typical smart card, serial, keyboard and I2C management functions are available for the MPU as part of

the Teridian standard library. A standard ANSI “C” 80515-application programming interface library is

available to help reduce design cycle. Refer to the 73S12xxF Software User’s Guide.

1.3.2 Memory Organization

The 80515 MPU core incorporates the Harvard architecture with separate code and data spaces.

Memory organization in the 80515 is similar to that of the industry standard 8051. There are three

memory areas: Program memory (Flash), external data memory (XRAM), and internal data m em ory

(IRAM). Data bus address space is allocated to on-chip memory as shown Table 2

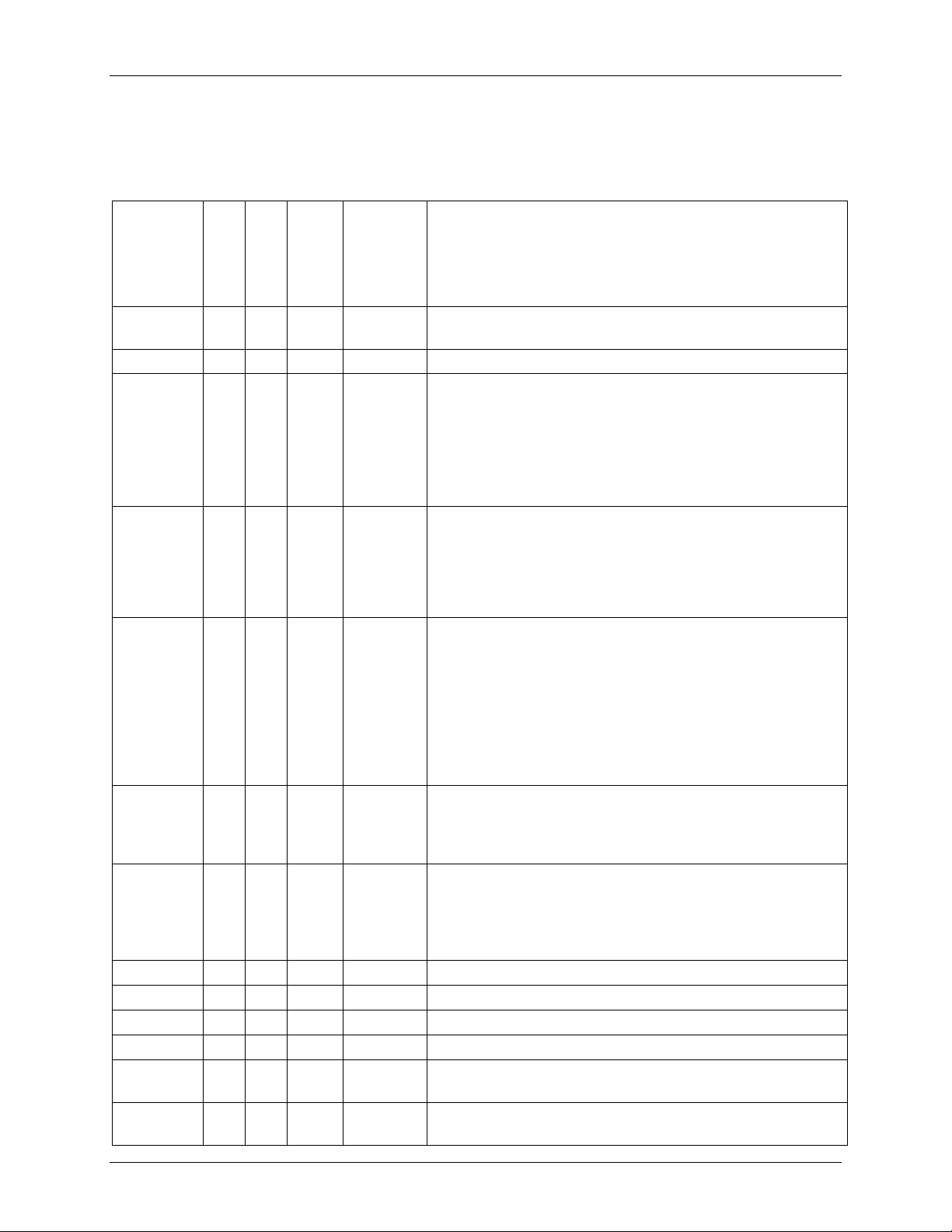

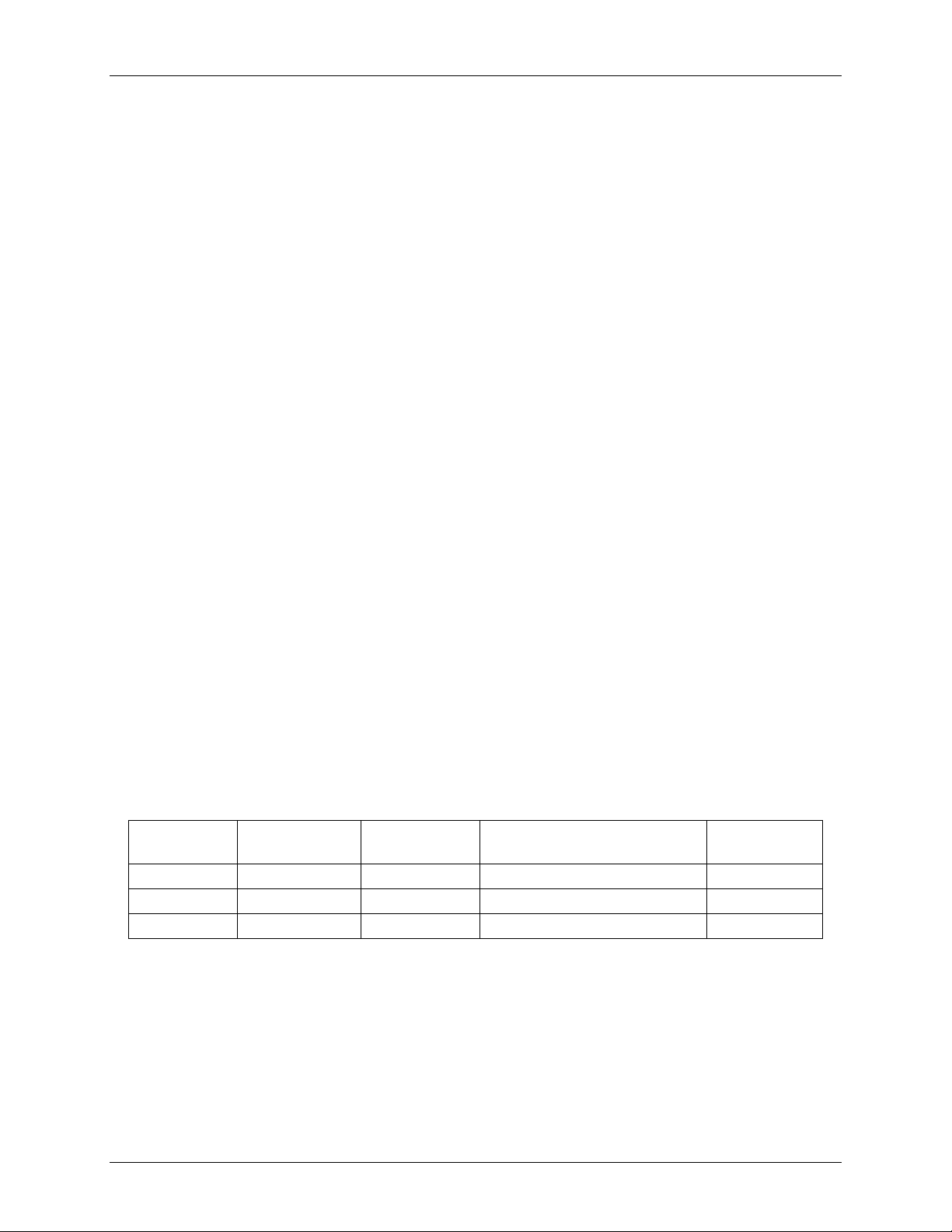

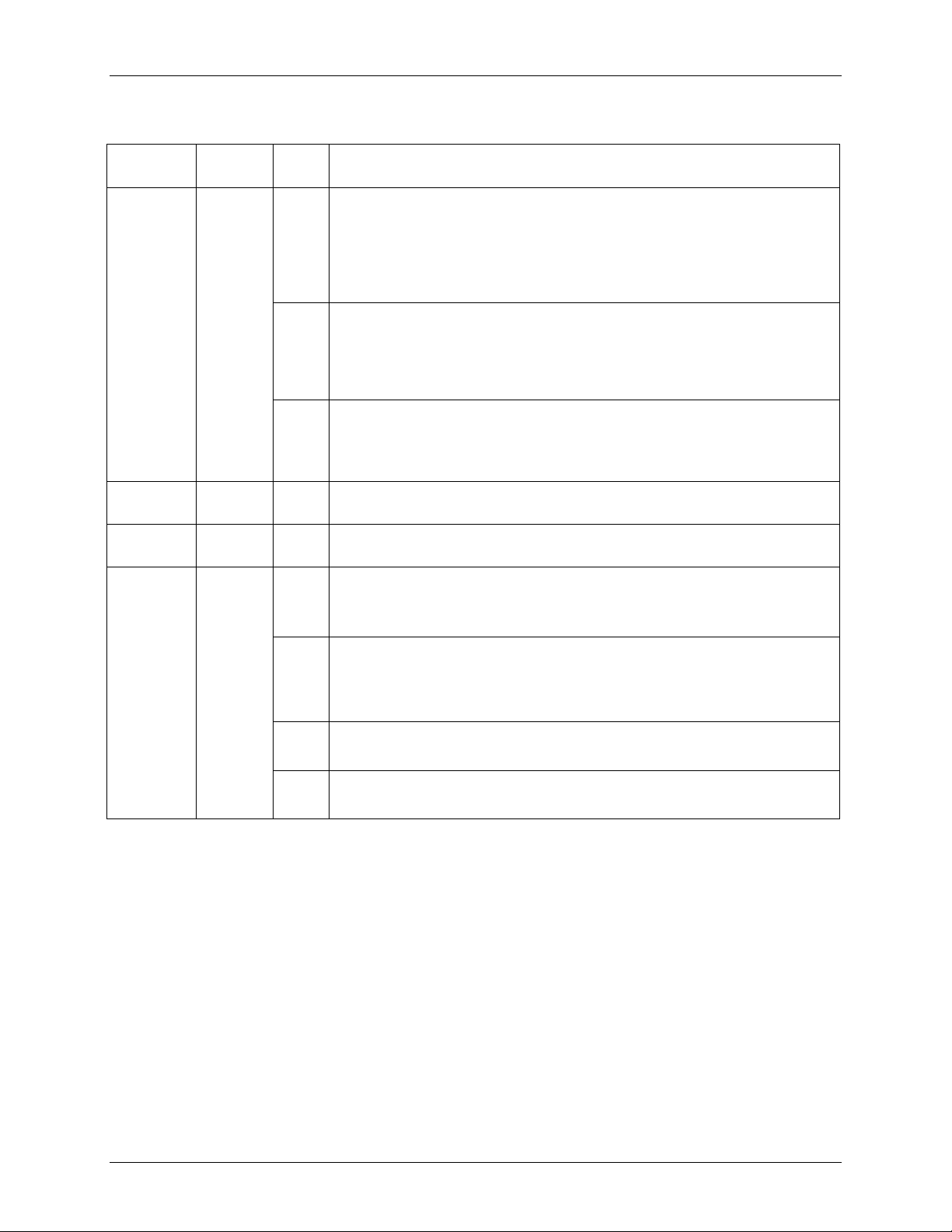

Table 2: MPU Data Memory Map

Address

(hex)

0000-7FFF Flash Memory Non-volatile Program and non-volatile data 32KB

0000-07FF Static RAM Volatile MPU data XRAM 2KB

FC00-FFFF External SFR Volatile Peripheral control 1KB

Note: The IRAM is part of the core and is addressed differently.

Program Memory: The 80515 can address up to 32KB of program memory space from 0x0000 to

0xFFFF. Program memory is read when the MPU fetches instructions or performs a MOVC operation.

After reset, the MPU starts program execution from location 0x0000. The lower part of the program

memory includes reset and interrupt vectors. The interrupt vectors are spaced at 8-byte intervals, starting

from 0x0003. Reset is located at 0x0000.

Flash Memory: The program memory consists of flash memory. The flash memory i s intended to

primarily contain MPU program code. Flash erasure is initiated by writing a specific data pattern to

Rev. 1.4 11

Memory

Technology

Memory Type Typi cal Usage

Memory Size

(bytes)

Page 12

73S1210F Data Sheet DS_1210F_001

specific SFR registers in the proper sequence. These special pattern/sequence requirements prevent

inadvertent erasure of the flash memory.

The mass erase sequence is:

1. Write 1 to the FLSH_MEEN bit in the FLSHCTL register (SFR address 0xB2[1]).

2. Write pattern 0xAA to ERASE (SFR address 0x94).

Note: The mass erase cycle can only be initiated when the ICE port is enabled.

The page erase sequence is:

1. Write the page address to PGADDR (SFR address 0xB7[7:1]).

2. Write pattern 0x55 to ERASE (SFR address 0x94).

The PGADDR register denotes the page address for page erase. The page size is 512 (200h) bytes and

there are 128 pages within the flash memory. The PGADDR denotes the upper seven bits of the flash

memory address such that bit 7:1 of the PGADDR corresponds to bit 15:9 of the flash memory address.

Bit 0 of the PGADDR is not used and is ignored. The MPU may write to the flash memory. This is one of

the non-volatile storage options available to the user. The FLSHCTL SFR bit FLSH_PWE (flash program

write enable) differentiates 80515 data store instructions (MOVX@DPTR,A) between Flash and XRAM

writes. Before setting FLSH_PWE, all interrupts need to be disabled by setting EAL = 1. Table 3 shows

the location and description of the 73S1210 flash-specific SFRs.

Any flash modifications must set the CPUCLK to operate at 3.6923 MHz (MPUCLKCtl = 0x0C)

before any flash memory operations are executed to insure the proper timing when modifying the

flash memory.

12 Rev. 1.4

Page 13

DS_1210F_001 73S1210F Data Sheet

Initiate Flash Page Erase cycle. Must be proceeded by a write

Table 3: Flash Special Function Registers

Register SFR

R/W Description

Address

ERASE 0x94 W This register is used to initiate either the Flash Mass Erase cycle or the

Flash Page Erase cycle. Specific patterns are expected for ERASE in

order to initiate the appropriate Erase cycle (default = 0x00).

0x55 –

to PGADDR @ SFR 0xB7.

0xAA – Initiate Flash Mass Erase cycle. Must be proceeded by a write

to FLSH_MEEN @ SFR 0xB2 and the debug port must be

enabled.

Any other pattern written to ERASE will have no effect.

PGADDR 0xB7 R/W Flash Page Erase Address register containing the flash memory page

address (page 0 through 127) that will be erased during the Page Erase

cycle (default = 0x00). Note: the page address is shifted left by one bit

(see detailed description above).

Must be re-written for each new Page Erase cycle.

FLSHCTL 0xB2 R/W

Bit 0 (FLSH_PWE): Program Write Enable:

0 – MOVX commands refer to XRAM Space, normal operation (default).

1 – MOVX @DPTR,A moves A to Program Space (Flash) @ DPTR.

This bit is automatically reset after each byte written to flash. Writes to

this bit are inhibited when interrupts are enabled.

W Bit 1 (FLSH_MEEN): Mass Erase Enable:

0 – Mass Erase disabled (default).

1 – Mass Erase enabled.

Must be re-written for each new Mass Erase cycle.

R/W Bit 6 (SECURE):

Enables security provisions that prevent external reading of flash

memory and CE program RAM. This bit is reset on chip reset and may

only be set. Attempts to write zero are ignored.

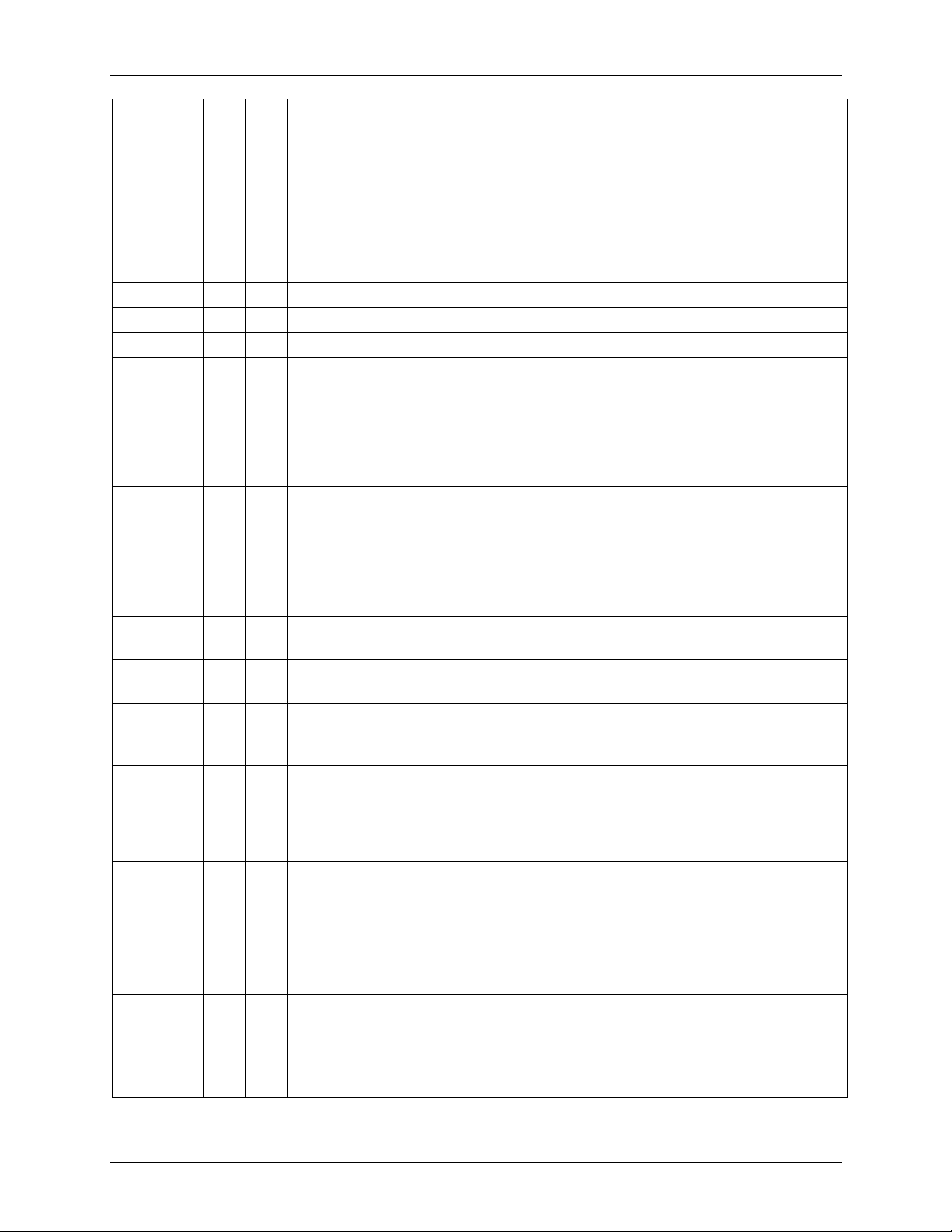

Internal Data Memory: The Internal data memory provides 256 bytes (0x00 to 0xF F) of data memory.

The internal data memory address is always one byte wide and can be accessed by either direct or

indirect addressing. The Special Function Registers occupy the upper 128 bytes. This SFR area is

available only by direct addressing. Indirect addressin g accesses the up per 128 bytes of Internal

RAM.

The lower 128 bytes contain working registers and bit-addressable memory. The lower 32 bytes form

four banks of eight registers (R0-R7). Two bits on the program memory status word (PSW) select which

bank is in use. The next 16 bytes form a block of bit-addressable memory space at bit addresses 0x000x7F. All of the bytes in the lower 128 bytes are accessible through direct or indirect addressing. Table 4

shows the internal data memory map.

Rev. 1.4 13

Page 14

73S1210F Data Sheet DS_1210F_001

Table 4: Internal Data Memory Map

Address Direct Addressing Indirect Addressing

0xFF

0x80

Special Function

Registers (SFRs)

RAM

0x7F

0x30

Byte-addressable area

0x2F

0x20

0x1F

0x00

Byte or bit-addressable area

Register banks R0…R7 (x4)

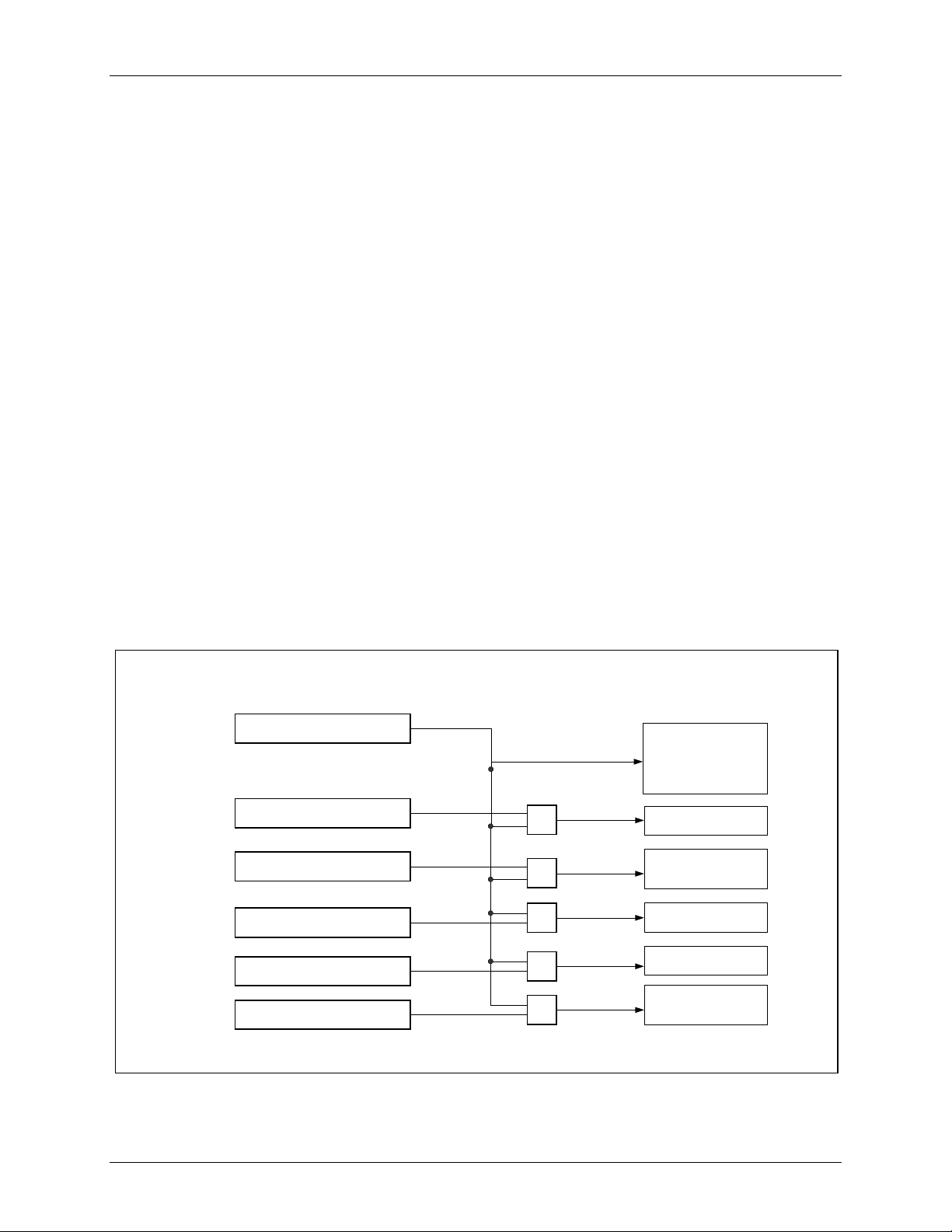

External Data Memory: While the 80515 can address up to 64KB of external data memory in the space

from 0x0000 to 0xFFFF, only the memory ranges shown in Figure 2 contain physical memory. The

80515 writes into external data memory when the MPU executes a MOVX @Ri,A or MO V X @DPTR,A

instruction. The MPU reads external data memory by executing a MOVX A,@Ri or MOVX A,@DPTR

instruction.

There are two types of instructions, differing in whether they provide an eight-bit or sixteen-bit indi rect

address to the external data RAM.

In the first type (MOVX A,@Ri), the contents of R0 or R1, in t he current regist er bank, prov i de the eight

lower-ordered bits of address. This method allows the user access to the first 256 bytes of the 2KB of

external data RAM. In the second type of MOVX instruction (MOVX A,@DPTR), the data pointer

generates a sixteen-bit address.

14 Rev. 1.4

Page 15

DS_1210F_001 73S1210F Data Sheet

Address Use

0x7FFF

Address Use

0xFFFF

0XFF80

0xFF7F

Peripheral Control

Registers (128b)

Smart Card Control

0XFE00

0xFBFF

0x0800

(384b)

–

Use

Address

Flash

Program

Memory

32K

Bytes

0x07FF

XRAM

0xFF

0x80

0x7F

0x48

0x47

0x20

0x1F

Indirect Access Direct Access

Byte RAM SFRs

Byte RAM

Bit/Byte RAM

Register bank 3

0x18

0x17

Register bank 2

0x10

0x0F

Register bank 1

0x08

0x07

Register bank 0

0x0000

0x0000

0x00

Program Memory External Data Memory Internal Data Memory

Figure 2: Memory Map

Dual Data Pointer: The Dual Data Pointer accelerates the block moves of data. The standard DPTR is a

16-bit register that is used to address external memory. In the 80515 core, the standard data pointer i s

called DPTR, the second data pointer is called DPTR1. The data pointer select bit chooses the active

pointer. The data pointer select bit is located at the LSB of the DPS IRAM special f unct i on regist er

(DPS.0). DPTR is selected when DPS.0 = 0 and DPTR1 is selected when DPS.0 = 1.

The user switches between pointers by toggling the LSB of the DPS register. All DPTR-related

instructions use the currently selected DPTR for any activity.

The second data pointer may not be supported by certain compilers.

Rev. 1.4 15

Page 16

73S1210F Data Sheet DS_1210F_001

1.4 Program Security

Two levels of program and data security are available. Each level requires a specific fuse to be blown in

order to enable or set the specific security mode. Mode 0 security is enabled by setting the SE CURE bi t

(bit 6 of SFR register FLSHCTL 0xB2). Mode 0 limits the ICE interface to only allow bulk erase of the

flash program memory. All other ICE operations are blocked. This guarantees the security of the user’s

MPU program code. Security (Mode 0) is enabled by MPU code that sets the SECURE bit. The M P U

code must execute the setting of the SECURE bit immediately af ter a reset to properly enable Mode 0.

This should be the first instruction after the reset vector jump has been executed. If the “startup.a51”

assembly file is used in an application, then it must be modified to set the SECURE bit after the reset

vector jump. If not using “startup.a51”, then this should be the first instructi on in m ain(). O nce security

Mode 0 is enabled, the only way to disable it is to perform a global erase of the flash f ol l owed by a full

circuit reset. Once the flash has been erased and the reset has been executed, security Mode 0 is

disabled and the ICE has full control of the core. The flash can be reprogrammed after the bulk erase

operation is completed. Global erase of the flash will also clear the data XRAM memory.

The security enable bit (SECURE) is reset whenever the MPU is reset. Hardware associated with the bit

only allows it to be set. As a result, the code may set the SECURE bit to enable the security Mode 0

feature but may not reset it. Once the SECURE bit is set, t he code is prot ected and no external read of

program code in flash or data (in XRAM) is possible. In order to invoke the security Mode 0, the

SECSET0 (bit 1 of the XRAM SFR register SECReg 0xFFD7) fuse must be blown beforehand or the

security mode 0 will not be enabled. The SECSET0 and SECSET1 fuses once blown, cannot be

overridden.

Specifically, when SECURE is set:

• The ICE is limited to bulk flash erase only.

• Page zero of flash memory, the preferred location for the user’s preboot code, may not be page-

erased by either MPU or ICE. Page zero may only be erased with global flash erase. Note that

global flash erase erases XRAM whether the SECURE bit is set or not.

• Writes to page zero, whether by MPU or ICE, are inhibited.

Security mode 1 is in effect when the SECSET1 fuse has been programmed (blown open). In security

mode 1, the ICE is completely and permanently disabled. The Flash program memory and the MPU are

not available for alteration, observation, nor control. As soon as the fuse has been blown, the ICE is

disabled. The testing of the SECSET1 fuse will occur during the reset and before the start of pre-boot

and boot cycles. This mode is not reversible, nor recoverable. In order to blow the SECSET1 f use, the

SEC pin must be held high for the fuse burning sequence to be executed properly. The firmware can

check to see if this pin is held high by reading the SECPIN bit (bit 5 of XRAM SFR register SECReg

0xFFD7). If this bit is set and the firmware desires, it can blow the SECSET1 f use. The burning of the

SECSET0 does not require the SEC pin to be held high.

In order to blow the fuse for SECSET1 and SECSET0, a particular set of register writ es in a specif ic order

need to be followed. There are two additional registers that need to have a specific value writt en to them

in order for the desired fuse to be blown. These registers are FUSECtl (0xFFD2) and TRIMPCtl

(0xFFD1). The sequence for blowing the fuse is as follows:

1. Write 0x54H to FUSECtl.

2. Write 0x81H for security mode 0. Note: only program one security mode at a time.

Write 0x82H for security mode 1. Note: SEC pin must be high for security mode 1.

3. Write 0xA6 to TRIMPCtl.

4. Delay about 500 µs.

5. Write 0x00 to TRIMPCtl and FUSECtl.

16 Rev. 1.4

Page 17

DS_1210F_001 73S1210F Data Sheet

Table 5: Program Security Registers

Register SFR

R/W Description

Address

FLSHCTL 0xB2 R/W Bit 0 (FLSH_PWE): Program Write Enable:

0 – MOVX commands refer to XRAM Space, normal operation (default).

1 – MOVX @DPTR,A moves A to Program Space (Flash) @ DPTR.

This bit is automatically reset after each byte written to flash. Writes to

this bit are inhibited when interrupts are enabled.

W Bit 1 (FLSH_MEEN): Mass Erase Enable:

0 – Mass Erase disabled (default).

1 – Mass Erase enabled.

Must be re-written for each new Mass Erase cycle.

R/W Bit 6 (SECURE):

Enables security provisions that prevent external reading of flash

memory and CE program RAM. This bit is reset on chip reset and may

only be set. Attempts to write zero are ignored.

TRIMPCtl 0xFFD1 W 0x54 value will set up for security fuse control. All ot her values are

reserved and should not be used.

FUSECtl 0xFFD2 W 0xA6 value will cause t he select ed fuse to be blown. All other values

will stop the burning process.

SECReg 0xFFD7 W Bit 7 (PARAMSEC):

0 – Normal operation.

1 – Enable permanent programming of the security fuses.

R Bit 5 (SECPIN):

Indicates the state of the SEC pin. The SEC pin is held low by a

pull-down resistor. The user can force this pin high during boot

sequence time to indicate to firmware that sec mode 1 is desired.

R/W Bit 1 (SECSET1):

See the Program Security section.

R/W Bit 0 (SECSET0):

See the Program Security section.

Rev. 1.4 17

Page 18

73S1210F Data Sheet DS_1210F_001

Hex

KCOL

KROW

KSCAN

KSTAT

KSIZE

KORDERL

KORDERH

USR70

UDIR70

ERASE

MCLKCtl

1.5 Special Function Registers (SFRs)

The 73S1210F utilizes numerous SFRs to communicate with the 73S1210Fs many peripherals. This

results in the need for more SFR locations outside the direct address IRAM space (0x80 to 0xFF). While

some peripherals are mapped to unused IRAM SFR locations, additional SFRs for the smart card and

other peripheral functions are mapped to the top of the XRAM data space (0xFC00 to 0xFFFF).

1.5.1 Internal Data Special Function Registers (SFRs)

A map of the Special Function Registers is shown in Table 6.

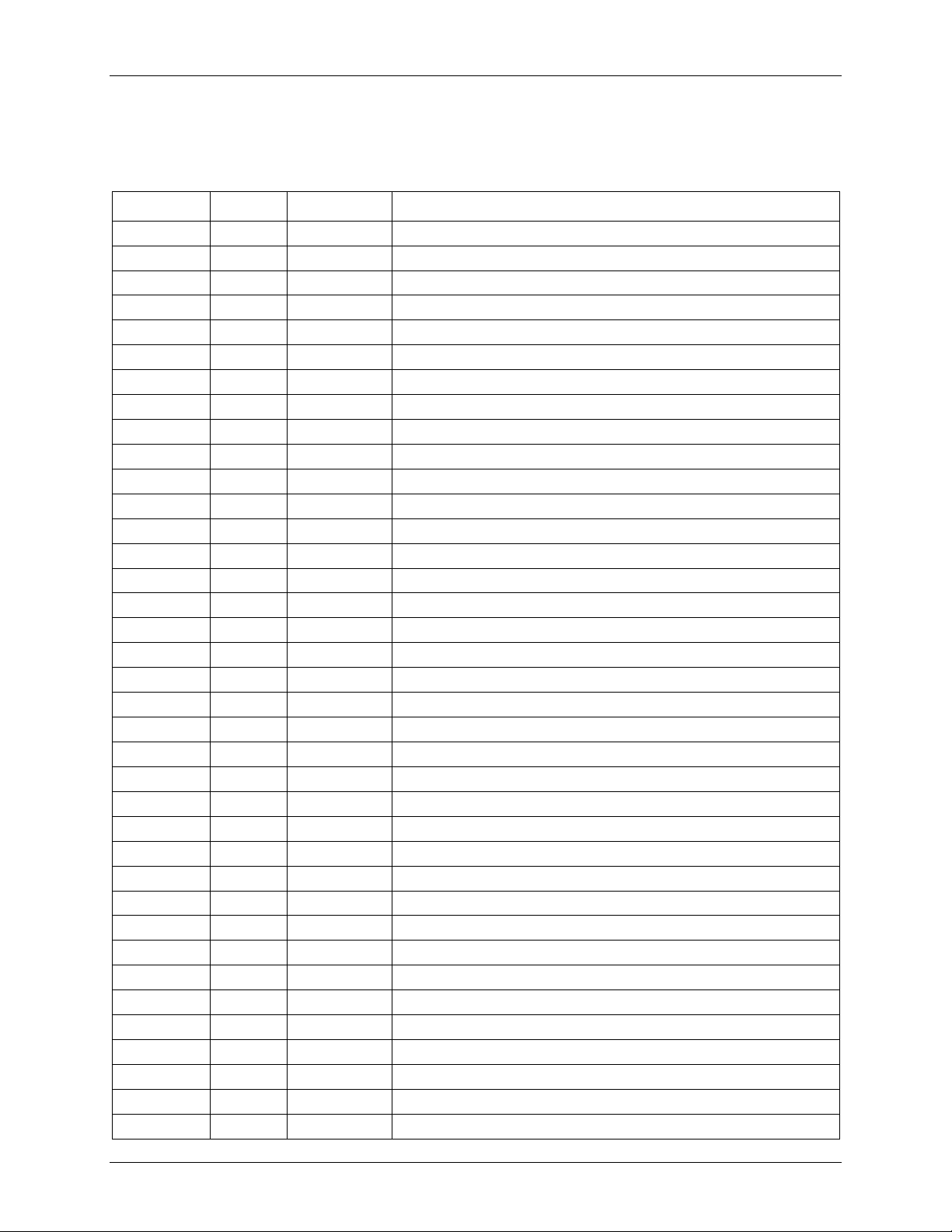

Table 6: IRAM Special Function Registers Locations

Hex\Bin X000 X001 X010 X011 X100 X101 X110 X111

F8 FF

F0 B F7

E8 EF

E0 A E7

D8 BRCON DF

D0 PSW

C8 T2CON CF

C0 IRCON C7

B8 IEN1 IP1 S0RELH S1RELH BF

B0

A8 IEN0 IP0 S0RELL AF

A0 A7

98 S0CON S0BUF IEN2 S1CON S1BUF S1RELL 9F

90

88 TCON TMOD TL0 TL1 TH0 TH1

80 SP DPL DPH DPL1 DPH1 WDTREL PCON 87

Only a few addresses are used, the others are not implemented. SFRs specific to the 73S1210F are

shown in bold print (gray background). Any read access to unimplemented addresses will return

undefined data, while most write access will have no effect. However, a few locations are reserved and

not user configurable in the 73S1210F. Writes to the unused SFR locations can affect the operation

of the core and therefore must not be written to. This applies to all the SFR areas in both the

IRAM and XRAM spaces. In addition, all unused bit locations within valid SFR registers must be

left in their default (power on default) states.

FLSHCTL

DPS

97

PGADDR

Bin/

D7

B7

8F

18 Rev. 1.4

Page 19

DS_1210F_001 73S1210F Data Sheet

1.5.2 IRAM Special Function Registers (Generic 80515 SFRs)

Table 7 shows the location of the SFRs and the value they assume at reset or power-up.

Table 7: IRAM Special Function Registers Reset Values

Name Location Reset Value Description

SP 0x81 0x07 Stack Pointer

DPL 0x82 0x00 Data Pointer Low 0

DPH 0x83 0x00 Data Pointer High 0

DPL1 0x84 0x00 Data Pointer Low 1

DPH1 0x85 0x00 Data Pointer Hi gh 1

WDTREL 0x86 0x00 Watchdog Timer Reload register

PCON 0x87 0x00 Power Control

TCON 0x88 0x00 Timer/Counter Control

TMOD 0x89 0x00 Timer Mode Control

TL0 0x8A 0x00 Timer 0, low byte

TL1 0x8B 0x00 Timer 1, high byte

TH0 0x8C 0x00 Timer 0, low byte

TH1 0x8D 0x00 Timer 1, high byte

MCLKCtl 0x8F 0x0A Master Clock Control

USR70 0x90 0xFF User Port Data (7:0)

UDIR70 0x91 0xFF User Port Direction (7:0)

DPS 0x92 0x00 Data Pointer Select Register

ERASE 0x94 0x00 Flash Erase

S0CON 0x98 0x00 Serial Port 0, Control Register

S0BUF 0x99 0x00 Serial Port 0, Data Buffer

IEN2 0x9A 0x00 Interrupt Enable Register 2

S1CON 0x9B 0x00 Serial Port 1, Control Register

S1BUF 0x9C 0x00 Serial Port 1, Data Buffer

S1RELL 0x9D 0x00 Serial Port 1, Reload Register, low byte

IEN0 0xA8 0x00 Interrupt Enable Register 0

IP0 0xA9 0x00 Interrupt Priority Regist er 0

S0RELL 0xAA 0xD9 Serial Port 0, Reload Register, low byte

FLSHCTL 0xB2 0x00 Flash Control

PGADDR 0xB7 0x00 Flash Page Address

IEN1 0xB8 0x00 Interrupt Enable Register 1

IP1 0xB9 0x00 Interrupt Priority Regist er 1

S0RELH 0xBA 0x03 Serial Port 0, Reload Register, high byte

S1RELH 0xBB 0x03 Serial Port 1, Reload Register, high byte

IRCON 0xC0 0x00 Interrupt Request Control Register

T2CON 0xC8 0x00 Timer 2 Control

PSW 0xD0 0x00 Program Status Word

KCOL 0XD1 0x1F Keypad Column

Rev. 1.4 19

Page 20

73S1210F Data Sheet DS_1210F_001

Name Location Reset Value Description

KROW 0XD2 0x3F Keypad Row

KSCAN 0XD3 0x00 Keypad Scan Time

KSTAT 0XD4 0x00 Keypad Control/Status

KSIZE 0XD5 0x00 Keypad Size

KORDERL 0XD6 0x00 Keypad Column LS Scan Order

KORDERH 0XD7 0x00 Keypad Column MS Scan Order

BRCON 0xD8 0x00 Baud Rate Control Register (only BRCON.7 bit used)

A 0xE0 0x00 Accumulator

B 0xF0 0x00 B Register

1.5.3 External Data Special Function Registers (SFRs)

A map of the XRAM Special Function Registers is shown in Table 8. The smart card registers are listed

separately in Table 107.

Table 8: XRAM Special Function Registers Reset Values

Name Location Reset Value Description

DAR 0x FF80 0x00 Device Address Register (I2C)

2

2

C)

C)

2

C)

2

2

C)

C)

WDR 0x FF81 0x00 Write Data Register (I

SWDR 0x FF82 0x00 Secondary Write Data Register (I

RDR 0x FF83 0x00 Read Data Register (I

SRDR 0x FF84 0x00 Secondary Read Data Register (I

CSR 0x FF85 0x00 Control and Status Register (I

USRIntCtl1 0x FF90 0x00 External Interrupt Control 1

USRIntCtl2 0x FF91 0x00 External Interrupt Control 2

USRIntCtl3 0x FF92 0x00 External Interrupt Control 3

USRIntCtl4 0x FF93 0x00 External Interrupt Control 4

INT5Ctl 0x FF94 0x00 External Int errupt Control 5

INT6Ctl 0x FF95 0x00 External Int errupt Control 6

MPUCKCtl 0x FFA1 0x0C MPU Clock Control

ACOMP 0x FFD0 0x00 Analog Compare Register

TRIMPCtl 0x FFD1 0x00 TRIM Pulse Control

FUSECtl 0x FFD2 0x00 FUSE Control

VDDFCtl 0x FFD4 0x00 VDDFault Control

SECReg 0x FFD7 0x00 Security Register

MISCtl0 0x FFF1 0x00 Miscellaneous Control Register 0

MISCtl1 0x FFF2 0x10 Miscellaneous Control Register 1

LEDCtl 0x FFF3 0xFF LED Control Register

Accumulator (ACC, A): ACC is the accumulator register. Most instructions use the accumulator to hold

the operand. The mnemonics for accumulator-specific instructions refer to accumulator as “A”, not ACC.

B Register: The B register is used during multiply and divide instructions. It can also be used as a

scratch-pad register to hold temporary data.

20 Rev. 1.4

Page 21

DS_1210F_001 73S1210F Data Sheet

Program Status Word (PSW):

Table 9: PSW Register

MSB LSB

CV AC F0 RS1 RS OV – P

Bit Symbol Function

PSW.7 CV Carry flag.

PSW.6 AC Auxiliary Carry flag for BCD operations.

PSW.5 F0 General purpose Flag 0 available for user.

PSW.4 RS1 Register bank select control bits. The contents of RS1 and RS0 select the

working register bank:

RS1/RS0 Bank Selected Location

PSW.3 RS0

00 Bank 0 (0x00 – 0x07)

01 Bank 1 (0x08 – 0x0F)

10 Bank 2 (0x10 – 0x17)

11 Bank 3 (0x18 – 0x1F)

PSW.2 OV Overflow flag.

PSW.1 F1 General purpose Flag 1 available for user.

PSW.0 P Parity flag, affected by hardware to indicate odd / even number of “one” bits

in the Accumulator, i.e. even parity.

Stack Pointer: The stack pointer (SP) is a 1-byte register initialized to 0x07 after reset. This register is

incremented before PUSH and CALL instructions, causing the stack to begin at location 0x08.

Data Pointer: The data pointer (DPTR) is 2 bytes wide. The lower part is DPL, and the highest is DPH.

It can be loaded as a 2-byte register (MOV DPTR,#data16) or as two registers (e.g. MOV DPL,#data8). I t

is generally used to access external code or data space (e.g. MOVC A,@A+DPTR or MOVX A,@DPTR

respectively).

Program Counter: The program counter (PC) is 2 bytes wide initialized to 0x0000 after reset. This

register is incremented during the fetching operation code or when operating on data from program

memory. Note: The program counter is not mapped to the SFR area.

Port Registers: The I/O ports are controlled by Special Function Register USR70. The contents of the

SFR can be observed on corresponding pins on the chip. Writing a 1 to any of the ports (see Table 10)

causes the corresponding pin to be at high level (3.3V), and writing a 0 causes the corresponding pin to

be held at low level (GND). The data direction register UDIR70 define individual pins as input or output

pins (see the User (USR) Ports section for details).

Table 10: Port Registers

Register

SFR

Address

R/W Description

USR70 0x90 R/W Register for User port bit 7: 0 read and write operations (pins USR0…

USR7).

UDIR70 0x91 R/W Data direction register for User port bits 0:7. Setting a bit to 0 means

that the corresponding pin is an output.

Rev. 1.4 21

Page 22

73S1210F Data Sheet DS_1210F_001

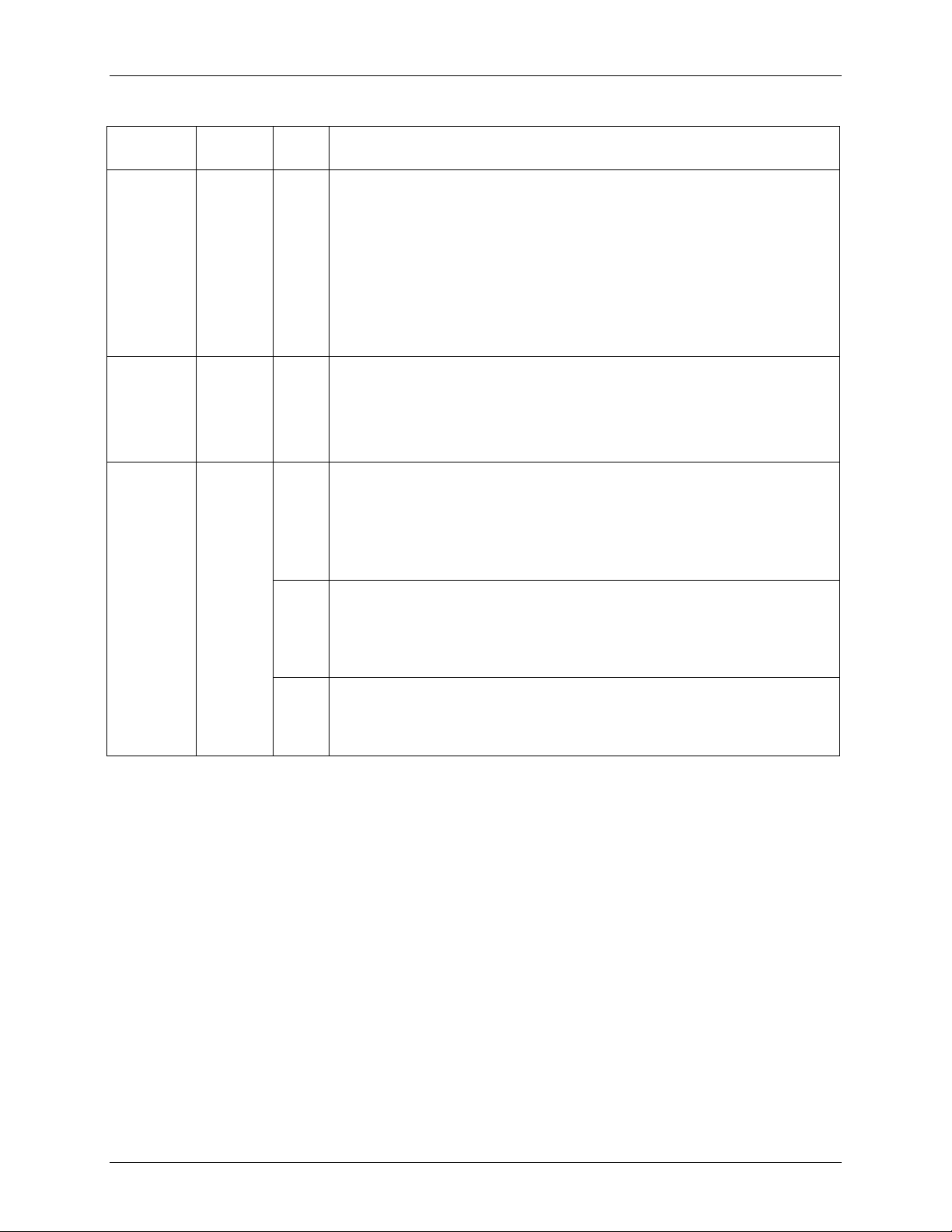

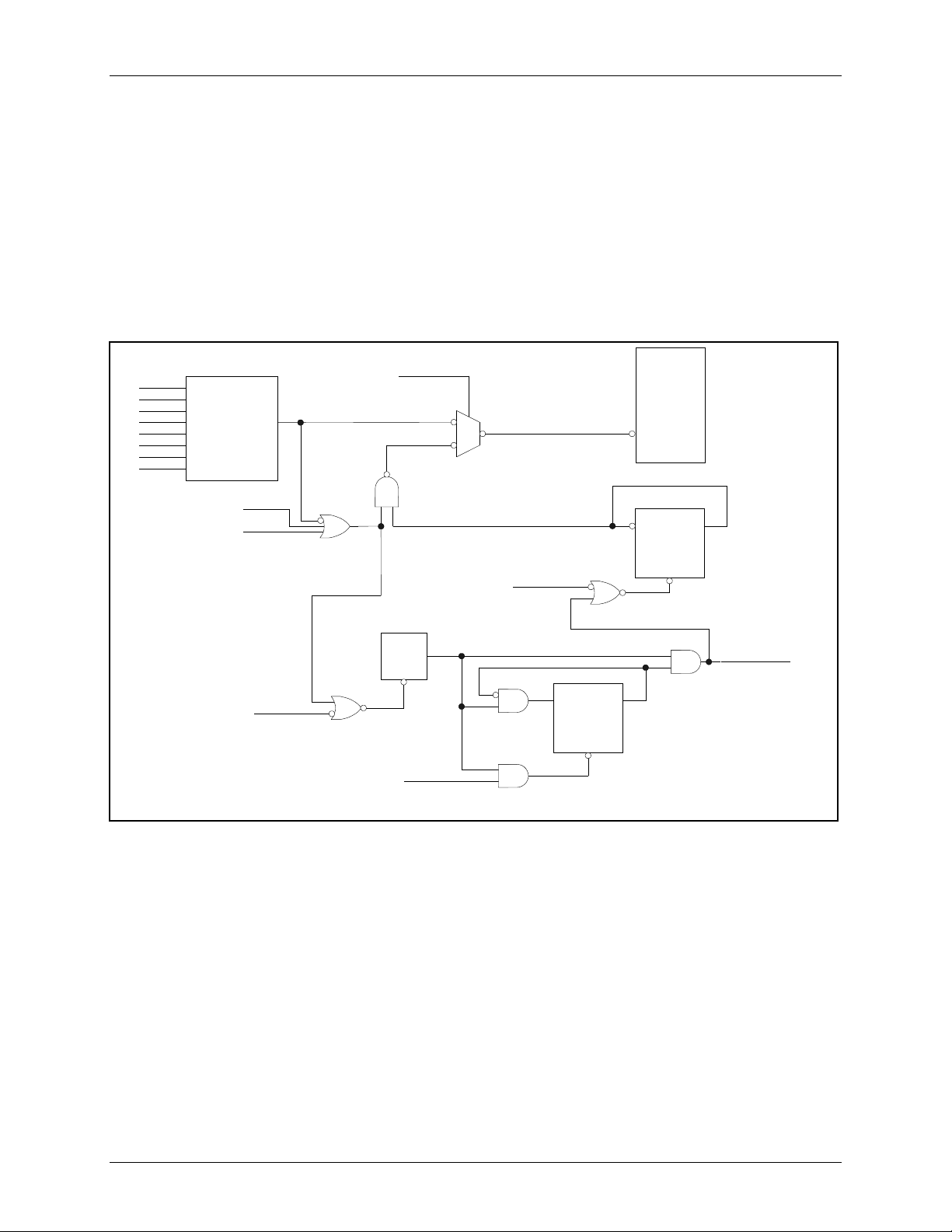

VCO

Phase

Freq

DET

CPU CLOCK

DIVIDER

6 bits

MCLK

96MHz

1.5-48MHz

MPU CLOCK - CPCLK

SMART CARD LOGIC

BLOCK CLOCK

SCCLK

SCLK

CLOCK

Prescaler 6bits

SC/SCE

CLOCK

Prescaler 6bits

SEL

ETU CLOCK

DIVIDER

12 bits

CPUCKDiv

See SC Clock descriptions for m ore accurate diagram

ETUCLK

MCount(2:0)

KEYCLK

I2CCLK

1kHz

400kHz

DIVIDE

by 120

DIVIDER

/93760

HIGH

XTAL

OSC

X12IN

X12OUT

M DIVIDER

/(2*N + 4)

HCLK

HOSCen

12.00MHz

12.00MHz

div 2

ICLK

SCCKenb

SELSC

DIVIDE

by 96

CLK1M

1MHz

7.386MHz

7.386MHz

3.6923MHz

I2C_2x

800kHz

div 2

SCECLK

div 2

div 2

All ports on the chip are bi-directional. Each consists of a Latch (SFR ‘USR70’), an output driver, and an

input buffer, therefore the MPU can output or read data through any of these ports if they are not used for

alternate purposes.

1.6 Instruction Set

All instructions of the generic 8051 microcontroller are supported. A complete list of the instructi on set

and of the associated op-codes is contained in the 73S12xxF Software User’s Guide.

1.7 Peripheral Descriptions

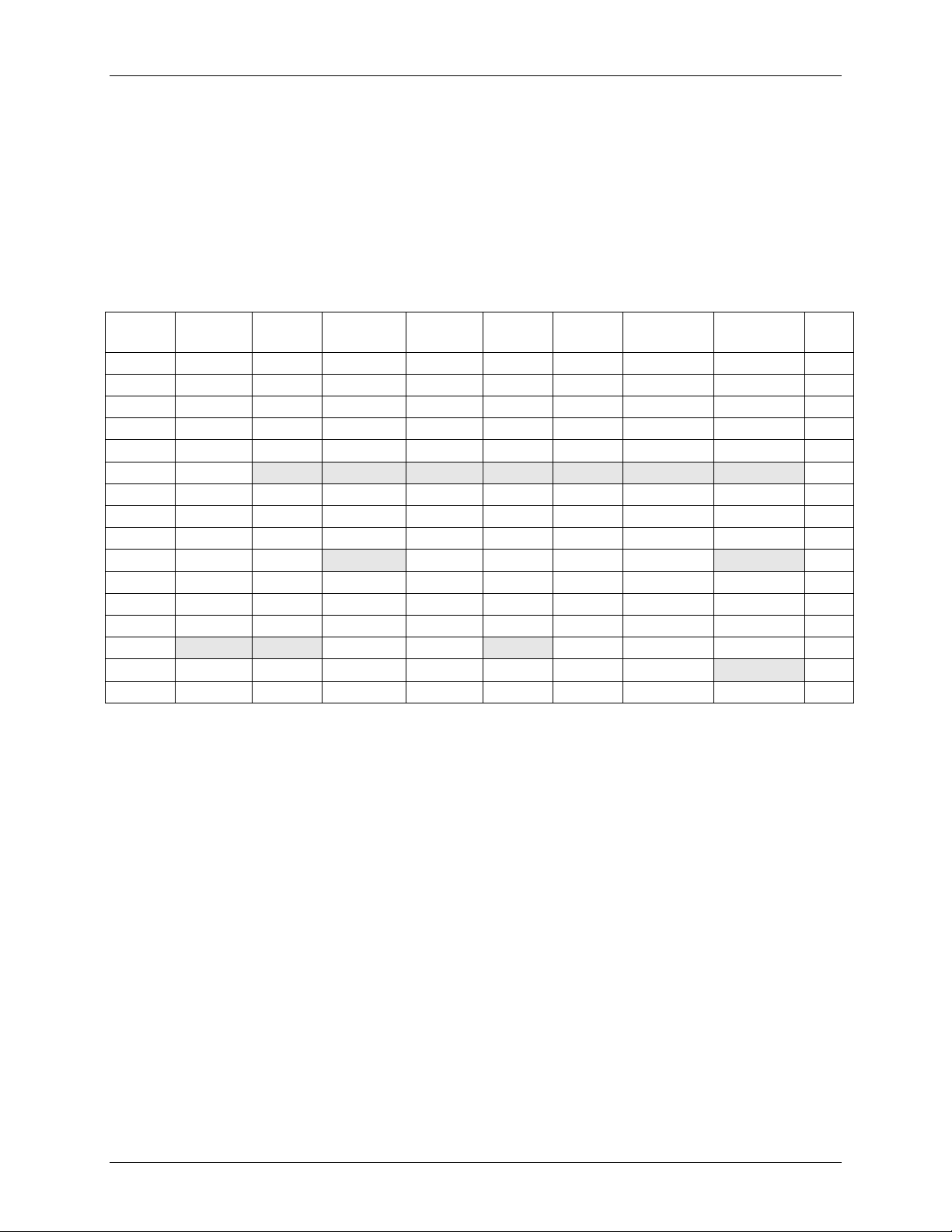

1.7.1 Oscillator and Clock Generation

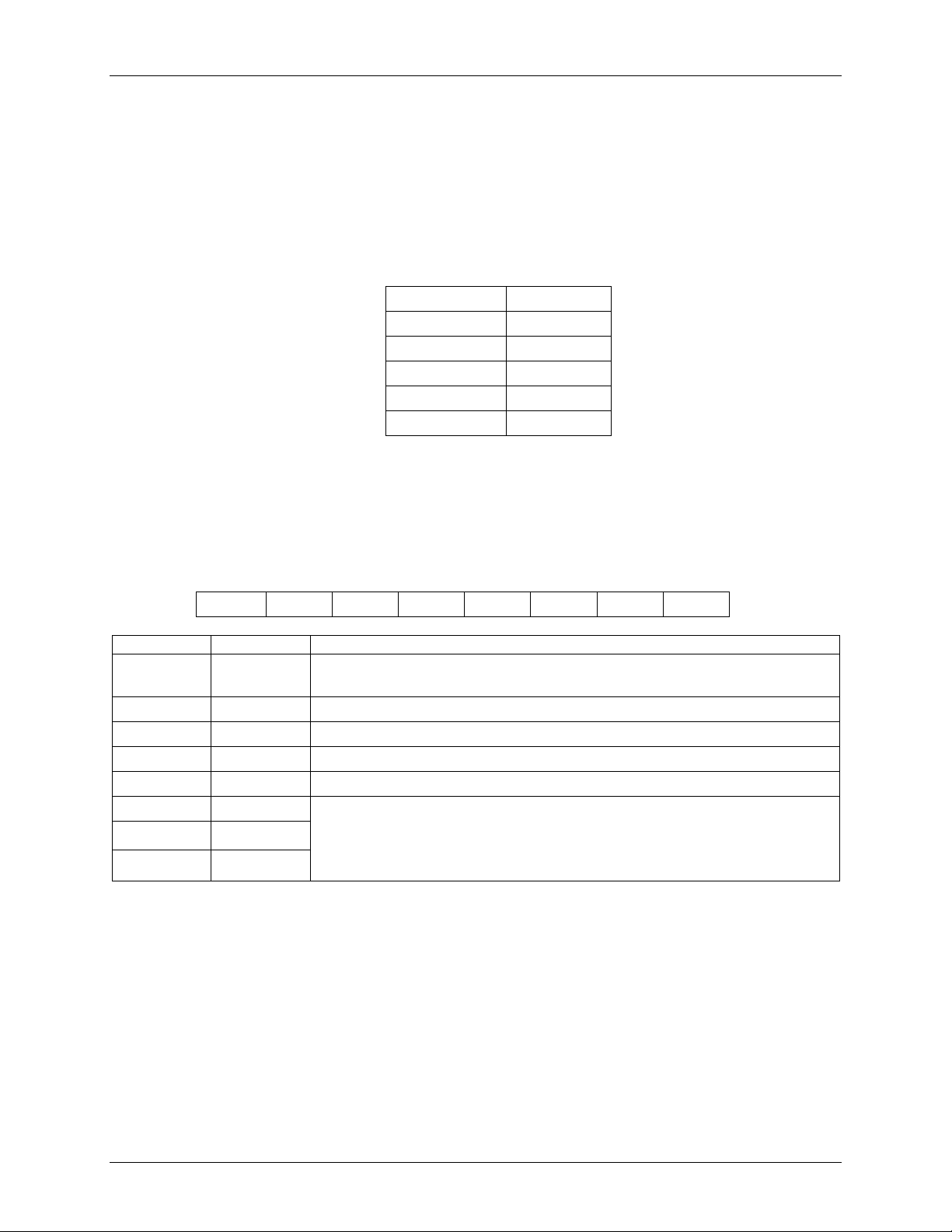

The 73S1210F has one oscillator circuit for the main CPU clock. The main oscillator circuit is designed to

operate with various crystal or external clock frequencies. An internal divider working in conjunction with a

PLL and VCO provides a 96MHz internal clock within the 73S1210F. 96 MHz is the recommended

frequency for proper operation of specific peripheral blocks such as the specific timers, ISO 7816 UART

and interfaces, Step-up converter, and keypad. The clock generation and control circuits are shown in

Figure 3.

22 Rev. 1.4

Figure 3: Clock Generation and Control Circuits

Page 23

DS_1210F_001 73S1210F Data Sheet

Bit

Symbol

Function

The master clock control register enables different sections of the clock circuitry and specifies the value

of the VCO Mcount divider. The MCLK must be configured to operate at 96MHz to ensure proper

operation of some of the peripheral blocks according to the following formula:

MCLK = (Mcount * 2 + 4) * F

= 96MHz

XTAL

Mcount is configured in the MCLKCtl register must be bound between a value of 1 to 10. The possible

crystal or external clock frequencies for getting MCLK = 96MHz are shown in Table 11.

Table 11: Frequencies and Mcount Values for MCLK = 96MHz

F

(MHz) Mcount (N)

XTAL

12.00 2

9.60 3

8.00 4

6.86 5

6.00 6

Master Clock Control Register (MCLKCtl): 0x8F

0x0A

The MPU clock that drives the CPU core defaults to 3.6923MHz after reset. The MPU clock is scalable

by configuring the MPU Clock Control register.

Table 12: The MCLKCtl Register

MSB LSB

HSOEN KBEN SCEN – – MCT.2 MCT.1 MCT.0

MCLKCtl.7 HSOEN

High-speed oscillator disable. When set = 1, disables the high-speed

crystal oscillator and VCO/PLL system. Do not set this bit = 1.

MCLKCtl.6 KBEN 1 = Disable the keypad logic clock.

MCLKCtl.5 SCEN 1 = Disable the smart card logic clock.

MCLKCtl.4 –

MCLKCtl.3 –

MCLKCtl.2 MCT.2 This value determines the ratio of the VCO frequency (MCLK) to the

MCLKCtl.1 MCT.1

MCLKCtl.0 MCT.0

high-speed crystal oscillator frequency such that:

MCLK = (MCount*2 + 4)* F

. The default value is MCount = 2h such

XTAL

that MCLK = (2*2 + 4)*12.00MHz = 96MHz.

Rev. 1.4 23

Page 24

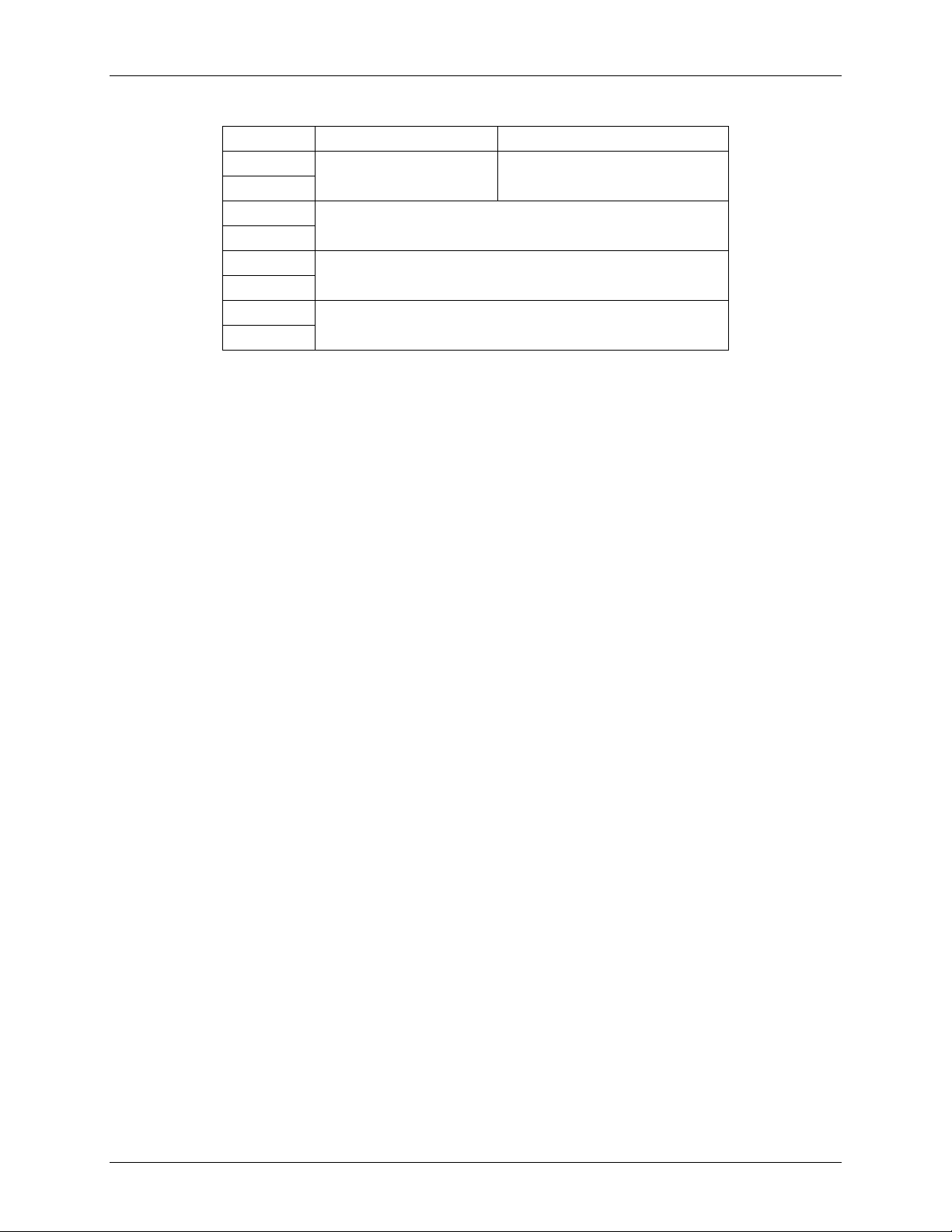

73S1210F Data Sheet DS_1210F_001

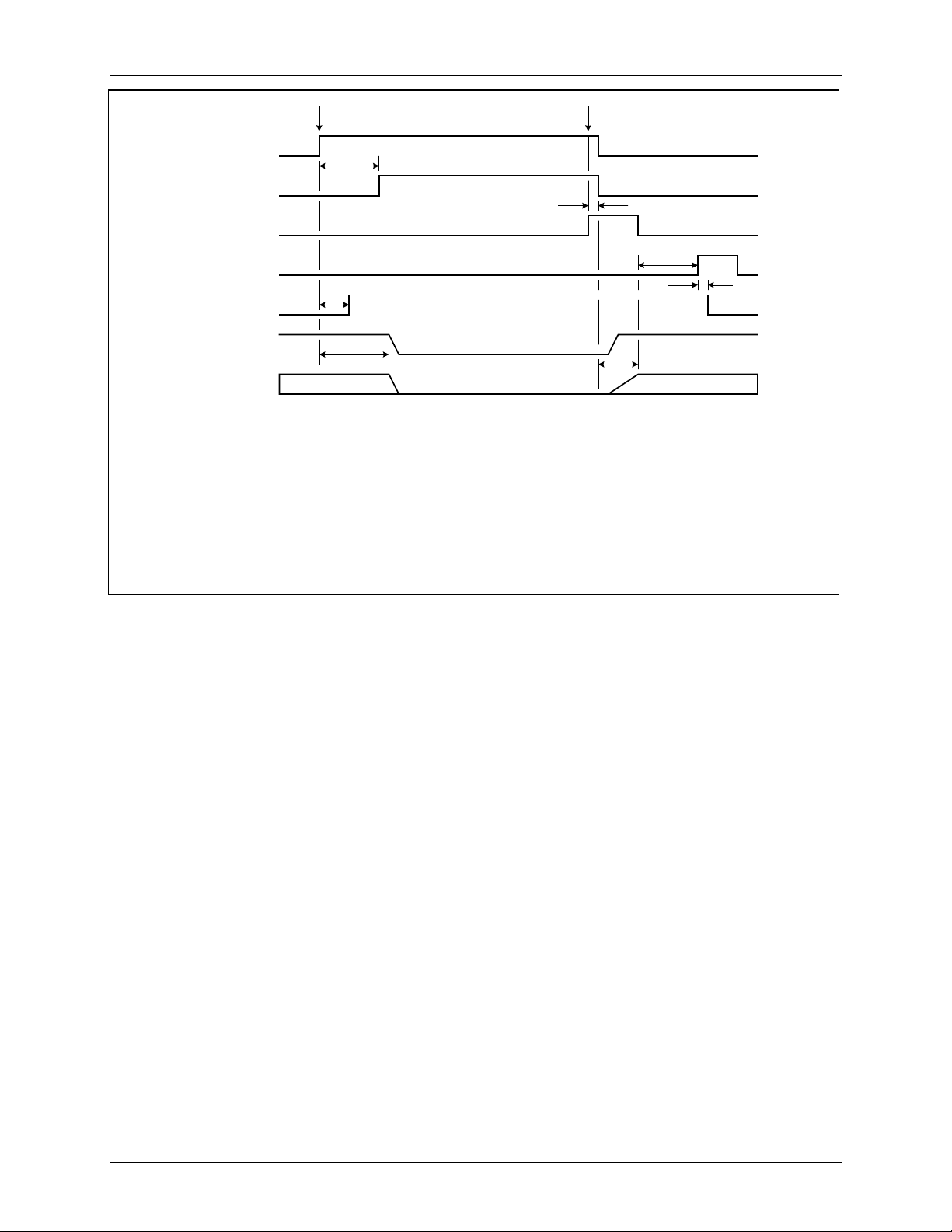

Bit

Symbol

Function

73S1210F

X12IN

X12OUT

12MHz

22pF 22pF

1MΩ

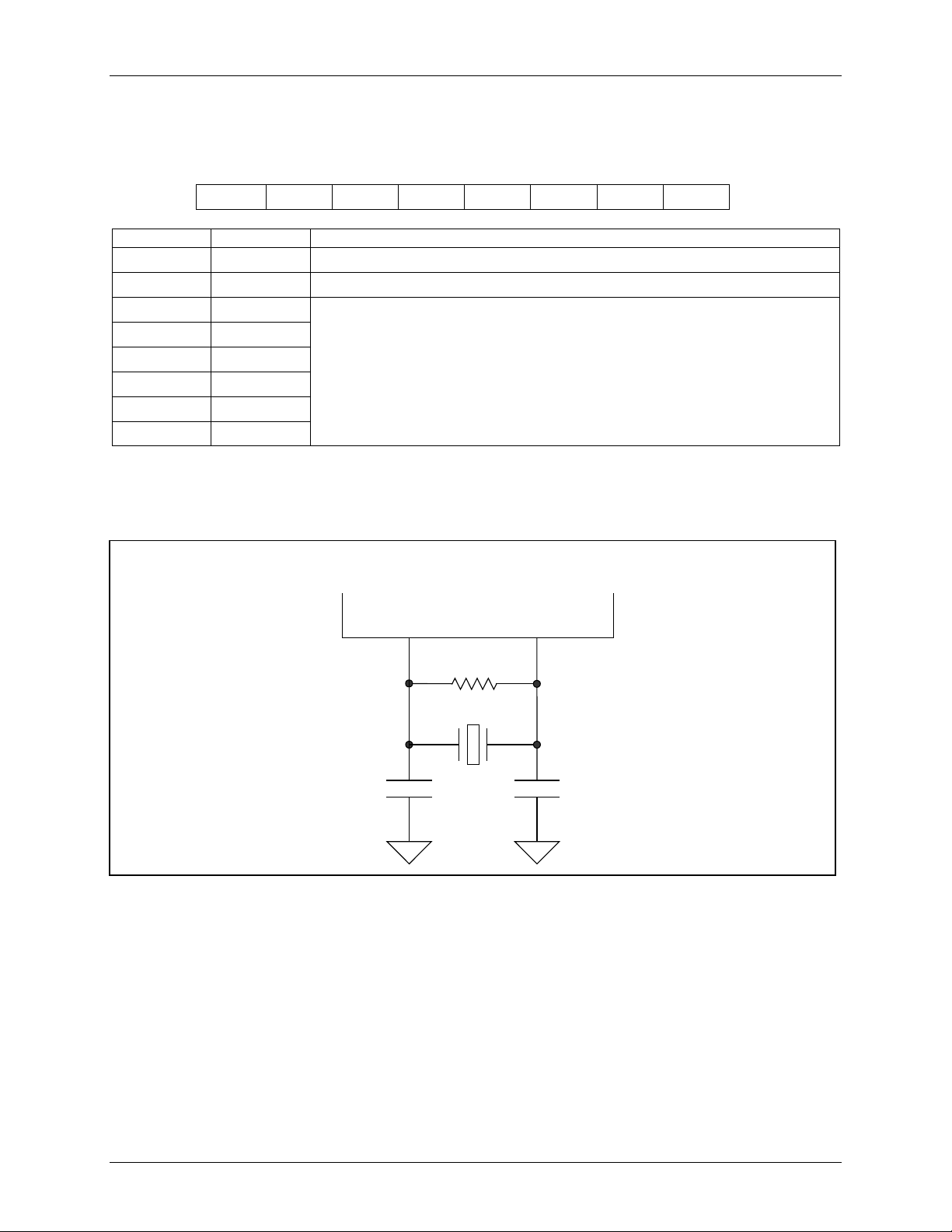

MPU Clock Control Register (MPUCKCtl): 0xFFA1 0x0C

Table 13: The TCON Register

MSB LSB

– – MDIV.5 MDIV.4 MDIV.3 MDIV.2 MDIV.1 MDIV.0

MPUCKCtl.7 –

MPUCKCtl.6 –

MPUCKCtl.5 MDIV.5

MPUCKCtl.4 MDIV.4

MPUCKCtl.3 MDIV.3

MPUCKCtl.2 MDIV.2

MPUCKCtl.1 MDIV.1

MPUCKCtl.0 MDIV.0

The oscillator circuits are designed to connect directly to standard parallel resonant crystal in a Pierce

oscillator configuration. Each side of the crystal should include a 22pF capacitor to ground for both

oscillator circuits and a 1MΩ resistor is required across the 12MHz crystal.

This value determines the ratio of the MPU master clock frequency to the

VCO frequency (MCLK) such that

MPUClk = MCLK/(2 * (MPUCKDiv(5:0) + 1)).

Do not use values of 0 or 1 for MPUCKDiv(n).

Default is 0Ch to set CPCLK = 3.6923MHz.