Page 1

TSC130BEF0

September

Page 2

123

Page 3

Page 4

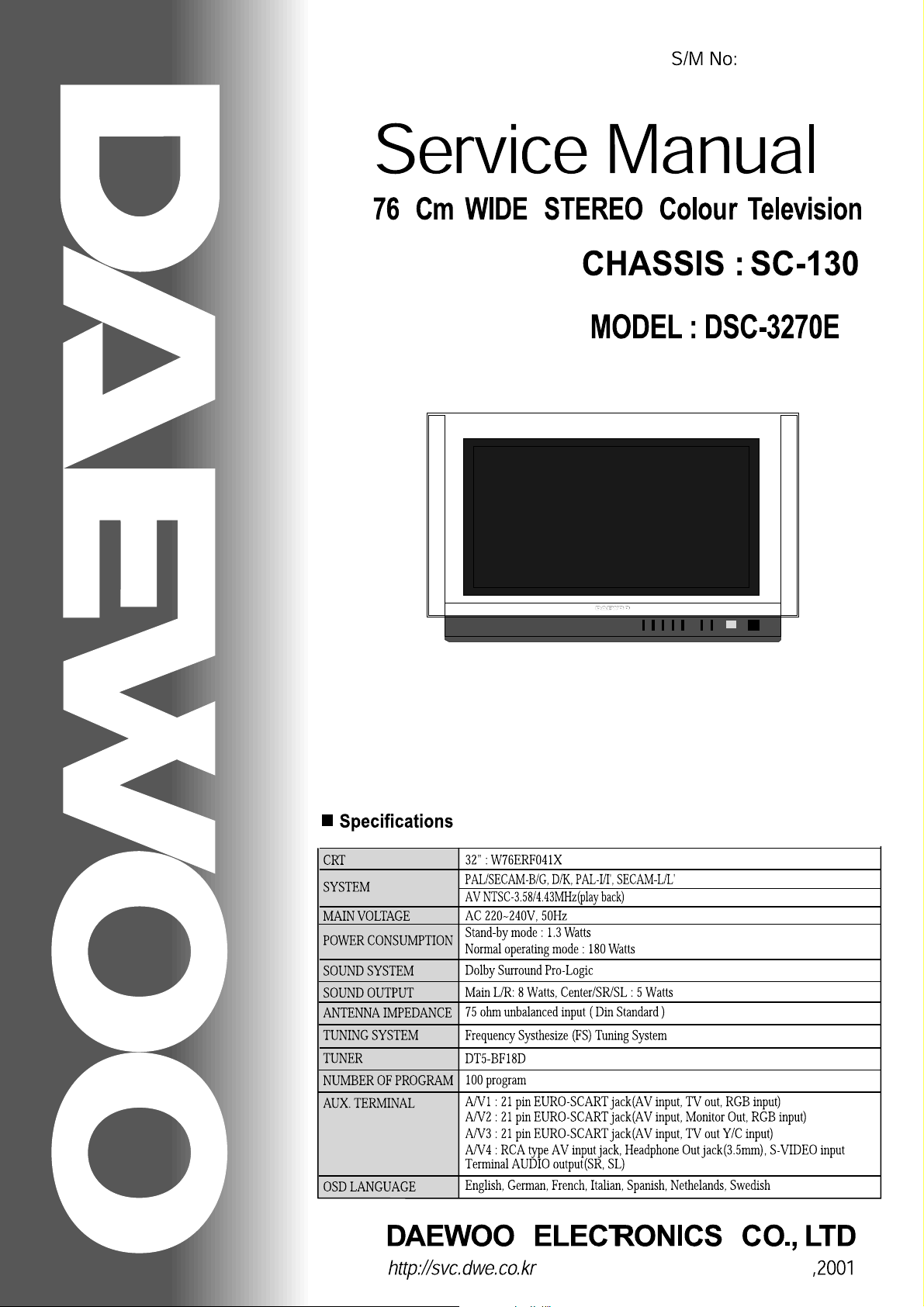

2. Specifications

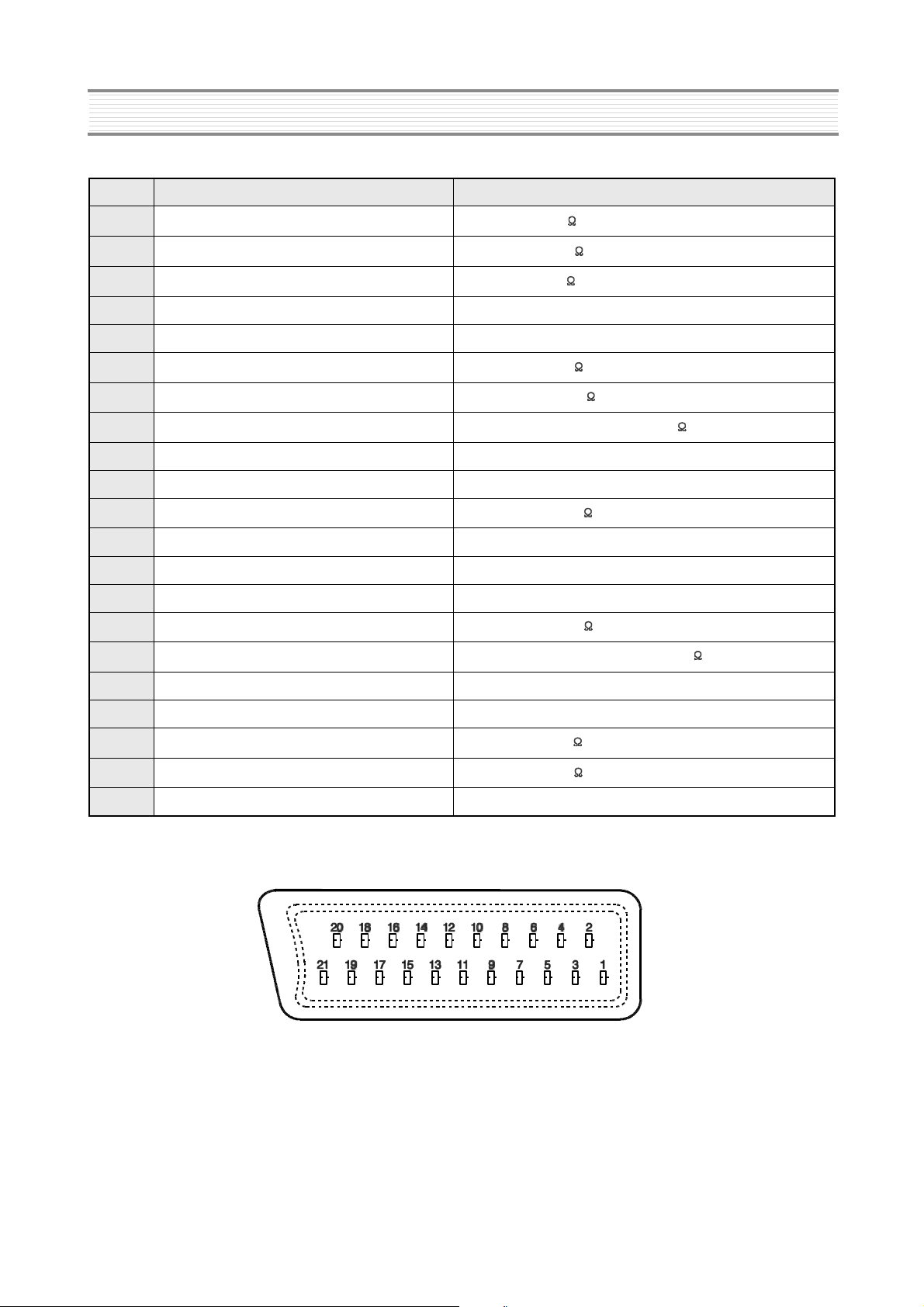

PIN Signal Designation Matching Value

1 Audio Out (linked with 3)

2 Audio In (linked with 6)

3 Audio Out (linked with 1)

4 Audio Earth

5 Blue Earth

6 Audio in (linked with 2)

7 Blue in

8 Slow (Function) Switching

9 Green Earth

10 NC

11 Green In

12 NC

13 Red Earth

14 Rapid(Blanking) Switching Earth

15 Red In, C In

16 Rapid(Blanking) switching

0.5Vrms, Imp < 1 k (RF 60% MOD)

0.5Vrms, Imp < 10 k

0.5Vrms, Imp < 1 k (RF 60% MOD)

0.5Vrms, Imp < 10 k (RF 60% MOD)

+

0.7Vpp 2dB, Imp 75

-

TV : 0-2V, PERI : 9.5 - 12V, Imp > 10 k

+

0.7Vpp 2dB, Imp 75

-

+

0.7Vpp 2dB, Imp 75

-

Logic 0 : 0 - 0.4V, Logic 1 : 1 - 3V, Imp 75

17 Video Earth

18 Rapid Blanking Earth

19 Video Out

20 Video In, Y In

21 Common Earth

+

1Vpp 2dB, Imp 75

-

+

1Vpp 2dB, Imp 75

-

Page 5

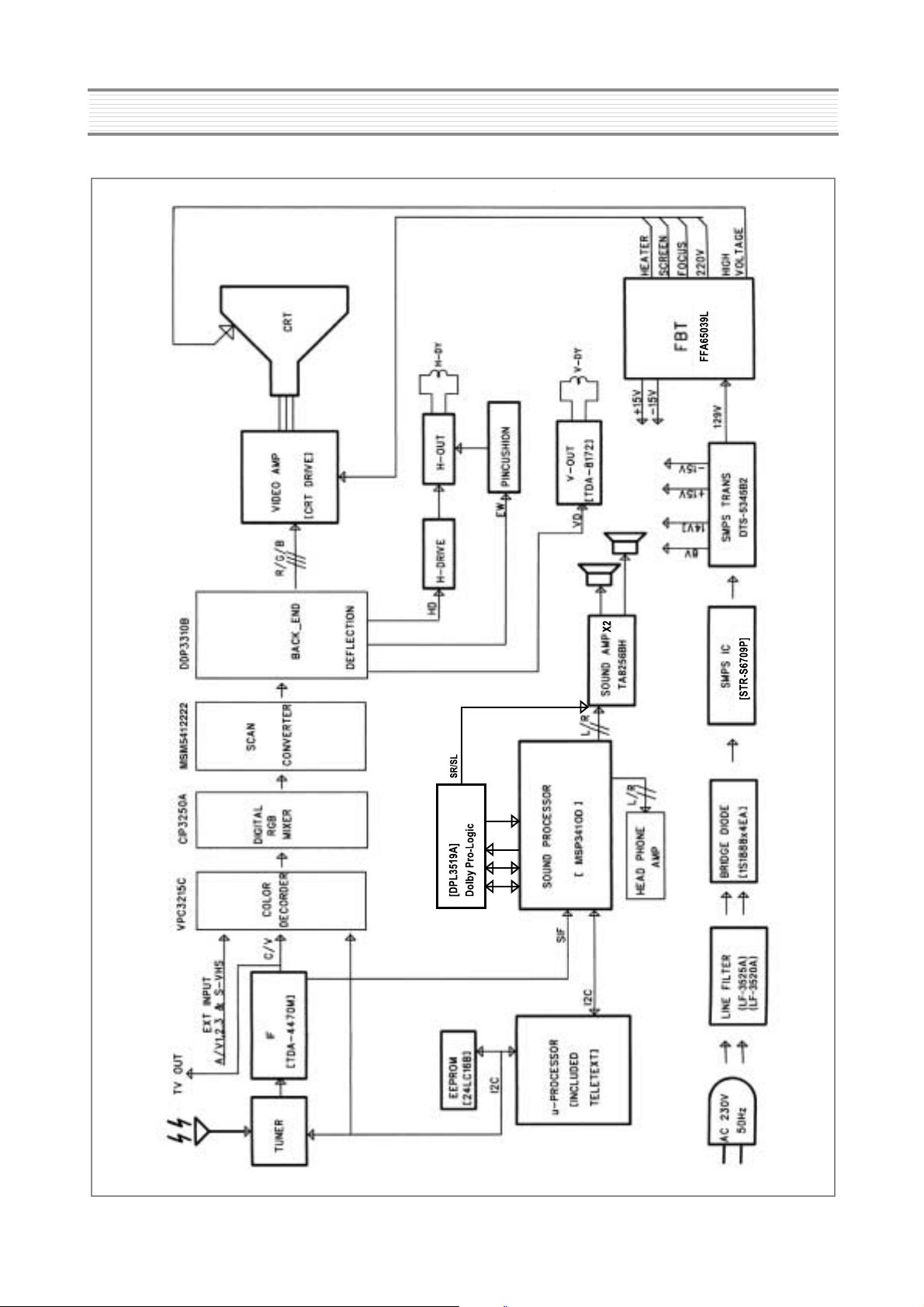

3. Circuit Block Diagram

4

Page 6

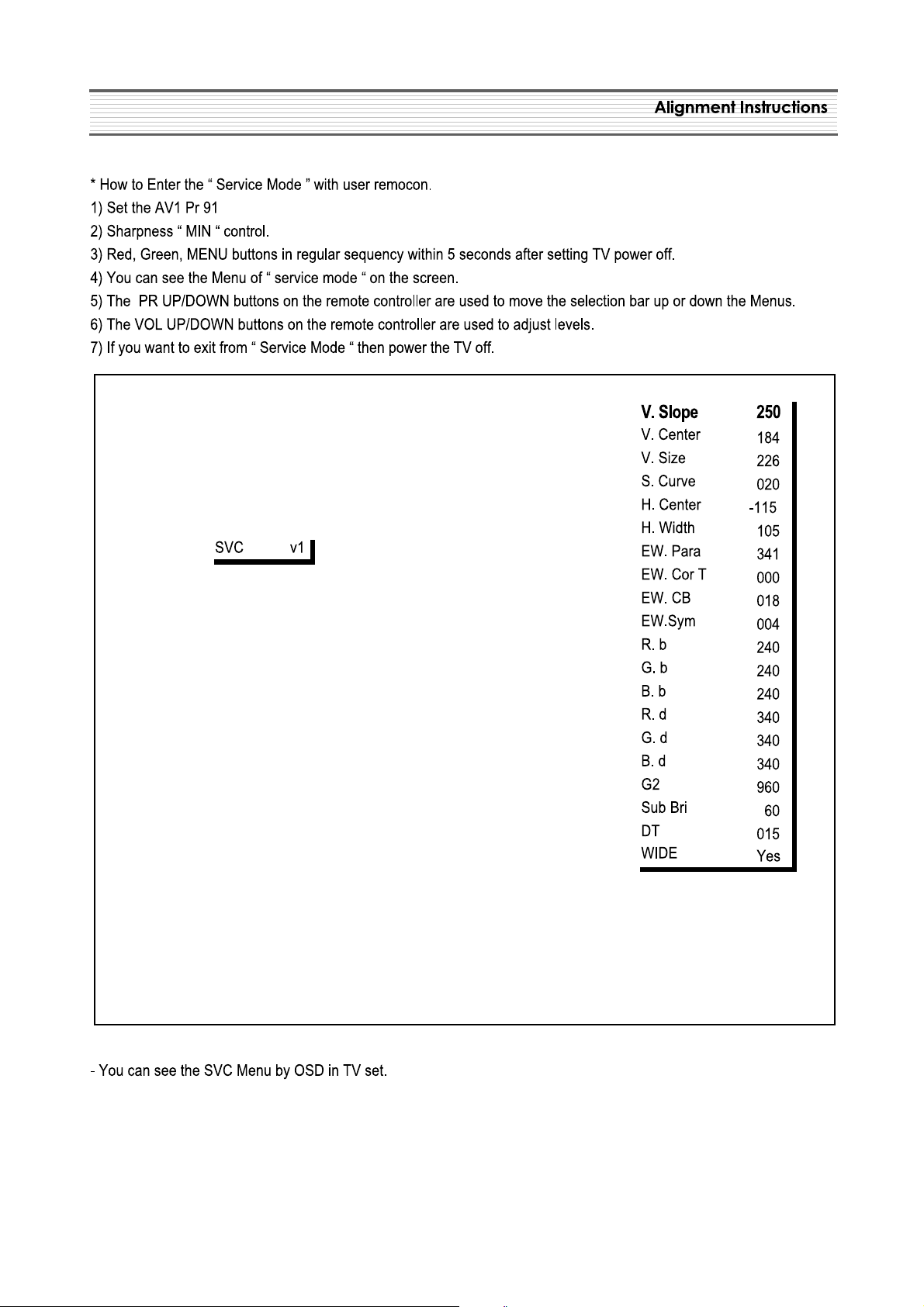

5. Alignment Instructions

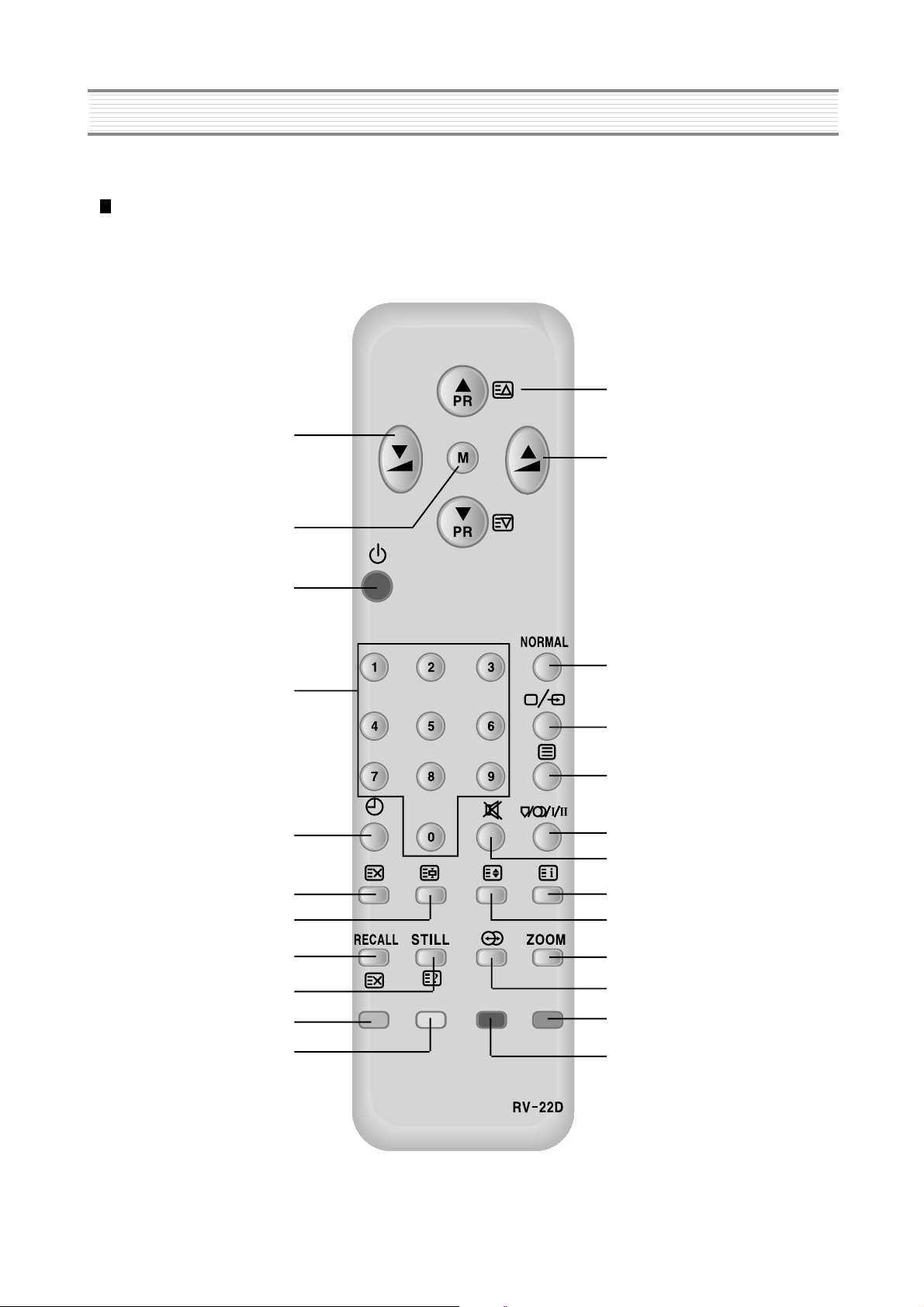

4-1. User Remocon

RV-22D

TV..........................TXT

VOLUME........VOLUME

DOWN DOWN

(CURSOR

LEFT)

MENU.................MENU

POWER...........POWER

PR.......................PAGE

NUMBER NUMBER

0-9 0-9

TV..............................TXT

PR UP...............PAGE UP

VOLUME UP

(CURSOR

RIGHT)

NORMAL.................Not used

AV............................Not used

....

VOLUME UP

SLEEP............Not used

Not used.........CANCEL

Not used.............HOLD

RECALL.......SUBP AGE

STILL..............REVEAL

Not used.....................R

Not used....................G

TXT...................................TV

SOUND MODE.......Not used

MUTE..........................MUTE

Not used........................SIZE

Not used........................SIZE

ZOOM.....................Not used

EFFECT..................Not used

Not used..............................C

Not used..............................Y

5

Page 7

678

Page 8

Page 9

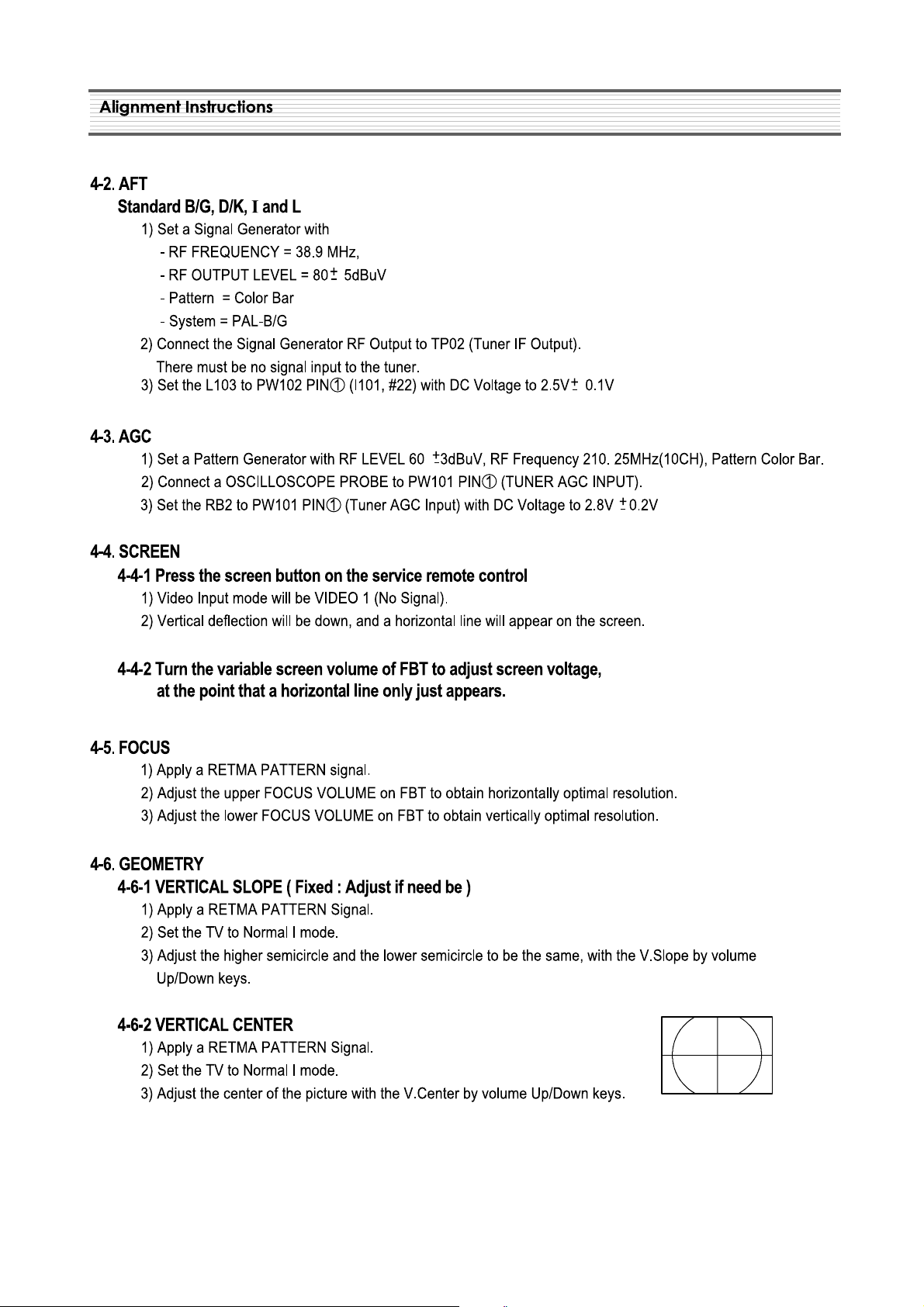

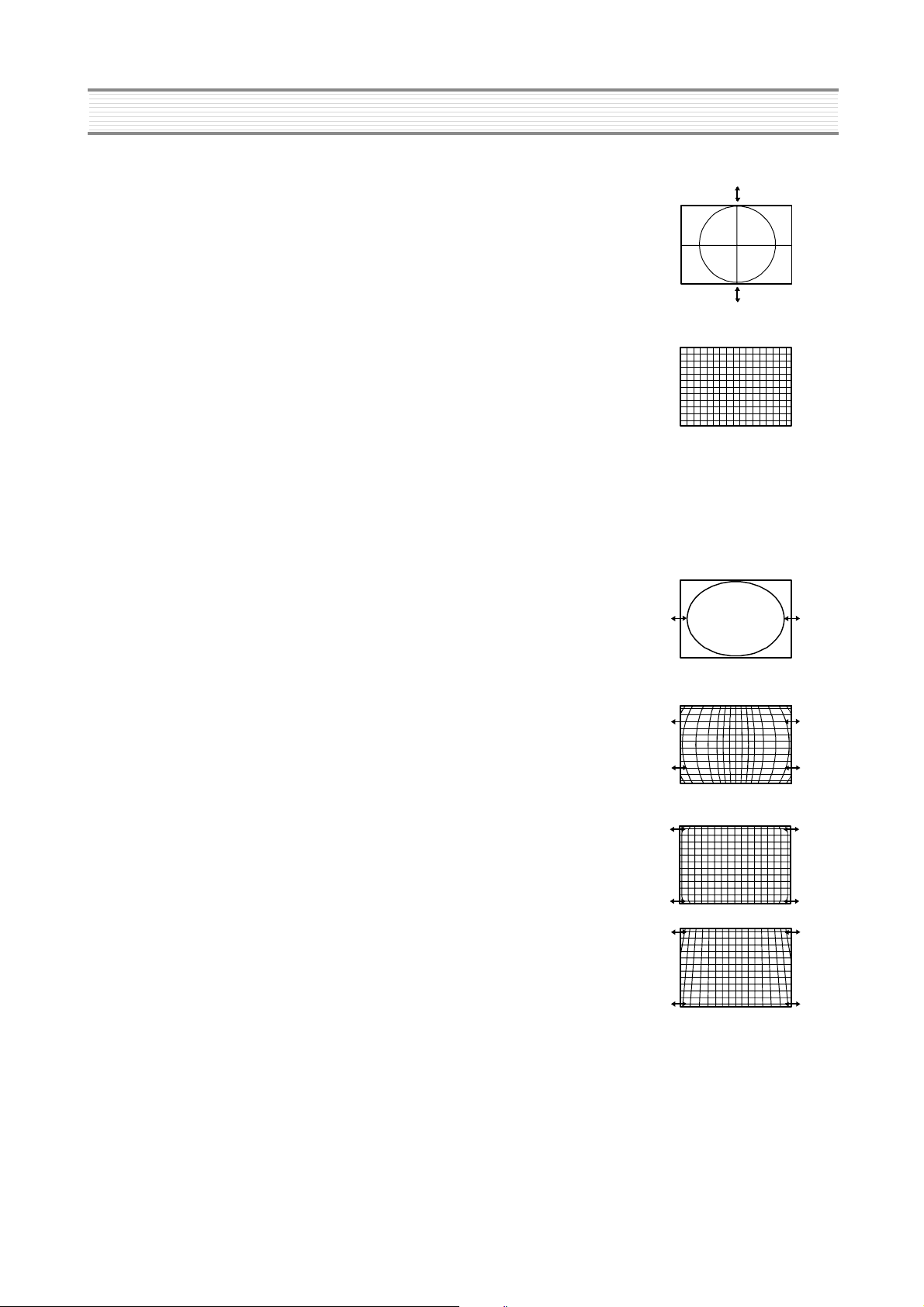

4-6-3 VERTICAL SIZE

* The VERTICAL CENTER adjustment has to be done in advance.

1) Apply a RETMA PATTERN Signal.

2) Set the TV to Normal I mode.

3) Adjust the VERTICAL SIZE of the picture with the select V.size by

volume UP/DOWN keys.

4-6-4 VERTICAL S-CORRECTION ( Fixed : Adjust if need be )

1) Apply a CROSSHATCH PATTERN Signal.

2) Adjust the S-CORRECTION to obtain the same distance between

horizontal lines with the S.Curve by volume UP/DOWN keys.

4-6-5 HORIZONTAL CENTER

1) Apply a RETMA PATTERN Signal.

2) Adjust picture centering with the select H.Center by volume UP/DOWN keys.

Alignment Instructions

4-7. EW

4-7-1 WIDTH

1) Apply a RETMA PATTERN Signal.

2) Adjust the horizontal width to make a perfect circle with the select H.Width

by volume UP/DOWN keys.

4-7-2 PARA

1) Apply a CROSSHATCH PATTERN Signal.

2) Adjust the vertical line to straight with the select E.W Para by volume

UP/DOWN keys.

4-7-3 CORNER ( Fixed : Adjust if need be )

1) Apply a CROSSHATCH PATTERN Signal.

2) Adjust the vertical line to straight with the select EW.Cor T by volume

UP/DOWN keys.

4-7-4 SYMMETRY ( Fixed : Adjust if need be )

1) Apply a CROSSHATCH PATTERN Signal.

2) Turn R451 to the maximum left.

3) Adjust the symmetrical balance to be suitable with the select EW Sym by

volume UP/DOWN keys.

Page 10

Alignment Instructions

4-8. WHITE BALANCE

4-8-1 RGB Reference R

2

4-8-2 Beam Reference LOW ( 288, 301 : 10Cd/ )

HIGH ( 288, 301 : 10Cd/ )

m

m

2

4-8-3 Adjust G, B Gain with select Menu G,B of BIAS, DRIVE of select Menu so that R, G, B Bars

are on the center position of the analog meter. If R Analog meter is not on center, control

the Brightness +/- of user Remocon so as R Analog meter to be on the center position.

4-9. SUB BRIGHT

4-9-1 Pattern : Retma

4-9-2 Adjust the SUB BRIGHT with the select Sub Bri by volume UP/DOWN keys.

so that only H-Center parts of picture can be seen.

4-10. DOUBLE TEXT CENTER

4-10-1 Pattern : Pattern RED

4-10-2 Select Menu

4-10-3 Select DT in SVC menu time to see the Double Text Picture.

( Left : RF Picture, Right : Text Picture )

4-10-4 Change the Double Text control keys volume UP/DOWN keys so that the left edge of text

picture concur with the right edge of RF picture.

9

Page 11

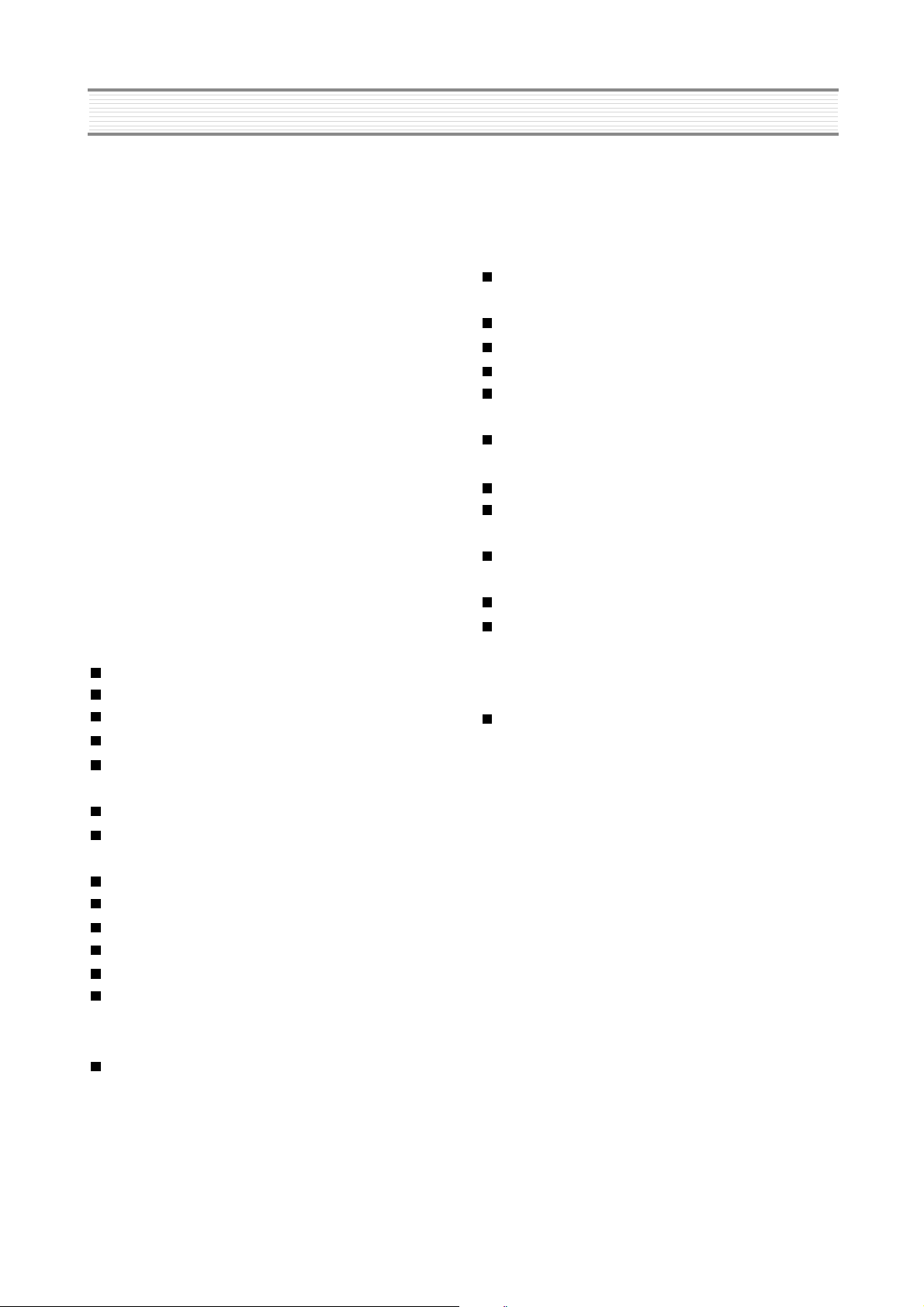

5. IC description

5-1. ST92195

(1) General Description

1.1 INTRODUCTION

The ST92195 microcnontoller is developed and manufac-

tured by STMicroelecrtonics using a proprietary n-well

HCMOS process. Its performance derives from the use of

a flexible 256-register programming model for ultra-fast

context switching and real-time event response. The intel-

ligent onchip peripherals offload the ST9 core from I/O

and data management processing tasks allowing critical

application tasks to get the maximum use off core

resources. The ST92195 MCU supports low power con-

sumption and low voltage operation for power-efficient

and low-cost embedded systems.

1.1.1 ST9+Core

The advanced Core consists of the Central Processing

Unit (CPU), the Register File and the Interrupt controller.

The general-purpose registers can be used as accumula-

tor, Index register, or address pointers. Adjacent register

pairs make up 16-bit registers for addressing or 16-bit

processing. Although the ST9 has an 8-bit ALU, the chip

handles 16-bit operations, including arithmetic, loads/

stores, and memory/register and memory/memory

exchanges. Two basic memory spaces are available :

Program Memory and the Register File, Which includes

the control and status registers of the on-chip peripherals.

1.1.2 Power Saving Modes

To optimize performance versus power consumption, a

range of operating modes can be dynamically selected.

Run Mode.

CPU and peripherals running at the maximum clock

speed delivered by the phase Locked Loop(PLL) of the

Clock Control Unit(CCU).

Wait For Interrupt Mode.

rupt(WFI) instruction suspends program execution until

an interrupt request is acknowledged. During WFI, the

CPU clock is halted while the peripheral and interrupt

controller keep running at a frequency programmable via

the CCU. In this mode, the power consumption of the

device can be reduced by more than 95%(LP WFI).

Wait For Interrupt Mode.

rupt(WFI) instruction, and if the Watchdog is not enable,

the CPU and its peripherals stop operation and the I/O

This is the full speed execution mode with

The Wait For Inter-

The Wait For Inter-

ports enter high impedance mode. A reset is necessary to

exit from Halt mode.

1.1.3 I/O Ports

Up to 28 I/O lines are dedicated to digital Input/Output.

These lines are grouped into up to five I/O Ports and can

be configureed on a bit basis under software control to pro-

vide timing, status signals, timer and output, analog inputs,

external interrupts and serial or parallel I/O.

1.1.4 TV Peripherals

A set of on-chip peripherals form a complete system for TV

set and VCR applications:

- Voltage Synthesis

- VPS/WSS Slicer

- Teletext Slicer

- Teletext Display RAM

- OSD

1.1.5 On Screen Display

The human interface is provided by the On Screen Display

module, this can produce up to 26 lines of up to 80 characters from a ROM defined 512 character set. The character

resolution is 10x10 dot. Four character sizes are supported. Serial attributes allow the user to select foreground

and background. Parallel attributes can be used to select

additional foreground and background colors and underline

on a character by character basis.

1.1.6 Teletext and Display RAM

The internal 8k Teletext and Display storage RAM can be

used to store Teletext pages as well as Display parame-

ters.

1.1.7 Teletext, VPS and WSS Data Slicers

The three on-board data slicers using a single external

crystal are used to extract the Teletext, VPS and WSS

information from the video signal. Hardware Hamming

decoding is provided.

1.1.8 Voltage Synthesis Tuning Control

14-bit Voltage Synthesis using the PWM (Pulse Width

Modulation)/BRM (Bit Rate Modulation) technique can be

used to genetate tuning voltages for TV set applications.

The tuning voltage is output on one of two separate output

pins.

10

Page 12

IC description

1.1.9 PWM Output

Control of TV settings is able to be made with up to eight

8-bit PWM outputs, with a frequency maximum of

23,437Hz at 8-bit resolution(INTCLK=12 MHz). Low reso-

lutions with higher frequency operation can be programmed.

1.1.10 Serial Peripheral Interface (SPI)

The SPI bus is used to communicate with external

devices via the SPI, or bus communication standards. The SPI uses one or two lines for serial data and a

synchronous clock signal.

2

I C

1.1.11 Standard Timer (STIM)

The Standard Timer includes a programmable 16-bit

down counter and an associated 8-bit prescaler with Sin-

gle and Continuous counting modes.

1.1.12 Analog/Digital Converter (ADC)

In addition there is a 3 channel Analog to Digital Converter with integral sample and hold, fast 5.7us conver-

sion timer and 6-bit guaranteed resolution.

(2) Feature

Register File based 8/16 bit Core Architecture with

RUN, WFI, SLOW and HALT modes

to operating temperature range

0 CO70 C

Up to 24 MHz Operation @5V 10%

Minimum instruction cycle time : 375ns at 16MHz internal clock

64K Bytes ROM

256 Bytes RAM of Register file(accumulator or index

registers)

256 Bytes of on-chip static RAM

8K Bytes of TDSRAM(Teletext and Display RAM)

56-lead Shrink DIP package

28 fully programmable I/O pins

Serial Peripheral Interface

Flexible Clock controller for OSD, Data Slicer and Core

clocks running from one single low frequency external

crystal.

Enhanced Display Controller with 26 rows of 40/80

characters

- Serial and Parallel attributes

- 10x10 dot Matrix, 512 ROM characters, definable by

user

- 4/3 and 16/9 supported

O

_

+

- Rounding, fringe, double width, double height,

scrolling, cursor, full background colour,

semitransparent mode and reduced intensity colour

supported

Teletext unit, including Data slicer, Acquisition Unit and

up to 8K Bytes RAM for Data Storage

VPS and Wode Screen Signalling slicer

Integrated Sync Extractor and Sync Controller

14-bit Voltage Synthesis for tuning reference voltage

Up to 6 external interrupts plus 1 non-maskable inter-

rupt

8x8-bit programmable PWM outputs with 5V open-

drain or push-pull capability

16-bit Watchdog timer with 8-bit prescale

16-bit standard timer with 8-bit prescaler usable as a

Watchdog timer

3-channel Analog-to-Digital converter ; 6-bit guaranteed

Rich instruction set and 14-Addressing modes

Versatile Development Tools, including Assembler,

Linker, C-compiler, Archiver, Source Level Debugger

and Hardware Emulators with Real-Time Operating

System available from third parties

Piggyback board available for prototyping

11

Page 13

(3) Block Diagram

IC description

12

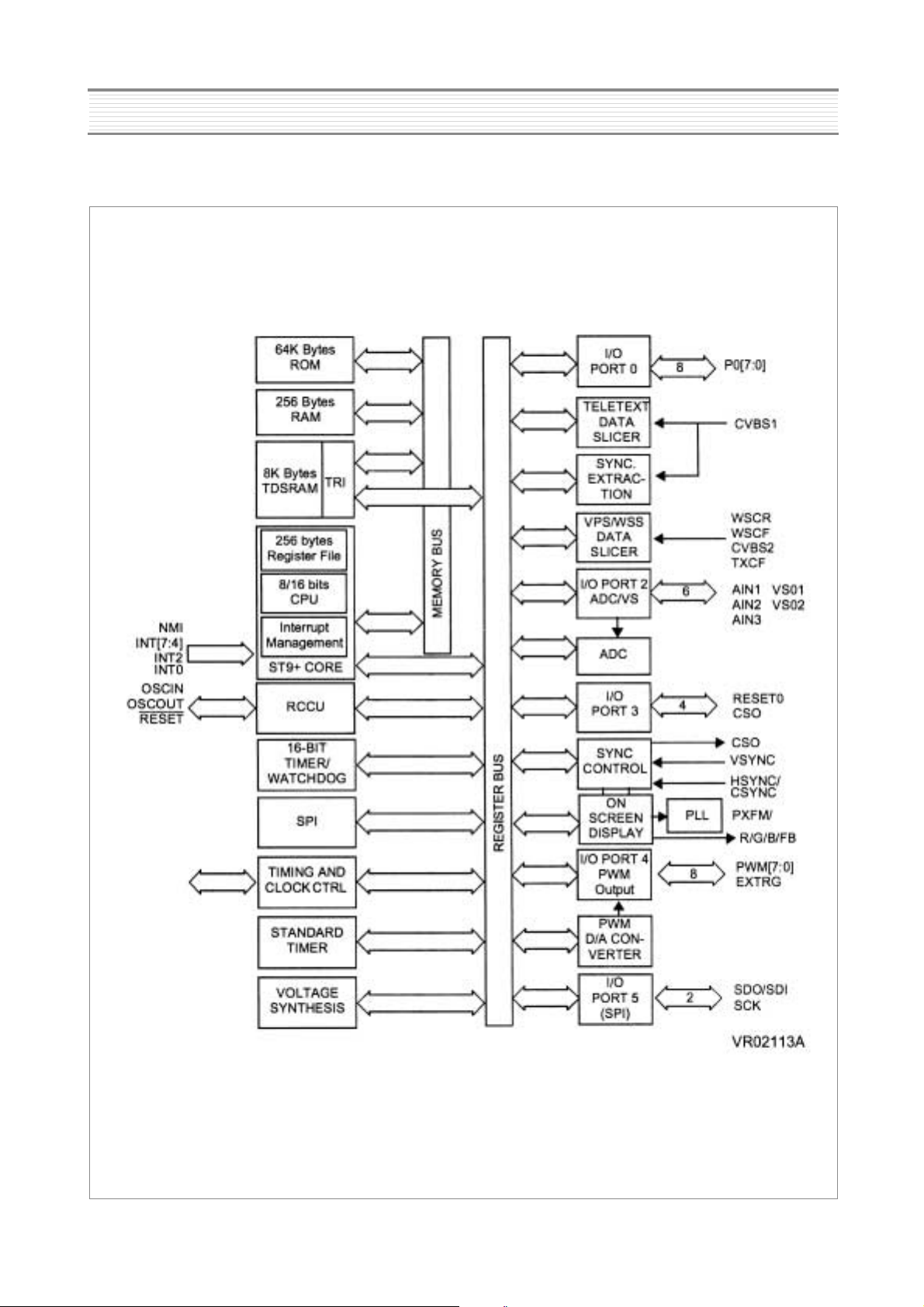

Page 14

IC description

(4) PIN DESCRIPTION

RESET Reset (input, active low). The ST9+ is initialised

by the Reset signal. With the deactivation of RESET,

program execution begins from the Program memory

location pointed to by the vector contained in program

memory locations 00h and 01h.

R/G/B Red/Green/Blue. Video color analog DAC out-

puts

FB Fast Blanking. Video analog DAC output.

VOD Main power supply voltage(5V 10%, digital)

WSCF, WSCR Analog pins for the VPS/WPP slicer line

PLL.

MCFM Analog pin for the display pixel frequency multiplier.

OSCIN, OSCOUT Oscillator (input and output).

These pins connect a parallel-resonant crystal(24MHz

maximum), or an external source to the on-chip clock

oscillator and buffer. OSCIN is the input of the oscilltor

inverter and internal clock generator; OSCOUT is the

HYNC/CSYNC Horizontal/Composite sync. Horizontal

or composite video synchronisation input to OSD. Positive or negativety.

PXFM Analog pin for the Display Pixel Frequency Multiplier

AVDD Analog VDD of PLL. This pin must be tied to

VDD externally to the ST92195.

GND Digital circuit ground.

AGND Analog circuit ground(must be tied externally to

digital GND).

CVBS1 Composite video input signal for the Teletext

slicer and sync extraction.

CVBS2 Composite video input signal for the VPS/WSS

slicer. Pin AC coupled.

AVDD1, AVDD2 Analog power supplies(must be tied

externally to AVDD).

TXCF Analog pin for the VPS/WSS line PLL.

CVBSO, JTDO, JTCK Test pins : leave floating.

output of the oscillator inverter.

VSYNC Vertical Sync. Vertical video synchronisation

input to OSD. Positive or negative polarity.

Figure 2. Pin Description

JTMS, TEST0 Test pins : must be tied to AVDD2.

JTRST0 Test pin : must be tied to GND.

13

Page 15

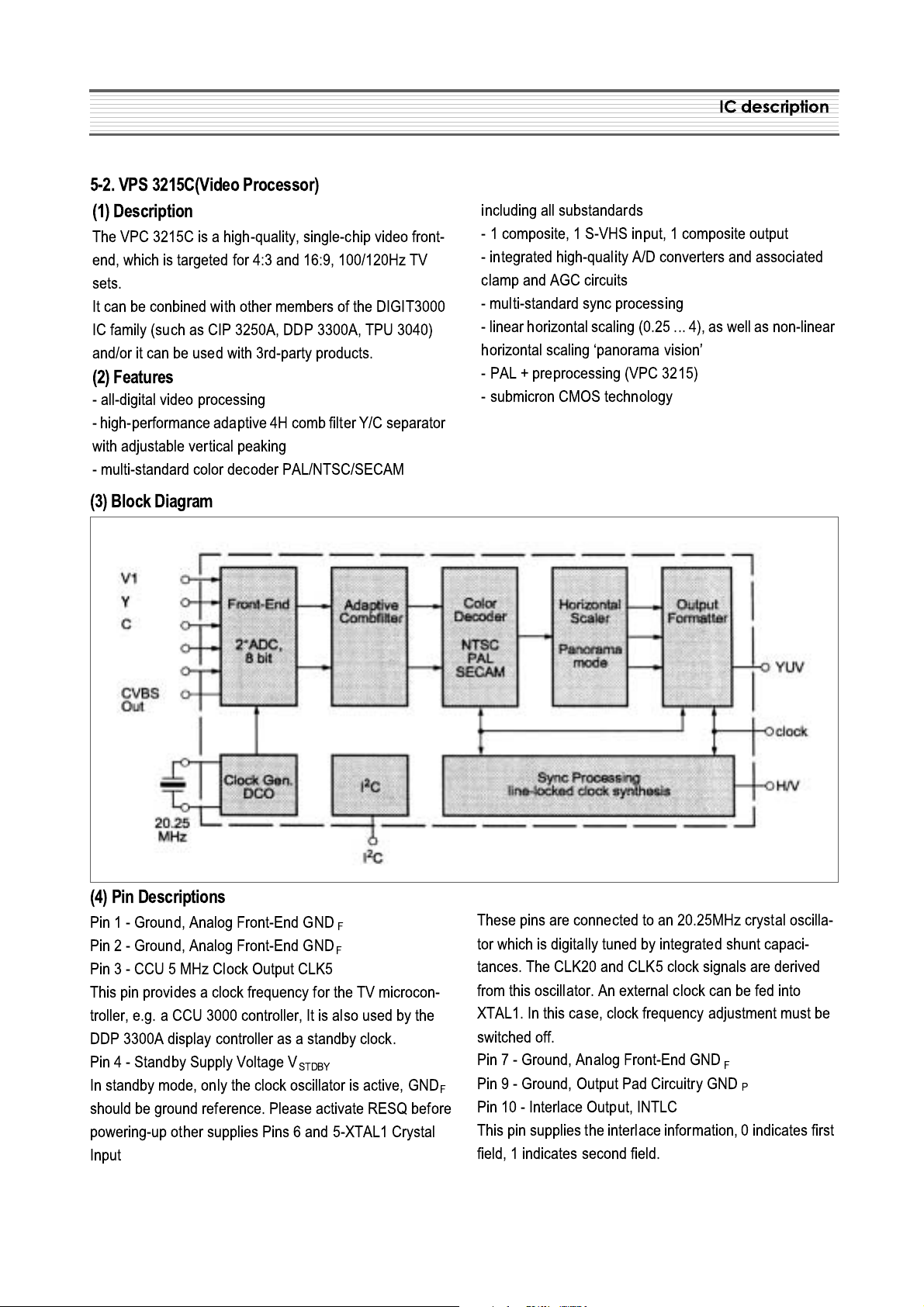

5-2. VPS 3215C(Video Processor)

(1) Description

The VPC 3215C is a high-quality, single-chip video front-

end, which is targeted for 4:3 and 16:9, 100/120Hz TV

sets.

It can be conbined with other members of the DIGIT3000

IC family (such as CIP 3250A, DDP 3300A, TPU 3040)

and/or it can be used with 3rd-party products.

(2) Features

- all-digital video processing

- high-performance adaptive 4H comb filter Y/C separator

with adjustable vertical peaking

- multi-standard color decoder PAL/NTSC/SECAM

(3) Block Diagram

IC description

including all substandards

- 1 composite, 1 S-VHS input, 1 composite output

- integrated high-quality A/D converters and associated

clamp and AGC circuits

- multi-standard sync processing

- linearhorizontal scaling (0.25... 4), as well as non-linear

horizontal scaling panorama vision

- PAL + preprocessing (VPC 3215)

- submicron CMOS technology

(4) Pin Descriptions

Pin 1 - Ground, Analog Front-End GND

Pin 2 - Ground, Analog Front-End GND

Pin 3 - CCU 5 MHz Clock Output CLK5

This pin provides a clock frequency for the TV microcon-

troller, e.g. a CCU 3000 controller, It is also used by the

DDP 3300A display controller as a standby clock.

Pin 4 - Standby Supply Voltage V

In standby mode, only the clock oscillator is active, GND

should be ground reference. Please activate RESQ before

powering-up other supplies Pins 6 and 5-XTAL1 Crystal

Input

F

F

STDBY

These pins are connected to an 20.25MHz crystal oscilla-

tor which is digitally tuned by integrated shunt capaci-

tances. The CLK20 and CLK5 clock signals are derived

from this oscillator. An external clock can be fed into

XTAL1. In this case, clock frequency adjustment must be

switched off.

Pin 7 - Ground, Analog Front-End GND

Pin 9 - Ground, Output Pad Circuitry GND

F

F

P

Pin 10 - Interlace Output, INTLC

This pin supplies the interlace information, 0 indicates first

field, 1 indicates second field.

14

Page 16

IC description

Pin 12 - Vertical Sync Pulse, VS

This pin supplies the vertical sync signal.

Pin 13 - Front Sync Pulse, FSY

This pin supplies the front sync information.

Pin 14 - Main Sync/Horizontal Sync Pulse MSY/HS

This pin supplies the horizontal sync pulse information in

line-locked mode. In DIGIT3000 mode, this pin is the main

sync input.

Pin 15 - Helper Line Output, Helper

This signal indicated a helper line in PAL + mode.

Pin 16 - Horizontal Clamp Pulse, HC

This signal canbe used to clamp an external video signal,

that is synchronous to the input signal. The timing is pro-

grammable.

Pin 17 - Active Video Output, AVO

This pin indicates the active video output data. The signal

is clocked with the LLC1 clock.

Pin 18 - Double Output Clock, LLC2

Pin 19 - Output Clock, LLC1

This is the clock reference for the luma, chroma, and sta-

tus outputs.

Pin 26 - Ground, Output Pad Circuitry GND

P

Pin 20 to 25,28,29 - Luma Output Y0-Y7

These output pins carry the digital luminance data. The

data are clocked with the LLC1 clock.

Pin 30 - Main Clock Output CLK20

This is the 20.25MHz main clock output.

Pin 31 - Supply Voltage, Digital Circuitry V

Pin 34 - Ground, Digital Circuitry GND

Pin 35 - Ground, Output Pad Circuitry GND

Pin 36 - Supply Voltage, Output Pad Supply V

SUPD

D

P

SUPP

Pin 38 to 43,46,47 - Chroma Outputs C0-C7

These outputs carry the digital CrCb chrominance data.

The data are clocked with the LL1 clock. The data are

sampled at half the clock rate and multiplexed. The CrCb

multiplex is reset for each TV line.

Pin 48 to 50 - Picture Bus Priority PR0-PR2

The Picture Bus Priority lines carry the digital priority

selection signals. The priority interface allows digital

switching of up to 8 sources to the back-end processor.

Switching for different sources is prioritized and can be on

a per pixel basis.

Pin 51 - Ground, Output Pad Circuitry GND

P

Pin 52 - VGAV-Input.

This pin is connected to the vertical sync signal of a VGA

signal.

Pin 53 - Front-End/Back-End Data FPDAT

This pininterfaces to theDDP 3300A back-endprocessor.

The information for the deflection drives and for the white

drive control,i.e. thebeam current limiter, is transmittedby

this pin.

Pin 54 - Reset Input RESQ

A low level on this pin resets the VPC 32xx.

2

Pin 55 - Bus Data SDA

The pin connects to the bus data line.

IC

2

IC

Pin 57 - Test Input TEST

This pinenables factory test modes. For normal operation,

it must be connected to ground.

Pin 59 - Ground, Analog Front-End GND

Pins 62,61,60,58 - Video 1-4

These are the analog video inputs. A CVBS or S-VHS

luma signal is converted using the luma (Video 1) AD con-

verter. The VIN1 input can alsobe switched to the chroma

(Video 2) ADC. The input signal must be AC-coupled.

Pin 63 - Chroma Input CIN

This pin is connected to the S-VHS chroma signal. A resis-

tive divider is used to bias the input signal to the middle of

the converter input range. CIN can only be connected to

the chroma (Video 2) A/D converter. The signal must be

AC-coupled.

Pin 64 - Analog Video Output, VOUT

The analog video signal that is selected for the main

(luma, CVBS)ADC is output at thispin. Anemitter follower

is required at this pin.

Pin 65 - Ground, Analog Shield Front-End GND

Pin 66 - Supply Voltage, Analog Front-End V

Pin 67 - Signal GND for Analog Input ISGND

This is the high quality ground reference for the video

input signals.

Pin 68 - Reference Voltage Top VRT

Via thispin, the referencevoltage for the A/D converters is

decoupled. The pin is connected with 10uF/47nF to the

Signal Ground Pin.

15

Page 17

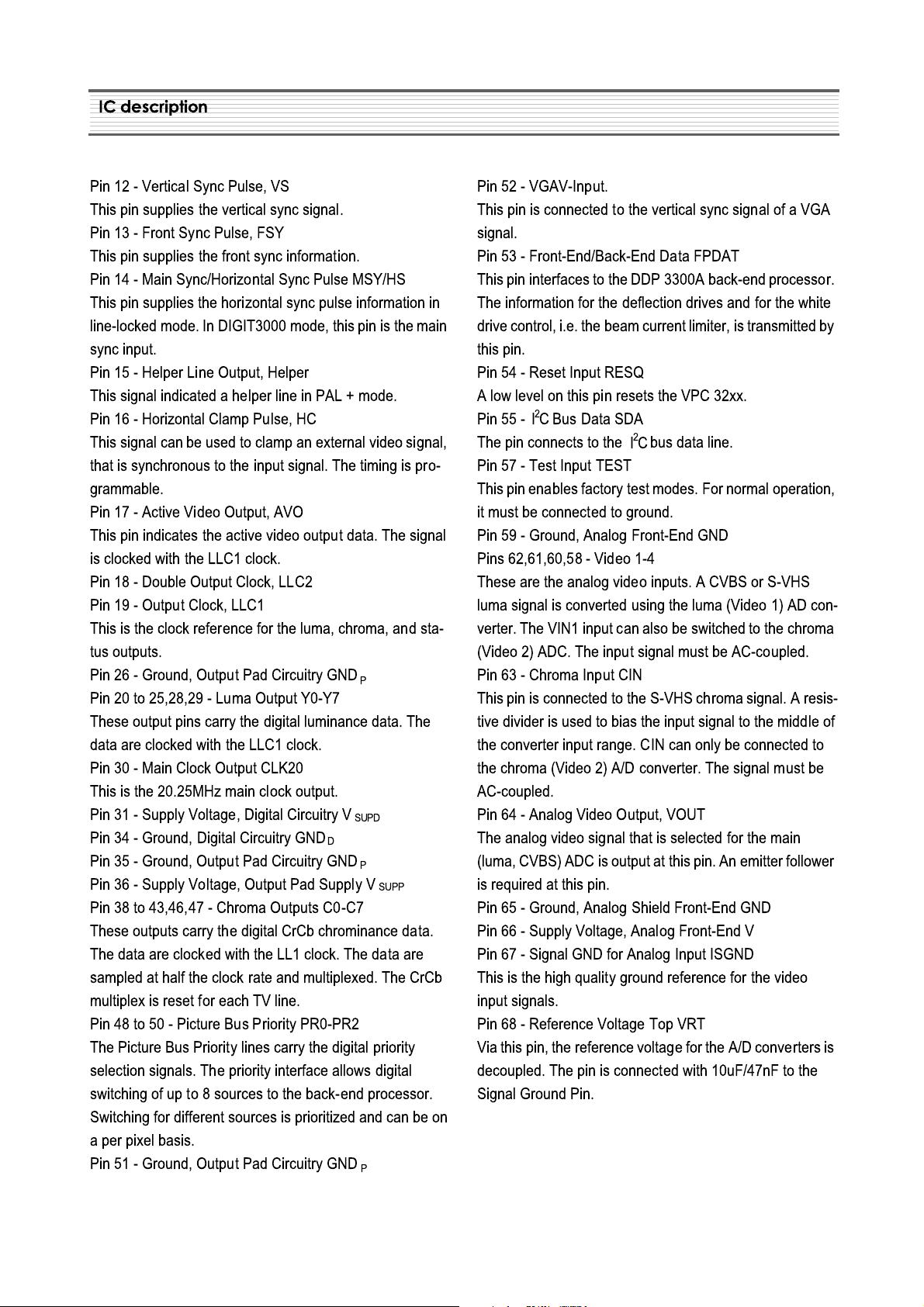

5-3. CIP3250A (Component Interface Processor)

(1) Description

The CIP 3250A is a new CMOS IC that contains on a sin-

gle chip the entire circuitry to interface analog YUV/RGB/

Fast Blank to a digital YUV system. The Fast Blank signal

is used to control a soft mixer between the digitized RGB

and an external digital YUV source. The CIP supports var-

ious output formats such as YUV 4:1:1/4:2:2 or RGB 4:4:4.

Together with the DIGIT 3000 (e.g. VPC 32xxA) or DIGIT

2000 (e.g. DTI 2250), an interface to a TV-scanrate con-

version circuit and/or multi-media frame buffer can be

obtained.

(2) Feature

- analog input for RGB or YUV and Fast Blank

- triple 8 bit analog to digital converters for RGB/YUV with

internal programmable clamping

- single 6 bit analog to digital converter for Fast Blank

singnal

IC description

- digital matrix RGB => YUV (Y, B-Y, R-Y)

- luma contrast and brightness correction for signals from

analog input

- color saturation and hue correction for signals from

analog input

- digital input for DIGIT 2000 or DIGIT 3000 formats

- digital interpolation to 4:4:4 format

- high quality soft mixer controlled by Fast Blank signal

- programmable delays to match digital YUV in and analog

RGB/YUV

- variable low pass filters for YUV output

- digital output in DIGIT 2000 and DIGIT 3000 formats, as

well as RGB 4:4:4

2

- bus interface

IC

- clock frequency 13.5...20.25 MHz

(3) Block Diagram

16

Page 18

IC description

(4) Pin Description

Pin 1 - STANDBY Input

Via this input pin, the standby mode of the CIP 3250A is

enabled. A high level voltage switches all outputs to

tristate mode, and power consumption is signigicantly

reduced. When the IC IS returned to active mode, a reset

is generated internally. Connect to VSS if not used.

Pins2to9-B7toB0Blue Output

In a stand alone application, where the CIP 3250A serces

as an A/D-converter, these are the output for the digital

Blue signal (pure binary) or the digital U signal (2scom-

plement). Leave vacant if not used.

Pin 10 to 17 - GL7 to GL0 Green/Luma Output

At theseoutputs, thedigital luminancesignal isreceived in

pure binary cided format for DIGIT 2000 and DIGIT 3000

applications. In a stand alone application, where the CIP

3250A serves as an A/D-converter, these are the outputs

for the digital Green signal(pure binary) or the digital luma

signal(pure binary). Leave vacant if not used.

Pin 18 - PVSS Output Pin Ground

This isthe common groundconnection of all output stages

and must be connected to ground.

Note : All ground pins of the chip (i.e.

18,52,58,60,62,64,66 and68) must be connected together

low resistive. The layout of the PCB must take into consid-

eration the need for a low-noise ground.

Pin 19 - PVDD Output Pin Supply + 5V/+3.3V

This pin supplies all output stages and must be connected

to a positive supply voltage.

Note : The layout of the PCB must take into consideration

the needfor a low-noisesupply. A bypass capacitor has to

be connected between ground and PVDD

Pins 20 to 27 - RC7 to RC0 Red/Chroma Output

These are the outputs for the digital chroma signal in the

DIGIT 3000 system, where U and V are multiplexed byte-

wise. In a DIGIT 2000 system, RC3 to RC0 and RC7 to

RC4 carry the halfbyte(nibble) multiplex format. In a stand

alone application, where the CIP 3250A serces as an AD-

converter, these are the outputs for the digital Red sig-

nal(pure binary) or the digital chroma V signal (2s compo-

nent). Leave vacant if not used.

Pin 29 - AVI Active Video Input

In a DIGIT 2000 application, this input can be connected

to ground. In a DIGIT 3000 application, this input expects

the DIGIT 3000 AVI signal. In a stand alone application,

this inputexpects the VSYNC vertical syncpulse. Connect

ground if not used.

Pin 30 - FSY Front Sync Input

In a DIGIT 2000 application, this input pin expects the

DIGIT 2000 SKEW protocol. In a DIGIT 3000 application,

this inputexpects the DIGIT3000 FSY protocol. In a stand

alone application, this unput expects the HSYNC horizon-

tal sync pulse. Connect to ground if not used.

Pin 31 to 32 - SDA and SCL of -Bus

These pins connect to the bus, which takes over the

2

IC

2

IC

control of the CIP 3250A via the internal registers. The

SDA pin is the data input/output, and the SCL pin is the

2

clock input/output of bus control interface. All registers

IC

are writerable(except address hex27) and readable.

Pin 33 to 35 - PRIO0 to PRIO2 Priority Bus

These pins connect to the Priority Bus of a DIGIT 3000

application. The Picture Bus Priority lines carry the digital

priority selection signals. The priority interface allows digi-

tal switching of up to 8 sources to the backend processor.

Switching for different sources is prioritized andcan be on

a perpixel basis. In all otherapplications, they must not be

connected.

Pin 36 to 43 - C0 to C7 Chroma Input

These are the inputs for the digital chroma signal which

can be received in binary offset or 2s complement coded

format. In a DIGIT 2000(4:1:1) system, C3 to C0 take the

halfbyte (nibble) multiplex format. C7 to C4 have to be

connected to ground. Within the DIGIT 3000(4:2:2) sys-

tem, Uand V aremultiplexed bytewise. Connect to ground

if not used.

17

Page 19

IC description

Pin 44 to 51 - L0 to L7 Luma Input

These are the inputs for the digitalluma signal which must

be in pure binary coded format. Connect to ground if not

used.

Pin 52 - DVSS Digital Ground

This is the common ground connectionof all digital stages

and must be connected to ground.

Note : All ground pins of the chip(i.e. 18, 52, 58, 60, 62,

64, 66, and 68) must be connected together low resistive.

The layout of the PCB must take into consideration the

need for a low-noise ground.

Pin 53 - DVDD Digital Supply +5V

This pin supplies all digital stages and must be connected

to a positive supply voltage.

Note : The layout of the PCB must take into consideration

the needfor a low-noisesupply. A bypasscapacitor has to

be connected between ground and DVDD.

Pin 54 - CLK Main Clock Input

This is the input for the clock signal. The frequency and

vary in the range from 13.5MHz to 20.25MHz.

Pin 55 - RESQ Input

A low signal at this input pingenerates a reset. The low-to-

high transition of this signal should occur when the supply

voltage is stable(power-on reset).

66, and 68) must be connected together low resistive. The

layout of the PCB must take into consideration the need

for a low-noise ground.

Pin 59 - ADREF Connect External Capacitor

This pinshould be connectedto ground over a 10uF and a

100nF capacitor in parallel.

Pin 60 - SUBSTRATE

This is connected to the platform which carries the die

and must be cvonnected to the ground.

Note : All ground pins of the chip(i.e.

18,52,58,60,62,64,66, and 68) must be connected

together low resistive. The layout of the PCB must take

into consideration the need for a low-noise ground.

Pin 61 - FB Analog Fast Blank Input

This input takes the DC-coupled analog Fast Blank signal.

The amplitude is 1.0V maximum at 75 Ohms. Connect to

ground if not used.

Pin 62 - GNDFB Analod Ground

This is the ground pin for the AD converter of the Fast

Blank signal and has to be connected to ground.

Note : All ground pins of the chip (i.e. 18,52,58,60,62,64,

62,64,66 and 68) must be connected together low resis-

tive. The layout of the PCB must take into consideration

the need for a low-noise ground.

Pin 56 - TMODE Input

This pin is for test purposes only and must be connected

to ground in normal operation.

Pin 57 - AVDD Analog Supply +5V

This is the supply voltage pin for the A/D converters and

must be connected to a positive supply voltage.

Note : The layout of the PCB must take into consideration

the needfor a low-noisesupply. A bypasscapacitor has to

be connected between ground and AVDD.

Pin 58 - AVSS Analog Ground

This is the ground pin for the A/D converters and must be

connected to ground.

Note : All ground pins of the chip (i.e. 18,52,58,60,62,64,

Pin 63 - BU Analog Blue/U Chroma Input

The inputpin takesthe AC-coupledanalog compont signal

Blue or U Chroma. The amplitude is 1.0V maximum at 75

Ohms and a coupling capacitor of 220 nF. Internally, the

DC-offset of the input signal is adjusted via the program-

mable internal clamping circuit. Connect to ground if not

used.

Pin 64 - GNDBU Analog Ground

This is the ground pin for the A/D converter of the Blue or

U Chroma signal and must be connected to ground.

Note : All ground pins of the chip(i.e.

18,52,58,60,62,64,66, and 68) must be connected

together low resistive. The layout of the PCB must take

into consideration the need for a low-noise ground.

18

Page 20

IC description

Pin 65 - GY Analog Green/Luma Input

This input pin takes the AC-coupled analog compinent sig-

nal Green or Luma. The amplitude is 1.0V maximum at 75

Ohms and a couplign capacitor of 220nF. Internally, the

DC-offset of the input signal is adjusted via the program-

mable internal clamping circuit. Connect to ground if not

used.

Pin 66 - GNDGY Analog Ground

This is the ground pin for the A/D converter of the Green

or Luma signal and must be connected to ground.

Note : All ground pins of the chip(i.e. 18,52,58,60,62,64,

66, and 68) must be connected together low rresistive.

The layout of the PCB must take into consideration the

need for a low-noise ground.

Pin 67 - RV Analog Red/V Chroma Input

This input pin takes the AC-coupled analog component

signal Red or V Chroma. The amplitude is 1.0V maximum

at 75ohms and a coupling capacitor of 220nF. Internally,

the DC-offset of the input signal is adjusted via the pro-

grammable internal clamping circuit. Connect to ground if

not used.

Pin 68 - GNDRY Analog Ground

This isthe ground pin for theA/D converter ofthe Red or V

Chroma signal and must be connected to ground.

Note : All ground pins of the chip (i.e. 18,52,58,62,64,66,

and 68) must be connected together low resistive. Thelay-

out of the PCB must take into consideration the need for a

low-noise ground.

19

Page 21

IC description

5-4. MSM5412222 ( 262, 214-Word X 12-Bit Field Memory )

(1) DESCRIPTION

The OKI MSM541222 is a high performance 3-Mbit, 256K x 12-bit, Field Memory. It is especially designed for

high-speed serial access applications such as HDTVs, conventional NTSC TVs, VTRs, digital movies and

Multi-media systems. MSM541222 is a FRAM for wide or low or low end use in general commodity TVs and

VTRs exclusively. MSM5412222 is not designed for high end use in medical systems, professional graphics

systems which require long term picture storage, data storage systems and others. Two or more MSM541222s

can be cascaded directly without any delay devices between them. ( Cascading provides larger storage depth

or a longer delay ).

Each of the 12-bit planes has separate serial write and read ports. These employ independent control clocks to

support asynchronous read and write operations. Different clock rates are also supported, which allow alternate

data rates between write and read data streams.

The MSM5412222 provides high speed FIFO, First-In First-Out, operation without external refreshing:

MSM5412222 refreshes its DRAM storage cells automatically, so that it appears fully static to the users.

Moreover, fully static type memory cells and decoders for serial access enable the refresh free serial access

operation, so that serial read and / or write control clock can be halted high or low for any duration as long as

the power is on. Internal conflicts of memory access and refreshing operations are prevented by special

arbitration logic.

The MSM5412222s function is simple, and similar to a digital delay device whose delay-bit-length is easily

set by reset timing. The delay length, and the number of read delay clocks between write and read, is

determined by externally controlled write and read reset timings.

Additional SRAM serial registers, or line buffers for the initial access of 256 x 12-bit enable high speed first-bit-

access with no clock delay just after the write of read reset timings.

Additionally, the MSM5412222 has a write mask function or input enable function (IE), and read-data skipping

function or output enable function (OE). The differences between write enable (WE) and input enable (IE), and

between read enable (RE) and output enable (OE) are that WE and RE can stop serial write / read address

increments, but IE and OE cannot stop the increment, when write / read clocking is continuously applied to

MSM5412222. The input enable (IE) function allows the user to write into selected locations of the memeory

only, leaving the reset of the memory contents unchanged. This facilitates data processing to display a

picture in picture on a TV screen.

The MSM5412222 is similar in operation and functionality to OKI 1-Mbit Field Memory MSM514222B and

2-Mbit Field Memory MSM518222. Three MSM514222Bs or one MSM514222B plus one MSM518222 can

be replaced simply by one MSM5412222.

20

Page 22

IC description

(2) FEATURES

Single power supply : 5V 10%

512 Rows x 512 Columns x 12 bits

Fast FIFO (First-In First-Out) operation

High speed asynchronous serial access

Read / write cycle time 25 ns / 30 ns

Access time 23 ns / 25 ns

Direct cascading capability

Write mask function (Input enable control)

Data skipping function (Output enable control)

Self refresh (No refresh control is required)

(3) BLOCK DIAGRAM

21

Page 23

(4) Pin Description

Pin No. Pin Name Function

17 SWCK Serial Write Clock

28 SRCK Serial Read Clock

20 WE Write Enable

25 RE Read Enable

21 IE Input Enable

24 OE Output Enable

18 RSTW Write Resert Clock

27 RSTR Read Reset Clock

IC description

2,3,5,6,7,8,10,11,12,13,15,16 Data Input

29,30,32,33,34,35,37,38,39,40,42,43 Data Output

D 0~D 11

IN IN

D 0~D 11

OUT OUT

22,23 Vcc Power Supply (5V)

1,31,44 Vss Ground(0V)

4,9,14,19,26,36,41 NC No Connection

22

Page 24

IC description

5-5. DDP 3310B (Display and Deflection Processor)

(1) Description

The DDP 3310B is a single-chip digitalDisplay and Deflec-

tion Processor designed for high-quality backend applica-

tions in 100/120MHz TV sets with 4:3- or 16:9 picture

tubes. The IC can be combined with members of the

DIGIT 3000 IC family (VPC 32xx, TPU 3040), or it can be

used with third-party products. The IC contains the entire

digital video component and deflection processing and all

analog interface components.

Deflection processing

- scan velocity modulation output

- high-performance H/V deflection

- EHT compensation for vertical / East/West

- soft start/stop of H-Drive

- vertical angle and bow

- differential vertical output

- horizontal and vertical protection circuit

- adjustable horizontal frequency for VGA/SVGA dislay

(2) Feature

Video processing

- linear horizontal scaling (0.25 ... 4)

- non-linear horizontal scaling panoramavision

- dynamic peaking

- soft limiter (gamma correction)

- color transient improvement

- programmable RGB matrix

- picture frame generator

- two analog RGB/Fast-Blank inputs

(3) Block Diagram

Miscellaneous

- selectable 4:1:1/4:2:2 YC C input

- selectable 27/32-MHz line-locked clock input

- crystal oscillator for horizontal protection

- automatic picture tube adjustment(cutoff, whitedrive)

- single 5-V power supply

- hardware for simple 50/60-Hz to 100/120-Hz conversion

(display frequency doubling)

2

- two -controlled PWM outputs

IC

- beam current limiter

r

b

23

Page 25

IC description

(4) Pin Description

Pin 1

- Supply Voltage, Output Pin Driver

This pin is used as supply for the following digital output

pins : FIFORRD, FIFORD, FIFOWR, FIFORWR.

Pin 2

- Ground, Output Pin Driver

GNDP*

Output Pin Driver Reference

Pin 3

- Sync Signal Input

VS2

Additional pin for the vertical sync information. Via

Register the used vertical sync can be switched between

the inputs VS2 and VS(Pin 64)

Pin 4

- Reset for FIFO Read Counter

This signal is active-High and resets the read counter in

the display frequency doubling FIFO.

Pin 5

- Read Enable for FIFO

FIFORD

This signal is active-High and enabels the read counter in

the display frequency doubling FIFO.

Pin 6

- Write Enable for FIFO

FIFOWR

This signal is active-High and enables the write counter in

the display frequency doubling FIFO.

Pin 7

- Reset for FIFO Write Counter

This signal is active-High and enables the write counter in

the display frequency doubling FIFO.

Pin 8

- Horizontal Drive

HOUT

This open-drain output supplies the drive pulse for the hor-

izontal output stage. A pull-up resistor has to be used.

Pin 9

- Horizontal Flyback Input

HFLB

Via this pin, the horizontal flyback pulse is supplied to the

DDP 3310B.

Pin 10

- Safety Input

SAFETY

This input has two thresholds. A signal between the lower

and upper threshold means normal function.Other signals

are detected as malfunction.

Pin 11

- Vertical Protection Input

VPROT

VSUPP*

FIFORRD

FIFOWR

2

IC

The vertical protection circuitry prevents the picture tube

from burn-in in the event of a malfunction of the vertical

deflection stage. If the peak-to-peak value of the vertical

sawtooth signal is too small, the RGB output signals are

blanked.

Pin 12

- H-Drive Frequency Range Select

FREQSEL

This pin selects the frequency range for the horizontal

drive signal.

Pin 13

- Clock Select 40.5 or 27/32 MHz

CM1

Low level selects 27/32 MHz, High level selects 40.5 MHz

Pin 14

- Clock Select 40.5 or 27/32 MHz

CM0

Low level selects 27 MHz, High level selects 32 MHz

Pin 15

- Range Switch2 for Measuring ADC

RSW2

This pin is an open-drain pull-down output. During cutoff

measurement the switch is off. During white drive mea-

surement the switch is on. Also during the restof time itis

on.

Pin 16

- Range Switch 1 or Second Input for Measuring

RSW1

ADC

This pin is an open-drain pull-down output. During cutoff

and white-drive measurement, the switch is off. During

the rest of time it is on. The RSW1 pin can be used as

second measurement ADC input.

Pin 17

- Measurement ADC Input

SENSE

This is the input of the analog to digital converter for the

picture and tube measurement. Three measurement

ranges are selectable with RSW1 and RSW2

Pin 18

- Measurement ADC Reference Input

MGND

This is the ground reference for the measurement A/D

converter.

Pin 19

- Vertical Sawtooth Output

VERT+(19)

This pin supplies the drive signal for the vertical output

stage. The drive signal is generated with 15-bit precision.

The analog voltage is generated by a 4-bit current DAC

with external resistor (6 k

for proper operation) and

uses digital noise-shaping.

Pin 20

- Vertical Sawtooth Output inverted

VERT-

This pin supplies the inverted signal of VERT+.

24

Page 26

IC description

Together with this pin, it can be used to drive symmetrical

deflection amplifiers.

Pin 21

- East/West Parabola Output

EW

This pin supplies the parabola signal for the East/West

correction. The drive signal is generated with 15-bit preci-

sion. The analog voltage is generated by a 4-bit current

DAC with external resistor and uses digital noise-shaping.

Pin 22

- DAC Current Reference

XREF

External referenceresistor for DAC output currents,typical

§Ù

, to adjust the output current of the D/A converters.

10 k

(see recommended operation conditions).

This resistor has to be connected to analog fround as

closely as possible to the pin.

Pin 23

- Scan Velocity Modulation Output

SVM

This output delivers the analog SVM signal. The D/A con-

verters. At zero signal the output current is 50% of the

maximum output current.

Pin 24,25,26

- Analog RGB Output

ROUT, GOUT, BOUT

These pins are the analog Red/Green/Blue outputs of the

back-end. The outputs are current sinks.

Pin 27

- Ground, Analog Back-end

GNDO*

This pin has to be connected to the analog supply voltage.

No supplycurrent for the digital stagesshould flow through

this line.

Pin 28

- Supply Voltage, Analog Back-end

VSUPO*

This pin has to be connected to the analog supply voltage.

No supplycurrent for the digital stagesshould flow through

this line.

Pin 29

- DAC ReferenceDecouplign/Beam Current Safety

VRD/BCS

Via this pin, the DAC referencevoltage is decoupled by an

external capacitor. The DAC output currents depend on

this voltage, therefore a pull-down transistor can be used

to shut off all beam currents. A decoupling capacitor of

4.7uF in parallel to 100uF (low inductance) is required.

Pin 30, 34

- Fast-Blank Input

FBLIN1/2

These pins are used to switch the RGB outputs to the

external analog RGB inputs. FBLIN1 switches the RIN1,

GIN1 and BIN1 inputs, FBLIN2 switches the RIN2, GIN2

and BIN2 inputs. The active level (Low or High) can be

selected by software.

Pin 31, 32, 33

- Analog RGB Input1

RIN1, GIN1, BIN1

These pin are used to insert an external analog RGB sig-

nal, e.g. from a SCART connector which can by switched

to the analog RGB outputs with the Fast-Blank signal.

The analog back-end provides separate brightness and

contrast settings for the external analog RGB signals.

Pin 35, 36, 37

- Analog RGB Input2

RIN2, GIN2, BIN2

These pins are used to insert an external analog RGB sig-

nal, e.g. from a SCART connector which can by switched

to the analog RGB outputs with the Fast-Blank signal.

The analog back-end provides separate brightness and

contrast settings for the external analog RGB signals.

Pin 38

- Test Input

TEST

This pinenables factory test modes. Fornormal operation

it must be connected to ground.

Pin 39

- Reset Input

RESQ

A low level on this pin resets the DDP 3310B.

Pin 40

- Adjustable DC Output 1

This output delivers a DC voltage with a resolution of 8

bit, adjustable over the bus. The output is driven by a

2

IC

PWM1

push-pull stage. The PWM frequency is appr 79.4MHz.

For a ripple-free voltage a first order lowpass filter with a

corner frequency < 120 Hz should be applied.

Pin 41

- Adjustable DC Output 2

PWM2

See pin 40.

Pin 42

- Half-Contrast Input

HCS

Via this input pin the output level of the D/A-converted

internal RGB signals can be reduced by 6dB. Inserted

external analog RGB signals remain unchanged.

Pin 43...50

- Picture Bus Chroma

C0...C7

The Picture Bus Chroma lines carry the multiplexed color

component data. For the 4:1:1 input signal (4-bit chroma)

the pins C4...C7 are used.

25

Page 27

IC description

Pin 51

- Supply Voltage, Digital Circuitry

- Ground, Digital Circuitry

Pin 52

GNDD*

VSUPD*

Digital Circuitry Input Reference

Pin 53

- Main Clock Input

LLC2(53)

This is the input for the line-locked clock signal. The fre-

quency can be 27, 32, or 40.5 MHz.

Pin 54...61

- Picture Bus Luma

Y0...Y7

The Picture Bus Luma lines carry the digital luminance

data.

Pin 62

- Line-Locked Clock Input

LLC1

This is the reference clock for the single frequency input

sync signals required in a FIFO application. The frequency

can be 13.5, 16, or 20.25 MHz.

Pin 63

- Sync Signal Input

HS

This pin gets the horizontal sync information. Either single

or double horizontal frequency or VGA horizontal sync sig-

nal.

Pin 65, 66

- Crystal Output / Input

XTAL2 / XTAL1

These pins are connectecd to an 5-MHz crystal oscillator.

The security unit for the HOUT signal uses this clock sig-

nal as reference.

Pin 67

Via this pin the - bus data are written to or read from

2

- Data Input/Output

IC

2

IC

SDA

the DDP 3310B.

Pin 68

Via this pin, the clock signal for the -bus will be sup-

2

- Clock Input

IC

SCL

2

IC

plied. The signal can be pulled down by an internal tran-

sistor.

* Application Note :

All ground pins should be connected separeately with

short and low-resistive lines to a central power supply

ground. Accordingly, all supply pins should be connected

separately with short and low-resistive lines to the power

supply. Decoupling capacitors from VSUPP to GNDP,

VSUPD to GNDD, and VSUPO to GNDO are recom-

mended to be placed as closely as possible to the pins.

Pin 64

- Sync Signal Input

VS

This pin gets the vertical sync informatoion. Either single

or double vertical frequency or VGA vertical sync signal.

26

Page 28

272829

Page 29

Page 30

7. Service Parts List

is recommendable spare part.

Caution

LOC PART-CODE PART-NAME PART-DESC LOC P ART-CODE P ART-NAME PART-DESC

ZZ100 48B3822D05 TRANSMITTER R-22D05

ZZ120 PEBCSHD018 COVER BACK AS DSC-3270E

M211 4952101201 COVER BACK HIPS

M541 4855415800 SPEC PLATE 150ART P/E FILM (C/TV)

M781 4857817612 CLOTH BLACK FELT 250X20X0.7

M782 4857817630 CLOTH BLACK FELT 400X20X0.7

ZZ130 PEPKCPD018 PAPKING AS DSC-3270E

M641 6520010100 STAPLE PIN AUTO W65

M681 4856812400 BAND 18MM X 3M

M801 4958000600 BOX CARTON DW-4

M811 4958100900 PAD EPS

M821 4858218700 BAG P.E

ZZ131 48519A4410 CRT GROUND NET 3301H-1015-2P

ZZ132 58G0000114 COIL DEGAUSSING DC-3200

ZZ133 58GD000002 COIL TILT DSC-3670N

ZZ140 PECACAD018 CABINET AS DSC-3270E

M201A 4956000100 SCREW CRT FIX SWRM10A L=35

M201B 4856215404 WASHER RUBBER CR T4.0

M201C 7178301211 SCREW TAPTITE TT2 WAS 3X12 MFZN

M201D 7178301211 SCREW TAPTITE TT2 WAS 3X12 MFZN

M201E 7178301211 SCREW TAPTITE TT2 WAS 3X12 MFZN

M201F 7178301211 SCREW TAPTITE TT2 WAS 3X12 MFZN

M211A 7172401612 SCREW TAPPTITE TT2 TRS 4X16 MFZN BK

M211C 7172401612 SCREW TAPPTITE TT2 TRS 4X16 MFZN BK

M211D 7172401612 SCREW TAPPTITE TT2 TRS 4X16 MFZN BK

M211E 7172401612 SCREW TAPPTITE TT2 TRS 4X16 MFZN BK

M353 97P4602700 CLAMP CORD POLYETHYLENE BLK

M353A 7172401612 SCREW TAPPTITE TT2 TRS 4X16 MFZN BK

M371 4853745100 RET A PLATE PVC T0.5

M481 4954800300 BUTTIN POWER ABS PAINT

M481A 4856716000 SPRING SWPA PIE0.5

M561 4955600100 MARK BRAND AL T1.0 DIA-CUTTING

M682 4856816300 CLAMP WIRE NYLON 6 (V0)

S601 4958301110 SPEAKER L SS-78128F05(L)

S601A 7172401612 SCREW TAPPTITE TT2 TRS 4X16 MFZN BK

S602 4958300110 SPEAKER UNIT 5W 8OHM H114/100400A

S602A 7178301211 SCREW TAPTITE TT2 WAS 3X12 MFZN

S603 4958301010 SPEAKER R SS-78128F05(R)

S603A 7172401612 SCREW TAPPTITE TT2 TRS 4X16 MFZN BK

ZZ200 PEFMSJD018 MASK FRONT AS DSC-3270E

M201 4952001101 MASK FRONT HIPS PAINT

M201D 4857817630 CLOTH BLACK FELT 400X20X0.7

M201E 4857817610 CLOTH BLACK FELT 300X20X0.7

ZZ290 PEMPMSD018 PCB MAIN DSC-3270E

C453 CMXL2E124K C MYLAR 250V MEU 0.12MF K

C856 CEYF1V222C C ELECTRO 35V RUS 2200MF (16X31.5)

C857 CEYF1V332C C ELECTRO 35V RUS 3300MF (18*35.5)

C863 CH1FFF472M C CERA AC AC400V 4700PF F DE7150F

D850 DR2KY—— DIODE AVALANCHE R 2-KY (TAPPING)

R

is safety component, so it must be used the same component.

R

REMOCON

FOAM+LDPE T0.5X1880X1380

MANUAL AS

D854 DUF5404LS- DIODE UF5404L-5702 400V 3A

I101 1TDA4470M- IC IF TDA4470-M

I102 1KA7805— IC REGULATOR KA7805

I601 1MSP3410D- IC AUDIO MSP3410D

I602 1DP3519AA2 IC AUDIO DOLBY DPL3519A-A2

I604 1KA4558— IC AMP KA4558

I605 1TA8256BH- IC AUDIO AMP TA8256BH

I605A 4857027534 HEAT SINK AL EXBK

I605B 7174300811 SCREW TAPPTITE TT2 RND 3X8 MFZN

I606 1TA8256BH- IC AUDIO AMP TA8256BH

I606A 4857027534 HEAT SINK AL EXBK

I606B 7174300811 SCREW TAPPTITE TT2 RND 3X8 MFZN

I701 1ST92T195- IC MICOM OTP ST92T195B

I701A 4959301310 SOCKET IC LSC-656-T051-00

I702 124LC16B1B IC MEMORY 24LC16B1B

I805 1KA7812P— IC REGULATOR KIA7812P

I805A 4857031201 HEAT SINK AL 6063S

I805B 7174300811 SCREW TAPPTITE TT2 RND 3X8 MFZN

I806 1KA7809— IC REGULATOR KA7809

I807 1KA7805— IC REGULATOR KA7805

I810 1T0P224Y— IC AUDIO POWER TOP224Y

I810A 4957000701 HEAT SINK AL EX

I810B 7174300811 SCREW TAPPTITE TT2 RND 3X8 MFZN

I811 1LTV817C— IC PHOTO COUPLER LTV-817C

I813 1LA6515— IC OP AMP LA6515

L103 5.80E+42 COIL AFT TRF-A005

L850 58C4500079 COIL CHOKE L-45

M381 4853812800 FRAME MAIN PCB FR HIPS BK

M681 4956800100 CLAMP WIRE STL-J-600-6M-01

PA101 4950708010 CONNECTOR

PA102 4950705007 CONNECTOR

PA601 4950704017 CONNECTOR

PA801 4950710010 CONNECTOR YH025-10+YST250+ULW=90

PA802 4950706021 CONNECTOR YH025-06+YST250+ULW=90

PA803 4950710010 CONNECTOR YH025-10+YST250+ULW=90

PW104 4859281320 CONN WAFER TAC-L18X-A3

PW105 4859281320 CONN WAFER TAC-L18X-A3

PW106 4859280820 CONN WAFER TAC-L13X-A3

PW107 4859280820 CONN WAFER TAC-L13X-A3

PW806 4859238620 CONN WAFER YPW500-02

SF101 5PK3953M— FILTER SA W K3953M

SF102 5PK9650M— FILTER SA W K9650M

T804 5DP2828A2- TRANS FORMER DTS-2828A2

U101 4859719930 TUNER VARACTO R DT5-BF18D

X601 5XE18R432E CR YS T AL QU ARTZ

ZZ200 PEMPJ2D018 PCB MAIN CHIP B AS DSC-3270E

CC101 HCBK102KCA C CHIP CERA 50V X7R 1000PF K 2012

CC102 HCBK102KCA C CHIP CERA 50V X7R 1000PF K 2012

CC103 HCBK102KCA C CHIP CERA 50V X7R 1000PF K 2012

CC104 HCQK220JCA C CHIP CERA 50V CH 22PF J 2012

CC106 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

YH025-08+YST250+ULW=400

YH025-05+YST250+ULW=300

YH025-04+YST250+USW=450

HC-49/U 18.43200MHZ 30PPM

Page 31

Service Parts List

LOC PART-CODE PART-NAME PART-DESC LOC PART-CODE PART-NAME PART-DESC

CC107 HCBK104KCA C CHIP CERA 50V X7R 0.1MF K 2012

CC108 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC109 HCBK104KCA C CHIP CERA 50V X7R 0.1MF K 2012

CC110 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC112 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC114 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC118 HCFH474ZCA C CHIP CERA 25V Y5V 0.47MF Z 2012

CC119 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC120 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC121 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC601 HCQK509DCA C CHIP CERA 50V CH 5PF D 2012

CC602 HCQK509DCA C CHIP CERA 50V CH 5PF D 2012

CC603 HCBK223KCA C CHIP CERA 50V X7R 0.022MF K 2012

CC604 HCBK471KCA C CHIP CERA 50V X7R 470PF K 2012

CC605 HCBK471KCA C CHIP CERA 50V X7R 470PF K 2012

CC606 HCBK104KCA C CHIP CERA 50V X7R 0.1MF K 2012

CC607 HCBK104KCA C CHIP CERA 50V X7R 0.1MF K 2012

CC608 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC609 HCQK101JCA C CHIP CERA 50V CH 100PF J 2012

CC610 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC612 HCQK101JCA C CHIP CERA 50V CH 100PF J 2012

CC613 HCBK102KCA C CHIP CERA 50V X7R 1000PF K 2012

CC614 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC615 HCBK102KCA C CHIP CERA 50V X7R 1000PF K 2012

CC616 HCBK102KCA C CHIP CERA 50V X7R 1000PF K 2012

CC617 HCBK392KCA C CHIP CERA 50V X7R 3900PF K 2012

CC618 HCBK392KCA C CHIP CERA 50V X7R 3900PF K 2012

CC619 HCBK104KCA C CHIP CERA 50V X7R 0.1MF K 2012

CC620 HCBK223KCA C CHIP CERA 50V X7R 0.022MF K 2012

CC621 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC622 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC624 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC625 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC626 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC627 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC701 HCBK102KCA C CHIP CERA 50V X7R 1000PF K 2012

CC702 HCFH474ZCA C CHIP CERA 25V Y5V 0.47MF Z 2012

CC704 HCBK472KCA C CHIP CERA 50V X7R 4700PF K 2012

CC705 HCBK222KCA C CHIP CERA 50V X7R 2200PF K 2012

CC706 HCQK220JCA C CHIP CERA 50V CH 22PF J 2012

CC707 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC708 HCQK220JCA C CHIP CERA 50V CH 22PF J 2012

CC709 HCQK820JCA C CHIP CERA 50V CH 82PF J 2012

CC710 HCBK472KCA C CHIP CERA 50V X7R 4700PF K 2012

CC711 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC713 HCQK820JCA C CHIP CERA 50V CH 82PF J 2012

CC716 HCBK102KCA C CHIP CERA 50V X7R 1000PF K 2012

CC717 HCBK102KCA C CHIP CERA 50V X7R 1000PF K 2012

CC718 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC719 HCFK224ZCA C CHIP CERA 50V Y5V 0.22MF Z 2012

CC720 HCBK473KCA C CHIP CERA 50V X7R 0.047MF K 2012

CC721 HCFH474ZCA C CHIP CERA 25V Y5V 0.47MF Z 2012

CC723 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC801 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC802 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC803 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC804 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

CC805 HCBK103KCA C CHIP CERA 50V X7R 0.01MF K 2012

RC103 HRFT472JCA R CHIP 1/10 4.7K OHM J 2012

RC104 HRFT333JCA R CHIP 1/10 33K OHM J 2012

RC106 HRFT101JCA R CHIP 1/10 100 OHM J 2012

RC107 HRFT472JCA R CHIP 1/10 4.7K OHM J 2012

RC108 HRFT153JCA R CHIP 1/10 15K OHM J 2012

RC109 HRFT222JCA R CHIP 1/10 2.2K OHM J 2012

RC110 HRFT472JCA R CHIP 1/10 4.7K OHM J 2012

RC111 HRFT103JCA R CHIP 1/10 10K OHM J 2012

RC112 HRFT562JCA R CHIP 1/10 5.6K OHM J 2012

RC113 HRFT563JCA R CHIP 1/10 56K OHM J 2012

RC128 HRFT472JCA R CHIP 1/10 4.7K OHM J 2012

RC130 HRFT151JCA R CHIP 1/10 150 OHM J 2012

RC131 HRFT153JCA R CHIP 1/10 15K OHM J 2012

RC132 HRFT153JCA R CHIP 1/10 15K OHM J 2012

RC133 HRFT102JCA R CHIP 1/10 1K OHM J 2012

RC136 HRFT751JCA R CHIP 1/10 750 OHM J 2012

RC137 HRFT101JCA R CHIP 1/10 100 OHM J 2012

RC139 HRFT222JCA R CHIP 1/10 2.2K OHM J 2012

RC602 HRFT103JCA R CHIP 1/10 10K OHM J 2012

RC603 HRFT473JCA R CHIP 1/10 47K OHM J 2012

RC604 HRFT223JCA R CHIP 1/10 22K OHM J 2012

RC605 HRFT223JCA R CHIP 1/10 22K OHM J 2012

RC606 HRFT473JCA R CHIP 1/10 47K OHM J 2012

RC622 HRFT000-CA R CHIP 1/10 0 OHM 2012

RC623 HRFT153JCA R CHIP 1/10 15K OHM J 2012

RC624 HRFT682JCA R CHIP 1/10 6.8K OHM J 2012

RC625 HRFT682JCA R CHIP 1/10 6.8K OHM J 2012

RC626 HRFT113JCA R CHIP 1/10 11K OHM J 2012

RC627 HRFT113JCA R CHIP 1/10 11K OHM J 2012

RC702 HRFT202JCA R CHIP 1/10 2K OHM J 2012

RC708 HRFT222JCA R CHIP 1/10 2.2K OHM J 2012

RC712 HRFT562JCA R CHIP 1/10 5.6K OHM J 2012

RC715 HRFT153JCA R CHIP 1/10 15K OHM J 2012

RC716 HRFT103JCA R CHIP 1/10 10K OHM J 2012

RC717 HRFT103JCA R CHIP 1/10 10K OHM J 2012

RC718 HRFT222JCA R CHIP 1/10 2.2K OHM J 2012

RC719 HRFT562JCA R CHIP 1/10 5.6K OHM J 2012

RC720 HRFT472JCA R CHIP 1/10 4.7K OHM J 2012

RC729 HRFT101JCA R CHIP 1/10 100 OHM J 2012

RC730 HRFT101JCA R CHIP 1/10 100 OHM J 2012

RC731 HRFT683JCA R CHIP 1/10 68K OHM J 2012

RC732 HRFT683JCA R CHIP 1/10 68K OHM J 2012

RC733 HRFT563JCA R CHIP 1/10 56K OHM J 2012

RC736 HRFT222JCA R CHIP 1/10 2.2K OHM J 2012

RC737 HRFT101JCA R CHIP 1/10 100 OHM J 2012

RC738 HRFT101JCA R CHIP 1/10 100 OHM J 2012

30

Page 32

Service Parts List

LOC PART-CODE PART-NAME PART-DESC LOC P ART-CODE P ART-NAME PART-DESC

RC739 HRFT362JCA R CHIP 1/10 3.6K OHM J 2012

ZZ200 PEMPJ0D018 PCB MAIN (RHU) AS DSC-3270E

C110 CEXF1C471V C ELECTRO

C118 CEXF1C471V C ELECTRO

C614 CEXF1V102V C ELECTRO

C615 CEXF1C471V C ELECTRO

C618 CEXF1C102V C ELECTRO

C620 CEXF1C471V C ELECTRO

C656 CEXF1V102V C ELECTRO

C657 CEXF1V102V C ELECTRO

C658 CEXF1V102V C ELECTRO

C663 CEXF1V102V C ELECTRO

C664 CEXF1V102V C ELECTRO

C671 CEXF1V102V C ELECTRO

C705 CEXF1C102V C ELECTRO

C893 CEXF1C471V C ELECTRO

C894 CEXF1C471V C ELECTRO

C895 CEXF1C471V C ELECTRO

C896 CEXF2G220V C ELECTRO 400V RSS 22MF (16X25) TP

ZZ200 PEMPJBD018 PCB MAIN M-10 AS DSC-3270E

E001 4856310600 EYE LET BSR T0.2 (R2.3)

E002 4856310600 EYE LET BSR T0.2 (R2.3)

E003 4856310600 EYE LET BSR T0.2 (R2.3)

E004 4856310600 EYE LET BSR T0.2 (R2.3)

PW101 485923162S CONN WAFER YW025-03 (STICK)

PW102 485923162S CONN WAFER YW025-03 (STICK)

PW602 485923162S CONN WAFER YW025-03 (STICK)

PW603 485923162S CONN WAFER YW025-03 (STICK)

PW604 485923172S CONN WAFER YW025-04 (STICK)

PW605 485923182S CONN WAFER YW025-05 (STICK)

PW701 485923162S CONN WAFER YW025-03 (STICK)

PW702 485923192S CONN WAFER YW025-06 (STICK)

PW807 485923162S CONN WAFER YW025-03 (STICK)

R118 RS01Z100J- R M-OXIDE FILM 1W 10 OHM J (TAPPING)

R850 RS02Z102J- R M-OXIDE FILM 2W 1K OHM J (TAPPING)

ZZ200 PEMPJRD018 PCB MAIN RADIAL AS DSC-3270E

C100 CXRH1H150J C CERA RH 50V 15PF J (TAPPING)

C101 CEXF1C470V C ELECTRO 16V RSS 47MF (5X11) TP

C103 CEXF1H339V C ELECTRO 50V RSS 3.3MF (5X11) TP

C104 CXCH1H220J C CERA 50V CH 22PF J (TAPPING)

C105 CEXF1H100V C ELECTRO 50V RSS 10MF (5X11) TP

C106 CCXB1H471K C CERA 50V B 470PF K (TAPPING)

C107 CEXF1H100V C ELECTRO 50V RSS 10MF (5X11) TP

C109 CEXF1C470V C ELECTRO 16V RSS 47MF (5X11) TP

C116 CEXF1H229V C ELECTRO 50V RSS 2.2MF (5X11) TP

C117 CEXF1H229V C ELECTRO 50V RSS 2.2MF (5X11) TP

C119 CEXF1C470V C ELECTRO 16V RSS 47MF (5X11) TP

C120 CEXF1C470V C ELECTRO 16V RSS 47MF (5X11) TP

C603 CEXF1H100V C ELECTRO 50V RSS 10MF (5X11) TP

C613 CEXF1H339V C ELECTRO 50V RSS 3.3MF (5X11) TP

C616 CEXF1H100V C ELECTRO 50V RSS 10MF (5X11) TP

C617 CEXF1H100V C ELECTRO 50V RSS 10MF (5X11) TP

16V RSS 470MF (10X12.5)BK

16V RSS 470MF (10X12.5)BK

35V RSS 1000MF (13X25) TP

16V RSS 470MF (10X12.5)BK

16V RSS 1000MF (10X20) TP

16V RSS 470MF (10X12.5)BK

35V RSS 1000MF (13X25) TP

35V RSS 1000MF (13X25) TP

35V RSS 1000MF (13X25) TP

35V RSS 1000MF (13X25) TP

35V RSS 1000MF (13X25) TP

35V RSS 1000MF (13X25) TP

16V RSS 1000MF (10X20) TP

16V RSS 470MF (10X12.5)BK

16V RSS 470MF (10X12.5)BK

16V RSS 470MF (10X12.5)BK

C619 CEXF1H100V C ELECTRO 50V RSS 10MF (5X11) TP

C630 CEXF1H100V C ELECTRO 50V RSS 10MF (5X11) TP

C634 CEXF1H100V C ELECTRO 50V RSS 10MF (5X11) TP

C635 CEXF1H100V C ELECTRO 50V RSS 10MF (5X11) TP

C637 CEXF1H339V C ELECTRO 50V RSS 3.3MF (5X11) TP

C638 CEXF1H100V C ELECTRO 50V RSS 10MF (5X11) TP

C640 CEXF1H100V C ELECTRO 50V RSS 10MF (5X11) TP

C641 CEXF1H100V C ELECTRO 50V RSS 10MF (5X11) TP

C643 CEXF1H479V C ELECTRO 50V RSS 4.7MF (5X11) TP

C645 CEXF1H479V C ELECTRO 50V RSS 4.7MF (5X11) TP

C648 CEXF1C470V C ELECTRO 16V RSS 47MF (5X11) TP

C649 CEXF1C470V C ELECTRO 16V RSS 47MF (5X11) TP

C650 CEXF1H479V C ELECTRO 50V RSS 4.7MF (5X11) TP

C651 CEXF1H109V C ELECTRO 50V RSS 1MF (5X11) TP

C652 CEXF1H479V C ELECTRO 50V RSS 4.7MF (5X11) TP

C653 CMXB1H104J C MYLAR 50V EU 0.1MF J (TP)

C654 CMXB1H104J C MYLAR 50V EU 0.1MF J (TP)

C655 CMXB1H104J C MYLAR 50V EU 0.1MF J (TP)

C661 CEXF1H109V C ELECTRO 50V RSS 1MF (5X11) TP

C662 CEXF1V101V C ELECTRO 35V RSS 100MF (8X11.5) TP

C665 CMXB1H104J C MYLAR 50V EU 0.1MF J (TP)

C666 CMXB1H104J C MYLAR 50V EU 0.1MF J (TP)

C667 CEXF1V101V C ELECTRO 35V RSS 100MF (8X11.5) TP

C668 CEXF1H109V C ELECTRO 50V RSS 1MF (5X11) TP

C669 CEXF1H109V C ELECTRO 50V RSS 1MF (5X11) TP

C670 CEXF1H109V C ELECTRO 50V RSS 1MF (5X11) TP

C675 CEXF1H479V C ELECTRO 50V RSS 4.7MF (5X11) TP

C676 CEXF1H479V C ELECTRO 50V RSS 4.7MF (5X11) TP

C677 CEXF1E221V C ELECTRO 25V RSS 220MF (8X11.5) TP

C678 CEXF1H100V C ELECTRO 50V RSS 10MF (5X11) TP

C701 CEXF1H109V C ELECTRO 50V RSS 1MF (5X11) TP

C702 CEXF1C470V C ELECTRO 16V RSS 47MF (5X11) TP

C850 CCXB3A471K C CERA 1KV B 470PF K (T)

C851 CEXF1H220V C ELECTRO 50V RSS 22MF (5X11) TP

C853 CMXL2E104K C MYLAR 250V MEU 0.1MF K

C854 CEXF1E470V C ELECTRO 25V RSS 47MF (5X11) TP

C855 CCXB3A471K C CERA 1KV B 470PF K (T)

C861 CMXL2E104K C MYLAR 250V MEU 0.1MF K

I607 1K1A7042AP IC REGULATOR KIA7042AP

I704 1K1A7042AP IC REGULATOR KIA7042AP

I812 1KA431AZ— IC REGULATOR KA431AZ

L101 5CPX120J— COIL PEAKING 12UH J (RADIAL)

Q101 TKTC3197— TR KTC3197 (TP)

Q102 TKTC3197— TR KTC3197 (TP)

Q103 TKTC3198Y- TR KTC3198Y

Q104 TKTC3198Y- TR KTC3198Y

Q105 TKTC3198Y- TR KTC3198Y

Q601 TKTC3198Y- TR KTC3198Y

Q602 TKTC3198Y- TR KTC3198Y

Q701 TKTC3198Y- TR KTC3198Y

RB2 RV5426103P R SEMI FIXED

X701 5XEX4R000C C RY ST A L QU ART Z

ENV-DJAA03B14 10K OHM B

HC-49/U 4.000MHZ 20PPM TP

31

Page 33

Service Parts List

LOC PART-CODE PART-NAME PART-DESC LOC PART-CODE PART-NAME PART-DESC

ZZ200 PEMPJAD018 PCB MAIN AXIAL AS DSC-3270E

A001 4959805724 PCB MAIN 330 X 246

C115 CCZB1H102K C CERA 50V B 1000PF K AXIAL

C706 CCZB1H222K C CERA

D101 D1N4148— DIODE 1N4148 (TAPPING)

D102 DSHS21—— DIODE SHS21

D602 D1N4148— DIODE 1N4148 (TAPPING)

D603 D1N4148— DIODE 1N4148 (TAPPING)

D610 DUZ8R2BM— DIODE ZENER UZ-8.2B (8.2V)

D701 D1N4148— DIODE 1N4148 (TAPPING)

D702 D1N4148— DIODE 1N4148 (TAPPING)

D703 DUZ5R1BM— DIODE ZENER UZ-5.1BM

D851 DZEG01C— DIODE EG01C

D852 D1N4148— DIODE 1N4148 (TAPPING)

J001 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J002 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J003 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J004 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J005 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J006 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J007 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J008 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J009 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J010 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J011 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J012 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J013 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J014 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J015 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J016 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J017 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J018 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J019 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J020 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J021 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J022 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J023 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J024 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J025 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J026 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J027 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J028 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J029 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J030 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J031 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J032 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J033 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J034 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J035 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J036 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J037 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J038 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

50V HIKB 2200PF K AXL 52M

J039 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J040 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J041 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J042 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J043 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J044 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J045 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J046 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J047 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J048 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J049 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J050 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J051 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J052 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J053 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J054 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J055 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J056 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J057 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J058 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J059 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J060 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J061 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J062 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J063 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J064 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J065 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J066 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J067 RD-AZ102J- R CARBON FILM 1/6 1K OHM J

J068 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J069 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J070 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J071 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J072 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J073 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J074 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J075 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J076 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J077 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J078 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J079 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J080 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J081 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J082 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J083 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J084 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J085 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J086 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J087 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J088 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J089 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J090 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

32

Page 34

Service Parts List

LOC PART-CODE PART-NAME PART-DESC LOC P ART-CODE P ART-NAME PART-DESC

J091 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J092 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J093 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J094 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J095 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J096 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J097 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J098 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J099 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J100 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J101 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J102 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J103 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J104 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J105 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J106 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J107 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J108 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J109 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J110 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J111 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J112 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J113 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J114 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J115 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J116 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J117 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J118 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J119 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J120 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J121 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J122 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J123 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J124 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J125 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J126 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J127 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J128 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J129 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J130 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J131 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J132 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J133 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J134 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J135 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J136 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J137 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J138 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J139 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J140 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J141 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J142 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J143 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J144 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J145 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J146 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J147 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J148 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J149 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J150 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J151 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J152 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J153 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J154 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J155 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J156 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J157 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J158 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J159 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J160 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J161 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J162 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J163 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J164 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J165 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J166 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J167 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J168 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J169 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J170 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J171 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J172 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J173 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J174 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J175 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J176 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

J177 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

L701 5MC0000100 COIL BEAD HC-3550

L702 5MC0000100 COIL BEAD HC-3550

R104 RN-AZ1502F R METAL FILM 1/6 15K OHM F

R105 RN-AZ3600F R METAL FILM 1/6 360.0 OHM F

R106 RD-AZ682J- R CARBON FILM 1/6 6.8K OHM J

R108 RD-AZ102J- R CARBON FILM 1/6 1K OHM J

R109 RD-AZ102J- R CARBON FILM 1/6 1K OHM J

R111 RD-AZ183J- R CARBON FILM 1/6 18K OHM J

R112 RD-AZ223J- R CARBON FILM 1/6 22K OHM J

R113 RD-AZ271J- R CARBON FILM 1/6 270 OHM J

R116 RD-AZ472J- R CARBON FILM 1/6 4.7K OHM J

R117 RD-AZ682J- R CARBON FILM 1/6 6.8K OHM J

R119 RD-4Z100J- R CARBON FILM 1/4 10 OHM J

R601 RD-AZ101J- R CARBON FILM 1/6 100 OHM J

R602 RD-AZ101J- R CARBON FILM 1/6 100 OHM J

R604 RD-AZ101J- R CARBON FILM 1/6 100 OHM J

R605 RD-AZ101J- R CARBON FILM 1/6 100 OHM J

33

Page 35

Service Parts List

LOC PART-CODE PART-NAME PART-DESC LOC PART-CODE PART-NAME PART-DESC

R606 RD-2Z470J- R CARBON FILM 1/2 47 OHM J

R608 RD-AZ152J- R CARBON FILM 1/6 1.5K OHM J

R609 RD-AZ152J- R CARBON FILM 1/6 1.5K OHM J

R610 RD-AZ113J- R CARBON FILM 1/6 11K OHM J

R617 RD-AZ152J- R CARBON FILM 1/6 1.5K OHM J

R618 RD-AZ152J- R CARBON FILM 1/6 1.5K OHM J

R619 RD-AZ393J- R CARBON FILM 1/6 39K OHM J

R620 RD-AZ393J- R CARBON FILM 1/6 39K OHM J

R623 RD-4Z220J- R CARBON FILM 1/4 22 OHM J

R624 RD-4Z220J- R CARBON FILM 1/4 22 OHM J

R627 RD-2Z104J- R CARBON FILM 1/2 100K OHM J

R628 RD-2Z104J- R CARBON FILM 1/2 100K OHM J

R629 RD-2Z104J- R CARBON FILM 1/2 100K OHM J

R630 RD-4Z229J- R CARBON FILM 1/4 2.2 OHM J

R631 RD-4Z229J- R CARBON FILM 1/4 2.2 OHM J

R632 RD-4Z229J- R CARBON FILM 1/4 2.2 OHM J

R633 RD-4Z229J- R CARBON FILM 1/4 2.2 OHM J

R635 RD-2Z104J- R CARBON FILM 1/2 100K OHM J

R636 RD-2Z104J- R CARBON FILM 1/2 100K OHM J

R637 RD-AZ152J- R CARBON FILM 1/6 1.5K OHM J

R638 RD-AZ103J- R CARBON FILM 1/6 10K OHM J

R654 RD-4Z229J- R CARBON FILM 1/4 2.2 OHM J

R673 RD-4Z301J- R CARBON FILM 1/4 300 OHM J

R674 RD-4Z301J- R CARBON FILM 1/4 300 OHM J

R701 85801065GY WIRE COPPER AWG22 1/0.65 TIN COATING

R702 RD-AZ102J- R CARBON FILM 1/6 1K OHM J

R703 RD-AZ334J- R CARBON FILM 1/6 330K OHM J

R704 RD-AZ103J- R CARBON FILM 1/6 10K OHM J

R705 RD-4Z100J- R CARBON FILM 1/4 10 OHM J

R706 RD-4Z100J- R CARBON FILM 1/4 10 OHM J

R707 RD-AZ472J- R CARBON FILM 1/6 4.7K OHM J

R708 RD-AZ222J- R CARBON FILM 1/6 2.2K OHM J

R709 RD-AZ362J- R CARBON FILM 1/6 3.6K OHM J

R713 RD-AZ622J- R CARBON FILM 1/6 6.2K OHM J

R714 RD-AZ101J- R CARBON FILM 1/6 100 OHM J

R715 RD-AZ101J- R CARBON FILM 1/6 100 OHM J

R716 RD-AZ101J- R CARBON FILM 1/6 100 OHM J

R717 RD-AZ471J- R CARBON FILM 1/6 470 OHM J

R718 RD-AZ222J- R CARBON FILM 1/6 2.2K OHM J

R719 RD-AZ102J- R CARBON FILM 1/6 1K OHM J

R720 RD-AZ472J- R CARBON FILM 1/6 4.7K OHM J

R721 RD-AZ223J- R CARBON FILM 1/6 22K OHM J

R722 RD-AZ101J- R CARBON FILM 1/6 100 OHM J

R723 RD-AZ101J- R CARBON FILM 1/6 100 OHM J