Cypress Semiconductor CY7C1041CV33-12BAC, CY7C1041CV33-10ZI, CY7C1041CV33-10ZC, CY7C1041CV33-10VI, CY7C1041CV33-10VC Datasheet

...

CY7C1041CV33

256K x 16 Static RAM

Features

• Pin equivalent to CY7C1041BV33

• High speed

—t

= 10 ns

AA

• Low active power

—324 mW (max.)

• 2.0V data retention

• Automatic power-down when deselected

• TTL-compatible inpu ts and outputs

• Easy memory expansion with CE

Functional Description

[1]

and OE features

HIGH Enable (BHE

–I/O15) is written into the location specified on the

(I/O

8

address pins (A

Reading from the device is accomplished by taking Chip

Enable (CE

) and Output Enable (OE) LOW while forcing the

Write Enable (WE

then data from the memory location specified by the address

pins will appear on I/O

LOW , then d ata f rom memory will a ppear on I/O

the truth table at the back of this data sheet for a complete

description of Read and Write modes.

The input/output pins (I/O

high-impedance state when the device is deselected (CE

HIGH), the outputs are disabled (OE HIGH), the BHE an d BLE

) is LOW, then data from I/O pins

).

0–A17

) HIGH. If Byte LOW Enable (BLE) is LOW,

– I/O7. If Byte HIGH Enable (BHE) is

0

–I/O15) are placed in a

0

are disabled (BHE, BLE HIGH), or during a Writ e operation

The CY7C1041CV33 is a high-performance CMOS Static

RAM organized as 262,144 words by 16 bits.

Writing to the device is accomplished by taking Chip Enable

) and Write Enable (WE) input s LOW. If Byte LOW En able

(CE

(BLE) is LOW, then data from I/O pins (I/O0–I/O7), is written

into the location sp ecified on the address pin s (A

0–A17

). If Byte

LOW, and WE LOW).

(CE

The CY7C1041CV33 is available in a standard 44-pin

400-mil-wide body width SOJ and 44-pin TSOP II package

with center power and ground (revolutionary) pinout, as well

as a 48-ball fine-pitch ball grid array (FBGA) package.

Logic Block Diagram Pin Configuration

SOJ

I/O

I/O

I/O

I/O

V

V

I/O

I/O

I/O

I/O

WE

A

A

A

A

A

CE

CC

SS

A

A

A

A

A

0

1

2

3

4

0

1

2

3

4

5

6

7

5

6

7

8

9

TSOP II

Top View

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

INPUT BUFFER

A

0

A

1

A

2

A

3

A

4

A

5

A

A

A

ROW DECODER

6

7

8

256K × 16

1024 x 4096

COLUMN

DECODER

9

10

A

A

A

ARRAY

11

12

A13A

14

15

AAA

SENSE AMPS

16

17

A

I/O0–I/O

I/O8–I/O

BHE

7

15

WE

CE

OE

BLE

A

17

A

16

A

15

OE

BHE

BLE

I/O

I/O

I/O

I/O

V

SS

V

CC

I/O

I/O

I/O

I/O

NC

A

14

A

13

A

12

A

11

A

10

15

14

13

12

11

10

9

8

to I/O15. See

8

Selection Guide

-8 -10 -12 -15 -20 Unit

Maximum Access Time 8 10121520ns

Maximum Operating Current Commercial 100 90 85 80 75 mA

Industrial 110 100 95 90 85 mA

Maximum CMOS Standby Current Commercial/

Industrial

Shaded areas contain advance information.

Note:

1. For guidelines on SRAM system design, please refer to the “System Design Guidelines” Cypress ap plicati on note, ava ilable on the intern et at www .cypr ess.com.

Cypress Semiconductor Corporation • 3901 North First Street • San Jose • CA 95134 • 408-943-2600

Document #: 38-05134 Rev. *D Revised October 18, 2002

10 10 10 10 10 mA

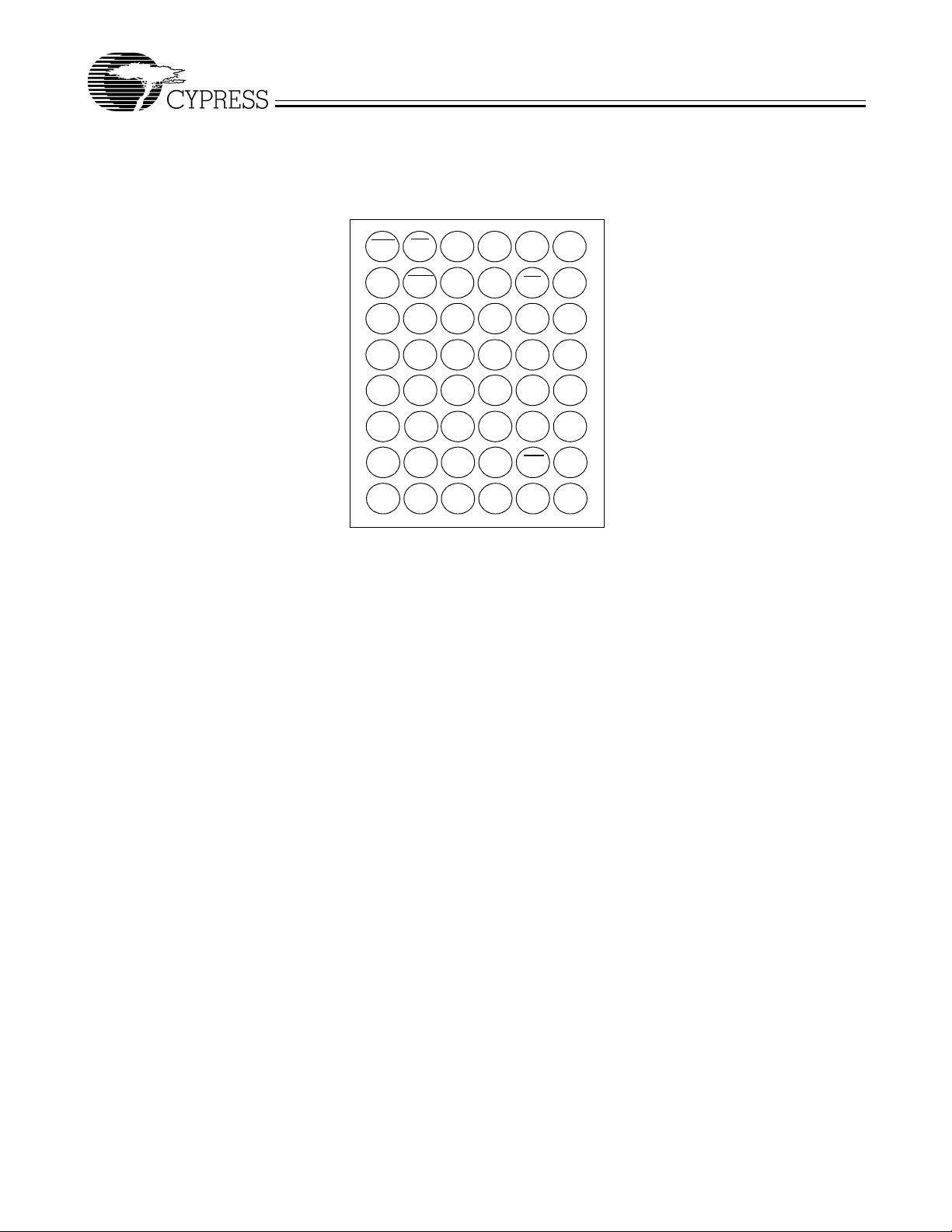

Pin Configurations

48-ball Mini FBGA

(Top View)

1

2

CY7C1041CV33

4

3

5

6

BLE

I/O

I/O

V

SS

V

CC

I/O

I/O

NC

A

OE

BHE

0

I/O

1

I/O

I/O

I/O

6

NC

7

0

A

3

A

2

5

A

3

17

NC

4

A

14

5

A

12

A

A

9

8

A

A

1

A

4

A

6

A

7

A

16

A

15

A

13

A

10

CE

I/O

I/O

I/O

I/O

WE

A

NC

2

I/O

I/O

10

V

CC

11

V

12

I/O

13

I/O

NC

11

SS

A

B

8

C

9

D

E

F

14

G

15

H

Document #: 38-05134 Rev. *D Page 2 of 11

Maximum Ratings

(Above which the useful life may be impaired. For user guidelines, not tested.)

Storage Temperature .................................–65°C to +150°C

Ambient Temperature with

Power Applied.............................................–55°C to +125°C

Supply Voltage on V

DC Voltage Applied to Outputs

in High-Z State

[2]

to Relative GND

CC

....................................–0.5V to VCC + 0.5V

[2]

....–0.5V to +4.6V

DC Electrical Characteristics Over the Operating Range

Parameter Description Test Conditions

V

OH

V

OL

V

IH

[2]

V

IL

I

IX

I

OZ

I

CC

I

SB1

I

SB2

Shaded areas contain advance information.

Output HIGH Voltage VCC = Min.,

= –4.0 mA

I

OH

Output LOW V o lt a ge VCC = Min.,

= 8.0 mA

I

OL

Input HIGH Voltage 2.0 V

Input LOW Voltage –0.3 0.8 –0.3 0.8 –0.3 0.8 –0.3 0.8 –0.3 0.8 V

Input Load Current GND < VI < V

Output Leakage

Current

VCC Operating

Supply Current

Automatic CE

Power-down Current

—TTL Inputs

Automatic CE

Power-down Current

—CMOS Inputs

GND < V

Output Disabled

VCC = Max., f = f

1/t

RC

Max. V

VIN > VIH or

< VIL, f = f

V

IN

Max. VCC,

> VCC – 0.3V,

CE

> VCC – 0.3V,

V

IN

< 0.3V, f = 0

or V

IN

OUT

, CE > V

CC

CC

< VCC,

MAX

IH

MAX

=

Comm’l 10090858075mA

Indus.

Comm’l

Indus.

CY7C1041CV33

[2]

DC Input Voltage

Current into Outputs (LOW) ........................................ 20 mA

Operating Range

Range

Commercial 0°C to +70°C 3.3V ± 0.3V

Industrial –40°C to +85°C

-8 -10 -12 -15 -20

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max.

2.4 2.4 2.4 2.4 2.4 V

0.4 0.4 0.4 0.4 0.4 V

CC

+ 0.3

–1 +1 –1+1–1+1–1+1–1+1µA

–1 +1 –1+1–1+1–1+1–1+1µA

110 100 95 90 85 mA

40 40 40 40 40 mA

10 10 10 10 10 mA

................................–0.5V to VCC + 0.5V

Ambient

Temperature V

2.0 V

CC

+ 0.3

2.0 V

CC

+ 0.3

2.0 V

CC

+ 0.3

2.0 V

CC

CC

+ 0.3

Unit

V

Capacitance

[3]

Parameter Description Test Conditions Max. Unit

C

IN

C

OUT

Notes:

2. Minimum voltage is–2.0V for pulse durations of less than 20 ns.

3. Tested initially and after any design or process changes that may affect these parameters.

Input Capacitance TA = 25°C, f = 1 MHz, VCC = 3.3V 8 pF

I/O Capacitance 8 pF

Document #: 38-05134 Rev. *D Page 3 of 11

CY7C1041CV33

AC Switching Characteristics

[4]

Over the Operating Range

-8 -10 -12 -15 -20

Parameter Description

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max.

Read Cycle

[5]

t

power

t

RC

t

AA

t

OHA

t

ACE

t

DOE

t

LZOE

t

HZOE

t

LZCE

t

HZCE

t

PU

t

PD

t

DBE

t

LZBE

t

HZBE

Write Cycle

t

WC

t

SCE

t

AW

t

HA

t

SA

t

PWE

t

SD

t

HD

t

LZWE

t

HZWE

t

BW

Shaded areas contain advance inform atio n.

Notes:

4. Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V.

5. t

POWER

6. t

HZOE

7. At any given temperature and voltage condition, t

8. The internal Write time of the memory is defined by the overlap of CE

either of these signals can terminate the Write. The input data set-up and hold timing should be referenced to the leading edge of the signal that terminates

the Write.

9. The minimum Write cycle time for Write Cycle No. 3 (WE

VCC(typical) to the first access 1 1111µs

Read Cycle T ime 8 10 12 15 20 ns

Address to Data Valid 810121520ns

Data Hold from Address Ch ang e 3 3333ns

CE LOW to Data Valid 810121520ns

OE LOW to Data Valid 456 7 8ns

OE LOW to Low-Z 0 0000ns

[7]

[6, 7]

[6, 7]

456 7 8ns

3 3333ns

456 7 8ns

OE HIGH to High-Z

CE LOW to Low-Z

CE HIGH to Hi gh-Z

CE LOW to Power-Up 0 0000ns

CE HIGH to Power-Down 810121520ns

Byte Enable to Data Valid 456 7 8ns

Byte Enable to Low-Z 0 0000ns

Byte Disable to High-Z 666 7 8ns

[8, 9]

Write Cycle Time 8 10 12 15 20 ns

CE LOW to Write End 6 7 8 10 10 ns

Address Set-Up to Write End 6 7 8 10 10 ns

Address Hol d from Write End 0 0000ns

Address Set-Up to Write Start 0 0000ns

WE Pulse Width 6 7 8 10 10 ns

Data Set-Up to Write End 4 5678ns

Data Hold from Write End 0 0000ns

WE HIGH to Low-Z

WE LOW to High-Z

[7]

[6, 7]

3 3333ns

456 7 8ns

Byte Enable to End of Write 6 7 8 10 10 ns

gives the minimum amount of time that the power supply should be at typical VCC values until the first memory access can be performed.

, t

HZCE

, and t

are specified with a load capacitance of 5 pF as in part (d) of AC Test Loads. Transition is measured ±500 mV from steady-state voltage.

HZWE

is less than t

HZCE

controlled, OE LOW) is the sum of t

, t

LZCE

HZOE

LOW, and WE LOW. CE and WE must be LOW to initiate a Write, and the transition of

is less than t

LZOE

HZWE

, and t

and tSD.

is less than t

HZWE

for any given device.

LZWE

Unit

Document #: 38-05134 Rev. *D Page 4 of 11

Loading...

Loading...