Page 1

Technical Reference Guide

For the

Compaq iPAQ Series of

Desktop Personal Computers

Covers iPAQ 1.0, 1.2, and 2.0 Models

Page 2

This hardcopy is designed to be placed into a standard 3-ring binder. Provided below is a title block that

can be copied and cut out and placed into the slip or taped onto the edge of the binder.

iPAQ Series of Desktop Personal Computers

TRG

Page 3

Reader Feedback

Please feel free to send any quest i ons, suggestions, co rrections, o r comments regarding this

document please to the following email address:

CPCG.Training@compaq.com

When responding, please state the title of the referenced document.

Page 4

Page 5

Technical Reference Guide

NOTICE

The information in this document is subject to change without notice.

COMPAQ COMPUTER CORPORATION SHALL NOT BE LIABLE FOR TECHNICAL OR

EDITORIAL ERRORS OR OMISSIONS HEREIN; NOR FOR INCIDENTAL OR

CONSEQUENTIAL DAMAGES RESULTING FROM THE FURNISHING, PERFORMANCE,

OR USE OF THIS MATERIAL. IT IS THE RESPONSIBILITY OF MANUFACTURERS TO

ENSURE THAT DEVICES DESIGNED TO BE USED WITH COMPAQ PRODUCTS

COMPLY WITH FCC CLASS B EMISSIONS REQUIREMENTS.

This guide contains information protected by copyright. Except for use as a reference for the

described Compaq product, no part of this document may be photocopied or reproduced in any

form without prior written consent from Compaq Computer Corporation.

2000 Compaq Computer Corporation

All rights reserved.

Compaq, t he Compaq logo ar e registered in the U.S. Patent and Trademark Office.

iPAQ is a trademark of Compaq Information Technologies Group, L.P.

Microsoft, Windows, Windows NT, and other names of Microsoft products referenced herein are trademarks or registered

trademarks of Microsoft Corporation.

Alert on LAN, Wake on LAN, and Ethernet names/brands are the property of IBM Corporation.

Intel and Pentium are registered trademarks of Intel Corporation. Celeron and MMX are trademarks of Intel Corporation.

Product names mentioned in this document may be trademarks and/or registered trademarks of other companies.

For more information regarding specifications and Compaq-specific parts please contact Compaq

Computer Corporation at http://www.compaq.com .

Technical Reference Guide

For the

Compaq iPAQ Series of Desktop Personal Computers

Second Edition – February 2001

Document Number 127M-0300B-WWEN

Compaq iPAQ Series of Desktop Personal Computers

i

Second Edition - February 2001

Page 6

Technical Reference Guide

Compaq iPAQ Series of Desktop Personal Computers

ii

Second Edition –- February 2001

Page 7

Technical Reference Guide

TABLE OF CONTENTS

CHAPTER 1 INTRODUCTION...................................................................................................................

1.1 ABOUT THIS GUIDE................................................................................................................ 1-1

1.1.1 USING THIS GUIDE.......................................................................................................... 1-1

1.2 ADDITIONAL INFORMATION SOURCES............................................................................. 1-2

1.3 MODEL NUMBERING CONVENTION................................................................................... 1-2

1.4 SERIAL NUMBER..................................................................................................................... 1-2

1.5 NOTATIONAL CONVENTIONS.............................................................................................. 1-3

1.5.1 VALUES ............................................................................................................................. 1-3

1.5.2 RANGES............................................................................................................................. 1-3

1.5.3 REGISTER NOTATION AND USAGE............................................................................. 1-3

1.5.4 BIT NOTATION AND BYTE VALUES............................................................................ 1-3

1.6 COMMON ACRONYMS AND ABBREVIATIONS................................................................. 1-4

CHAPTER 2 SYSTEM OVERVIEW...........................................................................................................

2.1 INTRODUCTION....................................................................................................................... 2-1

2.2 FEATURES AND OPTIONS...................................................................................................... 2-2

2.2.1 STANDARD FEATURES...................................................................................................2-2

2.2.2 OPTIONS............................................................................................................................ 2-3

2.3 MECHANICAL DESIGN........................................................................................................... 2-4

2.3.1 CABINET LAYOUTS ........................................................................................................ 2-4

2.3.2 CHASSIS LAYOUTS......................................................................................................... 2-6

2.3.3 SYSTEM BOARD LAYOUTS........................................................................................... 2-8

2.4 SYSTEM ARCHITECTURE.................................................................................................... 2-10

2.4.1 IPAQ 1.0/1.2 ARCHITECTURE....................................................................................... 2-10

2.4.2 IPAQ 2.0 ARCHITECTURE............................................................................................. 2-12

2.4.3 PROCESSORS.................................................................................................................. 2-14

2.4.4 CHIPSET........................................................................................................................... 2-16

2.4.5 SUPPORT COMPONENTS.............................................................................................. 2-17

2.4.6 SYSTEM MEMORY......................................................................................................... 2-17

2.4.7 MASS STORAGE............................................................................................................. 2-18

2.4.8 SERIAL AND PARALLEL INTERFACES...................................................................... 2-18

2.4.9 UNIVERSAL SERIAL BUS INTERFACE ...................................................................... 2-18

2.4.10 GRAPHICS SUBSYSTEM............................................................................................... 2-18

2.4.11 AUDIO SUBSYSTEM...................................................................................................... 2-19

2.5 SPECIFICATIONS ................................................................................................................... 2-19

CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM.............................................................................

3.1 INTRODUCTION....................................................................................................................... 3-1

3.2 PROCESSOR .............................................................................................................................. 3-2

3.2.1 CELERON PROCESSOR................................................................................................... 3-2

3.2.2 PENTIUM III PROCESSOR............................................................................................... 3-3

3.2.3 PROCESSOR UPGRADING.............................................................................................. 3-4

3.3 MEMORY SUBSYSTEM........................................................................................................... 3-5

3.4 SUBSYSTEM CONFIGURATION............................................................................................ 3-8

Compaq iPAQ Series of Desktop Personal Computers

iii

Second Edition - February 2001

Page 8

Technical Reference Guide

CHAPTER 4 SYSTEM SUPPORT...............................................................................................................

4.1 INTRODUCTION....................................................................................................................... 4-1

4.2 PCI BUS OVERVIEW................................................................................................................ 4-2

4.2.1 PCI BUS TRANSACTIONS............................................................................................... 4-3

4.2.2 PCI SUB-BUSSES.............................................................................................................. 4-5

4.2.3 PCI CONFIGURATION..................................................................................................... 4-6

4.3 SYSTEM RESOURCES .............................................................................................................4-7

4.3.1 INTERRUPTS..................................................................................................................... 4-7

4.3.2 DIRECT MEMORY ACCESS.......................................................................................... 4-10

4.4 SYSTEM CLOCK DISTRIBUTION........................................................................................ 4-11

4.5 REAL-TIME CLOCK AND CONFIGURATION MEMORY ................................................. 4-11

4.5.1 CLEARING CMOS........................................................................................................... 4-12

4.5.2 CMOS ARCHIVE AND RESTORE................................................................................. 4-12

4.5.3 STANDARD CMOS LOCATIONS.................................................................................. 4-13

4.6 SYSTEM MANAGEMENT...................................................................................................... 4-22

4.6.1 SECURITY FUNCTIONS ................................................................................................ 4-22

4.6.2 POWER MANAGEMENT................................................................................................ 4-23

4.6.3 SYSTEM STATUS ........................................................................................................... 4-24

4.6.4 TEMPERATURE SENSING AND COOLING................................................................ 4-25

4.7 REGISTER MAP AND MISCELLANEOUS FUNCTIONS.................................................... 4-26

4.7.1 SYSTEM I/O MAP ........................................................................................................... 4-26

4.7.2 82801 ICH GENERAL PURPOSE FUNCTIONS............................................................ 4-27

4.7.3 I/O CONTROLLER FUNCTIONS .................................................................................. 4-28

4.7.4 820802 FWH FUNCTIONS.............................................................................................. 4-30

CHAPTER 5 INPUT/OUTPUT INTERFACES..........................................................................................

5.1 INTRODUCTION....................................................................................................................... 5-1

5.2 ENHANCED IDE INTERFACE................................................................................................. 5-1

5.2.1 IDE PROGRAMMING....................................................................................................... 5-1

5.2.2 PRIMARY IDE INTERFACE............................................................................................. 5-3

5.2.3 SECONDARY IDE INTERFACE.......................................................................................5-4

5.3 DISKETTE DRIVE INTERFACE.............................................................................................. 5-5

5.4 SERIAL INTERFACE................................................................................................................ 5-6

5.4.1 RS-232 INTERFACE.......................................................................................................... 5-6

5.4.2 SERIAL TEST INTERFACE............................................................................................. 5-7

5.4.3 SERIAL INTERFACE PROGRAMMING ......................................................................... 5-7

5.5 PARALLEL INTERFACE.......................................................................................................... 5-9

5.5.1 STANDARD PARALLEL PORT MODE........................................................................... 5-9

5.5.2 ENHANCED PARALLEL PORT MODE .......................................................................... 5-9

5.5.3 EXTENDED CAPABILITIES PORT MODE .................................................................. 5-10

5.5.4 PARALLEL INTERFACE PROGRAMMING................................................................. 5-10

5.5.5 PARALLEL INTERFACE CONNECTOR....................................................................... 5-14

5.6 KEYBOARD/POINTING DEVICE INTERFACE................................................................... 5-15

5.6.1 KEYBOARD INTERFACE OPERATION....................................................................... 5-15

5.6.2 POINTING DEVICE INTERFACE OPERATION .......................................................... 5-17

5.6.3 KEYBOARD/POINTING DEVICE INTERFACE PROGRAMMING........................... 5-17

5.6.4 KEYBOARD/POINTING DEVICE INTERFACE CONNECTOR.................................. 5-21

5.7 UNIVERSAL SERIAL BUS INTERFACE .............................................................................. 5-22

5.7.1 USB DATA FORMATS.................................................................................................... 5-23

5.7.2 USB PROGRAMMING.................................................................................................... 5-24

5.7.3 USB CONNECTOR.......................................................................................................... 5-25

5.7.4 USB CABLE DATA......................................................................................................... 5-25

Compaq iPAQ Series of Desktop Personal Computers

iv

Second Edition –- February 2001

Page 9

Technical Reference Guide

5.8 AUDIO SUBSYSTEM..............................................................................................................5-26

5.8.1 FUNCTIONAL ANALYSIS............................................................................................. 5-26

5.8.2 AC97 AUDIO CONTROLLER......................................................................................... 5-28

5.8.3 AC97 LINK BUS ..............................................................................................................5-28

5.8.4 AUDIO CODEC ................................................................................................................5-29

5.8.5 AUDIO PROGRAMMING............................................................................................... 5-30

5.8.6 AUDIO SPECIFICATIONS.............................................................................................. 5-31

5.9 NETWORK INTERFACE CONTROLLER............................................................................. 5-32

5.9.1 WAKE ON LAN............................................................................................................... 5-33

5.9.2 ALERT ON LAN...............................................................................................................5-33

5.9.3 POWER MANAGEMENT SUPPORT............................................................................. 5-34

5.9.4 NIC PROGRAMMING..................................................................................................... 5-35

CHAPTER 6 GRAPHICS SUBSYSTEM.....................................................................................................

6.1 INTRODUCTION....................................................................................................................... 6-1

6.1.1 FEATURE SUMMARY...................................................................................................... 6-1

6.2 FUNCTIONAL DESCRIPTION................................................................................................. 6-2

6.2.1 DISPLAY MODES ............................................................................................................. 6-4

6.3 PROGRAMMING....................................................................................................................... 6-5

6.4 MONITOR POWER MANAGEMENT CONTROL.................................................................. 6-5

6.5 MONITOR CONNECTOR......................................................................................................... 6-6

6.6 UPGRADING GRAPHICS......................................................................................................... 6-6

CHAPTER 7 POWER SUPPLY AND DISTRIBUTION...........................................................................

7.1 INTRODUCTION....................................................................................................................... 7-1

7.2 POWER SUPPLY ASSEMBLY/CONTROL ............................................................................. 7-1

7.2.1 POWER SUPPLY ASSEMBLY......................................................................................... 7-2

7.2.2 POWER CONTROL ........................................................................................................... 7-3

7.3 POWER DISTRIBUTION .......................................................................................................... 7-4

7.3.1 3.3/5/12 VDC DISTRIBUTION.......................................................................................... 7-4

7.3.2 LOW VOLTAGE DISTRIBUTION ................................................................................... 7-6

7.4 SIGNAL DISTRIBUTION..........................................................................................................7-7

CHAPTER 8 BIOS ROM..............................................................................................................................

8.1 INTRODUCTION....................................................................................................................... 8-1

8.2 IPAQ 2.0 FEATURES................................................................................................................. 8-2

8.3 DESKTOP MANAGEMENT SUPPORT................................................................................... 8-3

8.3.1 SYSTEM ID........................................................................................................................ 8-4

8.3.2 EDID RETRIEVE ............................................................................................................... 8-5

8.3.3 DRIVE FAULT PREDICTION........................................................................................... 8-5

8.3.4 SYSTEM MAP RETRIEVAL............................................................................................. 8-6

8.3.5 FLASH ROM FUNCTIONS............................................................................................... 8-7

8.3.6 POWER BUTTON FUNCTIONS....................................................................................... 8-7

8.3.7 ACCESSING CMOS........................................................................................................... 8-8

8.3.8 ACCESSING CMOS FEATURE BITS .............................................................................. 8-8

8.3.9 SECURITY FUNCTIONS ................................................................................................ 8-10

8.4 MEMORY DETECTION AND CONFIGURATION............................................................... 8-11

Compaq iPAQ Series of Desktop Personal Computers

v

Second Edition - February 2001

Page 10

Technical Reference Guide

8.5 PNP SUPPORT ......................................................................................................................... 8-12

8.5.1 SMBIOS............................................................................................................................ 8-13

8.6 POWER MANAGEMENT FUNCTIONS................................................................................ 8-14

8.6.1 INDEPENDENT PM SUPPORT ...................................................................................... 8-14

8.6.2 ACPI SUPPORT................................................................................................................ 8-15

8.6.3 APM 1.2 SUPPORT.......................................................................................................... 8-15

8.7 USB LEGACY SUPPORT........................................................................................................ 8-17

8.8 BIOS UPGRADING.................................................................................................................. 8-18

APPENDIX A ERROR MESSAGES AND CODES....................................................................................

A.1 INTRODUCTION.......................................................................................................................A-1

A.2 BEEP/KEYBOARD LED CODES..............................................................................................A-1

A.3 POWER-ON SELF TEST (POST ) MESSAGES ........................................................................A-2

A.4 SYSTEM ERROR MESSAGES (1

A.5. MEMORY ERROR MESSAGES (2

A.6 KE Y BOARD ERROR MESSAGES (30

A.7 PRINTER ERROR MESSAGES (4

A.8 VIDEO (GRAPHICS) ERROR MESSAGES (5

A.9 DISKET TE DRIVE ERROR MESSAGES (6

A.10 SERIAL INTERFACE ERROR MESSAGES (11

A.11 MODEM COMMUNICATIONS ERROR MESSAGES (12

A.12 SYSTEM STATUS ERROR MESSAGES (16

A.13 HARD DRIVE ERROR MESSAGES (17

A.14 HARD DRIVE ERROR MESSAGES (19

A.15 VIDEO (GRAPHICS) ERROR MESSAGES (24

A.16 AUDIO ERROR MESSAGES (3206A.17 DVD/CD-ROM ERROR MESSAGES (33

A.18 NETWORK INTERFACE ERROR MESSAGES (60

A.19 SCSI INTERFACE ERROR MESSAGES (65

A.20 POINTING DEVICE INTERFACE ERROR MESSAGES (8601-

) .................................................................................A-3

XX-XX

) ...............................................................................A-4

XX-XX

) ...........................................................................A-4

X-XX

).................................................................................A-5

XX-XX

)..............................................................A-5

XX-XX

).................................................................A-6

XX-XX

)...........................................................A-6

XX-XX

)..........................................A-7

XX-XX

) ...............................................................A-8

XX-XX

).......................................................................A-8

XX-XX

).......................................................................A-9

XX-XX

)............................................................A-9

XX-XX

).................................................................................A-10

XX

)....................................................................A-10

XX-XX

) ..................................................A-10

XX-XX

, 66XX-XX, 67XX-XX).............................A-11

XX-XX

).....................................A-11

XX

APPENDIX B ASCII CHARACTER SET...................................................................................................

B.1 INTRODUCTION.......................................................................................................................B-1

APPENDIX C KEYBOARD..........................................................................................................................

C.1 INTRODUCTION.......................................................................................................................C-1

C.2 KEYSTROKE PROCESSING....................................................................................................C-2

C.2.1 PS/2-TYPE KEYBOARD TRANSMISSIONS...................................................................C-3

C.2.2 USB-TYPE KEYBOARD TRANSMISSIONS...................................................................C-4

C.2.3 KEYBOARD LAYOUTS....................................................................................................C-5

C.2.4 KEYS...................................................................................................................................C-8

C.2.5 KEYBOARD COMMANDS.............................................................................................C-11

C.2.6 SCAN CODES...................................................................................................................C-11

C.3 CONNECTORS.........................................................................................................................C-16

Compaq iPAQ Series of Desktop Personal Computers

vi

Second Edition –- February 2001

Page 11

LIST OF FIGURES

Technical Reference Guide

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

2–1. C

2–2. C

2–3. C

2–4. C

2–5. C

2–6. C

2–7. C

2–8. C

2–9. C

OMPAQ I

OMPAQ I

OMPAQ I

OMPAQ I

OMPAQ I

OMPAQ I

OMPAQ I

OMPAQ I

OMPAQ I

2–10. P

3–1. P

3–2. C

3–3. P

3–4. S

ROCESSOR/MEMORY SUBSYSTEM ARCHITECTURE

ELERON PROCESSOR INTERNAL ARCHITECTURE

ENTIUM

YSTEM MEMORY MAP

4-1. PCI B

4-2. C

ONFIGURATION CYCLE

4-3. PCI C

4-4. M

4-5. C

5-1.

5-2.

5-3.

5-4.

5-5.

5-6.

5-7.

5-8.

5-9.

5-10.

5-11.

5-12.

5-13.

5-14.

5-15.

ASKABLE INTERRUPT PROCESSING

ONFIGURATION MEMORY MAP

40-P

68-P

SERIAL INTERFACE CONNECTOR (MALE

SERIAL INTERFACE HEADER (I

PARALLEL INTERFACE CONNECTOR (FEMALE

8042-TO-K

KEYBOARD OR POINTING DEVICE INTERFACE CONNECTOR

USB I/F, B

USB P

UNIVERSAL SERIAL BUS CONNECTOR

AUDIO SUBSYSTEM FUNCTIONAL BLOCK DIAGRAM

AC’97 L

AD1881

NETWORK INTERFACE CONTROLLER BLOCK DIAGRAM

ETHERNET

PAQ D

ESKTOP PERSONAL COMPUTERS

PAQ D

ESKTOPS

PAQ D

ESKTOPS

PAQ 1.0/1.2 D

PAQ 2.0 C

PAQ 1.0/1.2 S

PAQ 2.0 S

PAQ 1.0/1.2 A

PAQ 2.0 A

ROCESSOR ASSEMBLY AND MOUNTING

III P

ROCESSOR INTERNAL ARCHITECTURE

, F

RONT VIEWS

, R

EAR VIEWS

ESKTOP CHASSIS LAYOUT

HASSIS LAYOUT

YSTEM BOARD LAYOUTS

YSTEM BOARD LAYOUT

RCHITECTURE

RCHITECTURE

............................................................................. 2-4

............................................................................... 2-5

.................................................................................... 2-7

, B

LOCK DIAGRAM

, B

LOCK DIAGRAM

........................................................................... 2-15

........................................................................ 2-9

......................................................................................................... 3-7

US DEVICES AND FUNCTIONS

......................................................................................... 4-2

......................................................................................................... 4-4

ONFIGURATION SPACE MAPPING

................................................................................... 4-5

, B

LOCK DIAGRAM

........................................................................................... 4-11

IN PRIMARY

IN MULTIBAY CONNECTOR (ON MULTIBAY BOARD

IDE C

ONNECTOR (ON SYSTEM BOARD

DB-9

PAQ 1.2

LEGACY-FREE AND

AS VIEWED FROM REAR OF CHASSIS

DB-25

EYBOARD TRANSMISSION OF CODE EDH

LOCK DIAGRAM

ACKET FORMATS

................................................................................................... 5-22

........................................................................................................ 5-23

................................................................................. 5-25

INK BUS PROTOCOL

AD1885 A

OR

TPE C

ONNECTOR

.............................................................................................. 5-28

UDIO CODEC FUNCTIONAL BLOCK DIAGRAM

(RJ-45,

VIEWED FROM CARD EDGE

................................................................. 2-1

.............................................................. 2-6

................................................................ 2-8

................................................... 2-11

......................................................... 2-13

.............................................................. 3-1

................................................................. 3-2

............................................................. 3-3

........................................................ 4-7

). ...................................................... 5-3

)........................................................ 5-4

)............... 5-6

2.0

SYSTEM BOARDS ONLY

AS VIEWED FROM REAR OF CHASSIS

, T

IMING DIAGRAM

.............................. 5-15

)........ 5-7

)..5-14

.................................................. 5-21

........................................................... 5-27

................................. 5-29

...................................................... 5-32

)...................................... 5-36

F

F

F

F

F

F

F

F

F

6-1. G

IGURE

6-2. GMCH I

IGURE

7–1.

IGURE

IGURE

IGURE

IGURE

IGURE

IGURE

IGURE

POWER DISTRIBUTION AND CONTROL

7–2. IPAQ 1.0/1.2 P

7–3. IPAQ 2.0 P

7–4. IPAQ 1.0/1.2 S

7–5. IPAQ 2.0 S

7–6. S

B–1. ASCII C

RAPHICS SUBSYSTEM

NTEGRATED GRAPHICS SUBSYSTEM

OWER CABLE DIAGRAM

IGNAL DISTRIBUTION DIAGRAM

YSTEM BOARD HEADER PINOUTS

HARACTER SET

Compaq iPAQ Series of Desktop Personal Computers

, B

LOCK DIAGRAM

.............................................................................. 6-2

......................................................................... 6-3

, B

LOCK DIAGRAM

OWER CABLE DIAGRAM

................................................................................. 7-4

....................................................................................... 7-5

IGNAL DISTRIBUTION DIAGRAM

........................................................................... 7-8

........................................................................................ 7-9

........................................................................................................B-1

Second Edition - February 2001

....................................................... 7-1

..................................................................... 7-7

vii

Page 12

Technical Reference Guide

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

C–1. K

EYSTROKE PROCESSING ELEMENTS

C–2. PS/2 K

C–3. U.S. E

C–4. N

C–5. U.S. E

C–6. N

C–7. 7-B

C–8. 8-B

NGLISH

ATIONAL

NGLISH WINDOWS

ATIONAL WINDOWS

UTTON EASY ACCESS KEYBOARD LAYOUT

UTTON EASY ACCESS KEYBOARD LAYOUT

C–9. PS/2 K

C–10. USB K

, B

LOCK DIAGRAM

EYBOARD-TO-SYSTEM TRANSMISSION

(101-KEY) K

(102-KEY) K

EYBOARD CABLE CONNECTOR (MALE

EYBOARD CABLE CONNECTOR (MALE

EYBOARD KEY POSITIONS

EYBOARD KEY POSITIONS

(101W-KEY) K

(102W-KEY) K

EYBOARD KEY POSITIONS

EYBOARD KEY POSITIONS

......................................................C-2

, T

IMING DIAGRAM

........................................C-3

..........................................................C-5

...............................................................C-5

.....................................C-6

..........................................C-6

.....................................................................C-7

.....................................................................C-7

)....................................................................C-16

) .................................................................C-16

Compaq iPAQ Series of Desktop Personal Computers

viii

Second Edition –- February 2001

Page 13

T

1–1. A

ABLE

T

2-1. IPAQ S

ABLE

T

2-2. IPAQ 1.0/1.2 A

ABLE

T

2-3. C

ABLE

T

2-4. S

ABLE

T

2-5. E

ABLE

T

2-6. E

ABLE

T

2-7. P

ABLE

T

2-8. M

ABLE

T

2-9. M

ABLE

T

2-10. H

ABLE

T

3–1. C

ABLE

T

3–2. P

ABLE

T

3–3. SPD A

ABLE

T

3–4. H

ABLE

LIST OF TABLES

CRONYMS AND ABBREVIATIONS

TANDARD FEATURE DIFFERENCE MATRIX

RCHITECTURAL COMPARISON

HIPSET FUNCTIONS

UPPORT COMPONENT FUNCTIONS

NVIRONMENTAL SPECIFICATIONS

LECTRICAL SPECIFICATIONS

HYSICAL SPECIFICATIONS

ULTIBAY 24X

ULTIBAY 24X

ARD DRIVE SPECIFICATIONS

ELERON PROCESSOR STATISTICAL COMPARISON

ENTIUM

OST

III P

DDRESS MAP

/PCI B

RIDGE CONFIGURATION REGISTERS

.............................................................................................................. 2-16

.................................................................................................... 2-20

CD-ROM D

CD-ROM D

ROCESSOR STATISTICAL COMPARISON

(SDRAM DIMM).................................................................................... 3-6

.......................................................................................... 1-4

......................................................................... 2-10

........................................................................................ 2-17

........................................................................................ 2-19

................................................................................................ 2-19

RIVE SPECIFICATIONS

RIVE SPECIFICATIONS

............................................................................................. 2-21

Technical Reference Guide

................................................................... 2-3

............................................................... 2-20

............................................................... 2-21

.................................................................. 3-2

............................................................. 3-3

(GMCH, F

UNCTION

0) ................................. 3-8

T

4-1. PCI D

ABLE

T

4-2. LPC B

ABLE

T

4-3. M

ABLE

T

4-4. M

ABLE

T

4-5. D

ABLE

T

4-6. C

ABLE

T

4-7. C

ABLE

T

4-8. IPAQ 2.0 S

ABLE

T

4-9. S

ABLE

T

4-10. S

ABLE

T

4-11. 82801 ICH GPIO R

ABLE

T

4-12 I/O C

ABLE

T

4-13. LPC47B357 GPIO R

ABLE

T

4-14. 82802 FWH GPIO R

ABLE

T

5–1. IDE PCI C

ABLE

T

5–2.

ABLE

T

5–3. 40-P

ABLE

T

5–4. 68-P

ABLE

T

5–5.

ABLE

T

5–6. S

ABLE

T

5–7. S

ABLE

T

5–8. P

ABLE

T

5–9.

ABLE

T

5–10. DB-25 P

ABLE

T

5–11. 8042-TO-K

ABLE

T

5–12. K

ABLE

T

5–13. CPU C

ABLE

T

5–14. K

ABLE

T

5–15. USB I

ABLE

T

5–16. USB C

ABLE

T

5–17. USB C

ABLE

T

5–18. USB C

ABLE

ASKABLE INTERRUPT PRIORITIES AND ASSIGNMENTS

ASKABLE INTERRUPT CONTROL REGISTERS

EFAULT

LOCK GENERATION AND DISTRIBUTION

ONFIGURATION MEMORY

YSTEM STATUS

YSTEM

IDE B

IN PRIMARY

IN MULTIBAY CONNECTOR PINOUT

DB-9 S

ERIAL INTERFACE CONFIGURATION REGISTERS

ERIAL INTERFACE CONTROL REGISTERS

ARALLEL INTERFACE CONFIGURATION REGISTERS

PARALLEL INTERFACE CONTROL REGISTERS

EYBOARD INTERFACE CONFIGURATION REGISTERS

EYBOARD/POINTING DEVICE CONNECTOR PINOUT

EVICE CONFIGURATION ACCESS DATA

RIDGE CONFIGURATION REGISTERS

.......................................................................... 4-4

(ICH, F

UNCTION

0)................................................ 4-6

.......................................................... 4-8

......................................................................... 4-8

DMA C

HANNEL ASSIGNMENTS AND REGISTER

I/O P

................................... 4-10

ORTS

.............................................................................. 4-11

(CMOS) MAP............................................................................. 4-13

YSTEM BOOT

LED I

/ROM F

NDICATIONS

LASH STATUS

....................................................................................... 4-24

LED I

NDICATIONS

........................................ 4-24

I/O MAP................................................................................................................ 4-26

EGISTER UTILIZATI ON

ONTROLLER CONTROL REGISTERS

EGISTER UTILIZATI ON (DESKTOP AND MINITOWER ONLY

EGISTER UTILIZATI ON

ONFIGURATION REGISTERS

US MASTER CONTROL REGISTERS

IDE C

ONNECTOR PINOUT

............................................................................ 4-27

................................................................................ 4-28

) .................. 4-29

.......................................................................... 4-30

.................................................................................... 5-2

................................................................................. 5-2

............................................................................ 5-3

................................................................................. 5-4

ERIAL CONNECTOR PINOUT

......................................................................................... 5-6

.................................................................... 5-7

............................................................................... 5-8

............................................................. 5-10

......................................................................... 5-11

ARALLEL CONNECTOR PINOUT

EYBOARD COMMANDS

.............................................................................. 5-14

...................................................................................... 5-16

.......................................................... 5-17

OMMANDS TO THE

8042.......................................................................................... 5-19

.......................................................... 5-21

NTERFACE CONFIGURATION REGISTERS

ONTROL REGISTERS

ONNECTOR PINOUT

ABLE LENGTH DATA

................................................................................................. 5-24

.................................................................................................. 5-25

................................................................................................ 5-25

.................................................................... 5-24

Compaq iPAQ Series of Desktop Personal Computers

ix

Second Edition - February 2001

Page 14

Technical Reference Guide

T

5–19. AC’97 A

ABLE

T

5–20. AC’97 A

ABLE

T

5–21. A

ABLE

T

5–22. AOL E

ABLE

T

5–23. NIC C

ABLE

T

5–24. NIC C

ABLE

T

5–25. 825

ABLE

T

6-1. G

ABLE

T

6-2. G

ABLE

T

6-3. M

ABLE

T

6-4. DB-15 M

ABLE

RAPHICS DISPLAY MODES

RAPHICS CONTROLLER

ONITOR POWER MANAGEMENT CONDITIONS

UDIO CONTROLLER

UDIO CODEC CONTROL REGISTERS

UDIO SUBSYSTEM SPECIFICATIONS

VENTS

ONTROLLER

ONTROL REGISTERS

NIC O

XX

ONITOR CONNECTOR PINOUT

PCI C

ONFIGURATION REGISTERS

........................................... 5-30

....................................................................... 5-30

................................................................................... 5-31

...................................................................................................................... 5-33

PCI C

ONFIGURATION REGISTERS

.......................................................... 5-35

.................................................................................................. 5-35

PERATING SPECIFICATIONS

............................................................................ 5-36

..................................................................................................... 6-4

PCI C

ONFIGURATION REGISTERS

...................................................... 6-5

........................................................................ 6-5

................................................................................... 6-6

7-1. 90-W

ABLE

T

T

7-2. 90-W

ABLE

T

8-1. D

ABLE

T

8-2. CMOS F

ABLE

T

8-3. PNP BIOS F

ABLE

T

8-4. APM BIOS F

ABLE

T

A–1. B

ABLE

T

A–2. P

ABLE

T

A–3. S

ABLE

T

A–4. M

ABLE

T

A–5. K

ABLE

T

A–6. P

ABLE

T

A–7. V

ABLE

T

A–8. D

ABLE

T

A–9. S

ABLE

T

A–10. S

ABLE

T

A–11. S

ABLE

T

A–12. H

ABLE

T

A–13. H

ABLE

T

A–14. V

ABLE

T

A–15. A

ABLE

T

A–16. DVD/CD-ROM D

ABLE

T

A–17. N

ABLE

T

A–18. SCSI I

ABLE

T

A–19. P

ABLE

ESKTOP MANAGEMENT FUNCTIONS

EEP/KEYBOARD

OWER-ON SELF TEST

YSTEM ERROR MESSAGES

EMORY ERROR MESSAGES

EYBOARD ERROR MESSAGES

RINTER ERROR MESSAGES

IDEO (GRAPHICS

ISKETTE DRIVE ERROR MESSAGES

ERIAL INTERFACE ERROR MESSAGES

ERIAL INTERFACE ERROR MESSAGES

YSTEM STATUS ERROR MESSAGES

ARD DRIVE ERROR MESSAGES

ARD DRIVE ERROR MESSAGES

IDEO (GRAPHICS

UDIO ERROR MESSAGES

ETWORK INTERFACE ERROR MESSAGES

OINTING DEVICE INTERFACE ERROR MESSAGES

ATT POWER SUPPLY ASSEMBLY SPECIFICATIONS (I

ATT POWER SUPPLY ASSEMBLY SPECIFICATIONS (I

(INT15)........................................................................ 8-3

EATURE BITS

UNCTIONS

UNCTIONS

............................................................................................................. 8-9

.......................................................................................................... 8-12

(INT15) .......................................................................................... 8-17

LED C

...............................................................................................A-1

ODES

(POST) M

ESSAGES

............................................................................A-2

....................................................................................................A-3

..................................................................................................A-4

..............................................................................................A-4

...................................................................................................A-5

) E

RROR MESSAGES

..................................................................................A-5

......................................................................................A-6

...................................................................................A-6

.................................................................................A-7

.....................................................................................A-8

..........................................................................................A-8

..........................................................................................A-9

) E

RROR MESSAGES

................................................................................A-9

..................................................................................................A-10

RIVE ERROR MESSAGES

........................................................................A-10

..........................................................................A-10

NTERFACE ERROR MESSAGES

..................................................................................A-11

..............................................................A-11

PAQ 1.X)......................................... 7-2

PAQ 2.0)......................................... 7-2

T

C–1. K

ABLE

T

C–2. K

ABLE

Compaq iPAQ Series of Desktop Personal Computers

x

EYBOARD-TO-SYSTEM COMMANDS

EYBOARD SCAN CODES

...................................................................................C-11

.....................................................................................................C-12

Second Edition –- February 2001

Page 15

Chapter 1

INTRODUCTION

Technical Reference Guide

1.

Chapter 1 INTRODUCTION

1.1 ABOUT THIS GUIDE

This guide provides technical information about Compaq iPAQ Desktop Personal Computers. This

document describes in detail the system’s design and operation for programmers, engineers,

technicians, and system administrators, as well as end-users wanting detailed information.

1.1.1 USING THIS GUIDE

The chapters of this guide primarily describe the hardware and firmware elements and primarily

deal with the system board and the power supply assembly. The appendices contain general data

such as error codes and information about standard peripheral devices such as keyboards, graphics

cards, and communications adapters.

This guide can be used either as an online document or in hardcopy form.

1.1.1.1 Online Viewing

Online viewing allows for quick navigating and convenient searching through the do cument. A

color monitor will also allow the user to view the color shading used to highlight differential data.

A softcopy of the latest edition of this guide is available for downloading in .pdf file format at the

URL listed below:

http://www.compaq.com/support/techpubs/technical_reference_guides/index.html

Viewing the file requires a copy of Adobe Acrobat Reader available at no charge from Adobe

Systems, Inc. at the following URL:

http://www.adobe.com

When viewing with Adobe Acrobat Reader, click on the ( ) icon in the tool bar to display

the navigation pane for quick access to any section in the guide.

1.1.1.2 Hardcopy

A hardcopy of this guide may be obtained by printing from the .pdf file. The document is designed

for printing in an 8 ½ x 11-inch format. Note that printing in black and white will lose color

shading properties.

Compaq iPAQ Series of Desktop Personal Computers

1-1

Second Edition – February 2001

Page 16

Chapter 1 Introduction

1.2 ADDITIONAL INFORMATION SOURCES

For more information on components mentioned in this guide refer to the indicated manufacturers’

documentation, which may be available at the following online sources:

♦ Compaq Computer Corpo ration: http://www.compaq.com

♦ Intel Corporation: http://www.intel.com

♦ Standard Microsystems Corporation: http://www.smsc.com

♦ Texas Instruments Inc.: http://www.ti.com

♦ USB user group: http://www.usb.org

1.3 MODEL NUMBERING CONVENTION

The model numbering convention for Compaq iPAQ units is as follows:

iPaqX/XNNN/NNX/N/NNNx

1.4 SERIAL NUMBER

The unit’s serial number is located on a sticker placed on the exterior cabinet. The serial number

may also be read with the Compaq Diagnostics or Compaq Insight Manager utilities.

Removable storage: b = CD/CDRW, c = CD, d = DVD, r = CDRW, z = ZIP

Memory (in MB)

OS type: 2 = Windows 2000; 6 = Dual i nstall. Windows NT 4. 0 or 2000)

Chipset type (b = 810E, e = 815E)

Hard drive size (in GB)

Processor speed (in MHz)

Processor type: C = Celeron; P = Pentium

Configuration: L = legacy, F or none = legacy-free

Compaq iPAQ Series of Desktop Personal Computers

1-2

Second Edition – February 2001

Page 17

1.5 NOTATIONAL CONVENTIONS

The notational guidelines used in this guide are described in the following subsections.

1.5.1 VALUES

Hexadecimal values are indicated by a numerical or alpha-numerical value followed by the letter

“h.” Binary values are indicated by a value of ones and zeros followed by the letter “b.”

Numerical values that have no succeeding letter can be assumed to be decimal unless otherwise

stated.

1.5.2 RANGES

Ranges or limits for a parameter are shown using the following methods:

Example A: Bits <7..4> = bits 7, 6, 5, and 4.

Example B: IRQ3-7, 9 = IRQ signals 3 thro ugh 7, and IRQ signal 9

Technical Reference Guide

1.5.3 REGISTER NOTATION AND USAGE

This guide uses sta ndard Intel naming co nventions in discussing the microprocessor ’s (CPU)

internal registers. Registers that are accessed through programmable I/O using an indexing scheme

are indicated using the following format:

03C5.17h

Index port

Data port

In the example above, register 03C5.17h is accessed by writing the index port value 17h to the

index address (03C4h), followed by a write to or a read from port 03C5h.

1.5.4 BIT NOTATION AND BYTE VALUE S

Bit designations are labeled between brackets (i.e., “bit <0 >”). Binary values are shown with the

most significant bit (MSb) on the far left, least significant bit (LSb) at the far right. Byte values in

hexadecimal are also shown with the MSB on the left, LSB on the right.

Compaq iPAQ Series of Desktop Personal Computers

1-3

Second Edition – February 2001

Page 18

Chapter 1 Introduction

1.6 COMMON ACRONYMS AND ABBREV IATIONS

Table 1-1 lists the acronyms and abbreviations used in this guide.

Table 1–1. Acronyms and Abbreviations

Table 1-1.

Acronyms and Abbreviations

Acronym/Abbreviation Description

A ampere

AC alternating current

ACPI Advanced Configuration and Power Interfac e

A/D analog-to-digital

AGP Accelerated graphics port

API applicat i on programming interface

APIC Advanced Programmable I n t errupt Controller

APM advanced power management

AOL Alert-On-LAN™

ASIC application-specific integrated circuit

AT 1) attention (modem commands) 2) 286-based PC arc hi tecture

ATA AT attachment (IDE protocol)

ATAPI AT attachment w/packet interface extensions

AVI audio-video int erl eaved

AVGA Advanced VGA

AWG American Wire Gauge (specifi cation)

BAT Basic assurance test

BCD binary-coded decimal

BIOS basic input/output system

bis second/new revision

BNC Bayonet Neill-Concelman (connector t ype)

bps or b/s bits per second

BSP Bootstrap processor

BTO Built to order

CAS column address strobe

CD compact disk

CD-ROM compact disk read-onl y memory

CDS compact disk system

CGA color graphics adapter

Ch Channel, chapter

cm centimeter

CMC cache/memory controller

CMOS complimentary metal-oxide semiconduct o r (configuration memory)

Cntlr controller

Cntrl control

codec compressor/decompressor

CPQ Compaq

CPU central processing unit

CRIMM Continuity (blank) RIMM

CRT cathode ray tube

CSM Compaq system management / Compaq server management

Continued

Compaq iPAQ Series of Desktop Personal Computers

1-4

Second Edition – February 2001

Page 19

Table 1-1. Acronyms and Abbreviations Continued

Acronym/Abbreviation Description

DAC digital-to-analog converter

DC direct current

DCH DOS compatibility hole

DDC Display Data Channel

DIMM dual inline memory module

DIN Deutche IndustriNorm (connector type)

DIP dual inline package

DMA direct memory access

DMI Desktop management i nterface

dpi dots per i nch

DRAM dynami c random access memory

DRQ data request

EDID extended display identification data

EDO extended data out (RAM type)

EEPROM elect ri cally eraseable PROM

EGA enhanced graphics adapter

EIA Elec tronic Industry Ass ociation

EISA extended ISA

EPP enhanced parallel port

EIDE enhanced IDE

ESCD Extended System Configuration Data (format)

EV Environmental Variable (data)

ExCA Exchangeable Card Architecture

FIFO first in / first out

FL flag (register)

FM frequency modulation

FPM fast page mode (RAM type)

FPU Floating point unit (numeric or math coprocessor)

FPS Frames per second

ft Foot/feet

GB gigabyte

GMCH Graphics/memory controller hub

GND ground

GPIO general purpose I/ O

GPOC general purpose open-coll ector

GART Graphics address re-mapping t abl e

GUI graphics user interface

h hexadecimal

HW hardware

hex hexadecimal

Hz Hertz (cycles-per-second)

ICH I/O controller hub

IDE integrated drive element

IEEE Inst i t ute of Electrical and El ectronic Engineers

IF interrupt flag

I/F interface

Technical Reference Guide

Continued

Compaq iPAQ Series of Desktop Personal Computers

1-5

Second Edition – February 2001

Page 20

Chapter 1 Introduction

Table 1-1. Acronyms and Abbreviations Continued

Acronym/Abbreviation Description

in inch

INT interrupt

I/O input/output

IPL initial program loader

IrDA InfraRed Data Assoc i ation

IRQ interrupt request

ISA indust ry standard architecture

Kb / KB kilobits / kilobytes (x 1024 bits / x 1024 bytes)

Kb/s kilobits per second

kg kilogram

KHz kilohertz

kV kilovolt

lb pound

LAN local area net work

LCD liquid crystal displ a y

LED light-emitting diode

LPC Low pin count

LSI large scale integration

LSb / LSB least significant bi t / least signific ant byte

LUN logical unit (SCSI)

m Meter

MCH Memory controller hub

MMX multimedia extensions

MPEG Motion Pic ture Experts Group

ms millisecond

MSb / MSB most significant bit / most significant byte

mux multiplex

MVA mot i on vi deo acceleration

MVW motion video window

n

NIC network interface card/controller

NiMH nickel-metal hydride

NMI non-maskable interrupt

NRZI Non-return-to-zero inverted

ns nanosecond

NT nested task flag

NTSC National Televi sion Standards Commi t tee

NVRAM non-volatile random access memory

OS operating system

PAL 1.) programmable array logic 2.) phase altering line

PC Personal computer

PCA Printed circuit assembl y

PCI peripheral component interconnect

PCM pulse code modulation

PCMCIA Personal Computer Memory Card I nternational Associati on

variable parameter/value

Continued

Compaq iPAQ Series of Desktop Personal Computers

1-6

Second Edition – February 2001

Page 21

Technical Reference Guide

Table 1-1. Acronyms and Abbreviations Continued

Acronym/Abbreviation Description

PFC Power factor correction

PIN personal identification number

PIO Programmed I/O

POST power-on self tes t

PROM programmable read-only memory

PTR pointer

RAM random access memory

RAS row address st robe

rcvr receiver

RDRAM (Direct) Rambus DRAM

RGB red/green/blue (monitor input)

RH Relative humidity

RMS root mean square

ROM read-only memory

RPM revolutions per minute

RTC real time clock

R/W Read/Write

SCSI small comput er system interface

SDRAM Synchronous Dynamic RA M

SEC Single E dge-Connector

SECAM sequential colour avec memoire (sequential color with memory)

SF sign flag

SGRAM Synchronous Graphics RAM

SIMD Single instruction multipl e data

SIMM single i n-l i ne memory module

SMART Self Monitor Analysis Report Technology

SMI system management interrupt

SMM system management mode

SMRAM system management RAM

SPD serial presence detect

SPDIF Sony/Philips Digit al I nt erface (IEC-958 specification)

SPN Spare part number

SPP standard parallel port

SRAM static RAM

SSE Streaming SIMD extensions

STN super twist pneumatic

SVGA super VGA

SW software

Continued

Compaq iPAQ Series of Desktop Personal Computers

1-7

Second Edition – February 2001

Page 22

Chapter 1 Introduction

Table 1-1. Acronyms and Abbreviations Continued

Acronym/Abbreviation Description

TAD telephone answering device

TAFI Temperature-s ensing And Fan control Integrated ci rc ui t

TCP tape carrier package

TF trap flag

TFT thin-film transistor

TIA Telecommunications Inform at i on Administration

TPE twisted pair ethernet

TPI track per inch

TTL transist or-t ransistor logic

TV television

TX transmit

UART universal asynchronous receiver/transmitter

UDMA Ultra DMA

URL Uniform resource loc ator

us / µs

USB Universal Serial Bus

UTP unshielded twisted pair

Vvolt

VESA Video Electronic Standards Association

VGA video graphics adapter

VLSI very large scale integration

VRAM Video RAM

Wwatt

WOL Wake-On-LAN

WRAM Windows RAM

ZF zero flag

ZIF zero insertion force (socket )

microsecond

Compaq iPAQ Series of Desktop Personal Computers

1-8

Second Edition – February 2001

Page 23

Chapter 2

SYSTEM OVERVIEW

2. Chapter 2 SYSTEM OVERVIEW

2.1 INTRODUCTION

The Compaq iPAQ Series of Desktop Personal Computers provides affordable business solutions

with the focus on internet access and mainstream performance. Based on an Intel Celeron and

Pentium III processors, these systems are designed to maximize the effectiveness of internet and

intranet usage while simplifying system management.

Technical Reference Guide

iPAQ 1.0/1.2 Desktop with

Monitor and Keyboard

iPAQ 2.0 Desktop

Figure 2–1. Compaq iPAQ Desktop Personal Computers

This chapter includes the following topics:

♦ Features and options (2.2) page 2-2

♦ Mechanical design (2.3) page 2-4

♦ System architecture (2.4) page 2-10

♦ Specifications (2.5) page 2-20

Compaq iPAQ Series of Desktop Personal Computers

2-1

Second Edition - February 2001

Page 24

Chapter 2 System Overview

2.2 FEATURES AND OPTIONS

This section describes the standard features and available options.

2.2.1 STANDARD FEATURES

The following standard features are available on all models:

♦ Celeron or Pentium III processor

♦ Two DIMM sockets for system memory

♦ AC’97 audio subsystem with front panel microphone and headphone jacks

♦ MultiBay w/hot-swap support

♦ Hard drive fault prediction

♦ Two USB ports on front panel

♦ Network interface controller

♦ VGA analog output (1600 x 1200 max resolution)

♦ APM 1.2 power management support

♦ Plug ’n Play compatible (with ESCD support)

♦ Intelligent Manageability support

♦ Energy Star compliant

♦ Security features including:

• Setup and power-on passwords

• DriveLock for MultiBay hard drive

• I/O interface disabling

• Administrator password

• Network service boot

• Asset tracking tag

• UUID

• Cable lock provision

♦ Compaq Easy-Access keyboard w/Windows support

♦ Mouse

♦ 90-watt power supply

Table 2-1 shows the differences in features between the iPAQ 1.0, 1.2, and 2.0 models:

2-2

Compaq iPAQ Series of Desktop Personal Computers

Second Edition – February 2001

Page 25

Technical Reference Guide

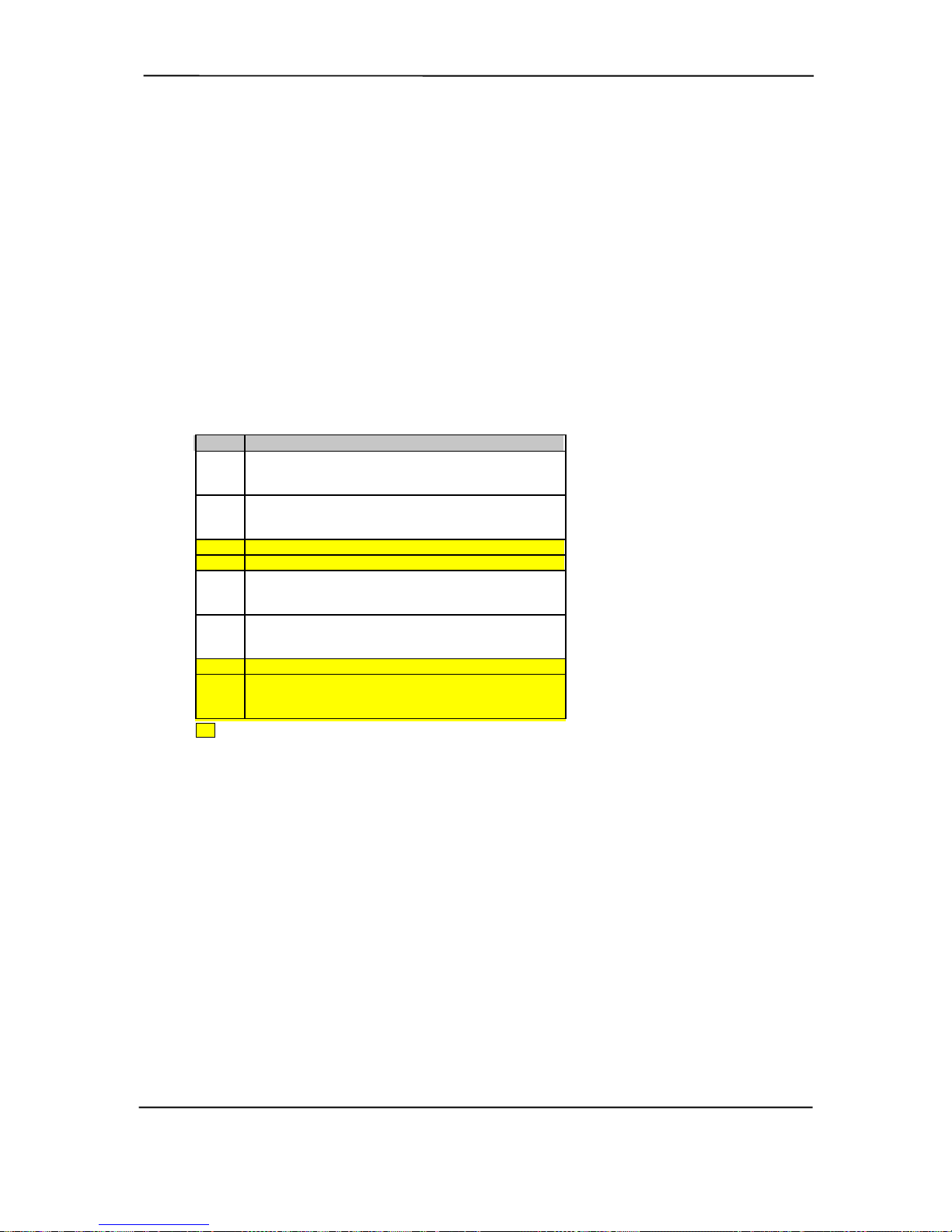

Table 2-1. iPAQ Standard Feature Difference Matrix

Table 2-1.

iPAQ Standard Feature Difference Matrix

iPAQ 1.0 iPAQ 1.2 iPAQ 2.0

Processor Celeron Pentium Pentium Celeron Pentium

Processor Speed (MHz) 500 500 733 700 866

Chipset 810E 810E 810E 815E 815E

System Memory:

DIMM type

DIMM technology (Max)

Max amount supported

4-MB Display cache No Yes Yes Optional Yes

Hard Drive Interface UATA/66 UATA/66 UA T A/66 UATA/100 UATA/100

Multibay eject button At rear At rear At rear At front At front

Rear panel USB ports 3 [1] 3 [1] 3 [ 1] 4 4

Serial port 1 [2] 1 [2] 1 [2] 1 [2] 1 [2]

Parallel port 1 [2] 1 [2] 1 [2] 1 [2] 1 [2]

NOTES:

Legacy models ship with PS /2 keyboard and mouse. Legacy-free models ship with

USB keyboard and mouse.

[1] Legacy-free models onl y.

[2] Legacy models only

PC100

128Mb

256 MB

PC100

128Mb

256 MB

PC100

128 Mb

256 MB

PC133

256 Mb

512 MB

PC133

256 Mb

512 MB

2.2.2 OPTIONS

The following items are available as options for all models and may be included in the standard

configuration of some models:

♦ Memory: 32-MB DIMM (non-ECC)

♦ Hard drives/accessories: 4.3 or 8.4 GB UATA/66 hard drive

♦ I/O Expansion: Legacy Module (iPAQ 2.0 only)

♦ Communications: USB 56K V.92 Modem

♦ Security: Security bar (iPAQ 2.0 only)

♦ MultiBay drives: 24x CD-ROM drive

64-MB DIMM (non-ECC)

128-MB DIMM (non-ECC)

256-MB DIMM (non-ECC) (iPAQ 2.0 only)

4-MB Display Cache module (iPAQ 2.0 only)

10 GB UATA/100 hard drive (iPAQ 2.0 only)

Multibay hard drive adapter

Multibay 250 Zip drive

USB 802.11b Adapter

8x DVD-ROM drive

4/4/20x CD-RW drive

Super Disk LS-120 Power Drive

Compaq iPAQ Series of Desktop Personal Computers

2-3

Second Edition - February 2001

Page 26

Chapter 2 System Overview

2.3 MECHANICAL DESIGN

The Compaq iPAQ Internet Device uses a minitower form factor featuring a smaller footprint and

reduced height than previous minitowers, allowing easy floor or desktop positioning. Commonly

used audio and USB connections are accessible from the front panel.

NOTE: The following information is primarily for identification purposes only. For

detailed information on servicing these systems refer to the applicab le service guides.

Most components of iPAQ 1.0/1.2 and 2.0 systems are not inter-changeable.

2.3.1 CABINET LAYOUTS

2.3.1.1 Front Views

1

2

4

7

3

5

6

8

iPAQ 1.0/1.2

Item Description

1 Power Button

2 Power LED

3 Hard drive activity LED

4 MultiBay device bay (accepts 5.25”/12. 7 mm storage device)

5 Microphone In Jack

6 Headphone Out Jack

7 USB port (through-Hub)

8 USB port (through-Hub)

9 Multibay device eject button

1

2

4

9

5

7

3

6

8

iPAQ 2.0

Figure 2–2. Compaq iPAQ Desktops, Front Views

2-4

Compaq iPAQ Series of Desktop Personal Computers

Second Edition – February 2001

Page 27

2.3.1.2 Rear Views

Technical Reference Guide

11

13

1

3

5

7

IPAQ 1.0/1.2 Legacy

11

12

8

10

12

14

2

4

6

8

1

3

5

9b

9a

13

2

4

6

9b

10

14

IPAQ 1.0/1.2 Legacy-Free

16

9a

9b

[1]

3

5

6

9a

9b

4

1

2

7

Legacy Module for

iPAQ 2.0

15

13

14

iPAQ 2.0

Item Description Item Description

1 A udi o l i ne output 2 Audio line input

3 Net work ac tivity LED indicator 4 Network I/F jack

5 Net work speed LED indicator 6 VGA monitor connector

7 P aral l el I/F connector 8 Serial I/F c onnector

9 US B port: a) direct, b) through-hub 10 MultiBay device eject butt on

11 PS/2 mouse connec t or 12 PS/2 keyboard connector

13 AC line in connector 14 Line voltage select switch

15 Legacy module connector 16 Carrying depressi on

NOTE: [1] Dedicated-direct USB port.

Figure 2–3. Compaq iPAQ Desktops, Rear Views

Compaq iPAQ Series of Desktop Personal Computers

Second Edition - February 2001

2-5

Page 28

Chapter 2 System Overview

2.3.2 CHASSIS LAYOUTS

2.3.2.1 iPAQ 1.0/1.2 CHASSIS LAYOUT

The internal assemblies of iPAQ 1.0/1.2 models are accessible from the right side of the system

unit. The right side (carbon-colored) cover features tool-less removal allowing quick access to the

DIMM sockets through an access opening and to the hard drive. Access to the system board and

processor requires removing the right chassis access panel. The multibay device is located on the

left side of the chassis and can be removed (using the eject button) without removing the left side

cover. Servicing the multibay board will, however, require remo val of the left side cover.

1

2

Left Side Cover Removed

3 5

4

Right Side Cover Removed

10

6

7

89

Right Side Cover and

Chassis Access Panel Removed

Figure 2–4. Compaq iPAQ 1.0/1.2 Desktop Chassis Layout

2-6

Compaq iPAQ Series of Desktop Personal Computers

Item Description

1 Multibay device board

2 Multibay storage device

3 Access opening to DIMM sockets

4 Hard drive in 3.5” 1/3 height bay

5 Power button/LED board (PCA# 010647)

6 System board (PCA# 161014 or 161015)

7 Power supply assembly

8 Processor

9 Speaker

10 Audio and USB I/O board (PCA# 010650)

Second Edition – February 2001

Page 29

2.3.2.2 iPAQ 2.0 CHASSIS LAYOUT

The internal assemblies of the iPAQ 2.0 model are accessible from both sides of the system unit.

Both side covers (carbon-colored) feature tool-less removal allowing quick access to serviceable

components such as DIMMs and hard drives.

1

Technical Reference Guide

Left Side Cover Removed

2

3

4

5

6

7

8

9

10

Right Side Cover Removed

Item Description

1 Multibay storage device

2 Access hole to CMOS cl ear button

3 Access opening to DI MM soc kets

4 Multibay device board (PCA #011059)

5 Hard drive in 3.5” 1/3 height bay

6 System board (PCA# 011010)

7 4-MB display cache module (PCA# 011044) (if installed)

8 Processor/heat sink assembly

9 Speaker

10 Power supply assembly

Right Side Cover and

Access Panel Removed

Figure 2–5. Compaq iPAQ 2.0 Chassis Layout

Compaq iPAQ Series of Desktop Personal Computers

2-7

Second Edition - February 2001

Page 30

Chapter 2 System Overview

2.3.3 SYSTEM BOARD LAYOUTS

Compaq iPAQ 1.0 and 1.2 systems use a FlexATX-type (9.0 x 7.5 inch) system board in one of

two variations; a legacy board or a legacy-free board (Figure 2-6).

1 2 4

22

21

20

19

18

17 1516

Legacy PCA# 161014

Item Description Item

1 USB ports 3 and 4 (front panel) header 12 USB ports 0, 1, 2 connectors

2 Battery 13 Dual PS/2 conn.: (mouse, keyboard)

3 BIOS ROM configuration jum per 14 Serial I/F header

4 Speaker connector 15 PGA370 processor socket

5 Audio microphone/headphone header 16 DIMM sockets

6 Audio line out jack 17 Processor (boxed) fan header

7 Audio line in jack 18 IDE (pri.) 40-pin connector

8 Network connector 19 IDE (sec.) 50-pin (multibay) connect or

9 VGA monitor connector 20 Power button/LED indicator c onnector

10 Parallel I/F connector 21 CD audio header

11 Serial I/F connector 22 Power supply connector

NOTE:

Refer to Chapter 7 “Power and Signal Distribution” for header pinouts.

3

5

22

6

21

7

20

8

9

19

10

11

13

1 2 4

18

17

3

1516

14

Legacy-Free PCA# 161015

5

6

7

8

9

12

Figure 2–6. Compaq iPAQ 1.0/1.2 System Board Layouts

2-8

Compaq iPAQ Series of Desktop Personal Computers

Second Edition – February 2001

Page 31

Technical Reference Guide

All iPAQ 2.0 systems use a Compaq-proprietary system board (Figure 2-7).

19

21

18

17

16

20

15

Item Description

1 Power button

2Battery

3 CMOS clear switch

4 Displ ay cache module connector

5 Pas sword enable jumper

6 Video graphi cs monitor connector

7 USB connector pairs: a) J111; b) J112

8 Network connector

9 Audio l ine i n j ack

10 Audio line out jack

11 Legacy module connector

12 PGA370 processor socket

13 DIMM sockets

14 Power supply connector

15 USB triple connector (center port not used)

16 Microphone in, Headphone out jacks

17 Speaker connector

18 Hard drive activity LED

19 Power LED

20 Hard drive connector (IDE primary)

21 Multibay board connector (IDE secondary)

1 2 4

14 13

PCA# 011010, Component SidePCA# 011010, Solder Side

12

53

6

7a

7b

8

9

10

11

Figure 2–7. Compaq iPAQ 2.0 System Board Layout

Compaq iPAQ Series of Desktop Personal Computers

2-9

Second Edition - February 2001

Page 32

Chapter 2 System Overview

2.4 SYSTEM ARCHITECTURE

The Compaq iPAQ Series of Desktop Personal Computers features Intel Celeron or Pentium III

processors. The iPAQ 1.0/1.2 models employ an architecture based on the Intel 810e chipset

while iPAQ 2.0 models are based on the Intel 815e chipset.

2.4.1 IPAQ 1.0/1.2 ARCHITECTURE

The architecture of iPAQ 1.0/1.2 models is based on the Intel 810e chipset with a Celeron or

Pentium III processor installed as standard. iPAQ 1.0 systems feature 500-MHz processors while

iPAQ 1.2 systems feature 733-MHz Pentium III processors. As indicated in the following table and

shown in Figure 2-8, two basic configurations are available:

♦ Legacy-free with Celeron or Pentium III processor

♦ Legacy with Celeron or Pentium III processor

Legacy-free systems provide five Universal Serial Bus (USB) ports for connecting peripherals

(including the supplied USB mouse and USB keyboard). Legacy light systems provide two USB

ports along with PS/2 ports for the supplied mouse and keyboard as well as parallel and serial

ports.

NOTE: A legacy-free iPAQ 1.0/1.2 system is upgradeable to become a legacy system

only by changing the system board.

All iPAQ 1.x systems use the 810E chipset. The 810E chipset includes the 82810E-DC100 GMCH

designed to support 100-MHz SDRAM and also integrates a 2D/3D Direct AGP graphics

controller. Pentium III-based systems come with an additional 4-MB display cache (soldered

down) to compliment the graphics controller.

The 810E chipset also includes an 82801 I/O Controller Hub (ICH) that provides two IDE

interfaces, two USB interfaces, and a PCI bus controller. The 82802 Firmware Hub (FWH)

component is loaded with Compaq BIOS. The iPAQ 1.0/1.2 features an AC’97 audio subsystem

with 5-watt amplifier and internal speaker. All iPAQ 1.0/1.2 systems feature a 90-watt power

supply. Table 2-2 lists differences between system architectures:

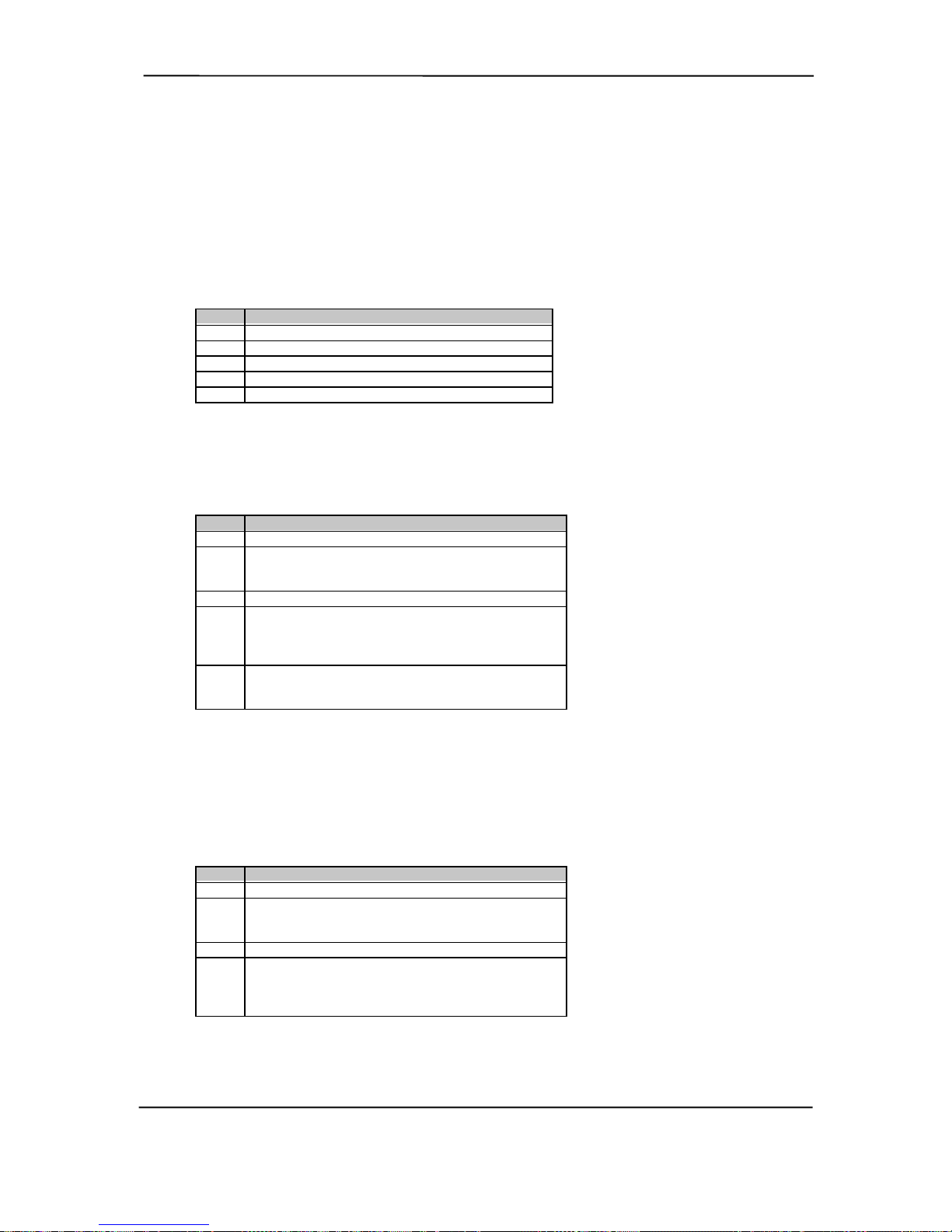

Table 2-2. iPAQ 1.0/1.2 Architectural Comp arison

Table 2-2.

IPAQ 1.0/1.2 Architectural Comparison

IPAQ 1.0 IPAQ 1.2

Legacy-Free Legacy Legacy-Free Legacy

Processor Type Celeron Pentium Celeron Pentium Pentium Pentium

Processor Speed (MHz) 500 500 500 500 733 733

FSB Speed (MHz) 66 100 66 100 133 133

4-MB Display Cache? No Yes No Yes Yes Yes

Mouse/Keyboard Type USB USB PS/2 PS/2 USB PS/2

Serial port? No No Yes Yes No Yes

Parallel port? No No Yes Yes No Yes

# of USB ports 5 5 2 2 5 2

2-10

Compaq iPAQ Series of Desktop Personal Computers

Second Edition – February 2001

Page 33

Celeron or

Pentium III

Processor

66-/100-/133- MHz FSB

Technical Reference Guide

Monitor

4-MB

Display Cache

UATA/66

Hard Drive

MultiBay

Device

Audio

Subsystem

RGB

Graphics

IDE I/F

IDE I/F

Beep

Audio

AC’97

Link Bus

810E Chipset

82810E-DC100

Cntlr.

Pri.

Sec.

Controller

GMCH

82801

ICH

82559

Ethernet

SDRAM

Cntlr.

Hub Link

Bus

USB

I/F

82802

FWH

33-MHz

32-Bit PCI Bus

PC100

Memory

Bus

LPC

Bus