Page 1

Alpha Architec ture Handbook

Order Number: EC–QD2KC–TE

Revision/Update Information:

This is Version 4 of the Alpha

Architecture Handbook.

Compaq Computer Corporation

Page 2

October 1998

The informatio n in this pu bl icat io n is subj ect to chang e with out noti ce.

COMP AQ COMPUTER CORPORATION SHALL NOT BE LIABLE FOR TECHNICAL OR EDITORIAL

ERRORS OR OMISSIONS CONTAINED HEREIN, NOR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES RESULTING FROM THE FURNISHING, PERFORMANCE, OR USE OF THIS MATERIAL. THIS

INFORMAT ION IS PROVIDED “AS IS” AND COMPAQ COMPUTER CORPORA TION DISCLAIMS ANY

WARRANTIES, EXPRESS, IMPLIED OR STATUTORY AND EXPRESSL Y DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR PARTICULAR PURPOSE, GOOD TITLE AND AGAINST

INFRINGEMENT.

This publication contains inf or m ation protected by copyright. No part of thi s publicat ion may be photocopied or

reproduced in any form without prior written consent from Compaq Computer Corporation.

© Compaq Computer Corporation 1998.

All rights reserved. Printed in the U.S.A.

The following are trademarks of Comaq Computer Corporation: Alpha AXP, AXP, DEC, DIGITAL, DIGITAL

UNIX, OpenVMS, PDP–11, VAX, VAX DOCUMENT, and the DIGITAL logo.

Cray is a regis tered trademark of Cray Resear ch, Inc. IBM is a registered trademar k of International Business

Machines Co rporation. UNIX is a r egistered trademark in the United States and other countries licensed exclusively

through X/O pen Company Ltd. Windows NT is a trademark of Microsoft Corporation.

All other trademarks and registered t rademarks are the property of their res pective owners.

Page 3

Table of Contents

1 Introduction

1.1 The Alpha Approach to RISC Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

1.2 Data Format Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

1.3 Instruction Format Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–4

1.4 Instruction Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–4

1.5 Instruction Set Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–6

1.6 Terminology and Conventions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–6

1.6.1 Numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–7

1.6.2 Security Holes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–7

1.6.3 UNPREDICTABLE and UNDEFINED . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–7

1.6.4 Ranges and Extent s. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–8

1.6.5 ALIGNED and UNALIGNED . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–8

1.6.6 Must Be Zero (MBZ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–9

1.6.7 Read As Zero (RAZ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–9

1.6.8 Should Be Zero (SBZ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–9

1.6.9 Ignore (IGN). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–9

1.6.10 Implementati on Dependent (IMP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–9

1.6.11 Illustration Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–9

1.6.12 Macro Code Example Conve nti ons . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–9

2 Basic Architecture

2.1 Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 – 1

2.2 Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

2.2.1 Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

2.2.2 Word. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

2.2.3 Longword . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

2.2.4 Quadword. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

2.2.5 VAX Floating-Point Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

2.2.5.1 F_floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

2.2.5.2 G_floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4

2.2.5.3 D_floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

2.2.6 IEEE Floating-Point Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

2.2.6.1 S_Floating. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–7

2.2.6.2 T_floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–8

2.2.6.3 X_Floating. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–9

2.2.7 Longword Integer Format in Floating-Point Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–11

2.2.8 Quadword Integer Format in Floating-Point Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–12

2.2.9 Data Types with No Hardware Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–12

iii

Page 4

2.3 Bi g-Endian Addressing Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–13

3 Instruction Formats

3.1 Al pha Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

3.1.1 Program Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

3.1.2 Integer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 – 1

3.1.3 Floating-Point Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

3.1.4 Lock Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

3.1.5 Processor Cycle Counter (PCC) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

3.1.6 Optional Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

3.1.6.1 Memory Prefetch Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

3.1.6.2 VAX Compatibility Regist er . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

3.2 Notation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

3.2.1 Operand Notation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

3.2.2 Instructi on Operand Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

3.2.2.1 Operand Name Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

3.2.2.2 Operand Access Type Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

3.2.2.3 Operand Data Type Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–6

3.2.3 Operators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–6

3.2.4 Notation Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–10

3.3 Instruction Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–10

3.3.1 Memory Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

3.3.1.1 Memory Format Instructions with a Function Code . . . . . . . . . . . . . . . . . . . . . . . . 3–11

3.3.1.2 Memory Format Jump Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–12

3.3.2 Branch Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–12

3.3.3 Operate Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–12

3.3.4 Floating-Point Operate Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–13

3.3.4.1 Floating-Point Convert Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–14

3.3.4.2 Floating-Point/Integer Register Moves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–14

3.3.5 PALcode Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–14

4 Instruction Descriptions

4.1 Instruction Set Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4– 1

4.1.1 Subsetting Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–2

4.1.2 Floating-Point Subsets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–2

4.1.3 Software Emulation Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–3

4.1.4 Opcode Qualifiers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–3

4.2 Memory Integer Load/Store Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–4

4.2.1 Load Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4– 5

4.2.2 Load Memory Data into Int eger Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–6

4.2.3 Load Unaligned Me mory Data into Integer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–8

4.2.4 Load Memory Data into Int eger Register Locked . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–9

4.2.5 Store Integer Register Data into Memory Conditional . . . . . . . . . . . . . . . . . . . . . . . . . . 4–12

4.2.6 Store Integer Register Data into Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–15

4.2.7 Store Unaligned Integer Register Data into Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–17

4.3 Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 – 1 8

4.3.1 Conditional Branch. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–20

4.3.2 Unconditional Branch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–21

4.3.3 Jumps. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–22

4.4 I nteger Arithmetic Instruct ions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–24

4.4.1 Longword Add . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–25

4.4.2 Scaled Longword A dd . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–26

4.4.3 Quadword Add . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–27

4.4.4 Scaled Quadword Add . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–28

iv

Page 5

4.4.5 Integer Signed Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–29

4.4.6 Integer Unsig ned Com pare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–30

4.4.7 Count Leading Zero. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–31

4.4.8 Count Population . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–32

4.4.9 Count Trailing Zero . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–33

4.4.10 Longword Multiply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–34

4.4.11 Quadword Multiply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–35

4.4.12 Unsigned Quadword Mult iply High. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–36

4.4.13 Longword Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–37

4.4.14 Scaled Longword Subtr act. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–38

4.4.15 Quadword Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–39

4.4.16 Scaled Quadword Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–40

4.5 Logical and Shift Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–41

4.5.1 Logical Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–42

4.5.2 Conditional Move Integer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–43

4.5.3 Shift Logical . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 – 4 5

4.5.4 Shift Arithmetic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–46

4.6 Byte Manipulation Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–47

4.6.1 Compare Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–49

4.6.2 Extract Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–51

4.6.3 Byte Insert . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4– 5 5

4.6.4 Byte Mask . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–57

4.6.5 Sign Extend . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–60

4.6.6 Zero Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–61

4.7 Floating-Point Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–62

4.7.1 Single-Precision Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–62

4.7.2 Subsets and Faults . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–62

4.7.3 Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–63

4.7.4 Encodings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–65

4.7.5 Rounding Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–66

4.7.6 Computational Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–67

4.7.6.1 VAX-Format Arithmetic with Precise Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . 4–67

4.7.6.2 High-Performance VAX-Format Arithmetic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–68

4.7.6.3 IEEE-Compliant Ari thmetic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–68

4.7.6.4 IEEE-Compliant Ari thmetic Without Inexact Exception. . . . . . . . . . . . . . . . . . . . . . 4–68

4.7.6.5 High-Performance IEEE-Format Arithmetic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–69

4.7.7 Trapping Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–69

4.7.7.1 VAX Trapping Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–69

4.7.7.2 IEEE Trapping Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–71

4.7.7.3 Arithmetic Trap Completion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–73

4.7.7.3.1 Trap Shadow Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–73

4.7.7.3.2 Trap Shadow Length Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–74

4.7.7.4 Invalid Operation (INV) Arithmetic Trap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–76

4.7.7.5 Division by Zero (DZE) Arithmetic Trap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–77

4.7.7.6 Overflow (OVF) Arithmetic Trap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–77

4.7.7.7 Underflow (UNF) Arithmetic Trap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–78

4.7.7.8 Inexact Result (INE) Arithmetic Trap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–78

4.7.7.9 Integer Overf low (IOV) Arithmetic Trap. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–78

4.7.7.10 IEEE Floating-Poi nt Trap Disable Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–78

4.7.7.11 IEEE Denormal Control Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–79

4.7.8 Floating-Point Control Register (FPCR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–79

4.7.8.1 Accessing the FPCR. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–82

4.7.8.2 Default Values of the FPCR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–83

4.7.8.3 Saving and Restoring the FPCR. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–83

4.7.9 Floating-Point Instruction Function Field Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–84

4.7.10 IEEE Standard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–8 8

4.7.10.1 Conversion of NaN and Infinity Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–88

4.7.10.2 Copying NaN Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–89

4.7.10.3 Generating NaN Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–89

v

Page 6

4.7.10.4 Propagating NaN Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–89

4.8 Memory Format Floating-Point Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–90

4.8.1 Load F_floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–91

4.8.2 Load G_floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–92

4.8.3 Load S_floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–93

4.8.4 Load T_floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–94

4.8.5 Store F_floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–95

4.8.6 Store G_floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–96

4.8.7 Store S_floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–97

4.8.8 Store T_floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–98

4.9 Branch Format Floating-Point Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–99

4.9.1 Conditional Branch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–100

4.10 Floating-Point Operate Format Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–102

4.10.1 Copy Sign . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–105

4.10.2 Convert Integer to Integer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–106

4.10.3 Floating- Point Conditional Move . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–107

4.10.4 Move from/to Floating-Point Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–109

4.10.5 VAX Floating Add . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–110

4.10.6 IEEE Floating Add . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–111

4.10.7 VAX Floating Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–112

4.10.8 IEEE Floating Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–113

4.10.9 Convert VAX Floating to Integer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–114

4.10.10 Convert Integer to VAX Floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–115

4.10.11 Convert VAX Floati ng to VAX Floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–116

4.10.12 Convert IEEE Floating to Integer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–117

4.10.13 Convert Integer to IEEE Floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–118

4.10.14 Convert IEEE S_Floating to IEEE T_Floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–119

4.10.15 Convert IEEE T_Floating to IEEE S_Floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–120

4.10.16 VAX Floating Divi de . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–121

4.10.17 IEEE Floating Div ide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–122

4.10.18 Floati ng-Point Register to Integer Register Move . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–123

4.10.19 Integer Register to Floating-Point Regis ter Move . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–124

4.10.20 VAX Floating Mult ipl y . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–126

4.10.21 IEEE Floating Multiply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–127

4.10.22 VAX Floating Square Root . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–128

4.10.23 IEEE Floating Square Root . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–129

4.10.24 VAX Floating Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–130

4.10.25 IEEE Floati ng Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–131

4.11 Miscellaneous Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–132

4.11.1 Architecture Mask . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–133

4.11.2 Call Privileged Architecture Library . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–135

4.11.3 Evict Data Cache Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–136

4.11.4 Exception Barrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–138

4.11.5 Prefetch Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–139

4.11.6 Implementation Version . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–141

4.11.7 Memory Barrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–142

4.11.8 Read Processor Cycle Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–143

4.11.9 Trap Barrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–144

4.11.10 Write Hint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–145

4.11.11 Write Memory Barrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–147

4.12 VAX Compatibility Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–149

4.12.1 VAX Compatibility Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–150

4.13 Multimedia (Graphics and Video) Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–151

4.13.1 Byte and Word Minimum and Maxi m um . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–152

4.13.2 Pixel Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–154

4.13.3 Pack Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–155

4.13.4 Unpack Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–156

vi

Page 7

5 System Architecture and Programming Implications

5.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–1

5.2 Physical Address Space Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–1

5.2.1 Coherency of Memory Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–1

5.2.2 Granularit y of Mem ory Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–2

5.2.3 Width of Memory Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–3

5.2.4 Memory-Lik e and Non-Mem ory-Like Behavior. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–3

5.3 Tr anslation Buffers and Virtual Caches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–4

5.4 Caches and Write Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–4

5.5 Data Sharing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–6

5.5.1 Atomic Change of a Single Datum. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–6

5.5.2 Atomic Update of a Single Datum . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–6

5.5.3 Atomic Update of Data Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–7

5.5.4 Ordering Considerations for Shared Data Structures . . . . . . . . . . . . . . . . . . . . . . . . . . 5–9

5.6 Read/Write Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–10

5.6.1 Alpha Shared Memory Mode l. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–10

5.6.1.1 Architectural Definition of Processor Iss ue Sequence . . . . . . . . . . . . . . . . . . . . . . 5–12

5.6.1.2 Definition of Before and After . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–12

5.6.1.3 Definition of Processor Issue Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–12

5.6.1.4 Definition of Location Access Constraints. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–14

5.6.1.5 Definition of Visibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–14

5.6.1.6 Definition of Storage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–14

5.6.1.7 Definition of Dependence Constraint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–15

5.6.1.8 Definition of Load-Locked and Store-Conditional. . . . . . . . . . . . . . . . . . . . . . . . . . 5–16

5.6.1.9 Timeliness. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–17

5.6.2 Litmus Tests. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–17

5.6.2.1 Litmus Test 1 (Impossible Sequence). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–17

5.6.2.2 Litmus Test 2 (Impossible Sequence). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–18

5.6.2.3 Litmus Test 3 (Impossible Sequence). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–18

5.6.2.4 Litmus Test 4 (Sequence Okay) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–19

5.6.2.5 Litmus Test 5 (Sequence Okay) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–19

5.6.2.6 Litmus Test 6 (Sequence Okay) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–19

5.6.2.7 Litmus Test 7 (Impossible Sequence). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–20

5.6.2.8 Litmus Test 8 (Impossible Sequence). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–20

5.6.2.9 Litmus Test 9 (Impossible Sequence). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–21

5.6.2.10 Litmus Test 10 (Sequence Okay) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–21

5.6.2.11 Litmus Test 11 (Impossible Sequence). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–21

5.6.3 Implied Barriers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–22

5.6.4 Implications for Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–22

5.6.4.1 Single Processor Data Stream . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–22

5.6.4.2 Single Processor Instruction Stream. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–22

5.6.4.3 Multiprocessor Data Stream (Including Single Processor with DMA I/O) . . . . . . . . 5–22

5.6.4.4 Multiproce ssor Instruction Stream (Includin g Singl e Processor with DMA I/O) . . . 5–23

5.6.4.5 Multiprocessor Context Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–24

5.6.4.6 Multiprocessor Send/Receive Interrupt. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–26

5.6.4.7 Implicati ons for Memory Mapped I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–27

5.6.4.8 Multiple Processors Writing to a Single I/O Device. . . . . . . . . . . . . . . . . . . . . . . . . 5–28

5.6.5 Implications for Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–29

5.7 Arithmetic Traps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–30

6 Common PALcode Architecture

6.1 PALcode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–1

6.2 PALcode Instructions and Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–1

6.3 PALcode Environment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–2

6.4 Special Functions Required for PALcode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–2

vii

Page 8

6.5 PALcode Effects on System Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–3

6.6 PALcode Replacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–3

6.7 Required PALcode Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–4

6.7.1 Drain Aborts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–6

6.7.2 Halt. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–7

6.7.3 Instruction Memory Barrier. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–8

7 Console Subsystem Overview

8 Input/Output Overview

9 OpenVMS Alpha

9.1 Unprivileged OpenVMS Alpha PALcode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–1

9.2 Pr ivileged OpenVMS Alpha Palcode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–8

10 Digital UNIX

10.1 Unprivileged Digital UNIX PALcode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10–1

10.2 Privileged Digital UNIX PALcode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10–2

11 Windows NT Alpha

11.1 Unprivileged Windows NT Alpha PALcode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11–1

11.2 Privileged Windows NT Alpha PALcode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11–2

A Software Considerations

A.1 Hardware-Software Compact . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–1

A.2 Instruction-Stream Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–2

A.2.1 Instruction Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–2

A.2.2 Branch Predict ion and Minimizing Branch-Taken — Factor of 3 . . . . . . . . . . . . . . . . . . A–2

A.2.3 Improving I-Stream Density — Factor of 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–4

A.2.4 Instruction Scheduling — Factor of 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–4

A.3 Data-Stream Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–4

A.3.1 Data Alignment — Factor of 10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–4

A.3.2 Shared Data in Multiple Processors — Factor of 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–5

A.3.3 Avoiding Cache/TB Conflicts — Factor of 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–6

A.3.4 Sequential Read/Writ e — Factor of 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–8

A.3.5 Prefetching — Factor of 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–8

A.4 Code Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–9

A.4.1 Aligned Byte/ Word (W ithin Register) Memory Accesses. . . . . . . . . . . . . . . . . . . . . . . . A–9

A.4.2 Division . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–10

A.4.3 Byte Swap. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–11

A.4.4 Stylized Code Forms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–11

A.4.4.1 NOP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–11

A.4.4.2 Clear a Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–12

A.4.4.3 Load Literal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–12

A.4.4.4 Register-to-Register Move . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–13

A.4.4.5 Negate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–13

viii

Page 9

A.4.4.6 NOT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–13

A.4.4.7 Booleans . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–13

A.4.5 Exceptions and Trap Barriers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–14

A.4.6 Pseudo-Oper ati ons (Stylized Code Forms) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–14

A.5 Timing Considerations: Atomi c Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–16

B IEEE Floating-Point Conformance

B.1 Alpha Choices for IEEE Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–1

B.2 Alpha Support for OS Completion Handlers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–3

B.2.1 IEEE Floating-Poi nt Cont rol (FP_C) Quadword . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–4

B.3 Mapping to IEEE Standard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–6

C Instruction Summary

C.1 Common Architecture Instruction Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–1

C.2 IEEE Floating- Point Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–6

C.3 VAX Floating-Point Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–7

C.4 Independent Floating-Point Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–8

C.5 Opcode Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–8

C.6 Common Architecture Opcodes in Numerical Order. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–10

C.7 OpenVMS Alpha PALcode Instruction Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–14

C.8 DIGITAL UNIX PALcode Instruction Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–16

C.9 Windows NT Alpha Instruction Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–17

C.10 PALcode Opcodes in Numerical Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–18

C.11 Required PALcode Opcodes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–20

C.12 Opcodes Reserved to PALcode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–20

C.13 Opcodes Reserved to Compaq. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–21

C.14 Unused Function Code Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–21

C.15 ASCII Character Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–22

D Registered System and Processor Identifiers

D.1 Processor Type Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D–1

D.2 PALcode Variation Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D–2

D.3 Architecture Mask and Implementation Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D–3

E Waivers and Implementation-Dependent Functionality

E.1 Waivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–1

E.1.1 DECchip 21064, DECchip 21066, and DECchip 21068 IEEE Divide Instruction Violation E–1

E.1.2 DECchip 21064, DECchip 21066, and DECchip 21068 Write Buffer Violation . . . . . . . E–2

E.1.3 DECchip 21264 LDx_L/STx_C with WH64 Violation . . . . . . . . . . . . . . . . . . . . . . . . . . . E–2

E.2 Implementation-Specific Functionality. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–3

E.2.1 DECchip 21064/21066/21068 Performance Monitori ng . . . . . . . . . . . . . . . . . . . . . . . . E–3

E.2.1.1 DECchip 21064/21066/21068 Performance Monitor Interrupt Mechanism . . . . . . E–4

E.2.1.2 Functions and Arguments for the DECchip 21064/21066/2 1068 . . . . . . . . . . . . . . E–5

E.2.2 DECchip 21164/21164PC Per formance Monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . E–9

E.2.2.1 Performance Mon it or Interrupt Mechanism. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–9

ix

Page 10

E.2.2.2 Windows NT Alpha Functions and Argument . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–10

E.2.2.3 OpenVMS Alpha and DIGITAL UNIX Functions and Arguments . . . . . . . . . . . . . . E–12

E.2.3 21264 Performance M onitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–23

E.2.3.1 Performance Mon it or Interrupt Mechanism. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–23

E.2.3.2 Windows NT Alpha Functions and Argument . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E–24

E.2.3.3 OpenVMS Alpha and DIGITAL UNIX Functions and Arguments . . . . . . . . . . . . . . E–25

Index

x

Page 11

Figures

1–1 Instruction Format Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–4

2–1 Byte Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

2–2 Word Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

2–3 Longword Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

2–4 Quadword Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

2–5 F_floating Datum . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

2–6 F_floating Register Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

2–7 G_floating Datum . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4

2–8 G_floating Register Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

2–9 D_floating Datum. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

2–10 D_floating Register Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

2–11 S_floating Datum. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–7

2–12 S_floating Register Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–7

2–13 T_floating Datum. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–8

2–14 T_floating Register Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–9

2–15 X_floating Datum. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–10

2–16 X_floating Register Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–10

2–17 X_floating Big-Endian Datum . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–11

2–18 X_floating Big-Endian Register Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–11

2–19 Longword Integer Datum. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–11

2–20 Longword Integer Floating- Register Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–11

2–21 Quadword Integer Datum . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–12

2–22 Quadword Integer Floating-Register Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–12

2–23 Little-Endian Byte Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–13

2–24 Big-Endian Byte Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–13

3–1 Memory Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

3–2 Memory Instruction with Function Code Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–11

3–3 Branch Instruction Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–12

3–4 Operate Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–12

3–5 Floating-Point Operate Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–13

3–6 PALcode Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–15

4–1 Floating-Point Control Register (FPCR) Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–80

4–2 Floating-Point Instruction Function Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–84

8–1 Alpha System Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8–1

A–1 Branch -Format BSR and BR Opcodes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–3

A–2 Memory-Format JSR Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–3

A–3 Bad Allocation in Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–7

A–4 Better Allocation in Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–7

A–5 Best Allocation in Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A– 7

B–1 IEEE Floating-Point Control (FP_C) Quadword . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–4

B–2 IEEE Trap Handli ng Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–7

xi

Page 12

Tables

2–1 F_ fl oating Load Exponent Mapping (MAP_F) ....................................... .. ............... .. ...... 2–4

2–2 S_floating Load Exponent Mapping (MAP_S) ......... .. ............... ...................................... 2–7

3–1 Opera n d N o ta ti o n .. ... .. .................................................................................................... 3–4

3–2 Operand Value Notation ................................................................................................. 3–4

3–3 Expression Operand Notation ........................................................................................ 3–4

3–4 Operand Name Notation ................................................................................................ 3–5

3–5 Operand Access Type Notation .................................................................................... 3–5

3–6 Operand Data Type Notation ......................................................................................... 3–6

3–7 Operators ....................................................................................................................... 3–6

4–1 Opc ode Q ualifiers ........ ............... .. ............... .. ............... .. ............... .. ............... .. .............. 4–3

4–2 Memor y Integer Load/Store Instructi ons.............. ................................. ............... .. ......... 4–4

4–3 Contro l In s tructio n s Su m m a ry ...................................................................................... 4– 1 8

4–4 Jump In s tr uc tions Bra n ch P re d ic ti on ............................................................................ 4– 2 3

4–5 Integer Arithmetic Instructions Summary . ..................................................................... 4–24

4–6 Logical and Shift Instructions Summary........................................................................ 4–41

4–7 Byte-Within-Register Manipulation Instructions Summary ........................................... 4–47

4–8 VAX Trappi ng Mo des Summary ........ ........................................................................... 4–71

4–9 Summary of I EEE Trappi ng Modes .................. ................... ......................................... 4–72

4–10 Trap Shadow Length Rules .......................................................................................... 4–75

4–11 Floating-Point Control Register (FPCR) Bit Descriptions ............................................. 4–80

4–12 IEEE Floating-Point Function Field Bit Summary ......................................................... 4–85

4–13 VAX Floating-Point Function Field Bi t Summary .......... ................................................ 4–87

4–14 Memory Format Floating-Point Instructions Summary .................................................. 4–90

4–15 Floating-Point Branch Instructions Summary ................................................................ 4–99

4–16 Floating-Point Operate Instructions Summary ........................................................... 4–102

4–17 Miscellaneous Instructions Summary............................ .. ............... .. ............... .. .......... 4–132

4–18 VAX Compatibility Instructions Summary . ................................................................... 4–149

5–1 Processor Issue Constraints ....................................................................................... 5–13

6–1 PALcode Instructions that Require Recognition............................. .. ............... .. .............. 6–4

6–2 Required PALcode Instructions....................................................................................... 6–5

9–1 Unp ri vileged OpenVMS Alpha PALcode Instructi on Sum m ary ............................... .. .... 9–1

9–2 Privileged OpenVMS Alpha PALcode Instructions Summ ary ............................... ......... 9–8

10–1 Unprivileged Digital UNIX PALcode Inst ruction Summary .................. ........................ 10–1

10–2 Privileged Digital UNIX PALcode Instruction Summary ........................ ....................... 10–2

11–1 Unprivileged Windows NT Alpha PALcode Instruction Summary ........... ..................... 11–1

11–2 Privileged Windows NT Alpha PALcode Instruction Summary ..................................... 11–2

A–1 Cache Block Prefetching................................................................................................ A–8

A–2 Decodabl e Pseudo-Operations (Stylized Code Forms) ........................ ............... .. ...... A–14

B–1 Floating-Point Control (FP_C) Quadword Bit Summary ................................................ B–5

B–2 IEEE Floating-Point Trap Handling .................. .. ........................................................... B–8

B–3 IEEE Standard Char ts ............. .................................................. .. ................... ............. B–12

C–1 Instruction Format and Opcode Notation ....................................................................... C–1

C–2 Common Architecture Instructions ................................................................................ C–2

C–3 IEEE Floating-Point Instruc ti on Function Codes ............... .. .......................................... C–6

C–4 VAX Floating-Point Instruction Function Codes ............................................................ C–7

C–5 Independent Floating-Point Instruction Function Codes .......... ..................................... C–8

C–6 Opcode Summary ..................................... ..................................................... ............... C–9

C–7 Key to Opcode Summary ................. .. ............................................................................ C–9

C–8 Common Architecture Opcodes in Numerical Order ................................................... C–10

C–9 OpenVMS Alpha Unprivileged PALcode Inst ructions ................................................. . C–14

C–10 OpenVMS Alpha Privileged PALcode Instructions ...................................................... C–15

C–11 DIGITAL UNIX Unprivileged PALcode Instructions ..................................................... C–16

C–12 DIGITAL UNIX Privileged PALcode Instructions ......................................................... C–16

C–13 Windows NT Alpha Unprivil eged PALcode Instructions ............................................. C–17

C–14 Windows NT Alpha Privileg ed PALcode instructions ............................................. ..... C–17

xii

Page 13

C–15 PALcode Opcodes in Numeric al Order ......... .............................................................. C–18

C–16 Required PALcode Opcodes.......... .............................................. .. .. ............... .. ........... C–20

C–17 Opcodes Reserved for PALcode .................................................................................. C–20

C–18 Opcodes Reserved for Compaq................................................................................... C–21

C–19 ASCII Character Set..................................................................................................... C–22

D–1 Processor Type Assignments ........................................................................................ D–1

D–2 PALcode Variation Assignments...................................... .. ............... .. ............... .. .......... D–2

D–3 AMASK Bit Assignments .......... .. .................................... ............................................... D–3

D–4 IMPLVER Value Assignments ....................................................................................... D–3

E–1 DECchip 21064/21066/21068 Performance Monitoring Functions ............................ E–5

E–2 DECchip 21064/21066/21068 MUX Control Fields in ICCSR Register ......................... E–7

E–3 Bit Summary of PMCTR Register for Windows NT Alpha .......................................... E–11

E–4 OpenVMS Alpha and DI GITAL UNIX Per formance Monitoring Functions .................. E–12

E–5 21164/21164PC Enable Counters for OpenVMS Alpha and DIGITAL UNIX............... E–15

E–6 21164/21164PC Disable Counters for OpenVMS Alpha and DIGITAL UNIX ............. E–15

E–7 21164 Select Desired Events for OpenVMS Alpha and DIGITAL UNIX ............. ........ E–16

E–8 21164PC Select Desired Events for OpenVMS Alpha and DIGITAL UNIX ............. E–16

E–9 21164/21164PC Select Special Options for OpenVMS Alpha and DIGITAL UNIX...... E–17

E–10 21164/21164PC Select Desired Frequencies for OpenVMS Alpha and DIGITAL UNIX E–18

E–11 21164/21164PC Read Counters for OpenVMS Alpha and DIGI TAL UNIX ................. E–19

E–12 21164/21164PC Write Counters for OpenVMS Alp ha and DIGITAL UNIX ......... .. ...... E–19

E–13 21164/21164PC Counter 1 (PCSEL1) Event Selection .............................................. E–19

E–14 21164/21164PC Counter 2 (PCSEL2) Event Selection .............................................. E–20

E–15 21164 CBOX1 Event Selection ................................................................................... E–21

E–16 21164 CBOX2 Event Selection ................................................................................... E–21

E–17 21164PC PM0_MUX Event Selection ....................................... .. ................... ............. E–22

E–18 21164PC PM1_MUX Event Selection ....................................... .. ................... ............. E–22

E–19 Bit Summary of PCTR_CTL Register for Windows NT Alpha.................................... E–24

E–20 OpenVMS Alpha and DIGITAL UNIX Performance Monitoring Functions................... E–25

E–21 21264 Enable Counters for OpenVMS Alpha and DIGITAL UNIX............. .................. E–27

E–22 21264 Disable Counters for OpenVMS Alpha and DIGITAL UNIX ............................. E–27

E–23 21264 Select Desired Events for OpenVMS Alpha and DIGITAL UNI X ..................... E–28

E–24 21264 Read Counters for OpenVMS Alpha and DIGITAL UNIX ................................. E–28

E–25 21264 Write Counters for OpenVMS Alpha and DIGITAL UNIX ................................. E–28

E–26 21264 Enable and Write Counters for OpenVMS Alpha and DIGITAL UNIX.............. . E–29

xiii

Page 14

xiv

Page 15

Preface

Chapters 1 through 8 and appendixes A through E of this book are directly derived from the Alpha System Reference Manual, Version 7 and passed engineering change orders (ECOs) that have been

applied. It is an accurate repr esentation of the described parts of the Alpha architecture.

References in this handbook to the Alpha Architecture Reference Manual are to the Third Edition of

that manual, EY-W938E-DP.

xv

Page 16

Page 17

Chapter 1

Introduction

Alpha is a 64-bit load/store RISC archite ct ure that is designe d with particular emph asis on the

three elements that most affect performance: clock speed, multiple instruction issue, and multiple processors.

The Alpha architects e xa mine d an d analy zed c ur rent and the or etical R ISC arc hitec tur e desig n

elements and developed high-performance alternatives for the Alpha architecture. The architects adopted only those design elements that appeared valuable for a projected 25-year design

horizon. Thus, Alpha becomes the firs t 21st century computer architecture.

The Alpha architecture is designed to avoid bias toward any partic ular operating system or programming language. Alpha supports the OpenVMS Alpha, DIGITAL UNIX, and Windows NT

Alpha op e rating syst e m s a n d s up ports simple software m igra ti on for app li cations tha t ru n o n

those operating systems.

This manual descr ibe s in detai l how A lpha is de signed to be the leadership 64-bit arc hite ctur e

of the computer industry.

1.1 The Alpha Approach to RISC Architecture

Alpha Is a True 64-Bit Architecture

Alpha was designed as a 64-bit architecture. All registers are 64 bits in length and all operations are performed between 64-bit registers. It is not a 32-bit architecture that was later

expanded to 64 bits.

Alpha Is Designed for Very High-Speed Implementations

The instructions are very simple. All instr uc tions are 32 bits in le ngth. M emor y operations are

either loads or stores. All data manipulation is done between registers.

The Alpha architecture facilitates pipelining multiple instances of the same operations because

there are no special registers and no condition codes.

The instructions interact with e ach other only by one ins tru ct ion w ri ting a r eg ister o r me mor y

and another instruction reading from the same place. That makes it particularly easy to build

implementations that issue multiple instructions every CPU cycle.

Introduction 1–1

Page 18

Alpha makes it easy to maintain binary compatibility across multiple implementations and easy

to maintain full speed on multiple-issue implementations. For example, there are no implementation-speci fic pipeline timing hazards, no load-delay slots, and no branch-delay slots.

The Alpha Approach to Byte Manipulation

The Alpha arc hi te ctur e reads and write s by te s be tw e en reg iste rs a nd m e mor y w ith the LDBU

and STB instructions. (Alpha also supports word read/writes with the LDWU and STW

instructions .)

Byte shifting a nd mas king is perfo rme d w ith n ormal 64 -b it r egiste r-to-r eg ister i nstru ction s,

crafted to keep instruction sequences short.

The Alpha Approach to Multiprocessor Shared Memor y

As viewed from a second processor (including an I/O device), a sequence of reads and writes

issued by one processor may be arbitrarily reordered by an implementation. This allows implementations to use multibank caches, bypassed write buffers, write merging, pipelined wri tes

with retry on error, and so forth. If strict ordering between two accesses must be maintained,

explicit memory barrie r ins tructions can be inserted in the program.

The basic multiprocessor interlocking primitiv e is a RISC-style load_locked, modify,

store_conditional sequence. If the sequence runs without interrupt, exception, or an interfering

write from another processor, then the conditional store succeeds. Otherwise, the store fails and

the program eventually must branch back and retry the sequence. This style of interlocking

scales well with very fast caches and makes Alpha an especially attractive architecture for

building multiple-processor systems.

Alpha Instruction s Incl ude Hints for Achie vi ng Highe r Speed

A number of Alpha instruc tions include hints for imple mentatio ns, all aimed at achie ving

higher speed.

• Calculated jump instructions have a target hint that can allow much faster subroutine

calls and returns.

• There are prefetching hints for the memory syste m that can allow much higher cache hit

rates.

• There are granularity hints for the virtual-address mapping that can allow much more

effective use of translation lookaside buffers for large contiguous stru ctu res.

PALcode – Alpha’s Very Flexible Privileged Software Library

A Privileged Ar chite c ture Libr ary (PA Lc ode ) is a se t of subroutines that are spe c ific to a par ticular Alpha operating system implementation. These subroutines provide operating-system

primitives for context switching, interrupts, exceptions, and memory management. PALcode is

similar to the BIOS libraries that are provided in personal computers.

PALcode subroutines are invoked by implementation hardware or by software CALL_PAL

instructions.

1–2 Alpha Architecture Handbook

Page 19

PALcode is written in standard machine code with some implementation-specific extensions to

provide access to low-le vel hardware.

PALcode lets Alpha impleme ntations run the f ull Ope nVMS Alpha , DI GITA L UN IX, and

Windows NT Alpha operating systems. PALcode can provide this functionality with little

overhea d. F or exa mple, the Op e nV M S Al ph a PA L co de instructions let Al ph a ru n O pe n VM S

with little more hardwar e than tha t found on a con ventiona l R ISC m achin e: the PAL m ode bit

itself, plus four extra protection bits in eac h translation buffer entry.

Other versions of PALcode can be developed for real-time, teaching, and other applications.

PALcode makes Alpha an especially attractive architecture for multiple operati ng syste ms.

Alpha and Programming Languages

Alpha is an attractive architecture for compiling a large variety of programming languages.

Alpha has been carefully designed to avoid bias toward one or two programmi ng languages.

For exampl e:

• Alpha does not contain a subroutine call instruction that moves a register window by a

fixed amount. Thus, Alpha is a good match for programming languages with many

parameters and programming languages with no parameters.

• Alpha does not contain a global integer overflow enable bit. Such a bit would need to

be changed at every subroutine boundary when a FORTRAN program calls a C program.

1.2 Data Format Overview

Alpha is a load/store RISC architecture with the following data characteristics:

• All operations are done between 64-bit registers.

• Memory is accessed via 64-bit virtual byte addresses, using the little-endian or, option-

ally, the big-endian byte numbering convention .

• There are 32 integer registers and 32 floating- point registers.

• Longword (32-bit) and quadword (64-bit) inte gers are supported.

• Five floating-point data types are supported:

– VAX F_floating (32-bit)

– VAX G_floating (64-bit)

– IEEE single (32-bit)

– IEEE double (64-bit)

– IEEE extended (128-bit)

Introduction 1–3

Page 20

1.3 Instruc tion Form at Overvie w

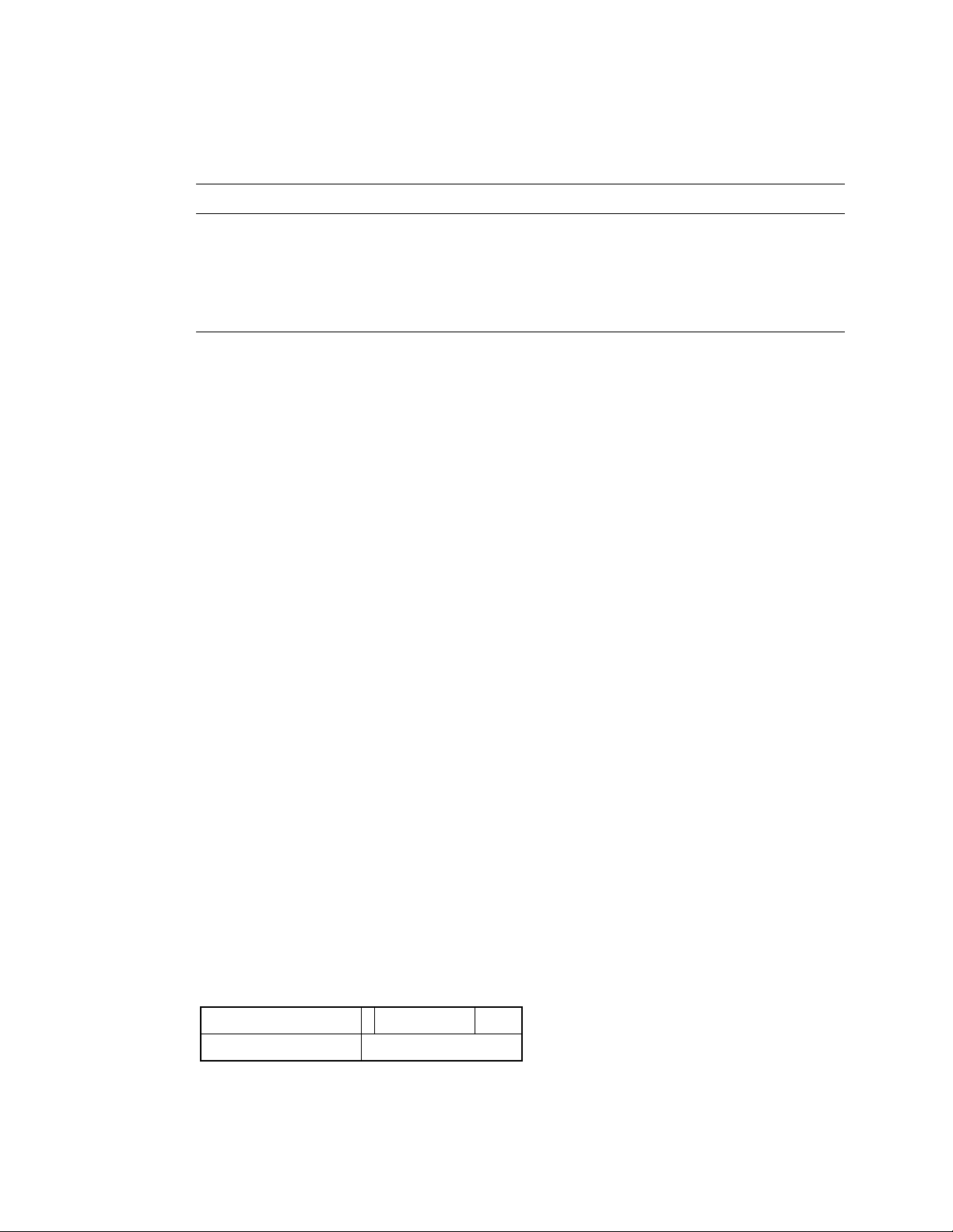

As shown in Figure 1–1, Alpha instructions are all 32 bits in length. Th ere are four major

instruction format classes that contain 0, 1, 2, or 3 register fields. All formats have a 6-bit

opcode.

Figure 1–1: I nstruct ion Format Overview

031 26 25 2120 16 15 5 4

NumberOpcode

PALcode Format

Function RCRB

Disp

Disp

Branch Format

Memory Format

Operate Format

Opcode

Opcode

Opcode

RA

RA

RA

RB

• PALcode instructi ons specify, in the function code field, one of a few dozen complex

operations to be performed .

• Conditional branch instructions test register Ra and specify a signed 21-bit PC-rela-

tive longword target displacement. Subroutine calls put the return address in register

Ra.

• Load and store instructions move bytes, words, longwords, or quadwords between

register Ra and memory, using Rb plus a signed 16-bit displacement as the memory

address.

• Operat e in stru ctions for floating-point and integer operations are both represented in

Figure 1–1 by the operate format ill ustr ation and are as follows:

– Word and byte sign-extension operators.

– Floating-point operations use Ra and Rb as source registers and write the result in

register Rc. There is an 11-bit extended opcode in the function field.

– Integer operations use Ra and Rb or an 8-b it literal as the source operand, and write

the result in registe r Rc.

– Integer operate instructions can use the Rb field and part of the function field to

specify an 8-bit litera l. There is a 7-bit extended opco de i n the func tion field.

1.4 Instruction Overview

PALcode Instructions

As described in Section 1.1, a Privileged Architecture Library (PALcode) is a set of subroutines that is specific to a particular Alpha operating-system implem entation. These subroutines

can be invoked by hardware or by software CALL_PAL instructions, which use the function

field to vector to the specifie d subroutine.

1–4 Alpha Architecture Handbook

Page 21

Branch Instruct i ons

Conditional branch i nstruc tions can tes t a reg ister fo r p ositiv e/negat ive or fo r zero /nonze ro,

and they can test inte ge r registe r s for e ven/odd. Uncondition al branc h ins tru ctions c a n write a

return address into a register.

There is also a calculated jump instruction that branches to an arbitrary 64-bit address in a

register.

Load / S tore Instruction s

Load and store instruc tion s m ove 8-bit, 16-bit, 32-bit, or 64-bit a ligne d qu an tities from a nd to

memory. Memory addresses are flat 64-bit virtual addresses with no segmentation.

The VAX floating-point load/store instructions swap words to give a consistent register format

for floating-point operations.

A 32-bit integer datum is placed in a register in a canonical form that makes 33 copies of the

high bit of the datum. A 32 -bit floating -po int datum is pla c ed in a regis ter in a canoni cal fo rm

that extends the exponent by 3 bits and extends the fraction with 29 low-order zeros. The 32bit operates preserve these canonical forms.

Compilers, as directed by user decl arations, can generate any mixture of 32-bit and 64-bit operations. The Alpha architecture has no 32/64 mode bit.

Integer Operate Instructions

The integer operate instructions manipulate full 64-bit values and include the usual assortment

of arithmetic, compare, logical, and shift instructions.

There are just three 32-bit inte ger ope rates: add , subtrac t, and mul tiply. The y diffe r from the ir

64-bit counterparts only in overflow detection and in producing 32-bit canonical results.

There is no integer divide instr uction.

The Alpha architectur e also suppor ts the following additional operations:

• Scaled add/subtract instructions for quick subscript calculation

• 128-bit multiply for division by a constant, and multiprecision arithmetic

• Conditional move instructions for avoiding branch instructions

• An extensive set of in-register byte and word manipul ation instructions

• A set of multimedia instructions that support gr aphics and video

Integer overflow tr ap enab le is en cod ed in th e fun ction field o f ea ch instruct ion, ra ther t han

kept in a global state bit. Thus, for example, both ADDQ/V and ADDQ opcodes exist for specifying 64 -bi t ADD w ith a nd w itho ut ov erfl ow check in g. Tha t m akes it eas ier to pi pel ine

implementations.

Introduction 1–5

Page 22

Floating-Point Operate Instructions

The floating-point operate instructions include four complete sets of VAX and IEEE arithmetic instructions, plus instructions for performing conversions between floating-point and

integer quantiti es.

In addition to the ope ratio ns f ound in co nventional RISC arc hitec tur es, A lpha inc lud es con ditional move instructions for avoiding branches and merge sign/exponent instructions for simple

field manipulation.

The arithmetic trap enables and rounding mode are encoded in the function field of each

instructi on, rather t han kept in g lobal stat e bits. Tha t makes it eas ier to pipe line

implementations.

1.5 Instruction Set Characteristics

Alpha instruction set char acteristics are as follows:

• All instructions are 32 bits long and have a regular for mat.

• There are 32 integer registers (R0 through R31), each 64 bits wide. R31 reads as zero,

and writes to R31 are ignored.

• All integer data manipulation is between intege r register s, with up to two variable regis-

ter source operands (one may be an 8-bit liter al) and one register destination operand.

• There are 32 floating-point registers (F0 through F31), each 64 bits wide. F31 reads as

zero, and writes to F31 are ignored.

• All floating-point data manipulation is between floating-point registers, with up to two

register source opera nds a nd one register destination operand.

• Instructions can move data in an integer register file to a f loating-point register file, and

data in a floating-point register file to an integer register file. The instructions do not

interpret bits in the register files and do not access memory.

• All mem ory referenc e instructions are of the load/store type that moves data between

registers and memory.

• There are no branch condition codes. Branch instructions test an integer or floating-

point register value , whic h may be the result of a previous compare.

• Integer and logical instructions operate on quadwords.

• Floating-point instructions operate on G_floating, F_floating, and IEEE extended, dou-

ble, and single operands. D_floating "format compatibility," in which binary files of

D_floating numbers may be processed, but without the last 3 bits of fraction precision,

is also provided.

• A minimal number of VAX compatibility instructions are included.

1.6 Terminology and Conventions

The following sections describe the terminology and conventions used in this book.

1–6 Alpha Architecture Handbook

Page 23

1.6.1 Numbering

All numbers are decima l unle ss oth erwis e ind icate d. Whe r e there is am bigu ity, numbe rs other

than decimal are indicated with the name of the base in subscript form, for example , 10

1.6.2 Securi ty Holes

A security hole is an erro r o f commission, omission, or oversight in a sy ste m tha t allows protection mechanisms to be bypassed.

Security holes exist when unprivileged software (software running outside of kernel mode)

can:

• Affect the operation of another process without authorization from the operating sys-

tem;

• Amplify its privilege without authorization from the operating system; or

• Communicate with another process, either overtly or covertly, without authorization

from the operating system.

The Alpha architecture has been designed to contain no a rchitectura l security holes. Hardwar e

(processors, buses, controllers, and so on) and software should likewise be designed to avoid

security holes.

16.

1.6.3 UNPREDICTABLE and UNDEFINED

The terms UNPREDIC TAB L E and UNDE FINE D are used through out this book. Their meanings are quite different and must be carefully distinguished.