Page 1

A

B

C

D

E

1

1

Compal Confidential

ZKU10 UMA M/B LA-B241P Schematics Document

2

Intel Shark Bay Haswell U

2014-01-10

REV:1.0

2

3

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

C

2013/09/22 2014/09/22

2013/09/22 2014/09/22

2013/09/22 2014/09/22

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-B241P

LA-B241P

LA-B241P

of

140Tuesday, January 21, 2014

of

140Tuesday, January 21, 2014

of

E

140Tuesday, January 21, 2014

3

4

1.0

1.0

1.0

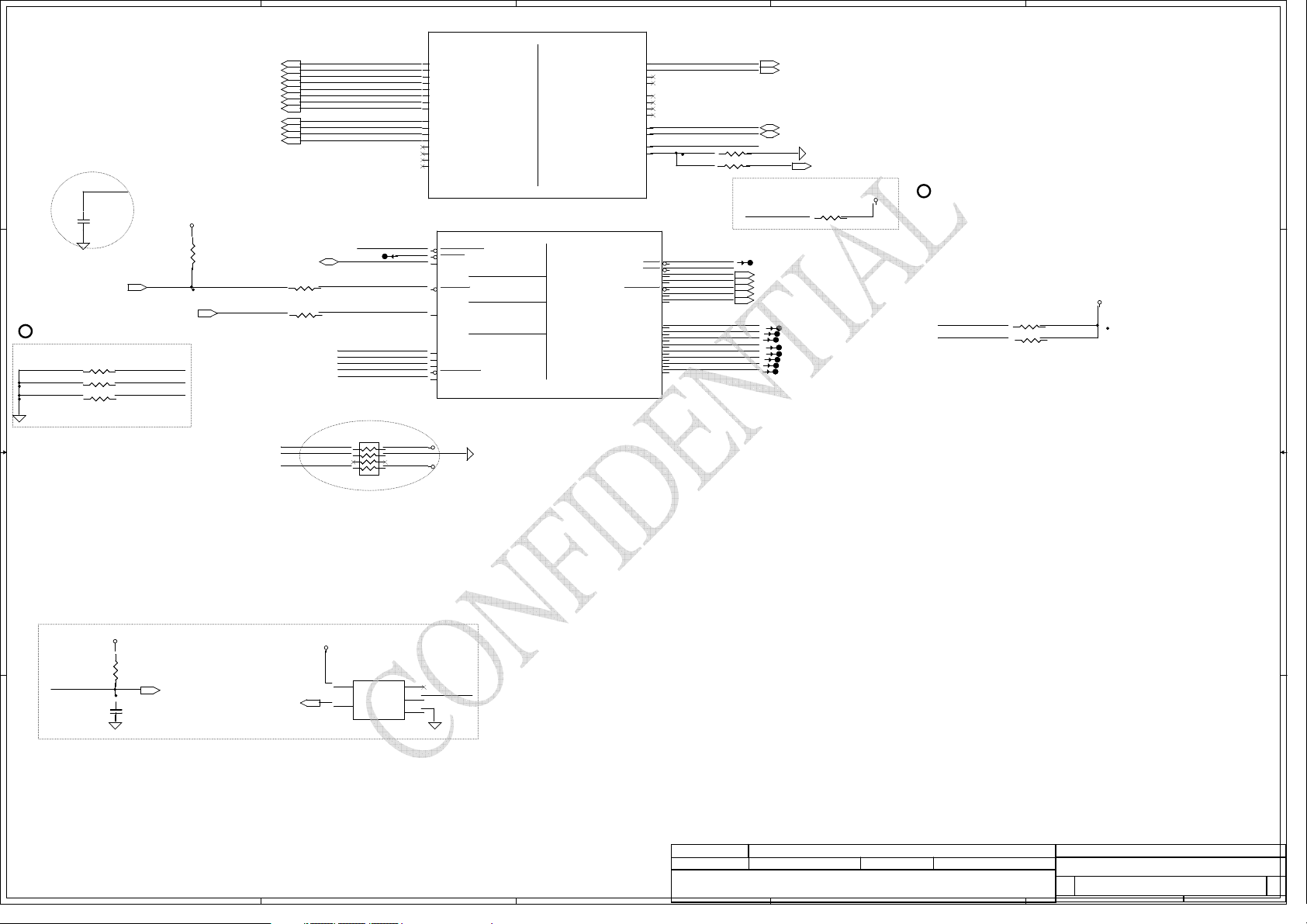

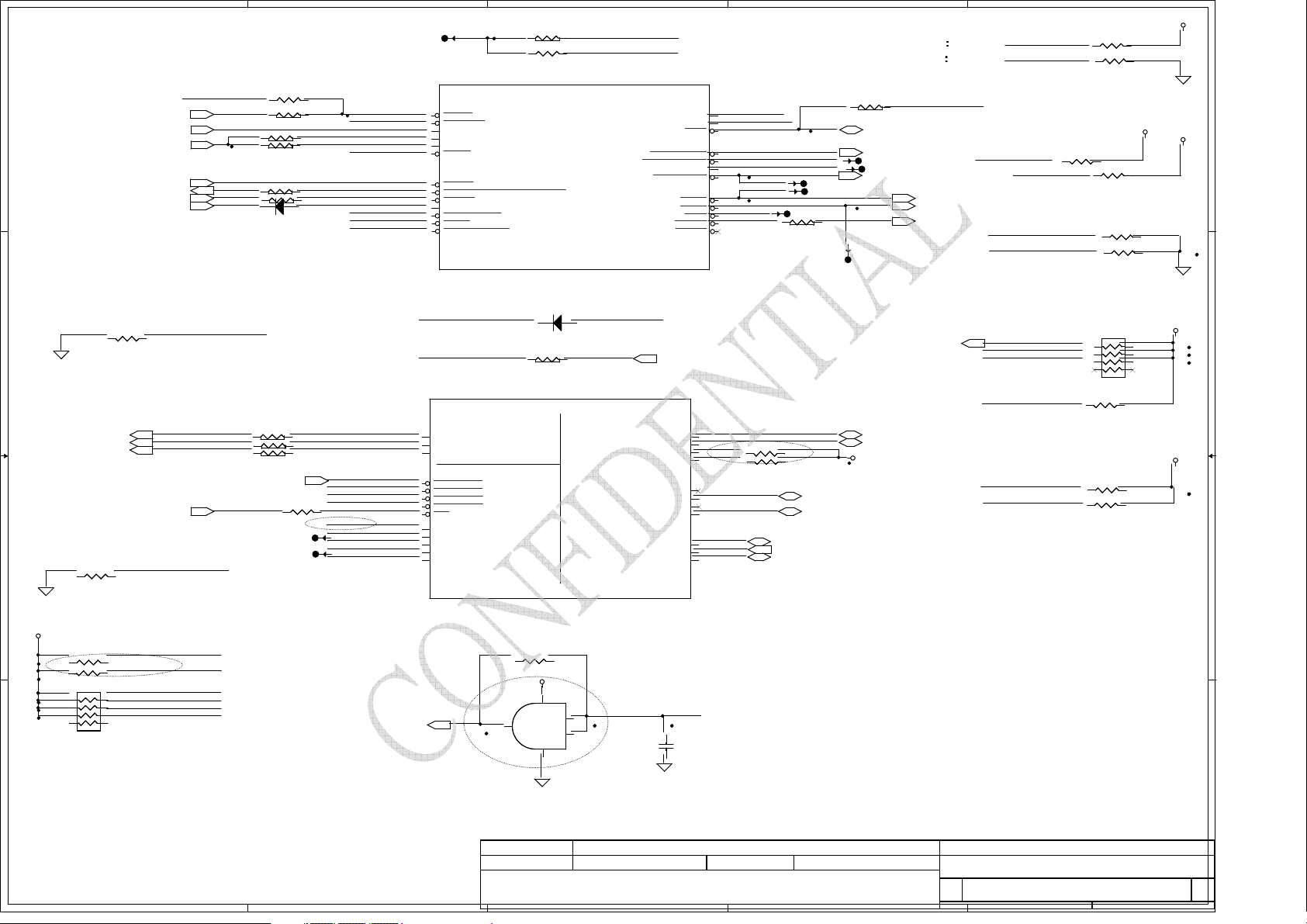

Page 2

A

Compal Confidential

Model Name :

Project Name :

B

C

D

E

1

2

LVDS Panel Conn.

Page 18

CRT Conn.

Page 28

eDP to LVDS Converter

(RTD2132R)

Page 17

DP to VGA Converter

(IT6512FN)

Page 27

HDMI Conn.

Page 19

Port 6Port 2

Port 3

eDP

DDI Port 1

DDI Port 2

PCIE

Memory Bus

1.35V DDR3L 1600MHz

USB2.0

Haswell

204pin DDRIII-SO-DIMM X1

Page 16

Port 0, 1

Port 2

Port 3

Port 4

USB3.0 CONN*2

For I/O Right Port

Page 23

USB2.0 CONN*1

For I/O Left Port

WLAN/BT

Camera

Page 28

Page 20

Page 18

1

2

Ultra Light & Thin

Page 8

LAN(GbE)Card Reader

Realtek RTL8151GH-CGRT5239-GR

RJ45 CONN

Page 21

Page 21

SPI

1168P BGA

(USW ULT)

USB3.0

SATA

Port 5

Port 0, 1

Port 0

Touch Screen

Page 18

USB3.0 CONN*2

For I/O Right Port

Page 23

SATA HDD 2.5"

Page 22

Int. Speaker

Page 24

3

WLAN/BT

Mini Card

Page 20Page 28

3

SYS BIOS ROM

8MB

Power/B

Fan Control

4

Page 26

Page 26

RTC CKT.

Page 7

DC/DC CKT

Page 29

HD Audio

Page 5~15

AUDIO CODEC

(ALC3227)

Page 24

Combo Jack

Page 24

D-MIC

Page 18

LPC

I2C

Page 25 Page 26

Int.KBDENE KB9012

www.schematic-x.blogspot.com

4

PS/2

Security Classification

Security Classification

Accelerometer

ST HP3DC2

A

Thermal

B

Touch Pad

Page 26Page 22 Page 8

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

C

2013/09/22 2014/09/22

2013/09/22 2014/09/22

2013/09/22 2014/09/22

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-B241P

LA-B241P

LA-B241P

Date: Sheet

Date: Sheet

D

Date: Sheet

Block Diagrams

Block Diagrams

Block Diagrams

E

1.0

1.0

1.0

of

240Tuesday, January 21, 2014

of

240Tuesday, January 21, 2014

of

240Tuesday, January 21, 2014

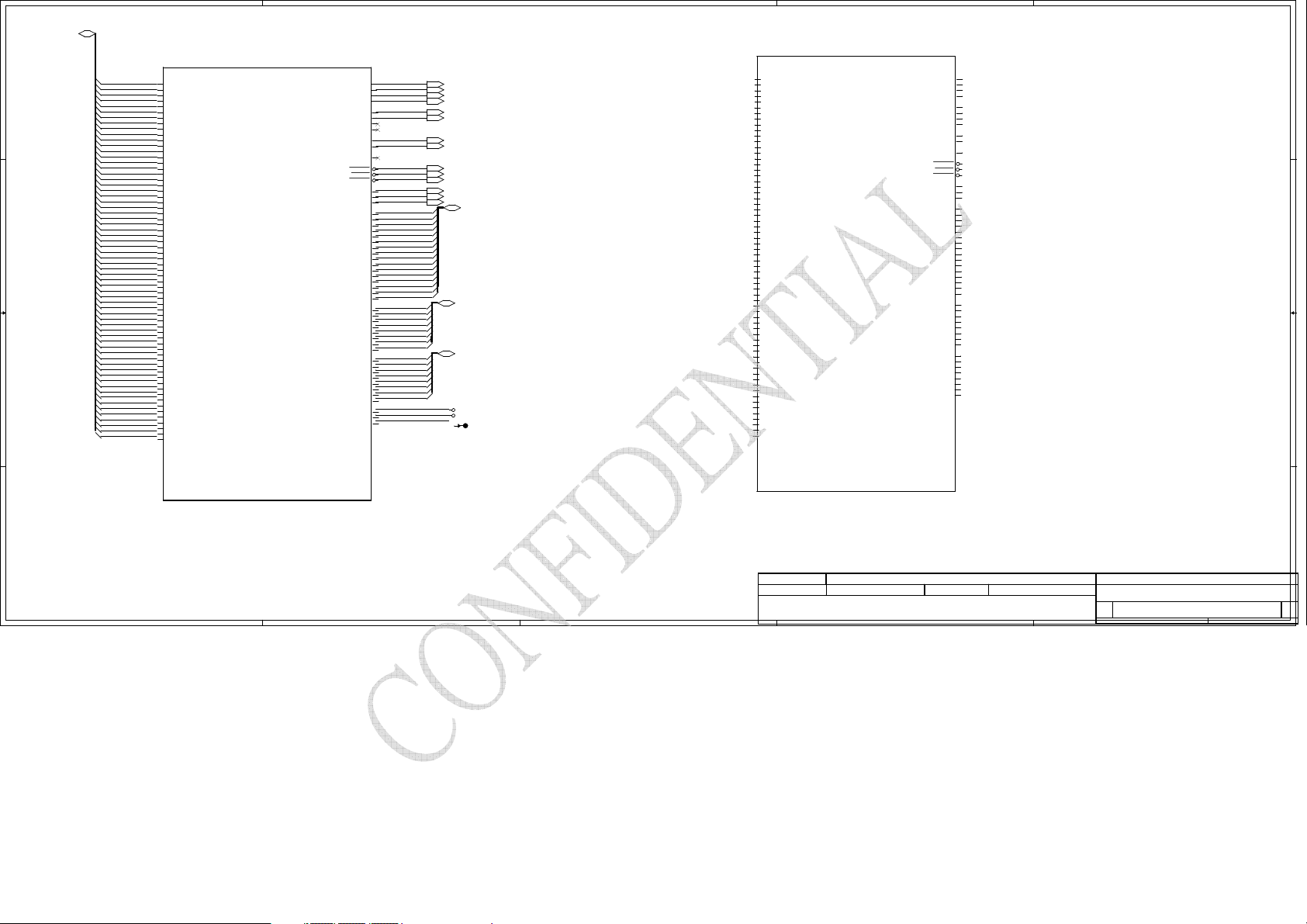

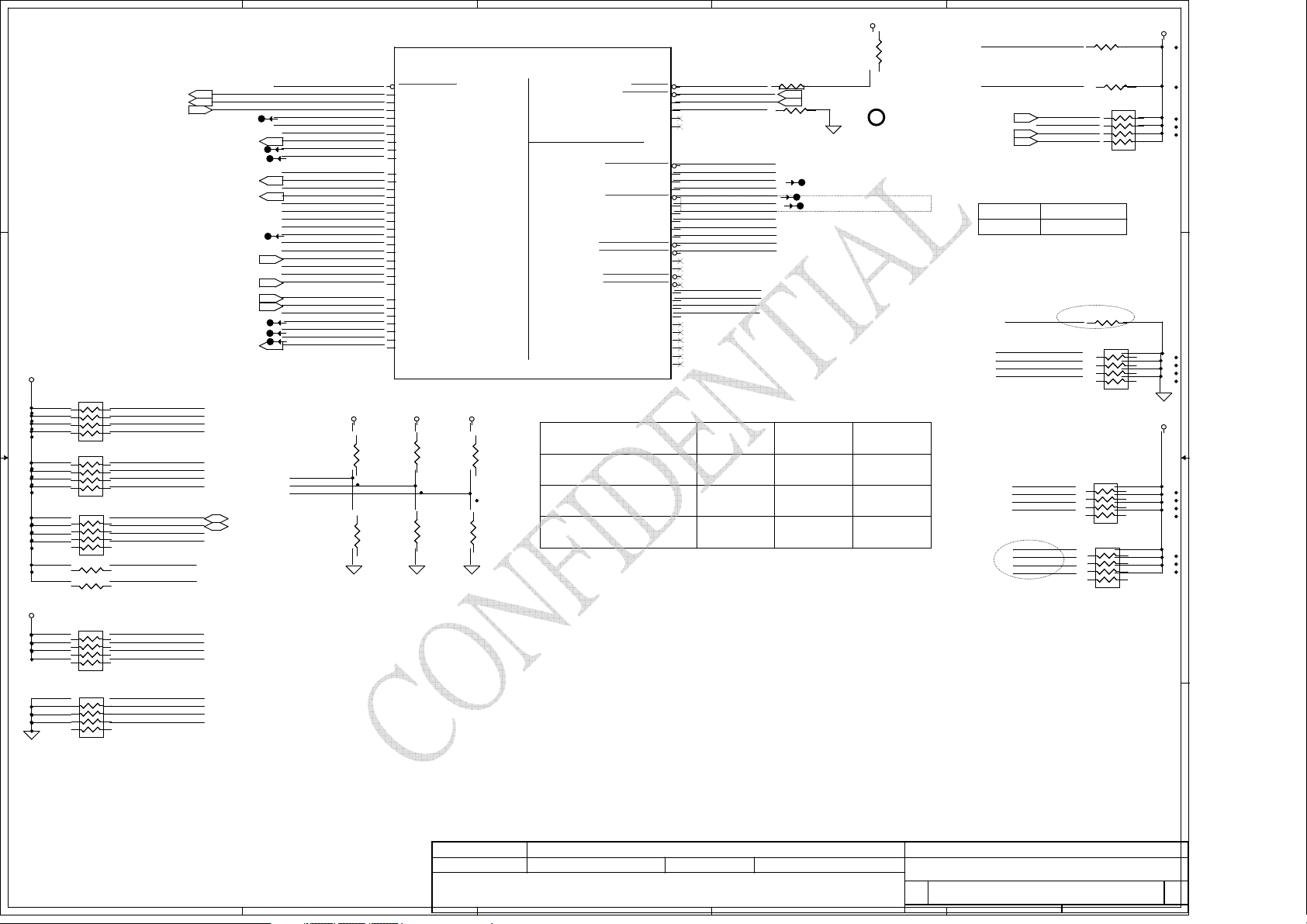

Page 3

A

B

C

D

E

Power Rails

VIN

BATT+ 12V Battery power supply

B+

1

2

+RTCVCC RTC Battery P ower

+3VL

+VL

+3VALW +3.3v Always power rail

+5VALW

+3V_PCH +3.3v Always power r ail for CPU

+0.6V_0.675VS +0.675V power r ail for DDR3L Ter minator

+3VS

+5VS

+1.05V/+1.05VS

+1.5VS

+VCC_CORE Core voltage for CPU

Note : ON* means that this power plane is O N only with AC power av ailable, otherwise it is OFF.

EC SM Bus1 address

Device Addre ss

Accelerometer

Battery

Charger

19V Adapter power supply

AC or batte ry pow er ra il for power circu it. (1 9V/12V)

+5.0v Always power r ail

+1.35V power r ail for DDR3L+1.35V_VDDQ

+3.3v system power rail

+5.0v system power rail

+1.05v system power rail

+1.5v system power rail

25 00101001

U25

S0 S3 S4/S5Power Plane Description

ON

ON ON

ON ONON

ON ONON

ON ONON

ON ONON

ON ONON

ON

ON ON

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ONON ON

ON

ON

ON

ONON

OFF

EC SM Bus2 address

Device Addre ss

Thermal Sensor UC3

4C 01001100 EMC1402-1

01001101 EMC1402-2

4D

Board ID / SKU ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7

100K +/- 1%Ra

Rb V min

0

12K +/- 1%

15K +/- 1%

20K +/- 1%

27K +/- 1%

33K +/- 1%

43K +/- 1%

56K +/- 1%

AD_BID

0 V

0.347 V 0.354 V 0.360 V

0.423 V

0.541 V

0.691 V

0.807 V 0.819 V 0.831 V

0.978 V

1.169 V

BOARD ID Table

Board ID

0

1

2

3

4

5

6

PCB Revision

0.1

V typ

AD_BID

V

AD_BID

max

0 V 0 .300V

0.430 V

0.550 V

0.438 V

0.559 V

0.702 V 0.713 V

0.992 V

1.185 V

1.006 V

1.200 V

BOM Option Table

BTO Item BOM Structure

Unpop @

ESD requirement unpop @ESD@

For Debug DB@

ESD requirement RF@

For SLB9635

For SLB9656

1

CONN@Connector

EMI@EMI requirement

ESD@ESD requirement

@EMI@EMI requirement unpop

2

9635@

9656@

Short@For short-pad

PCH SM Bus address

Device Addre ss

DDR3L

EC

eDP to LVD S IC

3

3

BOM config

PCB P/N

Pre SI BOM config

43 level BOM table

BOM Structure43 Level Description

4

DAX

DAX

PCB

PCB

Part Number = DAZ16B00201

Part Number = DAZ16B00201

PCB ZKU10 LA-B241P LS-A521P-24P/B245P

PCB ZKU10 LA-B241P LS-A521P-24P/B245P

A

ZZZ1

ZZZ1

HDMI

HDMI

Part Number = RO0000003HM

Part Number = RO0000003HM

PCB 102 LA-B151P REV0 M/B 3

PCB 102 LA-B151P REV0 M/B 3

45@

45@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

C

2013/09/22 2014/09/22

2013/09/22 2014/09/22

2013/09/22 2014/09/22

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Notes List

Notes List

Notes List

LA-B241P

LA-B241P

LA-B241P

of

340Tuesday, January 21, 2014

of

340Tuesday, January 21, 2014

of

E

340Tuesday, January 21, 2014

4

1.0

1.0

1.0

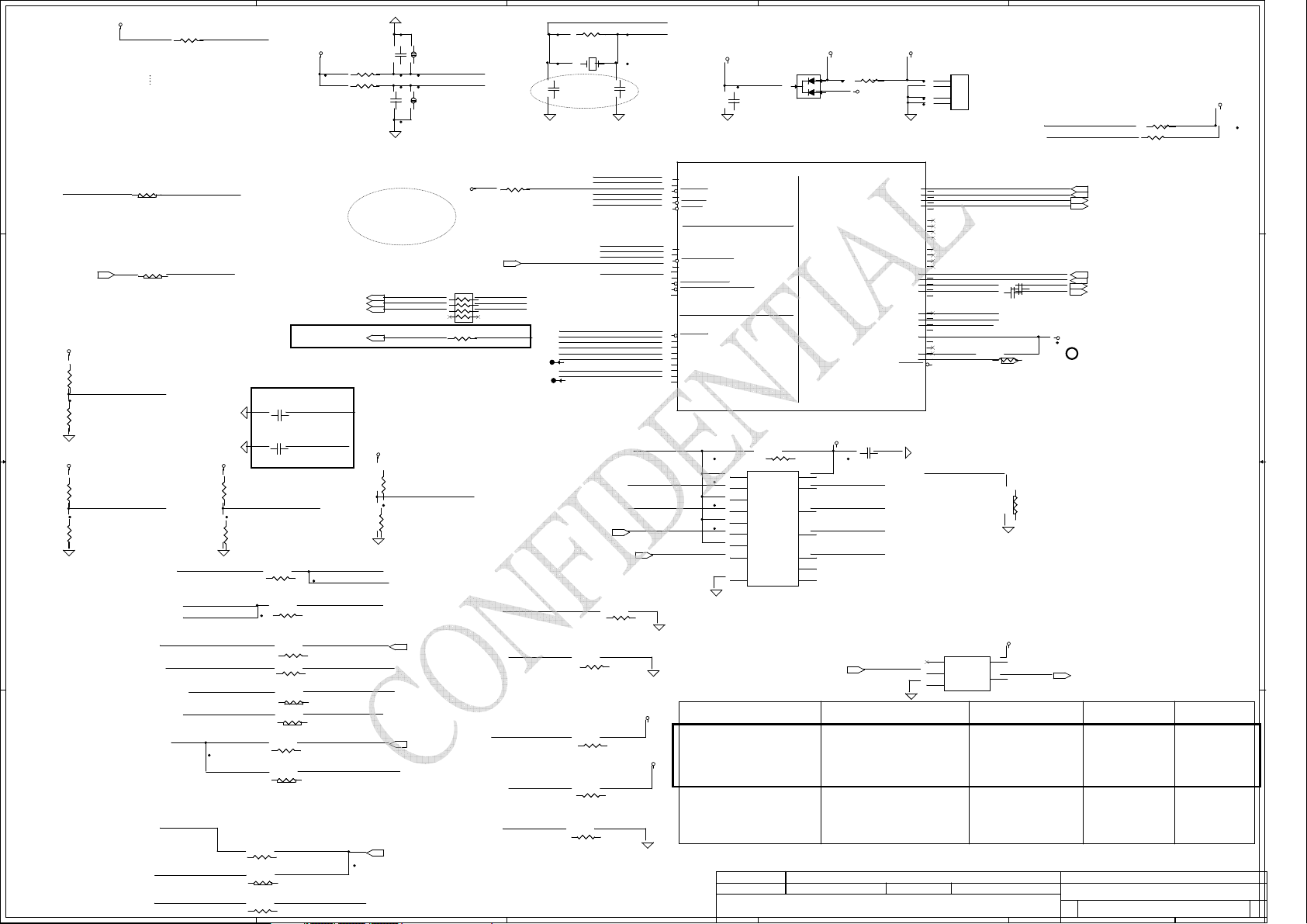

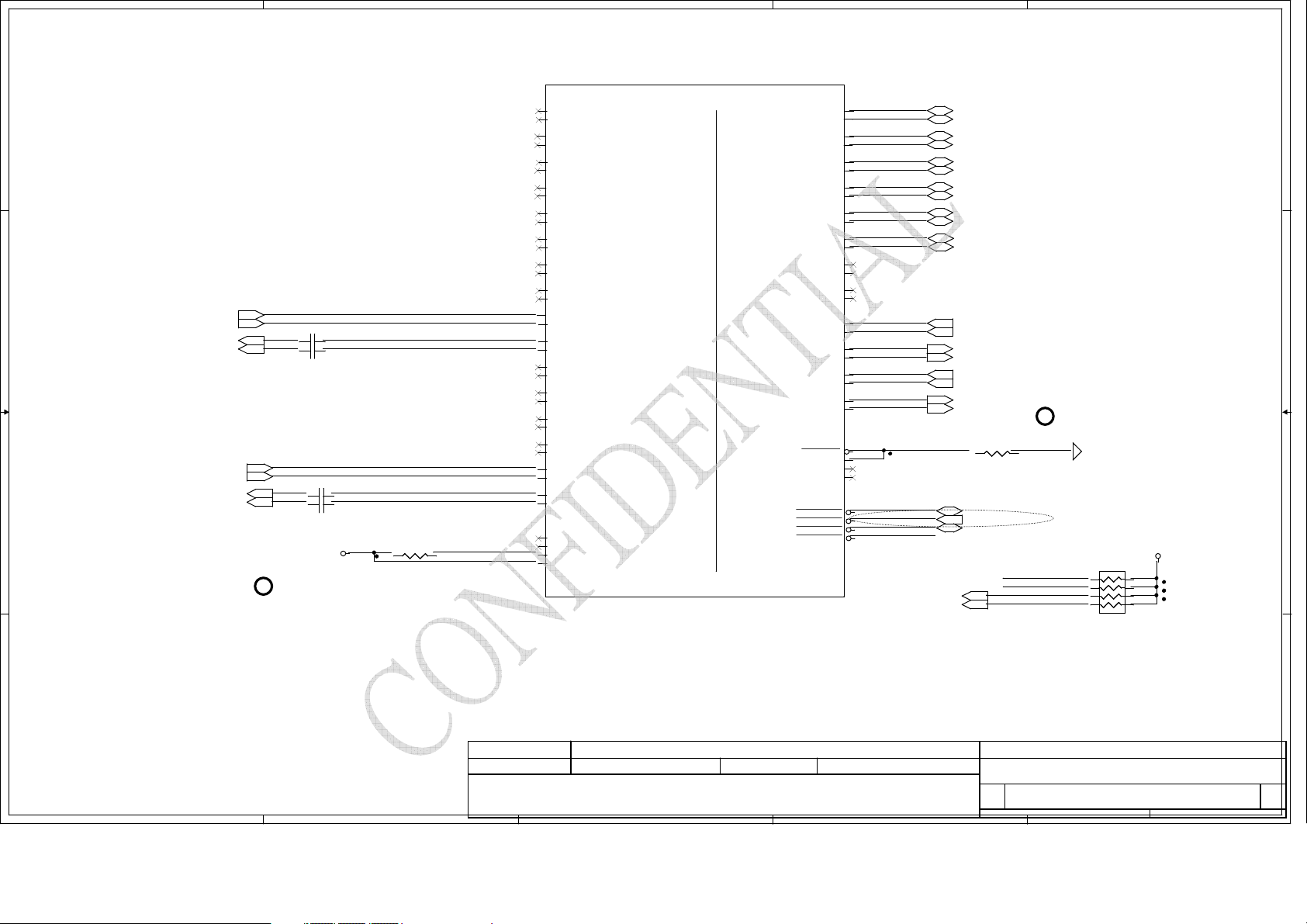

Page 4

5

4

3

2

1

D

EC_RSMRST#

PBTN_OUT#

EC_SLP_S4#

C

EC_SLP_S3#

DDR_PWROK

B

PMC_CORE_PWROK

DDR_CORE_PWROK

PMC_PLTRST#

ACIN

+3VLP

EC_ON

+3VALW

+5VALW

SPOK

+1.0VALW

+1.8VALW

ON/OFF

SYSON

+1.35V

VR_ON

+SOC_VCC

+SOC_VNN

VGATE

SUSP#

+1.0VS

+1.05VS

+1.35VS

+1.5VS

+1.8VS

+3VS

+5VS

+0.675VS

KBRST#

1.53ms

1.58ms

7.28ms

8.23ms

95.38ms

101ms

102ms

102ms

G3->S0 S0->S3 S3->S0

101ms

222ms

263ms

0.6ms

584ms

1.71ms

21ms

2.49ms

2.50ms

0.28ms

31.28us

1.30ms

1.84ms

2.79ms

2.11ms

3.77ms

4.41ms

12.83ms

49.83ms

110ms

110ms

116ms

33.68ms

11.71ms

8.8ms

1.56ms

11.71ms

11.71ms

2.56ms

8.85ms

10.55ms

8ms

10.71ms

22.32ms

2.50ms

2.50ms

279us

42.56ms

31.12us

16.59ms

15.31ms

20.48ms

19.61ms

144ms

1.29ms

1.83ms

2.08ms

2.8ms

3.77ms

4.41ms

12.77ms

49.87ms

110ms

110ms

116ms

2.38ms

SUSP#

5.57ms

1.52ms

2.18ms

36.20ms

9.81ms

11.5ms

8.12ms

10.71ms

16.63ms

15.34ms

S0->S5

20.27ms

19.60ms

148.3ms

204ms

3.29ms

3.29ms

ACIN

+3VLP

EC_ON

+3VALW

+5VALW

SPOK

+1.0VALW

+1.8VALW

ON/OFF

EC_RSMRST#

PBTN_OUT#

EC_SLP_S4#

EC_SLP_S3#

SYSON

+1.35V

DDR_PWROK

VR_ON

+SOC_VCC

+SOC_VNN

VGATE

SUSP#

+1.0VS

+1.05VS

+1.35VS

+1.5VS

+1.8VS

+3VS

+5VS

+0.675VS

KBRST#

PMC_CORE_PWROK

DDR_CORE_PWROK

PMC_PLTRST#

D

C

B

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRONI CS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRONI CS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRONI CS, INC.

3

2013/09/22 2014/09/22

2013/09/22 2014/09/22

2013/09/22 2014/09/22

Compal Secr et Data

Compal Secr et Data

Compal Secr et Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

LA-B241P

LA-B241P

LA-B241P

Power Sequence

Power Sequence

Power Sequence

1

of

440Tuesday, January 21, 2014

of

440Tuesday, January 21, 2014

of

440Tuesday, January 21, 2014

A

1.0

1.0

1.0

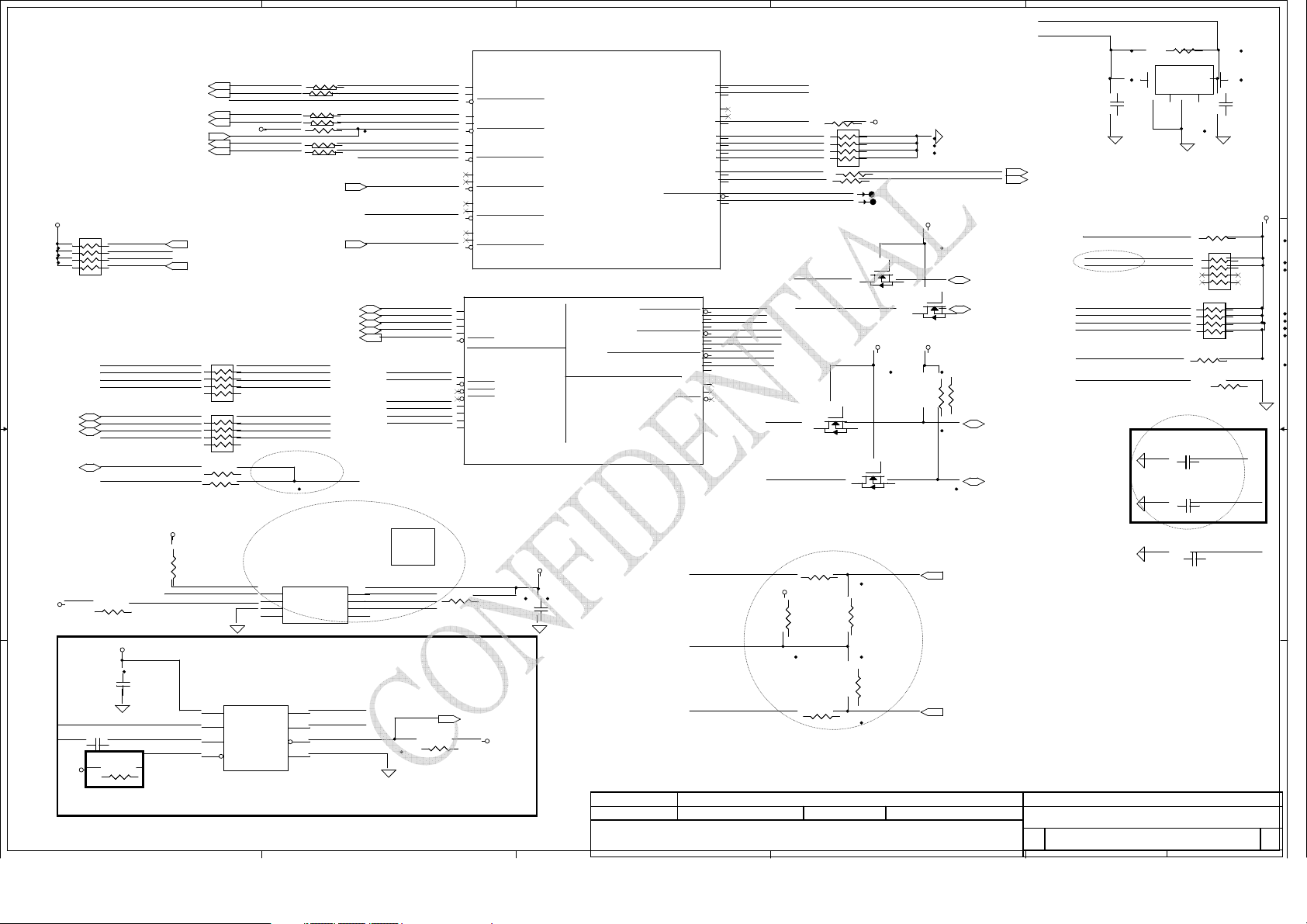

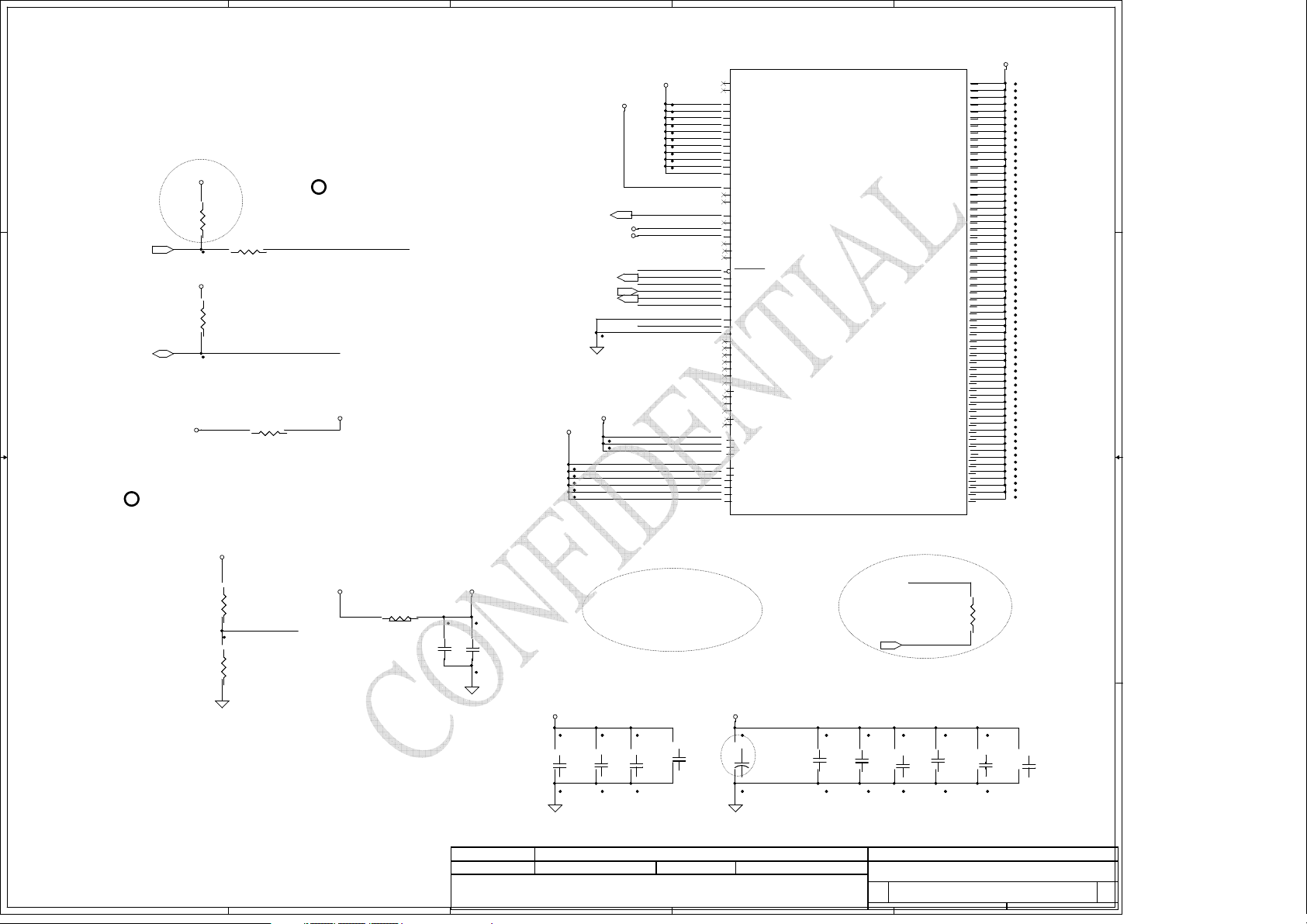

Page 5

D

H_PROCHOT#

1

CC108

CC108

22P_0402_50V8J

10/25 ESD's reuqest

DG V0.5 Trace width=12~15 mil

L

Max length=500mil

C

DDR3 COMPENSATION SIGNALS

22P_0402_50V8J

@ESD@

@ESD@

2

H_PROCHOT#[25,32]

2

2

2

1

RC18200_0402_1%

RC18200_0402_1%

1

RC19120_0402_1%

RC19120_0402_1%

1

RC20100_0402_1%

RC20100_0402_1%

5

H_PROCHOT#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

+VCCIO_OUT

RC4

RC4

62_0402_5%

62_0402_5%

+1.05VS_PG[7,12]

4

HASWELL_MCP_E

UCPU1A

<HDMI>

2

2

PCH_DPB_N2

PCH_DPB_P2

PCH_DPB_N1

PCH_DPB_P1

PCH_DPB_N0

PCH_DPB_P0

PCH_DPB_N3

PCH_DPB_P3

PCH_DPC_N0

PCH_DPC_P0

PCH_DPC_N1

PCH_DPC_P1

PROC_DETECT#

T51PAD @

T51PAD @

H_PROCHOT#_R

H_CPUPWRGD_R

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR3_DRAMRST#

DDR_PG_CNTL

RPC1

RPC1

4

5

3

6

2

7

1

8

10K_0804_8P4R_5%

10K_0804_8P4R_5%

PCH_DPB_N2[19]

PCH_DPB_P2[19]

PCH_DPB_N1[19]

PCH_DPB_P1[19]

PCH_DPB_N0[19]

PCH_DPB_P0[19]

PCH_DPB_N3[19]

PCH_DPB_P3[19]

PCH_DPC_N0[27]

PCH_DPC_P0[27]

PCH_DPC_N1[27]

PCH_DPC_P1[27]

1

2

H_PECI[25]

1

RC6 56_0402_5%

RC6 56_0402_5%

@

@

1

RC7 1K_0402_1%

RC7 1K_0402_1%

PROC_DETECT#

H_CPUPWRGD_R

+1.05VS_PG

UCPU1A

C54

DDI1_TXN0

C55

DDI1_TXP0

B58

DDI1_TXN1

C58

DDI1_TXP1

B55

DDI1_TXN2

A55

DDI1_TXP2

A57

DDI1_TXN3

B57

DDI1_TXP3

C51

DDI2_TXN0

C50

DDI2_TXP0

C53

DDI2_TXN1

B54

DDI2_TXP1

C49

DDI2_TXN2

B50

DDI2_TXP2

A53

DDI2_TXN3

B53

DDI2_TXP3

UCPU1B

UCPU1B

D61

PROC_DETECT

K61

CATERR

N62

PECI

K63

PROCHOT

C61

PROCPWRGD

AU60

SM_RCOMP0

AV60

SM_RCOMP1

AU61

SM_RCOMP2

AV15

SM_DRAMRST

AV61

SM_PG_CNTL1

+3V_PCH

+1.05VS_VCCST

20131120 HP's request

HASWELL_MCP_E

DDI EDP

DDI EDP

1 OF 19

1 OF 19

HASWELL_MCP_E

HASWELL_MCP_E

MISC

MISC

THERMAL

THERMAL

PWR

PWR

DDR3

DDR3

2 OF 19

2 OF 19

JTAG

JTAG

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

3

PRDY

PREQ

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

EDP_CPU_LANE_N0_C

EDP_CPU_LANE_P0_C

EDP_CPU_AUX#_C

EDP_CPU_AUX_C

EDP_COMP

RC1 0_0402_5%@

RC1 0_0402_5%@

RC2 0_0402_5%@

RC2 0_0402_5%@

XDP_PR DY#

J62

XDP_PR EQ#

K62

XDP_TC K

E60

XDP_TM S_CPU

E61

XDP_TR ST#_C PU

E59

XDP_TD I_CPU

F63

XDP_TD O_CPU

F62

XDP_OBS 0_R

J60

XDP_OBS 1_R

H60

XDP_OBS 2_R

H61

XDP_OBS 3_R

H62

XDP_OBS 4_R

K59

XDP_OBS 5_R

H63

XDP_OBS 6_R

K60

XDP_OBS 7_R

J61

EDP_CPU_LANE_N0_C [17]

EDP_CPU_LANE_P0_C [17]

EDP_CPU_AUX#_C [17]

EDP_CPU_AUX_C [17]

1

2

1

2

COMPENSATION PU FOR eDP

EDP_COMP

T58 PAD@

T58 PAD@

XDP_TC K [7]

XDP_TM S_CPU [7]

XDP_TR ST#_C PU [7]

XDP_TD I_CPU [7]

XDP_TD O_CPU [7]

T80 PAD@

T80 PAD@

T79 PAD@

T79 PAD@

T52 PAD@

T52 PAD@

T53 PAD@

T53 PAD@

T54 PAD@

T54 PAD@

T55 PAD@

T55 PAD@

T56 PAD@

T56 PAD@

T57 PAD@

T57 PAD@

BKL_PWM_CPU [9,17]

+VCCIOA_OUT

1

2

RC324.9_0402_1%

RC324.9_0402_1%

2

<eDP>

<eDP>

DG V0.9 PEG_COMP

L

Trace width=20mil and spacing=25mil

Max length=100mil

XDP_TD I_CPU

XDP_PR EQ#

2

RC12 51_0402_1%@

RC12 51_0402_1%@

2

RC13 51_0402_1%@

RC13 51_0402_1%@

1

D

+1.05VS_VCCST

1

1

C

B

+1.35V_VDDQ

1

RC308

RC308

470_0402_5%

470_0402_5%

@

@

2

1

CC88

CC88

0.1U_0402_16V7K

0.1U_0402_16V7K

2

5

DDR3_DRAMRST# [16]

DDR3_DRAMRST#

A

+1.35V_VDDQ

SM_PG_CTRL[16,35]

NonCS

UC10

UC10

5

4

NC

VCC

Y

GND

74AUP1G07GW_TSSOP5

74AUP1G07GW_TSSOP5

4

A

1

DDR_PG_CNTL

2

3

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

DDI,MSIC,XDP

DDI,MSIC,XDP

DDI,MSIC,XDP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-B241P

LA-B241P

LA-B241P

Date: Sheet

Date: Sheet

Date: Sheet

1

of

540Tuesday, January 21, 2014

of

540Tuesday, January 21, 2014

of

540Tuesday, January 21, 2014

Compal Electronics, Inc.

B

A

1.0

1.0

1.0

Page 6

5

DDR_A_D[0..63][16]

UCPU1C

UCPU1C

DDR_A_D0

D

C

B

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

AL58

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

<DDR3L>

HASWEL L_M CP_E

HASWEL L_M CP_E

DDR CHANNEL A

DDR CHANNEL A

SA_CLK#0

SA_CLK#1

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

SA_CLK0

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

4

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

DDR_A_MA0

AU36

DDR_A_MA1

AY37

DDR_A_MA2

AR38

DDR_A_MA3

AP36

DDR_A_MA4

AU39

DDR_A_MA5

AR36

DDR_A_MA6

AV40

DDR_A_MA7

AW39

DDR_A_MA8

AY39

DDR_A_MA9

AU40

DDR_A_MA10

AP35

DDR_A_MA11

AW41

DDR_A_MA12

AU41

DDR_A_MA13

AR35

DDR_A_MA14

AV42

DDR_A_MA15

AU42

DDR_A_DQS#0

AJ61

DDR_A_DQS#1

AN62

DDR_A_DQS#2

AM58

DDR_A_DQS#3

AM55

DDR_A_DQS#4

AV57

DDR_A_DQS#5

AV53

DDR_A_DQS#6

AL43

DDR_A_DQS#7

AL48

DDR_A_DQS0

AJ62

DDR_A_DQS1

AN61

DDR_A_DQS2

AN58

DDR_A_DQS3

AN55

DDR_A_DQS4

AW57

DDR_A_DQS5

AW53

DDR_A_DQS6

AL42

DDR_A_DQS7

AL49

+V_SM_VREF_CNT

AP49

+V_DDR_REFA_R

AR51

+V_DDR_REFB_R

AP51

M_CLK_DDR#0 [16]

M_CLK_DDR0 [16]

M_CLK_DDR#1 [16]

M_CLK_DDR1 [16]

DDR_CKE0_DIMMA [16]

DDR_CKE1_DIMMA [16]

DDR_CS0_DIMMA# [16]

DDR_CS1_DIMMA# [16]

DDR_A_RAS# [16]

DDR_A_WE# [16]

DDR_A_CAS# [16]

DDR_A_BS0 [16]

DDR_A_BS1 [16]

DDR_A_BS2 [16]

DDR_A_MA[0..15] [16]

DDR_A_DQS#[0..7] [16]

DDR_A_DQS[0..7] [16]

+V_SM_VREF_CNT

+V_DDR_REFA_R

T159

T159

3

HASWEL L_M CP_E

HASWEL L_M CP_E

DDR CHANNEL B

DDR CHANNEL B

AW31

AW29

AW27

AW25

AU25

AM29

AR29

AN29

AR28

AN26

AR26

AR25

AK26

AM26

AK25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

AY31

AY29

AV31

AU31

AV29

AU29

AY27

AY25

AV27

AU27

AV25

AK29

AL28

AK28

AP28

AP25

AL25

UCPU1D

UCPU1D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

2

AM38

SB_CK#0

AN38

SB_CK0

AK38

SB_CK#1

AL38

SB_CK1

AY49

SB_CKE0

AU50

SB_CKE1

AW49

SB_CKE2

AV50

SB_CKE3

AM32

SB_CS#0

AK32

SB_CS#1

AL32

SB_ODT0

AM35

SB_RAS

AK35

SB_WE

AM33

SB_CAS

AL35

SB_BA0

AM36

SB_BA1

AU49

SB_BA2

AP40

SB_MA0

AR40

SB_MA1

AP42

SB_MA2

AR42

SB_MA3

AR45

SB_MA4

AP45

SB_MA5

AW46

SB_MA6

AY46

SB_MA7

AY47

SB_MA8

AU46

SB_MA9

AK36

SB_MA10

AV47

SB_MA11

AU47

SB_MA12

AK33

SB_MA13

AR46

SB_MA14

AP46

SB_MA15

AW30

SB_DQSN0

AV26

SB_DQSN1

AN28

SB_DQSN2

AN25

SB_DQSN3

AW22

SB_DQSN4

AV18

SB_DQSN5

AN21

SB_DQSN6

AN18

SB_DQSN7

AV30

SB_DQSP0

AW26

SB_DQSP1

AM28

SB_DQSP2

AM25

SB_DQSP3

AV22

SB_DQSP4

AW18

SB_DQSP5

AM21

SB_DQSP6

AM18

SB_DQSP7

1

D

C

B

4 OF 19

3 OF 19

3 OF 19

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRONI CS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRONI CS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRONI CS, INC.

4 OF 19

Compal Secre t Data

Compal Secre t Data

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

Compal Secre t Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

DDRIII

DDRIII

DDRIII

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-B241P

LA-B241P

LA-B241P

Date: Sheet

Date: Sheet

Date: Sheet

1

of

640Tuesday, January 21, 2014

of

640Tuesday, January 21, 2014

of

640Tuesday, January 21, 2014

A

1.0

1.0

1.0

Page 7

5

+RTCVCC

2

RC236330K_0402_5%

RC236330K_0402_5%

HDA_SYNC

PCH_INT VRMEN

+RTCVCC

NonCS

RC32 20K_0402_5%

RC32 20K_0402_5%

RC34 20K_0402_5%

RC34 20K_0402_5%

1

INTVRMEN

H Integrated VRM enable

*

L

Integrated VRM disable

D

HDA_SYNC_R

1

RC353 0_0402_5%Short@

RC353 0_0402_5%Short@

2

Intel ME update

1

RC356 0_0402_5%Short@

RC356 0_0402_5%Short@

HDA_SDO[25]

R3d

R4

+3V_PCH

+3V_PCH

<XDP>

1

RC283

@

RC283

@

210_0402_5%

210_0402_5%

2

1

RC304

@

RC304

@

100_0402_1%

100_0402_1%

2

1

@

@

210_0402_5%

210_0402_5%

2

1

RC301

@

RC301

@

100_0402_1%

100_0402_1%

2

<XDP>

RC41

RC41

PCH_JTAG _TDO

PCH_JTAG _TDI

Contact ok

C

B

<PCH site>

<XDP>

<PCH site>

<XDP>

A

<PCH site>

<PCH site>

<PCH site>

5

HDA_SDOUT

2

HDA_SYNC_AUD IO[24]

HDA_SDOUT_AUD IO[24]

HDA_RST_AUDI O#[24]

HDA_BITCLK _AUDIO[24]

SI# 2012.11.01 Add RC367 for EMI

9/17 add RF solution

CC103

CC103

@RF@

@RF@

HDA_BITCLK _AUDIO

1

2

22P_0402_50V8J

22P_0402_50V8J

CC104

CC104

@RF@

@RF@

HDA_RST_AUDI O#

1

RC46

RC46

XDP_TCK _JTAGX

1

RC37 0_0402_5%@

RC37 0_0402_5%@

RC196 0_0402_5%@

RC196 0_0402_5%@

RC199 0_0402_5%@

RC199 0_0402_5%@

RC307 0_0402_5%@

RC307 0_0402_5%@

RC200 0_0402_5%Short @

RC200 0_0402_5%Short @

RC195 0_0402_5%Sho rt@

RC195 0_0402_5%Sho rt@

RC198 0_0402_5%@

RC198 0_0402_5%@

2

22P_0402_50V8J

22P_0402_50V8J

S1

S2

1

S3

1

J3S

1

J4d

1

1

S4

1

R5

2

PCH_JTAG _RST#

XDP_TMS _CPU

2

2

2

2

2

2

R8

XDP_TRS T#

PCH_JTAG _TMS

XDP_TMS

XDP_TDI _SWI TCH

PCH_JTAG _TDO

XDP_TDI

PCH_JTAG _TDI

XDP_TDO

+3V_PCH

1

2

1

2

@

@

210_0402_5%

210_0402_5%

RC302

@

RC302

@

100_0402_1%

100_0402_1%

J3D

1

RC194 0_0402_5%Sh ort@

RC194 0_0402_5%Sh ort@

XDP_TCK:XDP contact with CPU No 0ohm(RS5)

PCH_JTAG _TCK

J1S

1

RC197 0_0402_5%@

RC197 0_0402_5%@

XDP_TCK _JTAGX

XDP_TCK _JTAGX

J2D

1

RC193 0_0402_5%Short@

RC193 0_0402_5%Short@

J2S

1

RC306 0_0402_5%@

RC306 0_0402_5%@

2

2

2

XDP_TCK

2

XDP_TDO

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

1U_0402_6.3V6K

1U_0402_6.3V6K

XDP_TRS T#_CPU

XDP_TDI _CPU

XDP_TDI _SWI TCH

XDP_TDI _SWI TCH

XDP_TDI

XDP_TDO _CPU

PCH_JTAG _TDO

4

1

1

CC2

CC2

SHORT PADS

SHORT PADS

2

2

2

2

1

1

CC5

CC5

SHORT PADS

SHORT PADS

2

2

0927 No support WWAN

HDA_SYNC_AUD IO

HDA_RST_AUDI O#

+3V_PCH

1

RC45

@

RC45

@

210_0402_5%

210_0402_5%

2

1

RC303

@

RC303

@

100_0402_1%

100_0402_1%

2

Contact ok

<CPU site><PCH site>

XDP_TDI _CPU [5]

XDP_TDO _CPU [5]

XDP_TCK [5]

4

JCMOS1

JCMOS1

PCH_RTC RST#

PCH_SR TCRST#

JME1

JME1

EMI@

EMI@

PCH_JTAG _TMS

<PCH site>

<CPU and XDP>

<XDP>

CMOS

ME CMOS

+RTCVCC

RPC2

RPC2

1

2

3

4

RC367

RC367

1

33_0402_5%

33_0402_5%

<CPU site>

<PCH site>

HDA_SDIN0[24]

8

7

6

5

33_0804_8P4R_5%

33_0804_8P4R_5%

2

<CPU>

<XDP>

1

2

1

2

RC35 1M_0402_5%

RC35 1M_0402_5%

NonCS

HDA_SYNC_R

HDA_SDOUT

HDA_RST#

HDA_BIT_CL K

T151PAD~D

T151PAD~D

T153PAD~D

T153PAD~D

<CPU site>

PCH_JTAG _TCK

XDP_TRS T#_CPU

XDP_TDO _CPU

XDP_TDO

XDP_TCK

RC15 51_0402_1%

RC15 51_0402_1%

1

2

RC31 10M_0402_5%

RC31 10M_0402_5%

YC1

YC1

1

2

32.768KHZ Q13FC1350000500

32.768KHZ Q13FC1350000500

CC3

CC3

18P_0402_50V8J

18P_0402_50V8J

20131224 Change CC3/CC4 to 18pF

PCH_JTAG _RST#

PCH_JTAG _TCK

PCH_JTAG _TDI

PCH_JTAG _TDO

PCH_JTAG _TMS

RSVD_PGDMON

XDP_TCK _JTAGX

PCH_ED M

XDP_TMS _CPU[5]

PCH_RTC X1

PCH_RTC X2

SM_INTRUDER#

PCH_INT VRMEN

PCH_SR TCRST#

PCH_RTC RST#

HDA_BIT_CL K

HDA_SYNC

HDA_RST#

HDA_SDIN0

HDA_SDOUT

XDP_TRS T#_CPU[5]

1

CC4

CC4

18P_0402_50V8J

18P_0402_50V8J

2

R6

1

R9

1

2

RC16 51_0402_1%@

RC16 51_0402_1%@

R1d

2

RC10 51_0402_1%

RC10 51_0402_1%

+1.05VS_VCCST

1

R7

@

@

1

2

RC14 51_0402_1%

RC14 51_0402_1%

R2

1

2

3

PCH_RTC X1

PCH_RTC X2

AV11

AU12

AU11

AW10

AV10

AU62

AE62

AD61

AE61

AD62

AL11

AE63

EC_+1.05VS_PG

XDP_TDO _CPU

XDP_TDI _CPU

2

RC3851_0402_5% @

RC3851_0402_5% @

+1.05VS_VCCST

3

+RTCVCC

15mils

1U_0402_6.3V6K

UCPU1E

UCPU1E

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCL K

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_SDO/I2S0_TXD

DOCKEN/I2S1_TXD

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

PCH_TRST

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

TP5

AC4

TP6

JTAGX

AV2

RSVD

XDP_TRS T#_CPU

2

RTC

RTC

AUDIO

AUDIO

JTAG

JTAG

UC5

@

UC5

@

2

1OE

3

1A

5

2OE

6

2A

12

3OE

11

3A

15

4OE

14

4A

8

GND

74CBTLV3126DS_SSOP16

74CBTLV3126DS_SSOP16

1

CC6

CC6

1U_0402_6.3V6K

<EC output>

Topolog

Default Setting: Dual

TCK S can Chains

(also known as

"Shared JTAG" in

other docum ent)

Single TCK scan chain

(also known as "Com m on

JTAG" in other docum

ent)

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET I NFORMATION. THIS SH EET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRONI CS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRONI CS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CON SENT OF COMPAL ELECTRONI CS, INC.

1

BAV70W 3P C/C_SOT-323

BAV70W 3P C/C_SOT-323

HASWEL L_M CP_E

HASWEL L_M CP_E

5 OF 19

5 OF 19

RC240

RC240

1

2

10K_0402_5%

10K_0402_5%

VCC

1B

2B

3B

4B

NC

NC

2

RTC BAT conn

1K_0402_5%

1K_0402_5%

RC33

RC33

15mils15mils

1

2

+3VL

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_RCOMP

CC86

@

CC86

@

1

2

0.1U_0402_10V7K

0.1U_0402_10V7K

EC_+1.05VS_PG

Compal Secre t Data

Compal Secre t Data

Compal Secre t Data

2

+RTCBATT

SATA_IREF

TP7

TP8

SATALED

DIRECT_ESATA_DETECT#

Deciphered Date

Deciphered Date

Deciphered Date

JRTC1

JRTC1

1

1

2

2

3

GND

4

GND

ACES_50271-0020N-001

ACES_50271-0020N-001

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

PCIE_PT X_DRX_N6

C17

PCIE_PT X_DRX_P6

D17

V1

DIRECT_ESATA_DETECT#

U1

SATA_ODD_PRSNT_R_N

V6

mSATA_DET#

AC1

A12

L11

K10

SATA_COMP

C12

SATA_LED#

U3

UC11

UC11

1

NC

2

A

3

GND

74AUP1G07GW_TSSOP5

74AUP1G07GW_TSSOP5

Compal Electronics, Inc.

+RTCBATT_R

DC1

DC1

2

3

SATA

SATA

+3VS

@

@

16

XDP_TDO

4

XDP_TDI _SWI TCH

7

XDP_TMS

10

XDP_TRS T#

13

1

9

EC_+1.05VS_PG[25]

Description

In this topology, the

CPU JTAG chain will be

controlled by TCK0 and

TCK1 will control

the PCH JTAG chain.

In th is topolog y, PCH

TDI- TDO and CPU TDI-TDO

will be chained to form

one JTAG scan chain

controlled by TCK0

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

CONN@

CONN@

mSATA_DET#

SATA_ODD_PRSNT_R_N

1

2

CC7 0.1U_0402_16V7K

CC7 0.1U_0402_16V7K

1

2

CC8 0.1U_0402_16V7K

CC8 0.1U_0402_16V7K

0927 No support ODD/GPIO36

RC39

RC39

3K_0402_1%

3K_0402_1%

1

2

SATA_LED# [10,28]

1

RC220

short@

RC220

short@

0_0402_5%

0_0402_5%

2

+3V_PCH

5

VCC

4

Y

Be st Use for

- Run control oper.

- ME/Sx debug

-B oundary Scan/

Manufacturing est

1

+3VS

1

RC217 100K_0402_5%

RC217 100K_0402_5%

RC218 100K_0402_5%

RC218 100K_0402_5%

SATA_PRX_DTX_N0 [22]

SATA_PRX_DTX_P0 [22]

SATA_PTX_DRX_N0 [22]

SATA_PTX_DRX_P0 [22]

PCIE_PR X_DTX_N6 [20]

PCIE_PR X_DTX_P6 [20]

PCIE_PT X_C_DR X_N6 [20]

PCIE_PT X_C_DR X_P6 [20]

+1.05VS_VCCSATA3PLL

DG V0.9 SATA_COMP

L

Width=12mil

Max length=500mil

+1.05VS_PG [5,12]

Resistors

Stuffed

R1d,R2,R3d,

R4,R5,J1d

J2d,J3d*

J4d and Rs5*

J1s,J2s,J3s**

R2,R4,R5,R5s**

Title

Title

Title

RTC,SATA,HDA,JTAG

RTC,SATA,HDA,JTAG

RTC,SATA,HDA,JTAG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-B241P

LA-B241P

LA-B241P

Date: Sheet

Date: Sheet

Date: Sheet

2

1

2

2.5" HDD

WLAN/ BT

<Page 12>

<CPU,XDP,XDP Switch>

Resistors

ufStuffed

J1s, J2s,

J3s

R6,R7,R8,R9

R1d,r3d,J1d,J2d

J3d**,J4d,

R6,R7,R8,R9

1

of

740Tuesday, January 21, 2014

of

740Tuesday, January 21, 2014

of

740Tuesday, January 21, 2014

D

C

B

A

1.0

1.0

1.0

Page 8

D

C

B

+3V_PCH

A

PCIE LAN

PCIE Card reader

WLAN

+3VS

RPC4

RPC4

4

3

2

1

10K_0804_8P4R_5%

10K_0804_8P4R_5%

EC_SPI_SI[25]

EC_SPI_SO[25]

EC_SPI_CS0#[25]

EC_SPI_CLK[25]

RC85 3.3K_0402_5%

RC85 3.3K_0402_5%

1

+3VS

RC96 33K_0402_5%

RC96 33K_0402_5%

5

LAN_CLKREQ#_P

6

PCIECLKREQ4#

7

8

PCH_SPI_CS0#

PCH_SPI_SO

PCH_SPI_SI

PCH_SPI_WP#

EC_SPI_SI

EC_SPI_SO

EC_SPI_CS0#

PCH_SPI_HOLD#

EC_SPI_CLK

PCH_SPI_CLK

1

+3VS

0.1U_0402_16V4Z

0.1U_0402_16V4Z

CC15

CC15

2

2200P_0402_50V7K

2200P_0402_50V7K

1

5

1

RC49 0_0402_5%Short@

RC49 0_0402_5%Short@

1

RC50 0_0402_5%Short@

RC50 0_0402_5%Short@

1

RC310 0_0402_5%Short@

RC310 0_0402_5%Short@

1

RC311 0_0402_5%Short@

RC311 0_0402_5%Short@

1

RC53 10K_0402_5%

RC53 10K_0402_5%

+3VS

1

2

3

4

1

2

3

4

2

2

10/14 For BIOS's request, add SPI Socket

1

RC55 0_0402_5%Short@

RC55 0_0402_5%Short@

1

RC57 0_0402_5%Short@

RC57 0_0402_5%Short@

PCIECLKREQ3#[10]

PCIECLKREQ5#[10]

LPC_FRAME#[20,25]

PCH_SPI_CS0#_R

PCH_SPI_SO_R

PCH_SPI_SI_R

PCH_SPI_SIO2

PCH_SPI_SI_R

PCH_SPI_SO_R

PCH_SPI_CS0#_R

PCH_SPI_SIO3

10/18 Delete RC56 as EMI's requesst

PCH_SPI_CLK_R

PCH_SPI_CLK_R

SPI ROM 8M

UC2

UC2

1

CS#

2

SO/SIO1

3

WP#

4

GND

SI/SIO0

EN25Q64-104HIP SOP 8P

EN25Q64-104HIP SOP 8P

EC_SMI#

SERIRQ

2

CLK_PCIE_LAN#[21]

CLK_PCIE_LAN[21]

CLK_PCIE_CR#[28]

CLK_PCIE_CR[28]

CR_CLKREQ#[28]

CLK_PCIE_WLAN#[20]

CLK_PCIE_WLAN[20]

+3V_PCH

EC_SMI# [9]

SERIRQ [10,25]

RPC7

RPC7

8

7

6

5

15_0804_8P4R_5%

15_0804_8P4R_5%

RPC8

RPC8

8

7

6

5

15_0804_8P4R_5%

15_0804_8P4R_5%

1

RC368

EMI@

RC368

EMI@

15_0402_5%

15_0402_5%

1

RC369 15_0402_5%EMI@

RC369 15_0402_5%EMI@

2

@

@

RC80

RC80

3.3K_0402_5%

3.3K_0402_5%

PCH_SPI_CS0#_R

1

PCH_SPI_SO_R

PCH_SPI_WP#

CPU THERMAL SENSOR

1

@

@

CC14

CC14

2

H_THERMDA

H_THERMDC

CPU_THERM#

2

Thermal sensor SMBus address -->0111_100xb (0x78h)

5

UC3

SA00003PU00

UC3

SA00003PU00

1

VDD

2

D+

3

D-

4

THERM#

W83L771AWG-2 TSSOP 8P SENSOR

W83L771AWG-2 TSSOP 8P SENSOR

Address:0100_1100 EMC1402-1

Address:0100_1101 EMC1402-2

SCLK

SDATA

ALERT#

GND

8

7

6

5

EC_SMB_CK2

EC_SMB_DA2

THERMAL_ALERT#

LPC_AD0[20,25]

LPC_AD1[20,25]

LPC_AD2[20,25]

LPC_AD3[20,25]

VCC

HOLD#

SCLK

2

2

2

2

2

2

2

MINI1_CLKREQ#_P

EN25Q64-104HIP SOP 8P

EN25Q64-104HIP SOP 8P

8

PCH_SPI_HOLD#

PCH_SPI_CLK_R

7

PCH_SPI_SI_R

6

5

4

PCIE_LAN#

PCIE_LAN

LAN_CLKREQ#_P

PCIE_CR#

PCIE_CR

CR_CLKREQ#

PCIE_MINI1#

PCIE_MINI1

PCIECLKREQ3#

PCIECLKREQ4#

PCIECLKREQ5#

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_SIO2

PCH_SPI_SIO3

&UC2

45@

&UC2

45@

2

RC105 10K_0402_5%

RC105 10K_0402_5%

4

UCPU1F

UCPU1F

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

UCPU1G

UCPU1G

AU14

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

1

2

RC84

RC84

3.3K_0402_5%

3.3K_0402_5%

THERMAL_ALERT# [25]

1

HASWELL_MCP_E

HASWELL_MCP_E

LPC

LPC

SPI C-LINK

SPI C-LINK

+3V_PCH

1

@

@

CC11

CC11

0.1U_0402_16V7K

0.1U_0402_16V7K

2

+3VS

3

HASWELL_MCP_E

HASWELL_MCP_E

CPU_XTAL24_IN

A25

XTAL24_IN

XTAL24_OUT

DIFFCLK_BIASREF

CLOCK

CLOCK

SIGNALS

SIGNALS

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

6 OF 19

6 OF 19

SMBALERT/GPIO11

SMBCLK

SMBUS

SMBUS

SML1ALERT/PCHHOT/GPIO73

7 OF 19

7 OF 19

Security Classific ation

Security Classific ation

Security Classific ation

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_CLK

CL_DATA

CL_RST

3

CPU_XTAL24_OUT

B25

K21

TP15

M21

TP16

PCH_CLK_BIASREF

C26

TESTLOW1

C35

TP19

TESTLOW2

C34

TP20

TESTLOW3

AK8

TP21

TESTLOW4

AL8

TP22

CLK_PCI0

AN15

CLK_PCI1

AP15

CLK_CPU_ITP#

B35

CLK_CPU_ITP

A35

SMBALERT#

AN2

SMBCLK

AP2

SMBDATA

AH1

USB_CR_PWREN

AL2

SML0CLK

AN1

SML0DATA

AK1

SML1ALERT#

AU4

SML1CLK

AU3

SML1DATA

AH3

AF2

AD2

AF4

SMBCLK

SMBDATA

LAN_CLKREQ#_P

MINI1_CLKREQ#_P

PCIECLKREQ5#

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

+3VS

1

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

RC52

RC52

3K_0402_1%

3K_0402_1%

1

4

3

2

1

1

RC61 22_0402_5%EMI@

RC61 22_0402_5%EMI@

1

RC63 22_0402_5%EMI@

RC63 22_0402_5%EMI@

2N7002DWH_SOT363-6

2N7002DWH_SOT363-6

SML1CLK

SML1DATA

2

QC2A 2N7002DWH_S OT363-6

QC2A 2N7002DWH_S OT363-6

6

QC2B

QC2B

3

RC177

RC177

1

2

@

@

0_0402_5%

0_0402_5%

10K_0402_5%

10K_0402_5%

RC59

RC59

1

0_0402_5%

0_0402_5%

2

1

RC187

RC187

2

Deciphered Dat e

Deciphered Dat e

Deciphered Dat e

2

2

+1.05VS_AXCK_LCPLL

5

RPC3

RPC3

6

7

8

10K_0804_8P4R_5%

10K_0804_8P4R_5%

2

2

T82 PAD@

T82 PAD@

T81 PAD@

T81 PAD@

+3VS

2

6

1

QC6A

QC6A

5

3

2N7002DWH_SOT363-6

2N7002DWH_SOT363-6

QC6B

+3VS

1

LAN_CLKREQ#

0_0402_5%

0_0402_5%

2

RC184

RC184

0_0402_5%

0_0402_5%

QC6B

+3VS

2

RC78

RC78

10K_0402_5%

10K_0402_5%

1

5

2N7002DWH_SOT363-6

2N7002DWH_SOT363-6

4

RC183

RC183

20131120 Install RC183/RC187 to follow Intel HSW-U PCIECLKRQn# assignment

@

@

1

2

<Page12>

CLK_PCI_LPC

CLK_PCI_DEBUG

EC_SMB_CK2 [17,25]

EC_SMB_DA2 [17,25]

4

2

RC79

RC79

10K_0402_5%

10K_0402_5%

1

PCH_SMBCLK [16,17]

PCH_SMBDATA [16,17]

LAN_CLKREQ# [21]

MINI1_CLKREQ# [20]

CPU_XTAL24_IN

CPU_XTAL24_OUT

CC9

CC9

18P_0402_50V8J

18P_0402_50V8J

CLK_PCI_LPC [25]

CLK_PCI_DEBUG [20]

SMBALERT#

SML0CLK

SML0DATA

10/24 for layout smoothly

SMBCLK

SMBDATA

SML1CLK

SML1DATA

SML1ALERT#

USB_CR_PWREN

1

2

3

3

1

2

<EC>

<LPC Debug>

GND

4

YC2

YC2

24MHZ 12PF 20PPM X3G024000DC1H

24MHZ 12PF 20PPM X3G024000DC1H

RPC6

RPC6

2.2K_0804_8P4R_5%

2.2K_0804_8P4R_5%

1

RC481M_0402_5%

RC481M_0402_5%

1

1

GND

1

2

2

1

RPC5

RPC5

1

2

3

4

1K_0804_8P4R_5%

1K_0804_8P4R_5%

1

2

3

4

1

2

1

CC10

CC10

18P_0402_50V8J

18P_0402_50V8J

+3V_PCH

2

RC6910K_0402_5%

RC6910K_0402_5%

8

7

6

5

8

7

6

5

RC7710K_0402_5%

RC7710K_0402_5%

2

RF Solution

CC105

CC105

CLK_PCI_LPC

1

2

@RF@

@RF@

39P_0402_50V8J

39P_0402_50V8J

CC106

CC106

CLK_PCI_DEBUG

1

2

@RF@

@RF@

39P_0402_50V8J

39P_0402_50V8J

CC107

CC107

PCH_SPI_CLK_R

@RF@

@RF@

1

2

22P_0402_50V8J

22P_0402_50V8J

Compal Electronics, Inc.

Title

Title

Title

CLK,SPI,SMB,LPC

CLK,SPI,SMB,LPC

CLK,SPI,SMB,LPC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

LA-B241P

LA-B241P

LA-B241P

of

840Tuesday, January 21, 2014

of

840Tuesday, January 21, 2014

of

1

840Tuesday, January 21, 2014

D

C

RC24110K_0402_5%

RC24110K_0402_5%

B

A

1.0

1.0

1.0

Page 9

D

Deep S3

C

BKL_PWM_CPU[5,17]

ENBKL[25]

ENVDD_CPU[18]

B

RC120 100K_0402_5%

RC120 100K_0402_5%

5

SUSWARN#_R

SUSACK#[25]

SYS_PWROK[25]

PCH_PWROK[25]

PCH_RSMRST#[25]

PCH_SUSWARN#[25]

PBTN_OUT#[25]

ACIN[25,32,33]

1

2

RC112 100K_0402_5%

RC112 100K_0402_5%

PANEL_BKEN_CPU PD 100K on Page20

BKL_PWM_CPU

ENBKL

ENVDD_CPU

AOAC_PME#[25]

1

2

ENVDD_CPU

Non Deep S3 RC91-->SMT

Deep S3 RC93-->SMT

1

RC91 0_0402_5%@

RC91 0_0402_5%@

1

RC93 0_0402_5%Short@

RC93 0_0402_5%Short@

1

RC99 0_0402_5%Short@

RC99 0_0402_5%Short@

1

RC100 0_0402_5%Short@

RC100 0_0402_5%Short@

1

RC104 0_0402_5%

RC104 0_0402_5%

short@

short@

Short@

Short@

1

RC103 0_0402_5%

RC103 0_0402_5%

1

DC2

DC2

RB751V-40_SOD323-2

RB751V-40_SOD323-2

SYS_PWROK

1

RC114 0_0402_5%Short@

RC114 0_0402_5%Short@

1

RC115 0_0402_5%Short@

RC115 0_0402_5%Short@

1

RC116 0_0402_5%Short@

RC116 0_0402_5%Short@

EC_SMI#[8]

AOAC_PME#

RC305 0_0402_5%@

RC305 0_0402_5%@

4

1

RC268 0_0402_5%short@

PAD~D

PAD~D

PCH_RSMRST#

RC268 0_0402_5%short@

1

RC269 0_0402_5%@

RC269 0_0402_5%@

SYSTEM POWER MANAGEMENT

SYSTEM POWER MANAGEMENT

RB751V-40_SOD323-2

RB751V-40_SOD323-2

1

RC316 0_0402_5%Short@

RC316 0_0402_5%Short@

HASWELL _MCP_E

HASWELL _MCP_E

eDP SIDEBAND

eDP SIDEBAND

GPIO

GPIO

1

HASWELL _MCP_E

HASWELL _MCP_E

9 OF 19

9 OF 19

T83

T83

UCPU1H

2

2

2

2

2

2

2

2

2

2

1

T146

T146

T154

T154

BKL_PWM_CPU_R

ENBKL_CPU

ENVDD_CPU_R

EC_SMI#

PCI_PIRQB#

PCI_PIRQC#

GPIO80

AOAC_PME# _R

2

TP_INT#

TS_RST#

PCH_MC_WAKE#

PCH_MIC_DET

PCH_HP_DET

SUSACK#_R

SYS_RESET#

SYS_PWROK

PM_PWROK_R

APWRO K_R

PLT_RST#_PCH

PCH_RSMRST#

SUSWARN#_R

PBTN_OUT#_R

ACIN_R

PM_BATLOW#

PM_SLP_S0#_R

PCH_SLP_WLAN#

0927

UCPU1H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

PCH_DPWROK_R

UCPU1I

UCPU1I

B8

EDP_BKLCTL

A9

EDP_BKLEN

C6

EDP_VDDEN

U6

PIRQA/GPIO77

P4

PIRQB/GPIO78

N4

PIRQC/GPIO79

N2

PIRQD/GPIO80

AD4

PME

U7

GPIO55

L1

GPIO52

L3

GPIO54

R5

GPIO51

L4

GPIO53

3

2

2

8 OF 19

8 OF 19

PCH_PWROK

2

DC3

DC3

Deep S3 RC260-->SMT

2

DISPLAY

DISPLAY

PM_SLP_S0#_R

PM_SLP_S3#

DSWVRMEN

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

SLP_S5/GPIO63

PCH_DPWROK [25]

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

DPWROK

WAKE

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

DSWODVREN

AW7

PCH_DPWROK_R

AV5

WAKE#

AJ5

PM_CLKRUN#

V5

SUS_STAT#

AG4

SUSCLK

AE6

AP5

AJ6

PM_SLP_S3#

AT4

AL5

RC286 0_0402_5%

RC286 0_0402_5%

AP4

AJ7

Non Deep S3 RC286-->@

Deep S3 RC286-->SMT

PCH_DDPB_CLK

B9

PCH_DDPB_DAT

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

1

RC370 2.2K_0402_5%@

RC370 2.2K_0402_5%@

1

RC371 2.2K_0402_5%

RC371 2.2K_0402_5%

20131111 For CRT issue

DDI1_AUX_DN

DDI1_AUX_DP

2

RC108 0_0402_5%short@

RC108 0_0402_5%short@

T142

T142

T143

T143

T145

T145

1

2

Short@

Short@

T144

T144

2

2

DDI1_AUX_DN [27]

DDI1_AUX_DP [27]

PCH_DDPB_HPD [19]

DDI1_HPD [27]

EDP_HPD [17]

1

2

WAKE# [20,28]

PM_CLKRUN# [25]

T164

T164

T155

T155

PM_SLP_S5# [25]

PCH_DDPB_CLK [19]

PCH_DDPB_DAT [19]

+3VS

<HDMI>

<eDP HPD>

DSWODVREN - On Die DSW VR Enable

H Enable

*

Disable

L

AOAC_PME#

PM_SLP_S4# [25,35]

PM_SLP_S3# [25]

PM_SLP_SUS# [25]

EC_PME#[10,21,25]

WAKE#

PCH_RSMRST#

SUSCLK

EC_PME#

PM_BATLOW#

PCH_SLP_WLAN#

ACIN_R

DSWODVREN

DSWODVREN

RC98 1K_0402_5%

RC98 1K_0402_5%

SUSWARN#_R

RC101 100K_0402_5%

RC101 100K_0402_5%

<HDMI>

SYS_RESET#

PM_CLKRUN#

RC109 10K_0402_5%

RC109 10K_0402_5%

RC110 8.2K_0402_5%

RC110 8.2K_0402_5%

1

2

RC254 330K_0402_5%

RC254 330K_0402_5%

2

RC255 330K_0402_5%

RC255 330K_0402_5%

@

@

1

2

1

RC102 10K_0402_5%

RC102 10K_0402_5%

2

RC106 10K_0402_5%

RC106 10K_0402_5%

2

RC107 1K_0402_5%@

RC107 1K_0402_5%@

RPC9

RPC9

4

3

2

1

10K_0804_8P4R_5%

10K_0804_8P4R_5%

2

1

2

1

1

+3V_DSW_P

2

1

1

5

6

7

8

1

2

1

+RTCVCC

+3V_PCH

+3V_DSW_P

+3VS

D

C

B

+3VS

2

RC125 10K_0402_5%

RC125 10K_0402_5%

2

RC113 100K_0402_5%

RC113 100K_0402_5%

RPC10

RPC10

4

3

2

1

10K_0804_8P4R_5%

10K_0804_8P4R_5%

A

@

@

1

2

RC300 0_0402_5%

RC300 0_0402_5%

+3VS

5

UC9

UC9

VCC

4

Issued Date

Issued Date

Issued Date

IN1

OUT

IN2

GND

MC74VHC 1G08DFT2G _SC70-5

MC74VHC 1G08DFT2G _SC70-5

3

PLT_RST#_PCH

1

2

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

3

1

2

<CPU>

CC109

CC109

22P_0402_50V8J

22P_0402_50V8J

@ESD@

@ESD@

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

A

Title

Title

Title

PM,GPIO,DDI

PM,GPIO,DDI

PM,GPIO,DDI

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

2

LA-B241P

LA-B241P

LA-B241P

Date: Sheet

Date: Sheet

Date: Sheet

1

940Tuesday, January 21, 2014

940Tuesday, January 21, 2014

940Tuesday, January 21, 2014

1.0

1.0

1.0

of

of

of

5

PCH_MC_WAKE#

TP_INT#

10/01

PCI_PIRQB#

GPIO80

PCI_PIRQC#

PCH_HP_DET

PLT_RST#[20,21,25,28]

20131111 Correct Footprint

4

PLT_RST#

Security Classifi cation

Security Classifi cation

Security Classifi cation

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

1

5

6

7

8

Page 10

D

C

B

+3V_PCH

+3VS

RC213

RC213

RC139

RC139

NMI_DBG#_CPU[2 5]

LAN_PWR_EN[21]

EC_LID_OUT#[25]

RPC13

RPC13

4

5

3

6

2

7

1

8

10K_0804_8P4R_5%

10K_0804_8P4R_5%

RPC14

RPC14

4

5

3

6

2

7

1

8

10K_0804_8P4R_5%

10K_0804_8P4R_5%

RPC16

RPC16

4

5

3

6

2

7

1

8

10K_0804_8P4R_5%

10K_0804_8P4R_5%

USB32_P0_PWREN_R#

1

2

100K_0402_5%

RPC18

RPC18

RPC19

RPC19

100K_0402_5%

2

10K_0402_5%

10K_0402_5%

5

6

7

8

5

6

7

8

1

4

3

2

1

10K_0804_8P4R_5%

10K_0804_8P4R_5%

4

3

2

1

10K_0804_8P4R_5%

10K_0804_8P4R_5%

5

UART_WAKE#

BT_ON

EC_LID_OUT#

NMI_DBG#_CPU

PCH_GPIO44

HDDHALT_LED#

PCH_GPIO58

WL_OFF#

USB_OC0#

USB_OC2#

ACCEL_INT#

LANCB_DET#_PCH

EC_SCI#

PCH_GPIO17

DEVSLP1

DEVSLP2

MPHY_PWREN

PCH_AUDIO_PWREN

TOUCH_PANEL_PWREN

LAN_PWR_EN

USB_CAM_PWREN

EC_PME#[9,21,2 5]

HDDHALT_LED#[2 8]

WL_OFF#[20]

PCH_GPIO14[11 ]

ACCEL_INT#[22]

PCH_GPIO9[11]

EC_SCI#[2 5]

HDA_SPKR[24]

USB_OC0# [11,23]

USB_OC2# [11]

T166

T166

T148

T148

T149

T149

T150

T150

T158

T158

T162

T162

T163

T163

PCH_AUDIO_PWREN

NMI_DBG#_CPU

LAN_PWR_EN

EC_LID_OUT#

PCH_GPIO16

PCH_GPIO17

UART_WAKE#

EC_PME#

BT_ON

HDDHALT_LED#

PCH_GPIO58

WL_OFF#

PCH_GPIO44

LPDDR3_ID1

LPDDR3_ID2

LPDDR3_ID3

MPHY_PWREN

USB32_P0_PWREN_R#

PCH_GPIO14

USB_CAM_PWREN

LANCB_DET#_PCH

ACCEL_INT#

PCH_GPIO9

EC_SCI#

PCH_GPIO33

Dummy

DEVSLP1

DEVSLP2

HDA_SPKR

+3V_PCH

1

RC135

RC135

10K_0402_5%

LPDDR3_ID1

LPDDR3_ID2

LPDDR3_ID3

10K_0402_5%

2

1

2

4

UCPU1J

UCPU1J

P1

BMBUSY/GPIO76

AU2

GPIO8

AM7

LAN_PHY_PWR_CTRL/GPIO12

AD6

GPIO15

Y1

GPIO16

T3

GPIO17

AD5

GPIO24

AN5

GPIO27

AD7

GPIO28

AN3

GPIO26

AG6

GPIO56

AP1

GPIO57

AL4

GPIO58

AT5

GPIO59

AK4

GPIO44

AB6

GPIO47

U4

GPIO48

Y3

GPIO49

P3

GPIO50

Y2

HSIOPC/GPIO 71

AT3

GPIO13

AH4

GPIO14

AM4

GPIO25

AG5

GPIO45

AG3

GPIO46

AM3

GPIO9

AM2

GPIO10

P2

DEVSLP0/GPIO3 3

C4

SDIO_POWER_EN/ GPIO70

L2

DEVSLP1/GPIO3 8

N5

DEVSLP2/GPIO3 9

V2

SPKR/GPIO81

+3VS

@

@

RC263

@

RC263

@

10K_0402_5%

10K_0402_5%

1

RC261

RC261

10K_0402_5%

10K_0402_5%

@

@

2

1

RC264

@

RC264

@

10K_0402_5%

10K_0402_5%

2

HASWELL_MCP_E

HASWELL_MCP_E

GPIO

GPIO

+3VS

1

RC262

RC262

10K_0402_5%

10K_0402_5%

2

1

RC265

@

RC265

@

10K_0402_5%

10K_0402_5%

2

10 OF 19

10 OF 19

CPU/

CPU/

MISC

MISC

LPIO

LPIO

3

THRMTRIP

RCIN/GPIO82

SERIRQ

OPI_COMP2

RSVD

RSVD

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO9 1

UART0_TXD/GPIO 92

UART0_RTS/GPIO 93

UART0_CTS/GPIO 94

UART1_RXD/GPIO0

UART1_TXD/GPIO 1

UART1_RST/GPIO 2

UART1_CTS/GPIO 3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO6 4

SDIO_CMD/GPIO65

SDIO_D0/GPIO6 6

SDIO_D1/GPIO6 7

SDIO_D2/GPIO6 8

SDIO_D3/GPIO6 9

DG V0.9 PCH_OPIRCOMP

Width=12mil,spacing=12mil

Max length=500mil

H_THERMTRIP#_C

D60

EC_KBRST#

V4

SERIRQ

T4

PCH_OPIRCOMP

AW15

AF20

AB21

NGFF_WIFI_3.3_PWREN

R6

WWAN_PWREN

L6

PCH_GPIO85

N6

MSATA_SSD_PWREN

L8

WWAN_OFF#

R7

TOUCH_PAD_PWREN#

L5

TOUCH_PANEL_PWREN

N7

SATA1_PWREN

K2

PCH_LAN_RST#

J1

PCH_LAN_WAKE#

K3

PCH_CR_RST#

J2

PCH_CR_WAKE#

G1

K4

G2

J3

J4

I2C_ 0_SDA

F2

I2C_ 0_SCL

F3

I2C_ 1_SDA

G4

I2C_ 1_SCL

F1

E3

F4

D3

E4

C3

E2

RC129

RC129

0_0402_5%

0_0402_5%

1

2

Short@

Short@

49.9_0402_1%

49.9_0402_1%

GPIO47 GPIO48 GPIO49

2

H_THEMTRIP#

2

RC131

RC131

EC_KBRST# [25]

SERIRQ [8,25]

1

T165

T165

T160

T160

0927 Need add PU/PD?

T161

T161

+1.05VS_VCCST

1

RC242

RC242

1K_0402_5%

1K_0402_5%

2

L

EC_KBRST#

WWAN_OFF#

PCIECLKREQ3#[8]

PCIECLKREQ5#[8]

SATA_LED#[7,28]

Boot BIOS Strap

0

TOUCH_PAD_PWREN#

NGFF_WIFI_3.3_PWREN

WWAN_PWREN

MSATA_SSD_PWREN

SATA1_PWREN

1

1

PCIECLKREQ3#

PCH_GPIO33

PCIECLKREQ5#

SATA_LED#

9/24 Modify part conn

Boot BIOS LocationPCH_GPIO86

SPI

2

RC12810K_0402_5%

RC12810K_0402_5%

1

2

RPC11

RPC11

4

5

3

6

2

7

1

8

10K_0804_8P4R_5%

10K_0804_8P4R_5%

RC214

RC214

1

2

@

@

10/01

100K_0402_5%

100K_0402_5%

RPC12

RPC12

4

5

3

6

2

7

1

8

10K_0804_8P4R_5%

10K_0804_8P4R_5%

+3VS

RC36410K_0402_5%

RC36410K_0402_5%

D