Page 1

5

ZZZ1

ZZZ1

DAZ@

DAZ@

PCB

PCB

DAZXXXXXXXX

DAZXXXXXXXX

LA-B052P

D

LA-B052P

ZZZ2

ZZZ2

DA1@

DA1@

PCB

PCB

DA600143000

DA600143000

M/B LA-B052PR01

M/B LA-B052PR01

4

3

2

1

D

Compal Confidential

S1

C

S1

for WF

ZSJET_MB_FRAME 1 PC A false

ZSJET_MB_FRAME 1 PC A false

EC10G000200

EC10G000200

@

@

C

Schematics Document

ZSJET

LA-B052P

B

2013-09-25

REV:0.1

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

2013/08/20 2014/12/31

2013/08/20 2014/12/31

2013/08/20 2014/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

ZSJET LA-B052P

ZSJET LA-B052P

ZSJET LA-B052P

1

of

1 28Wednesday, September 25, 2013

of

1 28Wednesday, September 25, 2013

of

1 28Wednesday, September 25, 2013

B

A

0.1

0.1

0.1

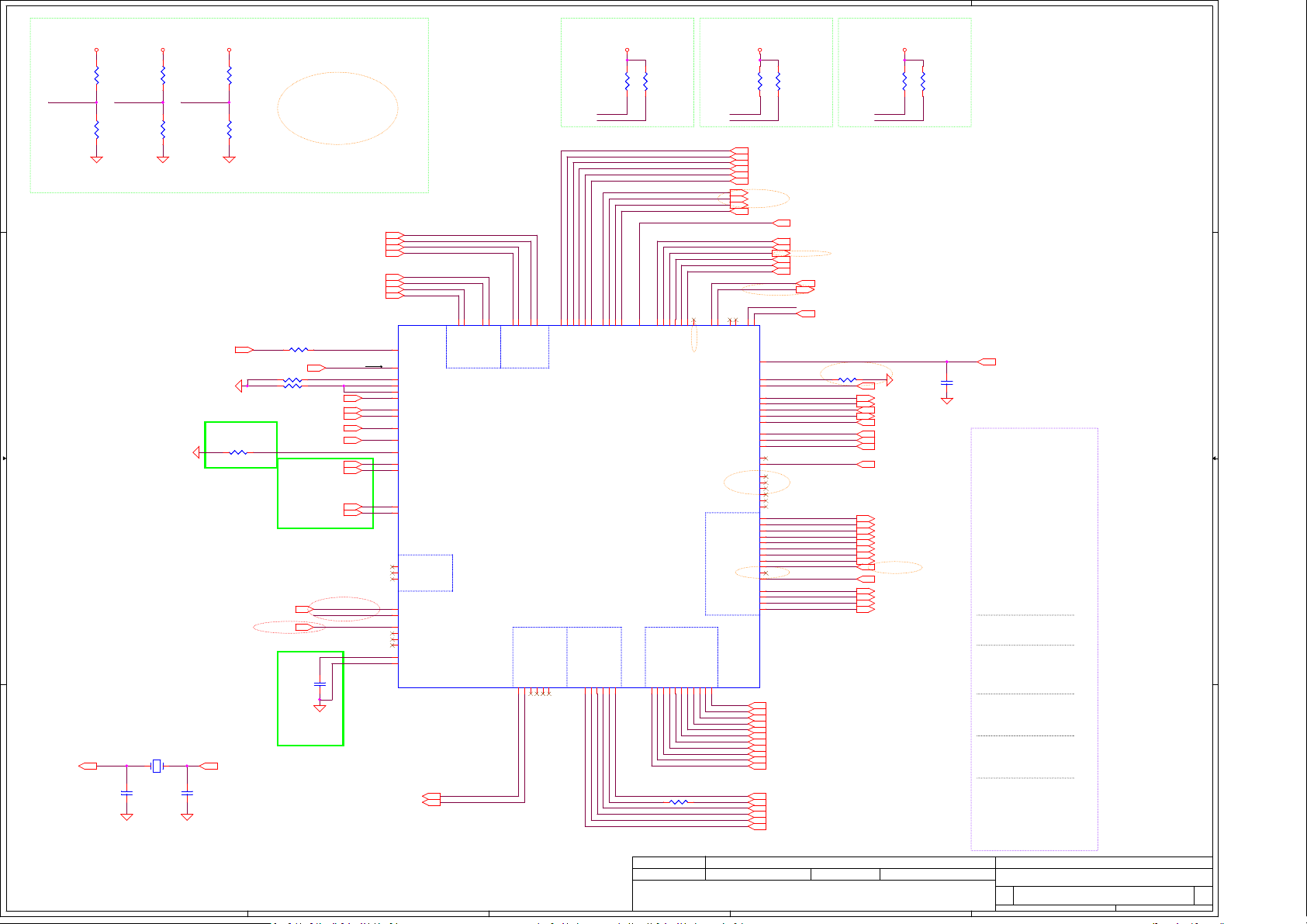

Page 2

5

4

3

2

1

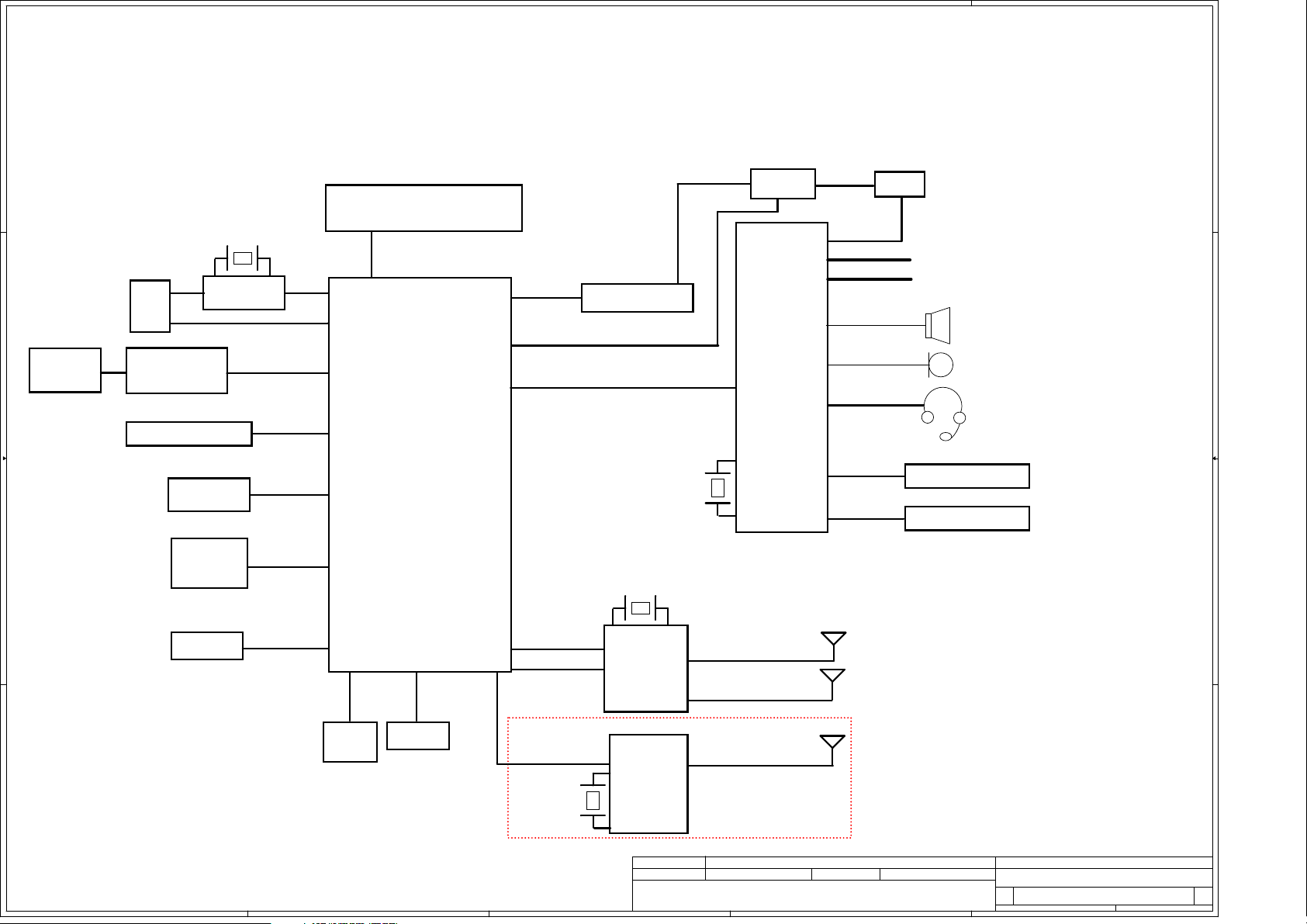

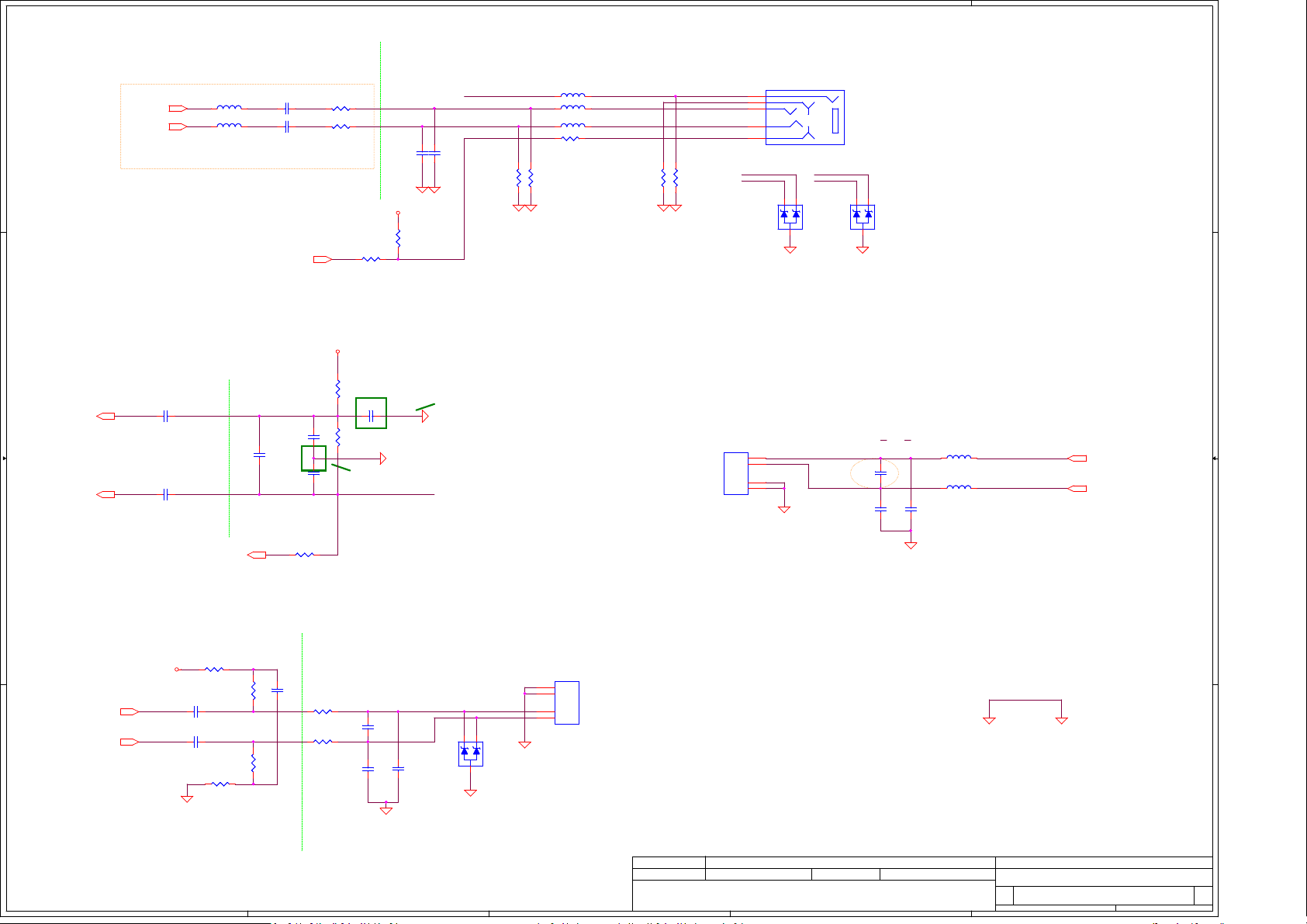

giordano3 block diagram

D

C

B

Capacitive

Touch Panel

CONN.

P15

LVDS

LCM

CONN.

P8

Touch Sensor IC

Goodix GT927

MT8193

P15

Sidekey (volume up)

Front Camera

G Sensor

Kionix_KXTIK-1004

26MHz

P16

P11

P13

P8

I2C,EINT

KCOL

YUV,I2C

I2C,EINT

Max. support VR AM size : 2GB.

DDR3L 1GB (512M X 8bits *2 Pcs)

External Memory Interface

RGB

I2C

EINT

PWM

MT8111/MT8312

Cortex-A7

1.3GHz Dual-Core

D

switching

Charger

P23 P23

I2C,EINT

P7

USB 2.0

micro USB, clie nt

I2S, SPI, EINT, I2C

P10

MT6323

PMIC

AUDIO

LDO OUTPUT

BUCK OUTPUT

CHARGER

Battery Input

LDO Output

BUCK Output

32.768KHz

P24

Speaker

MIC

combo JACK

FCHR_ENB

Battery

P9

P9

P9

Sidekey(volume down)

power key

C

P16

P16

B

26MHz

Debug Port

A

P12

www.schematic-x.blogspot.com

5

JTAG

UART0

UART1

MSDC0 MSDC1

eMMC

8G/16G

micro SD

P14

4

P10

P4,P5,P6

WB_CTRL,EINT

WB_TX,RX

GPS_TX,RX

Russian Sku

UART1, EINT

26MHz

MT6627

WIFI

BT4.0

GPS*

MT3332

P18

WIFI/BT

GPS

GPS

GLONASS

P19

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

A

Compal Electronics, Inc.

Compal Electronics, Inc.

2014/12/312013/08/20

2014/12/312013/08/20

2014/12/312013/08/20

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Block Diagram

Block Diagram

Block Diagram

ZSJET LA-B052P

ZSJET LA-B052P

ZSJET LA-B052P

1

0.1

0.1

2 28Wednesday, September 25, 2013

2 28Wednesday, September 25, 2013

2 28Wednesday, September 25, 2013

0.1

of

of

of

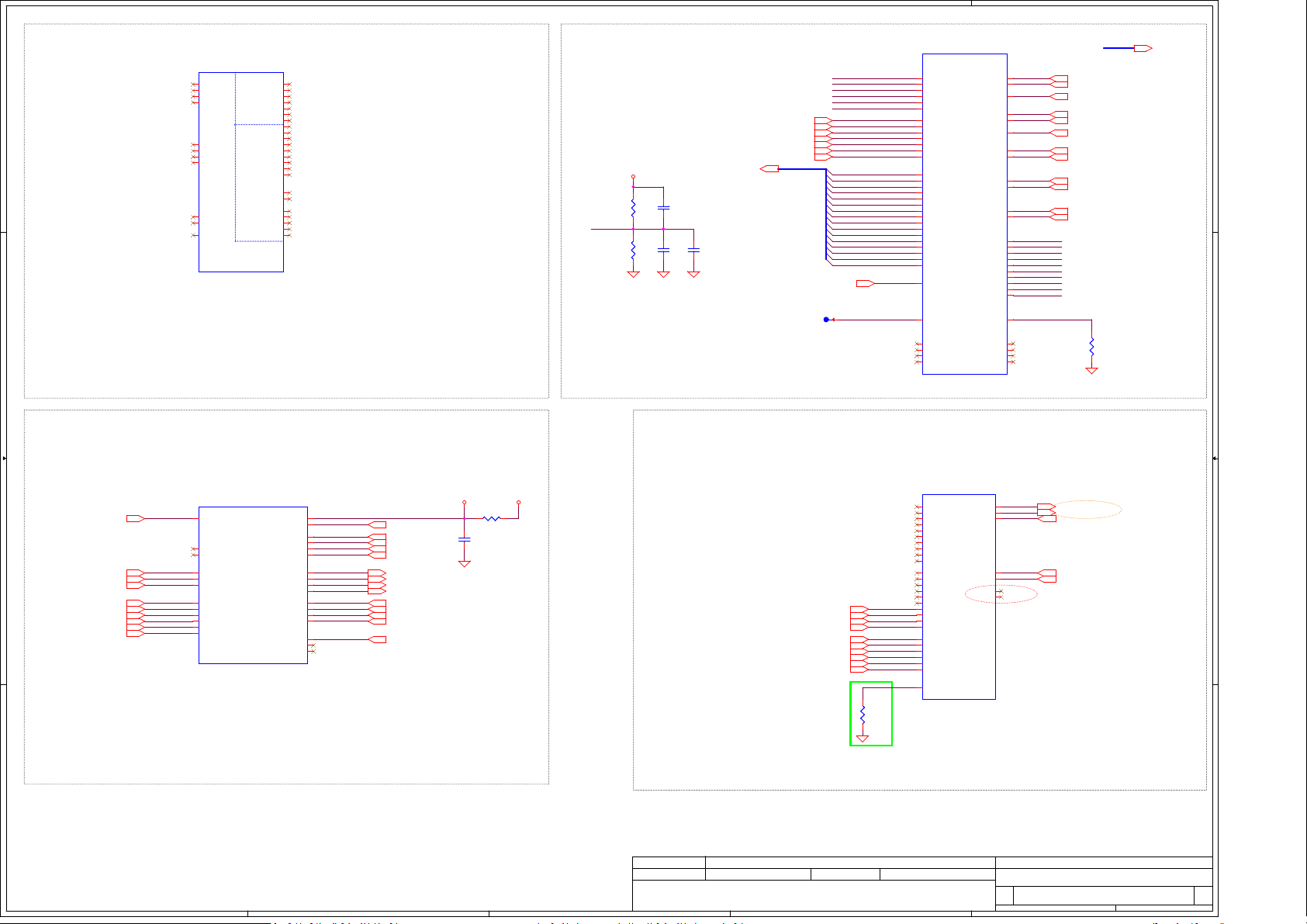

Page 3

5

4

3

2

1

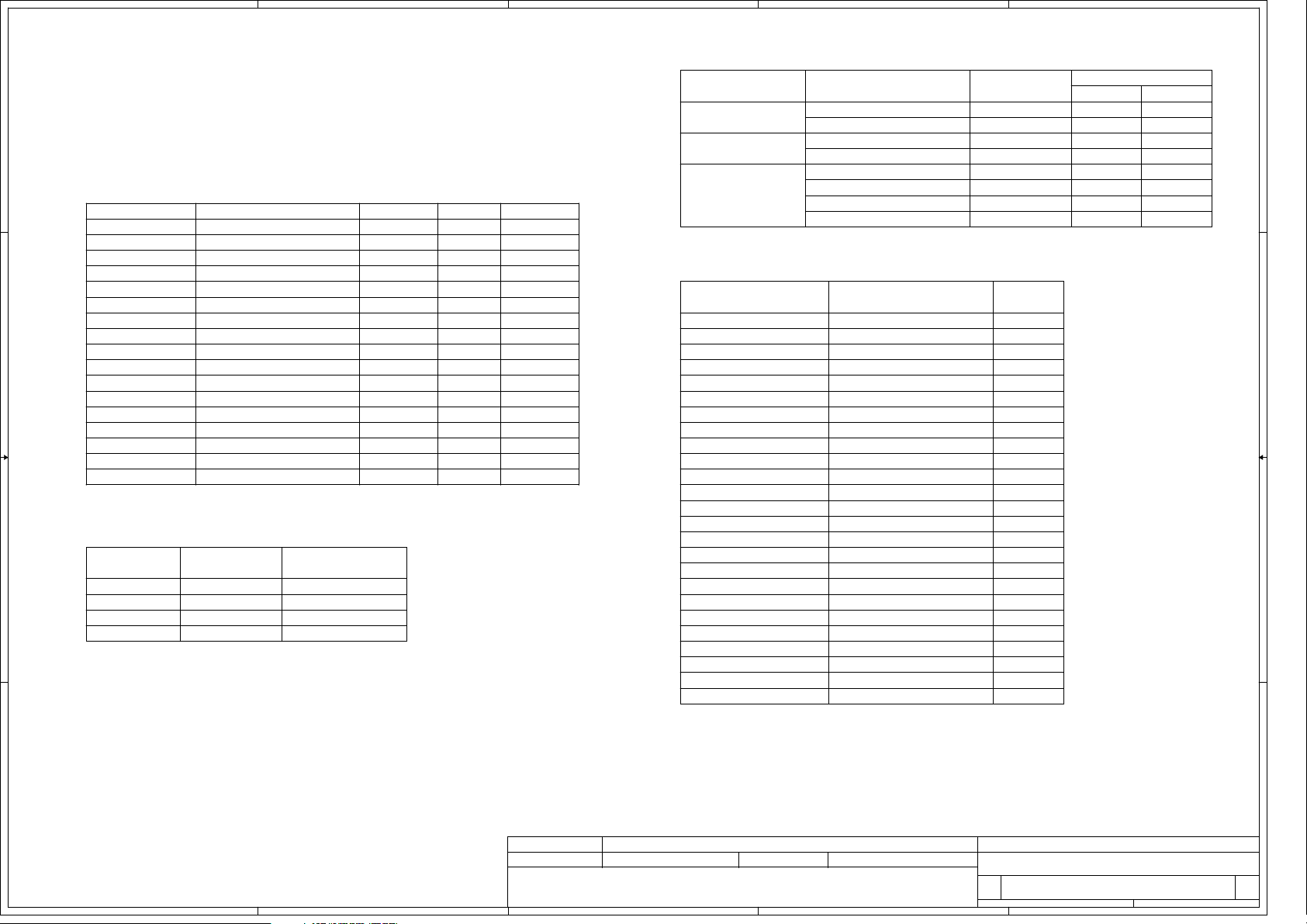

I2C address

I2C

D

I2C0

I2C1

Device

Touch screen (GT927)

Charge (BQ24196 )

G-sensor (KXTIK-1004)

Voltage Rails

MT6323 Power Plane

VPROC_PMU

VSYS_PMU Power supply input of VSYSLDO

VA_PMU

VTCXO_PMU

VCAMA_PMU

VM_PMU

VIO18_PMU

C

VIO28_PMU

VCAMD_IO_PMU

VEMC_3V3_PMU

VMCH_PMU LDO output for micro SD card 3.3V ON Gating by SW

VUSB_PMU LDO output for SOC 3.3V ON Gating by SW

VGP1_PMU LDO output for LCM 3.3V ON Gating by SW

VGP2_PMU LDO output for Touch IC 2.8V ON Gating by SW

VCN28_PMU LDO output for MT6627 2.8V

VCN33_PMU LDO output for MT6627 3.3V

VCN18_PMU LDO output for MT6627,SOC 1.8V

Function Power Level

VPROC switching output for SOC

LDO output for MT6323(audio)

LDO output for TCXO

LDO output for camera

LDO output for SOC(DDR3L)

LDO output for eMMC,G-sensor 1.8V

LDO output for G-sensor,SOC

LDO output for camera

LDO output for eMMC

0.7~ 1.4V ON

2.2V

2.8V

2.8V

2.8V

1.35V

2.8V

1.8V

3.3V

Main board ID

B

MB_ID0

0

0

1

1 1

MB_ID1

0

1

0

EVT

DVT

PVT

MP

IDLE Sleep mode

Low voltage

ON

ON

ON

ON

ON

ON

ON

ON

ON

Gating by SW

Gating by SW

OFF

Gating by SW

Gating by SW

Gating by SW

Gating by SW

Gating by SW

Gating by SW

BOM structure

TBD

I2C2

G-sensor (KXTJ2-1009)

G-sensor (STK8BA50)

Name

Function

EMC@ EMC/ESD/RF request

XEMC@ Reserve for EMC/ESD

XEMC@ Reserve for RF

For G SensorX76@

KIONIX@

G-sensor for Kionix

STK@ G-sensor for Sensortek

CONN@ Connector

ME@

DAZ@

NAN 256Mx16@

HYN 256Mx16@

HYN 8GB@

HYN 16GB@

KIN 8GB@

KIN 16GB@

SAM 8GB@

SAM 16GB@

CLIP

PCB

NANYA 256M(DDR3L)

HYNIX 256M(DDR3L)

HYNIX 8G(EMMC)

HYNIX 16G(EMMC)

Kinggston 8G(EMMC)

Kinggston 16G(EMMC)

Samsung 8G(EMMC)

Samsung 16G(EMMC)

Address(7 bit)

0x5D

0x1DLCD to LVDS (MT8193)

0x6A

0x0F

0x0E

0x18

Address(8bit)

Write

0xBA

Read

0xBB

0x3A 0x3B

0x420x21 0x43Camera (OV7675)

0xD50xD4

0x1E

0x1F

0x44 0x450x22G-sensor(STK8313)

0x1C

0x30

0x1D

0x31

D

C

B

A

Security Classif ication

Security Classif ication

Security Classif ication

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

2014/12/312013/08/20

2014/12/312013/08/20

2014/12/312013/08/20

2

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Notes List

Notes List

Notes List

ZSJET LA-B052P

ZSJET LA-B052P

ZSJET LA-B052P

3 28Wednesd ay, September 25, 20 13

of

3 28Wednesd ay, September 25, 20 13

of

3 28Wednesd ay, September 25, 20 13

1

of

A

0.1

0.1

0.1

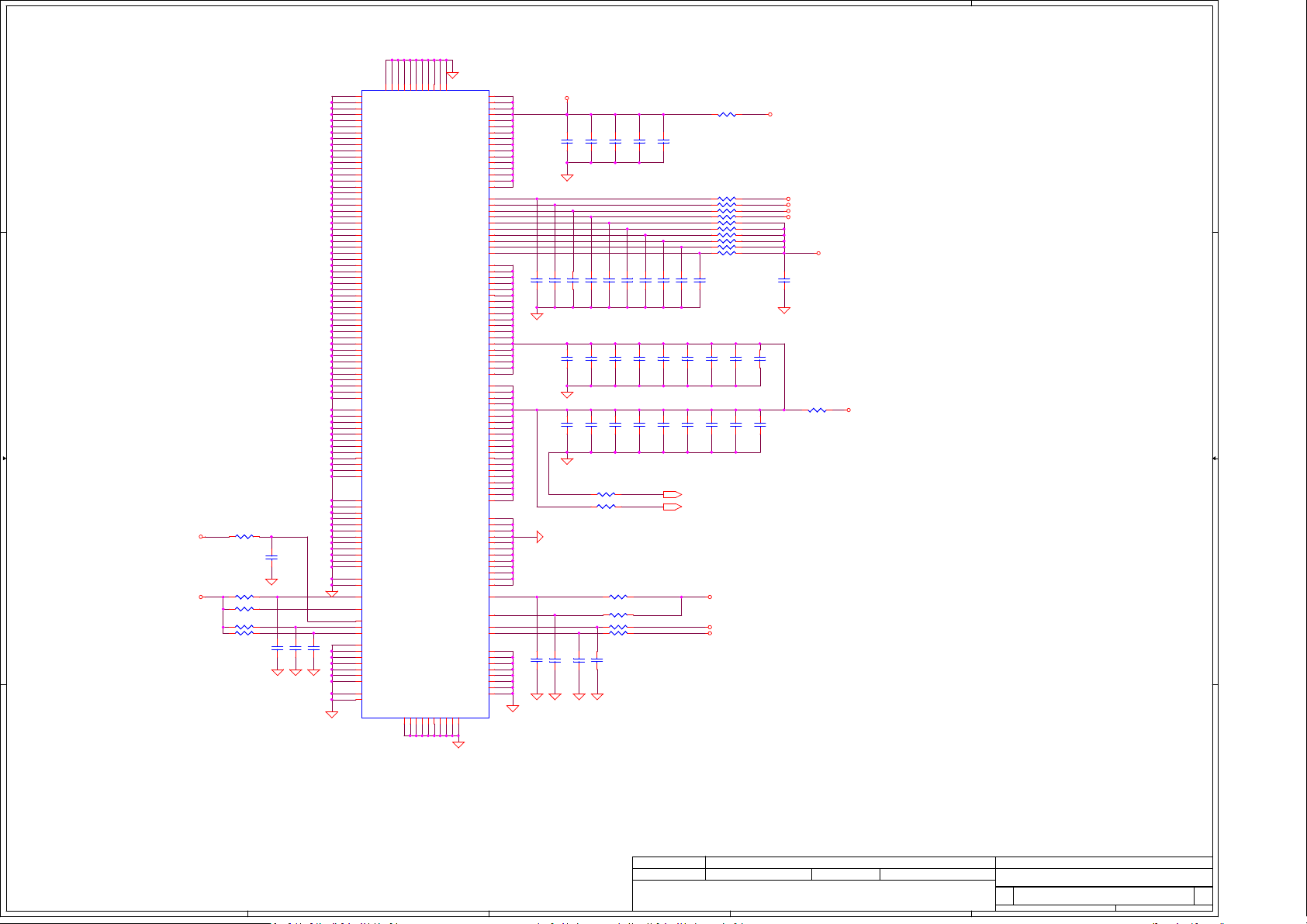

Page 4

1

D

C

B

VIO18_PMU

R12

R12

0_0805_5%

0_0805_5%

2

1

VPROC_PMU

3

1.35V for DDR3L

1.5V for DDR3

C3

C3

C2

C2

C1

C1

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1

1

2

2

C8

C8

C9

C9

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

1

1

2

2

1

1

C17

C17

C18

C18

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

2

1

1

C26

C26

C27

C27

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

2

1

R13 0_0402_5%

R13 0_0402_5%

1

R14 0_0402_5%

R14 0_0402_5%

(1)VPROC_BB, GND pin of 1st cap group should be laid differential

pair with ground shielding remote sense to PMIC

(2)R13 & R14 must be close to 1st cap group.

If you want to remove them,

please make sure the VPROC_FB/GND_VPROC_FB must connect from 1st cap. group of VPROC

1

C41

C41

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

2

C11

C11

C10

C10

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

1

1

2

2

1

C19

C19

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

1

C28

C28

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

2

2

2

1

R17 0_0402_5%

R17 0_0402_5%

2

1

R19 0_0402_5%

R19 0_0402_5%

2

1

R21 0_0402_5%

R21 0_0402_5%

2

1

R23 0_0402_5%

R23 0_0402_5%

1

C42

C42

1U_0402_10V6K

1U_0402_10V6K

2

C4

C4

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

2

C12

C12

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

2

1

C20

C20

0.1U_0402_10V7K

0.1U_0402_10V7K

2

1

C29

C29

0.1U_0402_10V7K

0.1U_0402_10V7K

2

C5

C5

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

2

C13

C13

C14

C14

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

1

2

2

1

1

C21

C21

0.1U_0402_10V7K

0.1U_0402_10V7K

2

2

1

1

C30

C30

0.1U_0402_10V7K

0.1U_0402_10V7K

2

2

GND_VPROC_FB (24)

VPROC_FB (24)

C15

C15

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

2

C22

C22

1U_0402_10V6K

1U_0402_10V6K

C31

C31

1U_0402_10V6K

1U_0402_10V6K

2

R1 0_0603_5%

R1 0_0603_5%

1

1

1

1

1

1

1

1

1

1

1

2

1

2

1

2

R2 0_0402_5%

R2 0_0402_5%

2

R3 0_0402_5%

R3 0_0402_5%

2

R4 0_0402_5%

R4 0_0402_5%

2

R5 0_0402_5%

R5 0_0402_5%

2

R6 0_0402_5%

R6 0_0402_5%

2

R7 0_0402_5%

R7 0_0402_5%

2

R8 0_0402_5%

R8 0_0402_5%

2

R9 0_0402_5%

R9 0_0402_5%

2

R10 0_0402_5%

R10 0_0402_5%

2

R11 0_0402_5%

R11 0_0402_5%

1

1

C24

C24

C23

C23

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

2

2

1

1

C32

C32

C33

C33

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

2

2

VIO18_PMU

VUSB_PMU

VIO18_PMU

VM_PMU

VMC_PMU

VIO28_PMU

VIO18_PMU

VIO18_PMU

C16

C16

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

@

@

2

C25

C25

@

@

10U_0805_25V6K

10U_0805_25V6K

2

C34

C34

10U_0805_25V6K

10U_0805_25V6K

0.1U_0402_10V7K

0.1U_0402_10V7K

4

T13

U1B

U1B

T11

DVSS

R11

DVSS

R2

DVSS

G6

DVSS

G7

DVSS

G14

DVSS

G17

DVSS

G20

DVSS

H10

DVSS

M20

DVSS

N11

DVSS

A19

DVSS

A26

DVSS

B4

DVSS

B10

DVSS

E21

DVSS

F6

DVSS

B12

DVSS

B14

DVSS

B17

DVSS

B22

DVSS

B24

DVSS

C4

DVSS

C8

DVSS

C11

DVSS

C12

DVSS

C16

DVSS

C17

DVSS

C18

DVSS

C20

DVSS

C21

DVSS

C22

DVSS

C23

DVSS

C25

DVSS

D4

DVSS

D5

DVSS

D7

DVSS

D9

DVSS

D11

DVSS

D13

DVSS

D15

DVSS

D17

DVSS

D21

DVSS

D24

DVSS

E5

DVSS

E8

DVSS

E10

DVSS

E18

DVSS

F18

DVSS

P21

DVSS

L10

DVSS

AE5

AVSS18_WBG

V7

AVSS18_WBG

U7

AVSS18_WBG

W7

AVSS18_WBG

Y7

AVSS18_WBG

AB6

AVSS18_WBG

AB8

AVSS18_WBG

AC3

AVSS18_WBG

AC5

AVSS18_WBG

AC7

AVSS18_WBG

AD4

AVSS18_WBG

AE3

AVSS18_WBG

W20

AVSS18_MD

U20

AVSS18_MD

V20

AVSS18_MD

V21

AVSS18_MD

U21

AVSS18_MD

W21

AVSS18_MD

Y20

AVSS18_MD

Y21

AVSS18_MD

AA21

AVSS18_MD

AB21

AVSS18_MD

U17

AVSS18_AP

U18

AVSS18_AP

A2

AVSS18_MEMPLL

R24

AVSS33_USB

AE21

AVDD18_MD

AE19

AVDD18_AP

AE22

AVDD28_DAC

AE18

DVDD18_PLLGP

A3

AVDD18_MEMPLL

AC21

AVSS18_MD

AD22

AVSS18_MD

AG26

AVSS18_MD

V17

AVSS18_AP

V18

AVSS18_AP

AA18

AVSS18_AP

AB19

AVSS18_AP

AF3

AVSS18_WBG

AG1

AVSS18_WBG

MT8111V-CA-1.3G_FCCSP475

MT8111V-CA-1.3G_FCCSP475

T16

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVDD28_MSDC1

DVDD28_MSDC2

DVDD18_MSDC0

DVDD18_MIPITX

DVDD18_MIPIIO

DVSS18_MIPIIO

DVSS18_MIPIIO

DVSS18_MIPIIO

DVSS18_MIPIIO

DVSS18_MIPITX

DVSS18_MIPITX

DVSS18_MIPITX

DVSS18_MIPITX

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

J21

T12

K21

H17

H20

H12

M17

M16

DVDD12_EMI

DVDD12_EMI

DVSS

DVDD12_EMI

DVDD12_EMI

DVDD12_EMI

DVDD12_EMI

DVDD12_EMI

DVDD12_EMI

DVDD12_EMI

DVDD12_EMI

DVDD12_EMI

DVDD12_EMI

DVDD12_EMI

DVDD12_EMI

DVDD12_EMI

DVDD12_EMI

DVDD28_BPI

DVDD28_MD

DVDD18_IO0

DVDD18_IO1

DVDD18_IO2

DVDD18_IO3

DVDD18_IO4

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

VCCK_VPROC

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

AVDD33_USB

AVDD18_USB

DVSS

DVSS

DVSS

V14

H14

H18

H16

H15

G9

G11

G13

G15

G16

G18

H8

E7

F7

F8

G8

H11

H13

E1

V1

AD26

U25

G26

L26

Y26

D1

W1

AG13

R10

P9

L11

L12

L13

L14

L15

L16

L17

M10

M18

N10

N18

P18

R9

R18

T10

U10

V10

N12

N13

N14

N15

N16

N17

P14

R15

P15

R14

R13

R12

R16

R17

T14

T15

U15

U16

V15

V16

M15

N21

P10

P11

P12

P13

P16

P17

L18

M14

M13

M12

L2

G1

T24

P26

H4

H5

J5

J7

L4

M7

M8

N3

DDR3VCCIO

C6

C6

1

2

DVDD

1

C39

C39

2

DDR3VCCIO

1U_0402_10V6K

1U_0402_10V6K

1

2

1

0.1U_0402_10V7K

0.1U_0402_10V7K

2

C7

C7

C40

C40

V13

V12

V11

U12

U11

M11

T21

T18

T17

5

D

C

AVSS18_MD and AVSS18_AP

via directly to GND layer

R15 0_0402_5%

R15 0_0402_5%

2

VTCXO_PMU

B

VIO18_PMU

AVDD18_MEMPLL pin and AVSS18_MEMPLL pin should

be connected with PCB CAP first, and then connected

with PMU and PCB ground. CAP should be near MT6582

as possible as we can.

1

C35

C35

0.1U_0402_10V7K

0.1U_0402_10V7K

1

R16

R16

0_0402_5%

0_0402_5%

1

R18

R18

0_0402_5%

0_0402_5%

1

R20 0_0402_5%

R20 0_0402_5%

1

R22 0_0402_5%

R22 0_0402_5%

1

2

2

2

2

2

1

1

1

C38

C38

C37

C37

C36

C36

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

2

2

2

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

5

4

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

2014/12/312013/08/20

2014/12/312013/08/20

2014/12/312013/08/20

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

MT8111 - Power

MT8111 - Power

MT8111 - Power

ZSJET LA-B052P

ZSJET LA-B052P

ZSJET LA-B052P

1

4 28Wednesday, September 25, 2013

of

4 28Wednesday, September 25, 2013

of

4 28Wednesday, September 25, 2013

of

A

0.1

0.1

0.1

Page 5

D

C

B

A

MB_ID0

Reserve

32K_OUT(24)

18P_0201_50V8J

18P_0201_50V8J

5

VIO18_PMU

2

R24

R24

@

@

100K_0201_5%

100K_0201_5%

1

MB_ID1

2

R35

R35

100K_0201_5%

100K_0201_5%

1

32.768KHZ_12.5P_1TJF125DP1A000D

32.768KHZ_12.5P_1TJF125DP1A000D

1

C45

C45

2

5

4

3

2

1

I2C1: CHARGER, CAMERA I2C0: CTP, MT8193I2C2: SENSOR

4.7K_0201_5%

4.7K_0201_5%

for 3G USE

AC13

AB13

KPCOL0

KPROW0

PWRAP_SPI0_CSN

PWRAP_SPI0_CK

PWRAP_SPI0_MI

PWRAP_SPI0_MO

PWRAP_INT

AUD_CLK_MOSI

AUD_DAT_MISO

AUD_DAT_MOSI

MSDC0_RSTB

MSDC0_CMD

MSDC0_CLK

E24

D26

G25

VIO18_PMU

R31

R31

SCL1

SDA1

SCL0 (15,8)

SDA0 (15,8)

SCL1 (11,23)

SDA1 (11,23)

SCL2 (13)

SDA2 (13)

MT3332_EN (19)

GPIO_FRAME_SYNC (19)

GNSS_HRST (19)

GPIO_SUB_CMPDN (11)

AA13

Y13

AE13

AD13

KPCOL2

KPCOL1

KPROW2

KPROW1

SYSRSTB

SRCLKENAI

SRCLKENA

GPIO12

GPIO13

SIM1_SCLK

SIM1_SIO

SIM1_SRST

SIM2_SCLK

SIM2_SIO

SIM2_SRST

EINT0

EINT1

EINT2

EINT3

EINT4

EINT5

EINT6

EINT7

EINT8

EINT9

EINT10

PCM_CLK

PCM_RX

PCM_SYNC

PCM_TX

1

1

R32

R32

4.7K_0201_5%

4.7K_0201_5%

2

2

EINT_G (13)

EINT_MC1INSI (10)

EINT_HP (9)

MT8389_EINT_MT3332 (19)

USB_ID (10)

EINT_MT8193 (8)

GPIO_CHG_EN (23)

MB_ID0

MB_ID1

M25

M24

N25

J23

H23

J24

H22

H24

K26

K25

J25

AG10

AF9

L21

K23

L23

L20

L24

K24

W22

V22

AA24

V24

W25

Y25

AA23

AA26

AA25

Y23

Y22

V23

V26

V25

U24

eMMC_RST (14)

eMMC_CMD (14)

eMMC_CLK (14)

eMMC_DAT0 (14)

eMMC_DAT1 (14)

eMMC_DAT2 (14)

eMMC_DAT3 (14)

eMMC_DAT4 (14)

eMMC_DAT5 (14)

eMMC_DAT6 (14)

eMMC_DAT7 (14)

MC1CM (10)

MC1CK (10)

MC1DA0 (10)

MC1DA1 (10)

MC1DA2 (10)

MC1DA3 (10)

KCOL0 (16)

MB_ID0 (10)

GPIO93_DRVVBUS (23)

MT6605 OSC_EN (SRCLKENAI) Need to default low

for MT6605 TESTMODE boot-strap

Need check with MTK 9/2

R242 10K_0402_5%

R242 10K_0402_5%

1

SRCLKENAI

for 3G USE

for 3G USE follow G3_3G 9/9

eMMC

SD

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4.7K_0201_5%

4.7K_0201_5%

2

2

R33

R33

SCL0

SDA0

SRCLKENA (24,8)

PMIC_SPI_CS (24)

PMIC_SPI_SCK (24)

PMIC_SPI_MISO (24)

PMIC_SPI_MOSI (24)

EINT_PMIC (24)

AUD_CLK (24)

AUD_DAT_MISO (24)

AUD_DAT_MOSI (24)

GPIO_CTP_RST (15)

DPI_D4 (8)

DPI_D5 (8)

DPI_D6 (8)

DPI_D7 (8)

DPI_D8 (8)

DPI_D9 (8)

DPI_D10 (8)

DPI_D11 (8)

EINT_SWCHR (23)

EINT_CTP (15)

DPI_D0 (8)

DPI_D2 (8)

DPI_D1 (8)

DPI_D3 (8)

VIO18_PMU

1

2

LCD

2014/12/312013/08/20

2014/12/312013/08/20

2014/12/312013/08/20

1

2

R34

R34

4.7K_0201_5%

4.7K_0201_5%

1

@

@

C43

C43

0.1U_0402_10V7K

0.1U_0402_10V7K

2

EINT0 : DPI_D4

EINT1 : DPI_D5

EINT2 : DPI_D6

EINT3 : DPI_D7

EINT4 : DPI_D8

EINT5 : DPI_D9

EINT6 : DPI_D10

EINT7 : DPI_D11

EINT8 : EINT_SWCHR

EINT9 : N/A

EINT10 : EINT_CTP

EINT11 : EINT_G

EINT14 : EINT_MC1INSI

EINT15 : EINT_HP

EINT16 : MT8389_EINT_MT3332

EINT17 : USB_ID

EINT18 : EINT_MT8193

EINT19 : GPIO_CHG_EN

EINT20 : N/A

GPIO12 : N/A

GPIO13 : GPIO_CTP_RST

UART0: Debug

UART1: Debug & MT3332

UART2: GPIO (LCD)

UART3: GPIO (LCD)

MSDC0 : eMMC

MSDC1 : SD Card

MSDC2 : GPIO (LCD)

I2C0 : CTP / MT8193

I2C1 : Camera / Charger

I2C2 : G Sensor

KPCOL0 : KCOL0 (VOL UP)

KPROW0 : MB_ID0

KPCOL1 : LCM_VLED_EN

KPROW1 : LCM_BL_EN

KPCOL2 : MB_ID1

KPROW2 : GPIO93_DRVVBUS

SYSRST_B (12,16,24,8)

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

MT8111_Baseband-1

MT8111_Baseband-1

MT8111_Baseband-1

ZSJET LA-B052P

ZSJET LA-B052P

ZSJET LA-B052P

1

5 28Wednesday, September 25, 2013

of

5 28Wednesday, September 25, 2013

of

5 28Wednesday, September 25, 2013

of

D

C

B

A

0.1

0.1

0.1

MB_ID2

MT8193_CLKBUF_1(8)

1

C46

C46

18P_0201_50V8J

18P_0201_50V8J

2

VIO18_PMU

2

R26

R26

@

@

100K_0201_5%

100K_0201_5%

1

2

R37

R37

@

@

100K_0201_5%

100K_0201_5%

1

Close to PIN

R44

R44

2

5.1K_0201_1%

5.1K_0201_1%

32K_IN (24)

DEL 9/2

2

1

R41 0_0402_5%

R41 0_0402_5%

RTC32K_CK(24,8)

2

R43 0_0402_5%

R43 0_0402_5%

R42 0_0402_5%

R42 0_0402_5%

1

1

2

1

WATCHDOG_B(24)

MCU_JTCK(12)

MCU_JTDO(12)

MCU_JTDI(12)

MCU_JTMS(12)

USB_VRT

USB_DP(10)

USB_DM(10)

90 Ohm

differential

CHD_DP(24)

CHD_DM(24)

Need check with MTK 8/29

Add MB_ID2 9/6

BAT_ID(23)

CHG_TEMP(23)

1U_0402_10V6K

1U_0402_10V6K

MB_ID2

1

C44

C44

2

C44 Close to MT8382

AF19 should connect to C44.2 first,

than connect to GND by via

DPI_CK(8)

DPI_DE(8)

DPI_HSYNC(8)

DPI_VSYNC(8)

URXD1(12,19)

UTXD1(12,19)

URXD0(12)

UTXD0(12)

CLK26M

TESTMODE

FSOURCE_P

REFP

AF26

L25

AF11

N26

AF12

AE12

AG11

AF13

P25

R26

R25

N23

N24

W5

AC19

AD19

AF18

AG17

AF17

AG16

AG19

AF19

LCM_RST_2V8(8)

LCM_STBY_2V8(8)

4

DPI_CK

DPI_DE

DPI_HSYNC

DPI_VSYNC

URXD1

UTXD1

URXD0

UTXD0

U1C

U1C

CLK26M

RTC32K_CK

TESTMODE

R5

FSOURCE_P

R4

DVDD18_EFUSE

WATCHDOG

JTCK

JTDO

JTDI

JTMS

USB_VRT

USB_DP

USB_DM

CHD_DP

CHD_DM

V5

I2S_BCK

U5

I2S_LRCK

I2S_DATA_IN

AUX_IN0

AUX_IN1

AUX_XP

AUX_XM

AUX_YP

AUX_YM

REFP

AVSS_REFN

MT8111V-CA-1.3G_FCCSP475

MT8111V-CA-1.3G_FCCSP475

2.8V GPIO

DVDD18_IO3

DVDD18_IO3

DVDD18_IO3

DVDD18_IO3

VIO18_PMU

1

1

R29

R29

R30

4.7K_0201_5%

4.7K_0201_5%

SCL2

SDA2

AA1

AA2

AE7

AD8

P22

V2

W2

Y2

UTXD0

P23

U2

UTXD2

UTXD1

URXD1

URXD0

DVDD28_MD

DVDD28_MD

T2

AB3

AC9

AC8

AA3

R23

T23

SCL2

SCL1

SCL0

SDA2

SDA1

SDA0

UTXD3

URXD2

URXD3

MSDC2_CMD

MSDC2_CLK

MSDC2_DAT0

MSDC2_DAT1

MSDC2_DAT2

MSDC2_DAT3

T3

T6

T5

T1

R7

SPI_CS

DVDD28_MSDC1DVDD28_MSDC2

DVDD28_MSDC1DVDD28_MSDC2

MSDC1_DAT0

MSDC1_DAT1

MSDC1_DAT2

MSDC1_DAT3

E4

C3

D2

C2

D3

R30

4.7K_0201_5%

4.7K_0201_5%

2

2

AE9

AD10

AC11

AE10

AG8

AF8

AF10

AD7

AB9

SPI_MI

EINT11

SPI_CK

SPI_MO

MSDC1_CMD

MSDC1_CLK

E3

MC1CK_R

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

3

EINT17

EINT16

EINT15

EINT14

DVDD18_MSDC0

DVDD18_MSDC0

MSDC0_DAT3

MSDC0_DAT4

MSDC0_DAT5

MSDC0_DAT6

MSDC0_DAT7

F24

F22

E25

E26

E23

G24

1

RF@

RF@

R241 0_0402_5%

R241 0_0402_5%

Issued Date

Issued Date

Issued Date

AC10

EINT19

EINT18

EINT20

DVDD28_MD

DVDD28_MD

MSDC0_DAT0

MSDC0_DAT1

MSDC0_DAT2

G22

G23

2

VIO18_PMU

2

R25

R25

@

@

100K_0201_5%

100K_0201_5%

1

2

R36

R36

@

@

100K_0201_5%

100K_0201_5%

1

X1

X1

2

1

Page 6

5

4

3

2

1

U1D

DDR3L3G

U1A

U1A

AF22

UL_I_P

AF21

UL_I_N

AG20

UL_Q_P

AF20

UL_Q_N

D

AG25

DL_I_P

AG24

DL_I_N

AG22

DL_Q_P

AG23

DL_Q_N

AF25

VBIAS

AE24

APC

AE14

TXBPI

MT8111V-CA-1.3G_FCCSP475

MT8111V-CA-1.3G_FCCSP475

C

BPI_BUS0

BPI_BUS1

BPI_BUS2

BPI_BUS3

BPI_BUS4

BPI_BUS5

BPI_BUS6

BPI_BUS7

BPI_BUS8

DVDD28_BPI

DVDD28_BPI

BPI_BUS9

BPI_BUS10

BPI_BUS11

BPI_BUS12

BPI_BUS13

BPI_BUS14

BPI_BUS15

VM0

VM1

BSI_EN

BSI_CLK

BSI_DATA0

DVDD18_IO4

DVDD18_IO4

BSI_DATA1

BSI_DATA2

AB24

AB23

AD25

AC24

AC23

AE25

AD24

AF16

AA17

AD16

AC16

AF15

AC17

AB17

AC15

Y15

AG14

AF14

AD14

Y14

AB14

AA14

AC14

8.06K_0201_1%

8.06K_0201_1%

EVREF

8.06K_0201_1%

8.06K_0201_1%

DDR3VCCIO

R45

R45

R46

R46

EBA0(7)

EBA1(7)

EBA2(7)

ECAS_B(7)

ERAS_B(7)

EWR_B(7)

ERESET_B(7)

ED[0..15](7)

1

1

C47

C47

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

2

1

1

1

C48

C48

C49

C49

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1U_0402_10V6K

1U_0402_10V6K

2

2

2

EA10

EA11

EA12

EA13

EA14

EA15

ED15

ED14

ED13

ED12

ED11

ED10

ED9

ED8

ED7

ED6

ED5

ED4

ED3

ED2

ED1

ED0

EVREF(7)

TP4PAD@

TP4PAD@

TP_MEMPLL

U1D

A14

RA10

A11

RA11

B11

RA12

A5

RA13

C10

RA14

A13

RA15

D8

RBA0

B13

RBA1

B16

RBA2

C15

RCAS_B

C14

RRAS_B

D14

RWR_B

C6

RRESET_B

B26

RDQ15

B25

RDQ14

C26

RDQ13

A25

RDQ12

D25

RDQ11

B23

RDQ10

C24

RDQ9

A23

RDQ8

A20

RDQ7

D20

RDQ6

B19

RDQ5

C19

RDQ4

B20

RDQ3

D22

RDQ2

B21

RDQ1

A22

RDQ0

F16

VREF

A1

TP_MEMPLL

B18

NC

A17

NC

D16

NC

D10

NC

MT8111V-CA-1.3G_FCCSP475

MT8111V-CA-1.3G_FCCSP475

RCS0_B

RCS1_B

RCKE

RDQM0

RDQM1

RODT0_R

RDQS0

RDQS1

RDQS0_B

RDQS1_B

RCLK0_B

RCLK0

REXTDN

B7

B6

B5

D18

D23

A16

F17

E20

E17

F20

F9

E9

A8

RA0

D12

RA1

A7

RA2

B15

RA3

A10

RA4

C7

RA5

B9

RA6

D6

RA7

B8

RA8

A4

RA9

B3

F15

NC

E15

NC

F12

NC

E12

NC

REXTDN

EA0

EA1

EA2

EA3

EA4

EA5

EA6

EA7

EA8

EA9

ECS0_B (7)

ECS1_B (7)

ECKE (7)

EDQM0 (7)

EDQM1 (7)

RODT0_R (7)

EDQS0 (7)

EDQS1 (7)

EDQS0_B (7)

EDQS1_B (7)

EDCLK_B (7)

EDCLK (7)

1

2

R47

R47

56_0402_5%

56_0402_5%

@

@

EA[0..15] (7)

D

C

WIFI/BT/GPS/RF CAMERA

U1E

U1F

WB_RSTB(18)

B

WB_SCLK(18)

WB_SDATA(18)

WB_SEN(18)

WB_CTRL0(18)

WB_CTRL1(18)

WB_CTRL2(18)

WB_CTRL3(18)

WB_CTRL4(18)

WB_CTRL5(18)

WB_RSTB

WB_CTRL0

WB_CTRL1

WB_CTRL2

WB_CTRL3

WB_CTRL4

WB_CTRL5

WB_RSTB

Y10

F2W_DATA

AA10

F2W_CLK

AG7

WB_SCLK

AF7

WB_SDATA

AE6

WB_SEN

Y6

WB_CRTL0

AA6

WB_CRTL1

AA5

WB_CRTL2

AA4

WB_CRTL3

AB5

WB_CRTL4

AB4

WB_CRTL5

MT8111V-CA-1.3G_FCCSP475

MT8111V-CA-1.3G_FCCSP475

U1F

AF6

AVDD18_WBG

XIN_WBG

GPS_RXQN

GPS_RXQP

GPS_RXIN

GPS_RXIP

WB_TXQN

WB_TXQP

WB_TXIN

WB_TXIP

WB_RXQN

WB_RXQP

WB_RXIN

WB_RXIP

ANT_SEL0

ANT_SEL1

ANT_SEL2

AE4

AD6

AF5

AG5

AG4

AF4

AF2

AG2

AF1

AE1

AE2

AD2

AC2

AC1

AB25

AC26

AC25

XO_IN

GPS_RX_QN

GPS_RX_QP

GPS_RX_IN

GPS_RX_IP

WB_TX_QN

WB_TX_QP

WB_TX_IN

WB_TX_IP

WB_RX_QN

WB_RX_QP

WB_RX_IN

WB_RX_IP

ANT_SEL0

XO_IN (18)

GPS_RX_QN (18)

GPS_RX_QP (18)

GPS_RX_IN (18)

GPS_RX_IP (18)

WB_TX_QN (18)

WB_TX_QP (18)

WB_TX_IN (18)

WB_TX_IP (18)

WB_RX_QN (18)

WB_RX_QP (18)

WB_RX_IN (18)

WB_RX_IP (18)

ANT_SEL0 (18)

AVDD18_WBG

VCN18_PMU

R48

R48

2

1

0_0402_5%

0_0402_5%

1

C50

C50

0.1U_0402_10V7K

0.1U_0402_10V7K

2

CMDAT9(11)

CMDAT8(11)

CMDAT5(11)

CMDAT4(11)

CMDAT7(11)

CMDAT6(11)

CMVREF(11)

CMHREF(11)

CMDAT3(11)

CMDAT2(11)

MIPI_VRT

1

R49

R49

1.5K_0201_1%

1.5K_0201_1%

2

U1E

M3

TCP

M4

TCN

M1

TDP0

M2

TDN0

P2

TDP1

N2

TDN1

P1

TDP2

R1

TDN2

N5

TDP3

M5

TDN3

K6

RCP

K5

RCN

L3

RDP0

K3

RDN0

K1

RDP1

K2

RDN1

J1

RDP2

J2

RDN2

G2

RDP3

H2

RDN3

F5

RCP_A

G5

RCN_A

G4

RDP0_A

G3

RDN0_A

J3

RDP1_A

H3

RDN1_A

N1

VRT

MT8111V-CA-1.3G_FCCSP475

MT8111V-CA-1.3G_FCCSP475

LCM_RST

DSI_TE

DISP_PWM

CMMCLK

CMPCLK

CMDAT0

CMDAT1

U3

Y3

AD9

B2

B1

E2

F2

Close to MT8382

LCM_VLED_EN (25)

LCM_BL_EN (25)

Need check 8/29

MTK Request 9/12

LCD_PWM (25)

CMMCLK (11)

CMPCLK (11)

B

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

5

4

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

2014/12/312013/08/20

2014/12/312013/08/20

2014/12/312013/08/20

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

MT8111_Baseband-2

MT8111_Baseband-2

MT8111_Baseband-2

ZSJET LA-B052P

ZSJET LA-B052P

ZSJET LA-B052P

1

6 28Wednesday, September 25, 2013

of

6 28Wednesday, September 25, 2013

of

6 28Wednesday, September 25, 2013

of

A

0.1

0.1

0.1

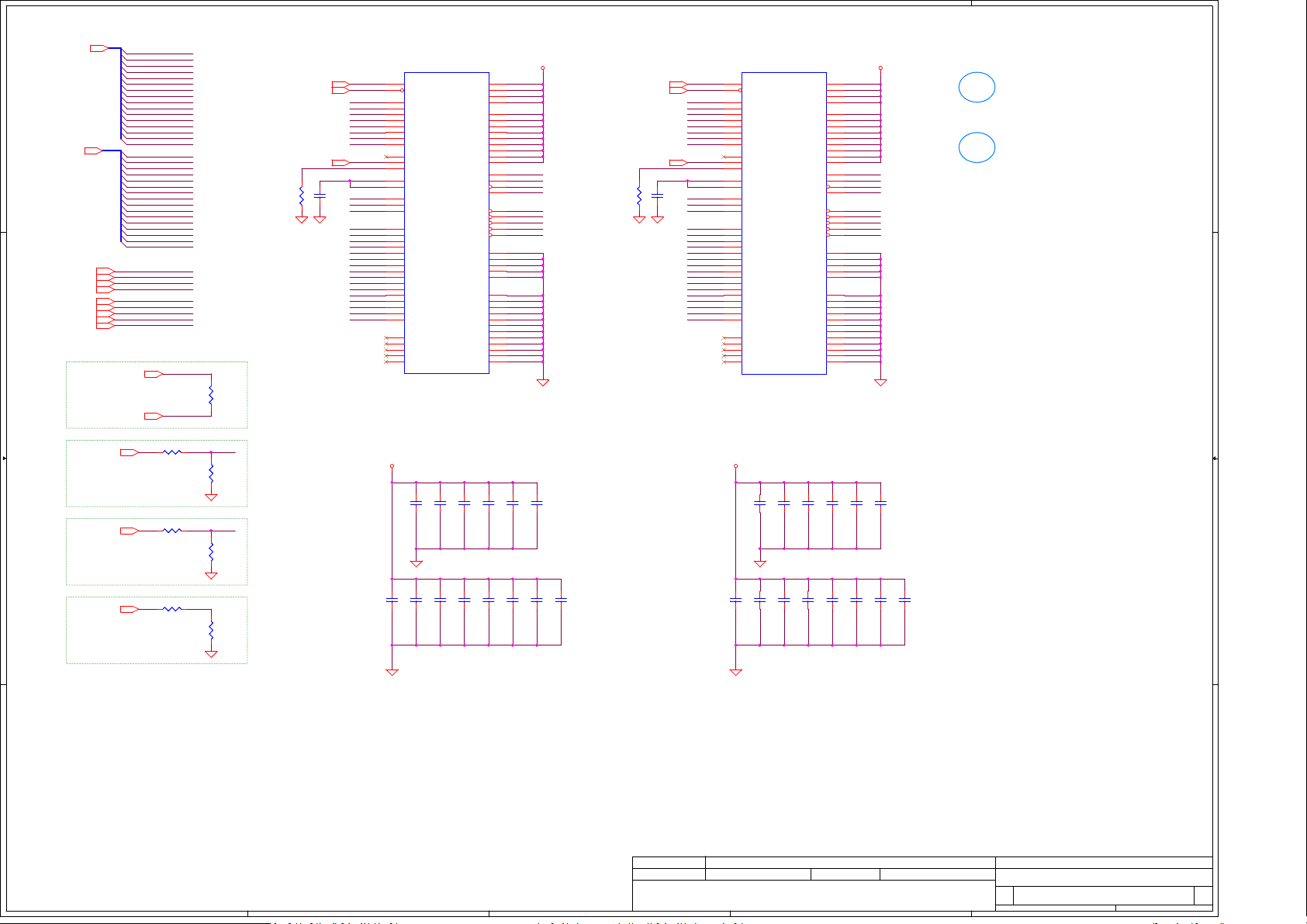

Page 7

5

4

3

2

1

ED[0..15](6)

D

EA[0..15](6)

EVREF(6)

EBA2(6)

EBA1(6)

EBA0(6)

ECKE(6)

ERAS_B(6)

ECAS_B(6)

EWR_B(6)

ERESET_B(6)

C

RODT0_R(6)

ECS0_B(6)

B

ECS1_B(6)

EDCLK(6)

EDCLK_B(6)

ED0

ED1

ED2

ED3

ED4

ED5

ED6

ED7

ED8

ED9

ED10

ED11

ED12

ED13

ED14

ED15

EA0

EA1

EA2

EA3

EA4

EA5

EA6

EA7

EA8

EA9

EA10

EA11

EA12

EA13

EA14

EA15

EVREF

EBA2

EBA1

EBA0

ECKE

ERAS_B

ECAS_B

EWR_B

ERESET_B

EDCLK

100_0402_1%

100_0402_1%

EDCLK_B

2

1

R51 0_0402_5%@

R51 0_0402_5%@

1K_0402_1%

1K_0402_1%

2

1

R55 0_0402_5%

R55 0_0402_5%

1K_0402_1%

1K_0402_1%

2

1

R57 0_0402_5%@

R57 0_0402_5%@

1K_0402_1%

1K_0402_1%

U2

X76@

U2

X76@

EDQS0(6)

EDQS0_B(6)

EDQM0(6)

1

1

C53

R54

R54

240_0402_1%

240_0402_1%

1

R50

R50

2

RODT0

1

R52

R52

2

RCS0_R

1

R56

R56

@

@

2

1

R58

R58

@

@

2

C53

0.1U_0402_10V7K

0.1U_0402_10V7K

2

2

ED0

ED1

ED2

ED3

ED4

ED5

ED6

ED7

EVREF

EBA2

EBA1

EBA0

EA0

EA1

EA2

EA3

EA4

EA5

EA6

EA7

EA8

EA9

EA10

EA11

EA12

EA13

EA14

EA15

C3

DQS

D3

DQS#

B3

DQ0

C7

DQ1

C2

DQ2

C8

DQ3

E3

DQ4

E8

DQ5

D2

DQ6

E7

DQ7

A7

NF/TDQS#

B7

DM/TDQS

H8

ZQ

E1

VREFDQ

J8

VREFCA

J3

BA2

K8

BA1

J2

BA0

K3

A0

L7

A1

L3

A2

K2

A3

L8

A4

L2

A5

M8

A6

M2

A7

N8

A8

M3

A9

H7

A10/AP

M7

A11

K7

A12/BC#

N3

A13

N7

A14

J7

A15

F1

NC

H1

NC

A3

NC

F9

NC

H9

NC

MT41K512M8RH-125-E_FBGA78

MT41K512M8RH-125-E_FBGA78

DDR3VCCIO

1

C66

C66

0.1U_0402_10V7K

0.1U_0402_10V7K

2

VDDQ

VDDQ

VDDQ

VDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

ODT

CK

CK#

CKE

CS#

RAS#

CAS#

WE#

RESET#

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

1

2

1

1

C56

C54

C54

1

C67

C67

2

C56

C55

C55

2.2U_0603_10V6K

2.2U_0603_10V6K

2.2U_0603_10V6K

0.1U_0402_10V7K

0.1U_0402_10V7K

2.2U_0603_10V6K

2.2U_0603_10V6K

2.2U_0603_10V6K

2

2

1

1

C68

C68

C69

C69

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

2

2

DDR3VCCIO

C1

E2

B9

E9

A2

A9

D7

G2

G8

K1

K9

M1

M9

G1

RODT0

F7

EDCLK

G7

EDCLK_B

G9

ECKE

H2

RCS0_R

F3

ERAS_B

G3

ECAS_B

H3

EWR_B

N2

ERESET_B

B2

B8

C9

D1

D9

A1

A8

B1

D8

F2

F8

J1

J9

L1

L9

N1

N9

1

1

2

1

C58

C58

C57

C57

1

C70

C70

2

C59

C59

2.2U_0603_10V6K

2.2U_0603_10V6K

2.2U_0603_10V6K

2.2U_0603_10V6K

0.1U_0402_10V7K

0.1U_0402_10V7K

2.2U_0603_10V6K

2.2U_0603_10V6K

2

2

1

1

C71

C71

C72

C72

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

2

2

240_0402_1%

240_0402_1%

1

C73

C73

0.1U_0402_10V7K

0.1U_0402_10V7K

2

EDQS1(6)

EDQS1_B(6)

EDQM1(6)

1

1

R53

R53

C52

C52

0.1U_0402_10V7K

0.1U_0402_10V7K

2

2

ED8

ED9

ED10

ED11

ED12

ED13

ED14

ED15

EVREF

EBA2

EBA1

EBA0

EA0

EA1

EA2

EA3

EA4

EA5

EA6

EA7

EA8

EA9

EA10

EA11

EA12

EA13

EA14

EA15

U3

X76@

U3

X76@

C3

DQS

D3

DQS#

B3

DQ0

C7

DQ1

C2

DQ2

C8

DQ3

E3

DQ4

E8

DQ5

D2

DQ6

E7

DQ7

A7

NF/TDQS#

B7

DM/TDQS

H8

ZQ

E1

VREFDQ

J8

VREFCA

J3

BA2

K8

BA1

J2

BA0

K3

A0

L7

A1

L3

A2

K2

A3

L8

A4

L2

A5

M8

A6

M2

A7

N8

A8

M3

A9

H7

A10/AP

M7

A11

K7

A12/BC#

N3

A13

N7

A14

J7

A15

F1

NC

H1

NC

A3

NC

F9

NC

H9

NC

MT41K512M8RH-125-E_FBGA78

MT41K512M8RH-125-E_FBGA78

DDR3VCCIO

1

C74

C74

0.1U_0402_10V7K

0.1U_0402_10V7K

2

VDDQ

VDDQ

VDDQ

VDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

ODT

CK#

CKE

CS#

RAS#

CAS#

WE#

RESET#

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

1

1

2

1

C61

C61

C60

C60

1

C75

C75

2

C62

C62

2.2U_0603_10V6K

2.2U_0603_10V6K

2.2U_0603_10V6K

2.2U_0603_10V6K

2

2

1

1

C77

C77

C76

C76

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

2

2

DDR3VCCIO

C1

E2

B9

E9

A2

A9

D7

G2

G8

K1

K9

M1

M9

G1

RODT0

F7

EDCLK

CK

G7

EDCLK_B

G9

ECKE

H2

RCS0_R

F3

ERAS_B

G3

ECAS_B

H3

EWR_B

N2

ERESET_B

B2

B8

C9

D1

D9

A1

A8

B1

D8

F2

F8

J1

J9

L1

L9

N1

N9

1

2.2U_0603_10V6K

2.2U_0603_10V6K

2

0.1U_0402_10V7K

0.1U_0402_10V7K

1

1

C63

C63

1

C78

C78

2

C65

C65

C64

C64

2.2U_0603_10V6K

2.2U_0603_10V6K

0.1U_0402_10V7K

0.1U_0402_10V7K

2.2U_0603_10V6K

2.2U_0603_10V6K

2.2U_0603_10V6K

2.2U_0603_10V6K

2

2

1

1

1

C79

C79

C80

C80

C81

0.1U_0402_10V7K

0.1U_0402_10V7K

2

C81

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

2

2

ZZZ8

ZZZ8

KIN 1GB@

KIN 1GB@

X76543BOL01

X76543BOL01

ALT. GROUP PARTS KINGSOTN 1G ZSJ1V

ALT. GROUP PARTS KINGSOTN 1G ZSJ1V

ZZZ9

ZZZ9

MICRON 1GB@

MICRON 1GB@

X76543BOL02

X76543BOL02

ALT. GROUP PARTS MICRON 1G ZSJ1V

ALT. GROUP PARTS MICRON 1G ZSJ1V

D

C

B

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

5

4

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

2014/12/312013/08/20

2014/12/312013/08/20

2014/12/312013/08/20

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Memory - DDR3L

Memory - DDR3L

Memory - DDR3L

ZSJET LA-B052P

ZSJET LA-B052P

ZSJET LA-B052P

1

7 28Wednesday, September 25, 2013

of

7 28Wednesday, September 25, 2013

of

7 28Wednesday, September 25, 2013

of

A

0.1

0.1

0.1

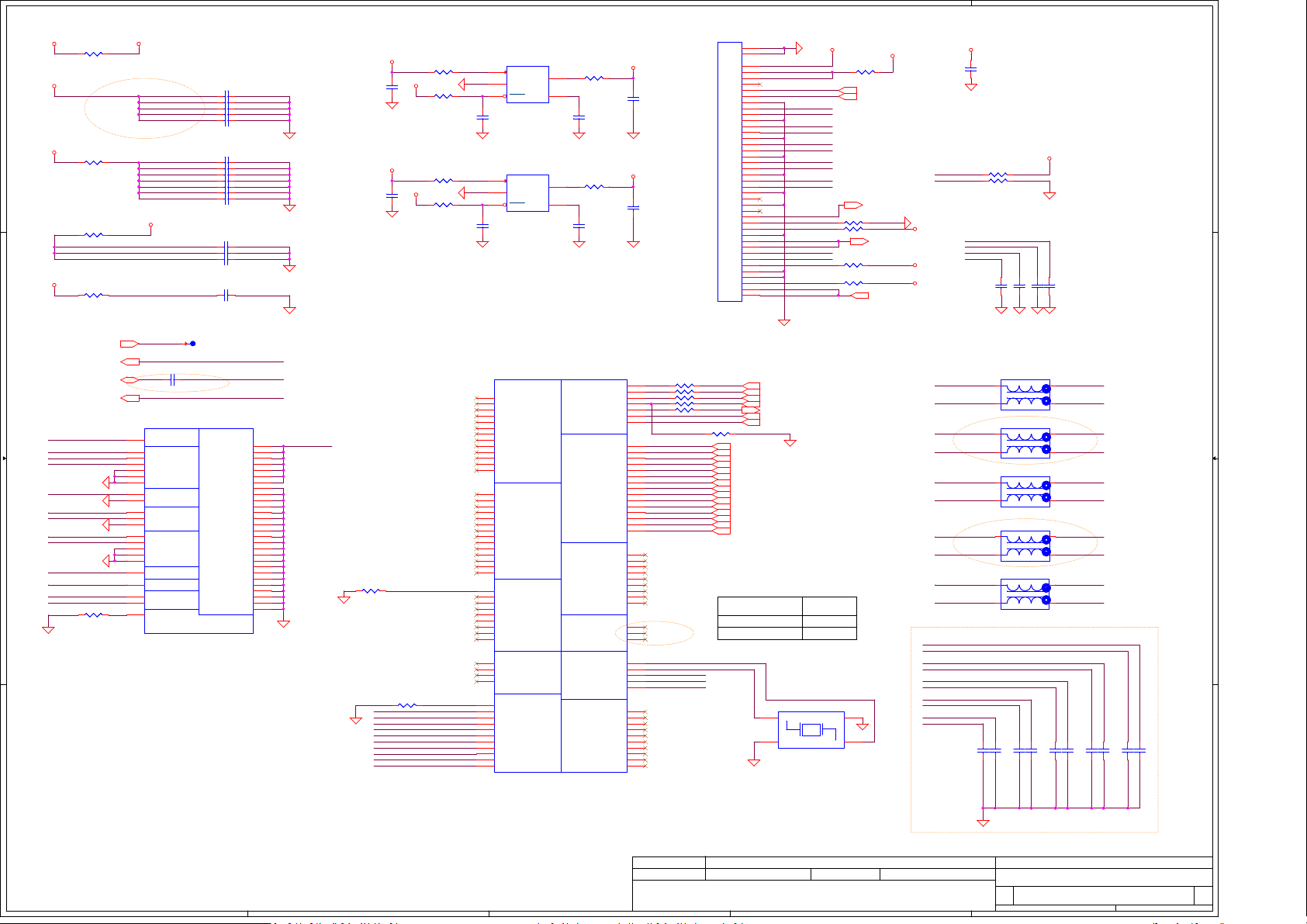

Page 8

XRF@

XRF@

C82

C82

1

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

4

1

4

1

4

1

4

1

4

1

10P_0201_50V8J

10P_0201_50V8J

2

LCM_RIN0+

LCM_RIN0-

LCM_RIN1-

LCM_RIN1+

LCM_RIN2+

LCM_RIN2-

LCM_CLKIN-

LCM_CLKIN+

LCM_RIN3+

LCM_RIN3-

Reserve for RF

C109

C109

XRF@

XRF@

1

C110

C110

10P_0201_50V8J

10P_0201_50V8J

2

1

D

C

SWAP 9/4

B

XRF@

XRF@

C113

C113

C112

C112

XRF@

XRF@

XRF@

XRF@

1

1

10P_0201_50V8JXRF@

10P_0201_50V8JXRF@

2

1

1

C111

C111

10P_0201_50V8J

10P_0201_50V8J

10P_0201_50V8J

10P_0201_50V8J

10P_0201_50V8J

10P_0201_50V8J

2

2

2

A

VCOM

2

1

1

R71 0_0402_5%

R71 0_0402_5%

1

R74 0_0402_5%

R74 0_0402_5%

OSC

Crystal

X2

X2

GND

IN

2

VGP1_PMU

2

1

R231 0_0402_5%

R231 0_0402_5%

LCM_RST_2V8 (5)

LCM_STBY_2V8 (5)

LCM_DIMO_R (25)

1

R67

R67

2

0_0402_5%

0_0402_5%

R68 0_0402_5%

R68 0_0402_5%

LCM_LEDK (25)

2

2

LCM_LEDA (25)

4

1

AVDD

VGL

VGH

CN_LCM_RIN0+

CN_LCM_RIN0-

CN_LCM_RIN1+

CN_LCM_RIN1-

CN_LCM_RIN2+

CN_LCM_RIN2-

CN_LCM_CLKIN+

CN_LCM_CLKIN-

CN_LCM_RIN3+

CN_LCM_RIN3-

VCOM

1

2

LCM_LR_SEL

LCM_UD_SEL

LCM_VDD

LCM_AVDD

LCM_VGL

LCM_VGH

CN_LCM_RIN0+

CN_LCM_RIN0-

CN_LCM_RIN1-

CN_LCM_RIN1+

CN_LCM_RIN2+

CN_LCM_RIN2-

CN_LCM_CLKIN-

CN_LCM_CLKIN+

CN_LCM_RIN3+

CN_LCM_RIN3-

C104

C104

XRF@

XRF@

C306

C306

0.1U_0402_16V4Z

0.1U_0402_16V4Z

R76 100K_0402_5%

R76 100K_0402_5%

2

1

2

1

R79 100K_0402_5%

R79 100K_0402_5%

C90

C90

C88

C88

C89

C89

1

1

1U_0402_16V6K

1U_0402_16V6K

1U 25V K X5R 0402

1U 25V K X5R 0402

1U_0402_16V6K

1U_0402_16V6K

2

2

EMC@

EMC@

2

3

OCE2012120YZF_4P

OCE2012120YZF_4P

EMC@

EMC@

2

3

OCE2012120YZF_4P

OCE2012120YZF_4P

EMC@

EMC@

2

3

OCE2012120YZF_4P

OCE2012120YZF_4P

EMC@

EMC@

2

3

OCE2012120YZF_4P

OCE2012120YZF_4P

EMC@

EMC@

2

3

OCE2012120YZF_4P

OCE2012120YZF_4P

C105

C105

XRF@

XRF@

1

1

1

C106

C106

10P_0201_50V8J

10P_0201_50V8J

10P_0201_50V8J

10P_0201_50V8J

10P_0201_50V8J

10P_0201_50V8J

10P_0201_50V8JXRF@

10P_0201_50V8JXRF@

2

2

2

LCM_VDD

1

2

XRF@

XRF@

1

C107

C107

2

L1

L1

L2

L2

L3

L3

L4

L4

L52

L52

C108

C108

2

R62 0_0603_5%

R62 0_0603_5%

1

C301

C301

@

@

3300P_0402_50V7K

3300P_0402_50V7K

2

2

R93 0_0603_5%

R93 0_0603_5%

1

C304

C304

@

@

3300P_0402_50V7K

3300P_0402_50V7K

2

RESET_N

control

control

RTC_32K_CK

DPI0

DPI0

DPI0VSYNC

DPI0HSYNC

DPI1

DPI1

I2S

I2S

I2S_LRCK

I2S_DATA

DCXO

DCXO

CLKBUF1

CLKBUF2

CLKBUF3

MT8193A-B_BGA150

MT8193A-B_BGA150

3

1

1

CK_SEL

EN_BB

DPI0D0

DPI0D1

DPI0D2

DPI0D3

DPI0D4

DPI0D5

DPI0D6

DPI0D7

DPI0D8

DPI0D9

DPI0D10

DPI0D11

DPI0CK

DPI1D0

DPI1D1

DPI1D2

DPI1D3

DPI1D4

DPI1D5

DPI1D6

DPI1D7

DPI1CK

I2S_BCK

XTALI

XTALO

VCLK

HSYNC

VSYNC

INT

SCL

SDA

G0

B5

B4

B3

B2

B1

B0

3.3V

MT8193_1V2

C8

D6

D8

D7

A7

E11

E12

A14

C13

B14

D13

B15

A15

C14

E13

E15

E14

G14

F13

H14

G13

H15

J13

J14

J15

K13

L15

L14

M14

N14

N15

M12

L13

L12

N1

N2

L4

L5

M3

L10

K11

M10

N10

L11

P11

R13

N11

P13

N12

1

C299

C299

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

C302

C302

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

R81 0_0402_5%

R81 0_0402_5%

1

R82 0_0402_5%

R82 0_0402_5%

1

R83 0_0402_5%

R83 0_0402_5%

1

R84 0_0402_5%

R84 0_0402_5%

1

R85 0_0402_5%

R85 0_0402_5%

EINT_MT8193_R

DPI_VSYNC

DPI_HSYNC

MT8193_CLKBUF_1

MT8193_CLKBUF_2

MT8193_CLKBUF_3

JP1

JP1

CONN@

CONN@

16V rating

2

2

2

2

2

1

R91 10K_0402_5%

R91 10K_0402_5%

41

GND

40

GND

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

SRCLKENA (24,5,8)

SRCLKENA (24,5,8)

SYSRST_B (12,16,24,5)

EINT_MT8193 (5)

RTC32K_CK (24,5)

SCL0 (15,5)

SDA0 (15,5)

H

L

3

2

26MHZ_7.3PF_TZ1689A

26MHZ_7.3PF_TZ1689A

VCOM

LCM_VDD

LCM_RST_2V8

LCM_STBY_2V8

CN_LCM_RIN0-

CN_LCM_RIN0+

CN_LCM_RIN1-

CN_LCM_RIN1+

CN_LCM_RIN2-

CN_LCM_RIN2+

CN_LCM_CLKIN-

CN_LCM_CLKIN+

CN_LCM_RIN3-

CN_LCM_RIN3+

LCM_DIMO_R

SELB

LCM_AVDD

LCM_LR_SEL

LCM_UD_SEL

LCM_VGL

LCM_VGH

LCM_LEDA

OUT

GND

LCM_LEDK

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

2

DPI_D0 (5)

DPI_D1 (5)

DPI_D2 (5)

DPI_D3 (5)

DPI_D4 (5)

DPI_D5 (5)

DPI_D6 (5)

DPI_D7 (5)

DPI_D8 (5)

DPI_D9 (5)

DPI_D10 (5)

DPI_D11 (5)

DPI_VSYNC (5)

DPI_HSYNC (5)

DPI_CK (5)

EINT_MT8193_R DCXO

5

VEMC_3V3_PMU

2

R59 0_0603_5%

R59 0_0603_5%

3.3V

D

VGP3_PMU

1

R75 0_0402_5%

R75 0_0402_5%

1

R63 0_0402_5%

R63 0_0402_5%

VTCXO_PMU

1

R69 0_0201_5%

R69 0_0201_5%

C

B

A

DPI_DE(5)

MT8193_CLKBUF_1(5)

MT8193_CLKBUF_2_C(18)

MT8193_CLKBUF_3(24)

3.3V

3.3V

MT8193_1V2

MT8193_1V2

MT8193_AVDD28

3.3V

MT8193_1V2

3.3V

MT8193_1V2

3.3V

MT8193_DVDDIO18

MT8193_DVDDIO18

MT8193_DVDDIO18

1

R87 0_0201_5%

R87 0_0201_5%

1

@

@

DEL R60,R61 9/6

C84 close to U8.C1 9/6

2

@

@

2

2

2

3.3V

3.3V

MT8193_1V2

VIO18_PMU

MT8193_DVDDIO18

MT8193_AVDD28

2

C99 1000P_0402_50V7K

C99 1000P_0402_50V7K

U4B

U4B

A3

DVDDIO33_18_NFI

C1

AVDD33_HDMI

K3

AVDD12_HDMI_C

L1

AVDD12_HDMI_D

F4

AVSS12_HDMI

H3

AVSS12_HDMI

K4

AVSS12_HDMI

L2

AVDD28

M4

AVSS28

P2

AVDD33_PLLGP

R1

AVDD12_VPLL

N3

AVSS12_VPLL

R10

AVDD33_LVDSA

R2

AVDD12_LVDSA

N6

AVSS12_LVDSA

M8

AVSS12_LVDSA

M7

AVSS12_LVDSA

R11

DVDDIO33_DGO

J12

DVDDIO18_33_DPI

A8

DVDDIO18_33

A13

DVDDIO18_33

N13

EFUSE

2

C83 0.1U_0402_16V4Z

C83 0.1U_0402_16V4Z

2

C85 0.1U_0402_16V4Z

C85 0.1U_0402_16V4Z

2

C86 0.1U_0402_16V4Z

C86 0.1U_0402_16V4Z

2

C87 0.1U_0402_16V4Z

C87 0.1U_0402_16V4Z

2

C84 0.1U_0402_16V4Z

C84 0.1U_0402_16V4Z

2

C96 0.1U_0402_16V4Z

C96 0.1U_0402_16V4Z

2

C97 0.1U_0402_16V4Z

C97 0.1U_0402_16V4Z

2

C98 0.1U_0402_16V4Z

C98 0.1U_0402_16V4Z

2

C100 0.1U_0402_16V4Z

C100 0.1U_0402_16V4Z

2

C101 0.1U_0402_16V4Z

C101 0.1U_0402_16V4Z

2

C102 0.1U_0402_16V4Z

C102 0.1U_0402_16V4Z

2

C103 0.1U_0402_16V4Z

C103 0.1U_0402_16V4Z

1

C92 0.1U_0402_25V4Z

C92 0.1U_0402_25V4Z

1

C93 0.1U_0402_25V4Z

C93 0.1U_0402_25V4Z

1

C94 0.1U_0402_25V4Z

C94 0.1U_0402_25V4Z

1

C95 0.1U_0402_25V4Z

C95 0.1U_0402_25V4Z

TP10PAD@

TP10PAD@

MT8193_CLKBUF_1

1

MT8193_CLKBUF_2

MT8193_CLKBUF_3

DVDD12_1

DVDD12_2

DVDD12_2

DVDD12_2

DVDD12_2

DVDD12_3

DVDD12_4

power domain

power domain

MT8193

MT8193

MT8193A-B_BGA150

MT8193A-B_BGA150

1

1

1

1

1

1

1

1

1

1

1

1

2

2

2

2

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

E4

MT8193_1V2

E7

E8

F8

G8

H10

J9

B7

G5

G6

G7

G9

G12

F5

H7

H8

H9

H11

H12

J6

J7

J8

J11

K6

K7

K8

K9

P10

4

VBAT

R92 0_0402_5%

R92 0_0402_5%

1

VIO18_PMU

C300

C300

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

R86 2.49K_0402_1%

R86 2.49K_0402_1%

1

C303

C303

VBAT

2

1

LCM_RIN0-

LCM_RIN0+

LCM_RIN1-

LCM_RIN1+

LCM_RIN2-

LCM_RIN2+

LCM_CLKIN-

LCM_CLKIN+

LCM_RIN3-

LCM_RIN3+

2

R232 20K_0402_1%

R232 20K_0402_1%

R233 0_0402_5%

R233 0_0402_5%

1

VIO18_PMU

2

R234 60.4K_0402_1%

R234 60.4K_0402_1%

@

@

2

R94 100_0201_5%

R94 100_0201_5%

1

2

1

2

1

2

1

IN

2

GND

3

SHDN

APL5320-33BI-TRG_SOT23-5

APL5320-33BI-TRG_SOT23-5

1

C91

C91

1U_0402_6.3V6K

1U_0402_6.3V6K

2

U34

U34

1

IN

2

GND

3

SHDN

APL5320-12BI-TRG_SOT23-5

APL5320-12BI-TRG_SOT23-5

1

C305

C305

0.1U_0402_25V4Z

0.1U_0402_25V4Z

2

U4A

U4A

B9

NLD0

D9

NLD1

B10

NLD2

C9

NLD3

A10

NLD4

D10

NLD5

B11

NLD6

D11

NLD7

A11

NREB

D12

NWEB

B12

NALE

C12

NCLE

B13

NRNB

B6

NFRBN

C5

NFCLE

B5

NFALE

A5

NFWEN

C4

NFREN

B3

NFCEN

A2

NFD7

B2

NFD6

A1

NFD5

B1

NFD4

C2

NFD3

D4

NFD2

C3

NFD1

D5

NFD0

D1

HDMI_EXT_RES

F2

CLK_M

F1

CLK_P

F3

CH0_M

G3

CH0_P

H1

CH1_M

H2

CH1_P

H4

CH2_M

J4

CH2_P

P15

HTPLG

R14

HDMISD

R15

HDMISCK

P14

CEC

P3

TP_VPLL

P4

AO0N

R4

AO0P

N4

AO1N

N5

AO1P

P6

AO2N

R6

AO2P

N7

AOCK0N

N8

AOCK0P

R8

AO3N

P8

AO3P

OUT

SET

OUT

SET

NFI_CPU

NFI_CPU

MT8193

MT8193

BGA-150

BGA-150

NFI_NAND

NFI_NAND

HDMI

HDMI

(analog)

(analog)

HDMI

HDMI

(digital)

(digital)

LVDS RGB

LVDS RGB

5

4

5

4

U33

U33

1

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

5

4

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

2014/12/312013/08/20

2014/12/312013/08/20

2014/12/312013/08/20

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

MT8193 - LCD

MT8193 - LCD

MT8193 - LCD

ZSJET LA-B052P

ZSJET LA-B052P

ZSJET LA-B052P

1

0.1

0.1

8 28Wednesday, September 25, 2013

8 28Wednesday, September 25, 2013

8 28Wednesday, September 25, 2013

0.1

of

of

of

Page 9

5

4

3

2

1

Earphone RECEIVER

Close to PMIC

C311

2

2

C311

22U_0805_6.3V6M

22U_0805_6.3V6M

2

2

C312

C312

22U_0805_6.3V6M

22U_0805_6.3V6M

L53

L53

FBMA-L11-160808-700LMT_2P

FBMA-L11-160808-700LMT_2P

D

AU_HPL(24)

AU_HPR(24)

1

1

L54

L54

FBMA-L11-160808-700LMT_2P

FBMA-L11-160808-700LMT_2P

R97

R97

100_0402_5%

100_0402_5%

1

2

1

2

R100

R100

100_0402_5%

100_0402_5%

Follow MTK 9/6

EINT_HP(5)

Close to connector

1

1

VIO18_PMU

1

2

2

1

R101 47K_0402_5%

R101 47K_0402_5%

1

C119

C119

33P_0402_50V8J

33P_0402_50V8J

2

R95

R95

470K_0402_5%

470K_0402_5%

Microphone: 6k~13k Ohm

2

HP_MIC

HP_MP3L

HP_MP3R

ADDJACK_DET

1

C115

C115

33P_0402_50V8J

33P_0402_50V8J

2

R245

R245

470_0402_1%

470_0402_1%

@

@

1

L8 EMC@ FBMA-L11-160808-700LMT_2P

L8 EMC@ FBMA-L11-160808-700LMT_2P

1

L5 EMC@ FBMA-L11-160808-700LMT_2P

L5 EMC@ FBMA-L11-160808-700LMT_2P

1

L7 EMC@ FBMA-L11-160808-700LMT_2P

L7 EMC@ FBMA-L11-160808-700LMT_2P

2

1

R248 0_0402_5%

R248 0_0402_5%

1

1

R244

R244

@

@

470_0402_1%

470_0402_1%

2

2

2

2

R103

R103

0_0402_5%

0_0402_5%

2

1

AUDJACK_MIC

AUDJACK_GND_R

AUDJACK_L

AUDJACK_R

ADDJACK_DET_R

2

R102

R102

@

@

0_0402_5%

0_0402_5%

1

Nomal OPEN

1

4

2

3

5

AUDJACK_R

AUDJACK_L

TVNST52302AB0 SOT523

TVNST52302AB0 SOT523

JHP1

JHP1

PROCO_879B-N004-00A0

PROCO_879B-N004-00A0

CONN@

CONN@

3

2

D2

D2

EMC@

EMC@

1

ADDJACK_DET_R

AUDJACK_MIC

3

2

1

D3

D3

EMC@

EMC@

TVNST52302AB0 SOT523

TVNST52302AB0 SOT523

D

Earphone MICPHONE

C

MICBIAS1

C

2

1K_0402_1%

Close to PMIC Close to MIC

C123

C123

2

AU_VIN1_N(24)

AU_VIN1_P(24)

B

1

0.1U_0402_10V7K

0.1U_0402_10V7K

C128

C128

2

1

0.1U_0402_10V7K

0.1U_0402_10V7K

100P_0402_50V8J

100P_0402_50V8J

AU_VIN1_N1

C125

C125

33P_0402_50V8J

33P_0402_50V8J

1

C126

C126

2

C127

C127

33P_0402_50V8J

33P_0402_50V8J

R106

R106

ACCDET(24)

2

1K_0402_1%

1K_0402_1%

1K_0402_1%

R104

R104

1

C124

C124

2

1

10U_0603_6.3V6M

10U_0603_6.3V6M

2

1

2

1

1

2

1

Close to JP2

1.5K_0402_1%

1.5K_0402_1%

R105

R105

tie together and single via to GND plane

GND of C124(10uF) and headset

should tie together and single via

to GND plane

HP_MIC

JP6

JP6

1

1

2

2

3

G1

4

G2

ACES_88266-02001

ACES_88266-02001

CONN@

CONN@

SPEAKER

SPK_N

SPK_P

Follow MTK 9/6

C310

C310

EMC@

EMC@

100P_0402_50V8J

100P_0402_50V8J

C190

C190

EMC@

EMC@

33P_0402_50V8J

33P_0402_50V8J

EMC@

EMC@

1

L13 FBMA-L11-160808-700LMT_2P

L13 FBMA-L11-160808-700LMT_2P

1

2

1

2

1