Page 1

A

B

C

D

E

COMPAL CONFIDENTIAL

MODEL NAME :

1 1

PCB NO :

BOM P/N :

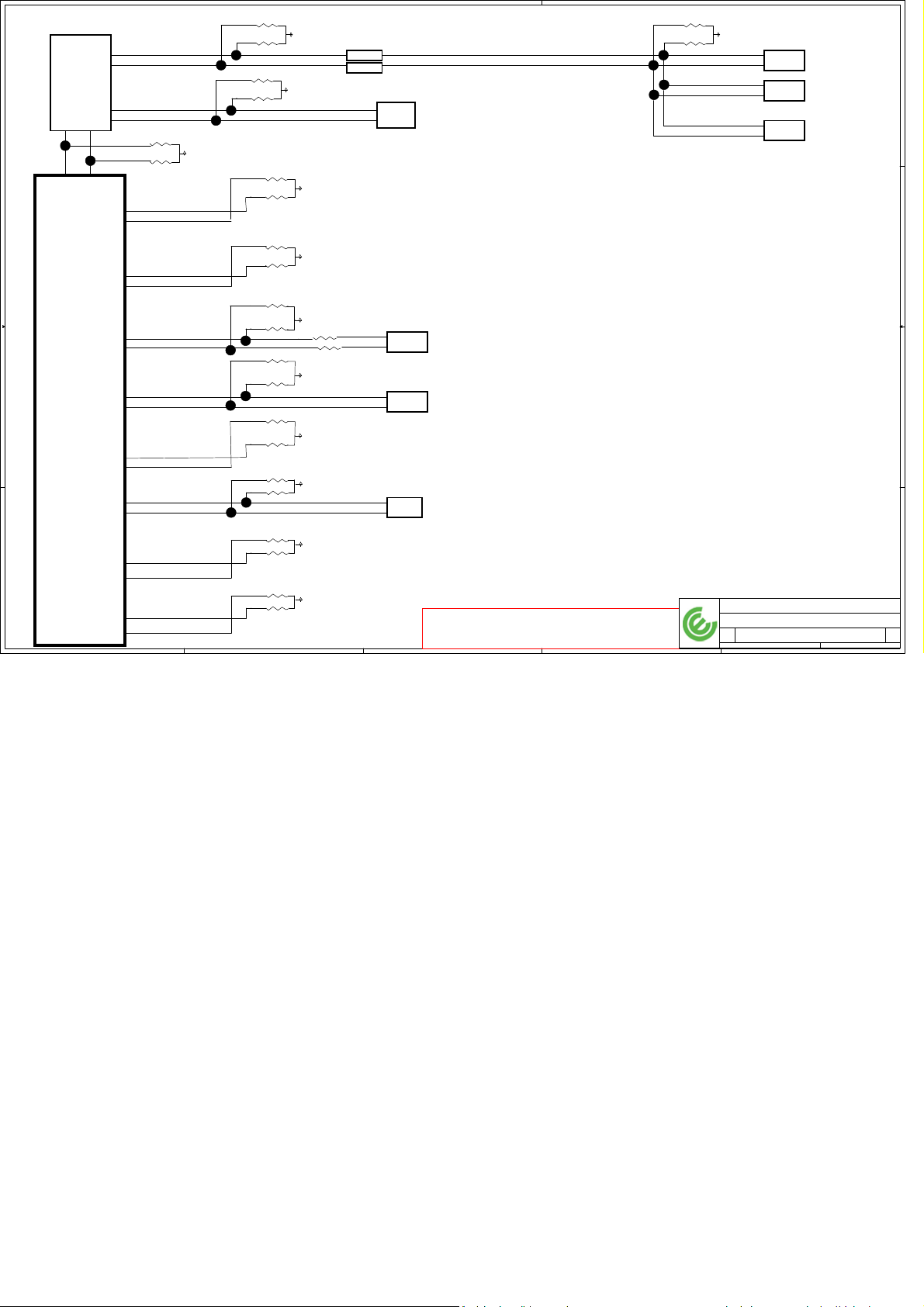

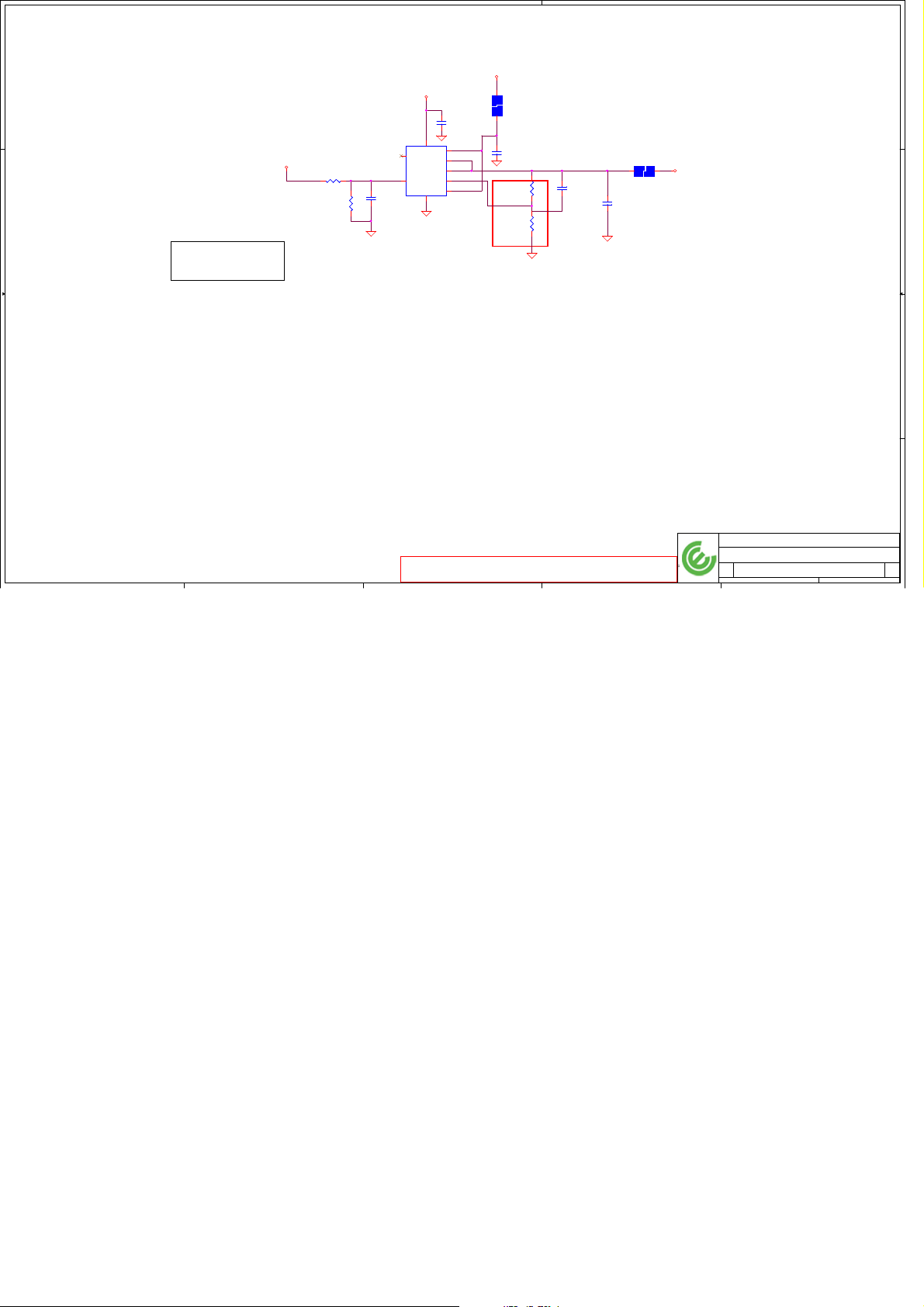

GPIO MAP: 3.3b

Goliad MLK 12 UMA

LA-A971P

4319RJ31LXX

2 2

Goliad MLK 12" UMA

Broadwell U Processor

2013-12-23

REV : 0.3 (X01)

@ : Nopop Component

EMC@ : EMI, ESD and RF Component

@EMC@ : EMI, ESD and RF Nopop Component

3 3

Layout Dell logo

COPYRIGHT 2013

ALL RIGHT RESERVED

REV: X01

PWB: 89XM3

4 4

DATE: 1351-05

MB PCB

MB PCB

Part Number

Part Number

Description

Description

PCB 14A LA-A971P REV0 MB WITH DOCKING 2

PCB 14A LA-A971P REV0 MB WITH DOCKING 2

DAA00083000

DAA00083000

A

B

CXDP@ : XDP Component

CONN@ : Connector Component

VPRO@ : Vpro Component

NVPRO@ : Non-Vpro Component

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

C

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Cover Sheet

Cover Sheet

Cover Sheet

LA-A971P

LA-A971P

LA-A971P

E

0.1

0.1

1 48Wednesday, March 19, 2014

1 48Wednesday, March 19, 2014

1 48Wednesday, March 19, 2014

0.1

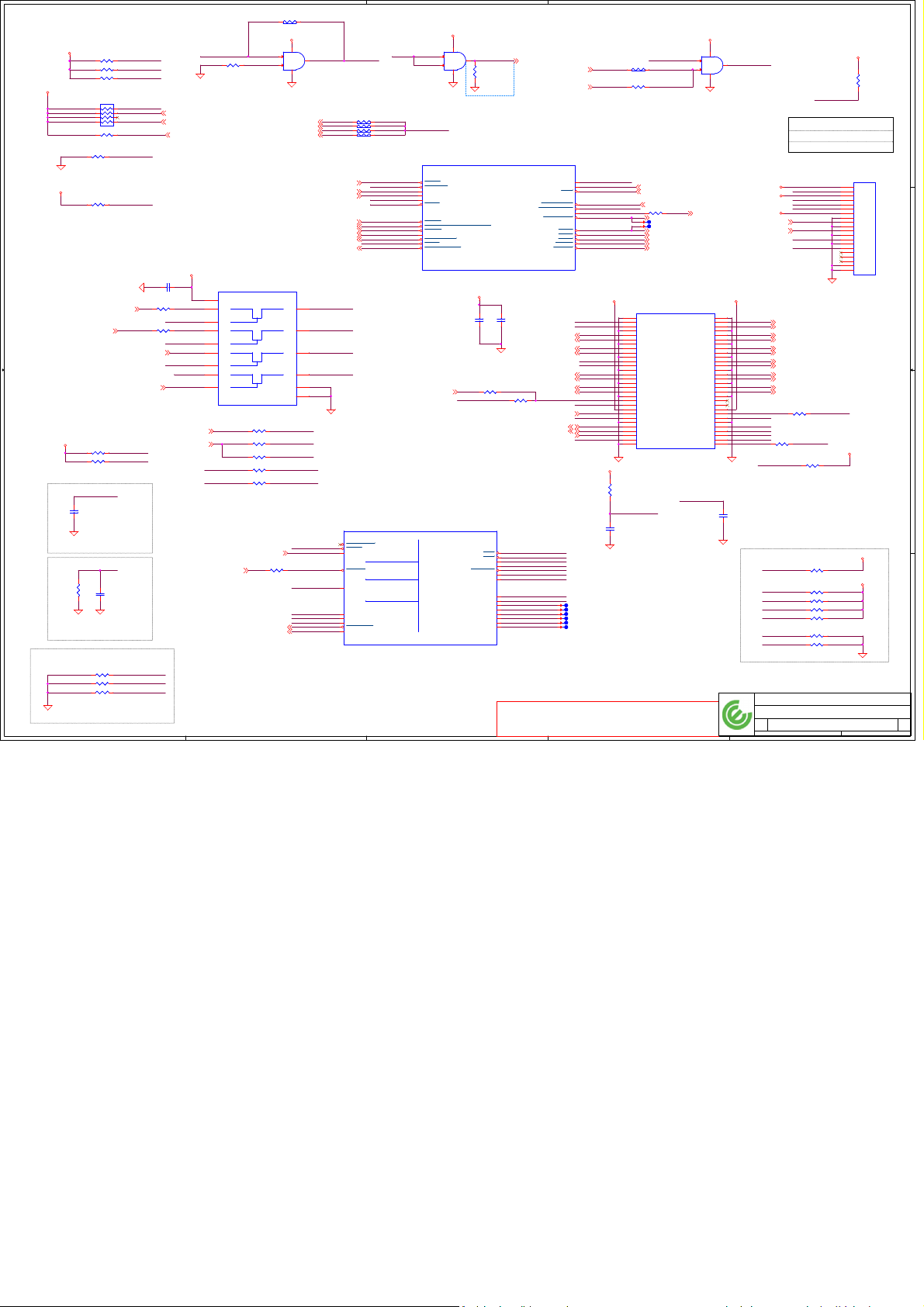

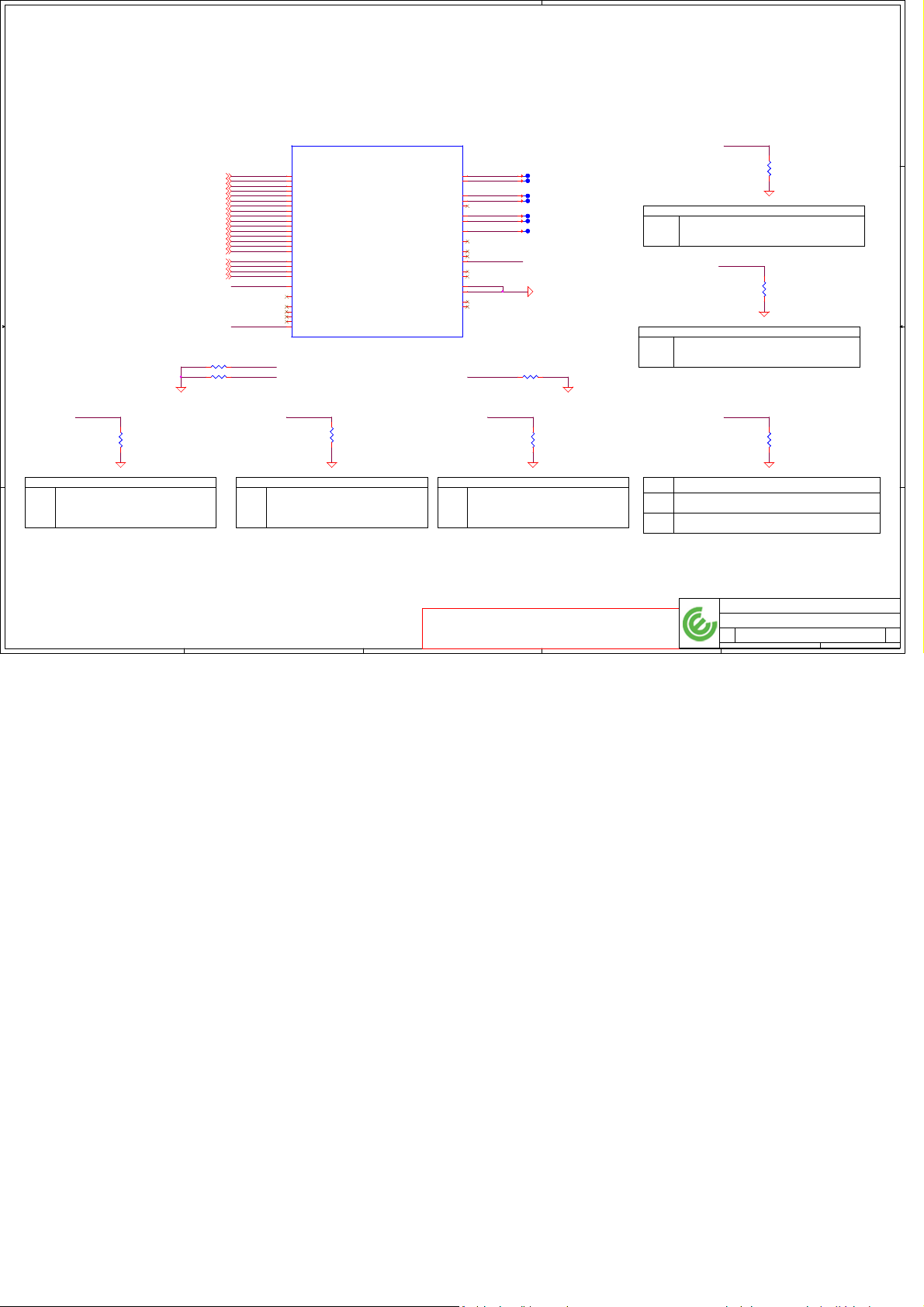

Page 2

A

B

C

D

E

Reverse Type

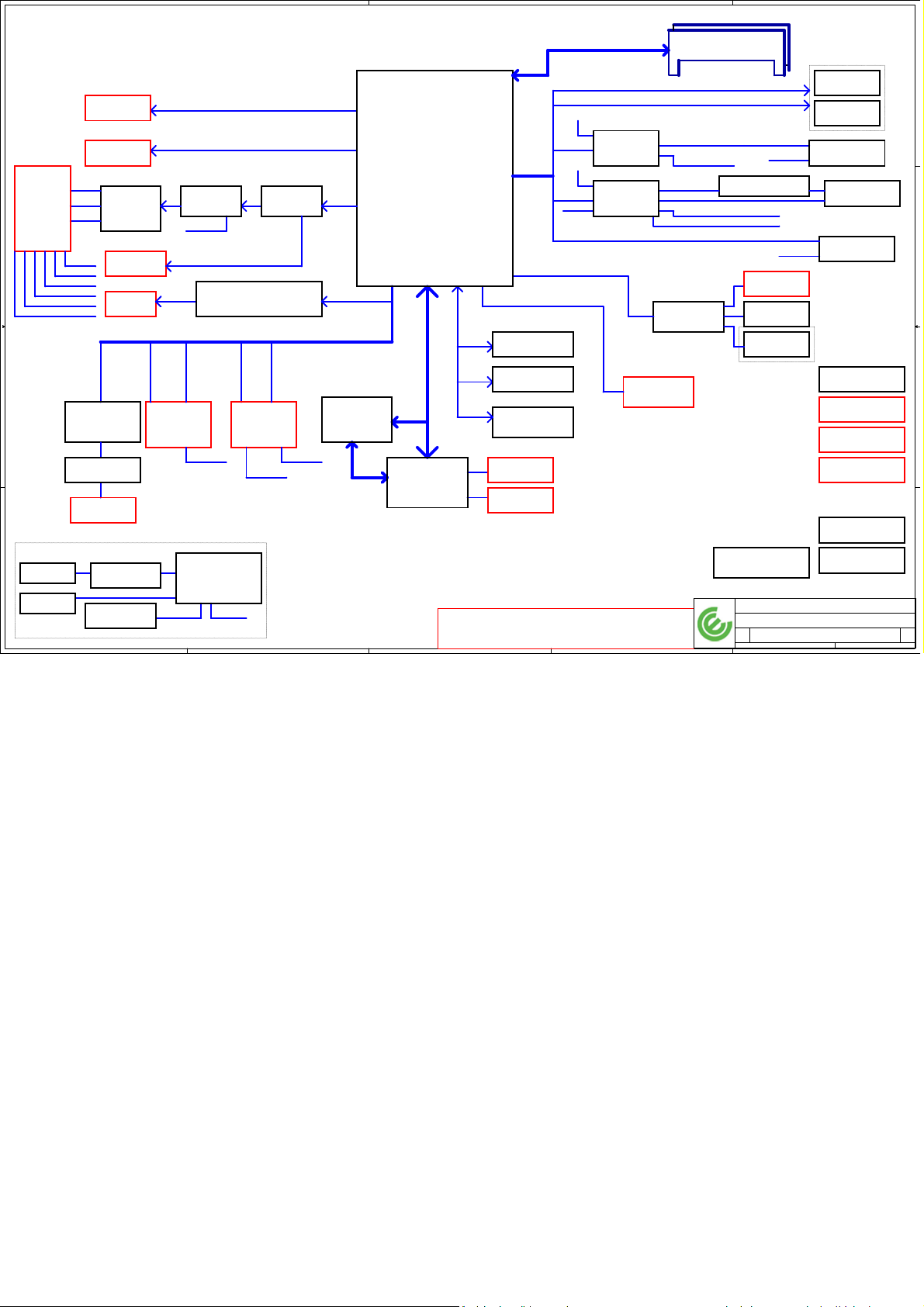

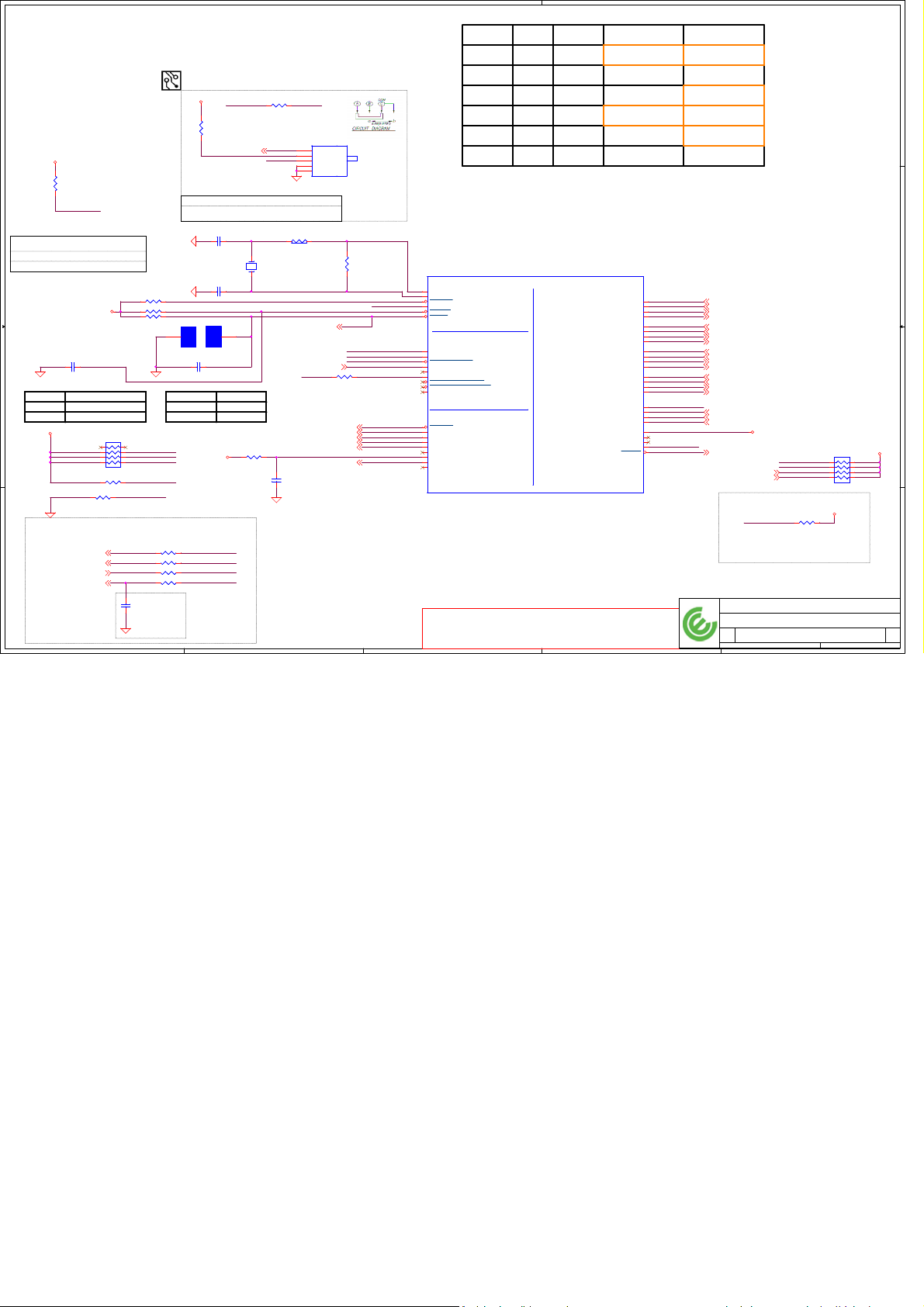

Goliad MLK 12 UMA Block Diagram

Memory BUS (DDR3L)

1 1

eDP CONN

PAGE 23

mDP CONN

PAGE 24

PAGE 34

DAI

LAN

SATA1

DOCK_USB2.0[0]

DOCK_USB2.0[5]

DOCK_USB3.0[3]

Intel Clarkville

I218LM

RFID

VGA

DP

IDT

VMM3320

DP

Transformer

PAGE 22

HDMI CONN

PAGE 24

SD4.0

PAGE 29 PAGE 29

PCIE3 PCIE4

PAGE 28

PAGE 28

RJ45

PAGE 28

TDA8034HN

Fingerprint

CONN

A

DOCKING

CONN

2 2

3 3

4 4

Smart Card

Parade

DP

PS8338

WIGIG_DP

PCIE6_L1

PCIE6_L0

WWAN/LTE

PAGE 30

USB2.0[7]

FP_USB

PAGE 27

PAGE 26

Card reader

O2 Micro OZ777FJ2LN

USH

BCM5882

USB2.0[6]

USH board

Parade

DP

PS8339

HDMI

PCI Express BUS

PCIE5_L0

WLAN/BT/

WIGIG

PAGE 30

WIGIG_DP

Dual Lane eDP1.3

DDI2

PAGE 25

USB2.0[2]

B

BROADWELL ULT

DDI1

PCIE1

SMSC SIO

ECE5048

PAGE 35

BC BUS

INTEL

USB

PAGE 6~17

SPI

LPC

SMSC KBC

MEC5085

PAGE 36

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

C

HD Audio I/F

SATA1

W25Q64CVSSIQ

64M 4K sector

W25Q32BVSSIQ

32M 4K sector

Discrete TPM

AT97SC3205

KB/TP CONN

PAGE 37

FAN CONN

PAGE 36

1333/1600MHz

DOCKED_LIO_EN

USB2.0[3]

DOCKED

USB2.0[0]

USB3.0[1]

PAGE 7

PAGE 27

NX3DV221

USB20 Switch

PAGE 31

PI3USB3102

USB3&2 Switch

PAGE 31

Full Mini Card

mSATA

HDA Codec

ALC3235

PAGE 20

D

SW_USB2.0[0]

SW_USB3.0[1]

DDR3L-DIMM X2

BANK 0, 1, 2, 3

PAGE 18 19

USB2.0[4]

USB2.0[5]

SW_USB2.0[3]

DOCK _USB2.0[3]

USB POWER SHARE

DOCK _USB2.0[0]

DOCK_USB3.0[1]

PAGE 21

USB3.0[4]

TPS2544

INT.Speaker

Universal Jack

USB2.0[1]

USB3.0[2]

PAGE 21

PAGE 21

Dig. MIC

Near Field

Communications con

PAGE 20

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Block diagram

Block diagram

Block diagram

LA-A971P

LA-A971P

LA-A971P

Trough eDP Cable

LCD Touch

PAGE 23

Camera

PAGE 23

USB3.0/2.0

PAGE 31

USB2.0[0]_PS

USB3.0/2.0+PS

USB3.0/2.0

Trough eDP Cable

LID switch

SIM+HALL/B

USH CONN

CPU XDP Port

Automatic Power

Switch (APS)

DC/DC Interface

Power On/Off

SW & LED

2 48Wednesday, March 19, 2014

2 48Wednesday, March 19, 2014

2 48Wednesday, March 19, 2014

E

PAGE 31

PAGE 32

PAGE 27

PAGE 9

PAGE 9

PAGE 38

PAGE 39

0.1

0.1

0.1

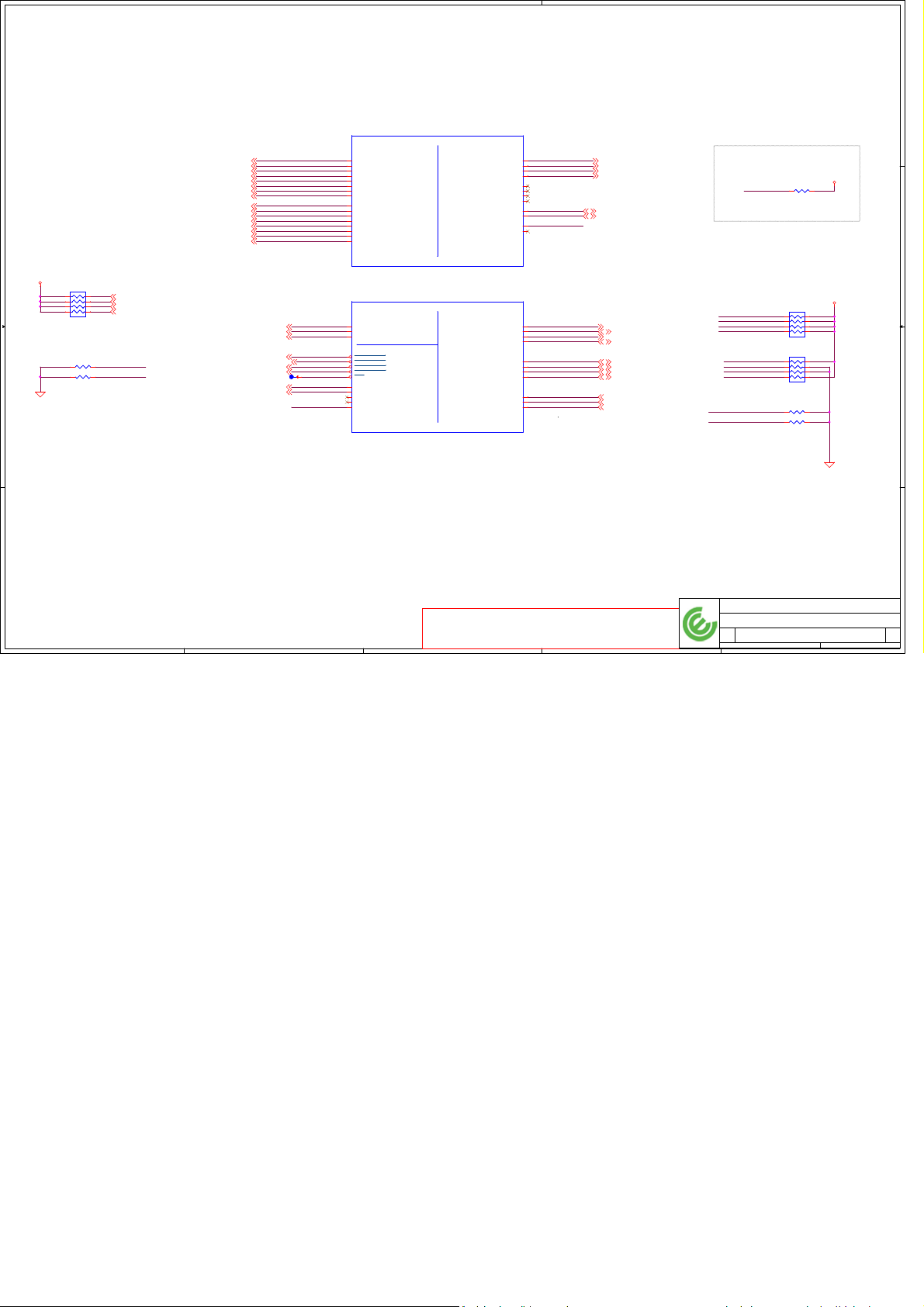

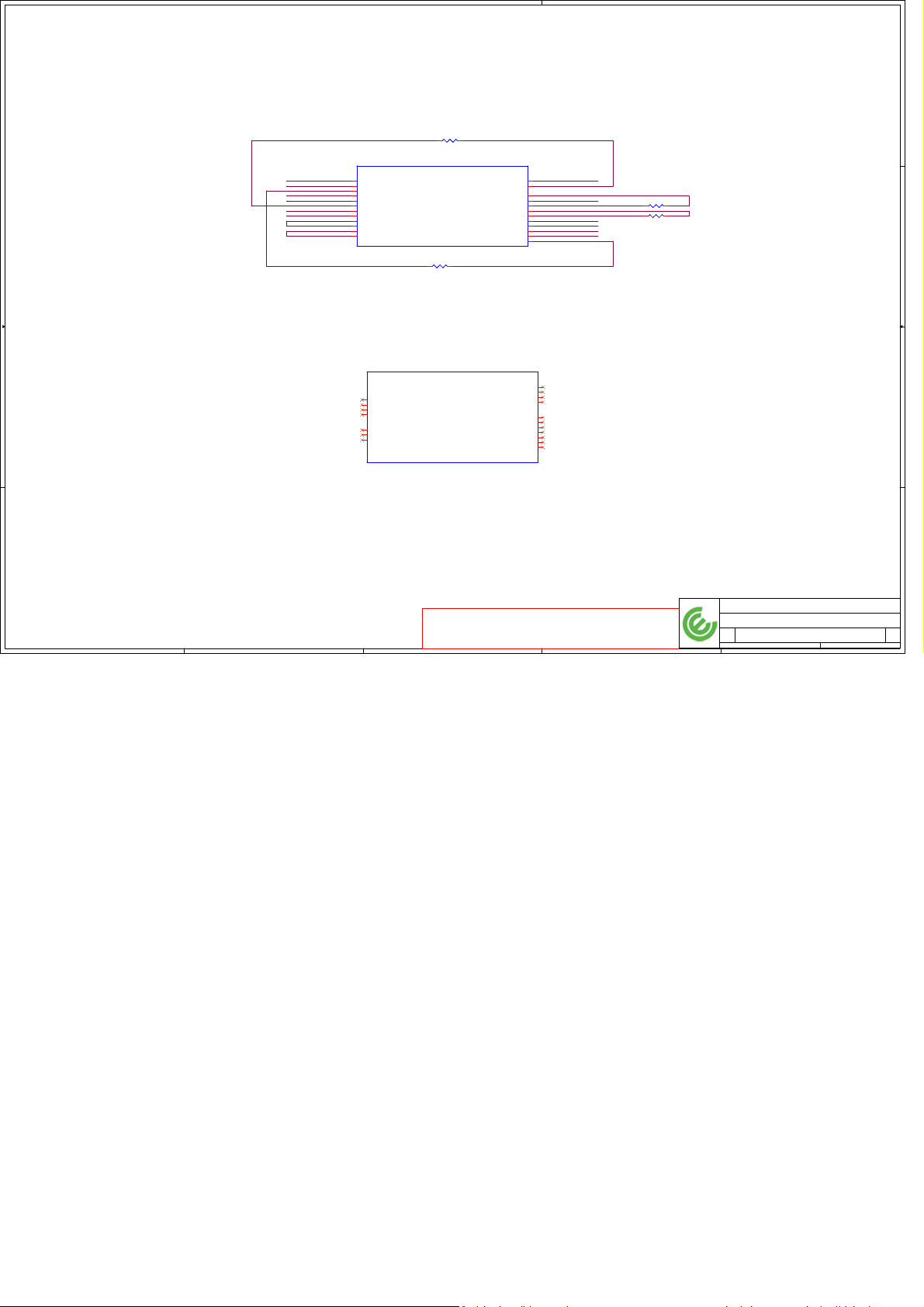

Page 3

5

4

3

2

1

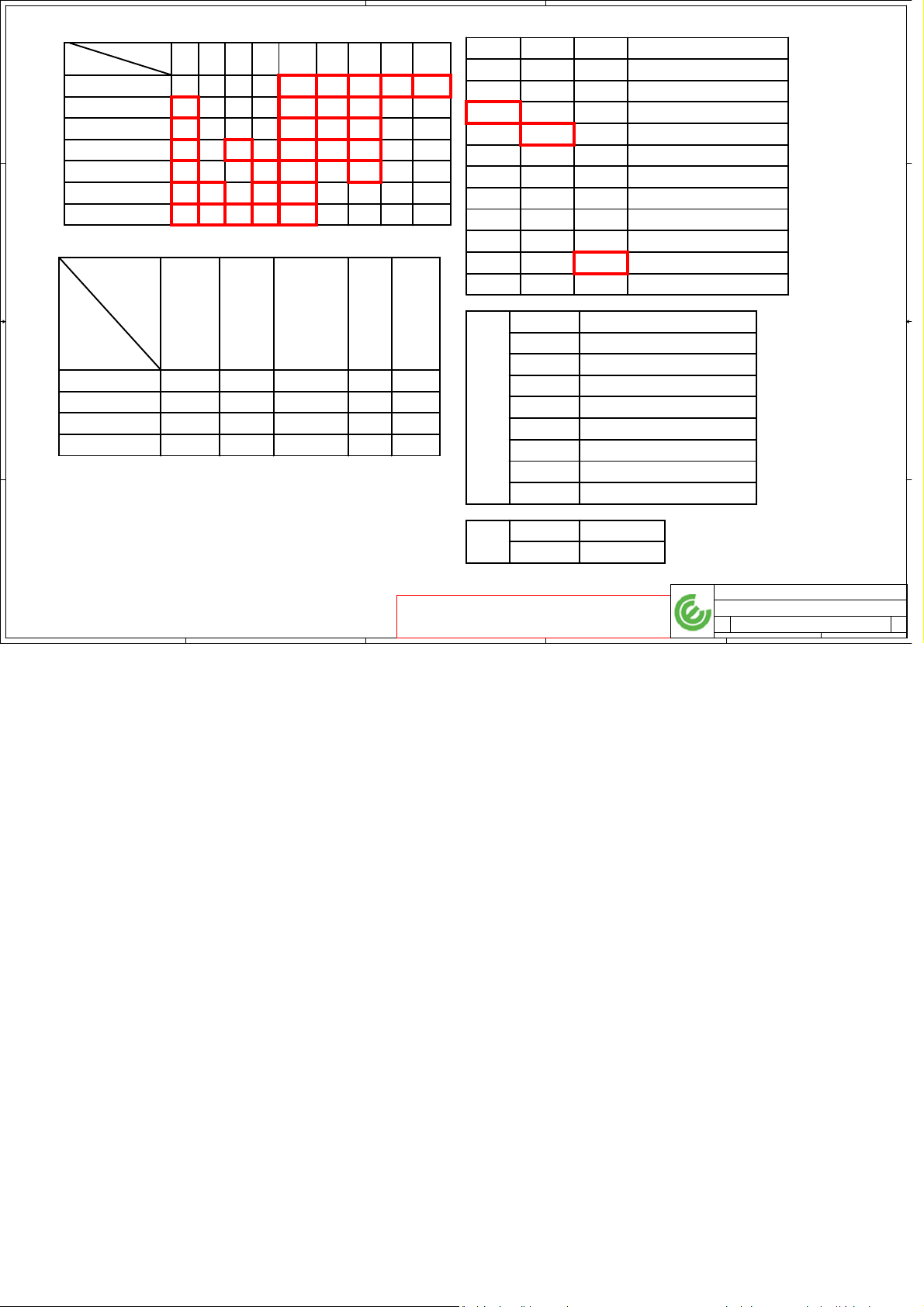

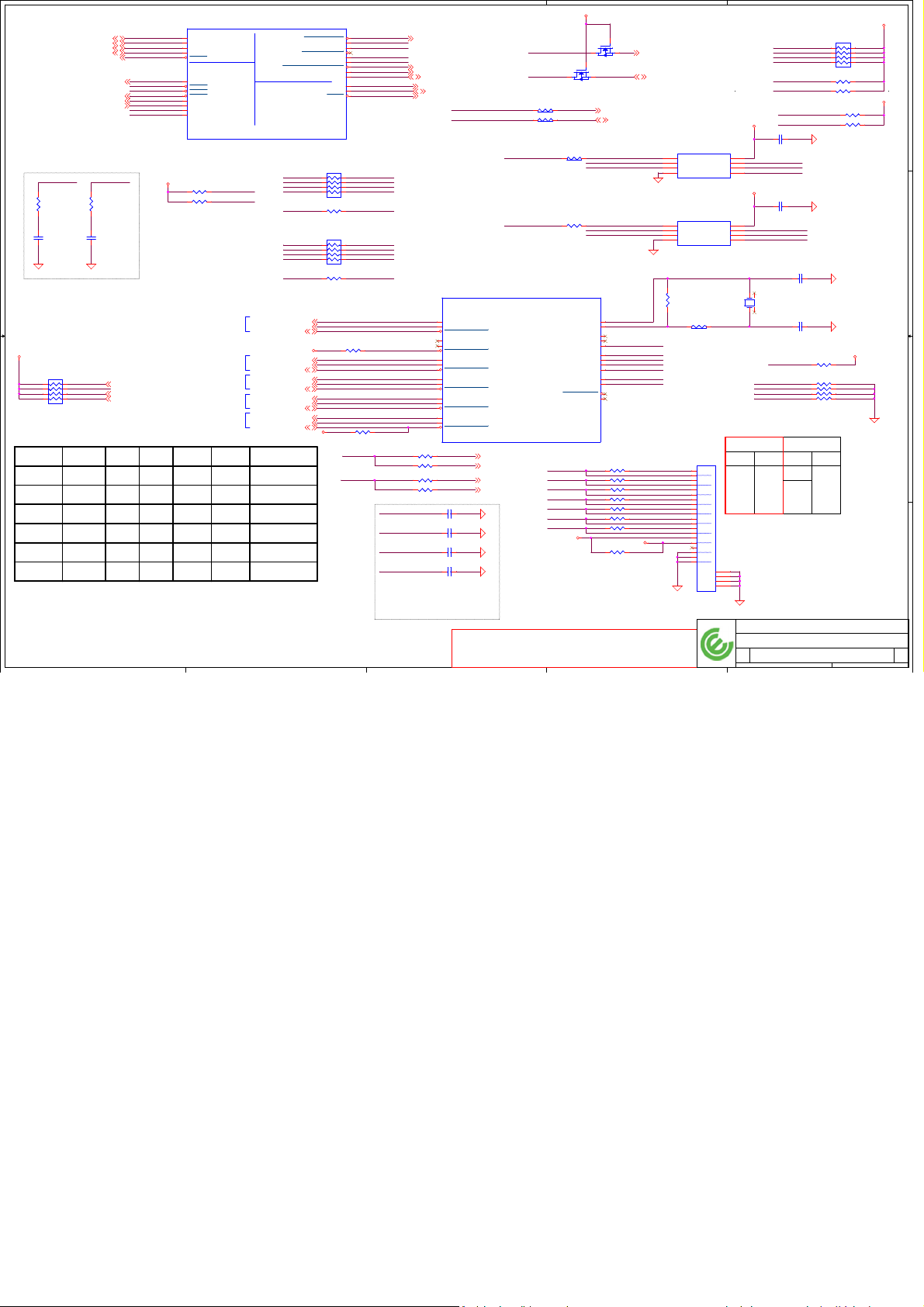

POWER STATES

Signal

State

D D

C C

S0 (Full ON) / M0

S3 (Suspend to RAM) / M3 LOW HIGH HIGH ON ON ON OFF

S4 (Suspend to DISK) / M3 ON ON OFF

S5 (SOFT OFF) / M3 ON ON OFFLOW HIGHLOW

S3 (Suspend to RAM) / M-OFF

S4 (Suspend to DISK) / M-OFF HIGH

S5 (SOFT OFF) / M-OFF

PM TABLE

power

plane

SLP

S3#

HIGH

LOW HIGH HIGH

LOW HIGH HIGH LOW ON ONOFF OFF OFF

LOW LOW LOW ON OFF OFF OFF OFF

LOW LOW LOW LOW ON OFF OFF OFF OFF

+3.3V_ALW

+3.3V_ALW _PCH

+3.3V_RTC_LDO

SLP

SLP

S5#

S4#

HIGH HIGH

LOW

LOW

+3.3V_SUS+5V_ALW +5V_RUN

+1.35V_MEM

ALWAYS

SLP

PLANE

A#

HIGH

HIGH

+0.675V_DDR_VTT

+1.05V_RUN

+VCC_CORE

M

SUS

RUN

PLANE

PLANE

ON

ON

ON ON ON

OFF

OFF

+3.3V_M +3.3V_M

+1.05V_M+3.3V_RUN

PLANE

+1.05V_M

(M-OFF)

CLOCKS

OFF

OFF

OFF

PCIE

PCIE 1

PCIE 2

PCIE 3

PCIE 4

PCIE 5

PCIE 6

USB3.0

USB3.0 1

USB3.0 2

USB3.0 3

USB3.0 4

SATA

SATA 3

SATA 2

SATA 0

USB PORT#

0

1

2

3

4

5

6

7

JUSB1 or DOCK1

JUSB3

WLAN + BT

JUSB2 or DOCK2

Touch Screen

CAMERA

USH

WWAN

State

ON

S0

B B

S3

S5 S4/AC

S5 S4/AC doesn't exist

ON

ON

ON ON

ON

OFF

OFFOFF

OFFON

OFF

OFF

ON

ON

OFF

ON

OFF

OFFOFF

BDW

ULT

DESTINATION

JUSB1-->Rear left

JUSB3-->Right

MMI (CARD READER)

JUSB2-->Rear Right

LOM

WLAN - JNGFF1

WiGig - JNGFF1

HCA & SATA Cache - JNGFF2

SATA Cache - JNGFF2

JMINI3SATA 1

JDOCK1

DESTINATION

A A

USH

1

0

BIO

NA

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Port assignment

Port assignment

Port assignment

LA-A971P

LA-A971P

LA-A971P

3 40Wednesday, March 19, 2014

3 40Wednesday, March 19, 2014

3 40Wednesday, March 19, 2014

1

0.1

0.1

0.1

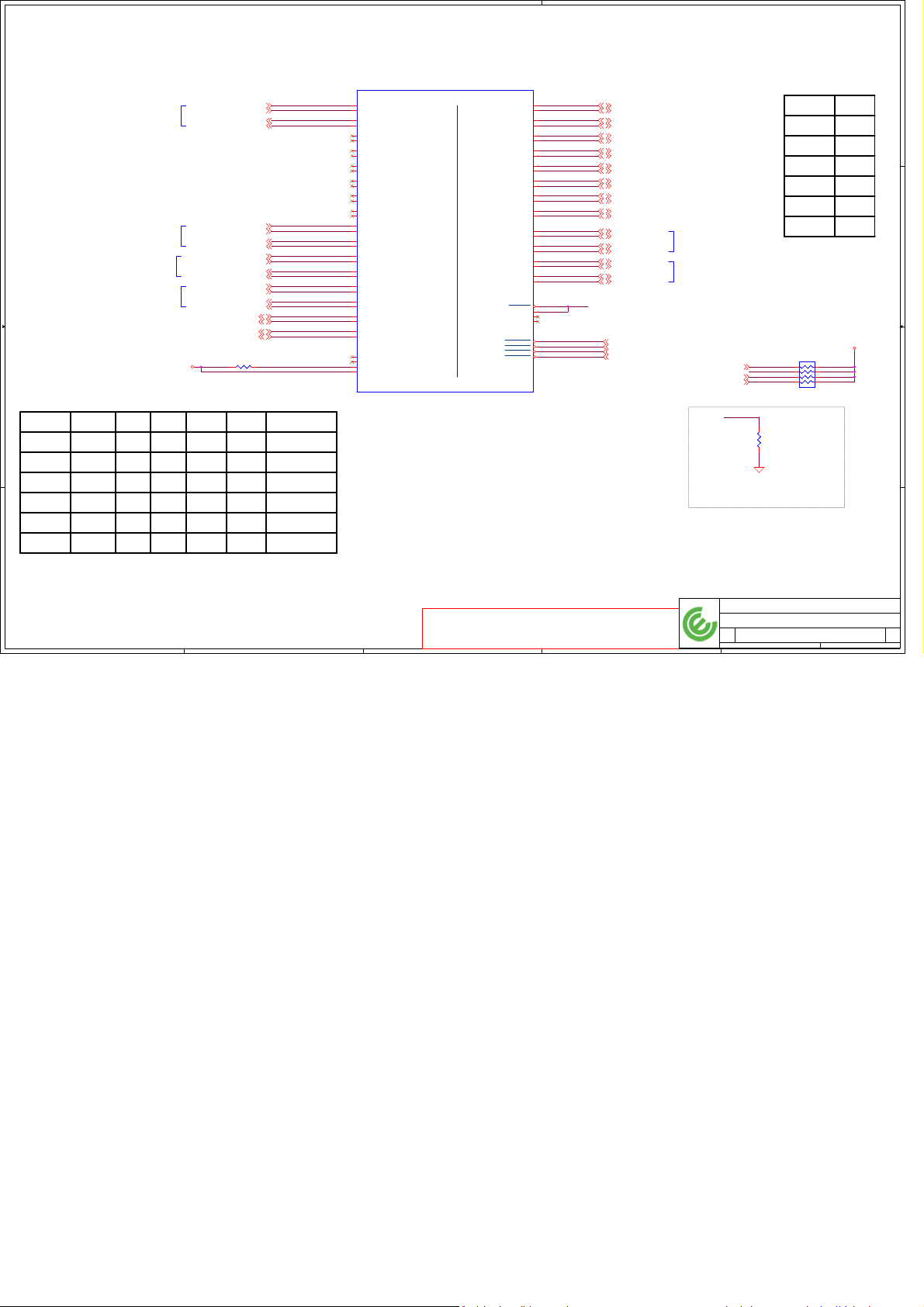

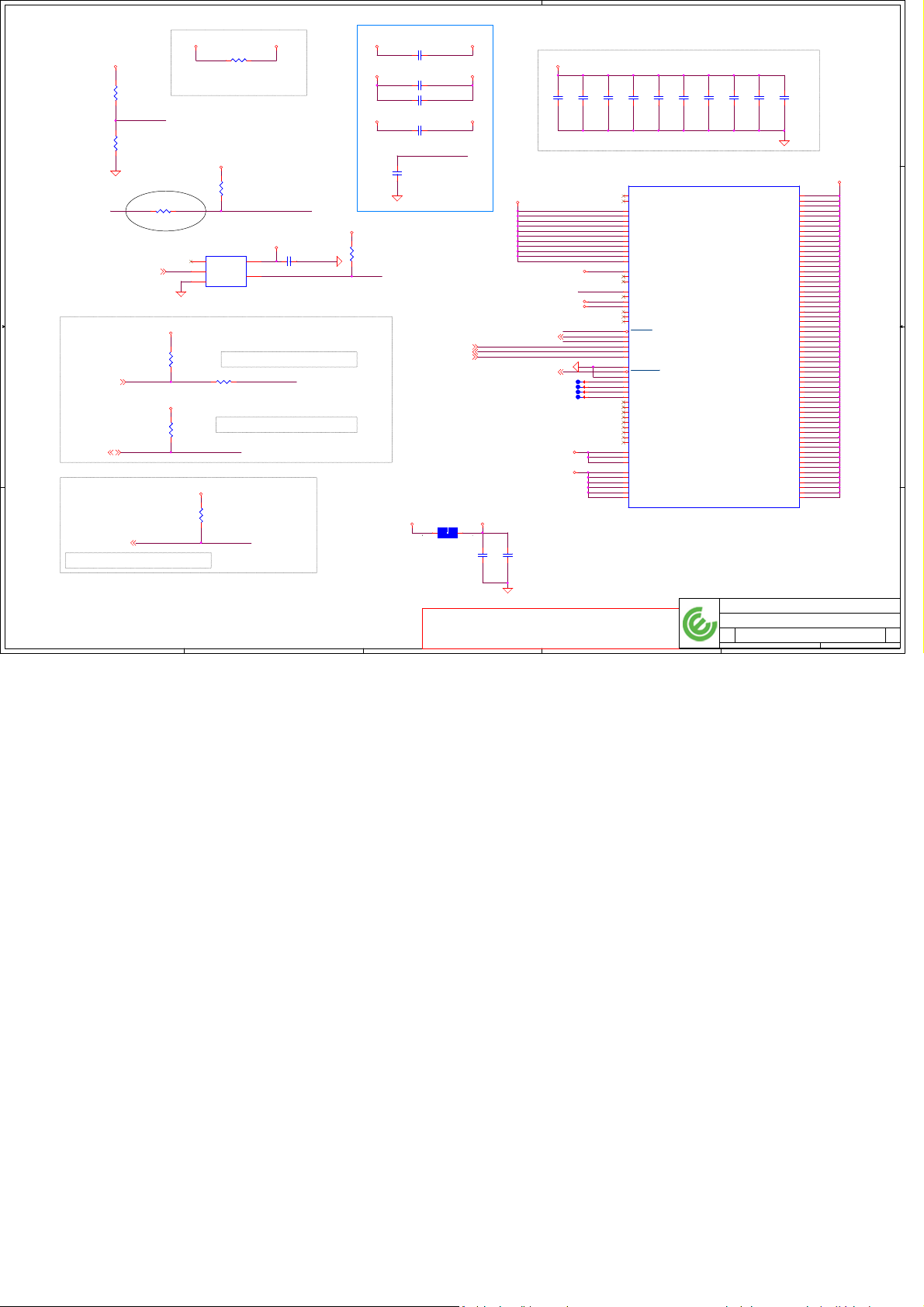

Page 4

5

4

3

2

1

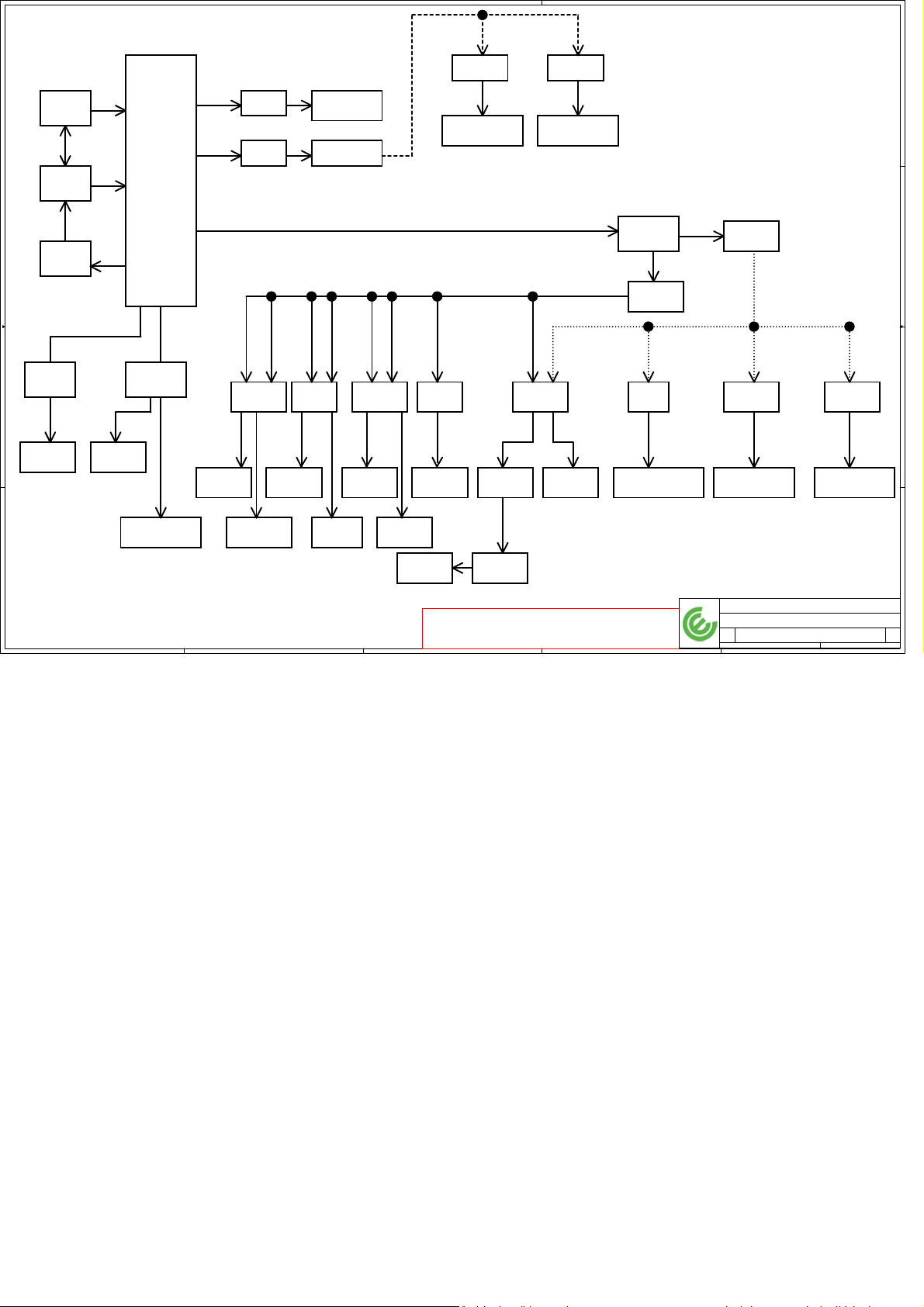

RUN_ON

TPS22966

D D

ADAPTER

EN_INVPWR

FDC654P

(QV1)

+BL_PWR_SRC

(UZ7)

+1.05V_RUN

A_ON

SY8208

(PU300)

+1.05V_M

MPHYP_PWR_EN

SI3456

(QZ6)

+1.05V_MODPHY

BATTERY +PWR_SRC

ALWON

C C

CHARGER

TPS51285

(PU100)

+5V_ALW

+3.3V_ALW

SUS_ON

ISL95813

(PU501)

B B

H_VR_EN

+VCC_CORE

SUS_ON

+1.35V_MEM

RT8207

(PU200)

0.675V_DDR_VTT_ON

+3.3V_SUS

3.3V_HDD_EN

TPS22966

(UZ8) (UZ9)

+3.3V_WWAN

3.3V_WWAN_EN

TPS22966

(UZ2)

AUX_EN_WOWL

SIO_SLP_LAN#

TPS22966

(UL3)

+3.3V_LAN

A_ON

EN_LCDPWR

APL3512

(UV24)

+LCDVDD

+3.3V_RUN

RUN_ON

RUN_ON

TPS22966

+5V_RUN

USB_PWR_SHR_EN#

TPS2544

(UI3)

+5V_USB_CHG_PWR

USB_PWR_EN1#

G547I2P81U

(UI1)

USB_PWR_EN2#

G547I2P81U

(UI2)

+USB_SIDE_PWR +USB_RIGHT_PWR

+0.675V_DDR_VTT

A A

+3.3V_HDD

+3.3V_WLAN

+3.3V_M

+3.3V_CAM

3.3V_CAM_EN#

LP2301ALT1G

(QZ1)

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

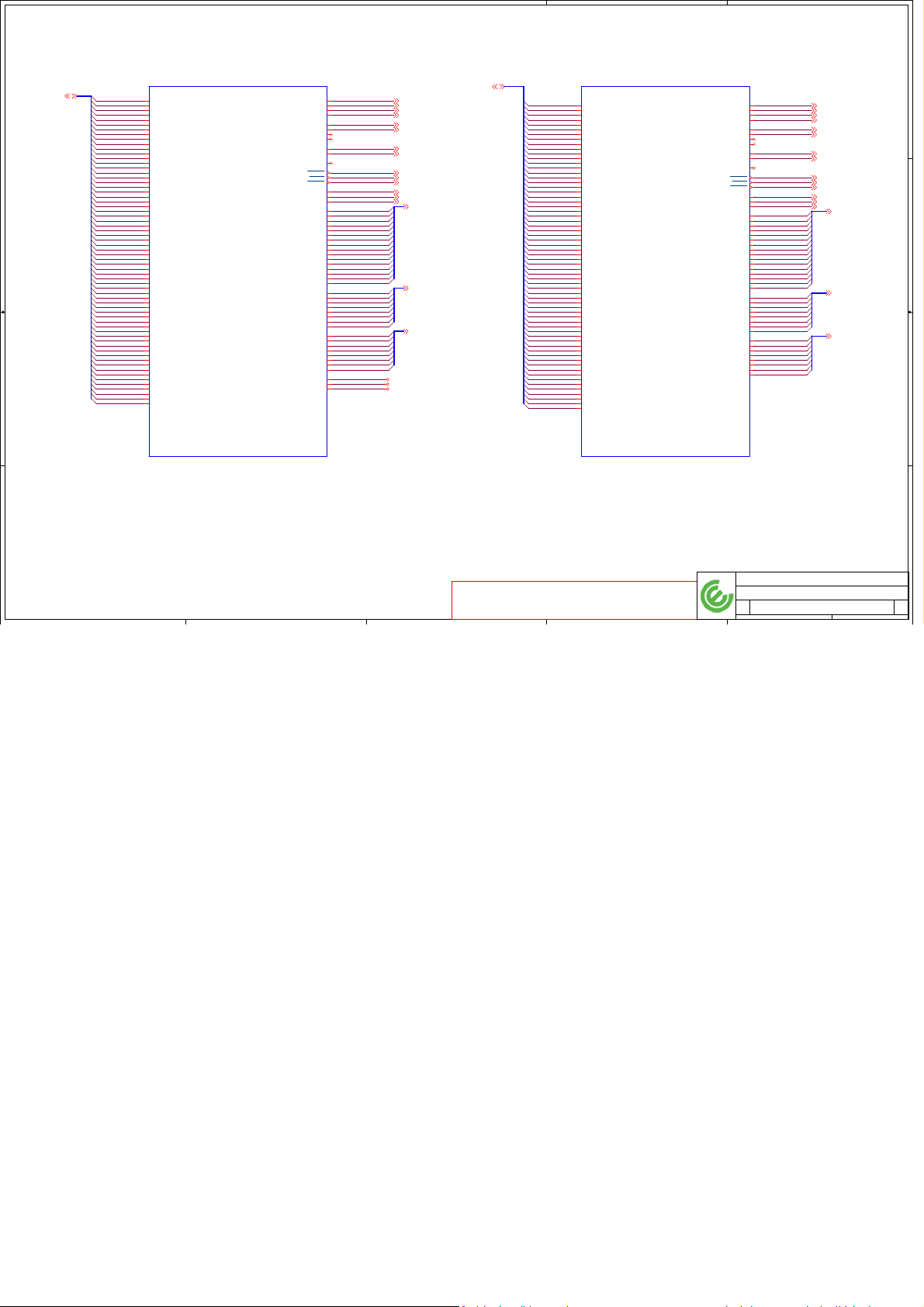

Power rails

Power rails

Power rails

LA-A971P

LA-A971P

LA-A971P

1

4 40Wednesday, March 19, 2014

4 40Wednesday, March 19, 2014

4 40Wednesday, March 19, 2014

0.1

0.1

0.1

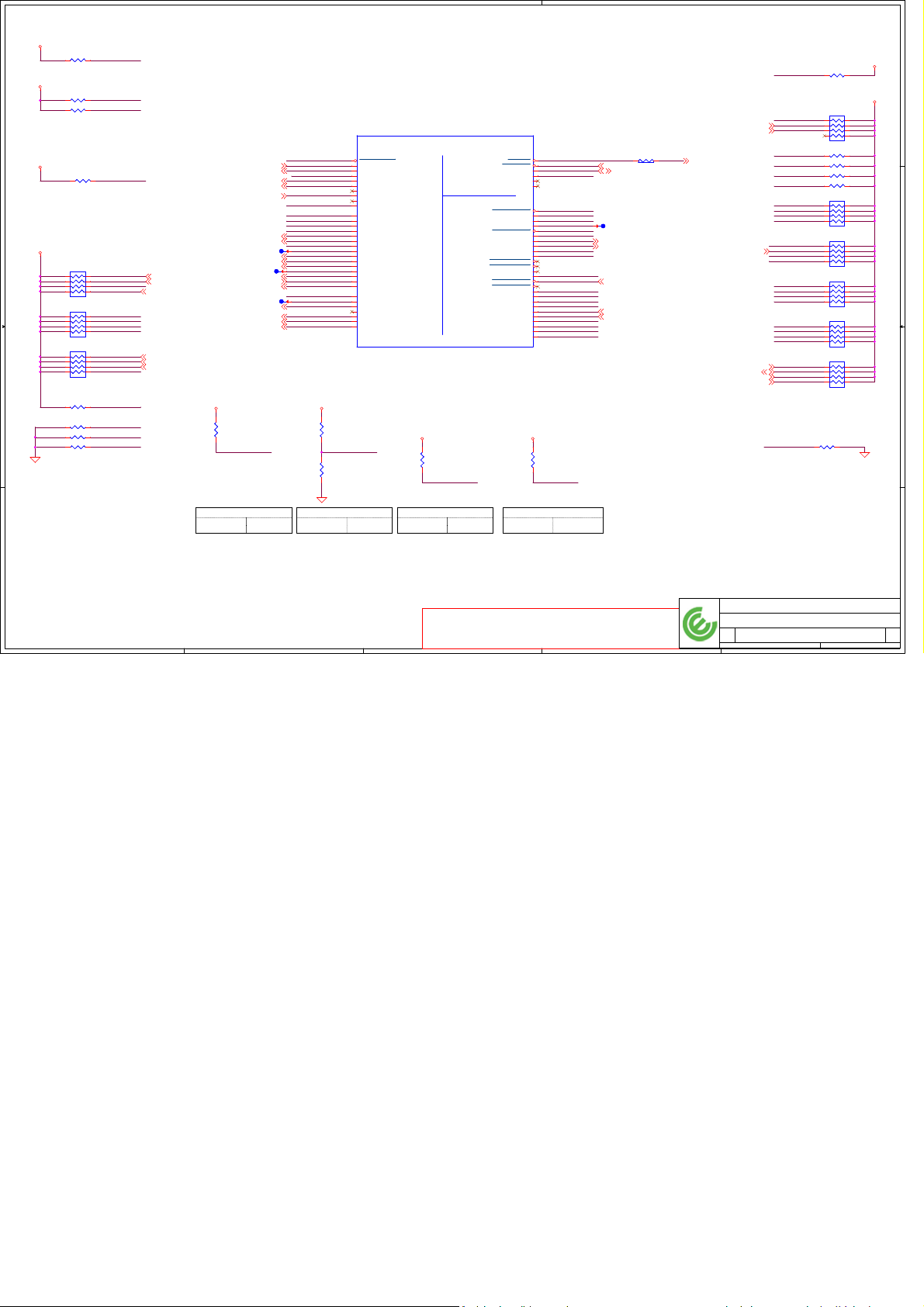

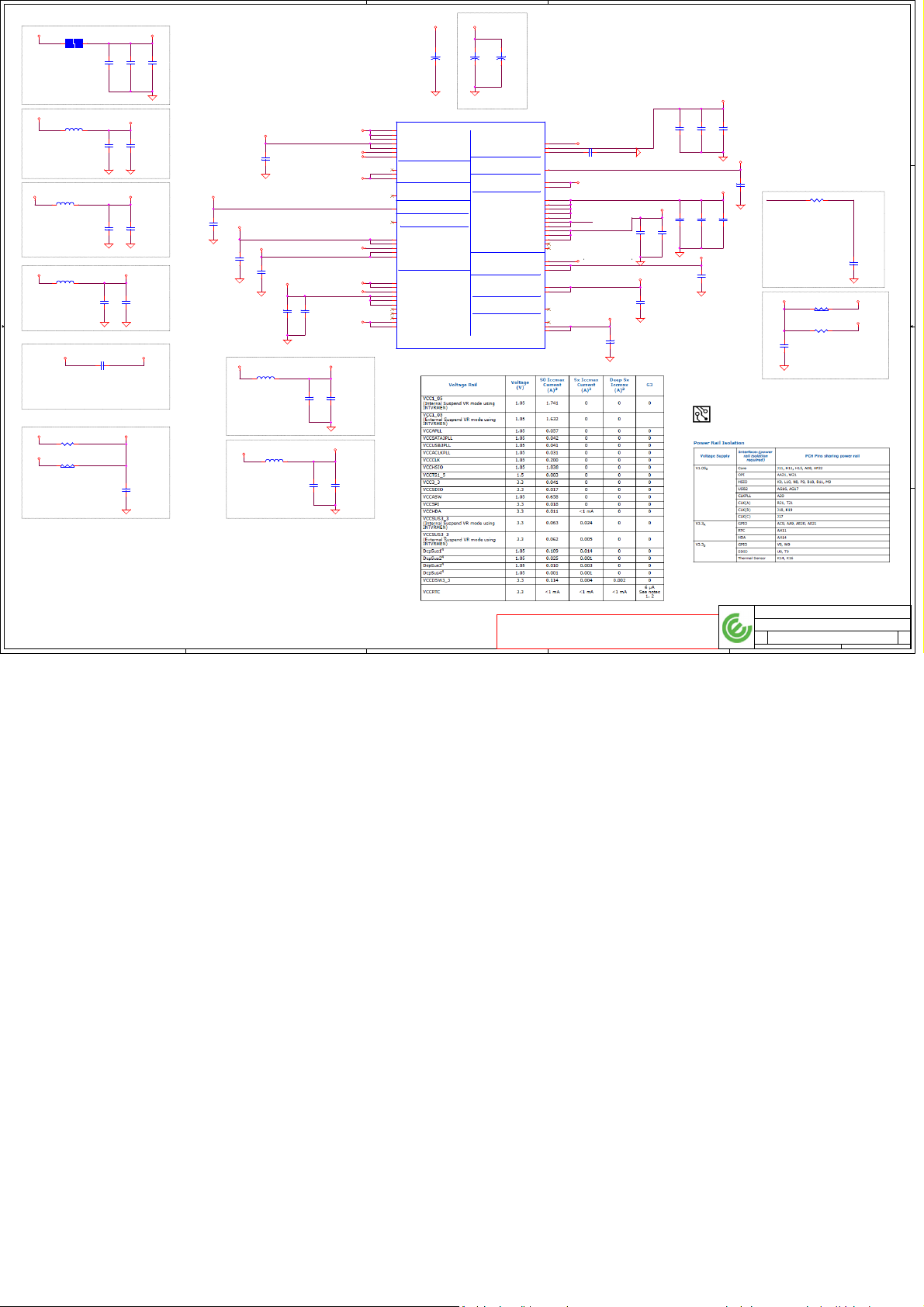

Page 5

5

SMBUS Address [0x9a]

MEM_SMBCLK

AP2

MEM_SMBDATA

AH1

D D

C C

BDW

SML0CLK

AN1

SML0DATA

AK1

AU3AH3

SML1_SMBDATA

SML1_SMBCLK

B6A5

3A

3A

2.2K

+3.3V_ALW_PCH

2.2K

B4

A3

B5

A4

DOCK_SMB_CLK

DOCK_SMB_DAT

LCD_SMBCLK

LCD_SMDATA

1A

1A

1B

1B

KBC

A56

A50

B53

A49

B52

B50

A47

B7

A7

B48

B49

PBAT_SMBCLK

PBAT_SMBDAT

USH_SMBCLK

USH_SMBDAT

CARD_SMBCLK

CARD_SMBDAT

CHARGER_SMBCLK

CHARGER_SMBDAT

BAY_SMBDAT

BAY_SMBCLK

GPU_SMBDAT

GPU_SMBCLK

1C1CB59

MEC 5085

B B

A A

1E

1E

2B

2B

1G

1G

2D

2D

2A

2A

5

2.2K

2.2K

1K

1K

4

+3.3V_ALW_PCH

2.2K

2.2K

2.2K

2.2K

2.2K

2.2K

2.2K

2.2K

2.2K

2.2K

10K

10K

2.2K

2.2K

2.2K

2.2K

4

+3.3V_ALW_PCH

+3.3V_ALW

+3.3V_ALW

+3.3V_ALW

100 ohm

100 ohm

+3.3V_SUS

+3.3V_ALW

+3.3V_ALW

9

8

+3.3V_ALW

+3.3V_ALW

2N7002

2N7002

3

2

1

2.2K

+3.3V_RUN

2.2K

202

4

200

202

28

31

LOM

7

BATTERY

6

CONN

M9

L9

USH

200

53

51

DIMMA

DIMMB

XDP

Charger

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

SMbus Block diagram

SMbus Block diagram

SMbus Block diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

LA-A971P

LA-A971P

LA-A971P

1

5 40Wednesday, March 19, 2014

5 40Wednesday, March 19, 2014

5 40Wednesday, March 19, 2014

0.1

0.1

0.1

Page 6

5

4

3

2

1

UMA SATA port

Service Mode Switch:

D D

+RTC_CELL

330K_0402_5%

330K_0402_5%

12

RC1

RC1

PCH_INTVRMEN

INTVRMEN - INTEGRATED SUS 1.05V VRM

C C

ENABLE

High - Enable Internal VRs

Low - Enable External VRs

RC9 1M_0402_5%RC9 1M_0402_5%

+RTC_CELL

RC10 20K_0402_5%RC10 20K_0402_5%

RC8 20K_0402_5%RC8 20K_0402_5%

1 2

CC3 1U_0402_6.3V6KCC3 1U_0402_6.3V6K

ME_CLR1

Shunt Clear ME RTC Registers

B B

Open

+1.05V_M

TPM setting

Keep ME RTC Registers

RPC21

RPC21

18

27

36

45

51_0804_8P4R_5%

51_0804_8P4R_5%

12

RC18@ 1K_0402_1%RC18@ 1K_0402_1%

12

PCH_JTAG_TCK

RC21@51_0402_5%RC21@51_0402_5%

Add a switch to ME_FWP signal to unlock the ME region and

allow the entire region of the SPI flash to be updated using FPT.

+3.3V_ALW_PCH

PT, ST pop RC2 & SW1; MP pop RC301.

12

RC2

RC2

1K_0402_5%

1K_0402_5%

ME_FWP_EC<36>

ME_FWP PCH has internal 20K PD.

FLASH DESCRIPTOR SECURITY OVERRIDE

LOW = ENABLE (DEFAULT) -->Pin1 & Pin3 short

HIGH = DISABLE (ME can update) -->Pin2 & Pin3 short

CC1

CC1

1 2

12P_0402_50V8J

12P_0402_50V8J

CC2

CC2

1 2

1 2

1 2

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_JTAGX

1 2

12P_0402_50V8J

12P_0402_50V8J

112

CMOS1@SHORT PADS~DCMOS1@SHORT PADS~D

1 2

1U_0402_6.3V6K

1U_0402_6.3V6K

CC4

CC4

CMOS place near DIMM

CMOS_CLR1

CMOS setting

Shunt Clear CMOS

Open

+1.05V_M

2

Keep CMOS

@

@

1 2

10K_0402_5%

10K_0402_5%

12

RC301

0_0402_5%

@RC301

0_0402_5%

@

ME_FWP

1 2

RC4@ 0_0402_5%RC4@ 0_0402_5%

12

YC1

YC1

32.768KHZ_12.5PF_9H03220008

32.768KHZ_12.5PF_9H03220008

PCH_AZ_CODEC_SDIN0<21>

RC300

RC300

@

@

1 2

ME_FWPME_FWP_EC

SW1

SW1

1

2

3

4

5

SS3-CMFTQR9_3P

SS3-CMFTQR9_3P

PCH_RTCRST#<9>

ME_FWP

PCH_JTAG_TRST#<9>

PCH_JTAG_JTAGX<9>

CC100

CC100

1U_0402_6.3V6K

1U_0402_6.3V6K

A

B

C

G1

G2

PCH_JTAG_TCK<9>

PCH_JTAG_TDI<9>

PCH_JTAG_TDO<9>

PCH_JTAG_TMS<9>

PCH_RTCX1PCH_RTCX1_R

10M_0402_5%

10M_0402_5%

12

RC7

RC7

PCH_RTCX2

INTRUDER#

PCH_INTVRMEN

SRTCRST#

PCH_RTCRST#

PCH_AZ_BITCLK

PCH_AZ_SYNC

PCH_AZ_RST#

PCH_AZ_CODEC_SDIN0

1 2

PCH_AZ_SDOUT

RC11 1K_0402_5%RC11 1K_0402_ 5%

PCH_JTAG_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PM_TEST_RST

AW5

AY5

AU6

AV7

AV6

AU7

AW8

AV11

AU8

AY10

AU12

AU11

AW10

AV10

AY8

AU62

AE62

AD61

AE61

AD62

AL11

AC4

AE63

AV2

SATA0

E-Dock

E-Dock

E-Dock

UC1E

UC1E

RTCX1

RTCX2

INTRUDER

INTVRMEN

SRTCRST

RTCRST

HDA_BCLK/I2S0_SCLK

HDA_SYNC/I2S0_SFRM

HDA_RST/I2S_MCLK

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_SDO/I2S0_TXD

HDA_DOCK_EN/I2S1_TXD

HDA_DOCK_RST/I2S1_SFRM

I2S1_SCLK

PCH_TRST

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

RSVD

RSVD

JTAGX

RSVD

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

5 OF 19

5 OF 19

mSATA

mSATA

mSATA

NANAmSATA

BDW_ULT_DDR3L

BDW_ULT_DDR3L

RTC

RTC

AUDIO SATA

AUDIO SATA

JTAG

JTAG

HDA for Codec

1 2

PCH_AZ_CODEC_SDOUT<21>

A A

PCH_AZ_CODEC_SYNC<21>

PCH_AZ_CODEC_RST#<21>

PCH_AZ_CODEC_BITCLK<21>

RC19 33_0402_5%RC19 33_0402_5%

RC20 33_0402_5%RC20 33_0402_5%

RC22 33_0402_5%RC22 33_0402_5%

RC23 33_0402_5%

RC23 33_0402_5%

27P_0402_50V8J

27P_0402_50V8J

@EMC@

@EMC@

12

CC5

CC5

Reserve for EMI

5

1 2

1 2

EMC@

EMC@

1 2

PCH_AZ_SDOUT

PCH_AZ_SYNC

PCH_AZ_RST#

PCH_AZ_BITCLK

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

HDD

HDD

PCB

G12 UMA

G12 EntryNA

G14 DSC

G14 UMA

G14D_En

G14U_En

SATA2/PCIE6 L1SATA1

M2 3042

2nd PCIe Lane for PCIe Cache

NA NA

M2 3042

SATA-Cache(no HCA)

M2 3042

2nd PCIe Lane for PCIe Cache

NA

NA

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_IREF

RSVD

RSVD

SATA_RCOMP

SATALED

2

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

U1

V6

AC1

A12

L11

K10

C12

U3

MPCIE_RST#

SATA2_PCIE6_L1

SATA_COMP

SATA_ACT#

SATA3/PCIE6 L0

M2 3042

(HCA & SATA-Cache)

M2 3030 WIGIG

M2 3042

(HCA & SATA-Cache)

M2 3030 WIGIG

contact to WWAN

SATA2/PCIE6_L1 contact to WWAN

SATA3/PCIE6 L0 contact to WLAN

contact to WWAN

contact to WLAN

NA

SATA_PRX_DKTX_N0_C <34>

SATA_PRX_DKTX_P0_C <34>

SATA_PTX_DKRX_N0_C <34>

SATA_PTX_DKRX_P0_C <34>

SATA_PRX_DTX_N1 <20>

SATA_PRX_DTX_P1 <20>

SATA_PTX_DRX_N1 <20>

SATA_PTX_DRX_P1 <20>

PCIE_PRX_SATATX_N6_L1 <30>

PCIE_PRX_SATATX_P6_L1 <30>

PCIE_PTX_SATARX_N6_L1 <30>

PCIE_PTX_SATARX_P6_L1 <30>

PCIE_PRX_SATATX_N6_L0 <30>

PCIE_PRX_SATATX_P6_L0 <30>

PCIE_PTX_SATARX_N6_L0 <30>

PCIE_PTX_SATARX_P6_L0 <30>

HDD_DET# <20>

SATA2_PCIE6_L1 <12,35>

mCARD_PCIE#_SATA <36,7>

SATA_ACT# <39>

MMICLK_REQ#<29,7>

DGPU_PWROK<10>

SATA Impedance Compensation

CAD note:

Place the resistor within 500 mils of the PCH. Avoid

routing next to clock pins.

+PCH_ASATA3PLL

SATA_COMP

for DOCK

SATA HDD

for PCIe Cache (WWAN)

for SATA-CACHE (WWAN)

MPCIE_RST#

HDD_DET#

7

8

10K_8P4R_5%

10K_8P4R_5%

+PCH_ASATA3PLL

1 2

RC173.01K_0402_1% RC173.01K_0402_1%

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (1/12)

CPU (1/12)

CPU (1/12)

LA-A971P

LA-A971P

LA-A971P

1

RPC18

RPC18

+3.3V_RUN

3456

2

1

0.1

0.1

6 48Wednesday, March 19, 2014

6 48Wednesday, March 19, 2014

6 48Wednesday, March 19, 2014

0.1

Page 7

5

UC1G

UC1G

AU14

LPC_LAD0<20,35,36>

LPC_LAD1<20,35,36>

LPC_LAD2<20,35,36>

LPC_LAD3<20,35,36>

LPC_LFRAME#<20,35,36>

D D

33_0402_5%

33_0402_5%

1 2

1 2

C C

PCH_SPI_CLK<27>

PCH_SPI_CS2#<27>

PCH_SPI_DO<27>

SPI_CLK32 SPI_CLK64

RC61

@EMC@

RC61

@EMC@

33P_0402_50V8J

33P_0402_50V8J

CC9

@EMC@

CC9

@EMC@

LPC_LAD0

LPC_LAD1

LPC_LAD2

LPC_LAD3

LPC_LFRAME#

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_CS1#

PCH_SPI_CS2#

PCH_SPI_DO

PCH_SPI_DIN

PCH_SPI_DIN<27>

PCH_SPI_DO2

PCH_SPI_DO3

33_0402_5%

33_0402_5%

RC62

@EMC@

RC62

@EMC@

1 2

33P_0402_50V8J

33P_0402_50V8J

CC10

@EMC@

CC10

@EMC@

1 2

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

7 OF 19

7 OF 19

+3.3V_SPI

1 2

RC29 1K_040 2_5%RC29 1K_04 02_5%

1 2

RC31 1K_040 2_5%RC31 1K_04 02_5%

SPI_PCH_DO2

SPI_PCH_DO3

MMI --->

+3.3V_RUN

RPC6

RPC6

4 5

3

2

1

10K_8P4R_5%

10K_8P4R_5%

B B

PCB

G12 UMA

G12 Entry NA

G14 DSC

G14 UMA

G14D_En

G14U_En

A A

CONTACTLESS_DET# <10,27>

6

LANCLK_REQ#

7

8

mCARD_PCIE#_SATA <36 ,6>

PCH_GPIO16 <12>

PCIE1 PCIE4

SD card

NA LOM

NA

SD card

SD card

SD card

SD card

NA

NA

NA

NA

5

10/100/1G LAN --->

WLAN (NGFF1)--->

WGIG (NGFF1)--->

HCA/PCIe cache (NGFF2)--->

PCIE3PCIE2

WLAN

LOM

WLAN

LOM

WLAN

LOM

WLAN

LOM

WLAN

LOM

WLAN

PCIE5

WIGIG

WIGIGSD card

GPU

WIGIG

GPU

WIGIG

4

BDW_ULT_DDR3L

BDW_ULT_DDR3L

LPC

LPC

SMBUS

SMBUS

SML1ALERT/PCHHOT/GPIO73

C-LINKSPI

C-LINKSPI

SPI_PCH_DIN

SPI_PCH_DO

SPI_PCH_CLK

SPI_PCH_DO3

SPI_PCH_DO2 SPI_PCH_ DO2_64

SPI_PCH_DO3

SPI_PCH_CLK

SPI_PCH_DO

SPI_PCH_DIN

SPI_PCH_DO2 SPI_PCH_ DO2_32

PCIECLK for UMA

CLK_PCIE_MMI#<29>

CLK_PCIE_MMI<29>

MMICLK_REQ#<29,6>

+3.3V_RUN

CLK_PCIE_LAN#<28>

CLK_PCIE_LAN<28>

LANCLK_REQ#<28>

CLK_PCIE_WLAN#<30>

CLK_PCIE_WLAN<3 0>

WLANCLK_REQ#<12,30 >

CLK_PCIE_WIGIG#<30>

CLK_PCIE_WIGIG<30>

WIGIGCLK_REQ#<12,30>

CLK_PCIE_SATA#<30>

CLK_PCIE_SATA<30>

SATACLK_REQ#<30>

+3.3V_RUN

PCIE6

M2 3042

(HCA & SATA-Cache)

WIGIG

M2 3042

(HCA & SATA-Cache)

WIGIG

NA

4

SMBALERT/GPIO11

SMBCLK

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_CLK

CL_DATA

CL_RST

SOFTWARE TAA

RPC11

RPC11

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

33_0804_8P4R_5%

1 2

RC38 33_0402_5%RC38 33_0402_5%

RPC12

RPC12

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

33_0804_8P4R_5%

1 2

RC55 33_0402_5%

RC55 33_0402_5%

VPRO@

VPRO@

RC66 10K_0402_5%RC66 10K_0402_5%

RC68 10K_0402_5%RC68 10K_0402_5%

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AF2

AD2

AF4

SPI_DIN64

SPI_DO64

SPI_CLK64

SPI_PCH_DO3_64

VPRO@

VPRO@

SPI_PCH_DO3_32

SPI_CLK32

SPI_DO32

SPI_DIN32

MMICLK_REQ#

1 2

LANCLK_REQ#

WLANCLK_REQ#

WIGIGCLK_REQ#

1 2

PCI_CLK_LPC_0

PCI_CLK_LPC_1

MEM_SMBCLK

MEM_SMBDATA

SML0_SMBCLK

SML0_SMBDATA

SML1_SMBCLK

SML1_SMBDATA

PCH_CL_CLK1

PCH_CL_DATA1

PCH_CL_RST1#

CLK_PCI_SIO

CLK_PCI_MEC

CLK_PCI_LPDEBUG

CLK_PCI_DOCK

PCH_SMB_ALERT# <11 >

PCH_GPIO73 <1 2>

SML1_SMBCLK <36>

SML1_SMBDATA <36>

PCH_CL_CLK1 <30>

PCH_CL_DATA1 <30>

PCH_CL_RST1# <30>

SML0_SMBCLK

SML0_SMBDATA

UC1F

UC1F

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCH_GPIO19

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

6 OF 19

6 OF 19

1 2

RC72EMC@ 22_04 02_5%RC72EMC@ 22_0402_ 5%

1 2

RC74EMC@ 22_04 02_5%RC74EMC@ 22_0402_ 5%

1 2

RC67EMC@ 22_04 02_5%RC67EMC@ 22_0402_ 5%

1 2

RC70EMC@ 22_0402_5%RC70EMC@ 22_0402_5%

MP Depop RC70.

33P_0402_50V8J @EMC@

33P_0402_50V8J @EMC@

33P_0402_50V8J @EMC@

33P_0402_50V8J @EMC@

33P_0402_50V8J @EMC@

33P_0402_50V8J @EMC@

33P_0402_50V8J @EMC@

33P_0402_50V8J @EMC@

Reserve for EMI

3

MEM_SMBCLK

MEM_SMBDATA

RC30 0_0402_5%@ RC30 0_0402_5%@

RC32 0_0402_5%@ RC32 0_0402_5%@

SPI_PCH_CS0#

SPI_PCH_CS1#

BDW_ULT_DDR3L

BDW_ULT_DDR3L

CLOCK

CLOCK

SIGNALS

SIGNALS

CLK_PCI_SIO <35>

CLK_PCI_MEC <36>

CLK_PCI_LPDEBUG <20,36>

CLK_PCI_DOCK <34>

12

CC12

CC12

12

CC13

CC13

12

CC14

CC14

12

CC15

CC15

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

+3.3V_RUN

5

3 4

QC1B

QC1B

DMN66D0LDW -7_SOT363-6

DMN66D0LDW -7_SOT363-6

12

12

1 2

RC35 0_0402_5%@RC35 0_0402_5%@

1 2

RC50 0_0402_5%

RC50 0_0402_5%

VPRO@

VPRO@

XTAL24_IN

XTAL24_OUT

RSVD

RSVD

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

PCH_SPI_CS1#

PCH_SPI_DO

PCH_SPI_DIN

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_DO2

+3.3V_SPI

126

QC1A

QC1A

DMN66D0LDW -7_SOT363-6

DMN66D0LDW -7_SOT363-6

LAN_SMBCLK <28>

LAN_SMBDATA <28>

SPI_PCH_CS0#_R

SPI_DIN64

SPI_PCH_DO2_64

SPI_PCH_CS1#_R

SPI_DIN32

SPI_PCH_DO2_32

A25

XTAL24_IN

B25

XTAL24_OUT

K21

M21

C26

CLK_BIASREF

C35

MCP_TESTLOW1

C34

MCP_TESTLOW2

AK8

MCP_TESTLOW3

AL8

MCP_TESTLOW4

AN15

PCI_CLK_LPC_0

AP15

PCI_CLK_LPC_1

B35

A35

12

RC224 0_0402_5%RC 224 0_0402_5%

12

RC225 0_0402_5%RC 225 0_040 2_5%

12

RC226 0_0402_5%RC 226 0_040 2_5%

12

RC227 0_0402_5%RC 227 0_0402_5%

12

RC228 0_0402_5%RC 228 0_040 2_5%

12

RC229 0_0402_5%RC 229 0_040 2_5%

12

RC230 0_0402_5%RC 230 0_040 2_5%

+3.3V_M

12

RC231 0_0402_5%RC 231 0_040 2_5%

2

DDR_XDP_WAN_ SMBCLK <18,19,9>

DDR_XDP_WAN_ SMBDAT <18,19,9>

64Mb Flash ROM

UC2

UC2

1

/CS

2

DO(IO1)

3

/WP(IO2)

GND4DI(IO0)

W25Q64FVSSIQ_SO8

W25Q64FVSSIQ_SO8

32Mb Flash ROM

UC3

UC3

1

/CS

2

DO/IO1

3

/WP/IO2

GND4DI/IO0

W25Q32FVSSIQ_SO8

W25Q32FVSSIQ_SO8

1M_0402_5%

1M_0402_5%

RC63

RC63

1 2

RC65@ 0_0402_ 5%RC65@ 0_0402_5 %

to SPI ROMfrom CPU

SPI_PCH_CS1#

SPI_PCH_DO

SPI_PCH_DIN

SPI_PCH_CLK

SPI_PCH_CS0#

SPI_PCH_DO2

SPI_PCH_DO3PCH_SPI_DO3

2

SML1_SMBDATA

SML1_SMBCLK

MEM_SMBCLK

MEM_SMBDATA

SML0_SMBCLK

SML0_SMBDATA

DDR_XDP_WAN_ SMBDAT

DDR_XDP_WAN_ SMBCLK

+3.3V_SPI

CC6

CC6

1 2

0.1U_0402_25V6

0.1U_0402_25V6

8

VCC

7

SPI_PCH_DO3_64

/HOLD(IO3)

6

SPI_CLK64

CLK

5

SPI_DO64

+3.3V_SPI

VPRO@

VPRO@

CC7

CC7

1 2

0.1U_0402_25V6

VPRO@

VPRO@

/HOLD/IO3

1 2

XTAL24_OUT_R

JSPI1

JSPI1

1

1

2

2 2

3

3

4

4 4

5

5

6

6 6

7

7

8

8 8

9

9

10

10 10

11

11

12

12 12

13

13

14

14 14

15

15

16

16 16

17

17

18

18 18

19

19

20

20 20

G1

G2

G3

G4

E-T_6700K-Y20N-00L

E-T_6700K-Y20N-00L

CONN@

CONN@

DELL CONFIDENTIAL/PROPRIETARY

0.1U_0402_25V6

8

VCC

7

SPI_PCH_DO3_32

6

SPI_CLK32

CLK

5

SPI_DO32

CC8

CC8

12

15P_0402_50V8J

15P_0402_50V8J

3

4

YC2

YC2

24MHZ_12PF_X3G0240 00DC1H

24MHZ_12PF_X3G0240 00DC1H

1

2

CC11

CC11

12

15P_0402_50V8J

15P_0402_50V8J

1 2

CLK_BIASREF

MCP_TESTLOW1

MCP_TESTLOW2

MCP_TESTLOW3

MCP_TESTLOW4

support SPI TPM

1 2

RC240 10K_0402_5%RC24 0 10K_0402_5%

1 2

RC241 10K_0402_5%RC24 1 10K_0402_5%

1 2

RC242 10K_0402_5%RC24 2 10K_0402_5%

1 2

RC243 10K_0402_5%RC24 3 10K_0402_5%

support LPC TPM

LPC_0 LPC_1 LPC_0 LPC_1

SIO

DOCK

MEC

21

22

23

24

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

CLKBUFF

DEBUG

SIO

MEC

TPM

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

CPU (2/12)

CPU (2/12)

CPU (2/12)

LA-A971P

LA-A971P

LA-A971P

1

RPC14

RPC14

1

2

3

4 5

2.2K_0804_8P4R_5%

2.2K_0804_8P4R_5%

+PCH_VCCACLKPLL

DOCK

DEBUG

1

+3.3V_ALW_PCH

8

7

6

12

RC33499_0402_ 1% RC33499_0402_ 1%

12

RC34499_0402_ 1% RC34499_0402_ 1%

+3.3V_RUN

12

RN32.2K_04 02_5% RN32.2K_0402_5%

12

RN42.2K_04 02_5% RN42.2K_0402_5%

RC693.01K_0402_1% RC6 93.01K_0 402_1%

0.1

0.1

0.1

7 48Wednesday, March 19, 2014

7 48Wednesday, March 19, 2014

7 48Wednesday, March 19, 2014

Page 8

5

BDW_ULT_DDR3L

D D

DDR_A_D[0..63]<18>

C C

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

UC1C

UC1C

AH63

SA_DQ0

AH62

SA_DQ1

AK63

SA_DQ2

AK62

SA_DQ3

AH61

SA_DQ4

AH60

SA_DQ5

AK61

SA_DQ6

AK60

SA_DQ7

AM63

SA_DQ8

AM62

SA_DQ9

AP63

SA_DQ10

AP62

SA_DQ11

AM61

SA_DQ12

AM60

SA_DQ13

AP61

SA_DQ14

AP60

SA_DQ15

AP58

SA_DQ16

AR58

SA_DQ17

AM57

SA_DQ18

AK57

SA_DQ19

AL58

SA_DQ20

AK58

SA_DQ21

AR57

SA_DQ22

AN57

SA_DQ23

AP55

SA_DQ24

AR55

SA_DQ25

AM54

SA_DQ26

AK54

SA_DQ27

AL55

SA_DQ28

AK55

SA_DQ29

AR54

SA_DQ30

AN54

SA_DQ31

AY58

SA_DQ32

AW58

SA_DQ33

AY56

SA_DQ34

AW56

SA_DQ35

AV58

SA_DQ36

AU58

SA_DQ37

AV56

SA_DQ38

AU56

SA_DQ39

AY54

SA_DQ40

AW54

SA_DQ41

AY52

SA_DQ42

AW52

SA_DQ43

AV54

SA_DQ44

AU54

SA_DQ45

AV52

SA_DQ46

AU52

SA_DQ47

AK40

SA_DQ48

AK42

SA_DQ49

AM43

SA_DQ50

AM45

SA_DQ51

AK45

SA_DQ52

AK43

SA_DQ53

AM40

SA_DQ54

AM42

SA_DQ55

AM46

SA_DQ56

AK46

SA_DQ57

AM49

SA_DQ58

AK49

SA_DQ59

AM48

SA_DQ60

AK48

SA_DQ61

AM51

SA_DQ62

AK51

SA_DQ63

BDW_ULT_DDR3L

DDR CHANNEL A

DDR CHANNEL A

4

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

3

UC1D

AU37

M_CLK_DDR#0

AV37

M_CLK_DDR0

AW36

M_CLK_DDR#1

AY36

M_CLK_DDR1

AU43

DDR_CKE0_DIMMA

AW43

DDR_CKE1_DIMMA DDR_CKE2_DIMMB

AY42

AY43

AP33

DDR_CS0_DIMMA#

AR32

DDR_CS1_DIMMA# DDR_C S2_DIMMB#

AP32

AY34

DDR_A_RAS#

AW34

DDR_A_WE#

AU34

DDR_A_CAS#

AU35

DDR_A_BS0

AV35

DDR_A_BS1

AY41

DDR_A_BS2

AU36

DDR_A_MA0

AY37

DDR_A_MA1

AR38

DDR_A_MA2

AP36

DDR_A_MA3

AU39

DDR_A_MA4

AR36

DDR_A_MA5

AV40

DDR_A_MA6

AW39

DDR_A_MA7

AY39

DDR_A_MA8

AU40

DDR_A_MA9

AP35

DDR_A_MA10

AW41

DDR_A_MA11

AU41

DDR_A_MA12

AR35

DDR_A_MA13

AV42

DDR_A_MA14

AU42

DDR_A_MA15

AJ61

DDR_A_DQS#0

AN62

DDR_A_DQS#1

AM58

DDR_A_DQS#2

AM55

DDR_A_DQS#3

AV57

DDR_A_DQS#4

AV53

DDR_A_DQS#5

AL43

DDR_A_DQS#6

AL48

DDR_A_DQS#7

AJ62

DDR_A_DQS0

AN61

DDR_A_DQS1

AN58

DDR_A_DQS2

AN55

DDR_A_DQS3

AW57

DDR_A_DQS4

AW53

DDR_A_DQS5

AL42

DDR_A_DQS6

AL49

DDR_A_DQS7

AP49

AR51

AP51

M_CLK_DDR#0 <18>

M_CLK_DDR0 <18>

M_CLK_DDR#1 <18>

M_CLK_DDR1 <18>

DDR_CKE0_DIMMA <18>

DDR_CKE1_DIMMA <18>

DDR_CS0_DIMMA# <18>

DDR_CS1_DIMMA# <18>

DDR_A_RAS# <18>

DDR_A_WE# <18>

DDR_A_CAS# <18>

DDR_A_BS0 <18>

DDR_A_BS1 <18>

DDR_A_BS2 <18>

DDR_A_MA[0..15] <18>

DDR_A_DQS#[0..7] <18>

DDR_A_DQS[0..7] <18>

+SM_VREF_CA

+SM_VREF_DQ0

+SM_VREF_DQ1

DDR_B_D[0..63]<19>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1D

AY31

SB_DQ0

AW31

SB_DQ1

AY29

SB_DQ2

AW29

SB_DQ3

AV31

SB_DQ4

AU31

SB_DQ5

AV29

SB_DQ6

AU29

SB_DQ7

AY27

SB_DQ8

AW27

SB_DQ9

AY25

SB_DQ10

AW25

SB_DQ11

AV27

SB_DQ12

AU27

SB_DQ13

AV25

SB_DQ14

AU25

SB_DQ15

AM29

SB_DQ16

AK29

SB_DQ17

AL28

SB_DQ18

AK28

SB_DQ19

AR29

SB_DQ20

AN29

SB_DQ21

AR28

SB_DQ22

AP28

SB_DQ23

AN26

SB_DQ24

AR26

SB_DQ25

AR25

SB_DQ26

AP25

SB_DQ27

AK26

SB_DQ28

AM26

SB_DQ29

AK25

SB_DQ30

AL25

SB_DQ31

AY23

SB_DQ32

AW23

SB_DQ33

AY21

SB_DQ34

AW21

SB_DQ35

AV23

SB_DQ36

AU23

SB_DQ37

AV21

SB_DQ38

AU21

SB_DQ39

AY19

SB_DQ40

AW19

SB_DQ41

AY17

SB_DQ42

AW17

SB_DQ43

AV19

SB_DQ44

AU19

SB_DQ45

AV17

SB_DQ46

AU17

SB_DQ47

AR21

SB_DQ48

AR22

SB_DQ49

AL21

SB_DQ50

AM22

SB_DQ51

AN22

SB_DQ52

AP21

SB_DQ53

AK21

SB_DQ54

AK22

SB_DQ55

AN20

SB_DQ56

AR20

SB_DQ57

AK18

SB_DQ58

AL18

SB_DQ59

AK20

SB_DQ60

AM20

SB_DQ61

AR18

SB_DQ62

AP18

SB_DQ63

2

BDW_ULT_DDR3L

BDW_ULT_DDR3L

DDR CHANNEL B

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

M_CLK_DDR#2

M_CLK_DDR2

M_CLK_DDR#3

M_CLK_DDR3

DDR_CKE3_DIMMB

DDR_CS3_DIMMB#

DDR_B_RAS#

DDR_B_WE#

DDR_B_CAS#

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

1

M_CLK_DDR#2 <19>

M_CLK_DDR2 <19>

M_CLK_DDR#3 <19>

M_CLK_DDR3 <19>

DDR_CKE2_DIMMB <19>

DDR_CKE3_DIMMB <19>

DDR_CS2_DIMMB# <19>

DDR_CS3_DIMMB# <19>

DDR_B_RAS# <19>

DDR_B_WE# <19>

DDR_B_CAS# <19>

DDR_B_BS0 <19>

DDR_B_BS1 <19>

DDR_B_BS2 <19>

DDR_B_MA[0..15] <19>

DDR_B_DQS#[0..7] <19>

DDR_B_DQS[0..7] <19>

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

3 OF 19

3 OF 19

A A

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

4 OF 19

4 OF 19

DELL CONFIDENTIAL/PROPRIETARY

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (3/12)

CPU (3/12)

CPU (3/12)

LA-A971P

LA-A971P

LA-A971P

1

8 48Wednesday, March 19, 2014

8 48Wednesday, March 19, 2014

8 48Wednesday, March 19, 2014

0.1

0.1

0.1

Page 9

5

+3.3V_ALW_PCH

1 2

ME_SUS_PWR_ACK

RC79 10K_0402_5%RC 79 10K_0402_5%

1 2

SUSACK#

RC81 10K_0402_5%RC 81 10K_0402_5%

1 2

SUS_STAT#/LPCPD#

+PCH_VCCDSW3_3

D D

C C

B B

A A

RC82@ 10K_04 02_5%RC82@ 1 0K_0402_5 %

RPC1

RPC1

4 5

PCH_PCIE_WAKE#

3

6

2

7

1

8

10K_8P4R_5 %

10K_8P4R_5 %

1 2

PM_LANPHY_ENABLE

RC92 10K_ 0402_5%@ RC92 10K _0402_5%@

1 2

PCH_RSMRST#_Q

RC91 47K_0402_5%RC 91 47K_0402_5%

+3.3V_RUN

1 2

RC95@ 8.2K_0 402_5%RC95@ 8 .2K_0402_ 5%

+1.05V_VCCST

CAD Note:

Avoid stub in the PWRGD path

while placing resistors RC123

DDR3 COMPENSATION SIGNALS

CAD Note:

Trace width=12~15 mil, Spcing=20 mils

Max trace length= 500 mil

ME_RESET#

PCH_JTAG_TDO<6>

PCH_JTAG_TDI

PCH_JTAG_TDI<6>

RUNPWROK<35,36>

1 2

H_CATERR#

RC114@ 49.9_ 0402_1%RC11 4@ 49.9_040 2_1%

1 2

H_PROCHOT#

RC116 6 2_0402_5 %RC116 62_04 02_5%

H_PROCHOT#

1

@EMC@

@EMC@

CC20

CC20

22P_0402_ 50V8J

22P_0402_ 50V8J

2

EMI request add

H_CPUPWRGD

100P_0402_50V8J

100P_0402_50V8J

10K_0402_5%

10K_0402_5%

@EMC@

@EMC@

12

CC83

CC83

RC123

RC123

1

2

12

RC130200_ 0402_1% RC130200_0402_ 1%

12

RC131121_040 2_1% RC13112 1_0402_1 %

12

RC132100_ 0402_1% RC132100_0402_ 1%

5

RC98 0_0 402_5%

RC98 0_0 402_5%

CXDP@

CXDP@

RC99 0_0 402_5%

RC99 0_0 402_5%

CXDP@

CXDP@

PCH_JTAG_TMS<6>

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

0.1U_0402_2 5V6

0.1U_0402_2 5V6

1 2

1 2

XDP_DBRESET#

RC80@ 8 .2K_0402_ 5%RC80@ 8. 2K_0402_5 %

AC_PRESENT <36,9>

PCH_BATLOW# <9>

PM_LANPHY_ENABLE <12,28>

+3.3V_RUN

CC17

CXDP@CC17

CXDP@

12

RUNPWROK

RUNPWROK

RUNPWROK

RUNPWROK

PCH_JTAG_TRST#<6>

PCH_JTAG_JTAGX<6>

UC7

UC7

14

VCC

2

TDO_XDP

1A

1

1OE

5

TDI_XDP_R

2A

4

2OE

9

PCH_JTAG_TMS

3A

10

3OE

12

TRST#_XDP

4A

13

4OE

74CBTLV3126BQ_ DHVQFN14_2P5X3

74CBTLV3126BQ_ DHVQFN14_2P5X3

reference Shark Bay ULT Validation Customer Debug Port

Implementation Requirement Rev 1.0

PCH_JTAG_TDO

PCH_JTAG_TCK

H_PROCHOT#<36,45,46>

12

ME_RESET#

CXDP@

CXDP@

RC121 56 _0402_5%RC121 56 _0402_5%

DDR3_DRAMRST#_CPU<18>

DDR_PG_CTRL<18>

4

1 2

RC77@ 0_040 2_5%RC77@ 0 _0402_5%

+3.3V_RUN

5

1

P

B

4

O

2

A

G

UC4@

UC4@

74AHC1G09GW_TSSO P5

74AHC1G09GW_TSSO P5

3

PLTRST_VMM2320#<2 2>

PLTRST_USH#<27>

PLTRST_MMI#<29>

PLTRST_LAN#<28>

3

1B

6

2B

8

3B

11

4B

7

GND

15

GND PAD

12

CPU_XDP_TRST#

RC1090_0402_5% CXDP@RC1090_0402_5% C XDP@

12

CPU_XDP_TCLK

RC1120_0402_5% CXDP@RC11 20_ 0402_5% CX DP@

12

TDO_XDP

RC115 @0_0402_5% RC115 @0_0402_5%

12

TDI_XDP_R

RC118 @0_0402_5% RC118 @0_0402_5%

12

CPU_XDP_TCLK

RC119 @0_0402_5% RC119 @0_0402_5%

H_CATERR#

PECI_EC

PECI_EC<36>

1 2

H_PROCHOT#_R

H_CPUPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

4

SYS_PWROK<36>

RESET_OUT#<15,36>

PCH_RSMRST#_Q<37>

ME_SUS_PWR_ACK<36>

SIO_PWRBTN#<36>

AC_PRESENT<36,9>

PCH_BATLOW#<9>

SIO_SLP_WLAN#<35>

CPU_XDP_TDO

CPU_XDP_TDI

CPU_XDP_TMS

CPU_XDP_TRST#

D61

K61

N62

K63

C61

AU60

AV60

AU61

AV15

AV61

SUSACK#<36>

3

+3.3V_RUN

5

1

SYS_RESET#

1 2

RC219@ 0_0402 _5%RC219@ 0_ 0402_5%

1 2

RC87@ 0_0402_5%RC87@ 0_0402_5%

1 2

RC88@ 0_0402_5%RC88@ 0_0402_5%

1 2

RC89@ 0_0402_5%RC89@ 0_0402_5%

UC1B

UC1B

PROC_DETECT

CATERR

PECI

PROCHOT

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

SM_PG_CNTL1

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

2 OF 19

2 OF 19

PCH_PLTRST#

TC7SH08FU_SSOP5~D

TC7SH08FU_SSOP5~D

SUSACK#

SYS_RESET#

SYS_PWROK

PM_APWROK_R

PCH_PLTRST#

PCH_RSMRST#_Q PCH_RTCRST#

ME_SUS_PWR_ACK

SIO_PWRBTN#

AC_PRESENT

PCH_BATLOW#

SIO_SLP_S0#

SIO_SLP_WLAN#

BDW_ULT_DDR3L

BDW_ULT_DDR3L

MISC

MISC

THERMAL

THERMAL

PWR

PWR

DDR3L

DDR3L

B

2

A

UC5

UC5

PCH_PLTRST#

UC1H

UC1H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

8 OF 19

8 OF 19

H_VCCST_PWRGD<15>

JTAG

JTAG

P

4

PCH_PLTRST#_EC

12

O

G

3

Fix Intel 7260 can not detect issue.

It will cause “floating” situation before 3V_RUN coming of AND gate

SYSTEM POWER MANAGEMENT

SYSTEM POWER MANAGEMENT

+1.05V_RUN

Place near JXDP1

RC102 1K_0402_5%

RC102 1K_0402_5%

CXDP@

CXDP@

H_CPUPWRGD

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

RC304

@RC304

@

100K_0402 _5%

100K_0402 _5%

BDW_ULT_DDR3L

BDW_ULT_DDR3L

0.1U_0402_25V6

0.1U_0402_25V6

0.1U_0402_25V6

0.1U_0402_25V6

@

@

@

@

12

12

CC18

CC18

CC19

CC19

RC5 need to close to JCPU1

1 2

1 2

RC103@ 1K_ 0402_5%RC10 3@ 1K_040 2_5%

J62

CPU_XDP_PRDY#

PRDY

K62

CPU_XDP_PREQ#

PREQ

E60

CPU_XDP_TCLK

E61

CPU_XDP_TMS

E59

CPU_XDP_TRST#

F63

CPU_XDP_TDI

F62

CPU_XDP_TDO

J60

XDP_OBS0_R

BPM#0

H60

XDP_OBS1_R

BPM#1

H61

XDP_OBS2_R

BPM#2

H62

XDP_OBS3_R

BPM#3

K59

XDP_OBS4_R

BPM#4

H63

XDP_OBS5_R

BPM#5

K60

XDP_OBS6_R

BPM#6

J61

XDP_OBS7_R

BPM#7

PCH_PLTRST#_EC <20,27,30,35,36>

PM_APWROK<36>

1.05V_M_PWRGD<43>

DSWVRMEN

DPWROK

WAKE

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

CFG0<13>

CFG1<13>

CFG2<13>

CFG3<13>

CFG4<13>

CFG5<13>

CFG6<13>

CFG7<13>

H_VCCST_PWRGD_XDP

CPU_PWR_DEBUG#<15>

DDR_XDP_WAN_SMBDAT<18,1 9,7>

DDR_XDP_WAN_SMBCLK<18,19,7>

PCH_JTAG_TCK<6>

AW7

AV5

AJ5

V5

AG4

AE6

AP5

AJ6

AT4

AL5

AP4

AJ7

CPU_XDP_PREQ#

CPU_XDP_PRDY#

XDP_OBS0_R

XDP_OBS1_R

SIO_PWRBTN#

SYS_PWROK

CPU_XDP_TCLK

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

T10 @PAD~D T10 @PAD~D

T11 @PAD~D T11 @PAD~D RC126

T12 @PAD~D T12 @PAD~D

T13 @PAD~D T13 @PAD~D

T14 @PAD~D T14 @PAD~D

T15 @PAD~D T15 @PAD~D

2

SIO_SLP_A#

1 2

PM_APWROK PM_APWROK_L

RC26 0_ 0402_5%@RC26 0 _0402_5%@

1 2

RC27 0_ 0402_5%@RC27 0 _0402_5%@

DSWODVREN

PCH_DPWROK

PCH_DPWROK <36>

PCH_PCIE_WAKE#

PCH_PCIE_WAKE# <35,36>

CLKRUN#

SUS_STAT#/LPCPD#

SUSCLK_R

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_S3#

SIO_SLP_A#

SIO_SLP_SUS#

SIO_SLP_LAN#

+3.3V_ALW_PCH

0.1U_0402_25V6

0.1U_0402_25V6

CC22@

CC22@

+1.05V_RUN

1K_0402_5%

1K_0402_5%

1 2

12

RC120

CXDP@

RC120

CXDP@

SYS_PWROK

13

19

21

23

25

31

37

47

49

51

53

55

57

59

CLKRUN# <10,35,36>

1 2

RC136 0_0402_5%@RC136 0_0402 _5%@

SIO_SLP_S5# <36>

T8 @PAD~DT8 @PAD~D

T9@PAD~DT9@PAD~D

SIO_SLP_S4# <36>

SIO_SLP_S3# <36>

SIO_SLP_A# <36>

SIO_SLP_SUS# <36>

SIO_SLP_LAN# <28,36>

JXDP1

JXDP1

1

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

OBSDATA_A09OBSDATA_C0

OBSDATA_A111OBSDATA_C1

GND4

OBSDATA_A215OBSDATA_C2

OBSDATA_A317OBSDATA_C3

GND6

OBSFN_B0

OBSFN_B1

GND8

OBSDATA_B027OBSDATA_D0

OBSDATA_B129OBSDATA_D1

GND10

OBSDATA_B233OBSDATA_D2

OBSDATA_B335OBSDATA_D3

GND12

PWRGOOD/HOOK039ITPCLK/HOOK4

HOOK141ITPCLK#/HOOK5

VCC_OBS_AB43VCC_OBS_CD

HOOK245RESET#/HOOK6

HOOK3

GND14

SDA

SCL

TCK1

TCK0

GND16

Place near JXDP1.47

+3.3V_ALW2

5

1

B

2

A

3

SUSCLK <30>

GND1

OBSFN_C0

OBSFN_C1

GND3

GND5

GND7

OBSFN_D0

OBSFN_D1

GND9

GND11

GND13

DBR#/HOOK7

GND15

TD0

TRST#

TDI

TMS

GND17

CONN@SAMTE_BSH-030-01-L -D-A

CONN@SAMTE_BSH-030-01-L -D-A

Place near JXDP1.48

XDP_DBRESET#

P

4

PM_APWROK_R

O

G

UC6

UC6

TC7SH08FU_SSOP5~D

TC7SH08FU_SSOP5~D

+1.05V_RUN

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

0.1U_0402_25V6

0.1U_0402_25V6

CC21

12

CXDP@CC21

CXDP@

+3.3V_ALW_PCH

+PCH_VCCDSW3_3

+PCH_VCCDSW3_3

PCH_RTCRST#<6>

POWER_SW#_MB<36,39>

CFG17

CFG16

CFG8

CFG9

CFG10

CFG11

CFG19

CFG18

CFG12

CFG13

CFG14

CFG15

XDP_RST#_R

XDP_DBRESET#

TDO_XDP

TRST#_XDP

PCH_JTAG_TDI

PCH_JTAG_TMS

RC113 1K_0402_5 %

RC113 1K_0402_5 %

CXDP@

CXDP@

DELL CONFIDENTIAL/PROPRIETARY

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Doc ument Number Rev

Size Doc ument Number Rev

Size Doc ument Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

DSWODVREN - ON DIE DSW VR ENABLE

HIGH = ENABLED (DEFAULT)

LOW = DISABLED

SIO_SLP_S3#

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_A#

SYS_RESET#

SIO_SLP_S0#

CFG17 <13>

CFG16 <13>

CFG8 <13>

CFG9 <13>

CFG10 <13>

CFG11 <13>

CFG19 <13>

CFG18 <13>

CFG12 <13>

CFG13 <13>

CFG14 <13>

CFG15 <13>

12

RC106 1K_0402_5 %

RC106 1K_0402_5 %

CXDP@

CXDP@

1 2

CFG3CFG3_R

TDO_XDP

51_0402_5 % RC 117

51_0402_5 %

XDP_DBRESET#

1K_0402_5 %

1K_0402_5 %

CPU_XDP_TMS

51_0402_5 %

51_0402_5 %

CPU_XDP_TDI

51_0402_5 %

51_0402_5 %

CPU_XDP_PREQ#

51_0402_5 %

51_0402_5 %

CPU_XDP_TDO

51_0402_5 %

51_0402_5 %

CPU_XDP_TCLK

51_0402_5 %

51_0402_5 %

CPU_XDP_TRST#

51_0402_5 %

51_0402_5 %

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

CPU (4/12)

CPU (4/12)

CPU (4/12)

1

+RTC_CELL

330K_0402_5%

330K_0402_5%

RC78

RC78

1 2

DSWODVREN

JAPS1

JAPS1

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

GND

20

GND

CONN@

CONN@

ACES_50506-01 841-P01

ACES_50506-01 841-P01

20130726 same as Goliad

PCH_PLTRST#_EC

+1.05V_RUN

12

@

@

RC117

+3.3V_RUN

12

RC122

RC122

+1.05V_RUN

@

@

12

RC124

RC124

@

@

12

RC125

RC125

@

@

12

RC126

12

RC127

RC127

12

RC128

RC128

@

@

12

RC129

RC129

LA-A971P

LA-A971P

LA-A971P

9 48Wednesday, Ma rch 19, 2014

9 48Wednesday, Ma rch 19, 2014

9 48Wednesday, Ma rch 19, 2014

1

0.1

0.1

0.1

Page 10

5

D D

DDI1_LANE_N0<25>

DDI1_LANE_P0<25>

DDI1_LANE_N1<25>

DDI1_LANE_P1<25>

DDI1_LANE_N2<25>

DDI1_LANE_P2<25>

DDI1_LANE_N3<25>

DDI1_LANE_P3<25>

DDI2_LANE_N0<24>

DDI2_LANE_P0<24>

DDI2_LANE_N1<24>

DDI2_LANE_P1<24>

DDI2_LANE_N2<24>

DDI2_LANE_P2<24>

DDI2_LANE_N3<24>

C C

+3.3V_RUN

RPC15

RPC15

7

8

10K_8P4R_5%

10K_8P4R_5%

1 2

RC139@ 100K_0402_5%RC139@ 100K_0402_5%

RC140@ 1K_0402_5%RC140@ 1K_0402_5%

B B

3456

2

1

12

SIO_RCIN# <12,36>

CLKRUN# <35,36,9>

USH_DET# <12,27>

IRQ_SERIRQ <12,35,36>

ENVDD_PCH

PCH_GPIO53

DDI2_LANE_P3<24>

4

UC1A

UC1A

C54

DDI1_TXN0

C55

DDI1_TXP0

B58

DDI1_TXN1

C58

DDI1_TXP1

B55

DDI1_TXN2

A55

DDI1_TXP2

A57

DDI1_TXN3

B57

DDI1_TXP3

C51

DDI2_TXN0

C50

DDI2_TXP0

C53

DDI2_TXN1

B54

DDI2_TXP1

C49

DDI2_TXN2

B50

DDI2_TXP2

A53

DDI2_TXN3

B53

DDI2_TXP3

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

1 OF 19

1 OF 19

UC1I

UC1I

B8

T16@ PAD~DT16@ PAD~D

PCH_GPIO52<12>

EDP_BIA_PWM

PANEL_BKLEN

ENVDD_PCH

DGPU_PWROK

HDD_FALL_INT

PCH_GPIO53

EDP_BKLCTL

A9

EDP_BKLEN

C6

EDP_VDDEN

U6

PIRQA/GPIO77

P4

PIRQB/GPIO78

N4

PIRQC/GPIO79

N2

PIRQD/GPIO80

AD4

PME

U7

GPIO55

L1

GPIO52

L3

GPIO54

R5

GPIO51

L4

GPIO53

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

9 OF 19

9 OF 19

eDP SIDEBAND

eDP SIDEBAND

PCIE

PCIE

EDP_BIA_PWM<23>

PANEL_BKLEN<23>

ENVDD_PCH<23,36>

CONTACTLESS_DET#<27,7>

DGPU_PWROK<6>

HDD_FALL_INT<12>

PCH_GPIO80<12>

TOUCHPAD_INTR#<12>

BDW_ULT_DDR3L

BDW_ULT_DDR3L

BDW_ULT_DDR3L

BDW_ULT_DDR3L

3

C45

EDP_CPU_LANE_N0

EDP_TXN0

B46

EDP_CPU_LANE_P0

EDP_TXP0

A47

EDP_CPU_LANE_N1

EDP_TXN1

B47

EDP_CPU_LANE_P1

EDP_TXP1

C47

EDP_TXN2

C46

EDP_TXP2

A49

EDP_TXN3

EDPDDI

EDPDDI

DISPLAY

DISPLAY

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

B49

A45

B45

D20

A43

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

EDP_CPU_AUX#

EDP_CPU_AUX

EDP_COMP

CPU_DPB_CTRLCLK

CPU_DPB_CTRLDAT

CPU_DPC_CTRLCLK

CPU_DPC_CTRLDAT

CPU_DPB_AUX#

CPU_DPC_AUX#

CPU_DPB_AUX

CPU_DPC_AUX

DPB_HPD

DPC_HPD

EDP_CPU_HPD

2

EDP_CPU_LANE_N0 <23>

EDP_CPU_LANE_P0 <23>

EDP_CPU_LANE_N1 <23>

EDP_CPU_LANE_P1 <23>

EDP_CPU_AUX# <23>

EDP_CPU_AUX <23>

CPU_DPB_CTRLCLK <25>

CPU_DPB_CTRLDAT <25>

CPU_DPC_CTRLCLK <24>

CPU_DPC_CTRLDAT <24>

CPU_DPB_AUX# <25>

CPU_DPC_AUX# <24>

CPU_DPB_AUX <25>

CPU_DPC_AUX <24>

DPB_HPD <25>

DPC_HPD <24>

EDP_CPU_HPD <23>

1

COMPENSATION PU FOR eDP

RPC2

RPC2

1

8

2

7

3

6

4 5

2.2K_0804_8P4R_5%

2.2K_0804_8P4R_5%

RPC20

RPC20

1

8

2

7

3

6

4 5

100K_0804_8P4R_5%

100K_0804_8P4R_5%

12

12

12

EDP_COMP

CAD Note:Trace width=20 mils ,Spacing=25mil,

Max length=100 mils.

CPU_DPB_CTRLDAT

CPU_DPB_CTRLCLK

CPU_DPC_CTRLCLK

CPU_DPC_CTRLDAT

CPU_DPB_AUX#

CPU_DPB_AUX

CPU_DPC_AUX

CPU_DPC_AUX#

EDP_CPU_HPD

DPB_HPD

+VCCIOA_OUT

RC13324.9_0402_1% RC13324.9_0402_1%

+3.3V_RUN

RC141100K_0402_5% RC14110 0K_0402_5%

RC142100K_0402_5% RC14210 0K_0402_5%

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (5/12)

CPU (5/12)

CPU (5/12)

LA-A971P

LA-A971P

LA-A971P

10 48Wednesday, March 19, 2014

10 48Wednesday, March 19, 2014

10 48Wednesday, March 19, 2014

1

0.1

0.1

0.1

Page 11

5

4

3

2

1

PCIE for UMA

D D

GPU

GPU

PCIE_PRX_WIGIGTX_N5

PCIE_PRX_WIGIGTX_P5

PCIE_PTX_WIGIGRX_N5

PCIE_PTX_WIGIGRX_P5

PCIE_PRX_GLANTX_N3

PCIE_PRX_GLANTX_P3

PCIE_PTX_GLANRX_N3

PCIE_PTX_GLANRX_P3

PCIE_PRX_WLANTX_N4

PCIE_PRX_WLANTX_P4

PCIE_PTX_WLANRX_N4

PCIE_PTX_WLANRX_P4

PCIE_PRX_MMITX_N1

PCIE_PRX_MMITX_P1

PCIE_PTX_MMIRX_N1

PCIE_PTX_MMIRX_P1

PCH_PCIE_RCOMP

PCIE6

M2 3042

(HCA & SATA-Cache)

WIGIG

M2 3042

(HCA & SATA-Cache)

WIGIG

NA

4

PCIE_PRX_WIGIGTX_N5<30>

WIGIG --->

C C

10/100/1G LAN --->

WLAN (Mini Card 2)--->

MMI -->

+PCH_AUSB3PLL

B B

PCB

PCIE1 PCIE4

G12 UMA

SD card

G12 Entry NA

G14 DSC

G14 UMA

G14D_En

G14U_En

A A

SD card

SD card

SD card

SD card

5

PCIE3PCIE2

NA LOM

NA

LOM

NA

LOM

NA

LOM

NA

LOM

NA

LOM

PCIE_PRX_WIGIGTX_P5<30>

PCIE_PTX_WIGIGRX_N5<30>

PCIE_PTX_WIGIGRX_P5<30>

PCIE_PRX_GLANTX_N3<28>

PCIE_PRX_GLANTX_P3<28>

PCIE_PTX_GLANRX_N3<28>

PCIE_PTX_GLANRX_P3<28>

PCIE_PRX_WLANTX_N4<30>

PCIE_PRX_WLANTX_P4<30>

PCIE_PTX_WLANRX_N4<30>

PCIE_PTX_WLANRX_P4<30>

PCIE_PRX_MMITX_N1<29>

PCIE_PRX_MMITX_P1<29>

PCIE_PTX_MMIRX_N1<29>

PCIE_PTX_MMIRX_P1<29>

USB3RN4<31>

USB3RP4<31>

USB3TN4<31>

USB3TP4<31>

RC149 3.01K_0402_1 %RC149 3.01K_0402_ 1%

1 2

PCIE5

WIGIG

WLAN

WIGIGSD card

WLAN

WLAN

WLAN

WIGIG

WLAN

WLAN

WIGIG

UC1K

UC1K

F10

PERN5_L0

E10

PERP5_L0

C23

PETN5_L0

C22

PETP5_L0

F8

PERN5_L1

E8

PERP5_L1

B23

PETN5_L1

A23

PETP5_L1

H10

PERN5_L2

G10

PERP5_L2

B21

PETN5_L2

C21

PETP5_L2

E6

PERN5_L3

F6

PERP5_L3

B22

PETN5_L3

A21

PETP5_L3

G11

PERN3

F11

PERP3

C29

PETN3

B30

PETP3

F13

PERN4

G13

PERP4

B29

PETN4

A29

PETP4

G17

PERN1/USB3RN3

F17

PERP1/USB3RP3

C30

PETN1/USB3TN3

C31

PETP1/USB3TP3

F15

PERN2/USB3RN4

G15

PERP2/USB3RP4

B31

PETN2/USB3TN4

A31

PETP2/USB3TP4

E15

RSVD

E13

RSVD

A27

PCIE_RCOMP

B27

PCIE_IREF

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

11 OF 19

11 OF 19

BDW_ULT_DDR3L

BDW_ULT_DDR3L

PCIE USB

PCIE USB

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB2N7

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

AN8

USBP0-

AM8

USBP0+

AR7

USBP1-

AT7

USBP1+

AR8

USBP2-

AP8

USBP2+

AR10

USBP3-

AT10

USBP3+

AM15

USBP4-

AL15

USBP4+

AM13

USBP5-

AN13

USBP5+

AP11

USBP6-

AN11

USBP6+

AR13

USBP7-

AP13

USBP7+

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

USBRBIAS

AJ11

AN10

RSVD

AM10

RSVD

AL3

USB_OC0#

AT1

USB_OC1#

AH2

AV3

USB_OC3#

USBP0- <31>

USBP0+ <31>

USBP1- <32>

USBP1+ <32>

USBP2- <30>

USBP2+ <30>

USBP3- <31>

USBP3+ <31>

USBP4- <23>

USBP4+ <23>

USBP5- <23>

USBP5+ <23>

USBP6- <27>

USBP6+ <27>

USBP7- <30>

USBP7+ <30>

USB3RN1 <31>

USB3RP1 <31>

USB3TN1 <31>

USB3TP1 <31>

USB3RN2 <32>

USB3RP2 <32>

USB3TN2 <32>

USB3TP2 <32>

USB_OC0# <31>

USB_OC1# <12,32>

USB_OC2# <12,31>

USB_OC3# <12>

2

-----> Ext Port 1 Charge

-----> Ext Port 3

-----> WLAN/BT

-----> Ext Port 2

-----> Touch

-----> Camera

-----> USH

-----> WWAN

-----> Ext USB3 Port 1 Charge

-----> Ext USB3 Port 3

-----> USB Port0 (JUSB1)

-----> USB Port1 (JUSB3)

-----> USB Port3 (JUSB2)

PCH_GPIO44<12>

KB_DET#<12,37>

USBRBIAS

USB_OC0#

12

22.6_0402_1%

22.6_0402_1%

RC152

RC152

PCH_SMB_ALERT#<7>

CAD NOTE:

Route single-end 50-ohms and max 500-mils length.

Avoid routing next to clock pins or under stitching capacitors.

Recommended minimum spacing to other signal traces is 15

mils.

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (6/12)

CPU (6/12)

CPU (6/12)

PCB

USB2 7

G12 UMA W WAN

G12 Entry

G14 DSC

G14 UMA

G14D_En

G14U_En

RPC19

RPC19

4 5

3

2

1

10K_8P4R_5%

10K_8P4R_5%

LA-A971P

LA-A971P

LA-A971P

NA

WWAN

WWAN

NA

NA

+3.3V_ALW_PCH

6

7

8

11 48Wednesday, March 19, 2014

11 48Wednesday, March 19, 2014

11 48Wednesday, March 19, 2014

1

0.1

0.1

0.1

Page 12

5

4

3

2

1

+PCH_VCCDSW3_3

+3.3V_RUN

D D

+3.3V_RUN

+3.3V_ALW_PCH

C C

B B

@

@

12

RC153 10K_ 0402_5%RC153 10K_0402_5 %

RC155 100K_0402_5%RC155 100K_0402_5%

RC156 100K_0402_5%RC156 100K_0402_5%

RC245 100K_0402_5%RC245 100K_0402_5%

RC174 100K_0402_5%RC174 100K_0402_5%

RC175 100K_0402_5%RC175 100K_0402_5%

RC171

LAN_WAKE#

12

MPHYP_PWR_EN

12

SIO_EXT_SCI#

1 2

RPC10

RPC10

4 5

3

2

1

10K_8P4R_5%

10K_8P4R_5%

RPC5

RPC5

4 5

3

2

1

10K_8P4R_5%

10K_8P4R_5%

RPC7

RPC7

4 5

3

2

1

10K_8P4R_5%

10K_8P4R_5%

6

7

SLATE_MODE

8

SIO_EXT_SMI#

6

PCH_GPIO9

7

MEDIACARD_RST#

8

MEDIACARD_IRQ#

6

7

8

PCH_GPIO57

12

PCH_GPIO59

12

3.3V_CAM_EN#

12

NFC_IRQ

12

MPHYP_PWR_EN

10K_0402_5%RC171

10K_0402_5%

TPM_PIRQ#

RC247 10K_0402_5%RC247 10K_0402_5%

PCH_NFC_RST for Goliad

USB_OC2# <11,31>

PCH_GPIO46 <12>

PCH_GPIO73 <7>

USB_OC3# <11>

SIO_EXT_WAKE# <12,36>

USB_OC1# <11,32>

+3.3V_RUN

12

1K_0402_5%

1K_0402_5%

PM_LANPHY_ENABLE<28,9>

RC176@

RC176@

SIO_EXT_WAKE#<12,36>

PCH_GPIO16<7>

TPM_PIRQ#<27>

LAN_WAKE#<28,36>

MEDIACARD_IRQ#<29>

@ PAD~D

@ PAD~D

TOUCH_PANEL_INTR#<23>

MPHYP_PWR_EN<38>

KB_DET#<11,37>

@ PAD~D

@ PAD~D

T21

T21

3.3V_CAM_EN#<23>

SIO_EXT_SMI#<36>

PCH_GPIO46<12>

mSATA_DEVSLP<30>

HDD_DEVSLP<20>

SIO_EXT_SCI#<36>

PCH_GPIO66

BDW_ULT_DDR3L

UC1J

UC1J

+3.3V_RUN

10K_0402_5%

10K_0402_5%

12

RC302@

RC302@

10K_0402_5%

10K_0402_5%

12

RC303

RC303

P1

BMBUSY/GPIO76

AU2

GPIO8

AM7

LAN_PHY_PWR_CTRL/GPIO12

AD6

GPIO15

Y1

GPIO16

T3

GPIO17

AD5

GPIO24

AN5

GPIO27

AD7

GPIO28

AN3

GPIO26

AG6

GPIO56

AP1

GPIO57

AL4

GPIO58

AT5

GPIO59

AK4

GPIO44

AB6

GPIO47

U4

GPIO48

Y3

GPIO49

P3

GPIO50

Y2

HSIOPC/GPIO71

AT3

GPIO13

AH4

GPIO14

AM4

GPIO25

AG5

GPIO45

AG3

GPIO46

AM3

GPIO9

AM2

GPIO10

P2

DEVSLP0/GPIO33

C4

SDIO_POWER_EN/GPIO70

L2

DEVSLP1/GPIO38

N5

DEVSLP2/GPIO39

V2

SPKR/GPIO81

BDW-ULT-DDR3L_BGA1168

BDW-ULT-DDR3L_BGA1168

10 OF 19

10 OF 19

DIMM_DET

PCH_GPIO76

SIO_EXT_WAKE# SIO_RCIN#

HOST_ALERT1_R_N

TPM_PIRQ#

LAN_WAKE#

NFC_IRQ

MEDIACARD_RST#

PCH_GPIO57

SLATE_MODE

PCH_GPIO59

PCH_GPIO44

PCH_GPIO44<11>

DIMM_DET

SPKR<21>

PCH_GPIO49

TOUCH_PANEL_INTR#

MPHYP_PWR_EN

KB_DET#

PCH_GPIO14

3.3V_CAM_EN#

SIO_EXT_SMI#

PCH_GPIO9

PCH_GPIO10

SIO_EXT_SCI#

SPKR

T22

T22

T27@ PAD~DT27@ PAD~D

BDW_ULT_DDR3L

GPIO

GPIO

+3.3V_ALW_PCH

1K_0402_5%

1K_0402_5%

12

RC179

RC179

SERIAL IO

SERIAL IO

HOST_ALERT1_R_N

CPU/

CPU/

MISC

MISC

THRMTRIP

RCIN/GPIO82

SERIRQ

PCH_OPI_RCOMP

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

RSVD

RSVD

+3.3V_RUN

D60

V4

T4

AW15

AF20

AB21

R6

L6

N6

L8

R7

L5

N7

K2

J1

K3

J2

G1

K4

G2

J3

J4