Page 1

5

ZZZ

ZZZ

0605 Change P/N for ZEJ00

DAZ@

DAZ@

PCB

PCB

DA60012D000

DA60012D000

PCB 125 LA-A791P REV0 M/B 3

D D

PCB 125 LA-A791P REV0 M/B 3

S1

S1

FRAME

FRAME

EC0MV000200

EC0MV000200

@

@

S4

S4

ZZZ1

ZZZ1

HDMI

HDMI

RO0000003HM

RO0000003HM

45@

45@

4

3

2

1

FRAME

FRAME

EC0MV000200

EC0MV000200

for GLONASS

@

@

C C

Compal Confidential

Schematics Document

ZEJ00

LA-A791P

B B

2013-05-27

REV:0.2

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

2012/11/09 2014/11/09

2012/11/09 2014/11/09

2012/11/09 2014/11/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

ZEJ00 -LA-A791P

ZEJ00 -LA-A791P

ZEJ00 -LA-A791P

1

1 28Thursday, August 08, 2013

1 28Thursday, August 08, 2013

1 28Thursday, August 08, 2013

0.2

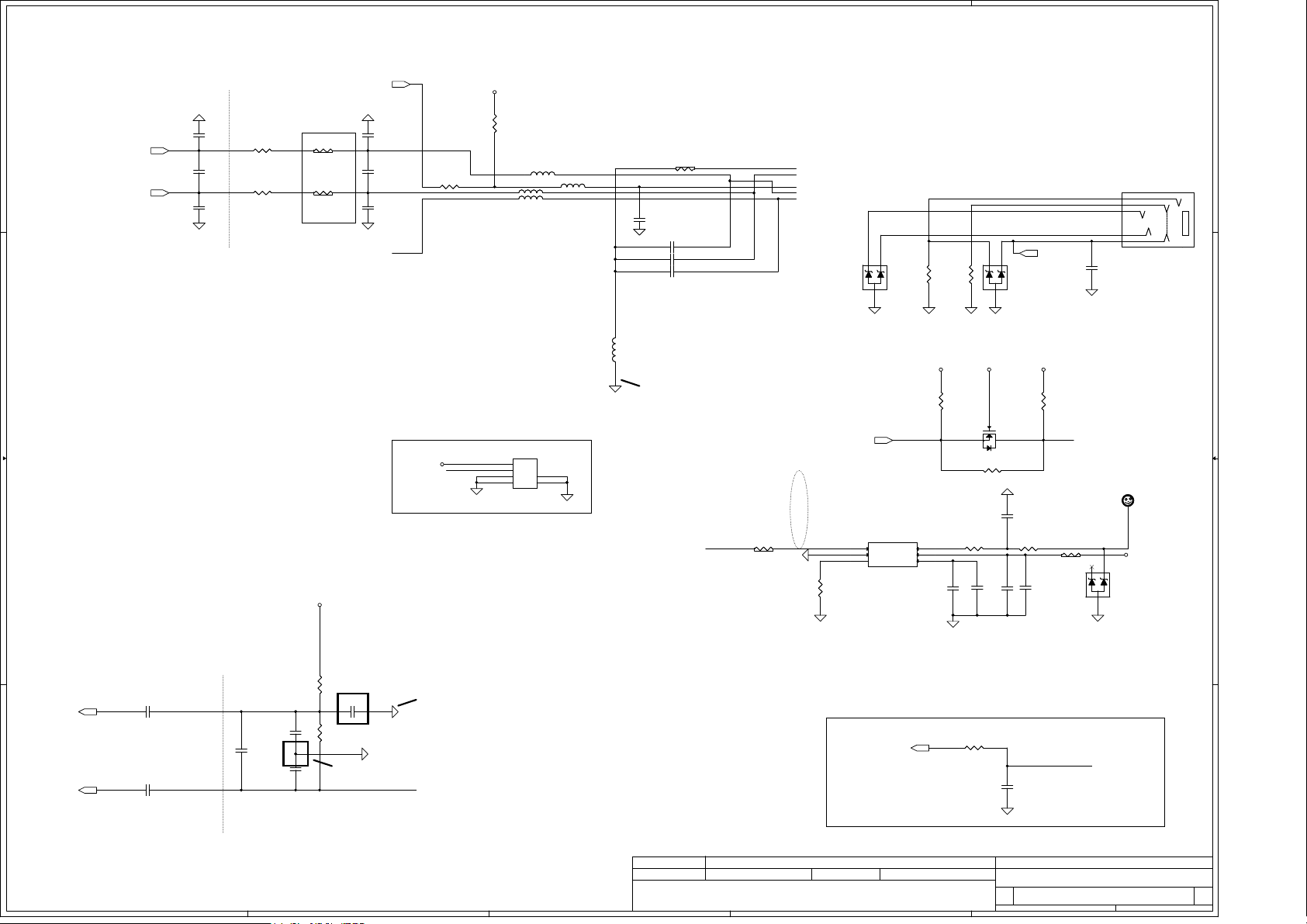

Page 2

5

4

3

2

1

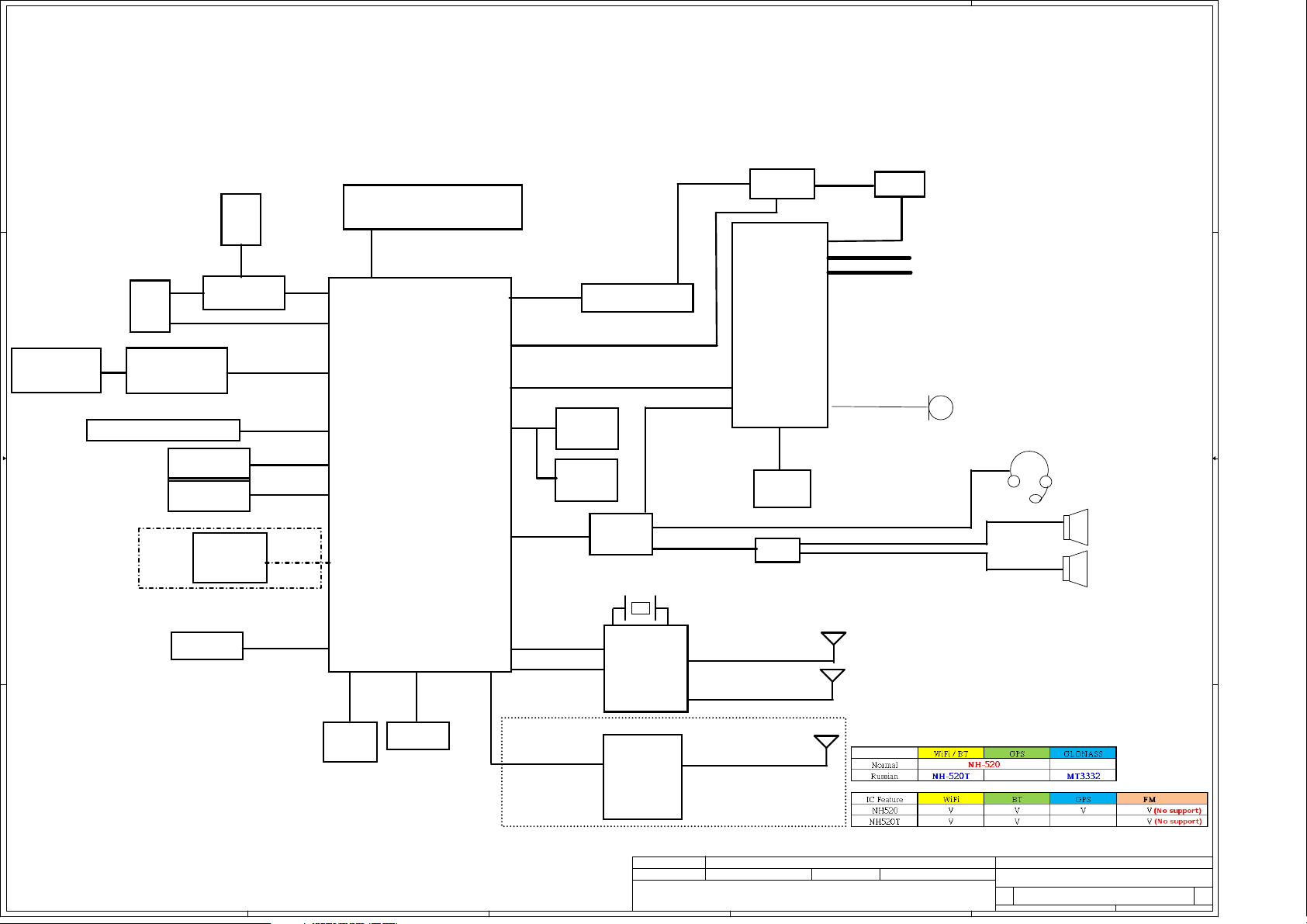

ZEJ00 block diagram

D D

Max. support VR AM size : 2GB.

R3L 1GB (4Gb X1 6 *2 Pcs)

HDMI

CONN.

P7

HDMI

LVDS

LCM

CONN.

P7

C C

S7

300B +

Vibrator CONN

P14

Touch Sensor

Board

CONN.

Button (Power o n/reset)

5M Camera

Front Camera

B B

Debug Port

A A

MT8193

P14

P15

P10

P10

Gyro+ G

se

nsor

MPU 6050

I2C, EINT

P11

PWM

P12

P7

I2C,

EINT

KCOL & KROW

MIPI,I2C

YUV,I2C

I2

C, EINT

JTAG

UART1

UART2

UART4

DD

External Memory Interface

RGB

MT8389W/MT8125

C

ortex-A7

1.2GHz Quad-Core

MSDC0 MS

eMMC

8G/16G

DC1

micro SD

P13

P17

P6

GPIO POUT

PCM, UART3, EINT

P4

,P5

Russian Sku

USB 2.0

P Sensor

P Sensor

Co

GPIO

BSI

MSDC3

UART1, EINT

micro USB,OGT

I2S, SPI, EINT, I2C

P8

nn

P8

Audio S/W

26

NH520T/NH520*

WIFI

BT4.0

GPS*

MT3332

GL

P17

HP R/L

P12

MHz

P9

ONASS

P21

switching

Charger

I2C

MT

6320

PMIC

AUDIO

LDO OUTPUT

BUCK OUTPUT

CHARGER

P23~P25

SIM Card

P18

AMP

P12

WIFI/BT

S

GP

GPS

MIC

Battery

P16

combo JACK

P22 P22

Battery Input

LDO Output

BUCK Output

D

MIC

Speaker

HP+MIC jack

P8

Speaker R

P16

Speaker L

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

5

4

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

2013/11/032012/11/03

2013/11/032012/11/03

2013/11/032012/11/03

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Block Diagram

Block Diagram

Block Diagram

ZEJ00 -LA-A791P

ZEJ00 -LA-A791P

ZEJ00 -LA-A791P

1

2 28Thursday, August 08, 2013

2 28Thursday, August 08, 2013

2 28Thursday, August 08, 2013

0.2

of

of

of

Page 3

5

D D

4

3

2

1

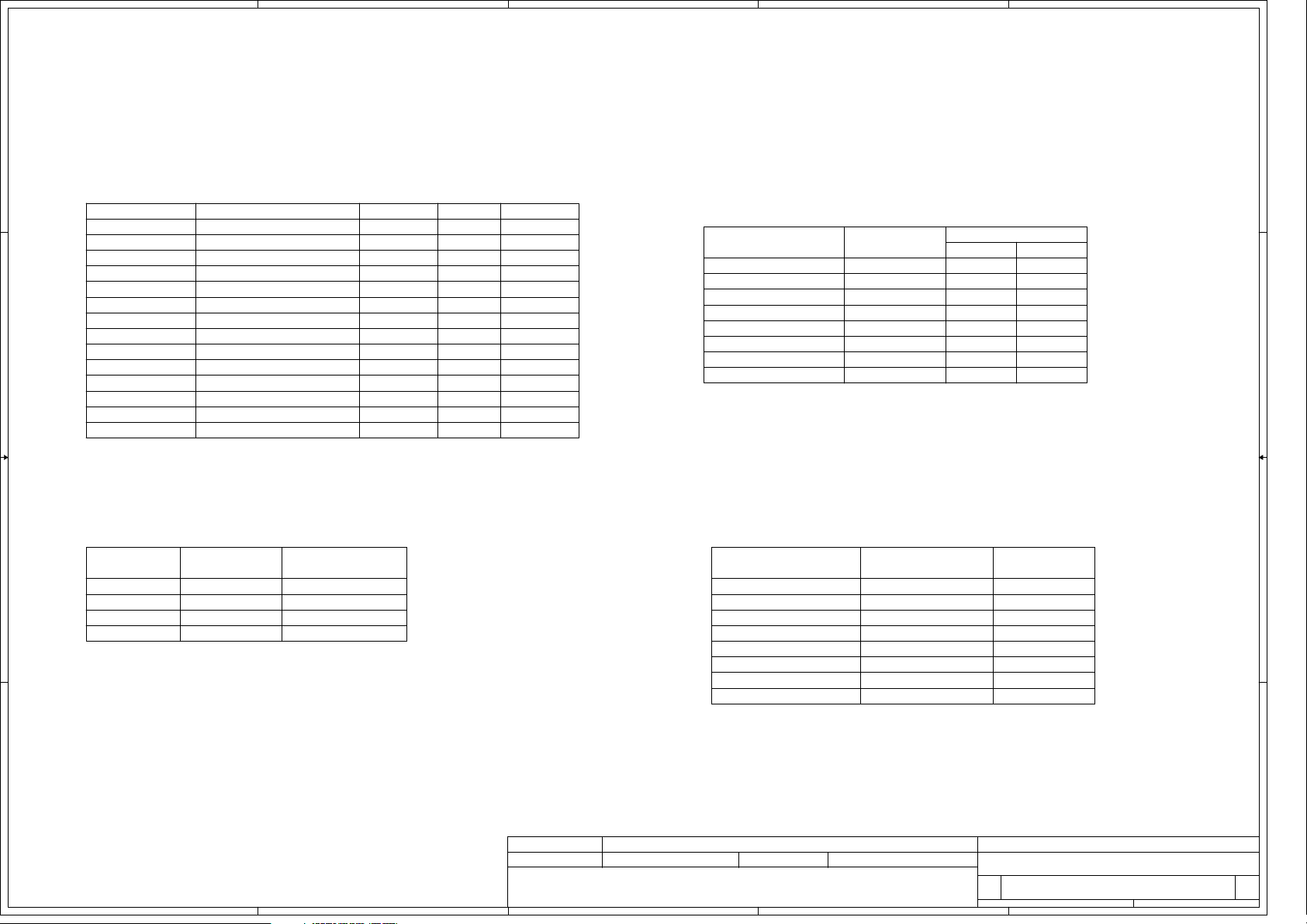

Voltage Rails

MT6320 Power Plane

VCORE_PMU

VPROC_PMU V

VTCXO_1_PMU

VCAMA_PMU

VSRAM_PMU

VDD28_6583

VGP2_PMU

C C

VEMC_3V3_PMU

VMCH_PMU

VGP5_PMU

DDR3VCCIO LDO output for DDR3L 1.35V ON Gating by SW

VDD18_6583 LDO output used for 1.8V IO 1.8V ON Gating by SW

VRF18_PMU L

Function Power Level

VCORE switching output

PROC switching output

LDO output for TCXO

LDO output for camaera analog

LDO output used for 1.2V SRAM

LDO output used for 2.8V IO

LDO output for camaera 1.8V 1.8V

LDO output for eMMC&P-sensor

LDO output for SD card

LDO output for Touch panel

DO output for RF_MT6167 1.8V ON Gating by SW

0.75 ~ 1.3 ON

0.75 ~ 1.3

2.8V

2.8V

1.2V

2.8V

3.3V

3.3V

2.8V

IDLE Sleep mode

Low voltage

ON

ON

ON

ON

ON

ON

ON

ON

ON

Low voltage

OFF

Gating by SW

Low voltage

Gating by SW

Gating by SW

Gating by SW

Gating by SW

Gating by SW

Gating by SW

I2C address

Device

Gyro (MPU-6050)

G-sensor (MPU-6050)

Touch screen (S7300B)

Address(7 bit)

0x68

0x68

0x20 0x40

0x21 0x43Camera 0.3M

Camera 5M

0x36 0x6C 0x6D

PMIC

Charger

0x6B 0xD6 0xD7

Battery 0x55 0xAA 0xAB

Address(8bit)

ReadWrite

0xD0

0xD1

0xD0 0xD1

0x41

0x42

Main board ID

B B

MB_ID0

0

0

1

1 1

A A

5

MB_ID1

0

1

0

EVT

DVT

PVT

MP

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

BOM structure

ame

N

3G@

WIFI_ONLY@

DAZ@

EMC@ f

NH520@

NH520_EMC@

GLONASS@

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Function

3G only

WIFI ONLY

PCB

or EMC request

AW-NH520

GPS EMC

MT3332

2013/11/032012/11/03

2013/11/032012/11/03

2013/11/032012/11/03

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

ZEJ00 -LA-A791P

ZEJ00 -LA-A791P

ZEJ00 -LA-A791P

3 28Thursday, August 0 8, 2013

3 28Thursday, August 0 8, 2013

3 28Thursday, August 0 8, 2013

1

0.2

Page 4

5

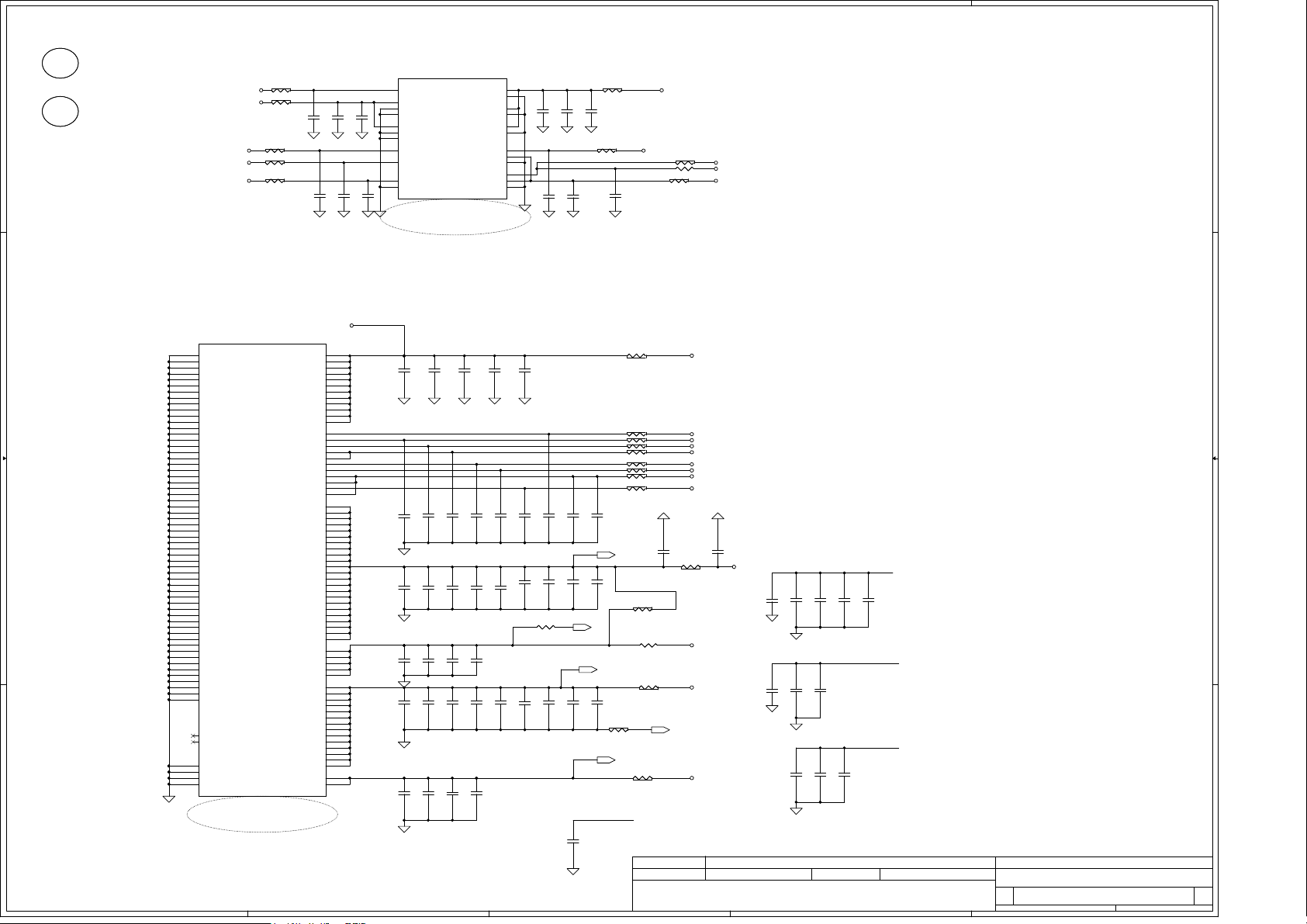

U201

U201

3G@

3G@

SA00006SG00

SA00006SG00

S IC MT8389WK/A 1.2G FCCSP 515P CPU

S IC MT8389WK/A 1.2G FCCSP 515P CPU

U201

U201

WIFI_ONLY@

WIFI_ONLY@

SA00006S510

D D

C C

B B

A A

SA00006S510

S IC MT8389WK/A 1.2G FCCSP 515P CPU

S IC MT8389WK/A 1.2G FCCSP 515P CPU

C5

C8

C21

C24

D7

D9

D11

D18

D20

D22

J6

J14

K10

K11

K12

K16

K17

K18

L24

P11

P12

P13

P14

P15

P16

R10

R11

R13

R14

R16

R18

R20

T8

T9

T11

T13

T14

T16

T18

T20

U8

U11

U16

U18

V6

V7

V8

V11

V16

V18

V19

W11

W16

W19

W24

AA6

AD20

AD24

AB11

AD11

A1

A29

AJ1

AJ29

5

VTCXO_1_PMU

VDD18_6583

VDD18_6583

U201B

U201B

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VPROC_FB

GND_VPROC_FB

NC

NC

NC

NC

MT8389E1_PCDDR3

MT8389E1_PCDDR3

@

@

0_0402_5% -22mil

0_0402_5% -22mil

VA_PMU

0_0402_5% -22mil

0_0402_5% -22mil

0_0402_5% -22mil

0_0402_5% -22mil

1 2

1 2

0_0402_5% -22mil

0_0402_5% -22mil

R1635

R1635

1 2

R1636

R1636

1 2

0_0402_5% -22mil

0_0402_5% -22mil

R1637

R1637

1 2

VDD18_6583

8125 footprint

R1632

R1632

R1633

R1633

DVDD18_NML1

DVDD28_NML2

DVDD18_NML3

DVDD18_NML4

DVDD18_MC12

C1607

C1607

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

C1610

C1610

DDR3VCCIO

DVDD18_EMI

DVDD18_EMI

DVDD18_EMI

DVDD18_EMI

DVDD18_EMI

DVDD18_EMI

DVDD18_EMI

DVDD18_EMI

DVDD18_EMI

DVDD18_EMI

DVDD18_EMI

DVDD18_EMI

DVDD18_MC0

DVDD33_MC1

DVDD33_MC2

DVDD28_BPI

DVDD28_BSI

DVDD18_BSI

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD

DVDD_GPU

DVDD_GPU

DVDD_GPU

DVDD_GPU

DVDD_GPU

DVDD_DVFS

DVDD_DVFS

DVDD_DVFS

DVDD_DVFS

DVDD_DVFS

DVDD_DVFS

DVDD_DVFS

DVDD_DVFS

DVDD_DVFS

DVDD_DVFS

DVDD_DVFS

DVDD_DVFS

DVDD_DVFS

DVDD_DVFS

DVDD_SRAM

DVDD_SRAM

1

2

1

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

C1608

C1608

C1618

C1618

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

H10

H19

H20

J10

J11

J17

J18

J19

J20

K13

K15

K20

R24

U1

Y1

AE25

AG23

AJ22

J29

Y24

AF1

F1

W8

N10

N11

N12

N13

N14

N15

N16

N17

P10

P17

P18

P19

P20

R17

R19

T17

T19

U17

U19

U20

V17

V20

W20

T10

U9

U10

V9

V10

R12

R15

T12

T15

U12

U13

U14

U15

V12

V13

V14

V15

W12

W15

W13

W14

4

U201F

U201F

AG17

DVDD18_MD

AH14

AVDD18_MD

AD16

1

1

C1609

C1609

2

1

C1621

C1621

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

DVDD

DVDD_GPU

DVDD_DVFS

DVDD_SRAM

4

AE17

AJ12

AD12

AE13

AH19

AJ11

M16

M15

MT8389E1_PCDDR3

MT8389E1_PCDDR3

@

@

C1665

C1665

2.2U_0402_6.3VM

2.2U_0402_6.3VM

C431

C431

1U_0402_6.3V6K

1U_0402_6.3V6K

C1651

C1651

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

C1649

C1649

C1644

C1644

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

C1642

C1642

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

AVSS18_MD

AVSS18_MD

AVDD18_AP

AVSS18_AP

AVSS18_AP

AVDD28_DAC

DVDD18_PLLGP

AVDD18_MEMPLL

AVSS18_MEMPLL

1

2

2

C1656

C1656

1

1

C1652

C1652

2

1

C1650

C1650

2

1

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

C1643

C1643

2

DVDD18_MIPITX

DVSS18_MIPITX

DVDD18_MIPIRX

DVSS18_MIPIRX

DVDD18_MIPIIO

DVSS18_MIPIIO

AVDD33_USB_P0

AVDD18_USB_P0

AVSS33_USB_P0

AVDD33_USB_P1

AVDD18_USB_P1

AVSS33_USB_P1

8125 footprint

1

C1662

C1662

C1661

C1661

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

1

C1658

C1658

C1657

C1657

2

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

1

C1654

C1654

C1653

C1653

2

2

2

1

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

C453

C453

C436

C436

1

2

1

1

C1645

C1645

C1646

C1646

1U_0402_6.3V6K

1U_0402_6.3V6K

2

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

2

C448

C448

C447

C447

2

1

1U_0402_6.3V6K

1U_0402_6.3V6K

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

T3

T2

1

L7

C1637

C1637

C1638

C1638

M6

2

H1

K6

AB28

AD27

AB26

AF29

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

AC26

AE28

1

1

C1664

C1664

C1663

C1663

2

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

1

C1660

C1660

C1659

C1659

2

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

1

C1655

C1655

C434

C434

2

2

1

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

1

1

C1647

C1647

C1648

C1648

C446

C446

10U_0402_6.3V6M

10U_0402_6.3V6M

2

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

2

10U_0402_6.3V6M

10U_0402_6.3V6M

0.1U 10V +-10% X7R 0402

2

C1640

C1640

C1641

C1641

1

1U_0402_6.3V6K

1U_0402_6.3V6K

1.8V IO for DDR

1.2V IO for DDR2

1.5V IO for DDR3

1.35V IO for DDR3L : Default

1

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

1

C1667

C1667

C1670

C1670

2

2

2

1

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

C454

C454

C455

C455

1

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1 2

10U_0402_6.3V6M

10U_0402_6.3V6M

@

@

R1657 0_0402_5%

R1657 0_0402_5%

2

1

C450

C450

C449

C449

1

2

1U_0402_6.3V6K

1U_0402_6.3V6K

10U_0402_6.3V6M

10U_0402_6.3V6M

1

C1639

C1639

2

2

1

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

1

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

1

2

10U_0402_6.3V6M

10U_0402_6.3V6M

1

2

1 2

1

2

R1628

R1628

1 2

0_0402_5% -22mil

0_0402_5% -22mil

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

C1673

C1673

1

C1671

C1671

2

C457

C457

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

10U_0402_6.3V6M

10U_0402_6.3V6M

DVDD_GPU_R <23>

22UF 6.3V M X5R 0805 H1.25

22UF 6.3V M X5R 0805 H1.25

C451

C451

1 2

22UF 6.3V M X5R 0805 H1.25

22UF 6.3V M X5R 0805 H1.25

DVDD_SRAM

EMC@

EMC@

C1683

C1683

12P_0402_50V8

12P_0402_50V8

3

R1627

R1627

0_0402_5% -22mil

0_0402_5% -22mil

1

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

DVDD <23>

DVDD_DVFS <23>

R1660

R1660

0_0402_5% -22mil

0_0402_5% -22mil

DVDD_SRAM <23>

3

VDD18_6583

VUSB_PMU

0_0402_5% -22mil

0_0402_5% -22mil

1 2

R1652

R1652

1 2

R1653 0_0402_5% @R1653 0_0402_5% @

1 2

R1629 0_0402_5% -22milR1629 0_0402_5% -22mil

R1639

R1639

0_0805_5%

0_0805_5%

R16540_0402_5% -22mil R16540_0402_5% -22mil

R16400_0402_5% -22mil R16400_0402_5% -22mil

R16410_0402_5% -22mil R16410_0402_5% -22mil

R16450_0402_5% -22mil R16450_0402_5% -22mil

R16430_0402_5% -22mil R16430_0402_5% -22mil

R16580_0402_5% -22mil R16580_0402_5% -22mil

R16590_0402_5% -22mil R16590_0402_5% -22mil

R16440_0402_5% -22mil R16440_0402_5% -22mil

0704 ADD C1687 C1686 FOR RF

EMC@

EMC@

1

12P_0402_50V8

12P_0402_50V8

C1687

C1687

2

1 2

R1655

R1655

1 2

0_0402_5% -22mil

0_0402_5% -22mil

R1649 0_0603_5%

R1649 0_0603_5%

1 2

@

@

R1650

R1650

1 2

0_0805_5%

0_0805_5%

GND_DVDD_DVFS <23>

R1651

R1651

1 2

0_0603_5% -35mil

0_0603_5% -35mil

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

R1648

R1648

0_0805_5%

0_0805_5%

VUSB_PMU

VSIM1_PMU

VDD18_6583

VM_PMU

VEMC_1V8_PMU

VMC_PMU

VDD28_6583

VDD18_6583

VDD18_6583

VDD18_6583

VDD18_6583

VDD18_6583

1

12P_0402_50V8

12P_0402_50V8

C1686

C1686

2

33P 50V J NPO 0402

33P 50V J NPO 0402

VGPU_PMU

33P 50V J NPO 0402

33P 50V J NPO 0402

VPROC_PMU

VSRAM_PMU

EMC@

EMC@

VCORE_PMU

C1756

C1756

EMC@

EMC@

C1757

C1757

EMC@

EMC@

EMC@

EMC@

1

2

C1675

C1675

C1674

C1674

12P_0402_50V8

12P_0402_50V8

2

1

1

2

C1678

C1678

@

@

2

1

0.1U 10V X7R 0402_NC

0.1U 10V X7R 0402_NC

EMC@

EMC@

1

C1681

C1681

C1680

C1680

@

@

2

0.1U 10V X7R 0402_NC

0.1U 10V X7R 0402_NC

Compal Secret Data

Compal Secret Data

Compal Secret Data

1

C1676

C1676

@

@

2

0.1U 10V X7R 0402_NC

0.1U 10V X7R 0402_NC

0.1U 10V X7R 0402_NC

0.1U 10V X7R 0402_NC

EMC@

EMC@

1

C1679

C1679

12P_0402_50V8

12P_0402_50V8

2

1

C1682

C1682

12P_0402_50V8

12P_0402_50V8

2

0.1U 10V X7R 0402_NC

0.1U 10V X7R 0402_NC

Deciphered Date

Deciphered Date

Deciphered Date

2

DVDD

1

C1677

C1677

@

@

2

DVDD_GPU

DVDD_DVFS

1

@

@

2

2

1

@

@

2

0.1U 10V X7R 0402_NC

0.1U 10V X7R 0402_NC

1

Compal Electronics, Inc.

Compal Electronics, Inc.

2013/11/032012/11/03

2013/11/032012/11/03

2013/11/032012/11/03

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

MT8377 - Power

MT8377 - Power

MT8377 - Power

ZEJ00 -LA-A791P

ZEJ00 -LA-A791P

ZEJ00 -LA-A791P

1

4 28Thursday, August 08, 2013

4 28Thursday, August 08, 2013

4 28Thursday, August 08, 2013

0.2

of

of

of

Page 5

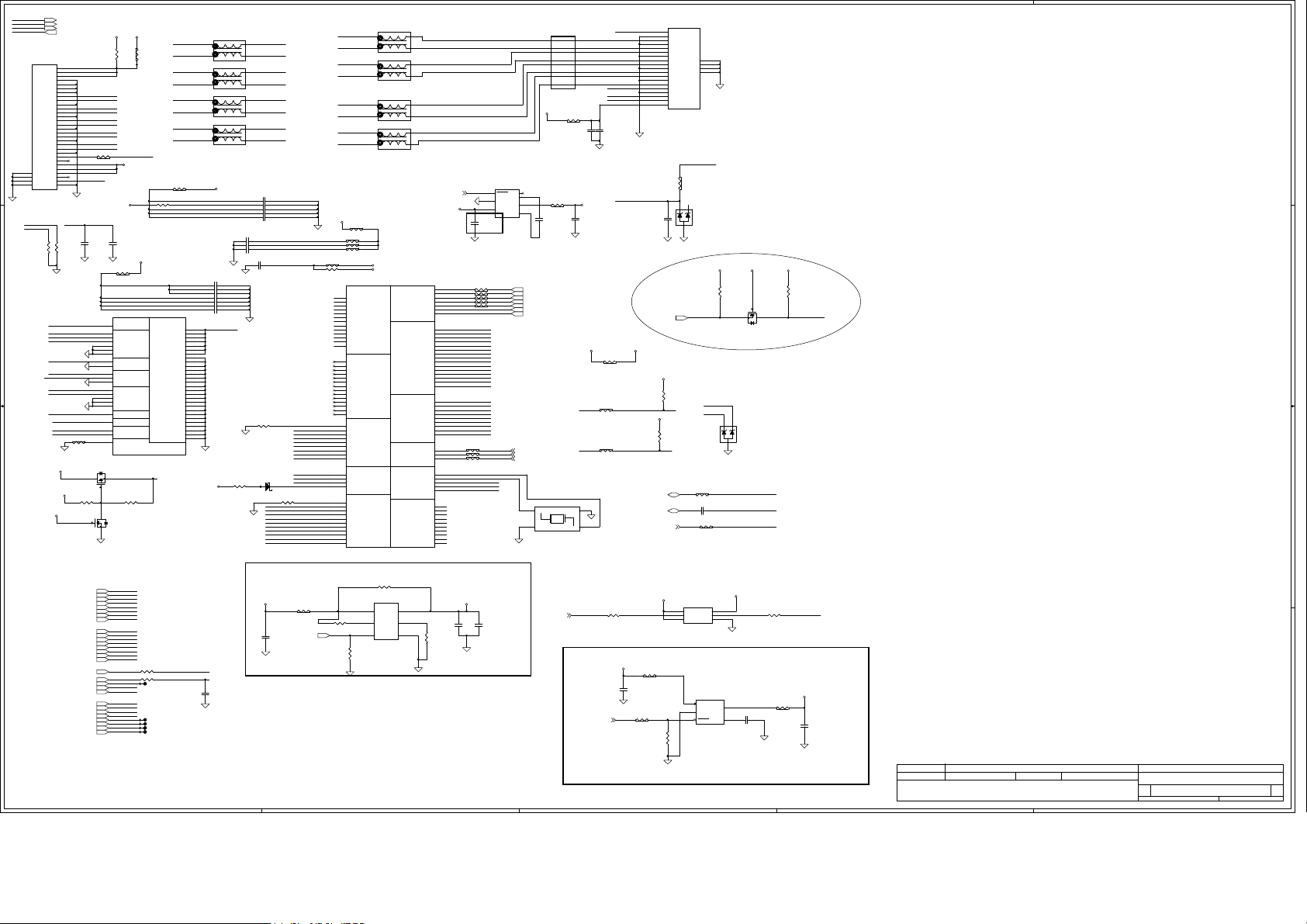

5

VDD18_ 6583

12

12

R207

R207

R208

R208

4.7K_0402_5%

4.7K_0402_5%

4.7K_0402_5%

D D

C C

B B

A A

SCL3<12,5>

SDA3<12,5>

C1754

C1754

18P_04 02_50V 8J

18P_04 02_50V 8J

EMC@

EMC@

SCL1<10,5>

SDA1<10,5>

SCL0<14,5>

SDA0<14,5>

4.7K_0402_5%

VDD18_ 6583

R217

R217

R218

R218

12

12

0531 Change BOM for MTK

4.7K_0402_5%

4.7K_0402_5%

4.7K_0402_5%

4.7K_0402_5%

SCL2

SDA2

VGP2_P MU

R210

R210

R212

R212

2

12

12

1

4.7K_0402_5%

4.7K_0402_5%

4.7K_0402_5%

4.7K_0402_5%

Power by CAM_IO

VDD18_ 6583

R220

R220

R219

R219

12

12

4.7K_0402_5%

4.7K_0402_5%

4.7K_0402_5%

4.7K_0402_5%

Power by CTP

<TESTMODE>

Connect to VIO18 : Enter Test Mode

Connect to GND : Normal mod e

<FSOURCE_P>

Connect to VGP6 (2v0) : w/i E FUSE program

Connect to GND : w/o EFUSE program

CLK1_B B_R2<7>

Close to MT6583

1 2

R222

R222

VBUS

4.99M +-1% 0 402

4.99M +-1% 0 402

1 2

R221

R221

1M_0402 _1%

1M_0402 _1%

USB11_D P_P<18>

USB11_D M_N<18>

5

R201

R201

5.11K +-1% 0402

5.11K +-1% 0402

12

90 Ohm

differential

0605 Change bom structure

1U 10V K X 5R 0402

1U 10V K X 5R 0402

Close to MT6583

0530 Update u201 pcb footprint for layout nc -p

RXD_BB IP

RXD_BB IN

RXD_BB QP

RXD_BB QN

WG_GG E_PA_V RAMP

TP1359 PAD @TP 1359P AD @

DCOC_F lag

POUT_1<8>

URXD4

URXD4<11>

UTXD4

UTXD4<11>

URXD3<9>

UTXD3<9>

URXD2

URXD2<11>

UTXD2

UTXD2<11>

URXD1

URXD1<21>

UTXD1

UTXD1<21>

U201C

SYSCLK1

USB11_D P

USB11_D M

GPIO_6 628_GP S_LNA_ EN<9>

MC3DA3<9>

MC3DA2<9>

U201C

AJ19

CLK26M1

AJ14

CLK26M2

P25

RTC32K_CK

L25

TESTMODE

D24

FSOURCE_P

R28

WATCHDOG

U24

JTCK

U28

JTDO

T25

JTRST_B

U29

JTDI

U25

JRTCK

V26

JTMS

AD28

USB_VRT

AE27

USB_VBUS

AC27

USB_DP_P0

AB27

USB_DM_P0

R26

IDDIG

AE29

USB_DP_P1

AD29

USB_DM_P1

AB25

CHD_DP_P0

AA25

CHD_DM_P0

B2

MRG_I2S_PCM_CLK

C2

MRG_I2S_PCM_RX

C3

MRG_I2S_PCM_SYNC

E2

MRG_I2S_PCM_TX

E1

DAI_RSTB

AG9

I2S_CLK

AH9

I2S_WS

AJ9

I2S_DATA_IN

AD8

I2S_DATA_OUT

AH11

AUXIN0

AH10

AUXIN1

AF12

AUX_XP

AE11

AUX_XM

AE12

AUX_YP

AG12

AUX_YM

AH12

REFP

AH13

REFN

MT8389E 1_PCDD R3

MT8389E 1_PCDD R3

@

@

8125 footprint

MC3DA1<9>

MC3DA0<9>

MC3CLK<9>

MC3CMD<9>

GPIO_6 628_PMU_ EN<9 >

LCM_RST _2V8

LCM_STB Y_2V8

EMC@

EMC@

1 2

R634 0_ 0402_5 %

R634 0_ 0402_5 %

RTC32K 1V8<23,7>

WATCHD OG_B<23>

MCU_JTCK<11>

MCU_JTDO<1 1>

MCU_JTRS T_B<11>

MCU_JTDI<11>

MCU_JRTC K< 11>

MCU_JTMS<1 1>

USB_DP<17>

USB_DM<17>

USB_ID<17 >

12

R1765 0_0402R1765 0_0402

12

R1766 0_0402R1766 0_0402

CHD_DP<23>

CHD_DM< 23>

DAICLK<9>

DAIPCMI N<9>

DAISYNC< 9>

DAIPCMO UT<9>

DAIRST<9>

I2S0_C K<7>

I2S0_W S<7>

I2S0_D AT_IN

I2S0_D AT_OUT<7>

TP1357 PAD @TP 1357P AD @

C213

C213

USB_VRT

2 1

TX_IP

TX_IN

TX_QP

TX_QN

RX_IP

RX_IN

RX_QP

RX_QN

TP1366 PAD @TP 1366P AD @

TP1369 PAD @TP 1369P AD @

4

U201A

U201A

AF18

UL_I_P1

AF17

UL_I_N1

AF19

UL_Q_P1

AF20

UL_Q_N1

AG13

UL_I_P2

AG14

UL_I_N2

AF14

UL_Q_P2

AF13

UL_Q_N2

AJ16

DL_I_P1

AH16

DL_I_N1

AH18

DL_Q_P1

AH17

DL_Q_N1

AG15

DL_I_P2

AG16

DL_I_N2

AF15

DL_Q_P2

AF16

DL_Q_N2

AG18

VBIAS

AG20

APC1

AG19

APC2

AH20

TXBPI1

AF21

BSI1C_CLK

AH23

BSI1C_DATA

MT8389E 1_PCDD R3

MT8389E 1_PCDD R3

@

@

8125 footprint

Y27

Y26

Y29

Y25

V24

W26

V25

UTXD1

UCTS1

URTS1

UTXD2

URXD1

URXD2

VDD28_NML2

VDD28_NML2

MSDC3_DAT3D3MSDC3_DAT2D4MSDC3_DAT1B4MSDC3_DAT0A4MSDC3_CLKC4MSDC3_CMDD5MSDC2_DAT3W5MSDC2_DAT2W2MSDC2_DAT1Y4MSDC2_DAT0V4MSDC2_CLKW3MSDC2_CMDW4MSDC1_DAT3T5MSDC1_DAT2V2MSDC1_DAT1T4MSDC1_DAT0V1MSDC1_CLKU2MSDC1_CMDU5MSDC0_DAT7

AJ24

BPI1_BUS0

AG26

BPI1_BUS1

AJ27

BPI1_BUS2

AH28

BPI1_BUS3

AF27

BPI1_BUS4

AG28

BPI1_BUS5

AF26

BPI1_BUS6

AJ25

BPI1_BUS7

AG27

BPI1_BUS8

AH26

BPI1_BUS9

AH24

BPI1_BUS10

DVDD28_BPI

DVDD28_BPI

AF24

BPI1_BUS11

AJ28

BPI1_BUS12

AH25

BPI1_BUS13

AE26

BPI1_BUS16

AH27

BPI1_BUS17

AE24

BPI1_BUS18

AF28

VM0

AH29

VM1

AE20

BSI1A_CS0

AH22

BSI1A_CLK

AH21

BSI1A_DATA0

AE21

BSI1A_DATA1

AG22

BSI1A_DATA2

AE23

BSI1B_CS0

AF23

BSI1B_CLK

AE22

BSI1B_DATA

DVDD28_BSI

DVDD28_BSI

Y28

W25

W28

F4

B3

AF9

AE9

D2

SCL0

SCL1

SCL2A2SCL3

SDA0

SDA1C1SDA2

UTXD4

UCTS2

URTS2

UTXD3

URXD4

URXD3

VDD28_NML2

VDD28_NML2

DVDD33_MC2

DVDD33_MC2

DVDD33_MC1

DVDD33_MC1

MSDC2_SDWPIV5MSDC2_INSI

Y3

4

3

VDD18_ 6583 VDD18_ 6583 VDD18 _6583 VDD18 _6583 VDD1 8_6583

R1520

R1520

R1522

R1522

GLONASS @

GLONASS @

@

@

10K_02 01_5%

10K_02 01_5%

100K_0 201_5%

1 2

MB_ID0 MB_ID1 GPIO_0 GPIO_1 GPI O_2

BPI1_B US0

BPI1_B US1

BPI1_B US2

TP1370PAD@ TP13 70P AD@

BPI1_B US4

TP1371PAD@ TP13 71P AD@

TP1372PAD@ TP13 72P AD@

BPI1_B US7

BPI1_B US8

BPI1_B US9

BPI1_B US10

BPI1_B US11

BPI1_B US12

BPI1_B US13

TP1390PAD@ TP13 90P AD@

TP1362PAD@ TP13 62P AD@

TP1361PAD@ TP13 61P AD@

VM0

VM1

BSI-A_E N

BSI-A_C K

BSI-A_D AT0

BSI-A_D AT1

BSI-A_D AT2

SCL0 <14,5>

SDA0 <14,5>

SCL1 <10,5>

SDA1 <10,5>

SCL2

SCL2 <7>

SDA2

SDA2 <7>

SCL3 <12,5>

SDA3 <12,5>

GPIO_S UB_CMPDN <10>

GPIO_1

GPIO_2

CABC_E NABLE1

GPIO_0

CABC_E NABLE0

MB_ID1

AJ6

AF5

AH5

AG5

V28

B1

V29

W27

AA29

AA26

SDA3

MSDC1_SDWPIU6MSDC1_INSI

Y2

AA28

PWM1

PWM2

PWM3

PWM4

PWRAP_SPI0_CSN

PWRAP_SPI0_CLK

PWRAP_SPI0_MI

PWRAP_SPI0_MO

PWRAP_EVENT

DAC_DAT_OUT

EINT10_AUXIN2

EINT11_AUXIN3

EINT16_AUXIN4

MSDC0_DAT0

MSDC0_CLK

MSDC0_CMD

MSDC0_RSTB

A28

E25

C27

SYSRSTB

EXT_CLK_EN

SRCLKENAI

SRCLKENA

SRCLKENA2

SRCVOLTEN

ADC_CLK

ADC_WS

ADC_DAT_IN

DAC_CLK

DAC_WS

SIM1_SCLK

SIM1_SIO

SIM1_SRST

SIM2_SCLK

SIM2_SIO

SIM2_SRST

LSCE0B

LSCE1B

LRSTB

LPCE0B

LPCE1B

DISP_PWM

EINT0

EINT1

EINT2

EINT3

EINT4

EINT5

EINT6

EINT7

EINT8

EINT9

LSCK

LSDA

LSA0

LPTE

R29

AJ21

E5

P26

AF22

P29

L29

M29

M26

M28

L28

K25

K26

K28

M27

L26

L27

N25

M25

P28

M24

N24

N28

Add TP1378 0808

T28

T27

T26

R27

R25

AE8

AH8

AG8

AJ8

AF8

AD10

AE10

AF10

AJ3

AJ5

AG4

MODE4/6 : MD1/2_GPS_SYNC

AH3

AE6

AH6

AH4

AF6

AH7

AE7

eMMC_RST <13 >

eMMC_CMD <1 3>

eMMC_CLK <1 3>

eMMC_DAT 0 <13>

eMMC_DAT 1 <13>

eMMC_DAT 2 <13>

eMMC_DAT 3 <13>

eMMC_DAT 4 <13>

eMMC_DAT 5 <13>

eMMC_DAT 6 <13>

eMMC_DAT 7 <13>

MC1INSI <17>

MC1CM <17>

MC1CK <17>

MC1DA0 <17 >

MC1DA1 <17 >

MC1DA2 <17 >

MC1DA3 <17 >

MB_ID0

SPI1_MI

SPI1_MO

SPI1_CLK

SPI1_CSN

VDD28_NML2

VDD28_NML2

MSDC0_DAT6

MSDC0_DAT5

MSDC0_DAT4

MSDC0_DAT3

MSDC0_DAT2

MSDC0_DAT1

B27

A27

A25

B25

B26

D26

D25

C26

1 2

0521 DEL X602

0509 Change

TP1358PAD@ TP13 58P AD@

SRCVOL TEN <23,7 >

TP1378PAD@ TP13 78P AD@

TP1360PAD@ TP13 60P AD@

AH4 NEED CHANGE

100K_0 201_5%

1 2

R1521

R1521

R1523

R1523

NH520@

NH520@

@

@

10K_02 01_5%

10K_02 01_5%

100K_0 201_5%

100K_0 201_5%

1 2

SYSRST_ B <11,15,23,7>

SRCLKE NAI <9>

SRCLKE NA <23,7 >

SRCLKE NA2 <23>

PWRAP _SPI0_ CSN <23 >

PWRAP _SPI0_ MI <23>

PWRAP _SPI0_ MO <23>

PWRAP _EVENT <2 3>

ADC_CL K <24>

ADC_W S <24>

ADC_DA T_IN <2 4>

DAC_CL K <24>

DAC_W S <24>

DAC_DA T_OUT <2 4>

SIM1_SC LK <24>

SIM1_SI O <24>

SIM1_SR ST <24>

EINT_GY <12>

GPIO_S W1 <12>

EINT_PMU <2 3>

EINT_CT P <14>

MT8389_ EINT_MT3 332 <21>

LED_Sig nal_EN <7>

EINT_66 28_BGF <9 >

EINT_66 28_WI FI <9>

EINT_HP <8 >

CHG_TEMP <2 2>

MT8193_ INT <7>

MT8389_ GPIO_G PS_EN <21>

DPI1_C K <7>

GPIO_6 628_GP S_SYNC <9>

LED_EN <7 >

GNSS_HRS T <21>

GPIO_HD MI_POW ER_EN <7>

MT8389_ GPIO_F RAME_S YNC < 21>

LCM_BL_ EN <7>

LCD_PW M <7>

1

2

5/22 gpio change for SW

TP1374PAD@ TP13 74P AD@

05/20 Change GPIO from SOC to PMIC

add GPIO PIN for GPIO_SW LED_Signal_EN 0522

MB_ID0 Change from AH4 to R25

5/22 add LED_Signal EN gpio pin for panel

0509 Change

0.1U 10V +-1 0% X7R 0 402

0.1U 10V +-1 0% X7R 0 402

3

1 2

1 2

EMC@

EMC@

0_0402 _5%

0_0402 _5%

1 2

R636

R636

C1736

@C1 736

@

33P 50V J NPO 040 2

33P 50V J NPO 040 2

LTE_RESET GPS_OFF#LTE_ON_OFF#

ADD C79 FOR EMI 8/1

5/10

1

C79

C79

EMC@

EMC@

2

10K_04 02_5%

10K_04 02_5%

GPIO_C TP_RST

EINT_CT P

0603 ADD PULL HIGH

0730 change bom structure for MTK recommend

R1524

R1524

@

@

100K_0 201_5%

100K_0 201_5%

R1525

R1525

@

@

100K_0 201_5%

100K_0 201_5%

PWRAP _SPI0_ CLK <23>

5/23 ADD FOR RF

GPIO_C TP_RST <14 >

VDD18_ 6583

R1869

@R1869

@

1 2

R1526

R1526

@

@

100K_0 201_5%

100K_0 201_5%

1 2

R1527

R1527

@

@

100K_0 201_5%

100K_0 201_5%

1 2

EVREF<6>

EINT0 : Gyro-Sensor

EINT1 : SIM

EINT2 : G-Sensor

EINT3 : PMU MT6320

EINT5 : CTP

EINT6 : MT3332

EINT8 : MT6628 BGF

EINT9 : MT6628 WiFi

EINT10 : HEADSET

UART1: Debug/MT3332

UART2:

UART3: MT6628

UART4: Debug

I2C0 : CTP

I2C1 : Sub Camera

I2C2 :

I2C3 : G/GYRO sensor

I2C4 (PMIC) : Charger IC

I2C5 (PMIC) :

I2C6 (PMIC) :

I2S :

MSDC0 : eMMC

MSDC1 : SD Card

MSDC2 : GPIO (2.8V)

MSDC3 : MT6628

R1872

@ R1872

@

10K_04 02_5%

10K_04 02_5%

1 2

R1528

R1528

@

@

100K_0 201_5%

100K_0 201_5%

1 2

R1529

R1529

@

@

100K_0 201_5%

100K_0 201_5%

1 2

Reserve

DDR3VC CIO

8.06K +-1% 0402

8.06K +-1% 0402

R209

R209

EVREF

8.06K +-1% 0402

8.06K +-1% 0402

R211

R211

12

12

2

ED[0..31]<6>

ED31

ED30

ED29

ED28

1

C205

C205

0.1U 10V +-1 0% X7R 0 402

0.1U 10V +-1 0% X7R 0 402

2

1

C206

C206

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

C207

C207

1U 10V K X 5R 0402

1U 10V K X 5R 0402

2 1

EA[0..14]<6>

ED27

ED26

ED25

ED24

ED23

ED22

ED21

ED20

ED19

ED18

ED17

ED16

ED15

ED14

ED13

ED12

ED11

ED10

ED9

ED8

ED7

ED6

ED5

ED4

ED3

ED2

ED1

ED0

EVREF

EBA2<6>

EBA1<6>

EBA0<6>

EA14

EA13

EA12

EA11

EA10

EA9

EA8

EA7

EA6

EA5

EA4

EA3

EA2

EA1

EA0

ERESET _<6>

1

C1611

C1611

EMC@

EMC@

12P_0402_50V8

12P_0402_50V8

2

RCP<10>

RCN<10>

RDP0<10>

RDN0<10>

RDP1<10>

RDN1<10>

CMDAT9<10>

CMDAT8<10>

CMVREF<10>

CMHREF<10>

CMDAT7<10>

CMDAT6<10>

CMDAT5<10>

CMDAT4<10>

CMDAT3<10>

CMDAT2<10>

MIPI_VR T

12

R203

R203

1.5K_04 02_1%

1.5K_04 02_1%

Close to MT6583

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

ANDTRADESECRETINFORMATION.THISSHEETMAYNOTBETRANSFEREDFROMTHECUSTODYOFTHECOMPETENTDIVISIONOFR&D

ANDTRADESECRETINFORMATION.THISSHEETMAYNOTBETRANSFEREDFROMTHECUSTODYOFTHECOMPETENTDIVISIONOFR&D

ANDTRADESECRETINFORMATION.THISSHEETMAYNOTBETRANSFEREDFROMTHECUSTODYOFTHECOMPETENTDIVISIONOFR&D

DEPARTMENTEXCEPTASAUTHORIZEDBY COMPALELECTRONICS,INC.NEITHERTHISSHEETNORTHEINFORMATIONITCONTAINS

DEPARTMENTEXCEPTASAUTHORIZEDBY COMPALELECTRONICS,INC.NEITHERTHISSHEETNORTHEINFORMATIONITCONTAINS

DEPARTMENTEXCEPTASAUTHORIZEDBY COMPALELECTRONICS,INC.NEITHERTHISSHEETNORTHEINFORMATIONITCONTAINS

MAYBEUSEDBY ORDISCLOSEDTOANYTHIRDPARTYWITHOUTPRIORWRITTENCONSENTOFCOMPALELECTRONICS,INC.

MAYBEUSEDBY ORDISCLOSEDTOANYTHIRDPARTYWITHOUTPRIORWRITTENCONSENTOFCOMPALELECTRONICS,INC.

MAYBEUSEDBY ORDISCLOSEDTOANYTHIRDPARTYWITHOUTPRIORWRITTENCONSENTOFCOMPALELECTRONICS,INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

C11

B12

B11

A12

C10

D10

C23

B17

A24

B18

C22

D19

B24

A17

B20

C20

D21

C19

B21

D23

A20

B22

H14

H18

C15

C12

B14

D12

D17

B13

F16

D14

F17

F18

C17

E18

C16

A13

A15

D13

E12

E11

E17

U201E

U201E

P8

TCP

R7

TCN

R3

TDP0

P3

TDN0

P4

TDP1

R4

TDN1

R1

TDP2

R2

TDN2

P7

TDP3

P6

TDN3

M4

RCP

N4

RCN

L1

RDP0

M1

RDN0

N3

RDP1

M3

RDN1

M2

RDP2

N2

RDN2

P2

RDP3

P1

RDN3

L4

RCP_A

K4

RCN_A

L3

RDP0_A

K3

RDN0_A

K2

RDP1_A

L2

RDN1_A

J4

RCP_B

H4

RCN_B

J3

RDP0_B

H3

RDN0_B

J2

RDP1_B

J1

RDN1_B

R6

VRT

MT8389E 1_PCDD R3

MT8389E 1_PCDD R3

@

@

Deciphered Date

Deciphered Date

Deciphered Date

U201D

U201D

RDQ31

C7

RDQ30

RDQ29

B5

RDQ28

RDQ27

A5

RDQ26

RDQ25

C6

RDQ24

D8

RDQ23

RDQ22

B7

RDQ21

RDQ20

D6

RDQ19

A9

RDQ18

B8

RDQ17

B9

RDQ16

RDQ15

RDQ14

RDQ13

RDQ12

RDQ11

RDQ10

RDQ9

RDQ8

RDQ7

RDQ6

RDQ5

RDQ4

RDQ3

RDQ2

RDQ1

RDQ0

VREF

VREF

RBA2

RBA1

RBA0

RA14

RA13

RA12

RA11

RA10

RA9

RA8

RA7

RA6

RA5

RA4

RA3

RA2

RA1

TN_MEMPLL

RA0

DDR3RSTB

MT8389E 1_PCDD R3

MT8389E 1_PCDD R3

@

@

8125 footprint

DPIVSYNC

DPIHSYNC

MIPI function only

CMMCLK

CMPCLK

CMFLASH

8125 footprint

RCS1_

RRAS_

RCAS_

RDQM0

RDQM1

RDQM2

RDQM3

RDQS0

RDQS1

RDQS2

RDQS3

RDQS0_

RDQS1_

RDQS2_

RDQS3_

RCLK0

RCLK0_

RCLK1

RCLK1_

NLD15

NLD14

NLD13

NLD12

NLD11

NLD10

NWEB

NCEB0

NCEB1

TP_MEMPLL

REXTDN

DPIDE

DPICK

DPIR0

DPIR1

DPIR2

DPIR3

DPIR4

DPIR5

DPIR6

DPIR7

DPIG0

DPIG1

DPIG2

DPIG3

DPIG4

DPIG5

DPIG6

DPIG7

DPIB0

DPIB1

DPIB2

DPIB3

DPIB4

DPIB5

DPIB6

DPIB7

CMRST

CMPDN

1

F12

RCS_

E14

E16

RWE_

C14

B15

E13

RCKE

A21

C18

A8

C9

F23

E20

E6

F9

E23

F20

F6

E9

H16

H15

H12

H13

G25

D28

F28

F25

E26

H25

J28

NLD9

E28

NLD8

C29

NLD7

G28

NLD6

H28

NLD5

B28

NLD4

G27

NLD3

H27

NLD2

G26

NLD1

C28

NLD0

B29

NRNB

D27

NCLE

H26

NALE

F29

J25

NREB

E29

H29

N19

N18

E15

AD1

AC2

AF4

AJ2

AE5

AG3

AB2

AD5

AF2

AD2

AC4

AG2

AC1

AB5

AH1

AD3

AD6

AA5

AH2

AA2

AC3

AC5

AG1

AB4

Y5

AE2

AD4

AA1

G3

H2

G4

F2

G2

2013/11/032012/11/03

2013/11/032012/11/03

2013/11/032012/11/03

RCS0_R <6>

RCS1_R <6>

/EWR <6>

/ERAS <6>

/ECAS <6>

ECKE <6>

EDQM0 <6>

EDQM1 <6>

EDQM2 <6>

EDQM3 <6>

EDQS0 <6>

EDQS1 <6>

EDQS2 <6>

EDQS3 <6>

/EDQS0 <6>

/EDQS1 <6>

/EDQS2 <6>

/EDQS3 <6>

EDCLK <6>

EDCLK_ B <6>

EDCLK1 <6>

EDCLK1 _B <6>

12

R204

R204

68 +-1% 04 02

68 +-1% 04 02

@

@

DPI_VS YNC <7>

DPI_HSYNC <7>

DPI_DE <7>

DPI_PC LK <7>

DPI_R0 <7>

DPI_R1 <7>

DPI_R2 <7>

DPI_R3 <7>

DPI_R4 <7>

DPI_R5 <7>

DPI_R6 <7>

DPI_R7 <7>

DPI_G0 <7>

DPI_G1 <7>

DPI_G2 <7>

DPI_G3 <7>

DPI_G4 <7>

DPI_G5 <7>

DPI_G6 <7>

DPI_G7 <7>

DPI_B0 <7>

DPI_B1 <7>

DPI_B2 <7>

DPI_B3 <7>

DPI_B4 <7>

DPI_B5 <7>

DPI_B6 <7>

DPI_B7 <7>

CMMCLK <10>

CMRST <10>

CMPCLK <10>

CMPDN <10 >

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

MT8377 - Baseband

MT8377 - Baseband

MT8377 - Baseband

Size D ocument Numb er Rev

Size D ocument Numb er Rev

Size D ocument Numb er Rev

D

D

D

ZEJ00 -LA-A791P

ZEJ00 -LA-A791P

1

ZEJ00 -LA-A791P

Date: Sheet

Date: Sheet

Date: Sheet

5 28Thursday, August 0 8, 2013

5 28Thursday, August 0 8, 2013

5 28Thursday, August 0 8, 2013

of

of

of

0.2

Page 6

5

4

3

2

1

ZZZ

ZZZ

1

C1669

C1669

2.2U_0402_6.3VM

2.2U_0402_6.3VM

2

1

C1668

C1668

2.2U_0402_6.3VM

2.2U_0402_6.3VM

2

EDCLK

100_0201_5%

100_0201_5%

R525

R525

1 2

EDCLK_B

EDCLK1

100_0201_5%

100_0201_5%

R526

R526

1 2

EDCLK1_B

NANYA-1G

U5

U5

U5

U5

RCS1_R

1K_0402_1%

1K_0402_1%

2013/11/032012/11/03

2013/11/032012/11/03

2013/11/032012/11/03

V

endor

@

@

SA00006UM10

SA00006UM10

256M16 NT5CC256M16BP-DI

256M16 NT5CC256M16BP-DI

@

@

SA00005AV50

SA00005AV50

256M16/1600 H5TC4G63AFR-PBA

256M16/1600 H5TC4G63AFR-PBA

12

R70

R70

@

@

TP01 PAD @TP01 PAD @

TP02 PAD @TP02 PAD @

TP03 PAD @TP03 PAD @

TP06 PAD @TP06 PAD @

TP13 PAD @TP13 PAD @

TP18 PAD @TP18 PAD @

NAN 256Mx16@

NAN 256Mx16@

DDR3L

DDR3L

X76521BOL01

X76521BOL01

ALT. GROUP PARTS NANYA 1G ZEJ00

ALT. GROUP PARTS NANYA 1G ZEJ00

ZZZ

ZZZ

HYN 256Mx16@

HYN 256Mx16@

DDR3L

DDR3L

X76521BOL02

X76521BOL02

ALT. GROUP PARTS HYNIX 1G ZEJ00

ALT. GROUP PARTS HYNIX 1G ZEJ00

0605 Change bom X76 Part number

X76 level

X76521BOL01

X76521BOL02HYNIX-1G

U5 Test Point

0606 DEL 4 PCS TEST POINT

U6 Test Point

TP19 PAD @TP19 PAD @

TP20 PAD @TP20 PAD @

TP21 PAD @TP21 PAD @

TP23 PAD @TP23 PAD @

TP34 PAD @TP34 PAD @

TP35 PAD @TP35 PAD @

TP36 PAD @TP36 PAD @

Title

Title

Title

Memory (DDR3)

Memory (DDR3)

Memory (DDR3)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

BOM structure

NAN 256Mx16@

HYN 256Mx16@

U6

U6

@

@

SA00006UM10

SA00006UM10

256M16 NT5CC256M16BP-DI

256M16 NT5CC256M16BP-DI

U6

U6

@

@

SA00005AV50

SA00005AV50

256M16/1600 H5TC4G63AFR-PBA

256M16/1600 H5TC4G63AFR-PBA

/ERAS

/ECAS

/EWR

EBA1

EA9

ED15

/ERAS

/ECAS

/EWR

EBA0

ED21

ED30

ED31

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

ZEJ00 -LA-A791P

ZEJ00 -LA-A791P

ZEJ00 -LA-A791P

1

6 28Thursday, August 08, 2013

6 28Thursday, August 08, 2013

6 28Thursday, August 08, 2013

of

of

of

0.2

U6

EA0

EA1

EA2

EA3

EA4

EA5

EA6

EA7

EA8

EA9

EA10

EA11

EA12

EA13

EA14

EBA0

EBA1

EBA2

Issued Date

Issued Date

Issued Date

U6

M8

VREFCA

H1

VREFDQ

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12

T3

A13

T7

A14

M7

A15/BA3

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK

K9

CKE/CKE0

K1

ODT/ODT0

L2

CS/CS0

J3

RAS

K3

CAS

L3

WE

F3

DQSL

C7

DQSU

E7

DML

D3

DMU

G3

DQSL

B7

DQSU

T2

RESET

L8

ZQ/ZQ0

J1

NC/ODT1

L1

NC/CS1

J9

NC/CE1

L9

NCZQ1

96-BALL

96-BALL

SDRAM DDR3

SDRAM DDR3

H5TC4G63MFR-PBA 96P

H5TC4G63MFR-PBA 96P

@

@

E3

DQL0

F7

DQL1

F2

DQL2

F8

DQL3

H3

DQL4

H8

DQL5

G2

DQL6

H7

DQL7

D7

DQU0

C3

DQU1

C8

DQU2

C2

DQU3

A7

DQU4

A2

DQU5

B8

DQU6

A3

DQU7

B2

VDD

D9

VDD

G7

VDD

K2

VDD

K8

VDD

N1

VDD

N9

VDD

R1

VDD

R9

VDD

A1

VDDQ

A8

VDDQ

C1

VDDQ

C9

VDDQ

D2

VDDQ

E9

VDDQ

F1

VDDQ

H2

VDDQ

H9

VDDQ

A9

VSS

B3

VSS

E1

VSS

G8

VSS

J2

VSS

J8

VSS

M1

VSS

M9

VSS

P1

VSS

P9

VSS

T1

VSS

T9

VSS

B1

VSSQ

B9

VSSQ

D1

VSSQ

D8

VSSQ

E2

VSSQ

E8

VSSQ

F9

VSSQ

G1

VSSQ

G9

VSSQ

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

ED20

ED19

ED22

ED23

ED18

ED21

ED16

ED17

ED30

ED29

ED28

ED25

ED24

ED31

ED26

ED27

DDR3VCCIODDR3VCCIO

12

R73

@ R73

@

1K_0201_1%

1K_0201_1%

RODT2_RRCS0_R RODT1_R

12

R72

R72

1K_0201_1%

1K_0201_1%

DDR3VCCIO

1

C78

C78

2

DDR3VCCIO

1

C57

C57

2

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

DDR3VCCIO

1

C76

C76

2

DDR3VCCIODDR3VCCIO DDR3VCCI O DDR3VCCIO

1

C77

C77

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

NANYA-1G

HYNIX-1G

DDR3VCCIO

DDR3VCCIO

2

U5

U5

M8

EVREF<5,6>

D D

ED0

ED1

ED2

ED3

ED4

ED5

ED6

ED7

ED8

ED9

ED10

ED11

ED12

ED13

ED14

ED15

ED16

ED17

ED18

ED19

ED20

ED21

ED22

ED23

ED24

ED25

ED26

ED27

EA0

EA1

EA2

EA3

EA4

EA5

EA6

EA7

EA8

EA9

EA10

EA11

EA12

EA13

EA14

5

ED28

ED29

ED30

ED31

C C

ED[0..31]<5>

EBA1<5>

/EWR<5>

ECKE<5>

EBA0<5>

ERESET_<5>

EBA2<5>

/ERAS<5>

/ECAS<5>

B B

EA[0..14]<5>

A A

EVREF

C66

C66

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

DDR3VCCIO

C71

C71

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

DDR3VCCIO

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

C64

C64

1

2

EDCLK<5>

EDCLK_B<5>

EDQS0<5>

EDQS1<5>

EDQM0<5>

EDQM1<5>

/EDQS0<5>

/EDQS1<5>

240_0201_1%

240_0201_1%

C62

C62

C73

C73

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

1

C61

C61

2

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

ERESET_

12

R65

R65

DDR3VCCIO

1

C56

C56

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

1

C70

C70

2

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

1

C58

C58

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

1

C72

C72

2

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

EVREF

H1

N3

EA0

P7

EA1

P3

EA2

N2

EA3

P8

EA4

P2

EA5

R8

EA6

R2

EA7

T8

EA8

R3

EA9

L7

EA10

R7

EA11

N7

EA12

T3

EA13

T7

EA14

M7

M2

EBA0

N8

EBA1

M3

EBA2

J7

K7

K9

ECKE

K1

RODT1_R

L2

RCS0_R

J3

/ERAS

K3

/ECAS

L3

/EWR

F3

C7

E7

D3

G3

B7

T2

L8

J1

L1

J9

L9

DDR3VCCIO

1

2

DDR3VCCIO

1

2

DDR3VCCIODDR3VCCIO DDR3VCCIODDR3VCCIO

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

1

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

DDR3VCCIODDR3VCCIO DDR3VCCIODDR3VCCIO

1

2

VREFCA

VREFDQ

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15/BA3

BA0

BA1

BA2

CK

CK

CKE/CKE0

ODT/ODT0

CS/CS0

RAS

CAS

WE

DQSL

DQSU

DML

DMU

DQSL

DQSU

RESET

ZQ/ZQ0

NC/ODT1

NC/CS1

NC/CE1

NCZQ1

96-BALL

96-BALL

SDRAM DDR3

SDRAM DDR3

H5TC4G63MFR-PBA 96P

H5TC4G63MFR-PBA 96P

@

@

DDR3L DDR3L

1

C60

C60

2

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

1

C74

C74

2

1

C63

C63

2

1

C75

C75

2

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

E3

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

RCS0_R<5> RCS1_R<5>

DDR3VCCIO

1

C67

C67

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

DDR3VCCIODDR3VCCIO

1

C54

C54

2

1

C68

C68

2

1

C59

C59

2

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

4

ED3

F7

ED6

F2

ED2

F8

ED5

H3

ED1

H8

ED4

G2

ED0

H7

ED7

D7

ED8

C3

ED13

C8

ED14

C2

ED15

A7

ED10

A2

ED9

B8

ED12

A3

ED11

B2

D9

G7

K2

K8

N1

N9

R1

R9

A1

A8

C1

C9

D2

E9

F1

H2

H9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

DDR3VCCIO DDR3VCCIO

R75

0_0201_5%

0_0201_5%

12

R77

R77

@

@

1K_0402_1%

1K_0402_1%

DDR3VCCIO DDR3VCCI O DDR3VCCIO

1

2

DDR3VCCIO DDR3VCCI O DDR3VCCIO

1

2

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

DDR3VCCIO DDR3VCCI O DDR3VCCIO

1

2

0.1U 6.3V K X5R 0201

0.1U 6.3V K X5R 0201

1

2

1K_0201_1%

1K_0201_1%

C1619

C1619

2.2U_0402_6.3VM

2.2U_0402_6.3VM

C1620

C1620

2.2U_0402_6.3VM

2.2U_0402_6.3VM

C1626

C1626

2.2U_0402_6.3VM

2.2U_0402_6.3VM

C1627

C1627

2.2U_0402_6.3VM

2.2U_0402_6.3VM

R76

R76

12

12

1

2

1

2

1

2

1

2

DDR3VCCIO

EVREF<5,6>

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

EVREF

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

EDCLK1_B<5>

EDQS2<5>

EDQS3<5>

EDQM2<5>

EDQM3<5>

/EDQS2<5>

/EDQS3<5>

@R75

@

C1630

C1630

2.2U_0402_6.3VM

2.2U_0402_6.3VM

C1629

C1629

2.2U_0402_6.3VM

2.2U_0402_6.3VM

C1632

C1632

2.2U_0402_6.3VM

2.2U_0402_6.3VM

C1631

C1631

2.2U_0402_6.3VM

2.2U_0402_6.3VM

1

C1617

C1617

2.2U_0402_6.3VM

2.2U_0402_6.3VM

2

C65

C65

EDCLK1<5>

240_0201_1%

240_0201_1%

1

2

1

2

1

2

1

2

EVREF

1

C69

C69

2

1

2

ECKE

RODT2_R

RCS1_R

/ERAS

/ECAS

/EWR

ERESET_

12

R71

R71

C1634

C1634

2.2U_0402_6.3VM

2.2U_0402_6.3VM

C1633

C1633

2.2U_0402_6.3VM

2.2U_0402_6.3VM

C1636

C1636

2.2U_0402_6.3VM

2.2U_0402_6.3VM

C1635

C1635

2.2U_0402_6.3VM

2.2U_0402_6.3VM

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

3

Page 7

NEED CHECK DEL OR NOT?

LCM_DIMO _R

CABC_E NABLE1 < 5>

CABC_E NABLE0 < 5>

LVDS_S HUTDOWN_ N

need check vcom 0513

JP8JP8

1

LCM_VDD

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

31

32

33

34

LED_ID 1

LED_ID 2

10K_04 02_5%

10K_04 02_5%

G1

G2

G3

G4

R5179

R5179

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

LCM_VDD

12

R5183

R5183

10K_04 02_5%

10K_04 02_5%

1 2

3.3V_R

MT8193_ AVDD33 _HDMI

VAST_P MU_R

VAST_P MU_R

MT8193_ AVDD28

3.3V_R

VAST_P MU_R

3.3V_R

VAST_P MU_R

3.3V_R

MT8193_ DVDDIO 18_DP I

MT8193_ DVDDIO 18_2

MT8193_ DVDDIO 18_1

3.3V

3.3V

VDD18_ 6583

1 2

R5219

R5219

0_0201 _5%

0_0201 _5%

47K +-5% 0 402

47K +-5% 0 402

LED_Sig nal_EN_R

1

1U 6.3V K X5R 0402

1U 6.3V K X5R 0402

2

@

@

1 2

R5221

R5221

0605 Change Q26 QL1 P/N FOR LOAD BOM

0605 DEL R5224

D D

C C

B B

5

VGP6_PMU for LCM 3.3V

0526 Change net name

VGP1_P MU

VCD_VD D

R5131

@R5131

@

0_0402 _5%

0_0402 _5%

1 2

0527 ADD GND FOR Dummy pin

LCM_RIN0 -_C

LCM_RIN0 +_C

LCM_RIN1 -_C

LCM_RIN1 +_C

LCM_RIN2 -_C

LCM_RIN2 +_C

LCM_CLK IN-_C

LCM_CLK IN+_C

LED_ID 1

LED_ID 2

12

LCD_PW M_R

R5154

R5154

0_0402

0_0402

+LEDVDD

NEED CHECK LCM_EL_EN

3.3V

DEL R FOR Layout 0521

2

C1755

C1755

C4219

C4219

18P_04 02_50V 8J

18P_04 02_50V 8J

1

EMC@

EMC@

VAST_P MU

1 2

R5178

R5178

0_0402 _5% -22m il

0_0402 _5% -22m il

VAST_P MU_R

U1B

U1B

A3

DVDDIO33_18_NFI

C1

AVDD33_HDMI

K3

AVDD12_HDMI_C

L1

AVDD12_HDMI_D

F4

AVSS12_HDMI

H3

AVSS12_HDMI

K4

AVSS12_HDMI

L2

AVDD28

M4

AVSS28

P2

AVDD33_PLLGP

R1

AVDD12_VPLL

N3

AVSS12_VPLL

R10

AVDD33_LVDSA

R2

AVDD12_LVDSA

N6

AVSS12_LVDSA

M8

AVSS12_LVDSA

M7

AVSS12_LVDSA

R11

DVDDIO33_DGO

J12

DVDDIO18_33_DPI

A8

DVDDIO18_33

A13

DVDDIO18_33

N13

EFUSE

MT8193

MT8193

<BOM Structure>

<BOM Structure>

Q26 AO3413_SO T23-3

Q26 AO3413_SO T23-3

D

S

D

S

1 3

MT8193_ AVDD33 _HDMI

G

G

2

1 2

R5230

R5230

47K +-5% 0 402

47K +-5% 0 402

0530 add R5230 and NC R5221 FOR MTK

13

D

D

2

QL1

QL1

BSS138 W-7-F_S OT323 -3

BSS138 W-7-F_S OT323 -3

G

G

S

S

R5132

R5132

0_0402 _5% -22m il

0_0402 _5% -22m il

1 2

0_0402 _5% -22m il

0_0402 _5% -22m il

1 2

3.3V_R

1 2

R5194 0_0402 _5%

R5194 0_0402 _5%

@

@

DVDD12_1

DVDD12_2

DVDD12_2

DVDD12_2

DVDD12_2

DVDD12_3

DVDD12_4

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

power domain

power domain

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

DVSS12

LCM_RIN0 -_C

1 2

LCM_RIN0 +_C

L3507 DL P11TB8 00UL2L _4P

L3507 DL P11TB8 00UL2L _4P

EMC@

EMC@

LCM_RIN1 -_C

1 2

LCM_RIN1 +_C

L3505 DL P11TB8 00UL2L _4P

L3505 DL P11TB8 00UL2L _4P

EMC@

EMC@

LCM_RIN2 -_C

1 2

LCM_RIN2 +_C

L3506 DL P11TB8 00UL2L _4P

L3506 DL P11TB8 00UL2L _4P

EMC@

EMC@

LCM_CLK IN-_C

1 2

LCM_CLK IN+_C

L3508 DL P11TB8 00UL2L _4P

L3508 DL P11TB8 00UL2L _4P

EMC@

EMC@

5/22 ADD L for RF require

R5192

R5192

MT8193_ AVDD33 _HDMI

C4234 0.1U_040 2_16V4 ZC4234 0.1U_040 2_16V4 Z

C4235 0.1U_040 2_16V4 ZC4235 0.1U_040 2_16V4 Z

C4236 0.1U_040 2_16V4 ZC4236 0.1U_040 2_16V4 Z

C4237 0.1U_040 2_16V4 ZC4237 0.1U_040 2_16V4 Z

C4238 0.1U_040 2_16V4 ZC4238 0.1U_040 2_16V4 Z

C4239 0.1U_040 2_16V4 ZC4239 0.1U_040 2_16V4 Z

C4240 0.1U_040 2_16V4 ZC4240 0.1U_040 2_16V4 Z

E4

VAST_P MU_R

E7

E8

F8

G8

H10

J9

B7

G5

G6

G7

G9

G12

F5

H7

H8

H9

H11

H12

J6

J7

J8

J11

K6

K7

K8

K9

P10

3.3V

0521 Change P to 0201

0730 change R5227 bom structure

for MTK recommend

34

LCM_RIN0 -

LCM_RIN0 +

34

LCM_RIN1 -

LCM_RIN1 +

34

LCM_RIN2 -

LCM_RIN2 +

34

LCM_CLK IN-

LCM_CLK IN+

3.3V

12

12

12

12

12

12

12

12

C4241 0.1U_040 2_16V4 ZC4241 0.1U_040 2_16V4 Z

12

C4242 0.1U_040 2_16V4 ZC4242 0.1U_040 2_16V4 Z

12

C4243 0.1U_040 2_16V4 ZC4243 0.1U_040 2_16V4 Z

12

C4244 0.1U_040 2_16V4 ZC4244 0.1U_040 2_16V4 Z

12

C4245 0.1U_040 2_16V4 ZC4245 0.1U_040 2_16V4 Z

1 2

C4230 0.1U_040 2_25V4 ZC42 30 0.1U_0402_2 5V4Z

1 2

C4231 0.1U_040 2_25V4 ZC42 31 0 .1U_0402 _25V4 Z

1 2

C4232 0.1U_040 2_25V4 ZC42 32 0 .1U_0402 _25V4 Z

1 2

MT8193_ AVDD28

C4233

C4233

0.1U_040 2_25V4 Z

0.1U_040 2_25V4 Z

0530 Update u1 pcb footprint for layout nc -p

0605 Change R5218 P/N FOR LOAD BOM

1 2

R5218 2.49K_ 0402_1 %R5218 2.49K_ 0402_1 %

0604 Change D815 for ME

D815

D815

R5225

R5225

12

RB551V -30_SOD 323-2

RB551V -30_SOD 323-2

1 2

R5227 100_02 01_5%

R5227 100_02 01_5%

LCM_RIN0 LCM_RIN0 +

LCM_RIN1 LCM_RIN1 +

LCM_RIN2 LCM_RIN2 +

LCM_CLK INLCM_CLK IN+

LCM_RIN3 LCM_RIN3 +

1 2

27K +-1% 0 402

27K +-1% 0 402

MT8193_ DVDDIO 18_1

MT8193_ DVDDIO 18_2

MT8193_ DVDDIO 18_DP I

R5175 0_0201 _5%R5175 0_0201_5%

R5176 0_0201 _5%

R5176 0_0201 _5%

HDMI_CK_ M

HDMI_CK_ P

HDMI_DAT 0_M

HDMI_DAT 0_P

HDMI_DAT 1_M

HDMI_DAT 1_P

HDMI_DAT 2_M

HDMI_DAT 2_P

HDMI_HPD

DDC_SD

DDC_SC

HDMI_CEC

@

@

HDMI_DAT 2_P

HDMI_DAT 2_M

HDMI_DAT 1_P

HDMI_DAT 1_M

HDMI_DAT 0_P

HDMI_DAT 0_M

HDMI_CK_ P

HDMI_CK_ M

VDD18_ 6583

R5169 0_0201 _5%R5169 0_0201_5%

1 2

R5171 0_0201 _5%R5171 0_0201_5%

1 2

R5173 0_0201 _5%R5173 0_0201_5%

1 2

R5174 0_0201 _5%R5174 0_0201_5%

0521 Change P to 0201

1 2

12

@

@

B9

D9

B10

C9

A10

D10

B11

D11

A11

D12

B12

C12

B13

B6

C5

B5

A5

C4

B3

A2

B2

A1

B1

C2

D4

C3

D5

D1

F2

F1

F3

G3

H1

H2

H4

J4

P15

R14

R15

P14

P3

P4

R4

N4

N5

P6

R6

N7

N8

R8

P8

1 2

U1A

U1A

NLD0

NLD1

NLD2

NLD3

NLD4

NLD5

NLD6

NLD7

NREB

NWEB

NALE

NCLE

NRNB

NFRBN

NFCLE

NFALE

NFWEN

NFREN

NFCEN

NFD7

NFD6

NFD5

NFD4

NFD3

NFD2

NFD1

NFD0

HDMI_EXT_RES

CLK_M

CLK_P

CH0_M

CH0_P

CH1_M

CH1_P

CH2_M

CH2_P

HTPLG

HDMISD

HDMISCK

CEC

TP_VPLL

AO0N

AO0P

AO1N

AO1P

AO2N

AO2P

AOCK0N

AOCK0P

AO3N

AO3P

4

L3502 DL P11TB8 00UL2L _4P

L3502 DL P11TB8 00UL2L _4P

1 2

EMC@

EMC@

1 2

L3501 DL P11TB8 00UL2L _4P

L3501 DL P11TB8 00UL2L _4P

EMC@

EMC@

L3503 DL P11TB8 00UL2L _4P

L3503 DL P11TB8 00UL2L _4P

1 2

EMC@

EMC@

1 2

L3504 DL P11TB8 00UL2L _4P

L3504 DL P11TB8 00UL2L _4P

EMC@

EMC@

5/24 swap for layout

need check GPIO_HDMI_POWER_EN

VTCXO_ 1_PMU

VTCXO_ 2_PMU

control

control

NFI_CPU

NFI_CPU

MT8193

MT8193

BGA-150

BGA-150

DPI0

DPI0

NFI_NAND

NFI_NAND

DPI1

DPI1

HDMI

HDMI

(analog)

(analog)

I2S

I2S

HDMI

HDMI

(digital)

(digital)

DCXO

DCXO

LVDS RGB

LVDS RGB

34

34

34

34

GPIO_HD MI_POW ER_EN<5>

CK_SEL

EN_BB

RESET_N

RTC_32K_CK

DPI0D0

DPI0D1

DPI0D2

DPI0D3

DPI0D4

DPI0D5

DPI0D6

DPI0D7

DPI0D8

DPI0D9

DPI0D10

DPI0D11

DPI0VSYNC

DPI0HSYNC

DPI0CK

DPI1D0

DPI1D1

DPI1D2

DPI1D3

DPI1D4

DPI1D5

DPI1D6

DPI1D7

DPI1CK

I2S_BCK

I2S_LRCK

I2S_DATA

CLKBUF1

CLKBUF2

CLKBUF3

HSYNC

VSYNC

C8

D6

D8

D7

INT

A7

E11

SCL

E12

SDA

A14

C13

B14

D13

B15

A15

C14

E13

E15

E14

G14

F13

H14

G13

H15

J13

J14

J15

K13

L15

L14

M14

N14

N15

M12

L13

L12

N1

XTALI

N2

XTALO

L4

L5

M3

L10

G0

K11

B5

M10

B4

N10

B3

L11

B2

P11

B1

R13

B0

N11

VCLK

P13

N12

5V_DDC

1U_0603_10V6K

1U_0603_10V6K

C4228

C4228

12

16V rating

R5197 0_0402R51 97 0_0402

R5193 0_0402R51 93 0_0402

R5191 0_0402R51 91 0_0402

R5190 0_0402R51 90 0_0402

R5187 0_0402R51 87 0_0402

DPI_B0

DPI_B1

DPI_B2

DPI_B3

DPI_B4

DPI_B5

DPI_B6

DPI_B7

DPI_G0

DPI_G1

DPI_G2

DPI_G3

DPI_VS YNC

DPI_HSYNC

RGB_CK

DPI_R0

DPI_R1

DPI_R2

DPI_R3

DPI_R4

DPI_R5

DPI_R6

DPI_R7

DPI1_C LK

1 2

R5220 0_0201 _5%R5220 0_0201_5%

1 2

R5222 0_0201 _5%R5222 0_0201_5%

1 2

R5223 0_0201 _5%R5223 0_0201_5%

MT8193_ CLKBUF_ 1

MT8193_ CLKBUF_ 2

MT8193_ CLKBUF_ 3

U4030U4030

1

SHDN

2

GND

3

VOUT

12

12

12

12

12

7

TP

6

C-

5

VIN

4

C+

SRCLKE NA <23,5>

SRCVOL TEN <23,5>

SYSRST_ B <11,15,2 3,5>

MT8193_ INT <5>

RTC32K 1V8 <23,5>

SCL2 <5>

SDA2 <5>

0521 Change R to 0201

I2S0_C K <5>

I2S0_W S <5>

I2S0_D AT_OUT <5>

OUT3GND

2

GND

26MHZ_7.3 PF_TZ1 689A

26MHZ_7.3 PF_TZ1 689A

Differential Signal !

No Through Hole !

100 ohm - Impedance

5V_DDC

0_0402 _5% -22m il

0_0402 _5% -22m il

1 2

R5150

R5150

C4224

C4224