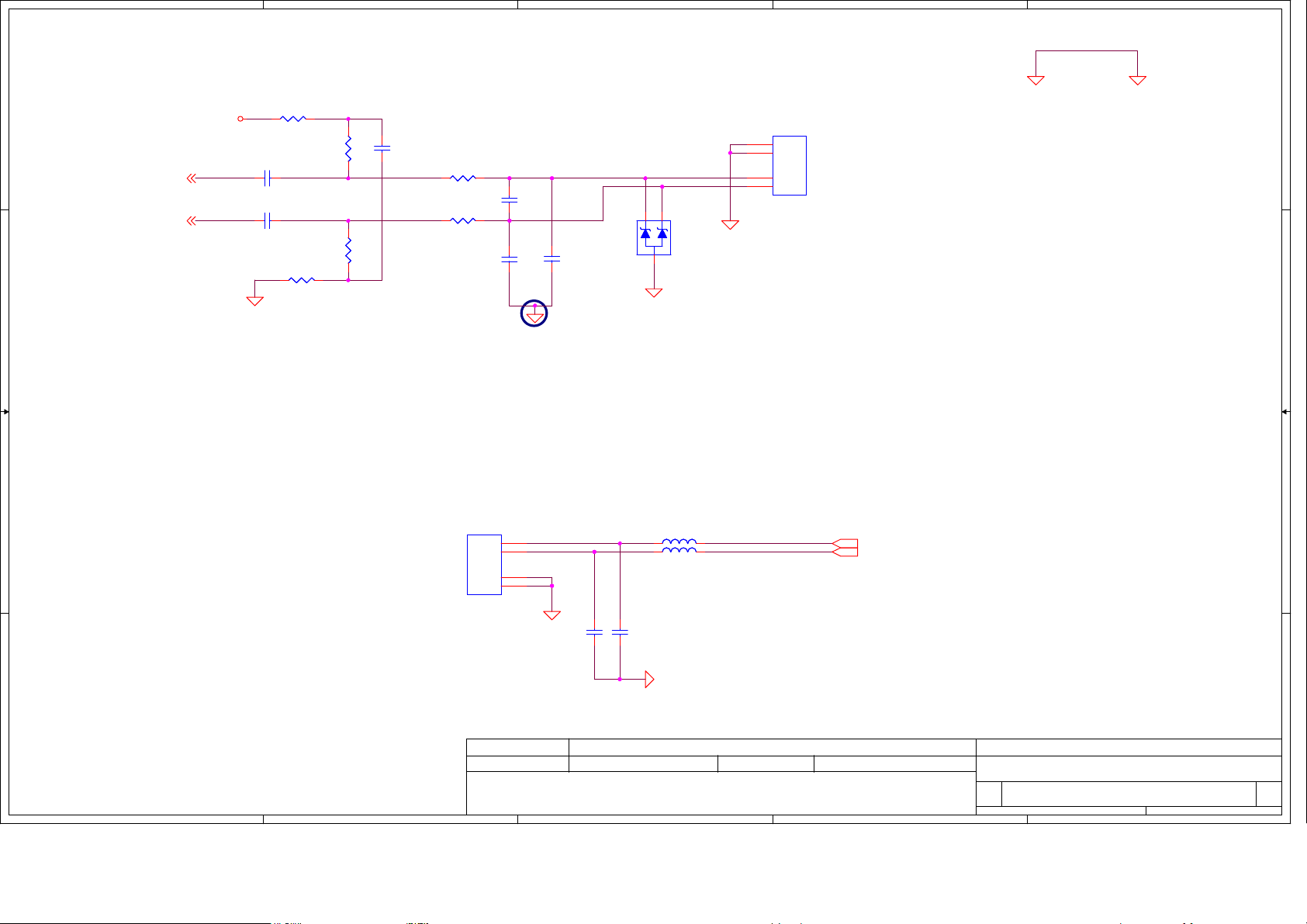

Page 1

5

ZZZ

ZZZ

DAZ@

DAZ@

PCB

PCB

DA6000YE000

DA6000YE000

PCB 0YR LA-A031P REV0 M/B

D D

PCB 0YR LA-A031P REV0 M/B

S1

S1

FRAME

FRAME

EC0MV000200

EC0MV000200

@

@

4

3

2

1

Compal Confidential

C C

Schematics Document

VSJEV

MT8317

B B

LA-A031P

2013-01-02

REV:1B

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

2013/11/032012/11/03

2013/11/032012/11/03

2013/11/032012/11/03

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

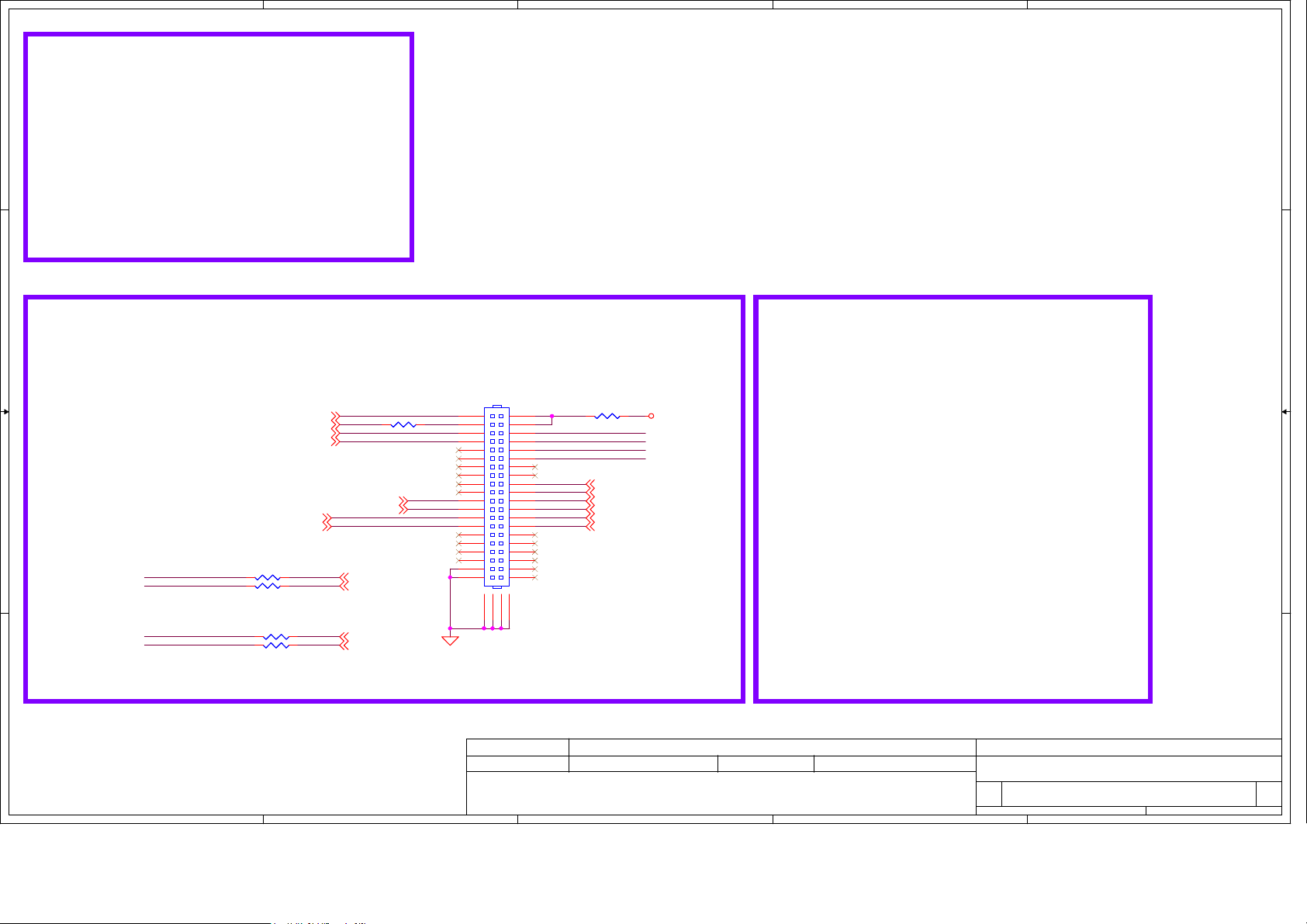

Cover Page

Cover Page

Cover Page

LA-A031P

LA-A031P

LA-A031P

1

1 23Wednesday, January 02, 2013

1 23Wednesday, January 02, 2013

1 23Wednesday, January 02, 2013

1B

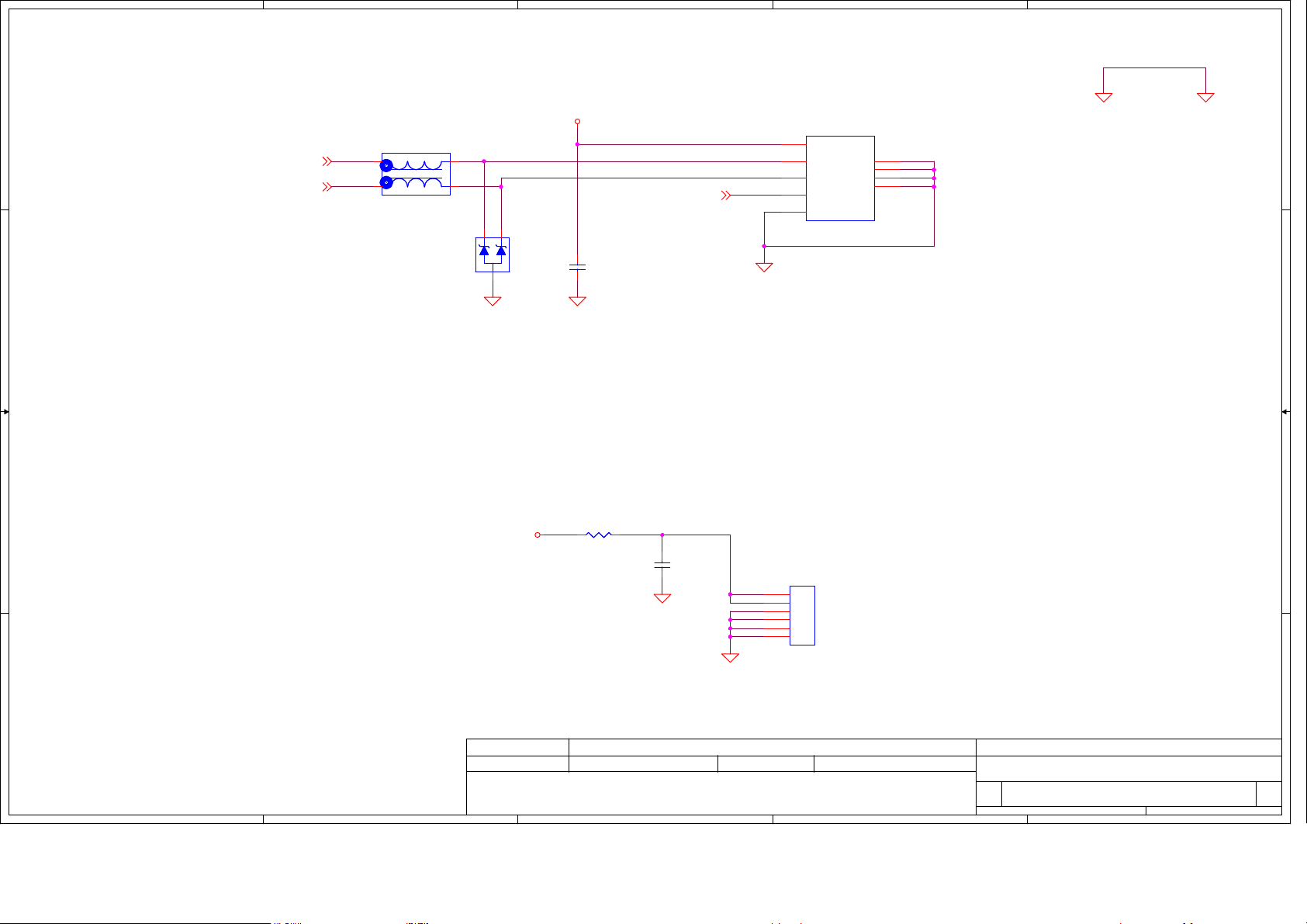

Page 2

A

B

C

D

E

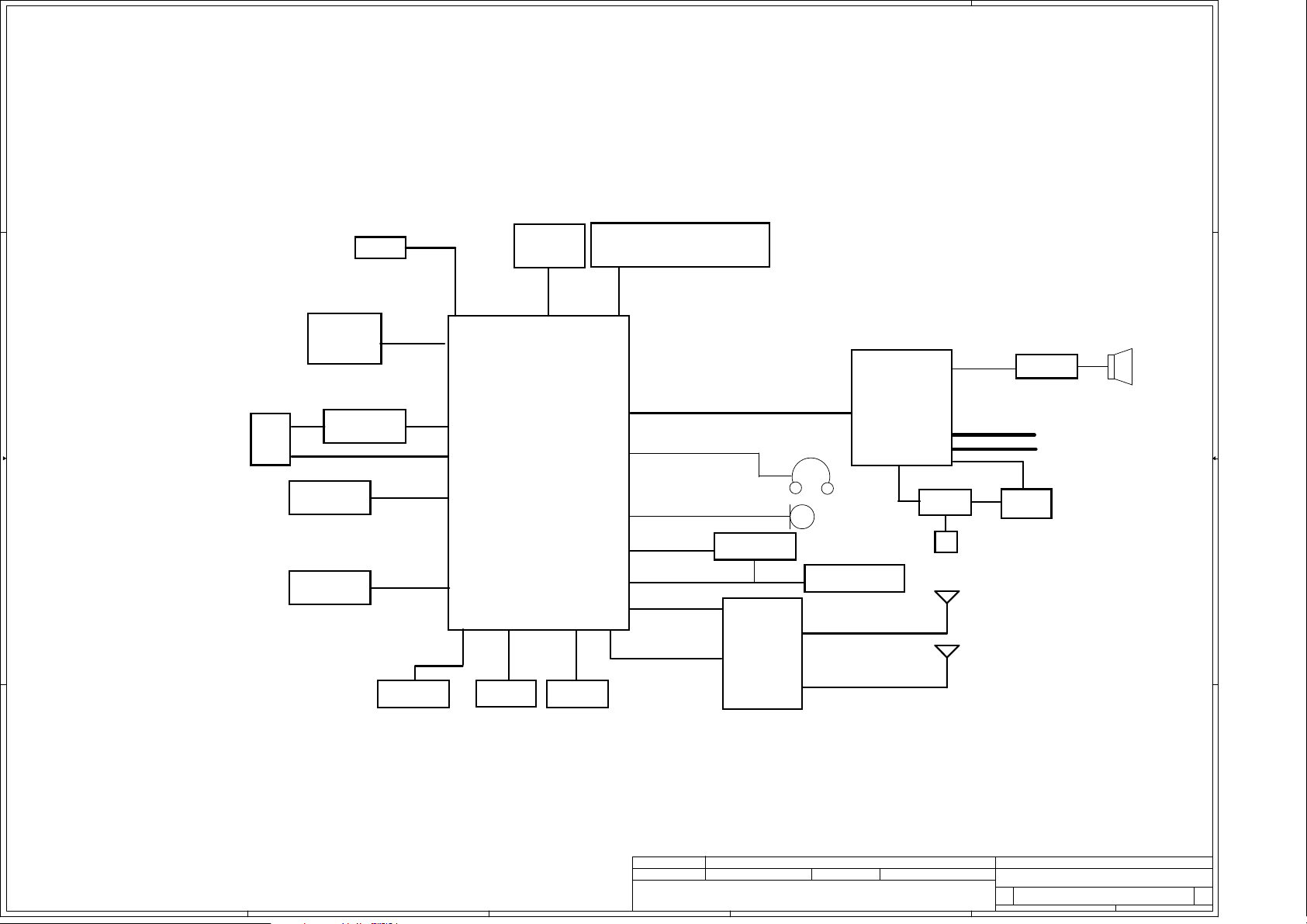

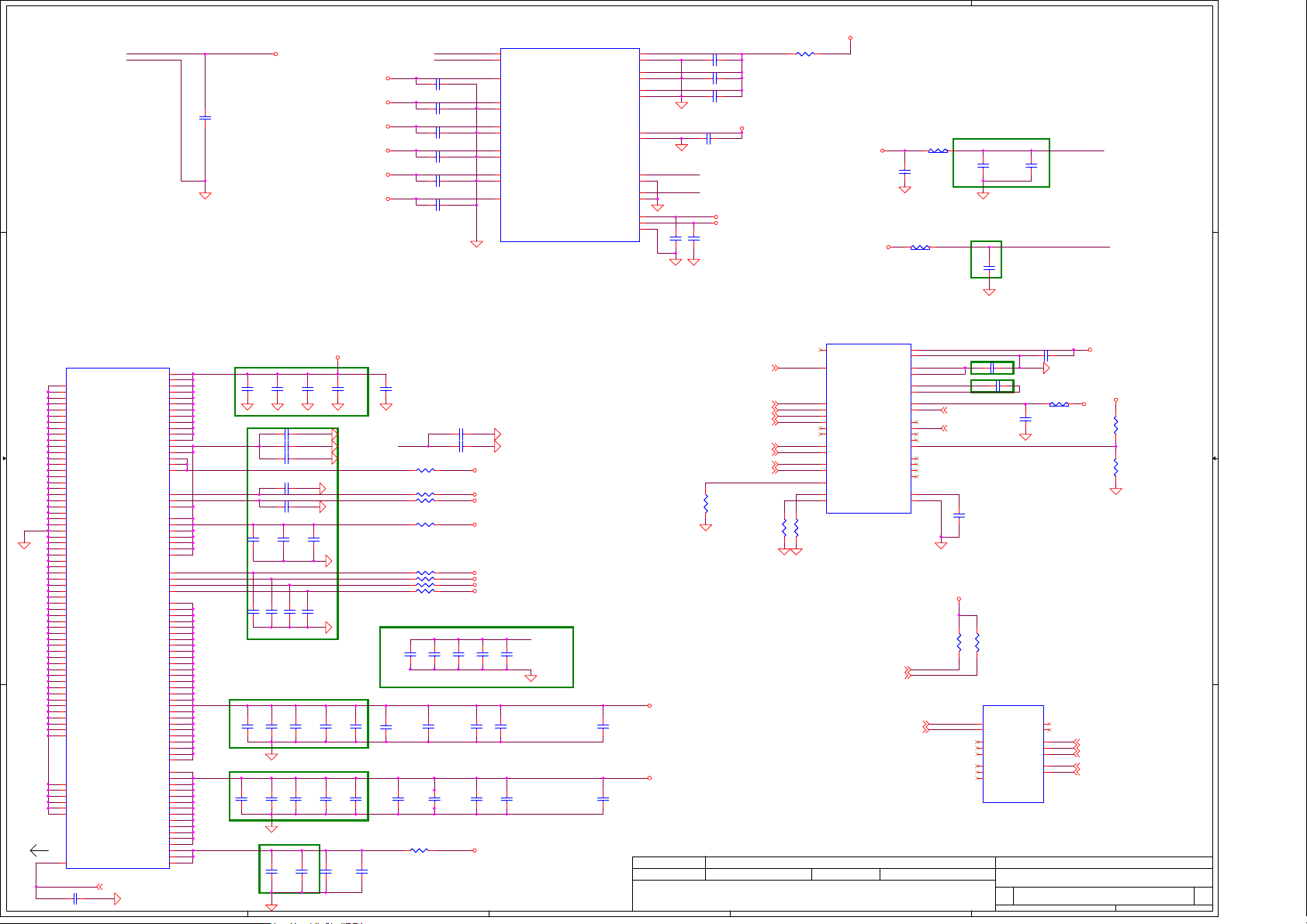

VSJEV system block diagram

1 1

Capacitive

Touch Panel

C

ortex-A9

DC0

eMMC

CONN.

I2C,

EINT

I2C

EI

M

GP

Camera IF, I2C

KCOL & KROW

NT

RGB

MT8317/MT8377

IO

1.2GHz Dual-Core

JTAG

UART1

UART2

UART3

RT4

UA

Sidekey

G Sensor

ro Sensor

2 2

LCM

CONN.

3 3

Gy

LVDS

SN75LVDS83B

Flashlight

Dr

iver

PW

Sub Camera

Debug Port

DDR3 512MB (2Gb X16 *2 Pcs)

DDR3 1GB (4Gb X16 *2 Pcs)

EMI

AUD, HSP,

Headset (HPLP, HPRP, MIC3)

MIC1

PC

MSDC1MS

micro SD

OR

USB

M, UART3, I2S

MSDC3

OTGDRVVBUS

MT6620

4-in-1

Blue Tooth

FM

WiFi

GPS

MT6329

PMU

AUDIO

LDO OUTPUT

BUCK OUTPUT

CHARGER

10-pin mini USB

Sp

eaker (HPLP)

LDO Output

BUCK Output

Battery Input

BJT

DC

IN

Class D /

ass AB

Cl

Ba

ttery

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

A

B

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

2013/11/032012/11/03

2013/11/032012/11/03

2013/11/032012/11/03

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Block Diagram

Block Diagram

Block Diagram

LA-A031P

LA-A031P

LA-A031P

E

2 23Wednesday, May 15, 2013

2 23Wednesday, May 15, 2013

2 23Wednesday, May 15, 2013

1B

of

of

of

Page 3

5

D D

4

3

2

1

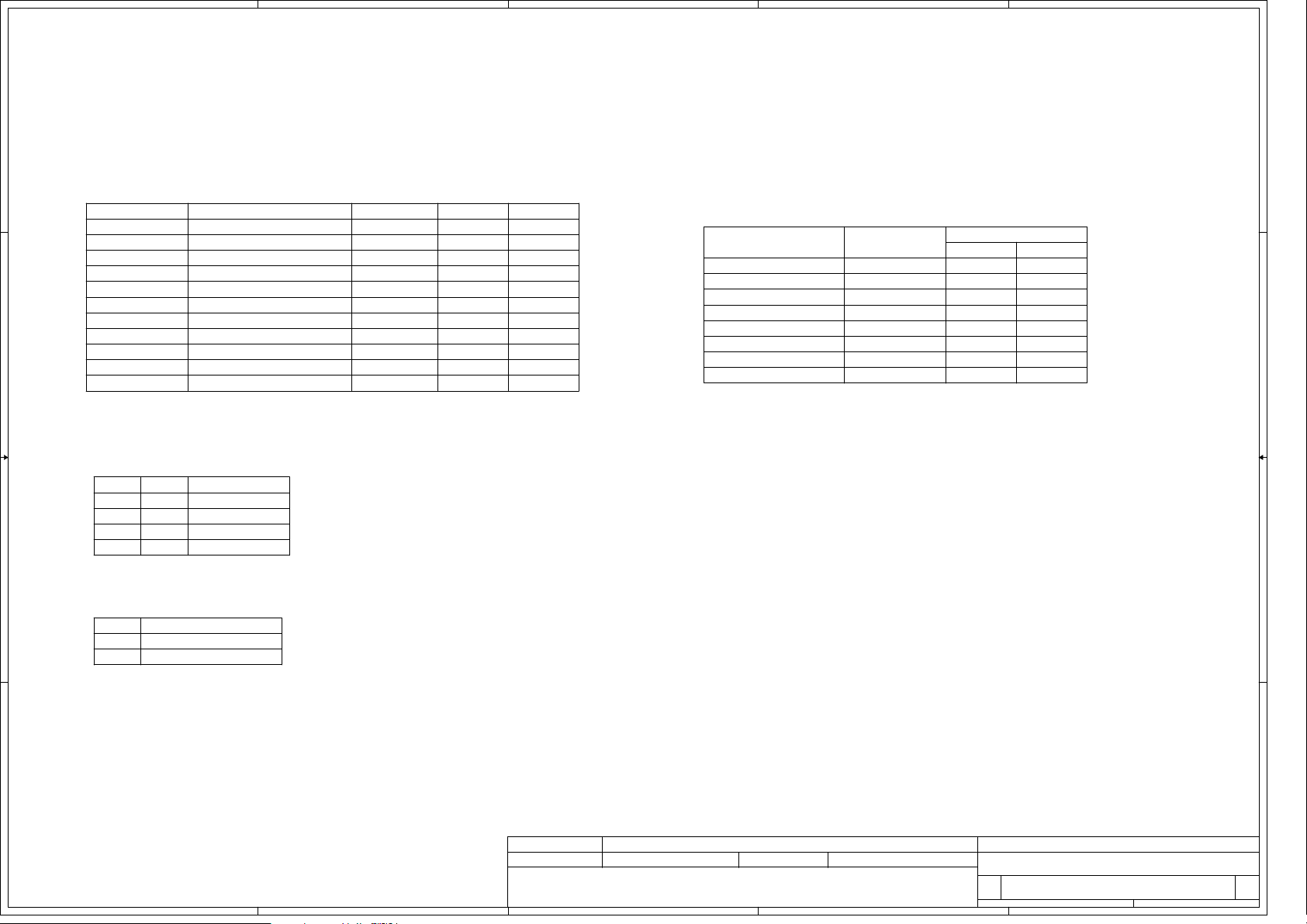

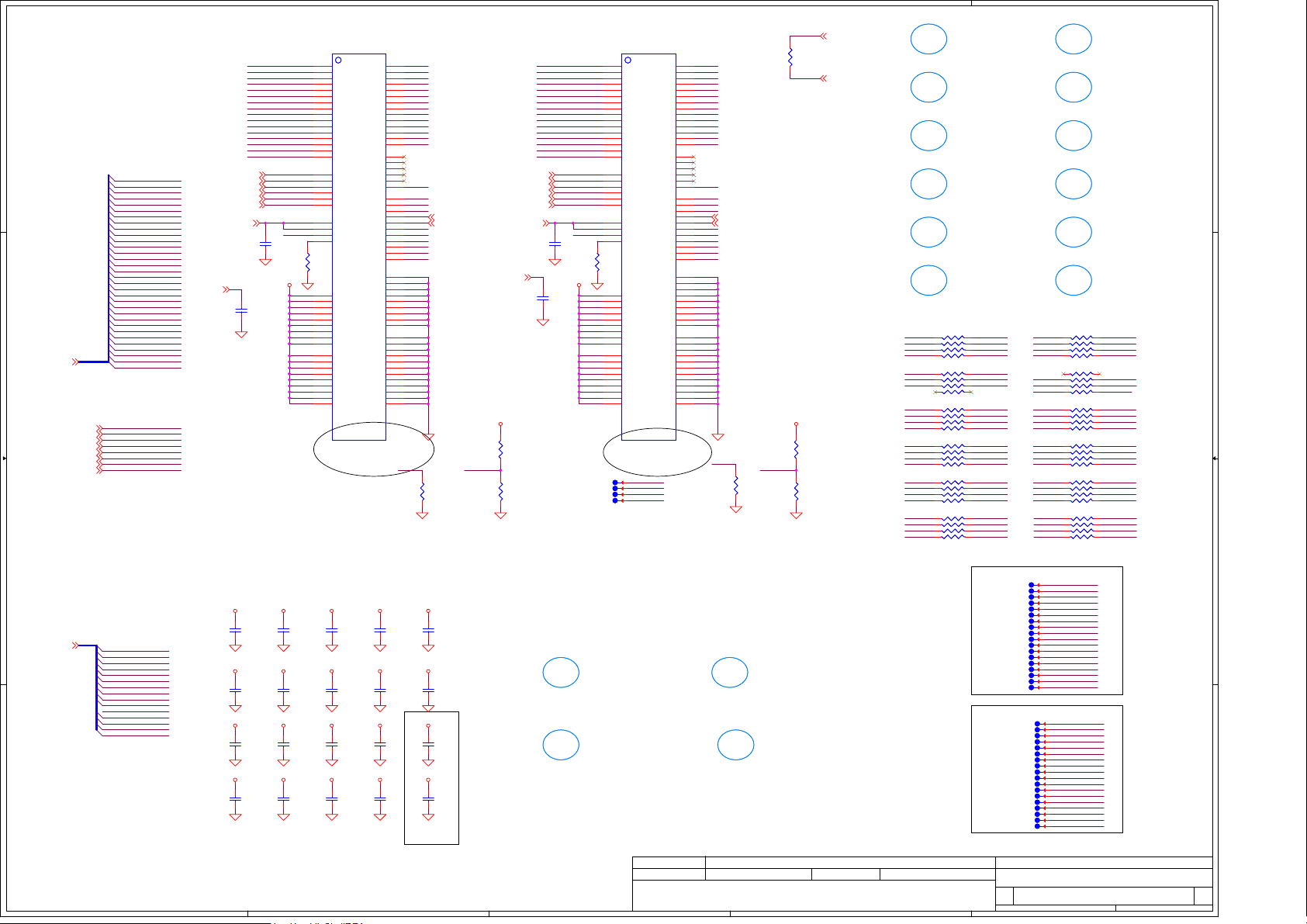

Voltage Rails

MT6329 Power Plane

VCORE_PMU

VAPROC_PMU VPROC switching output

TCXO_PMU

V

VCAMA_PMU

VDD12_INT_PMU

VIO28_IC

VCAM_IO

VMC_PMU

C C

VMCH

VGP

VGP2

Function Power Level

VCORE switching output

0.75 ~ 1.3 ON

0.75 ~ 1.3

LDO output for TCXO

LDO output for camaera analog

LDO output used for 1.2V SRAM

LDO output used for 2.8V IO

2.8V

2.8V

1.2V

2.8V

VCAM_IOPMU 1.8V

SD card I/O and eMMC power

SD card power

Reserve for LCM 3.3V

Touch panel GT927 power

3.3V

3.3V

3.3V

2.8V

IDLE Sleep mode

Low voltage

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

Low voltage

OFF

Gating by SW

Low voltage

Gating by SW

Gating by SW

Gating by SW

Gating by SW

Gating by SW

Gating by SW

I2C address

Device

Gyro (MPU-3050)

G-sensor (MC3210)

Touch screen (GT927)

Charge (NCP1851) 0x36

PMU(MT6329)

Codec

Address(7 bit)

Address(8bit)

rite

0x68

0x4C

0x5D 0xBB

0x21 0x43Camera (OV7675)

0xD0

0x98

0xBA

0x42

ReadW

0xD1

0x99

0x6D0x6C

Main board ID

MB_ID0 MB_ID1

PC

B1.0+mCube0 0

0 1

1 0

1 1

B B

PCB2.0+mCube

PCB2.0+STK8311

PCB2.0+KXTIK

Battery ID

BAT_ID

LG1

0 S

A A

5

anyo

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

2013/11/032012/11/03

2013/11/032012/11/03

2013/11/032012/11/03

2

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

LA-A031P

LA-A031P

LA-A031P

3 23Friday, January 04, 2013

3 23Friday, January 04, 2013

3 23Friday, January 04, 2013

1

1B

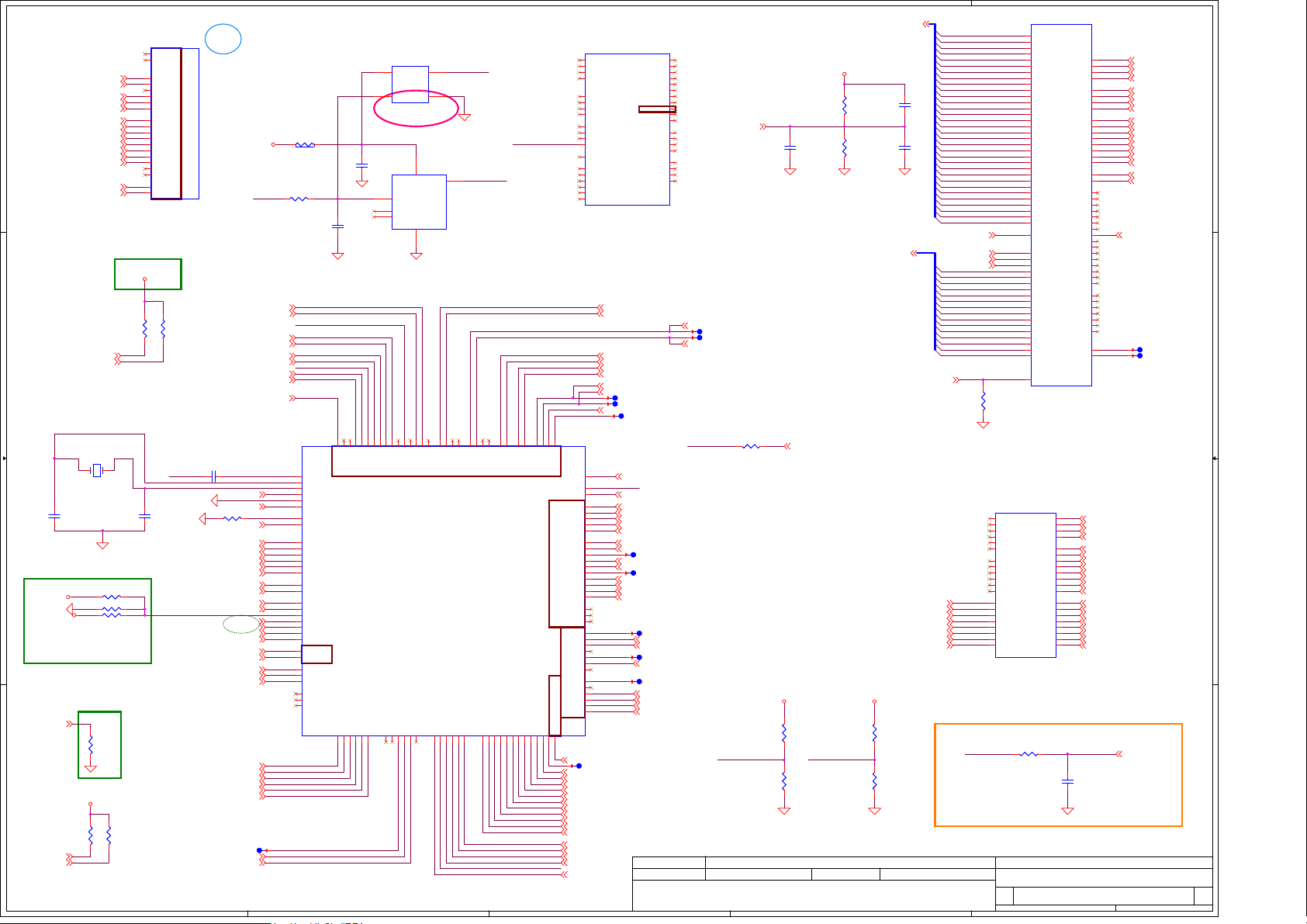

Page 4

5

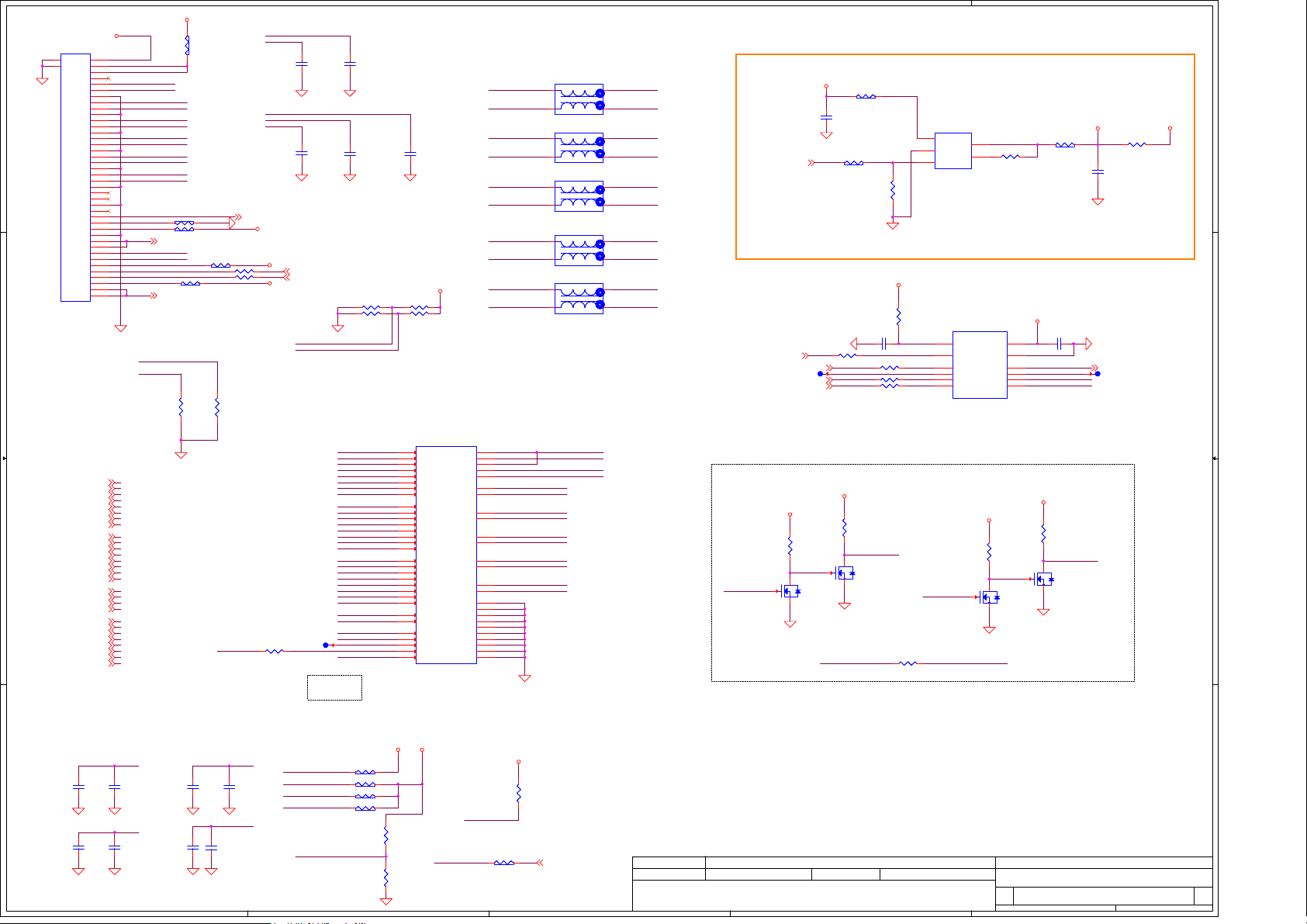

U201

U201

@

@

U201I

U201I

K11

PWM4

D4

CMFLASH

4.7K_0402_5%

4.7K_0402_5%

18P_0402_50V8J

18P_0402_50V8J

0_0402_5%@

0_0402_5%@

1 2

R0216

R0216

1 2

1 2

VCAM_IOPMU

R0212

R0212

C199

C199

E6

E7

B2

E5

B1

B3

A3

D6

B5

E4

A2

A4

B4

B6

C3

C4

K10

K9

1 2

2

1

CMMCLK

CMPCLK

CMRST

CMPDN

CMHSYNC

CMVSYNC

CMDAT9

CMDAT8

CMDAT7

CMDAT6

CMDAT5

CMDAT4

CMDAT3

CMDAT2

CMDAT1

CMDAT0

SCL_1

SDA_1

MT8317_DDR3

MT8317_DDR3

4.7K_0402_5%

4.7K_0402_5%

R0211

R0211

1 2

90 Ohm

fferential

di

DVDD_CAM

1000P_0402_50V7K

1000P_0402_50V7K

SYSCLK

VBUS_BB

CMMCLK (10)

CMPCLK (10)

CMPDN (10)

CMHREF (10)

CMVREF (10)

D D

I2C1: CAMERA, ATV

C C

18P_0402_50V8J

18P_0402_50V8J

C200

C200

B B

VUSB_6575

USB_VBUS rating: 3.3V

In device only mode, you

can use R0216 instead of

R0202 and R0201

CMDAT9 (10)

CMDAT8 (10)

CMDAT7 (10)

CMDAT6 (10)

CMDAT5 (10)

CMDAT4 (10)

CMDAT3 (10)

CMDAT2 (10)

SCL1 (10,4)

SDA1 (10,4)

SCL1 (10,4)

SDA1 (10,4)

X2

X2

1 2

32.768KHZ_12.5P_1TJF125DP1A000D

32.768KHZ_12.5P_1TJF125DP1A000D

2

1

C

lose to MT8317

R0202 1M_0402_1%R0202 1M_0402_1%

R0201 2M +-1% 0402R0201 2M +-1% 0402

VBUS

I2C0: CTP, M-Sensor, G-Sensor, ALS&PS, Gyro, OFN

Close to MT8317

USB_VRT (4)

5.11K +-1% 0402

5.11K +-1% 0402

R0203

R0203

1 2

A A

VDD18_6575

4.7K_0402_5%

R0205

R0205

4.7K_0402_5%

R0204

R0204

1 2

1 2

5

4.7K_0402_5%

4.7K_0402_5%

SCL0 (12,14,17,20,4)

SDA0 (12,14,17,20,4)

SA00006GQ10

SA00006GQ10

MT8317TA 1.2G TFBGA 537P

MT8317TA 1.2G TFBGA 537P

NC21

VTCXO_PMU

LEVEL_SHIFT_EN

BGF_INT_B_6620 (9)

ALL_INT_B_6620

WiFi_INT_B_6620 (9)

C198

C198

1 2

RTC_GPIO_2V8

BBWAKEUP

1 2

R217 0_0402_5%R217 0_0402_5%

WATCHDOG_RESET_B

MCU_JTRST_B (11)

MCU_JTCK (11)

MCU_JTDI (11)

MCU_JTMS (11)

MCU_JTDO (11)

MCU_JRTCK (11)

SWDIO (11)

CHD_DP (21)

CHD_DM (21)

USB_DM (18)

USB_DP (18)

USB_VRT (4)

USB_ID (18)

SCL0 (12,14,17,20,4)

SDA0 (12,14,17,20,4)

I2S1_CK

I2S1_DAT

I2S1_WS

MC3CMD (9)

MC3CLK (9)

MC3DA0 (9)

MC3DA1 (9)

MC3DA2 (9)

MC3DA3 (9)

TP1335 PAD @TP1335 PAD @

6620_LNA_EN (9)

GPIO12_6620_PWR_EN (9)

1 2

0_0402_5%

0_0402_5%

0.01UF_0402_25V7K

0.01UF_0402_25V7K

R611

R611

1 2

AFC

0_0402_5%

0_0402_5%

0.01UF_0402_25V7K

0.01UF_0402_25V7K

@ C638

@

Need to turn of f if I2C1 devic es not operated

NCP_SPM (20)

MB_ID1

KCOL1 (15)

KCOL0 (11,15,21)

MB_ID0

BAT_ID (20)

KROW0 (11,15,21)

@

@

U201E

U201E

AB21

26M_CK_IN

32K_OUT

32K_IN

CLK26M

AK15

RTC_XOUT

AK16

RTC_XIN

AD16

32K_OUT

AJ16

TESTMODE

AG16

BBWAKEUP

D27

FSOURCE

AF5

WATCHDOG_B

R30

JTRST_B

T30

JTCK

T29

JTDI

U27

JTMS

U28

JTDO

R29

JRTCK

U26

SWCLKTCK

T26

SWDIOTMS

AA27

CHD_DP

AA26

CHD_DM

AA29

USB_VBUS

AB26

USB_DM

AC26

USB_DP

AA30

USB_VRT

Y29

IDDIG

AG1

SCL_0

AH2

SDA_0

W5

I2S1_CK

Y5

I2S1_DAT

W1

I2S1_WS

W2

I2S0_CK

Y6

I2S0_WS

V1

I2S0_DAT

MT8317_DDR3

MT8317_DDR3

@NC21

@

C638

(21,9)

(21)

(21)

4

CO-Layout

26MHZ_10PF_TG-5035CJ-12N

26MHZ_10PF_TG-5035CJ-12N

change to SJ000004W00

12

C643

C643

1 2

(7)

AG6

AC10

AF6

AF7

AJ6

AK6

AH8

KP_ROW0

KP_ROW1

KP_ROW2

KP_ROW3

KP_ROW4

KP_ROW5

DVDD_NML

MSDC3_DAT1

MSDC3_DAT3

MSDC3_CLK

MSDC3_DAT2

MSDC3_CMD

MSDC3_DAT0

AJ3

AJ4

AK3

AH3

AH4

AG4

4

4

1

2

5

1

AF9

AK7

KP_COL0

KP_ROW6

KP_ROW7

MSDC2_CMD

J29

X3

X3

Vdd

OUT

GND

N.C.

6

U606

U606

VCC

ENABLE/DISABLE

NC

NC

GND

3

AH7

AG7

AF8

AB11

AJ7

KP_COL4

KP_COL5

KP_COL3

KP_COL2

KP_COL1

MSDC2_DAT0

MSDC2_CLK

MSDC2_DAT1

MSDC2_DAT3

MSDC2_DAT2

J30

J28

K24

H26

H29

3

2

@

@

4

OUTPUT

26MHZ_10PF_TX5651

26MHZ_10PF_TX5651

AJ5

AG8

P27

P26

R27

R25

URTS1

UTXD1

URXD1

KP_COL7

KP_COL6

DVDD_NML

MSDC1_CMD

MSDC1_CLK

MSDC1_DAT0

MSDC1_DAT1

J26

K26

K28

K29

K30

3

Note: AFC > 3G_ TX_VGA > APC > 3G_VBIAS

@

@

U201A

U201A

AF20

DL_I_P

AF21

DL_I_N

R26

URXD4

MSDC0_DAT4

N28

AG2

DVDD_LCD

MSDC0_DAT5

P29

N30

MC1CK

AG3

AH1

SPI_MI

SPI_MO

MSDC0_DAT7

MSDC0_DAT6

L26

M30

AG21

AH21

AG23

AF23

AG24

AH24

AK13

AJ13

AB16

AC19

AJ12

AG12

AK12

AH12

AF12

AD11

AF4

SPI_CLK

SPI_CSN

SYSRST_B

SRCLKENAI

SRCLKENA

DAICLK

DAIPCMOUT

DAIPCMIN

BTSYNC

DAIRSTB

EINT0

EINT1

EINT2

EINT3

EINT4

EINT5

EINT6

EINT7

EINT8

EINT9

PWM1

PWM2

PWM3

LPCE1B

LPCE0B

LPTE

LRSTB

LRDB

LPA0

LWRB

LSCE1B

LSCE0B

LSDA

LSA0

LSCK

MSDC0_SDWPI

MSDC1_INSI

N29

DL_Q_P

DL_Q_N

UL_I_P

UL_I_N

UL_Q_P

UL_Q_N

VM0

VM1

Y16

APC

AFC

3G_VBIAS

BPI_BUS11

BPI_BUS12

BPI_BUS13

BPI_BUS14

TDD_TIMINGSYNC

TDD_AFC_SW

MT8317_DDR3

MT8317_DDR3

W30

U29

SRCLKENAI

V29

AA3

AA2

AA4

AB1

Y2

AC2

AD2

AE4

AA5

AD4

AE2

AA6

AB5

Y4

AA1

AB2

AB4

AB3

K4

K1

J2

K2

K5

J3

K3

U2

V4

V2

V3

V5

U3

LSDI

MC0INS (17)

TP1345PAD@ TP1345PAD@

MC0DA7 (13)

MC0DA6 (13)

MC0DA5 (13)

MC0DA4 (13)

MC0DA3 (13)

MC0DA2 (13)

MC0DA1 (13)

MC0DA0 (13)

MC0CK (13)

MC0CM0 (13)

MC0RSTB (13)

MC1DA3 (17)

MC1DA2 (17)

MC1DA1 (17)

MC1DA0 (17)

MC1CMD (17)

DVDD

BPI_BUS10

BSI0_DATA

BSI1_DATA

UTXD1 (11,21)

URXD1 (11,21)

UTXD3 (9)

URXD3 (9)

UTXD4 (11,21)

URXD4 (11,21)

CABC_ENABLE0 (7)

CABC_ENABLE1 (7)

TP1342PAD@ TP1342PAD@

TP1343PAD@ TP1343PAD@

GPIO86_CTP_RST(14)

SYSRST_B (11,15,21)

SRCLKENA (21)

DAICLK (9)

DAIPCMOUT (9)

DAIPCMIN (9)

DAISYNC (9)

DAIRST (9)

LCD3V3_POWER_EN(7)

EINT1_GY (12)

EINT3_G (17)

EINT4_CHARGER (20)

EINT6_C (14)

GPIO_USB_DRVVBUS(20)SWCLK (11)

EINT8_EARPHONE (8)

PMU_INT (21)

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

3

UCTS1

MSDC1_DAT2

J27

SYSCLK

SYSCLK

AE1

MSDC1_DAT3

AFC

AE3

AD1

AF2

AD5

AC5

P28

UCTS2

UTXD3

UTXD2

URTS2

UTXD4

URXD3

URXD2

DVDD_NML

DVDD_NML

MSDC0_DAT3

MSDC0_DAT2

MSDC0_DAT0

MSDC0_DAT1

MSDC0_CLK

MSDC0_CMD

MSDC0_RSTB

L27

L29

K27

N26

N27

M26

M29

AK9

BPI_BUS0

AJ9

BPI_BUS1

AJ8

BPI_BUS2

AF10

BPI_BUS3

AG10

BPI_BUS4

AJ10

BPI_BUS5

AH11

BPI_BUS6

AJ11

BPI_BUS7

AF11

BPI_BUS8

AK10

BPI_BUS9

AG11

AB14

BSI0_CS0

AC14

BSI0_CS1

AF14

AA13

BSI0_CLK

AH15

BSI1_CS0

AG14

BSI1_CS1

AJ14

AG15

BSI1_CLK

TP1347PAD@ TP1347PAD@

TP1361PAD@ TP1361PAD@

TP1360PAD@ TP1360PAD@

TP1348PAD@ TP1348PAD@

MEM_PWR_EN (20)

LCM_BL_EN (22)

TP1350PAD@ TP1350PAD@

LCM_PWM4 (7)

TP1358PAD@ TP1358PAD@

LCM_VLED_EN (22)

LCM_RST (7)

LVDS_SHUTDOWN_N(7)

LCM_STBY (7)

Issued Date

Issued Date

Issued Date

EVREF (4,6)

UTXD2 (11)

TP1340PAD@ TP1340PAD@

TP1341PAD@ TP1341PAD@

URXD2 (11)

SRCLKENAI

0_0402_5%

0_0402_5%

100K_0402_5%

100K_0402_5%

MB_ID0 MB_ID1

100K_0402_5%

100K_0402_5%

DDR3VCCIO

1K_0402_1%

1K_0402_1%

R213

R213

1

1K_0402_1%

1K_0402_1%

C401

C401

1U_0402_10V6K

1U_0402_10V6K

@

@

R0224

R0224

12

VDD18_6575 VDD18_6575

@

@

R1687

R1687

R1689

R1689

R214

R214

2

OSC_EN_6620 (9)

1 2

1 2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

1 2

1 2

R1688

R1688

100K_0402_5%

100K_0402_5%

R1690

@ R1690

@

100K_0402_5%

100K_0402_5%

2

C534

C534

0.1U_0402_10V7K

0.1U_0402_10V7K

C531

C531

0.1U_0402_10V7K

0.1U_0402_10V7K

1 2

1 2

ED[0..31](6)

1

2

1

2

EA[0..14](6)

2013/11/032012/11/03

2013/11/032012/11/03

2013/11/032012/11/03

ED0

ED1

ED2

ED3

ED4

ED5

ED6

ED7

ED8

ED9

ED10

ED11

ED12

ED13

ED14

ED15

ED16

ED17

ED18

ED19

ED20

ED21

ED22

ED23

ED24

ED25

ED26

ED27

ED28

ED29

ED30

ED31

EVREF (4,6)

EBA2 (6)

EBA1 (6)

EBA0 (6)

EA14

EA13

EA12

EA11

EA10

EA9

EA8

EA7

EA6

EA5

EA4

EA3

EA2

EA1

EA0

ERESET_ (6)

R219

@ R219

@

1K_0402_5%

1K_0402_5%

12

driving calibration setting (LPDDR1/LPDDR2)

U201G

U201G

E3

RDN0

F3

RDP0

C2

RDN1

D2

RDP1

D1

RCN

E2

RCP

F2

TDN0

F1

TDP0

G1

TDN1

G2

TDP1

H4

TCN

G5

TCP

DPI_B0 (7)

DPI_B1 (7)

DPI_B2 (7)

DPI_B3 (7)

DPI_B4 (7)

DPI_B5 (7)

DPI_B6 (7)

DPI_B7 (7)

N2

DPIB0

P8

DPIB1

N7

DPIB2

P2

DPIB3

N3

DPIB4

M2

DPIB5

L2

DPIB6

T1

DPIB7

MT8317_DDR3

MT8317_DDR3

EMC@

EMC@

MC1CK MC1CK_RMC1CK_R

RF request to add.1102.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

@

@

U201F

U201F

C27

ED0

C23

ED1

D25

ED2

D24

ED3

B25

ED4

B24

D23

A26

A24

C24

A23

E21

A22

D21

B22

D20

B12

C12

D12

C11

A10

B10

B11

D11

D9

B9

D8

B8

C8

A9

C7

A7

D19

B21

B16

A13

A17

C15

B15

D16

C20

B14

B18

B13

A16

A14

D17

C16

D15

C19

B19

D7

@

@

DPIVSYNC

DPIHSYNC

R1669

R1669

1 2

0_0402_5%

0_0402_5%

EWR#

ERAS#

ED5

ECAS#

ED6

ECKE

ED7

ED8

ED9

DQM3

ED10

DQM2

ED11

DQM1

ED12

DQM0

ED13

ED14

EDQS3

ED15

EDQS2

ED16

EDQS1

ED17

EDQS0

ED18

/EDQS3

ED19

/EDQS2

ED20

/EDQS1

ED21

/EDQS0

ED22

ED23

/EDCLK

ED24

EDCLK

ED25

ED26

NLD15

ED27

NLD14

ED28

NLD13

ED29

NLD12

ED30

NLD11

ED31

NLD10

NLD9

RVREF

NLD8

NLD7

NLD6

EBA2

NLD5

EBA1

NLD4

EBA0

NLD3

EA14

NLD2

EA13

NLD1

EA12

NLD0

EA11

EA10

NRNB

NCLE

EA9

EA8

NALE

EA7

NWEB

NREB

EA6

EA5

NCEB0

EA4

NCEB1

EA3

EA2

EA1

MEMPLL_TXN

EA0

MEMPLL_TXP

DDR3RESET

MT8317_DDR3

MT8317_DDR3

T4

DPICK

DPIDE

DPIR0

DPIR1

DPIR2

DPIR3

DPIR4

DPIR5

DPIR6

DPIR7

DPIG0

DPIG1

DPIG2

DPIG3

DPIG4

DPIG5

DPIG6

DPIG7

MT8377 - Baseband

MT8377 - Baseband

MT8377 - Baseband

DPICK (7)

N5

DPIDE (7)

L5

DPIVSYNC (7)

M5

DPIHSYNC (7)

T2

DPI_R0 (7)

U4

DPI_R1 (7)

R1

DPI_R2 (7)

R2

DPI_R3 (7)

N1

DPI_R4 (7)

M1

DPI_R5 (7)

P6

DPI_R6 (7)

N8

DPI_R7 (7)

R5

DPI_G0 (7)

T5

DPI_G1 (7)

P4

DPI_G2 (7)

N4

DPI_G3 (7)

P7

DPI_G4 (7)

U5

DPI_G5 (7)

P3

DPI_G6 (7)

P5

DPI_G7 (7)

MC1CK_RMC1CK_R

2

C1653

C1653

10P_0402_50V8J

10P_0402_50V8J

1

@

@

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

LA-A031P

LA-A031P

LA-A031P

1

A19

B20

A20

B17

B7

A11

B23

B26

E9

E12

E20

E24

E10

E13

E19

E23

E16

E17

B30

B29

E27

G30

E29

C30

D30

A28

C28

G27

G29

D29

F29

D28

E26

B28

A29

B27

C29

E28

F30

F27

F28

K21

K22

1

/EWR (6)

/ERAS (6)

/ECAS (6)

ECKE

EDQM3 (6)

EDQM2 (6)

EDQM1 (6)

EDQM0 (6)

EDQS3 (6)

EDQS2 (6)

EDQS1 (6)

EDQS0 (6)

/EDQS3 (6)

/EDQS2 (6)

/EDQS1 (6)

/EDQS0 (6)

EDCLK_B (6)

EDCLK (6)

BPI_GPS (9)

MC1CK_R (17)

4 23Wednesday, December 19, 2012

4 23Wednesday, December 19, 2012

4 23Wednesday, December 19, 2012

(6)

TP1386PAD@ TP1386PAD@

TP1387PAD@ TP1387PAD@

1B

of

of

of

Page 5

5

4

3

2

1

@

@

U201H

AVDD28_RTC

AVSS28_RTC

2

0.1U 10V +-10% X7R 0402

F9

DDR3VCCIO

F12

F14

F15

F16

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

F17

F18

F21

F23

G11

G15

G17

N22

N23

N10

N11

P10

K8

AF13

AB12

AB8

AB9

AE5

AC9

Y25

U23

V23

R22

R23

P23

AK4

P11

K12

N12

P12

R12

T12

U12

V12

W12

L13

M13

W13

G14

H14

J14

W14

K15

V15

VDDK

K16

V16

K17

V17

G18

1U 6.3V K X5R 0402

1U 6.3V K X5R 0402

H18

J18

U18

V19

M20

N20

VDDK_DVFS

P20

R20

T20

U20

V20

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

M21

N21

P21

R21

T21

V21

M19

VDDK_MDVFS

U21

V22

0.1U 10V +-10% X7R 0402

C312

C312

1

C377

C377

Close to MT8317

VDD_NFI

VDD_LCD

DVDD_CAM

DVDD_BPI

VDD_NFI

C341

C341

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

DVDD_MC0

DVDD_MC1

DVDD_MC2

DVDD_MC3

C371

C371

C352

C352

C350

C350

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

D D

C C

H12

H16

H21

J8

J10

J13

J16

J19

J20

J22

J24

K14

K18

L14

L15

L16

L17

L18

M14

M15

M16

M17

M18

N13

N14

N15

N16

N17

N18

N19

P13

B B

A A

P14

P15

P16

P17

P18

P19

R13

R14

R15

R16

R17

R18

R19

T13

T14

T15

T16

T17

T18

T19

U13

U14

U15

U16

U17

U19

V13

V14

A30

AK30

AJ1

AK1

AK2

E25

C378

C378

1U 6.3V K X5R 0402

1U 6.3V K X5R 0402

A1

U201B

U201B

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

CORNER

CORNER

CORNER

CORNER

CORNER

CORNER

VDDK_DVFS_OUT

MT8317_DDR3

MT8317_DDR3

VPROC_FB

1 2

@

@

VDD_EMI

VDD_EMI

VDD_EMI

VDD_EMI

VDD_EMI

VDD_EMI

VDD_EMI

VDD_EMI

VDD_EMI

VDD_EMI

VDD_EMI

VDD_EMI

DVDD_NFI

DVDD_NFI

DVDD_LCD

DVDD_LCD

DVDD_LCD

DVDD_CAM

DVDD_BPI

DVDD_BSI

DVDD_NML1

DVDD_NML2

DVDD_NML3

DVDD_NML4

DVDD_NML5

DVDD_NML6

DVDD_NML6

DVDD_MC0

DVDD_MC1

DVDD_MC2

DVDD_MC3

VDDK_DVFS

VDDK_DVFS

VDDK_DVFS

VDDK_DVFS

VDDK_DVFS

VDDK_DVFS

VDDK_DVFS

VDDK_DVFS

VDDK_DVFS

VDDK_DVFS

VDDK_DVFS

VDDK_DVFS

VDDK_DVFS

VDDK_VSRAM

VDDK_VSRAM

VDDK_VSRAM

VPROC_FB (21)

5

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VDDK

VRTC

1

1

1

C334

C334

2

2.2U_0402_6.3VM

2.2U_0402_6.3VM

C398 0.1U 10V +-10% X7R 0402C398 0.1U 10V +-10% X7R 0402

C393 0.1U 10V +-10% X7R 0402C393 0.1U 10V +-10% X7R 0402

C392 0.1U 10V +-10% X7R 0402C392 0.1U 10V +-10% X7R 0402

C376 0.1U 10V +-10% X7R 0402C376 0.1U 10V +-10% X7R 0402

C347 0.1U 10V +-10% X7R 0402C347 0.1U 10V +-10% X7R 0402

1

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

1 2

1 2

1 2

1 2

1 2

1

C338

C338

2

1

1

C343

C343

C342

C342

C379

C379

2

2

C332

C332

2

1

2

1

2

Close to MT8317

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

Close to MT8317

1

2

1

C353

C353

2.2U_0402_6.3VM

2.2U_0402_6.3VM

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

C354

C354

2

Close to MT8317

1

2

C372

C372

C374

C374

2

2

1

1

Close to MT8317

1

1

C386

C386

C385

C385

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2.2U_0402_6.3VM

2.2U_0402_6.3VM

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

VTCXO_PMU

VDD25_VA1_6575

VDD25_VA1_6575

VDD25_VA1_6575

VDD25_VA1_6575

VDD25_VA2_6575

DDR3VCCIO

1

C333

C333

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

C337

C337

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

1

C355

C355

C391

C391

2

2

2.2U_0402_6.3VM

2.2U_0402_6.3VM

1

1

C358

C358

C357

C357

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

2

2.2U_0402_6.3VM

2.2U_0402_6.3VM

1

1

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

C375

C375

2

2

1

2.2U 10V K X7R 0603

2.2U 10V K X7R 0603

2

R378 0_0402_5%R378 0_0402_5%

R384 0_0402_5%R384 0_0402_5%

R382 0_0402_5%R382 0_0402_5%

R343 0_0402_5%R343 0_0402_5%

R323 0_0402_5%R323 0_0402_5%

R317 0_0402_5%R317 0_0402_5%

R379 0_0402_5%R379 0_0402_5%

R380 0_0402_5%R380 0_0402_5%

03/07 for Power noise

C246

C246

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

C368

C368

1

C364

C364

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

R391 0_0402_5%R391 0_0402_5%

C387

C387

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

4

AVDD28_RTC

AVSS28_RTC

12

C470 1U_0402_6.3V6KC470 1U_0402_6.3V6K

12

C459 1U_0402_6.3V6KC459 1U_0402_6.3V6K

12

C460 1U_0402_6.3V6KC460 1U_0402_6.3V6K

12

C461 1U_0402_6.3V6KC461 1U_0402_6.3V6K

12

C468 1U_0402_6.3V6KC468 1U_0402_6.3V6K

12

C469 1U_0402_6.3V6KC469 1U_0402_6.3V6K

C1618

C1618

1 2

C395 0.1U 10V +-10% X7R 0402C395 0.1U 10V +-10% X7R 0402

VDD_LCD

10U_0402_6.3V6M

10U_0402_6.3V6M

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

2

1 2

1 2

C394 0.1U 10V +-10% X7R 0402C394 0.1U 10V +-10% X7R 0402

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

C1656

C1656

C247

C247

1

1

2

2

10U_0402_6.3V6M

10U_0402_6.3V6M

10U_0402_6.3V6M

10U_0402_6.3V6M

1

C373

C373

2

1

C365

C365

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

10U_0402_6.3V6M

10U_0402_6.3V6M

AJ15

AK18

AK22

AC20

K23

H20

AK19

W15

AK21

W16

AC22

VDD18_6575

VCAM_IOPMU

VDD28_6575

VDD18_6575

VDD18_6575

VMC_6575

VDD28_6575

MT6620_SDIO1

C1657

C1657

1

1

2

2

10U_0402_6.3V6M

10U_0402_6.3V6M

1

C245

C245

10U_0402_6.3V6M

10U_0402_6.3V6M

2

1

C256

C256

2

VM12_INT_6575

AVDD28_RTC

AVSS28_RTC

AVDD28_DAC

AVDD25_MD

AVSS25_MD

AVDD25_MEMPLL

AVSS25_MEMPLL

AVDD25_VDAC

AVSS25_VDAC

AVDD25_PLL

AVSS25_PLL

AVDD25_VBUF

MT8317_DDR3

MT8317_DDR3

DVDD18_MIPITX

DVSS18_MIPITX

DVDD18_MIPIRX

DVSS18_MIPIRX

AVDD33_USB11

VMC_6575 3.3V power for SD card

VDDK

12

C248

C248

0.01UF_0402_25V7K

0.01UF_0402_25V7K

C1658

C1658

1

10U_0402_6.3V6M

10U_0402_6.3V6M

2

1

C1659

C1659

10U_0402_6.3V6M

10U_0402_6.3V6M

2

U201H

AH16

J1

H5

H3

AVDD18_MIPI

J5

AVSS18_MIPI

H2

J4

AK24

AVDD18_MD

AJ26

AVSS18_MD

AA28

V18

AVSS33_USB11

AB28

AVDD33_USB

W18

AVSS33_USB

AB30

AVDD30_VSIM

AE30

AVDD30_VSIM2

W17

AVSS30_VSIM

1

2

1

2

C521

C521

1U 6.3V K X5R 0402

1U 6.3V K X5R 0402

CT5

CT5

100U_1206_6.3V6M

100U_1206_6.3V6M

CT6

CT6

100U_1206_6.3V6M

100U_1206_6.3V6M

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

3

1 2

C339 0.1U 10V +-10% X7R 0402C339 0.1U 10V +-10% X7R 0402

1 2

C344 0.1U 10V +-10% X7R 0402C344 0.1U 10V +-10% X7R 0402

1 2

C360 0.1U 10V +-10% X7R 0402C360 0.1U 10V +-10% X7R 0402

VDD18_6575

1 2

C361 1U 6.3V K X5R 0402C361 1U 6.3V K X5R 0402

AVDD33_USB11

AVDD33_USB

VSIM_6575

VSIM2_6575

2

2

C520

C520

1U 6.3V K X5R 0402

1U 6.3V K X5R 0402

1

1

0_0402_5%

0_0402_5%

R315

R315

1 2

VCORE_6575

VAPROC_6575

Separate SIO1/2 and SCLK1/2

SIO/SCLK trace 6mil

1 2

VDD18_MIPI

ACCDET (8)

MICP0 (16)

MICN0 (16)

MICP1 (8)

MICN1 (8)

HPRP (21,8)

HPLP (21,8)

HSP (21)

HSN (21)

12

R456

R456

51K_0402_5%

51K_0402_5%

VDD18_6575

R344

R344

0_0402_5%

0_0402_5%

VUSB_6575

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

U201C

U201C

AF18

VDAC_OUT

AK28

ACCDET

AK25

NS_AU_VIN0_P

AJ25

NS_AU_VIN0_N

AJ27

NS_AU_VIN1_P

AK27

NS_AU_VIN1_N

AF25

NS_AU_VIN2_P

AE25

NS_AU_VIN2_N

AJ29

HPRP

AJ28

HPLP

AH28

HSP

AH29

HSN

AH30

AUDREFN

AF28

FMINR

AF27

FMINL

12

R451

R451

51K_0402_5%

51K_0402_5%

Compal Secret Data

Compal Secret Data

Compal Secret Data

4 mil trace Gnd Via

MT8317_DDR3

MT8317_DDR3

Close to MT6329

Deciphered Date

Deciphered Date

Deciphered Date

2

C367

C367

@

@

VSIM_6575

@

@

AVDD18_AUD

AVSS18_AUD

COUT_AVSS12N

AVSS12N_DAC

SCL_2

SDA_2

L301

L301

1 2

0_0402_5%

0_0402_5%

1

2

L302

L302

1 2

0_0402_5%

0_0402_5%

AF29

AG25

star connect to cap gnd

AK29

AVSS12N

AJ30

star connect to cap.(thicker)

AG29

FLYP

CF

AG30

AH27

AF26

AJ20

AJ17

AF16

AJ18

AJ19

AH19

AG19

AF17

AG18

AJ23

AJ22

4.7K_0402_5%

4.7K_0402_5%

2013/11/032012/11/03

2013/11/032012/11/03

2013/11/032012/11/03

FLYN

R206

R206

CF_IN

VMIC

EARBIAS

AUX_IN0

AUX_IN1

AUX_IN2

AUX_IN3

AUX_IN4

AUX_XM

AUX_XP

AUX_YM

AUX_YP

REFP

REFN

SCL_2

SDA_2

Cl

ose to MT8317

1

C356

C356

@

@

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

AVDD33_USB11

EARBIAS (8)

ADC1_ACCESSORY(8)

VDD18_6575

Close to MT8317

1

C369

C369

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

1 2

C313 2.2U 10V K X7R 0603C313 2.2U 10V K X7R 0603

1 2

C363 1U 6.3V K X5R 0402C363 1U 6.3V K X5R 0402

close to IC

1

C345

C345

1U 6.3V K X5R 0402

1U 6.3V K X5R 0402

2

4.7K_0402_5%

4.7K_0402_5%

R205

R205

1 2

1 2

(21,5)

(21,5)

U201D @

U201D @

W26

(21,5)

SCL_2

Y26

(21,5)

SDA_2

AD27

SRST

AC27

SIO

AD26

SCLK

AD29

SRST2

AD30

SIO2

AD28

SCLK2

MT8317_DDR3

MT8317_DDR3

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

AVDD33_USB

1

C366

C366

1U 6.3V K X5R 0402

1U 6.3V K X5R 0402

2

AVDD33_USB11AVDD33_USB11AVDD33_USB11

C458

C458

1 2

0_0402_5%

0_0402_5%

1

C362

C362

1U 6.3V K X5R 0402

1U 6.3V K X5R 0402

2

ADC0: Not used

ADC1: Accessory

ADC2: UMTS Power

ADC3: UMTS Temp

USB11_DM

USB11_DP

PACTRL0

PACTRL1

PACTRL2

PMUCTRL0

PMUCTRL1

MT8377 - Power and ABB

MT8377 - Power and ABB

MT8377 - Power and ABB

VDD18_6575

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

VBAT_SUPPLY

R327

R327

12

VMIC

AC29

AB29

V30

PACTRL0 (21)

V28

PACTRL1 (21)

W29

PACTRL2 (21)

W27

PMUCTRL0 (21)

V27

PMUCTRL1 (21)

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

LA-A031P

LA-A031P

LA-A031P

1

12

100K_0402_1%

100K_0402_1%

R332

R332

R376

R376

100K_0402_1%

100K_0402_1%

1 2

5 23Wednesday, November 28, 2012

5 23Wednesday, November 28, 2012

5 23Wednesday, November 28, 2012

1B

of

of

of

Page 6

5

ED3

ED6

ED2

ED5

ED1

ED4

ED0

ED7

ED8

D D

ED0

ED1

ED2

ED3

ED4

ED5

ED6

ED7

ED8

ED9

ED10

ED11

ED12

ED13

ED14

ED15

ED16

ED17

ED18

ED19

ED20

ED21

ED22

ED23

ED24

ED25

ED26

ED27

C C

ED[0..31]

EBA1 (4)

/EWR (4)

ECKE

EBA0 (4)

ERESET_ (4)

EBA2 (4)

/ERAS (4)

/ECAS (4)

ED28

ED29

ED30

(4)

ED31

(4)

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

EVREF (4,6)

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

ED13

ED14

ED15

ED10

ED9

ED12

ED11

EDQS1

/EDQS1 (4)

EDQS0

/EDQS0 (4)

EDQM1

EDQM0

1

C61

C61

2

240_0402_1%

240_0402_1%

1

C66

C66

2

E3

F7

F2

F8

H3

H8

G2

H7

D7

C3

C8

C2

A7

A2

B8

A3

C7

(4)

B7

F3

(4)

G3

D3

(4)

E7

(4)

H1

EVREF

M8

T2

RRESET_R

L8

12

R65

R65

A1

A8

C1

C9

D2

E9

F1

H2

H9

B2

D9

G7

K2

K8

N1

N9

R9

R1

Compal footptint Compal footptint

4

U5

U5

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

UDQS

UDQS#

LDQS

LDQS#

UDM

LDM

VREFDQ

VREFCA

RESET#

ZQ

VDDQ_0

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDD_0

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_8

VDD_7

IC DDR3 x16 FBGA-96

IC DDR3 x16 FBGA-96

MT41J256M16RE-15E-D_FBGA_96P

MT41J256M16RE-15E-D_FBGA_96P

@

@

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC#

T3

A13

J1

NC_0

J9

NC_1

L1

NC_2

L9

NC_3

M7

NC_4

T7

NC_6

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK#

L2

CS#

K3

CAS#

K1

ODT

J3

RAS#

L3

WE#

K9

CKE

B1

VSSQ_0

B9

VSSQ_1

D1

VSSQ_2

D8

VSSQ_3

E2

VSSQ_4

E8

VSSQ_5

F9

VSSQ_6

G1

VSSQ_7

G9

VSSQ_8

A9

VSS_0

B3

VSS_1

E1

VSS_2

G8

VSS_3

J2

VSS_4

J8

VSS_5

M1

VSS_6

M9

VSS_7

P1

VSS_8

P9

VSS_9

T1

VSS_10

T9

VSS_11

RCS1__R RODT1_R

1K_0402_1%

1K_0402_1%

RA0_R

RA1_R

RA2_R

RA3_R

RA4_R

RA5_R

RA6_R

RA7_R

RA8_R

RA9_R

RA10_R

RA11_R

RA12_R

RA13_R

RA14_R

RBA0_R

RBA1_R

RBA2_R

RCS1__R

RCAS__R

RODT1_R

RRAS__R

RWE__R

RCKE_R

R77

R77

3

U6

U6

ED20

ED19

ED22

ED23

ED18

ED21

ED16

ED17

ED30

ED29

ED28

ED25

ED24

ED31

ED26

ED27

EDQS3

/EDQS3 (4)

EDQS2

/EDQS2 (4)

EDQM3

EDQM2

EDCLK

EDCLK_B

12

(4,6)

(4,6)

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

12

R75

R75

0_0402_5%

0_0402_5%

12

R76

R76

1K_0402_1%

1K_0402_1%

EVREF (4,6)EVREF (4,6)

1

C69

C69

2

240_0402_1%

EVREF (4,6)

@

@

240_0402_1%

DDR3VCCIODDR3VCCIO

1

C65

C65

2

E3

DQ0

F7

DQ1

F2

DQ2

F8

DQ3

H3

DQ4

H8

DQ5

G2

DQ6

H7

DQ7

D7

DQ8

C3

DQ9

C8

DQ10

C2

DQ11

A7

DQ12

A2

DQ13

B8

DQ14

A3

DQ15

C7

(4)

UDQS

B7

UDQS#

F3

(4)

LDQS

G3

LDQS#

D3

(4)

UDM

E7

(4)

LDM

H1

EVREF

RRESET_R_2 RCAS__R_2

TP41 PAD @TP41 PAD @

TP38 PAD @TP38 PAD @

TP39 PAD @TP39 PAD @

TP40 PAD @TP40 PAD @

M8

T2

L8

12

R71

R71

A1

A8

C1

C9

D2

E9

F1

H2

H9

B2

D9

G7

K2

K8

N1

N9

R9

R1

IC DDR3 x16 FBGA-96

IC DDR3 x16 FBGA-96

MT41J256M16RE-15E-D_FBGA_96P

MT41J256M16RE-15E-D_FBGA_96P

@

@

VREFDQ

VREFCA

RESET#

ZQ

VDDQ_0

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDD_0

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_8

VDD_7

A12/BC#

VSSQ_0

VSSQ_1

VSSQ_2

VSSQ_3

VSSQ_4

VSSQ_5

VSSQ_6

VSSQ_7

VSSQ_8

EDCLK

EDCLK

EDCLK_B

EDCLK_B

A10/AP

NC_0

NC_1

NC_2

NC_3

NC_4

NC_6

CAS#

ODT

RAS#

WE#

VSS_0

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

N3

RA0_R_2

A0

P7

RA1_R_2

A1

P3

RA2_R_2

A2

N2

RA3_R_2

A3

P8

RA4_R_2

A4

P2

RA5_R_2

A5

R8

RA6_R_2

A6

R2

RA7_R_2

A7

T8

RA8_R_2

A8

R3

RA9_R_2

A9

L7

RA10_R_2

R7

RA11_R_2

A11

N7

RA12_R_2

T3

RA13_R_2

A13

J1

J9

L1

L9

M7

T7

RA14_R_2

M2

RBA0_R_2

BA0

N8

RBA1_R_2

BA1

M3

RBA2_R_2

BA2

J7

K7

L2

K3

K1

J3

L3

K9

B1

B9

D1

D8

E2

E8

F9

G1

G9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

RCS2__R

RODT2_R

RRAS__R_2

RWE__R_2

RCKE_R_2

1K_0402_1%

1K_0402_1%

EDCLK

EDCLK_B

RCS2__R

12

R70

R70

CK

CK#

CS#

CKE

(4,6)

(4,6)

DDR3VCCIODDR3VCCIO

0_0402_5%

0_0402_5%

RODT2_R

1K_0402_1%

1K_0402_1%

R73

R73

R72

R72

1 2

12

12

100_0402_5%

100_0402_5%

R525

R525

@

@

EDCLK

EDCLK_B

2

RN1

RN1

(4,6)

(4,6)

SD309220A80

SD309220A80

22 +-5% 8P4R 0804

22 +-5% 8P4R 0804

RN2

RN2

SD309220A80

SD309220A80

22 +-5% 8P4R 0804

22 +-5% 8P4R 0804

RN3

RN3

SD309220A80

SD309220A80

22 +-5% 8P4R 0804

22 +-5% 8P4R 0804

RN4

RN4

SD309220A80

SD309220A80

22 +-5% 8P4R 0804

22 +-5% 8P4R 0804

RN5

RN5

SD309220A80

SD309220A80

22 +-5% 8P4R 0804

22 +-5% 8P4R 0804

RN6

RN6

SD309220A80

SD309220A80

22 +-5% 8P4R 0804

22 +-5% 8P4R 0804

RN1 22x4

RN1 22x4

RN0402_SMD

RN0402_SMD

RN2 22x4

RN2 22x4

RN0402_SMD

RN0402_SMD

RN3 22x4

RN3 22x4

RN0402_SMD

RN0402_SMD

RN4 22x4

RN4 22x4

RN0402_SMD

RN0402_SMD

RN5 22x4

RN5 22x4

RN0402_SMD

RN0402_SMD

RN6 22x4

RN6 22x4

RN0402_SMD

RN0402_SMD

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

RA6_R

RA11_REA11

RCAS__R/ECAS

RRAS__R/ERAS

RWE__R/EWR

RCKE_RECKE

RBA2_REBA2

RA5_REA5

RA13_R

RRESET_R

EA14 RA14_R_2

EA11 RA11_R_2

EA8 RA8_R_2

EA6 RA6_R_2

/ERAS RRAS__R_2

/ECAS RCAS__R_2

EBA2 RBA2_R_2

EA10 RA10_R_2

EA2 RA2_R_2

EA5 RA5_R_2

EA0 RA0_R_2

EA3 RA3_R_2

EA13 RA13_R_2

EA9 RA9_R_2

EA7 RA7_R_2

EA1

EA4 RA4_R_2

EA12 RA12_R_2

EBA1 RBA1_R_2

EA6

EA8 RA8_R

EA14 RA14_R

EA10 RA10_R

EBA0 RBA0_R ECKE RCKE_R_2

EA3 RA3_R

EA0 RA0_R

EA2 RA2_R

EA7 RA7_R

EA9 RA9_R

EA13

ERESET_

EBA1 RBA1_R

EA12 RA12_R

EA4 RA4_R

EA1 RA1_R

RN7

RN7

RN8

RN8

RN9

RN9

RN10

RN10

RN11

RN11

RN12

RN12

RN11 22x4

RN11 22x4

RN0402_SMD

RN0402_SMD

RN7 22x4

RN7 22x4

RN0402_SMD

RN0402_SMD

RN8 22x4

RN8 22x4

RN0402_SMD

RN0402_SMD

RN9 22x4

RN9 22x4

RN0402_SMD

RN0402_SMD

RN10 22x4

RN10 22x4

RN0402_SMD

RN0402_SMD

RN12 22x4

RN12 22x4

RN0402_SMD

RN0402_SMD

1

SD309220A80

SD309220A80

22 +-5% 8P4R 0804

22 +-5% 8P4R 0804

SD309220A80

SD309220A80

22 +-5% 8P4R 0804

22 +-5% 8P4R 0804

SD309220A80

SD309220A80

22 +-5% 8P4R 0804

22 +-5% 8P4R 0804

SD309220A80

SD309220A80

22 +-5% 8P4R 0804

22 +-5% 8P4R 0804

SD309220A80

SD309220A80

22 +-5% 8P4R 0804

22 +-5% 8P4R 0804

SD309220A80

SD309220A80

22 +-5% 8P4R 0804

22 +-5% 8P4R 0804

12

34

56

78

12

34

RWE__R_2/EWR

56

78

12

RBA0_R_2EBA0

34

56

78

12

34

56

78

12

RRESET_R_2ERESET_

34

56

78

12

RA1_R_2

34

56

78

B B

DDR3VCCIO DDR3VCCIO DDR3VCCIODDR3VCCIO DDR3VCCIO

1

C71

C71

0.1U 10V +-10% X7R 0402

EA[0..14] (4)

A A

EA0

EA1

EA2

EA3

EA4

EA5

EA6

EA7

EA8

EA9

EA10

EA11

EA12

EA13

EA14

5

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

1

C62

C62

2

1

C73

C73

2

1

C64

C64

2

1

C56

C56

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

1

C70

C70

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

C58

C58

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

1

C72

C72

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

C60

C60

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

DDR3VCCIODDR3VCCIO DDR3VCCIODDR3VCCIO DDR3VCCIO

C74

C74

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

DDR3VCCIODDR3VCCIO DDR3VCCIODDR3VCCIO

C63

C63

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

DDR3VCCIODDR3VCCIO DDR3VCCIODDR3VCCIO

C75

C75

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

C67

C67

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

1

C54

C54

2

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

1

C68

C68

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

1

C59

C59

0.1U 10V +-10% X7R 0402

0.1U 10V +-10% X7R 0402

2

4

1

2

1

2

1

2

1

2

DDR3VCCIO

DDR3VCCIO

1

C1619

C1619

2.2U 10V K X7R 0603

2.2U 10V K X7R 0603

2

1

C1620

C1620

2.2U 10V K X7R 0603

2.2U 10V K X7R 0603

2

1

C1626

C1626

2.2U_0402_6.3VM

2.2U_0402_6.3VM

2

1

C1627

C1627

2.2U_0402_6.3VM

2.2U_0402_6.3VM

2

U5

U5

U5

U5

Hyn 256Mx16@

Hyn 256Mx16@

SA00005GI10

SA00005GI10

H5TQ4G63MFR-PBC

H5TQ4G63MFR-PBC

Nan 256Mx16@

Nan 256Mx16@

SA00006HI10

SA00006HI10

NT5CB256M16BP-CG

NT5CB256M16BP-CG

3

U6

U6

Hyn 256Mx16@

Hyn 256Mx16@

SA00005GI10

SA00005GI10

H5TQ4G63MFR-PBC

H5TQ4G63MFR-PBC

U6

U6

Nan 256Mx16@

Nan 256Mx16@

SA00006HI10

SA00006HI10

NT5CB256M16BP-CG

NT5CB256M16BP-CG

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2013/11/032012/11/03

2013/11/032012/11/03

2013/11/032012/11/03

U5 Test Point

TP01 PAD @TP01 PAD @

TP02 PAD @TP02 PAD @

TP03 PAD @TP03 PAD @

TP04 PAD @TP04 PAD @

TP05 PAD @TP05 PAD @

TP06 PAD @TP06 PAD @

TP07 PAD @TP07 PAD @

TP08 PAD @TP08 PAD @

TP09 PAD @TP09 PAD @

TP10 PAD @TP10 PAD @

TP11 PAD @TP11 PAD @

TP12 PAD @TP12 PAD @

TP13 PAD @TP13 PAD @

TP14 PAD @TP14 PAD @

TP15 PAD @TP15 PAD @

TP16 PAD @TP16 PAD @

TP17 PAD @TP17 PAD @

TP18 PAD @TP18 PAD @

TP19 PAD @TP19 PAD @

TP20 PAD @TP20 PAD @

TP21 PAD @TP21 PAD @

TP22 PAD @TP22 PAD @

TP23 PAD @TP23 PAD @

TP24 PAD @TP24 PAD @

TP25 PAD @TP25 PAD @

TP26 PAD @TP26 PAD @

TP27 PAD @TP27 PAD @

TP28 PAD @TP28 PAD @

TP29 PAD @TP29 PAD @

TP30 PAD @TP30 PAD @

TP31 PAD @TP31 PAD @

TP32 PAD @TP32 PAD @

TP33 PAD @TP33 PAD @

TP34 PAD @TP34 PAD @

TP35 PAD @TP35 PAD @

TP36 PAD @TP36 PAD @

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

RRAS__R

RCAS__R

RWE__R

RCKE_R

RBA0_R

RBA1_R

EDQM0

EDQM1

EDQS0

/EDQS0

EDQS1

/EDQS1

RA9_R

RA10_R

ED1

ED5

ED10

ED15

U6 Test Point

RRAS__R_2

RCAS__R_2

RWE__R_2

RCKE_R_2

RBA0_R_2

RBA1_R_2

EDQM2

EDQM3

EDQS2

/EDQS2

EDQS3

/EDQS3

RA9_R_2

RA10_R_2

ED20

ED21

ED30

ED31

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Memory (DDR3)

Memory (DDR3)

Memory (DDR3)

LA-A031P

LA-A031P

LA-A031P

1

6 23Tuesday, December 18, 2012

6 23Tuesday, December 18, 2012

6 23Tuesday, December 18, 2012

of

of

of

1B

Page 7

5

+LCD_VCOM

JP3

JP3

40

42

GND

41

GND

STBYB=1 "Normal mode"

STBYB=0 "timing control"

D D

ACES_88716-4001

ACES_88716-4001

CONN@

CONN@

C C

B B

LCM_VCOM

40

39

LCM_VDD

39

38

38

37

37

36

36

35

35

34

34

33

CN_LCM_RIN0-

33

32

CN_LCM_RIN0+

32

31

31

30

CN_LCM_RIN1-

30

29

CN_LCM_RIN1+

29

28

28

27

CN_LCM_RIN2-

27

26

CN_LCM_RIN2+

26

25

25

24

CN_LCM_CLKIN-

24

23

CN_LCM_CLKIN+

23

22

22

21

CN_LCM_RIN3-

21

20

CN_LCM_RIN3+

20

19

19

18

18

17

17

16

16

15

15

14

14

13

13

12

12

11

11

10

10

9

9

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

DPI_B0 (4)

DPI_B1 (4)

DPI_B2 (4)

DPI_B3 (4)

DPI_B4 (4)

DPI_B5 (4)

DPI_B6 (4)

DPI_B7 (4)

DPI_R0 (4)

DPI_R1 (4)

DPI_R2 (4)

DPI_R3 (4)

DPI_R4 (4)

DPI_R5 (4)

DPI_R6 (4)

DPI_R7 (4)

DPICK (4)

DPIDE (4)

DPIVSYNC (4)

DPIHSYNC (4)

DPI_G0 (4)

DPI_G1 (4)

DPI_G2 (4)

DPI_G3 (4)

DPI_G4 (4)

DPI_G5 (4)

DPI_G6 (4)

DPI_G7 (4)

LCM_RST_3V3

LCM_STBY_3V3

LCM_AVDD

LCM_LR_SEL

LCM_UD_SEL

LCM_VGL

LCM_VGH

CABC1

CABC0

10K_0402_5%

10K_0402_5%

VDD33_6575

R372

R372

0_0402_5%

0_0402_5%

1 2

12

R3730_0402_5% R3730_0402_5%

12

R54

R54

0_0402_5%

0_0402_5%

LCM_LEDK (22)

CABC1

CABC0

1 2

R57 0_0402_5%R57 0_0402_5%

LCM_LEDA (22)

R1675

R1675

1 2

1 2

1U 6.3V K X5R 0402

1U 6.3V K X5R 0402

12

R620_0402_5% R620_0402_5%

R1676

R1676

10K_0402_5%

10K_0402_5%

DPICK

LCM_VCOM

LCM_VDD

1U 6.3V K X5R 0402

1U 6.3V K X5R 0402

C1346

C1346

LCM_AVDD

LCM_VGL

LCM_VGH

C1343

C1343

LCM_DIMO_R (22)

AVDD

VGL

12

12

R630_0402_5% @ R 630_0402_5% @

R640_0402_5% @ R 640_0402_5% @

VGH

TP1367 PAD @TP1367 PAD @

R16860_0402_5% R16860_0402_5%

2

1

1

2

CABC_ENABLE1 (4)

CABC_ENABLE0 (4)

12

1 : Rising edge

0 : Falling edge

2

1U 6.3V K X5R 0402

1U 6.3V K X5R 0402

C1347

C1347

1

2

1U 6.3V K X5R 0402

1U 6.3V K X5R 0402

C1344

C1344

1

@

@

R879

R879

1 2

0_0402_5%

0_0402_5%

1 2

R880100K_0402_5% R 880100K_0402_5%

LCM_LR_SEL

LCM_UD_SEL

LVDS Bridge

DPI_R0

DPI_R1

DPI_R2

DPI_R3

DPI_R4

DPI_R5

DPI_R6

DPI_R7

DPI_G0

DPI_G1

DPI_G2

DPI_G3

DPI_G4

DPI_G5

DPI_G6

DPI_G7

DPI_B0

DPI_B1

DPI_B2

DPI_B3

DPI_B4

DPI_B5

DPI_B6

DPI_B7

DPIHSYNC

DPIVSYNC

LVDS83A_SHDTN

DPIDE

DPICK_R

LVDS83A_CLKSEL

4

2

1U 6.3V K X5R 0402

1U 6.3V K X5R 0402

C1345

C1345

1

VDD33_6575

R877

R877

1 2

100K_0402_5%

100K_0402_5%

1 2

@

@

R878 0_0402_5%

R878 0_0402_5%

U2

U2

51

D0

52

D1

54

D2

55

D3

56

D4

3

D6

50

D27

2

D5

4

D7

6

D8

7

D9

11

D12

12

D13

14

D14

8

D10

10

D11

15

D15

19

D18

20

D19

22

D20

23

D21

24

D22

16

D16

18

D17

27

D24

28

D25

32

SHTDN#

30

D26

25

D23

31

CLKIN

17

CLKSEL

SN75LVDS83BDGGR_TSSOP56

SN75LVDS83BDGGR_TSSOP56

LVDSVcc

PLLVcc

CLKOUTP

CLKOUTM

GND

GND

GND

GND

GND

PLLGND

PLLGND

LVDSGND

LVDSGND

LVDSGND

3

L1009

EMC@ L1009

CN_LCM_RIN0+

CN_LCM_RIN0-

CN_LCM_RIN1+

CN_LCM_RIN1-

CN_LCM_RIN2+

CN_LCM_RIN2-

CN_LCM_CLKIN+

CN_LCM_CLKIN-

CN_LCM_RIN3+

CN_LCM_RIN3-

1

Vcc

9

Vcc

26

Vcc

44

34

47

Y0P

48

Y0M

45

Y1P

46

Y1M

41

Y2P

42

Y2M

37

Y3P

38

Y3M

39

40

5

13

21

53

29

33

35

36

43

49

EMC@

3 4

OCE2012120YZF_4P

OCE2012120YZF_4P

EMC@ L1010

EMC@

3 4

OCE2012120YZF_4P

OCE2012120YZF_4P

EMC@ L1011

EMC@

3 4

OCE2012120YZF_4P

OCE2012120YZF_4P

EMC@ L1012

EMC@

3 4

OCE2012120YZF_4P

OCE2012120YZF_4P

EMC@ L1013

EMC@

3 4

OCE2012120YZF_4P

OCE2012120YZF_4P

LVDS83A_IOVCC

LVDS83A_VCC

LVDS83A_LVDSVCC

LVDS83A_PLLVCC

LCM_RIN0+

LCM_RIN0-

LCM_RIN1+

LCM_RIN1-

LCM_RIN2+

LCM_RIN2-

LCM_RIN3+

LCM_RIN3-

LCM_CLKIN+

LCM_CLKIN-

L1010

L1011

L1012

L1013

12

12

12

12

12

LCM_RIN0+

LCM_RIN0-

LCM_RIN1+

LCM_RIN1-

LCM_RIN2+

LCM_RIN2-

LCM_CLKIN+

LCM_CLKIN-

LCM_RIN3+

LCM_RIN3-

2.2U_0603_10V6K

2.2U_0603_10V6K

LCD3V3_POWER_EN (4)

LEVEL_SHIFT_EN (4)

LCM_PWM4 (4) LCM_BLU_PWM (22)

TP1359 PAD @TP1359 PAD @

LCM_RST (4)

LCM_STBY (4)

VDD18_6575

R1681

R1681

100K_0402_5%

100K_0402_5%

1 2

13

D

D

2

LCM_RST

G

G

S

S

Q3

Q3

BSS138W-7-F_SOT323-3~D

BSS138W-7-F_SOT323-3~D

C1615

C1615

2

VBAT

1 2

R1640 0_0402_5%R1640 0_0402_5%

12

R415

R415

0_0402_5%

0_0402_5%

R1638

R1638

100K_0402_5%

100K_0402_5%

12

@

R463 0_0402_5%

R463 0_0402_5%

R396 0_0402_5%

R396 0_0402_5%

R397 0_0402_5%

R397 0_0402_5%

VDD33_6575

R1679

R1679

100K_0402_5%

100K_0402_5%

1 2

LCM_RST_3V3

13

D

D

2

Q1

Q1

G

G

BSS138W-7-F_SOT323-3~D

BSS138W-7-F_SOT323-3~D

S

S

12

APL5320-33BI-TRG SOT-23 5P LDO

APL5320-33BI-TRG SOT-23 5P LDO

12

VDD18_6575

@

@

R876

R876

0_0402_5%

0_0402_5%

1 2

@

@

12

C44 0.1U_0402_25V4Z

C44 0.1U_0402_25V4Z

SHIFT_EN_R

R4440_0402_5%@R4440_0402_5%

1 2

@

@

1 2

@

@

1 2

@

@

U21

U21

1

VDD

5

VOUT

2

GND

4

VFB

3

CE

PN: SA00005J700

U1615

U1615

B2

VL

B3

EN

A1

IOVL1

A2

IOVL2

A3

IOVL3

A4

IOVL4

NLSX4378FCT1G_BGA12

NLSX4378FCT1G_BGA12

VDD18_6575

R1682

R1682

100K_0402_5%

100K_0402_5%

2

LCM_STBY

G

G

Q4

Q4

BSS138W-7-F_SOT323-3~D

BSS138W-7-F_SOT323-3~D

12

LCM_BLU_PWMLCM_PWM4

R16830_0402_5% R16830_0402_5%

@

@

IOVCC1

IOVCC2

IOVCC3

IOVCC4

1 2

13

D

D

S

S

0_0402_5%

0_0402_5%

VCC

GND

R1685

R1685

@

@

B1

B4

C1

C2

C3

C4

12

VDD33_6575

VDD33_6575

2

G

G

LCM_RST_3V3

LCM_STBY_3V3

1 2

13

D

D

S

S

1

VDD33_6575 VGP

R387

R387

1 2

0_0603_5%

0_0603_5%

C43

C43

12

@

@

0.1U_0402_25V4Z

0.1U_0402_25V4Z

R1680

R1680

100K_0402_5%

100K_0402_5%

LCM_STBY_3V3

Q2

Q2

BSS138W-7-F_SOT323-3~D

BSS138W-7-F_SOT323-3~D

@ R398

@

12

C1616

C1616

2.2U_0603_10V6K

2.2U_0603_10V6K

R398

1 2

0_0603_5%

0_0603_5%

TP1357PAD@ TP1357PAD@

VDD33_6575VDD18_6575

LVDS83A_VCC

1

C535

C535

0.1U_0402_25V4Z

0.1U_0402_25V4Z

2

LVDS83A_LVDSVCC

1

C538

C538

0.1U_0402_25V4Z

0.1U_0402_25V4Z

2

1

2

1

2

5

0.01U_0402_25V7K

0.01U_0402_25V7K

0.1U_0402_25V4Z

0.1U_0402_25V4Z

C536

C536

0.01U_0402_25V7K

0.01U_0402_25V7K

A A

C539

C539

0.01U_0402_25V7K

0.01U_0402_25V7K

C533

C533

C541

C541

LVDS83A_PLLVCC

1

C532

C532

0.1U_0402_25V4Z

0.1U_0402_25V4Z

2

LVDS83A_IOVCC

1

2

0.1U_0402_25V4Z

0.1U_0402_25V4Z

C537

C537

2

1

1

2

LVDS83A_IOVCC

LVDS83A_VCC

LVDS83A_LVDSVCC

LVDS83A_PLLVCC

LVDS83A_CLKSEL

12

R4160_0402_5% R4160_0402_5%

12

R4090_0402_5% R4090_0402_5%

12

R4120_0402_5% R4120_0402_5%

12

R4130_0402_5% R4130_0402_5%

R1641

R1641

0_0402_5%

0_0402_5%

@

@

1 2

1 2

4

R1643

R1643

4.7K_0402_5%

4.7K_0402_5%

@

@

LVDS83A_SHDTN

LVDS83A_CLKSEL

R410

R410

1 2

0_0402_5%

0_0402_5%

VDD18_6575

10K_0402_1%

10K_0402_1%

R1642

R1642

1 2

LVDS_SHUTDOWN_N(4)

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2013/11/032012/11/03

2013/11/032012/11/03

2013/11/032012/11/03

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

ze Document Number Rev

Si

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

LCD

LCD

LCD

LA-A031P

LA-A031P

LA-A031P

1

7 23Tuesday, December 18, 2012

7 23Tuesday, December 18, 2012

7 23Tuesday, December 18, 2012

of

of

of

1B

Page 8

5

4

3

2

1

Earphone RECEIVER

R457

R457

1 2

47K +-5% 0402

47K +-5% 0402

(4)

VDD18_6575

12

R454

R454

470K_0402_5%

470K_0402_5%

EMC@ FBM A-L11-160808-700LMT_2P

EMC@ FBM A-L11-160808-700LMT_2P

1 2

L1016

L1016

EMC@ FBM A-L11-160808-700LMT_2P

EMC@

EMC@

L1018

L1019

EMC@