Page 1

A

B

C

D

E

ZZZ0

ZZZ0

ZZZ1

ZZZ1

ZZZ2

ZZZ2

ZZZ3

ZZZ3

ZZZ4

ZZZ4

ZZZ5

ZZZ5

PCB DAZ0I200101

MB DA60000KP10

LS-7074P

LS-7071P

PCB

PCB

M/B

M/B

DAZ@

DAZ@

1 1

LA-7071P

LA-7071P

M/B

M/B

DA@

DA@

LS-7071P

USB IO/B

USB IO/B

DA@

DA@

LS-7074P

HDD/B

HDD/B

DA@

DA@

LS-7075P

LS-7075P

LED/B

LED/B

DA@

DA@

LA-7076P

LA-7076P

TP/B

TP/B

DA@

DA@

USB IO/B DA60000KQ10

HDD/B DA400011R10

LED/B DA400011T10

TP/B DA400013910

Compal Confidential

2 2

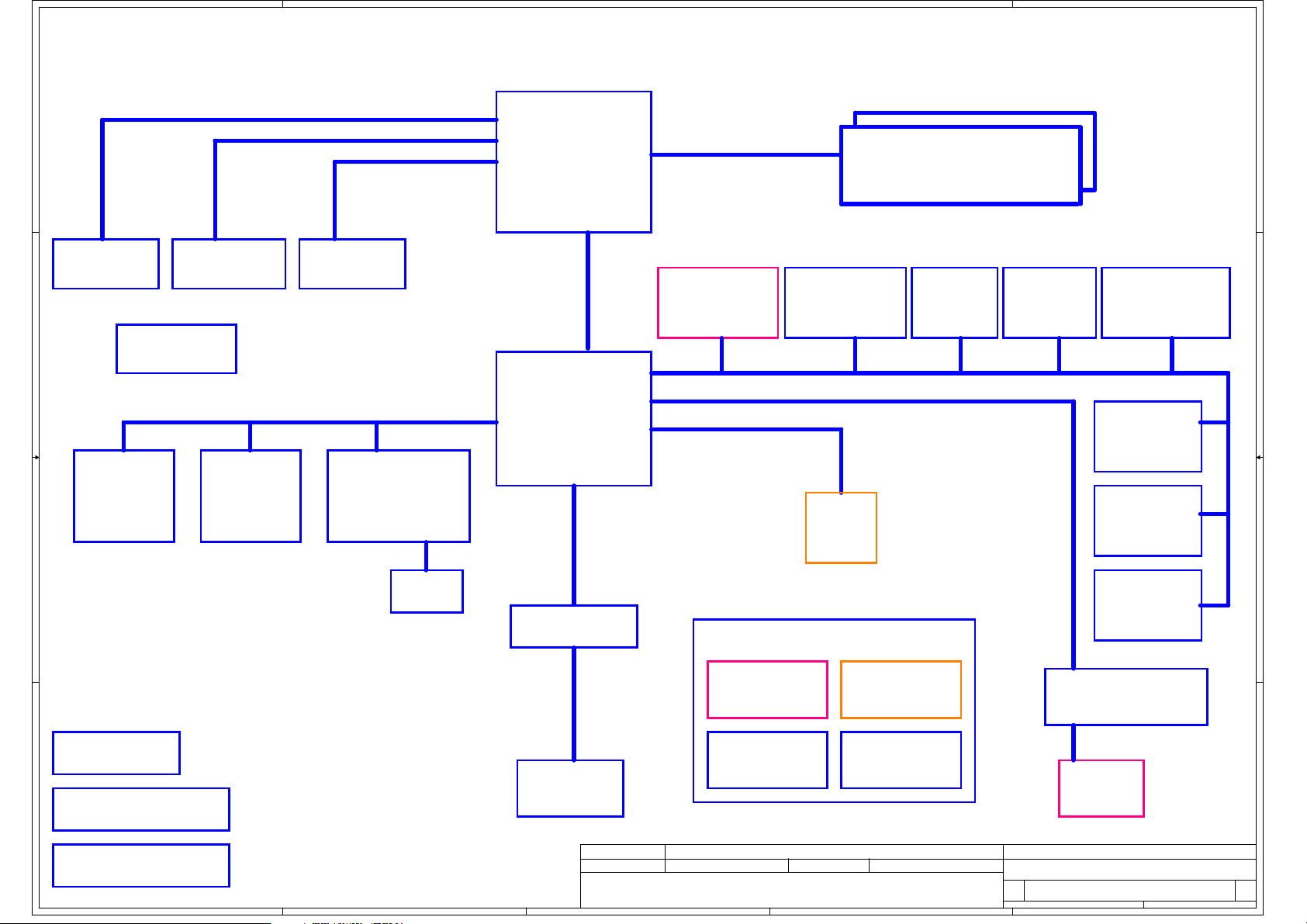

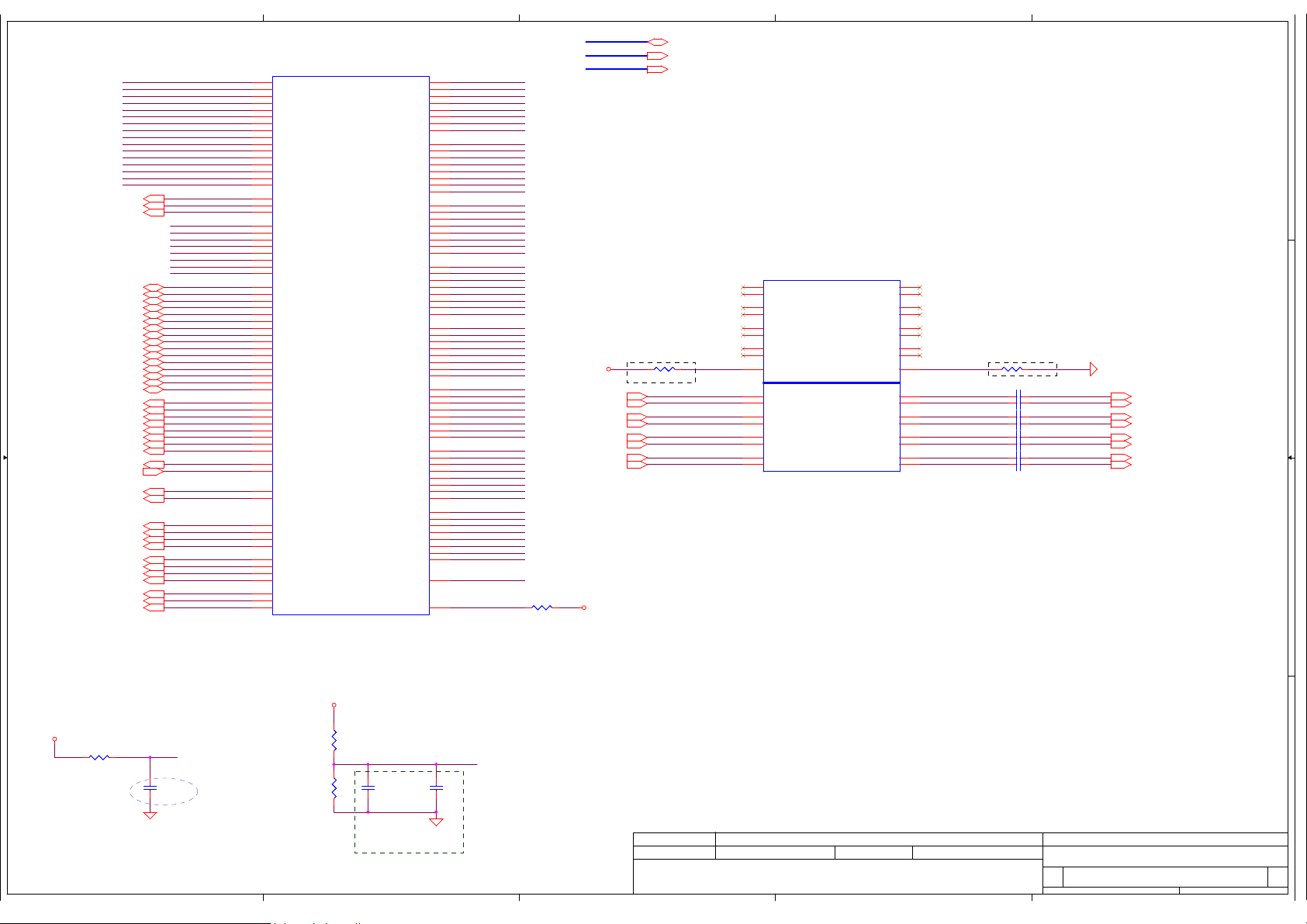

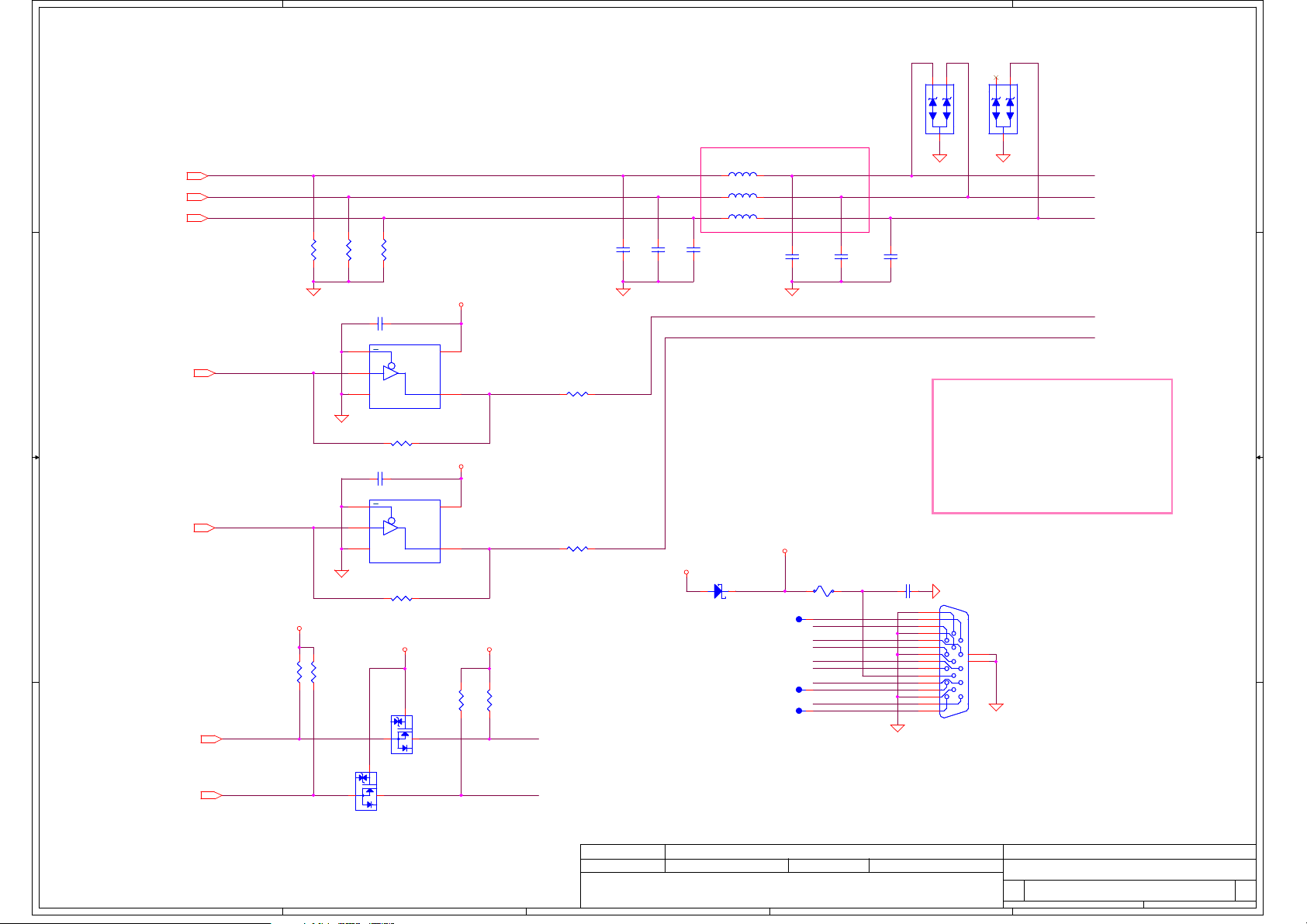

P1VE6 LA7071P Schematics Document

AMD Ontario Processor with DDRIII + Hudson M1

11.6" M/B

3 3

2011-03-17

Rev : 1.0

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/11/09 2012/11/09

2010/11/09 2012/11/09

2010/11/09 2012/11/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

P1VE6 Schematics

P1VE6 Schematics

P1VE6 Schematics

1 37Thursday, March 17, 2011

1 37Thursday, March 17, 2011

1 37Thursday, March 17, 2011

E

1.0

1.0

1.0

Page 2

A

Compal Confidential

B

C

D

E

Model Name : P1VE6

Brazos Platform

File Name : LA-7071P

1 1

HDMI

RGB

LVDS

HDMI Conn.

Page 10

2 2

Fan Circuit

PWM

D-Sub Conn.

Page 11

Page 27

LVDS Conn.

Page 9

PCI-Express X3

100MHz

Port 1

WWAN

JMINI1

WLAN

JMINI2

Media processor Wireless Card

Port 1

Page 20

3 3

Port 3 Port 2

Page 21

PCIE Gen1 2.5GT/S

Port 2Port 3

LAN(10/100)

AR8158

Page 18

RJ-45

Page 18

AMD

Ontario FT1

APU

BGA 413-Ball

19mm X 19mm

UMI x4

Gen.1

2.5GT/s

per Lane

AMD

Hudson M1

FCH

BGA 605-Ball

23mm X 23mm

Page 12 ~ 16

LPC

33MHz

ENE KB930

Page 26

Page 4,5,6

Memory Bus (DDRIII)

Dual Channel

1.5V DDRIII 800/1066

6.4G/8.5G

100M/133M

USB Conn.x2

(Left Side)

Port 0 , 1

USB

HD Audio

SATA

Gen1 1.5GT/S ,Gen2 3GT/S

USB Conn.x1

(Right Side)

Port 2

IO/B Page 20 Page 19

3.3V 48MHz

3.3V 24MHz

HDD

Small Board

204 Pin DDRIII SO-DIMM x2

BANK 0, 1, 2, 3

Camera Bluetooth

Port 5

Page 25

100MHz

(2.5")

Port 0

Page 22

Page 9

Page 7 , 8

Port 7

Card Reader

RTS 5138

Port 6

3G Card

Port 3, 9

Page 20

SIM Card

Port 4

Page 20

WLAN

Port 8

Page 21

IO/B

LS-7071P

RTC Ckt.

Page 12

BIOS ROM

4 4

Power Button

Page 23

DC/DC Interface Ckt.

Page 28

A

B

2MB

Page 27

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

LED/B

LS-7072P

Compal Secret Data

Compal Secret Data

2010/11/09 2012/11/09

2010/11/09 2012/11/09

2010/11/09 2012/11/09

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

HDD/B

LS-7074P

TP BTN/B

LS-7073P

D

HDA Codec+AMP

CX20584

HP Jack x1

MIC Jack x1

IO/B

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

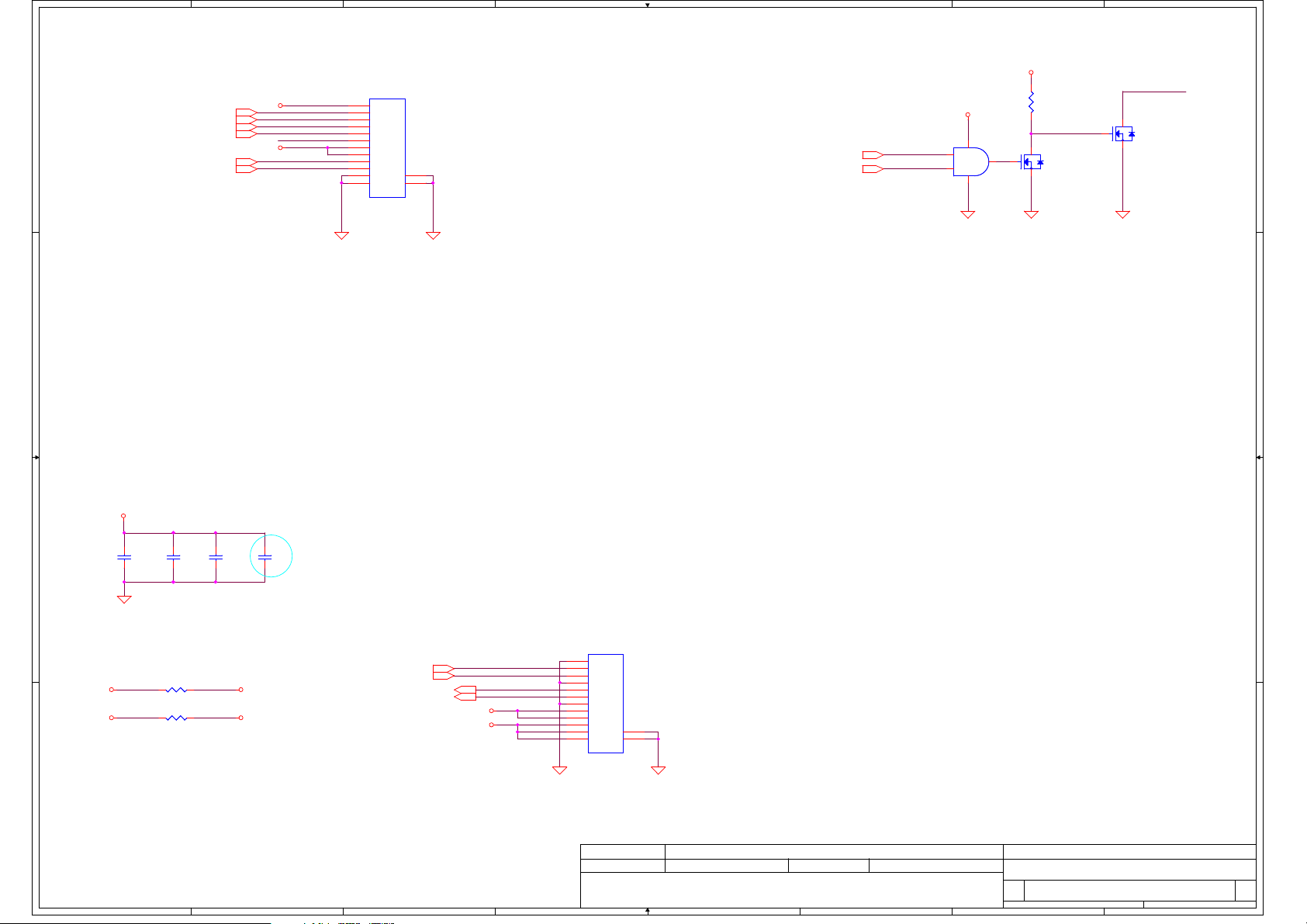

Block Diagrams

Block Diagrams

Block Diagrams

P1VE6 Schematics

P1VE6 Schematics

P1VE6 Schematics

Page 17

2 37Thursday, March 17, 2011

2 37Thursday, March 17, 2011

2 37Thursday, March 17, 2011

E

1.0

1.0

1.0

Page 3

A

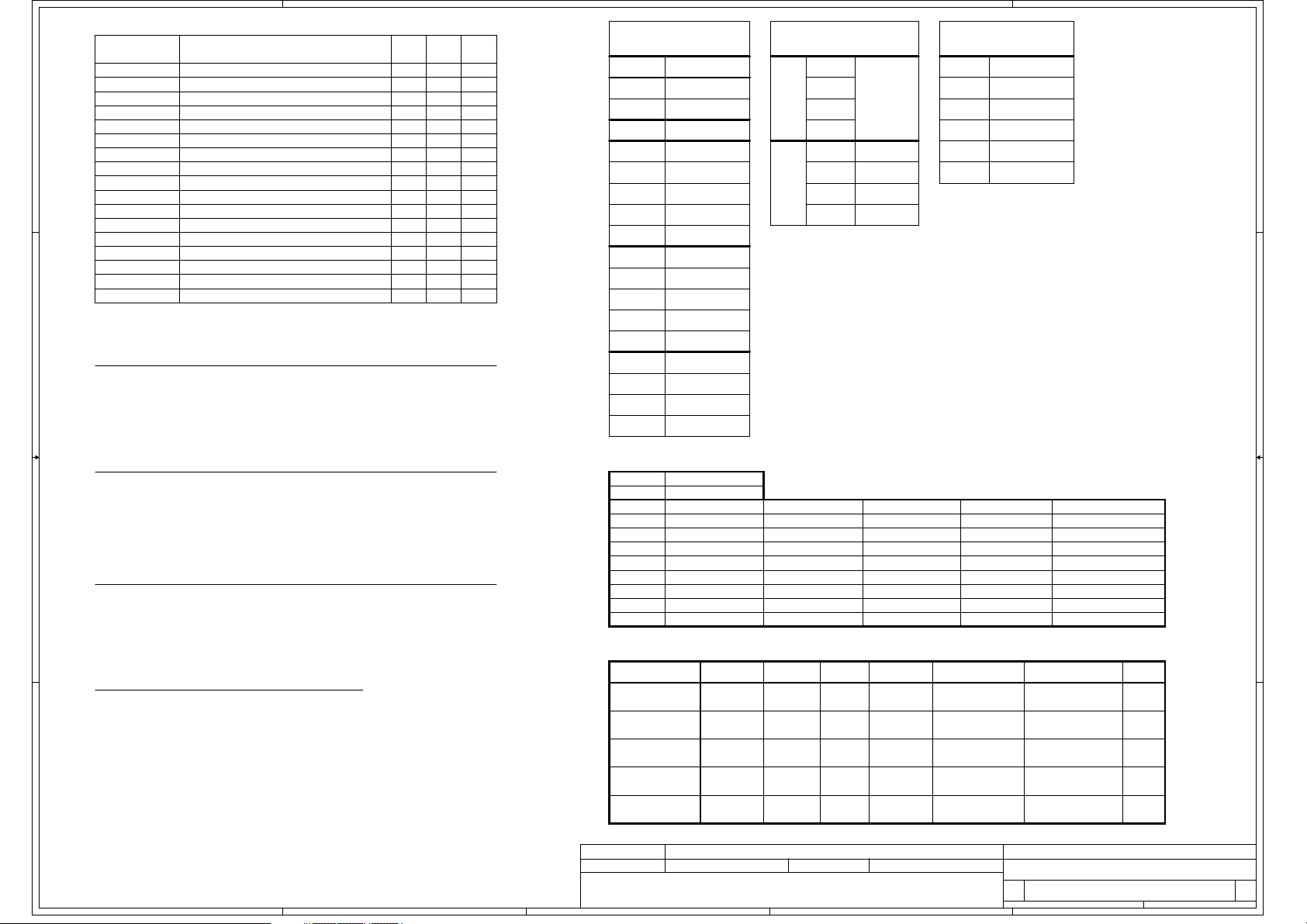

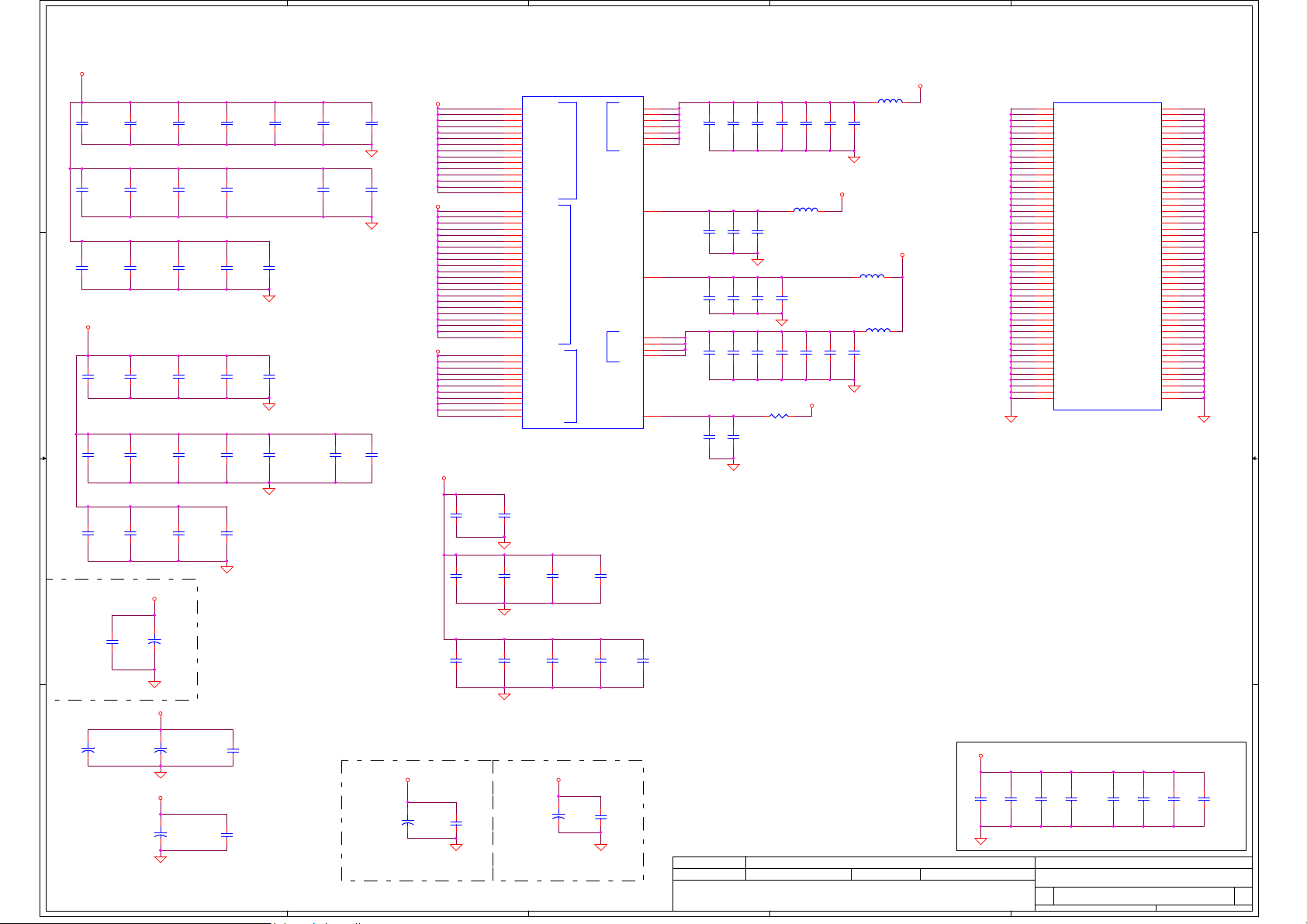

Voltage Rails

Power Plane Description

VIN

B+

+APU_CORE

1 1

2 2

+APU_CORE_NB 1.0V switched power rail ON OFF

+1.5V

+0.75VS 0.75VS switched power rail for DDR terminator

+1.05VS

+1.1VS 1.1VS switched power rail ON OFF OFF

+1.8VS 1.8V switched power rail

+3VALW

+3VS

+1.5VS 1.5VS switched power rail ON OFF OFF

+5VALW

+5VS

+VSB VSB always on power rail ON ON*

+RTCBATT

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

EC SM Bus1 address

Device

Smart Battery

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU (0.7-1.2V)

1.5V power rail for CPU VDDIO and DDRIII

1.05V switched power rail for NB VDDC & VGA

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

RTC power

EC SM Bus2 address

Address Address

0001-011xb

HEX

16H

Device

SB-TSI

B

S1 S3 S5

N/A N/A N/A

ON OFF

ON

ON

ON OFF OFF

ON

ON

ON

ON

ON

ON

1001-100xb

N/AN/AN/A

OFF

OFF

ON

OFF

OFF

OFF

OFF

OFF

ON ON*

ON ON*ON+1.1VALW 1.1V always on power rail

OFF

OFF

ON ON*

OFF

OFFON

ONON

HEX

98H

C

FCH Hudson-M1

USB Port List

USB1.1

Port0

Port1

USB2.0

Port0

Port1

Port2

Port3

Port4

Port5

Port6

Port7

Port8

Port9

Port10

Port11

Port12

Port13

NC

NC

Left conn

Left conn

WWAN

SIM

USB Camera

CardReader

BT

WiMax

WWAN

NC

NC

NC

NC

D

Brazos

PCIE Port List

PCIE0

APUFCH

PCIE1

PCIE2

PCIE3

PCIE0

PCIE1

PCIE2

PCIE3

NC

NC

WWAN

LANRight conn

WLAN

FCH Hudson-M1

SATA Port List

SATA0

SATA1

SATA2

SATA3

SATA4

SATA5

HDD

NC

NC

NC

NC

NC

E

SM Bus Controller 0

Device Address

APU SIC/SID (FCH_SMB3)

H_THERMTRIP# (FCH_ALERT#)

3 3

SM Bus Controller 1

Device Address HEX

DDR DIMM1 (FCH_SMB0)

(FCH_SMB1 ~ FCH_SMB4, SMB_AL ERT#)

HEX

(FCH_SMB0)

1001-000xb

90

Board ID / SKU ID Table for AD channel

Vcc +3VALW

Board ID

0

*

1

2

3

4

5

6

7 NC

100K +/- 5%Ra

Rb V min

AD_BID

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

0 V

V typ

AD_BID

V

AD_BID

0 V 0 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

2.200 V

3.300 V

2.341 V

3.300 V

max

PCB Revision

0.1

0.2

SMBUS Control Table

BOM Structure

EC_SMB_CK1

HDMI@ : HDMI function

BT@ : BT function

CONN@ : Connetors

45@ : 45 Level

3G@ : 3G function

4 4

N3G@ : None 3G function

CMBS@ : Combo Jack POPO noise Solution

NCMBS@: None Combo Jack POPO noise Solution

A

B

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

HDMI_DATA

HDMI_CLK

EDID_DATA

EDID_CLK

FCH_SMDAT0

FCH_SMCLK0

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Source BATT DIMM MINI Card LCD DDC ROM HDMI DDC ROM APU

KB930

V

KB930

APU FT1

APU FT1

FCH M1

Compal Secret Data

Compal Secret Data

2010/11/09 2012/11/09

2010/11/09 2012/11/09

2010/11/09 2012/11/09

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

VV

D

V

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

V

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Notes List

Notes List

Notes List

P1VE6 Schematics

P1VE6 Schematics

P1VE6 Schematics

V

1.0

1.0

3 37Thursday, March 17, 2011

3 37Thursday, March 17, 2011

3 37Thursday, March 17, 2011

E

1.0

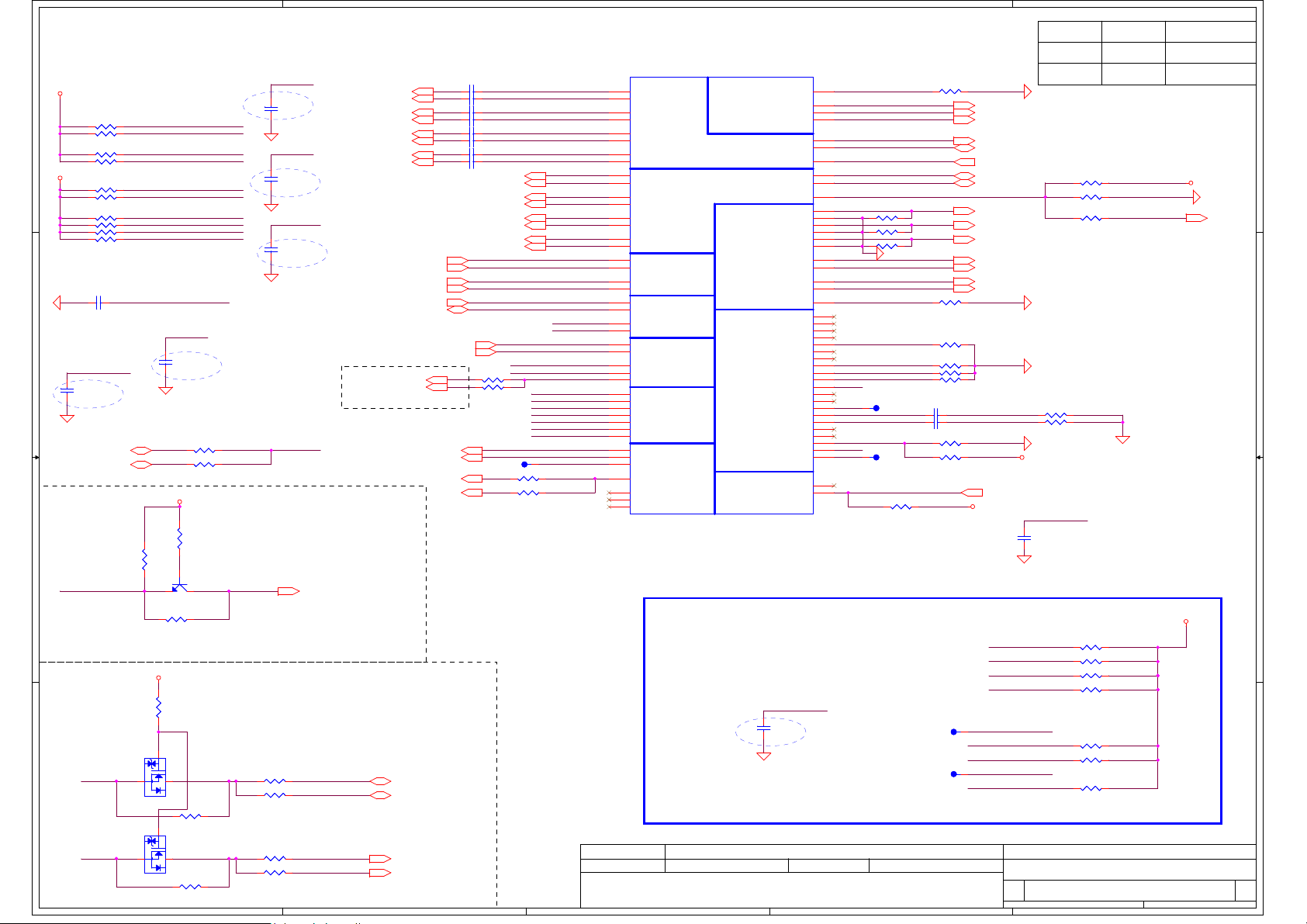

Page 4

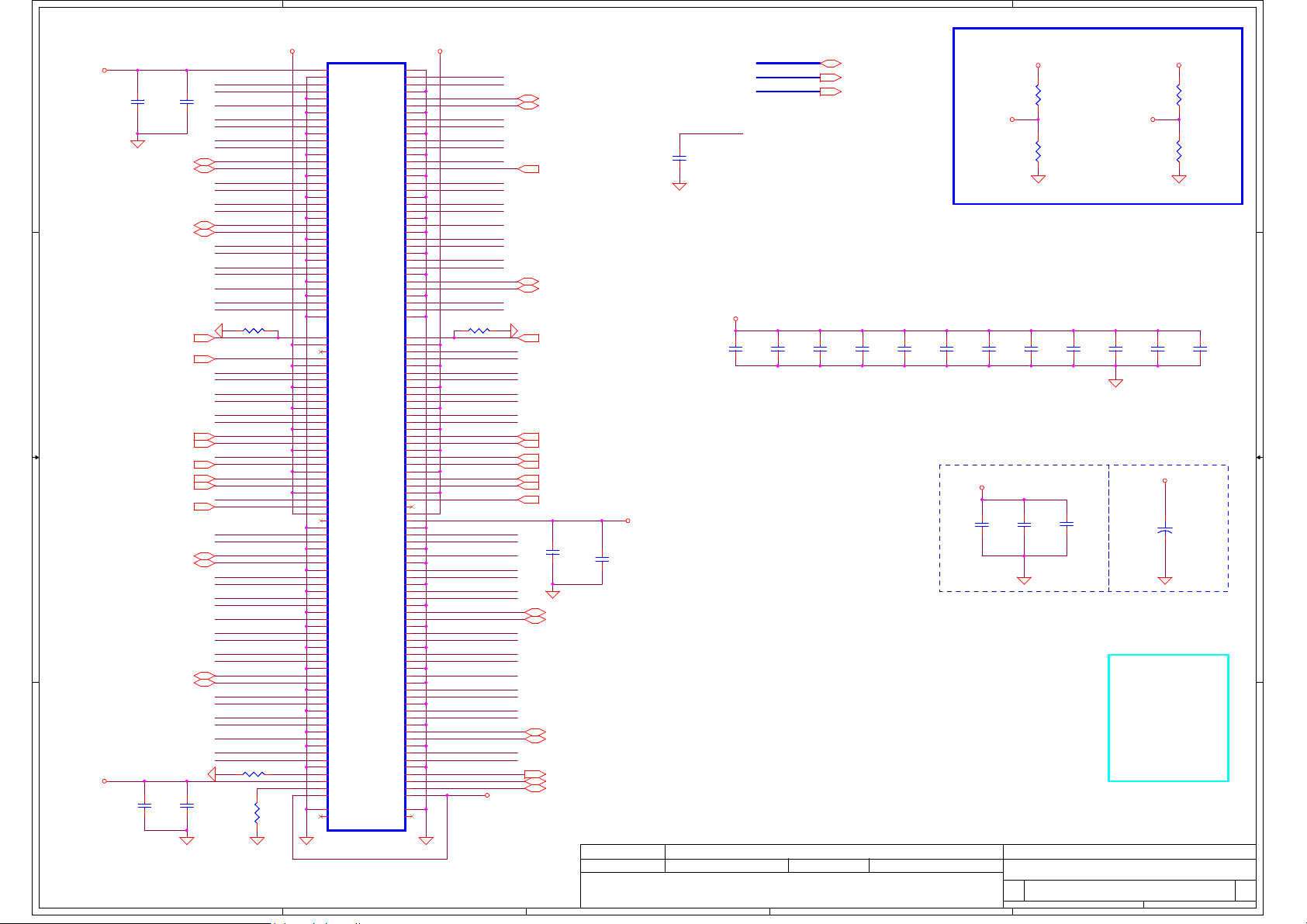

5

4

3

2

1

1

DMIC_CLK

Display

LVDS

eDP

+3VS

+1.8VS

4 37Thursday, March 17, 2011

4 37Thursday, March 17, 2011

4 37Thursday, March 17, 2011

DMIC_CLK <9,17>

1.0

1.0

1.0

APU C50 P/N change to SA00004KD50

Tock 2010/12/30

SA00004KD50

U1B

U1B

A8

TDP1_TXP0

B8

TDP1_TXN0

B9

TDP1_TXP1

A9

TDP1_TXN1

D10

TDP1_TXP2

C10

TDP1_TXN2

A10

TDP1_TXP3

B10

TDP1_TXN3

B5

LTDP0_TXP0

A5

LTDP0_TXN0

D6

LTDP0_TXP1

C6

LTDP0_TXN1

A6

LTDP0_TXP2

B6

LTDP0_TXN2

D8

LTDP0_TXP3

C8

LTDP0_TXN3

V2

CLKIN_H

V1

CLKIN_L

D2

DISP_CLKIN_H

D1

DISP_CLKIN_L

J1

SVC

J2

SVD

P3

SIC

P4

SID

T3

RESET_L

T4

PWROK

U1

PROCHOT_L

U2

THERMTRIP_L

T2

ALERT_L

N2

TDI

N1

TDO

P1

TCK

P2

TMS

M4

TRST_L

M3

DBRDY

M1

DBREQ_L

F4

VDDCR_NB_SENSE

G1

VDDCR_CPU_SENSE

F3

VDDIO_MEM_S_SENSE

F1

VSS_SENSE

B4

RSVD_1

W11

RSVD_2

V5

RSVD_3

S IC ONTARIO CMC50AFPB22GT 1G BGA ABO!

S IC ONTARIO CMC50AFPB22GT 1G BGA ABO!

DISPLAYPORT 1

DISPLAYPORT 1

DISPLAYPORT 0

DISPLAYPORT 0

CLK

CLK

SER

SER

JTAG CTRL

JTAG CTRL

DP MISC

DP MISC

VGA DAC

VGA DAC

TEST

TEST

DP_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

TDP1_AUXP

TDP1_AUXN

TDP1_HPD

LTDP0_AUXP

LTDP0_AUXN

LTDP0_HPD

DAC_RED

DAC_REDB

DAC_GREEN

DAC_GREENB

DAC_BLUE

DAC_BLUEB

DAC_HSYNC

DAC_VSYNC

DAC_SCL

DAC_SDA

DAC_ZVSS

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST31

TEST33_H

TEST33_L

TEST34_H

TEST34_L

TEST35

TEST36

TEST37

TEST38

DMAACTIVE_L

TEST4

TEST5

TEST6

DP_ZVSS

H3

G2

H2

H1

HDMI_CLK

B2

HDMI_DATA

C2

C1

EDID_CLK

A3

EDID_DATA

B3

LTDP0_HPD

D3

C12

R12 150_0402_1%R12 150_0402_1%

D13

A12

B12

A13

B13

E1

E2

F2

D4

D12

R1

R2

R6

T5

E4

K4

L1

L2

M2

K1

K2

L5

M5

M21

J18

J19

U15

T15

H4

N5

R5

K3

T1

1 2

R15 150_0402_1%R15 150_0402_1%

1 2

R18 150_0402_1%R18 150_0402_1%

1 2

DAC_ZVSS

TEST15

TEST18

TEST19

TEST25_H

TEST_25_L

TEST31

TEST33_H

TEST33_L

TEST35

TEST36

TEST37

R31 1K_0402_5%R31 1K_0402_5%

R1 150_0402_1%R1 150_0402_1%

1 2

R19 499_0402_1%R19 499_0402_1%

1 2

R20 1K_0402_5%R20 1K_0402_5%

1 2

R21 1K_0402_5%R21 1K_0402_5%

1 2

R22 1K_0402_5%R22 1K_0402_5%

1 2

R25 510_0402_1%R25 510_0402_1%

1 2

T8

PADT8PAD

C9 0.1U_0402_16V4ZC9 0.1U_0402_16V4Z

1 2

C10 0.1U_0402_16V4ZC10 0.1U_0402_16V4Z

1 2

R30 1K_0402_5%@R30 1K_0402_5%@

1 2

R386 1K_0402_5%R386 1K_0402_5%

1 2

T13

T13

PAD

PAD

9/9 Add R386 (1k@) to +1.8VS on TEST35

9/13 Change R30 from mount to @, R386 from @ to mount (AMD Recommend)

1 2

9/17 Remove JHDT1 R40, R44, R45, R46 , Add T26~T32

9/20 Delete R41~R43

APU_PWRGD

1

C421

C421

100P_0402_50V8J

100P_0402_50V8J

2

@

@

Reserve C421 for APU_PWRGD

Michael 2010/11/18

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/11/09 2012/11/09

2010/11/09 2012/11/09

2010/11/09 2012/11/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

AMD Debug

2

T29

T29

PAD

PAD

T30

T30

PAD

PAD

APU_ENBKL <26>

APU_ENVDD <9>

APU_BLPWM <9>

HDMI_CLK <10>

HDMI_DATA <10>

HDMI_DET <10>

EDID_CLK <9>

EDID_DATA <9>

DAC_RED <11>

DAC_GRN <11>

DAC_BLU <11>

CRT_HSYNC <11>

CRT_VSYNC <11>

CRT_DDC_CLK <11>

CRT_DDC_DATA <11>

10/01 Remove T1,T3~T7,T11,T12,T31,T32

ALLOW_STOP# <12>APU_VDDNB_RUN_FB_ L<36>

+1.8VS

@

@

APU_TRST#

APU_TDI

APU_TMS

APU_TCK

APU_TDO

APU_PWRGD

LDT_RST#

APU_DBRDY

APU_DBREQ#

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

+1.8VS

D D

R3 1K_0402_5%R3 1K_0402_5%

1 2

R4 1K_0402_5%R4 1K_0402_5%

1 2

R8 510_0402_1%R8 510_0402_1%

1 2

R6 1K_0402_5%R6 1K_0402_5%

1 2

+3VS

R10 10K_0402_5%R10 10K_0402_5%

1 2

R11 10K_0402_5%R11 10K_0402_5%

1 2

R13 1K_0402_5%R13 1K_0402_5%

1 2

R14 1K_0402_5%R14 1K_0402_5%

1 2

R16 1K_0402_5%R16 1K_0402_5%

1 2

R17 1K_0402_5%R17 1K_0402_5%

1 2

Change R10, R11 to RP1

Michael 2010/12/23

C405 100P_0402_50V8JC405 100P_0402_50V8J

1 2

APU_SVC

APU_SVD

TEST_25_L

TEST36

HDMI_DATA

HDMI_CLK

APU_PROCHOT#

APU_ALERT#_R

APU_SIC

APU_SID

LDT_RST#

10/05 Add 100p(C405) on LDT_RST#

C C

APU_PROCHOT#

@

@

1

C429

C429

100P_0402_50V8J

100P_0402_50V8J

2

Add C429 for APU_PROCHOT#

Michael 2010/11/18

FCH_PROCHOT#<12>

EC_PROCHOT#<26>

R33

R33

1K_0402_5%

B B

If FCH internal pull-up disab led, level-shif ter could be de leted.

Need BIOS to di sable internal pull-up!!

DMN66D0LDW-7_SOT363-6

DMN66D0LDW-7_SOT363-6

A A

DMN66D0LDW-7_SOT363-6

DMN66D0LDW-7_SOT363-6

1K_0402_5%

APU_THERMTRIP#

@

@

@

@

APU_SIC

@

@

1

C434

C434

100P_0402_50V8J

100P_0402_50V8J

2

R23 0_0402_5%@R23 0_0402_5%@

1 2

R27 0_0402_5%R27 0_0402_5%

1 2

+3VS

12

R32

R32

10K_0402_5%

10K_0402_5%

<BOM Structure>

<BOM Structure>

B

B

2

1 2

S

S

Q2A

Q2A

S

S

Q2B

Q2B

Q1

Q1

E

E

3 1

C

C

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

1 2

R34 0_0402_5%@R34 0_0402_5%@

+3VS

12

R39

R39

10K_0402_5%

10K_0402_5%

@

@

G

G

2

EC_SMB_DAAPU_SID

61

D

D

1 2

R49 0_0402_5%R49 0_0402_5%

G

G

5

EC_SMB_CKAPU_SIC

34

D

D

1 2

R52 0_0402_5%R52 0_0402_5%

5

@

@

1

2

@

@

1

2

@

@

1

2

APU_SVD

C433

C433

100P_0402_50V8J

100P_0402_50V8J

APU_SVC

C432

C432

100P_0402_50V8J

100P_0402_50V8J

Reserve C432, C433, C434, C435

Michael 2010/11/18

APU_SID

C435

C435

100P_0402_50V8J

100P_0402_50V8J

HDMI_TX2P<10>

HDMI_TX2N<10>

HDMI_TX1P<10>

HDMI_TX1N<10>

HDMI_TX0P<10>

HDMI_TX0N<10>

HDMI_CLKP<10>

HDMI_CLKN<10>

Power Circuit

C1 .1U_0402_16V7KC1 .1U_0402_16V7K

1 2

C6 .1U_0402_16V7KC6 .1U_0402_16V7K

1 2

C2 .1U_0402_16V7KC2 .1U_0402_16V7K

1 2

C3 .1U_0402_16V7KC3 .1U_0402_16V7K

1 2

C7 .1U_0402_16V7KC7 .1U_0402_16V7K

1 2

C8 .1U_0402_16V7KC8 .1U_0402_16V7K

1 2

C4 .1U_0402_16V7KC4 .1U_0402_16V7K

1 2

C5 .1U_0402_16V7KC5 .1U_0402_16V7K

1 2

APU_CLK<12>

APU_CLK#<12>

DISP_CLK<12>

DISP_CLK#<12>

APU_SVC<36>

APU_SVD<36>

LVDS_A2<9>

LVDS_A2#<9>

LVDS_A1<9>

LVDS_A1#<9>

LVDS_A0<9>

LVDS_A0#<9>

LVDS_ACLK<9>

LVDS_ACLK#<9>

9/9 Change R24 from @ to mount R26 from mount to @

9/15 Change R24 from mount to @

APU_ALERT#_FCH<14>

Connection to EC, FCH input need to pull-down

APU_PROCHOT#

Power Circuit

Power Circuit

APU_ALERT#_EC<26>

APU_VDDNB_RUN_FB_ H<36>

APU_VDD0_RUN_FB_H<36>

APU_VDD0_RUN_FB_L<36>

LDT_RST#<12>

APU_PWRGD<12>

Close to APU

R24 0_0402_5%@R24 0_0402_5 %@

1 2

R26 0_0402_5%@R26 0_0402_5 %@

1 2

T14PADT14PAD

R379 0_0402_5%R379 0_0402_5%

R380 0_0402_5%R380 0_0402_5%

1 2

1 2

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

9/6 Add R379, R380 for APU_VDDNB_RUN_FB_L

H_THERMTRIP# <13>

2N7002DW-T/R7

Vgs(th): min 1.0V

If Q8 or R429, R432 implemented,

EC side pull-up need to be mounted

@

@

1 2

R47 0_0402_5%

R47 0_0402_5%

1 2

R48 0_0402_5%R48 0_0402_5%

8/19 Change Q2A Q2B SB00000DH00 (S TR DMN66D0LDW-7 2N SOT363-6)

@

@

1 2

R50 0_0402_5%

R50 0_0402_5%

1 2

R51 0_0402_5%R51 0_0402_5%

Typ 1.6V

Max 2.0V

FCH_SID

EC_SMB_DA2

FCH_SIC

EC_SMB_CK2

FCH_SID <13>

EC_SMB_DA2 <26>

FCH_SIC <13>

EC_SMB_CK2 <26>

4

T0 FCH

TO EC

T0 FCH

TO EC

HDMI_TX2P_C

HDMI_TX2N_C

HDMI_TX1P_C

HDMI_TX1N_C

HDMI_TX0P_C

HDMI_TX0N_C

HDMI_CLKP_C

HDMI_CLKN_C

APU_SIC

APU_SID

APU_PROCHOT#

APU_THERMTRIP#

APU_ALERT#_R

8/31 Change U1 P/N to SA00004DF00 S IC ONTARIO ZM121034B1238 1.2G BGA 413P

R9 R352

mount

*

R28 51_0402_1%R28 51_0402_1%

R29 51_0402_1%R29 51_0402_1%

@

8/25 Pull-up 100k(@ R352) to +3VS

on LTDP0_HPD for eDP

R352 100K_0402_5%@R352 100K_0402_5%@

R9 100K_0402_5%R9 100K_0402_5%

R389 0_0402_5%

R389 0_0402_5%

Reserve R389 for eDP function

Tock 2010/12/30

1 2

1 2

+1.8VS

ALLOW_STOP#

1

C438

C438

100P_0402_50V8J

100P_0402_50V8J

2

Reserve C438 for ALLOW_STOP#

Michael 2010/11/18

R37 1K_0402_5%R37 1K_0402_5%

R38 1K_0402_5%R38 1K_0402_5%

R36 1K_0402_5%R36 1K_0402_5%

R35 1K_0402_5%R35 1K_0402_5%

R5 300_0402_5%R5 300_0402_5%

R7 300_0402_5%R7 300_0402_5%

R2 300_0402_5%R2 300_0402_5%

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

mount

1 2

1 2

eDP@

eDP@

1 2

12

12

12

12

12

12

12

FT1 CTRL/DP/CRT

FT1 CTRL/DP/CRT

FT1 CTRL/DP/CRT

P1VE6 Schematics

P1VE6 Schematics

P1VE6 Schematics

@

Page 5

A

U1E

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

4 4

3 3

2 2

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_BS0<7,8>

DDR_A_BS1<7,8>

DDR_A_BS2<7,8>

DDR_A_DQS0<7,8>

DDR_A_DQS#0<7,8>

DDR_A_DQS1<7,8>

DDR_A_DQS#1<7,8>

DDR_A_DQS2<7,8>

DDR_A_DQS#2<7,8>

DDR_A_DQS3<7,8>

DDR_A_DQS#3<7,8>

DDR_A_DQS4<7,8>

DDR_A_DQS#4<7,8>

DDR_A_DQS5<7,8>

DDR_A_DQS#5<7,8>

DDR_A_DQS6<7,8>

DDR_A_DQS#6<7,8>

DDR_A_DQS7<7,8>

DDR_A_DQS#7<7,8>

DDR_A_CLK0<7>

DDR_A_CLK#0<7>

DDR_A_CLK1<7>

DDR_A_CLK#1<7>

DDR_B_CLK2<8>

DDR_B_CLK#2<8>

DDR_B_CLK3<8>

DDR_B_CLK#3<8>

DDR_RST#<7,8>

DDR_EVENT#<7,8>

DDR_CKE0<7,8>

DDR_CKE1<7,8>

DDR_A_ODT0<7>

DDR_A_ODT1<7>

DDR_B_ODT0<8>

DDR_B_ODT1<8>

DDR_CS0_DIMMA#<7>

DDR_CS1_DIMMA#<7>

DDR_CS0_DIMMB#<8>

DDR_CS1_DIMMB#<8>

DDR_A_RAS#<7,8>

DDR_A_CAS#<7,8>

DDR_A_WE#<7,8>

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_CLK1

DDR_A_CLK#1

DDR_B_CLK2

DDR_B_CLK#2

DDR_B_CLK3

DDR_B_CLK#3

DDR_RST#

DDR_EVENT#

DDR_CKE0

DDR_CKE1

DDR_A_ODT0

DDR_A_ODT1

DDR_B_ODT0

DDR_B_ODT1

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS0_DIMMB#

DDR_CS1_DIMMB#

DDR_A_RAS#

DDR_A_CAS#

DDR_A_WE#

U1E

R17

M_ADD0

H19

M_ADD1

J17

M_ADD2

H18

M_ADD3

H17

M_ADD4

G17

M_ADD5

H15

M_ADD6

G18

M_ADD7

F19

M_ADD8

E19

M_ADD9

T19

M_ADD10

F17

M_ADD11

E18

M_ADD12

W17

M_ADD13

E16

M_ADD14

G15

M_ADD15

R18

M_BANK0

T18

M_BANK1

F16

M_BANK2

D15

M_DM0

B19

M_DM1

D21

M_DM2

H22

M_DM3

P23

M_DM4

V23

M_DM5

AB20

M_DM6

AA16

M_DM7

A16

M_DQS_H0

B16

M_DQS_L0

B20

M_DQS_H1

A20

M_DQS_L1

E23

M_DQS_H2

E22

M_DQS_L2

J22

M_DQS_H3

J23

M_DQS_L3

R22

M_DQS_H4

P22

M_DQS_L4

W22

M_DQS_H5

V22

M_DQS_L5

AC20

M_DQS_H6

AC21

M_DQS_L6

AB16

M_DQS_H7

AC16

M_DQS_L7

M17

M_CLK_H0

M16

M_CLK_L0

M19

M_CLK_H1

M18

M_CLK_L1

N18

M_CLK_H2

N19

M_CLK_L2

L18

M_CLK_H3

L17

M_CLK_L3

L23

M_RESET_L

N17

M_EVENT_L

F15

M_CKE0

E15

M_CKE1

W19

M0_ODT0

V15

M0_ODT1

U19

M1_ODT0

W15

M1_ODT1

T17

M0_CS_L0

W16

M0_CS_L1

U17

M1_CS_L0

V16

M1_CS_L1

U18

M_RAS_L

V19

M_CAS_L

V17

M_WE_L

S IC ONTARIO CMC50AFPB22GT 1G BGA ABO!

S IC ONTARIO CMC50AFPB22GT 1G BGA ABO!

DDR SYSTEM MEMORY

DDR SYSTEM MEMORY

B

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_VREF

M_ZVDDIO_MEM_S

B14

A15

A17

D18

A14

C14

C16

D16

C18

A19

B21

D20

A18

B18

A21

C20

C23

D23

F23

F22

C22

D22

F20

F21

H21

H23

K22

K21

G23

H20

K20

K23

N23

P21

T20

T23

M20

P20

R23

T22

V20

V21

Y23

Y22

T21

U23

W23

Y21

Y20

AB22

AC19

AA18

AA23

AA20

AB19

Y18

AC17

Y16

AB14

AC14

AC18

AB18

AB15

AC15

M23

M22

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

+MEM_VREF

+M_ZVDDIO

R55

R55

39.2_0402_1%

39.2_0402_1%

12

DDR_A_MA[0..15]

DDR_A_DM[0..7]

+1.05VS

UMI_RX0P<12>

UMI_RX0N<1 2>

UMI_RX1P<12>

UMI_RX1N<1 2>

UMI_RX2P<12>

UMI_RX2N<1 2>

UMI_RX3P<12>

UMI_RX3N<1 2>

+1.5V

DDR_A_D[0..63]

Less than 1"

C

DDR_A_D[0..63] <7,8>

DDR_A_MA[0..15] <7,8>

DDR_A_DM[0..7] <7,8>

1 2

R53 2 K_0402_1%R53 2K_0402_1%

P_ZVDD_10

8/22 Delete C11~C18 (No VGA)

9/6 Change PCI-E from FCH to APU

9/6 Update PCI-E port List

9/15 Change PCI-E from APU to FCH

U1A

U1A

AA6

P_GPP_RXP0

Y6

P_GPP_RXN0

AB4

P_GPP_RXP1

AC4

P_GPP_RXN1

AA1

P_GPP_RXP2

AA2

P_GPP_RXN2

Y4

P_GPP_RXP3

Y3

P_GPP_RXN3

Y14

P_ZVDD_10

AA12

P_UMI_RXP0

Y12

P_UMI_RXN0

AA10

P_UMI_RXP1

Y10

P_UMI_RXN1

AB10

P_UMI_RXP2

AC10

P_UMI_RXN2

AC7

P_UMI_RXP3

AB7

P_UMI_RXN3

S IC ONTARIO CMC50AFPB22GT 1G BGA ABO!

S IC ONTARIO CMC50AFPB22GT 1G BGA ABO!

PCIE I/F

PCIE I/F

UMI I/F

UMI I/F

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_ZVSS

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

D

AB6

AC6

AB3

AC3

Y1

Y2

V3

V4

AA14

AB12

AC12

AC11

AB11

AA8

Y8

AB8

AC8

P_ZVSS

R54 1.27K_0402_1%R54 1.27K_0402_1%

Less than 1"

UMI_TX0P_C

UMI_TX0N_C

UMI_TX1P_C

UMI_TX1N_C

UMI_TX2P_C

UMI_TX2N_C

UMI_TX3P_C

UMI_TX3N_C

C19 .1U_0402_16V7KC19 .1U_0402_16V7K

C20 .1U_0402_16V7KC20 .1U_0402_16V7K

C21 .1U_0402_16V7KC21 .1U_0402_16V7K

C22 .1U_0402_16V7KC22 .1U_0402_16V7K

C23 .1U_0402_16V7KC23 .1U_0402_16V7K

C24 .1U_0402_16V7KC24 .1U_0402_16V7K

C25 .1U_0402_16V7KC25 .1U_0402_16V7K

C26 .1U_0402_16V7KC26 .1U_0402_16V7K

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

E

UMI_TX0P <12>

UMI_TX0N <12>

UMI_TX1P <12>

UMI_TX1N <12>

UMI_TX2P <12>

UMI_TX2N <12>

UMI_TX3P <12>

UMI_TX3N <12>

9/11 Delete DDR Signal link to JDIMM2

+1.5V

+1.5V

1 1

Reserve C439 for DDR_EVENT#

Michael 2010/11/18

R57

R57

1 2

1K_0402_5%

1K_0402_5%

DDR_EVENT#

@

@

1

2

A

C439

C439

100P_0402_50V8J

100P_0402_50V8J

R56

R56

1K_0402_1%

1K_0402_1%

R58

R58

1K_0402_1%

1K_0402_1%

1 2

1

C27

C27

1000P_0402_50V7K

1000P_0402_50V7K

2

1 2

Place within 1000 mils to APU

20100526

B

C28

C28

+MEM_VREF

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING D RAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING D RAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING D RAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/11/09 2012/11/09

2010/11/09 2012/11/09

2010/11/09 2012/11/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

FT1 DDRIII/UMI/PCIE

FT1 DDRIII/UMI/PCIE

FT1 DDRIII/UMI/PCIE

P1VE6 Schematics

P1VE6 Schematics

P1VE6 Schematics

E

5 37Thursday, March 17, 2011

5 37Thursday, March 17, 2011

5 37Thursday, March 17, 2011

1.0

1.0

1.0

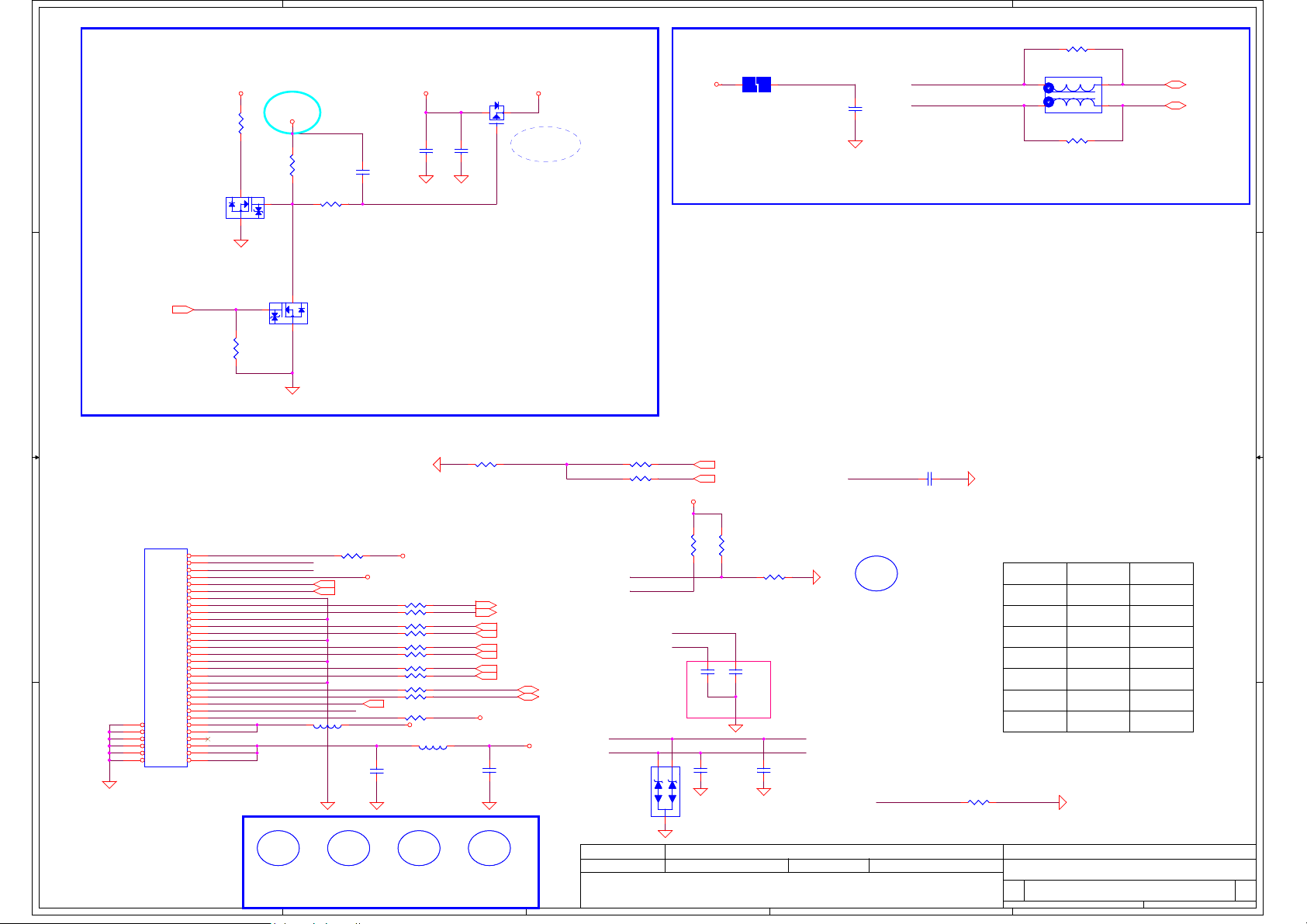

Page 6

5

4

3

2

1

+APU_CORE

1

D D

C31

C31

2

1

C43

C43

2

1

C52

C52

2

+APU_CORE_NB

C C

C68

C68

C75

C75

C84

C84

B B

1

C29

C29

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C44

C44

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C53

C53

2

.1U_0402_16V7K

.1U_0402_16V7K

1

1

C69

C69

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

C76

C76

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C85

C85

2

2

.1U_0402_16V7K

.1U_0402_16V7K

POWER

1

C92

C92

@

@

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1U_0402_6.3V6K

1U_0402_6.3V6K

.1U_0402_16V7K

.1U_0402_16V7K

10U_0603_6.3V6M

10U_0603_6.3V6M

1U_0402_6.3V6K

1U_0402_6.3V6K

.1U_0402_16V7K

.1U_0402_16V7K

+1.05VS

1

2

1

C32

C32

2

1

C45

C45

2

1

C54

C54

2

1

C70

C70

2

1

C77

C77

2

1

C86

C86

2

+

+

C93

C93

220U_D2_2VY_R15M

220U_D2_2VY_R15M

SGA00004L00

1

C41

C41

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C46

C46

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C55

C55

2

.1U_0402_16V7K

.1U_0402_16V7K

1

C71

C71

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C78

C78

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C87

C87

2

.1U_0402_16V7K

.1U_0402_16V7K

9/20 Change C93 to SGA00004L00

1

C42

C42

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C56

C56

2

.1U_0402_16V7K

.1U_0402_16V7K

1

C72

C72

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C79

C79

2

1U_0402_6.3V6K

1U_0402_6.3V6K

.1U_0402_16V7K

.1U_0402_16V7K

1

C30

C30

2

10U_0603_6.3V6M

10U_0603_6.3V6M

.1U_0402_16V7K

.1U_0402_16V7K

10U_0603_6.3V6M

10U_0603_6.3V6M

1U_0402_6.3V6K

1U_0402_6.3V6K

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C47

C47

2

180P_0402_50V8J

180P_0402_50V8J

1

C80

C80

2

180P_0402_50V8J

180P_0402_50V8J

9/15 Change C99,C100 to 470U(SGA00003K00)

SGA00003K00

1

+

+

330U_D2_2V_Y

330U_D2_2V_Y

2

A A

SGA20331E10

change C99,C100 from 470U to 330U , 2011/01/28 Tock

change C99,C100 footprint from C_D2 to C_X for placement

+APU_CORE

1

+

C99

C99

+

C100

C100

330U_D2_2V_Y

330U_D2_2V_Y

2

+APU_CORE_NB

1

+

+

C114

C114

330U_D2_2V_Y

330U_D2_2V_Y

2

1

C102

10U_0603_6.3V6M

10U_0603_6.3V6M

2

Near CPU Socket

1

C117

C117

10U_0603_6.3V6M

10U_0603_6.3V6M

2

Near CPU Socket Near CPU Socket

5

POWER

@C102

@

SGA20331E10

4500 mA

1

C33

C33

2

1

C48

C48

2

1

C81

C81

2

330U_D2_2V_Y

330U_D2_2V_Y

+APU_CORE

10U_0603_6.3V6M

10U_0603_6.3V6M

8000 mA

+APU_CORE_NB

180P_0402_50V8J

180P_0402_50V8J

2000 mA

+1.5V

180P_0402_50V8J

180P_0402_50V8J

8/22 Change C111~C113 from E-Cap to Poly-Cap (SGA20331E10)

8/25 Change C111 from poly-cap to E-cap (SF000002Z00)

9/11 Change C111 to SGA20331E10

C111

C111

+1.5V

1

C82

C82

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C88

C88

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C94

C94

2

.1U_0402_16V7K

.1U_0402_16V7K

+1.5V +1.8VS

POWER POWER

1

2

1

+

+

C115

C115

2

22U_0805_6.3V6M

22U_0805_6.3V6M

U1C

U1C

E5

VDDCR_CPU_1

E6

VDDCR_CPU_2

F5

VDDCR_CPU_3

F7

VDDCR_CPU_4

G6

VDDCR_CPU_5

G8

VDDCR_CPU_6

H5

VDDCR_CPU_7

H7

VDDCR_CPU_8

J6

VDDCR_CPU_9

J8

VDDCR_CPU_10

L7

VDDCR_CPU_11

M6

VDDCR_CPU_12

M8

VDDCR_CPU_13

N7

VDDCR_CPU_14

R8

VDDCR_CPU_15

E8

VDDCR_NB_1

E11

VDDCR_NB_2

E13

VDDCR_NB_3

F9

VDDCR_NB_4

F12

VDDCR_NB_5

G11

VDDCR_NB_6

G13

VDDCR_NB_7

H9

VDDCR_NB_8

H12

VDDCR_NB_9

K11

VDDCR_NB_10

K13

VDDCR_NB_11

L10

VDDCR_NB_12

L12

VDDCR_NB_13

L14

VDDCR_NB_14

M11

VDDCR_NB_15

M12

VDDCR_NB_16

M13

VDDCR_NB_17

N10

VDDCR_NB_18

N12

VDDCR_NB_19

N14

VDDCR_NB_20

P11

VDDCR_NB_21

P13

VDDCR_NB_22

G16

VDDIO_MEM_S_1

G19

VDDIO_MEM_S_2

E17

VDDIO_MEM_S_3

J16

VDDIO_MEM_S_4

L16

VDDIO_MEM_S_5

L19

VDDIO_MEM_S_6

N16

VDDIO_MEM_S_7

R16

VDDIO_MEM_S_8

R19

VDDIO_MEM_S_9

W18

VDDIO_MEM_S_10

U16

VDDIO_MEM_S_11

S IC ONTARIO CMC50AFPB22GT 1G BGA ABO!

S IC ONTARIO CMC50AFPB22GT 1G BGA ABO!

1

C83

C83

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C89

C89

2

1

C95

C95

2

1U_0402_6.3V6K

1U_0402_6.3V6K

.1U_0402_16V7K

.1U_0402_16V7K

C112

C112

330U_D2_2V_Y

330U_D2_2V_Y

1

C90

C90

2

1

C96

C96

2

1

+

+

2

SGA20331E10

Near CPU Socket

4

2000 mA

TSense/PLL/DP/PCIE/IO

TSense/PLL/DP/PCIE/IO

VDD_18_1

VDD_18_2

VDD_18_3

VDD_18_4

VDD_18_5

VDD_18_6

CPU CORE

CPU CORE

VDD_18_7

DAC

DAC

VDD_18_DAC

GPU AND NB CORE

GPU AND NB CORE

POWER

POWER

DIS PLL

DIS PLL

VDDPL_10

PCIE/IO/DDR3 Phy

PCIE/IO/DDR3 Phy

VDD_10_1

VDD_10_2

VDD_10_3

VDD_10_4

DDR3

DDR3

DP Phy/IO

DP Phy/IO

VDD_33

1

C91

C91

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

.1U_0402_16V7K

.1U_0402_16V7K

1U_0402_6.3V6K

1

C97

C97

2

180P_0402_50V8J

180P_0402_50V8J

1

C116

C116

@

@

2

10U_0603_6.3V6M

10U_0603_6.3V6M

+VDD_18

U8

W8

U6

U9

W6

T7

V7

W = 20 mil / Spcae = 20 mil

W9

W = 15 mil / Spcae = 20 mil

U11

5500 mA

U13

W13

V12

T12

500 mA

A4

1

C98

C98

2

180P_0402_50V8J

180P_0402_50V8J

3

1

1

C34

C34

C35

C35

2

2

180P_0402_50V8J

180P_0402_50V8J

+VDD_18_DAC

+VDDL_10

+VDD_10

+VDD_33

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

1

C49

C49

2

1

C57

C57

2

1

C61

C61

2

1

C73

C73

2

Issued Date

Issued Date

Issued Date

1

C50

C50

2

180P_0402_50V8J

180P_0402_50V8J

1

C58

C58

2

180P_0402_50V8J

180P_0402_50V8J

1

C62

C62

2

180P_0402_50V8J

180P_0402_50V8J

1

C74

C74

2

.1U_0402_16V7K

.1U_0402_16V7K

1

1

C36

C36

2

.1U_0402_16V7K

.1U_0402_16V7K

1

C51

C51

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C59

C59

2

.1U_0402_16V7K

.1U_0402_16V7K

1

C63

C63

2

.1U_0402_16V7K

.1U_0402_16V7K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C37

C37

C38

C38

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

L2

L2

FBMA-L11-201209-221LMA30T_0805

FBMA-L11-201209-221LMA30T_0805

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C60

C60

2

1U_0402_6.3V6K

1U_0402_6.3V6K

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

C65

C65

C64

C64

2

2

.1U_0402_16V7K

.1U_0402_16V7K

1U_0402_6.3V6K

1U_0402_6.3V6K

+3VS

R333

R333

1 2

0_0603_5%

0_0603_5%

8/22 Reserve R333 ( 0 ohm 0603 )

2010/11/09 2012/11/09

2010/11/09 2012/11/09

2010/11/09 2012/11/09

1

1

C40

C40

C39

C39

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

10U_0603_6.3V6M

10U_0603_6.3V6M

+1.8VS

12

8/25 Change +1.0VS to +1.05VS

L3

L3

FBMA-L11-201209-221LMA30T_0805

FBMA-L11-201209-221LMA30T_0805

1

1

C66

C66

C67

C67

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

+1.8VS

L1

L1

12

FBMA-L11-201209-221LMA30T_0805

FBMA-L11-201209-221LMA30T_0805

+1.05VS

12

L4

L4

12

FBMA-L11-201209-221LMA30T_0805

FBMA-L11-201209-221LMA30T_0805

2

U1D

U1D

A7

VSS_1

B7

VSS_2

B11

VSS_3

B17

VSS_4

B22

VSS_5

C4

VSS_6

D5

VSS_7

D7

VSS_8

D9

VSS_9

D11

VSS_10

D14

VSS_11

B15

VSS_12

D17

VSS_13

D19

VSS_14

E7

VSS_15

E9

VSS_16

E12

VSS_17

E20

VSS_18

F8

VSS_19

F11

VSS_20

F13

VSS_21

G4

VSS_22

G5

VSS_23

G7

VSS_24

G9

VSS_25

G12

VSS_26

G20

VSS_27

G22

VSS_28

H6

VSS_29

H11

VSS_30

H13

VSS_31

J4

VSS_32

J5

VSS_33

J7

VSS_34

J20

VSS_35

K10

VSS_36

K14

VSS_37

L4

VSS_38

L6

VSS_39

L8

VSS_40

L11

VSS_41

L13

VSS_42

L20

VSS_43

L22

VSS_44

M7

VSS_45

N4

VSS_46

N6

VSS_47

N8

VSS_48

N11

VSS_49

S IC ONTARIO CMC50AFPB22GT 1G BGA ABO!

S IC ONTARIO CMC50AFPB22GT 1G BGA ABO!

By case (Along split)

+1.5V

1

1

C103

C103

2

.1U_0402_16V7K

.1U_0402_16V7K

1

C104

C104

C105

C105

2

2

.1U_0402_16V7K

.1U_0402_16V7K

.1U_0402_16V7K

.1U_0402_16V7K

.1U_0402_16V7K

.1U_0402_16V7K

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

N13

VSS_50

N20

VSS_51

N22

VSS_52

P10

VSS_53

P14

VSS_54

R4

VSS_55

R7

VSS_56

R20

VSS_57

T6

VSS_58

T9

VSS_59

T11

VSS_60

T13

VSS_61

U4

VSS_62

U5

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSSBG_DAC

C107

C107

180P_0402_50V8J

180P_0402_50V8J

U7

U12

U20

U22

V8

V9

V11

V13

W1

W2

W4

W5

W7

W12

W20

Y5

Y7

Y9

Y11

Y13

Y15

Y17

Y19

AA4

AA22

AB2

AB5

AB9

AB13

AB17

AB21

AC5

AC9

AC13

A11

1

1

C109

C109

C108

C108

2

2

180P_0402_50V8J

180P_0402_50V8J

GND

GND

1

1

C106

C106

2

2

180P_0402_50V8J

180P_0402_50V8J

Compal Electronics, Inc.

P07-FT1 PWR/VSS

P07-FT1 PWR/VSS

P07-FT1 PWR/VSS

P1VE6 Schematics

P1VE6 Schematics

P1VE6 Schematics

1

6 37Thursday, March 17, 2011

6 37Thursday, March 17, 2011

6 37Thursday, March 17, 2011

1

C110

C110

2

180P_0402_50V8J

180P_0402_50V8J

1.0

1.0

1.0

Page 7

5

4

3

2

1

+1.5V

3500 mA

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D12

DDR_A_D13

DDR_A_DM1

DDR_A_D14

DDR_A_D15

DDR_A_D20

DDR_A_D21

DDR_A_DM2

DDR_A_D22

DDR_A_D23

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

R397

R397

1 2

100_0402_1%

100_0402_1%

DDR_A_MA15

DDR_A_MA14

DDR_A_MA11

DDR_A_MA7

DDR_A_MA6

DDR_A_MA4

DDR_A_MA2

DDR_A_MA0

DDR_A_D36

DDR_A_D37

DDR_A_DM4

DDR_A_D38

DDR_A_D39

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D52

DDR_A_D53

DDR_A_DM6

DDR_A_D54

DDR_A_D55

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

+0.75VS

100 mA

DDR_A_D0

DDR_A_D1

DDR_A_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

R396

R396

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_MA10

DDR_A_MA13

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

12

R64

R64

10K_0402_5%

10K_0402_5%

+1.5V

JDIMM1

1

VREF_DQ

3

VSS

5

DQ0

7

DQ1

9

VSS

11

DM0

13

VSS

15

DQ2

17

DQ3

19

VSS

21

DQ8

23

DQ9

25

VSS

27

DQS1#

29

DQS1

31

VSS

33

DQ10

35

DQ11

37

VSS

39

DQ16

41

DQ17

43

VSS

45

DQS2#

47

DQS2

49

VSS

51

DQ18

53

DQ19

55

VSS

57

DQ24

59

DQ25

61

VSS

63

DM3

65

VSS

67

DQ26

69

DQ27

71

VSS

73

CKE0

75

VDD

77

NC

79

BA2

81

VDD

83

A12/BC#

85

A9

87

VDD

89

A8

91

A5

93

VDD

95

A3

97

A1

99

VDD

101

CK0

103

CK0#

105

VDD

107

A10/AP

109

BA0

111

VDD

113

WE#

115

CAS#

117

VDD

119

A13

121

S1#

123

VDD

125

TEST

127

VSS

129

DQ32

131

DQ33

133

VSS

135

DQS4#

137

DQS4

139

VSS

141

DQ34

143

DQ35

145

VSS

147

DQ40

149

DQ41

151

VSS

153

DM5

155

VSS

157

DQ42

159

DQ43

161

VSS

163

DQ48

165

DQ49

167

VSS

169

DQS6#

171

DQS6

173

VSS

175

DQ50

177

DQ51

179

VSS

181

DQ56

183

DQ57

185

VSS

187

DM7

189

VSS

191

DQ58

193

DQ59

195

VSS

197

SA0

199

VDDSPD

201

SA1

203

VTT

205

GND1

207

BOSS1

FOX_AS0A621-U4RG-7H

FOX_AS0A621-U4RG-7H

CONN@JD IMM1

CONN@

VSS

DQ4

DQ5

VSS

DQS0#

DQS0

VSS

DQ6

DQ7

VSS

DQ12

DQ13

VSS

DM1

RESET#

VSS

DQ14

DQ15

VSS

DQ20

DQ21

VSS

DM2

VSS

DQ22

DQ23

VSS

DQ28

DQ29

VSS

DQS3#

DQS3

VSS

DQ30

DQ31

VSS

CKE1

VDD

VDD

VDD

VDD

VDD

CK1

CK1#

VDD

BA1

RAS#

VDD

ODT0

VDD

ODT1

VDD

VREF_CA

VSS

DQ36

DQ37

VSS

DM4

VSS

DQ38

DQ39

VSS

DQ44

DQ45

VSS

DQS5#

DQS5

VSS

DQ46

DQ47

VSS

DQ52

DQ53

VSS

DM6

VSS

DQ54

DQ55

VSS

DQ60

DQ61

VSS

DQS7#

DQS7

VSS

DQ62

DQ63

VSS

EVENT#

SDA

SCL

VTT

GND2

BOSS2

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

A15

80

A14

82

84

A11

86

A7

88

90

A6

92

A4

94

96

A2

98

A0

100

102

104

106

108

110

112

114

S0#

116

118

120

122

NC

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

206

208

4

W=20mil

+VREF_DQ

1

C118

C118

D D

C C

B B

+3VS

A A

2

DDR_CS1_DIMMA#<5 >

C138

C138

1

C119

C119

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

DDR_A_DQS#1<5,8>

DDR_A_DQS1<5,8>

DDR_A_DQS#2<5,8>

DDR_A_DQS2<5,8>

DDR_CKE0<5,8>

DDR_A_BS2<5,8>

DDR_A_CLK0<5>

DDR_A_CLK#0<5>

DDR_A_BS0<5,8>

DDR_A_WE#<5,8>

DDR_A_CAS#<5,8>

DDR_A_DQS#4<5,8>

DDR_A_DQS4<5,8>

DDR_A_DQS#6<5,8>

DDR_A_DQS6<5,8>

1

2

1000P_0402_50V7K

1000P_0402_50V7K

1 2

100_0402_1%

100_0402_1%

R63 10K_0402_5%R63 10K_0402_5%

1 2

1

C139

C139

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

5

Change JDIMM1 socket to SP07000NN00

2010/12/06 Tock

Change JDIMM1 socket to SP07000NZ00

2010/12/14 Tock

DDR_A_DQS#0 <5,8>

DDR_A_DQS0 <5,8>

DDR_RST#

1

@

@

C413

C413

100P_0402_50V8J

DDR_RST# <5,8>

100P_0402_50V8J

2

DDR_A_D[0..63]

DDR_A_MA[0..15]

DDR_A_DM[0..7]

Reserve C413 for DDR_RST#

Michael 2010/11/18

9/23 Reserve R396,R397 on CKE0 & CKE1(S3 hang Issue)

DDR_A_DQS#3 <5,8>

DDR_A_DQS3 <5,8>

+1.5V

0.1U_0402_16V4Z

0.1U_0402_16V4Z

DDR_CKE1 <5,8>

2

C120

C120

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C121

C121

1

2

C122

C122

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

10/11 Change R396 R397 from @ to mount (For A1 APU,B0 APU no Need)

DDR_A_CLK1 <5>

DDR_A_CLK#1 <5>

DDR_A_BS1 <5,8>

DDR_A_RAS# <5,8>

DDR_CS0_DIMMA# <5>

DDR_A_ODT0 <5>

DDR_A_ODT1 <5>

W=20mil

+VREF_CA

1

C132

C132

2

DDR_A_DQS#5 <5,8>

DDR_A_DQS5 <5,8>

DDR_A_DQS#7 <5,8>

DDR_A_DQS7 <5,8>

DDR_EVENT# <5,8>

FCH_SMDAT0 <8,13,20,21>

FCH_SMCLK0 <8,13,20,21>

1

C133

C133

2

1000P_0402_50V7K

1000P_0402_50V7K

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/11/09 2012/11/09

2010/11/09 2012/11/09

2010/11/09 2012/11/09

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

C126

C126

@

@

1

+1.5V

R59

R59

1K_0402_1%

1K_0402_1%

1 2

R61

R61

1K_0402_1%

1K_0402_1%

1 2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C127

C127

@

@

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

DDR_A_D[0..63] <5,8>

DDR_A_MA[0..15] <5,8>

DDR_A_DM[0..7] <5,8>

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C123

C123

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C124

C124

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C125

C125

1

+VREF_DQ

0.1U_0402_16V4Z

0.1U_0402_16V4Z

9/11 Change C137 to SGA00004L00

CRB 0.1u X1 4.7u X1

+0.75VS

2

2

C135

C135

C134

C134

@

@

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Place near JDIMM1

8/25 Change C137 from poly-cap to E-cap (SF000002Y00)

8/25 Reserve C381 E-cap (SF000002Y00) on +1.5V

9/11 Remove C381

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

C136

C136

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Compal Electronics, Inc.

+1.5V

R60

R60

1K_0402_1%

1K_0402_1%

2

C128

C128

@

@

1

+VREF_CA

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C129

C129

@

@

1

2

C130

C130

@

@

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1 2

R62

R62

1K_0402_1%

1K_0402_1%

1 2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

CRB 100U X2

+1.5V

1

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

change C137 to SF000002Y00

2010/12/14 Tock

DDR3 SODIMM-I Socket

DDR3 SODIMM-I Socket

DDR3 SODIMM-I Socket

P1VE6 Schematics

P1VE6 Schematics

P1VE6 Schematics

1

+

+

@

@

2

SGA00004L00

1

C137

C137

220U_6.3V_M

220U_6.3V_M

7 37Thursday, March 17, 2011

7 37Thursday, March 17, 2011

7 37Thursday, March 17, 2011

2

C131

C131

@

@

1

1.0

1.0

1.0

Page 8

5

4

3

2

1

+1.5V

3500 mA

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D12

DDR_A_D13

DDR_A_DM1

DDR_A_D14

DDR_A_D15

DDR_A_D20

DDR_A_D21

DDR_A_DM2

DDR_A_D22

DDR_A_D23

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

R401

@R401

@

1 2

100_0402_1%

100_0402_1%

DDR_A_MA15

DDR_A_MA14

DDR_A_MA11

DDR_A_MA7

DDR_A_MA6

DDR_A_MA4

DDR_A_MA2

DDR_A_MA0

DDR_A_D36

DDR_A_D37

DDR_A_DM4

DDR_A_D38

DDR_A_D39

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D52

DDR_A_D53

DDR_A_DM6

DDR_A_D54

DDR_A_D55

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

+0.75VS

100 mA

DDR_A_D0

DDR_A_D1

DDR_A_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

R421

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_MA10

DDR_A_MA13

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

12

R131

R131

@

@

+1.5V

JDIMM2

3

5

7

9

11

13

15

17

19

21

23

25

27

33

35

39

41

45

47

49

51

53

55

57

59

63

67

69

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

203

205

FOX_AS0A621-U4SG-7H

10K_0402_5%

10K_0402_5%

FOX_AS0A621-U4SG-7H

CONN@JD IMM2

CONN@

VREF_DQ1VSS1

VSS2

DQ0

DQ1

VSS4

DM0

VSS5

DQ2

DQ3

VSS7

DQ8

DQ9

VSS9

DQS#1

DQS129RESET#

VSS1131VSS12

DQ10

DQ11

VSS1337VSS14

DQ16

DQ17

VSS1543VSS16

DQS#2

DQS2

VSS18

DQ18

DQ19

VSS20

DQ24

DQ25

VSS2261DQS#3

DM3

VSS2365VSS24

DQ26

DQ27

VSS2571VSS26

CKE0

VDD1

NC1

BA2

VDD3

A12/BC#

A9

VDD5

A8

A5

VDD7

A3

A1

VDD9

CK0

CK0#

VDD11

A10/AP

BA0

VDD13

WE#

CAS#

VDD15

A13

S1#

VDD17

NCTEST

VSS27

DQ32

DQ33

VSS29

DQS#4

DQS4

VSS32

DQ34

DQ35

VSS34

DQ40

DQ41

VSS36

DM5

VSS37

DQ42

DQ43

VSS39

DQ48

DQ49

VSS41

DQS#6

DQS6

VSS44

DQ50

DQ51

VSS46

DQ56

DQ57

VSS48

DM7

VSS49

DQ58

DQ59

VSS51

SA0

VDDSPD

SA1

VTT1

G1

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

DQ14

DQ15

DQ20

DQ21

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS3

DQ30

DQ31

CKE1

VDD2

VDD4

VDD6

VDD8

VDD10

CK1

CK1#

VDD12

BA1

RAS#

VDD14

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

A15

80

A14

82

84

A11

86

A7

88

90

A6

92

A4

94

96

A2

98

A0

100

102

104

106

108

110

112

114

S0#

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

206

G2

4

W=20mil

+VREF_DQ

1

C166

C166

2

@

+3VS

@

DDR_CS1_DIMMB#<5 >

C158

C158

@

@

D D

C C

B B

A A

1

C160

C160

2

@

@

0.1U_0402_16V4Z

0.1U_0402_16V4Z

DDR_A_DQS#1<5,7>

DDR_A_DQS1<5,7>

DDR_A_DQS#2<5,7>

DDR_A_DQS2<5,7>

DDR_CKE0<5,7>

DDR_A_BS2<5,7>

DDR_B_CLK2<5>

DDR_B_CLK#2<5>

DDR_A_BS0<5,7>

DDR_A_WE#<5,7>

DDR_A_CAS#<5,7>

DDR_A_DQS#4<5,7>

DDR_A_DQS4<5,7>

DDR_A_DQS#6<5,7>

DDR_A_DQS6<5,7>

1

2

+3VS

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

5

1000P_0402_50V7K

1000P_0402_50V7K

@R421

@

1 2

100_0402_1%

100_0402_1%

R130 10K_040 2_5%@R130 10K_0402_5%@

1 2

1

C159

C159

@

@

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Change JDIMM2 socket to SP07000NZ00 for reverse

2010/12/06 Tock

Change JDIMM2 socket to SP07000NN00

2010/12/14 Tock

DDR_A_DQS#0 <5,7>

DDR_A_DQS0 <5,7>

DDR_RST# <5,7>

DDR_A_DQS#3 <5,7>

DDR_A_DQS3 <5,7>

DDR_CKE1 <5,7>

1

@

@

2

DDR_RST#

C414

C414

100P_0402_50V8J

100P_0402_50V8J

0.1U_0402_16V4Z

0.1U_0402_16V4Z

DDR_A_D[0..63]

DDR_A_MA[0..15]

DDR_A_DM[0..7]

Reserve C414 for DDR_RST#

Michael 2010/11/18

+1.5V

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

2

C167

C167

@

@

1

C145

C145

@

@

1

2

C141

C141

@

@

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

9/23 Reserve R421,R401 on CKE0 & CKE1(S3 hang Issue)

10/11 Change R421 R401 from @ to mount (For A1 APU,B0 APU no Need)

DDR_B_CLK3 <5>

DDR_B_CLK#3 <5>

DDR_A_BS1 <5,7>

DDR_A_RAS# <5,7>

DDR_CS0_DIMMB# <5>

DDR_B_ODT0 <5>

DDR_B_ODT1 <5>

W=20mil

+VREF_CA

1

C146

C146

@

@

2

DDR_A_DQS#5 <5,7>

DDR_A_DQS5 <5,7>

DDR_A_DQS#7 <5,7>

DDR_A_DQS7 <5,7>

DDR_EVENT# <5,7>

FCH_SMDAT0 <7,13,20,21>

FCH_SMCLK0 <7,13,20,21>

1

C147

C147

@

@

2

0.1U_0402_16V4Z

1000P_0402_50V7K

1000P_0402_50V7K

0.1U_0402_16V4Z

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL