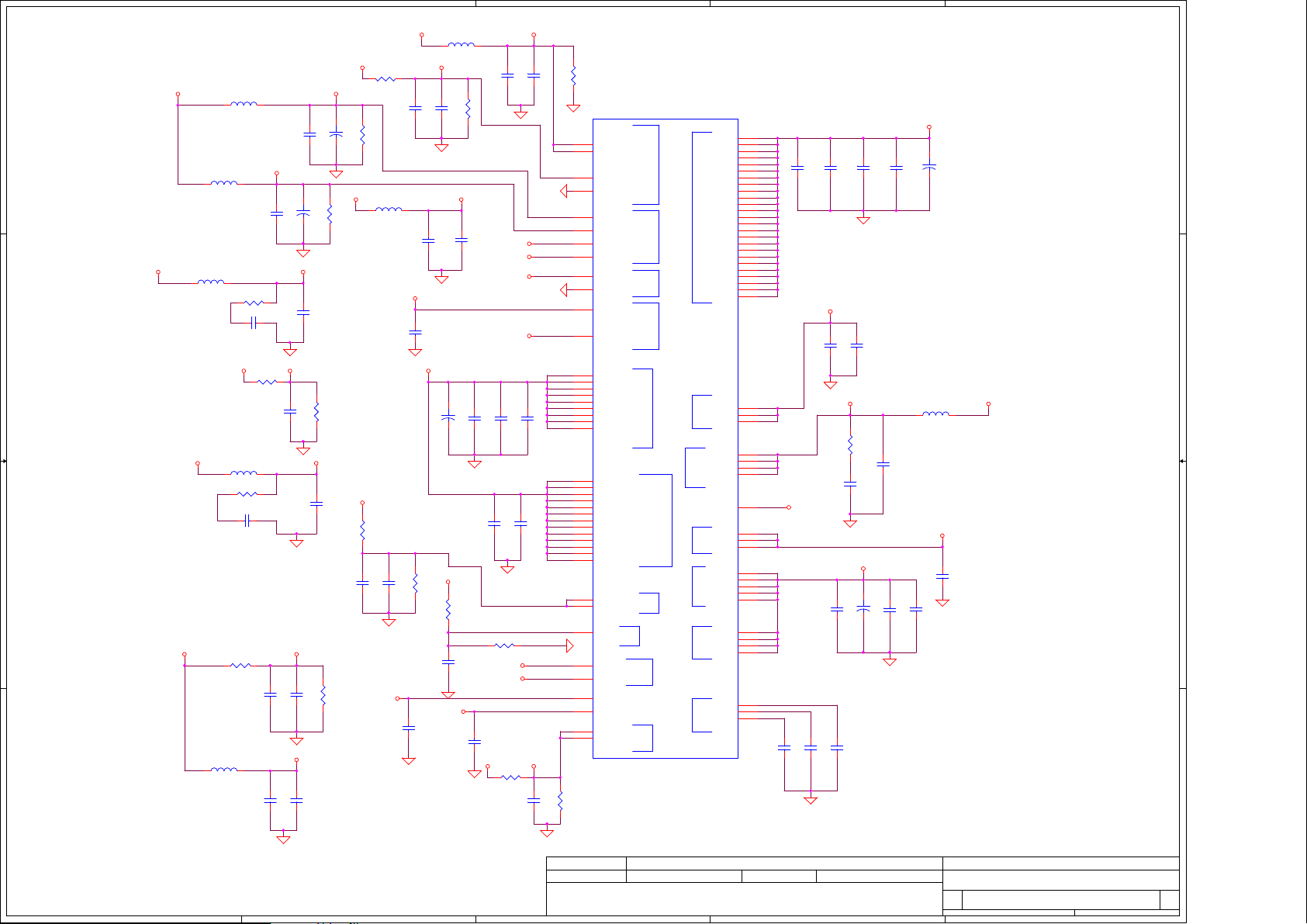

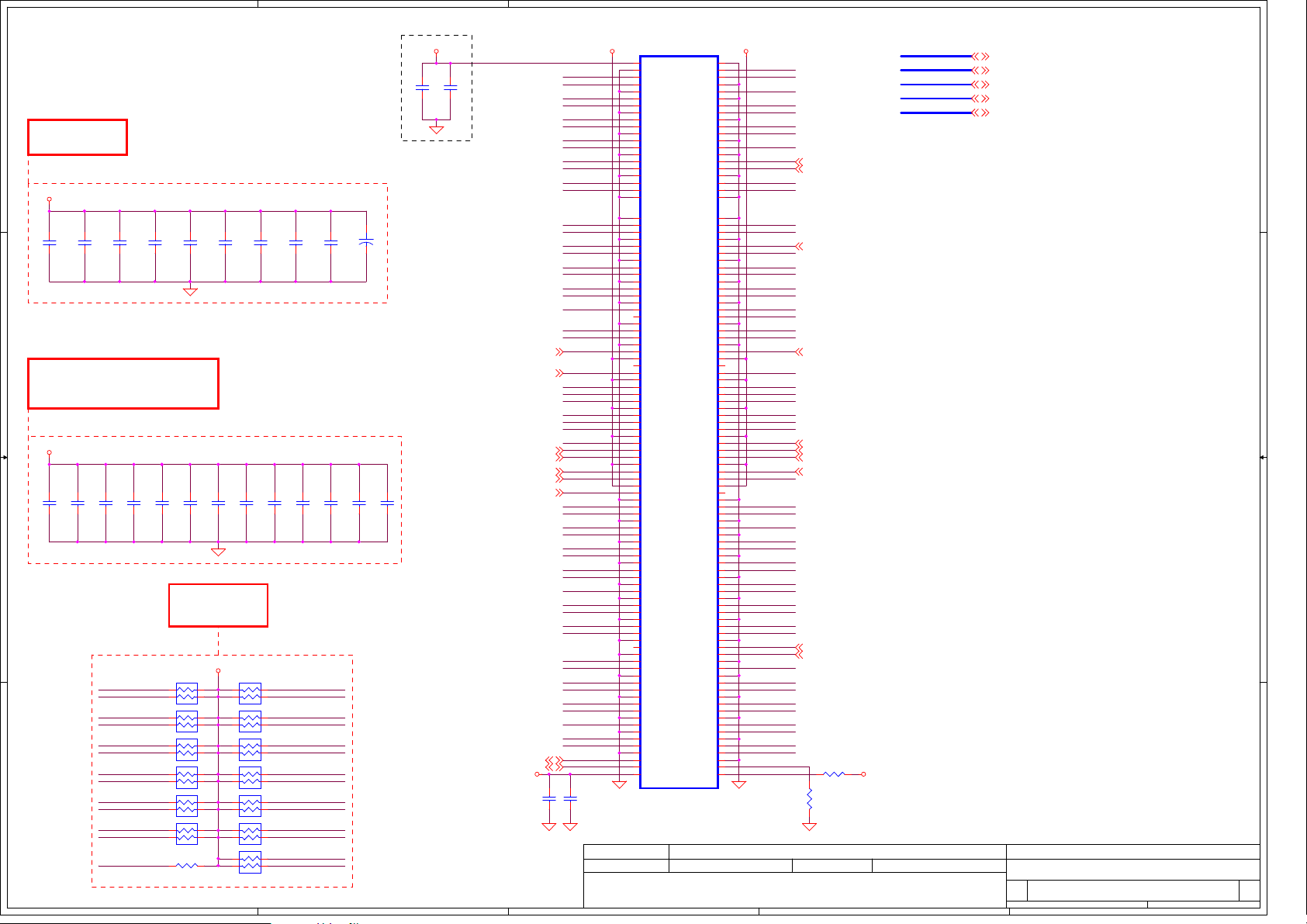

Compal LA-5162P KAM00 UMA, Inspiron Mini 10, LA-5162P KAM01 DIS Schematic

A

B

C

D

E

Compal Model Name:

KAM01(DIS)

KAM00(UMA)

PCB NO:

BOM P/N:

1 1

DA80000E800 LA-5162P R02(X01)(DIS & UMA)

46170431L11 (DIS)

46170431L01 (UMA)

Liver-Pool 13.3"

Compal Confidential

2 2

Schematic Document

Penryn + Cantiga(GM45) + ICH9-M

2009 / 04 / 20

Rev:0.2(X01)

@ : Nopop Component

3 3

1@ : UMA Only

2@ : Discrete Only

ME@ : Mechanical Component

Main-Board TYPE

DIS M/B

UMA M/B

4 4

A

B

BOM P/N

46170431L11

46170431L01

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

BOM CONFIGURATION

2@+ME@

1@+ME@

2009/01/05 2009/01/05

C

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

D

Date: Sheet of

Compal Electronics, Inc.

Cover Sheet

LA-5162P

E

1 60Monday, A pril 20, 2009

0.2

A

B

C

D

E

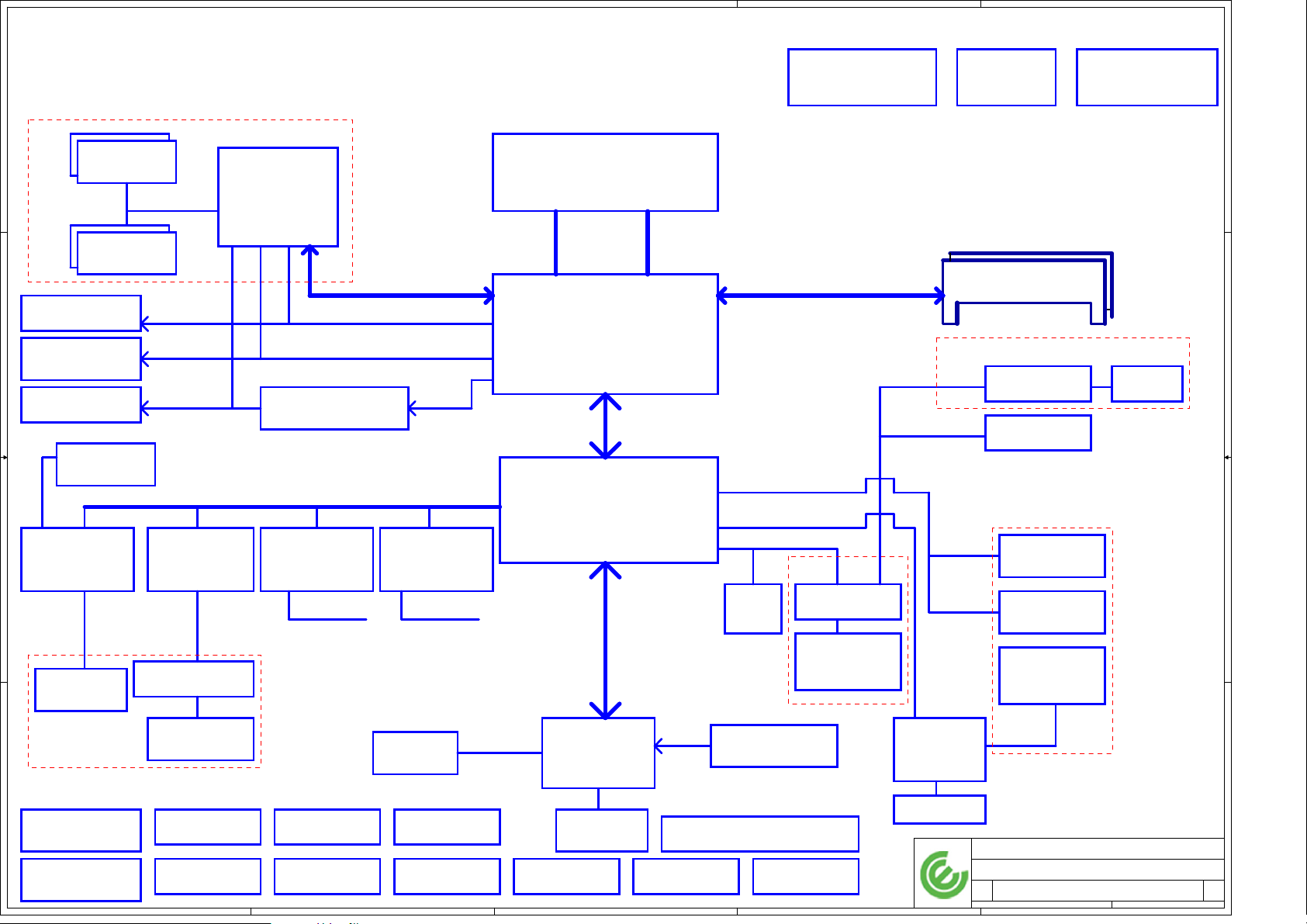

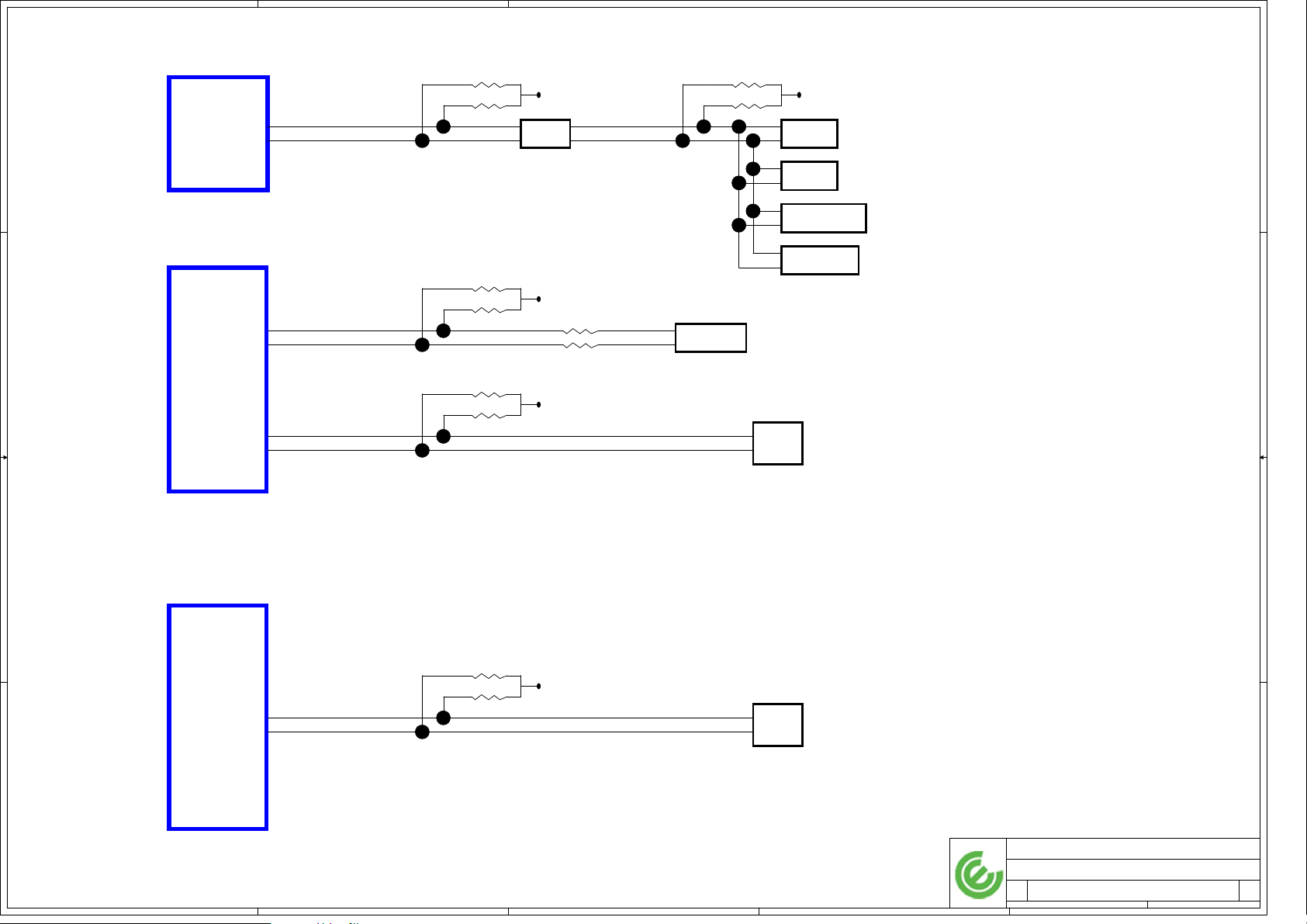

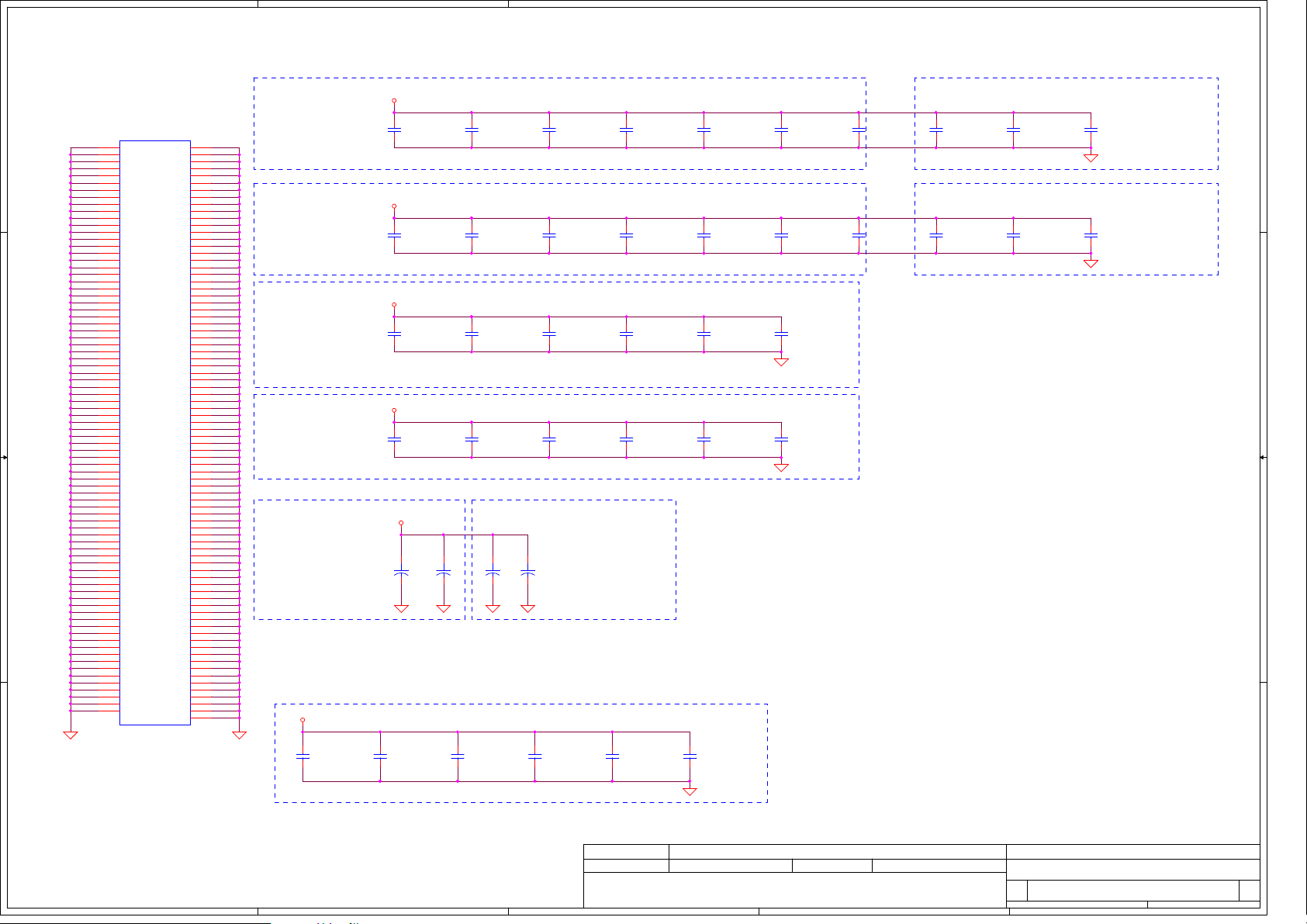

Block Diagram

Compal confidential

Model : KAM00 LA-5162P (UMA)

KAM01 LA-5162P (DIS)

1 1

Discrete Only

DDR2

+1.8VS

64MX16

512 MB

DDR2

+1.8VS

64MX16

CRT CONN

+5VS

2 2

LVDS CONN

+B+

+3VS

+LCDVDD

HDMI CONN

+3VS

CardReader

OZ888GS0L3N

3 3

+3.3VS

page 19

page 19

page 20

3 in 1 CONN

+3VS_CR

page 27

page 27

Giga LAN

RTL8111DL

+3VALW

+LAN_IO

+LAN_VDD

M92-S2-LP

+1.8VS

+VGA_CO RE

+3VS_DE LAY

+1.1V S_GFX_PCIE

PCI Express BUS

page 26

page 34 ~39

PCIE-E 16X

RG B

L VD S

HDMI level shift

PS8101T

+3.3V _RUN

Mini Card

WiFi

+3VS

+1.5VS

+3VALW

+3V_WLAN

USB[4]

PC IE3PC IE2PC IE5

page 28

page 20

+3VS

+3V_PEC

+3VS_PEC

+1.5VS

+1.5VS_PEC

HD MI

PC IE4

EX PRESS Card

page30

USB[7]

+1.5VS

+VCCP

+CPU_CORE

H_ A#( 3.. 35) H_ D#( 0..6 3)

+3VS

+1.8V/+1.8VS

+1.5VS

+VCCP

+3VS

+VCCP

+1.5VS

+3VALW

+RTCVCC

Pe ntium-M

Penryn -4MB (Socket P)

uFCPGA CPU

478pin

FSB

FSB 800/106 6 MHz

IN TEL

Cantiga

1329pin BGA

page 10,11 ,12,13,14, 15

DM I

+1.5V_R UN

100M Hz

IN TEL

IC H9-M

67 6pin BGA

page 21,22,23,24

page 7,8,9

Memory BUS

(DDR2)

IHDA I/F

S-ATA 0/4

HDD

+5VS

page 28

Clock Generator

CK505

SLG8LP554BVTR

+3VS

+1.8 V_MEM 667/800M Hz

USB 2.0

SA TA0

eSATA Repeater

+3VS

USB[2]

SA TA4

page 29

page6

USB[11]

USB[8]

FAN

FAN1_POWER

+5VS

DDRII-DIMM X2

BANK 0, 1, 2, 3, 4 ,5 ,6 ,7

+1.8V

+V_DDR_MCH_REF

Combine with LVDS Cable

+5VS

Bl ue Tooth

+3VS

USB[0]

USB[1]

page 16,17

Ca mera

USB Port

+5V_USBR

USB Port

+5V_USBR

page 28

page 30

page 29

page 29

The rmal Sensor

+3VS

1402

page 18page 18

INT MIC

IEEE 139 4

C onn

page 29

Transformer

page 29

LPC BUS

E-SATA

CONN

+5V_ESATA

page 29

HeadPhone &

MIC Jack

page 29

On IO/B

RJ45 Conn

+LAN_IO

page 29

On IO/B

4 4

Power On/Off

SW & LED

page 31

Power Cont rol

page 32

DCIN/Pre charge

Ch arger

A

page 40

page 41

+3VALWP/+5VALWP

page 42

+VCCP

page 43

Touch Pad

+5VS

B

page 31

+1.8VP

+1.5VSP

PS2 I/F

page 44

page 45

+VGA_COREP

KBC

KB926D3

+RTC_CELL

+3.3V_ALW

Int.KBD

page 46

page 30

page 31

+CPU_COREP

C

SPI

MX 2 5 L 160 5AM 2C

+3VALW

+EC_AVCC

page 30

2Mb

+0.9V SP/+1.1V_GFX_PCIEP

page 47

Battery

page 48

page 49

D

HD Codec

92 HD81B

+3VS

+AVDD_H D

page 25

INT. Speaker

2 x 1W

On IO/B

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Doc ument Number Re v

Date: Sheet of

Compal Electronics, Inc.

Block Diagram

LA-5162P

2 60Monday, A pril 20, 2009

E

1A

A

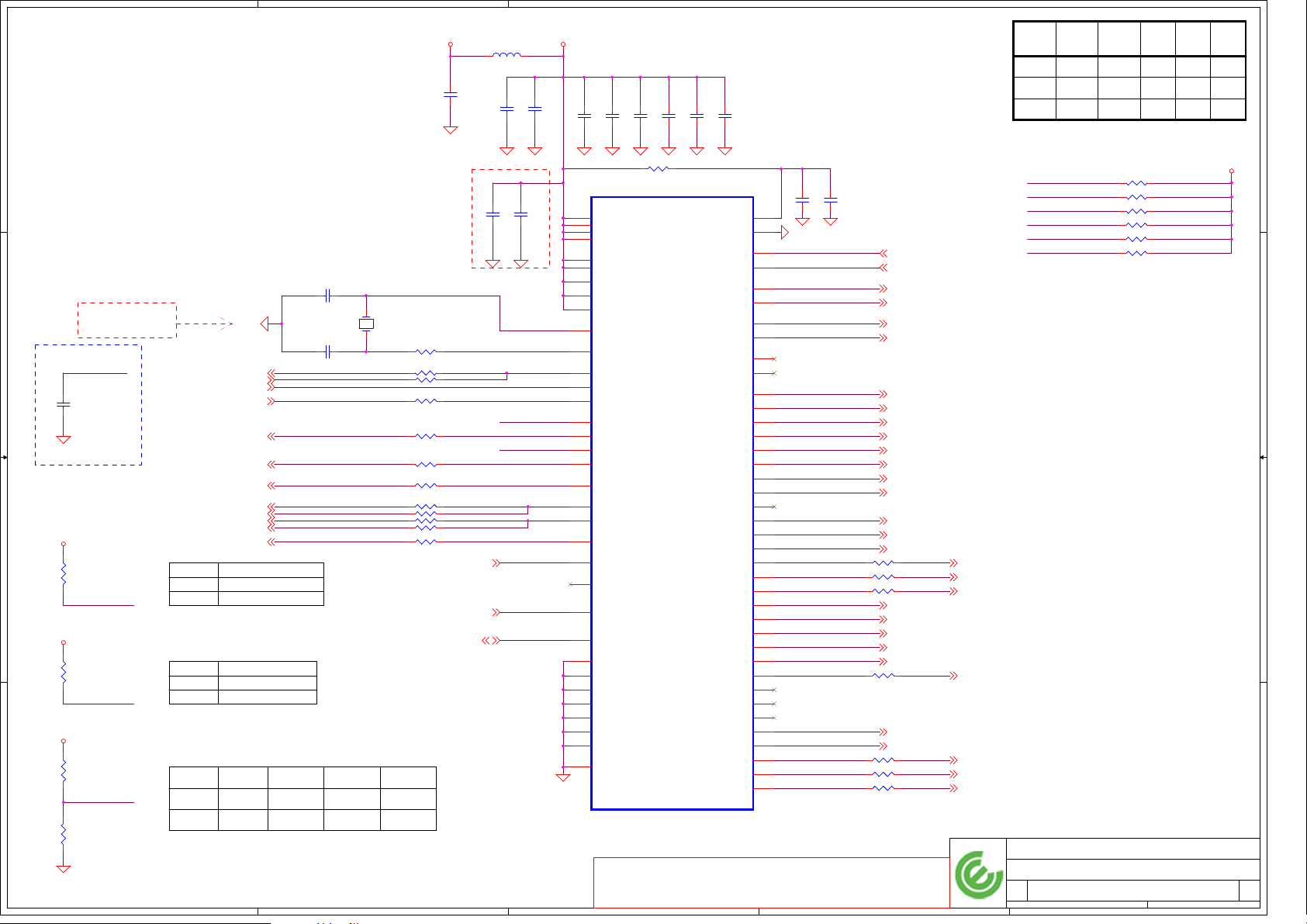

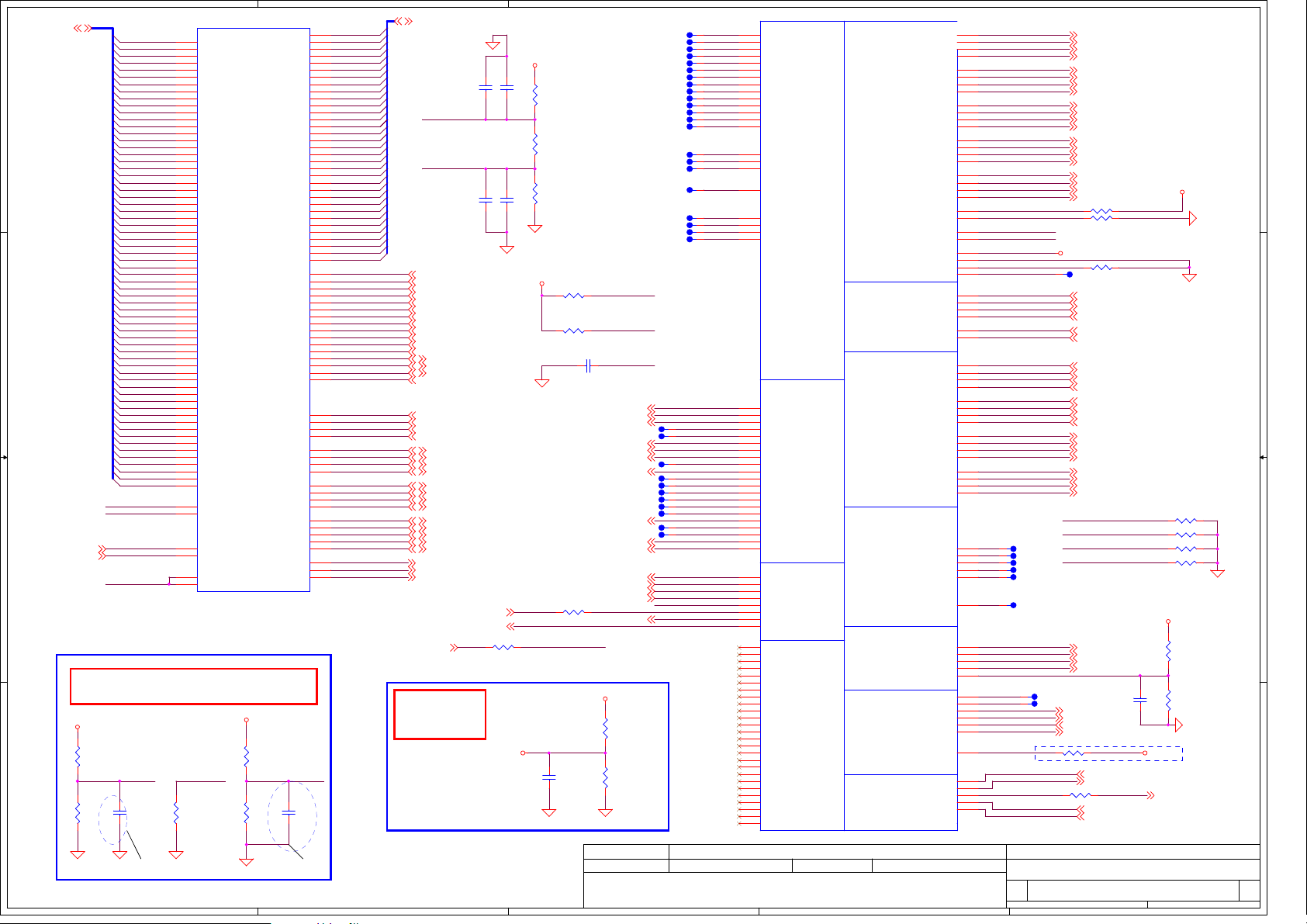

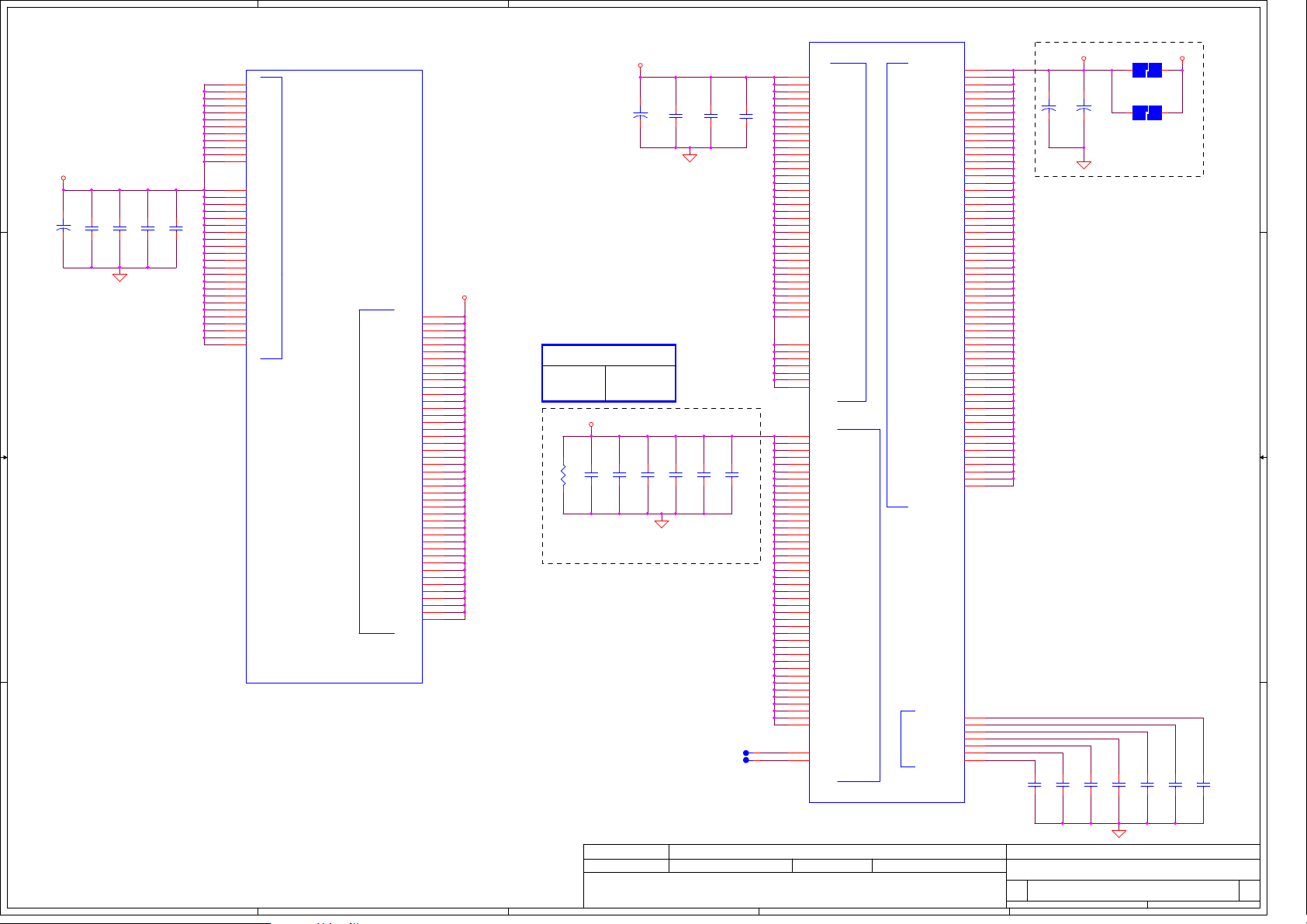

Voltage Rails

State

S0

S1

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

1 1

O MEANS ON X MEANS OFF

power

plane

+B

O

O

O

O

O

X

+5VALW

+3VALW

+1.8V

+1.1VS_GFX_PCIE

O

O

O

O

X

O

X X

X

X X X

+5VS

+3VS

+1.5VS

+VCCP

+CPU_CORE

+GPU_CORE

+1.8VS

+0.9VS

OO

OO

X

X

SATA

Lane 0

Lane 1

Lane 4

Lane 5

DESTINATION

HDD

NONE

ESATA

NONE

USB PORT#

0

1

2

3

DESTINATION

JUSBR1

JUSBR2

JUSBR3(E-SATA)

NONE

PCI EXPRESS

Lane 1 NONE

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

DESTINATION

GIGA LAN

WLAN

EXPRESS CARD

CARD READER

NONE

BOARD ID Table

BOARD ID

ID

0

0.1(X00)

1

0.2(X01)

2

0.3(X02)

3

1.0(A00)

NC

100K

100K

100K

Symbol Note :

: means Digital Ground

: means Analog Ground

@ : means just reserve , no build

DEBUG@ : means just reserve for debug.

RbRa

0

9.09K

20K

37.4K

Vab

0V

0.25V

0.50V

0.82V

ICH9-M

4

5

6

*

7

8

9

10

11

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

WLAN

NONE

NONE

Express card

Bluetooth

NONE

NONE

CAMERA

2009/01/05 2009/01/05

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

Compal Electronics, Inc.

Index and Configuration

LA-5162P

3 60Monday, A pril 20, 2009

0.2

5

4

3

2

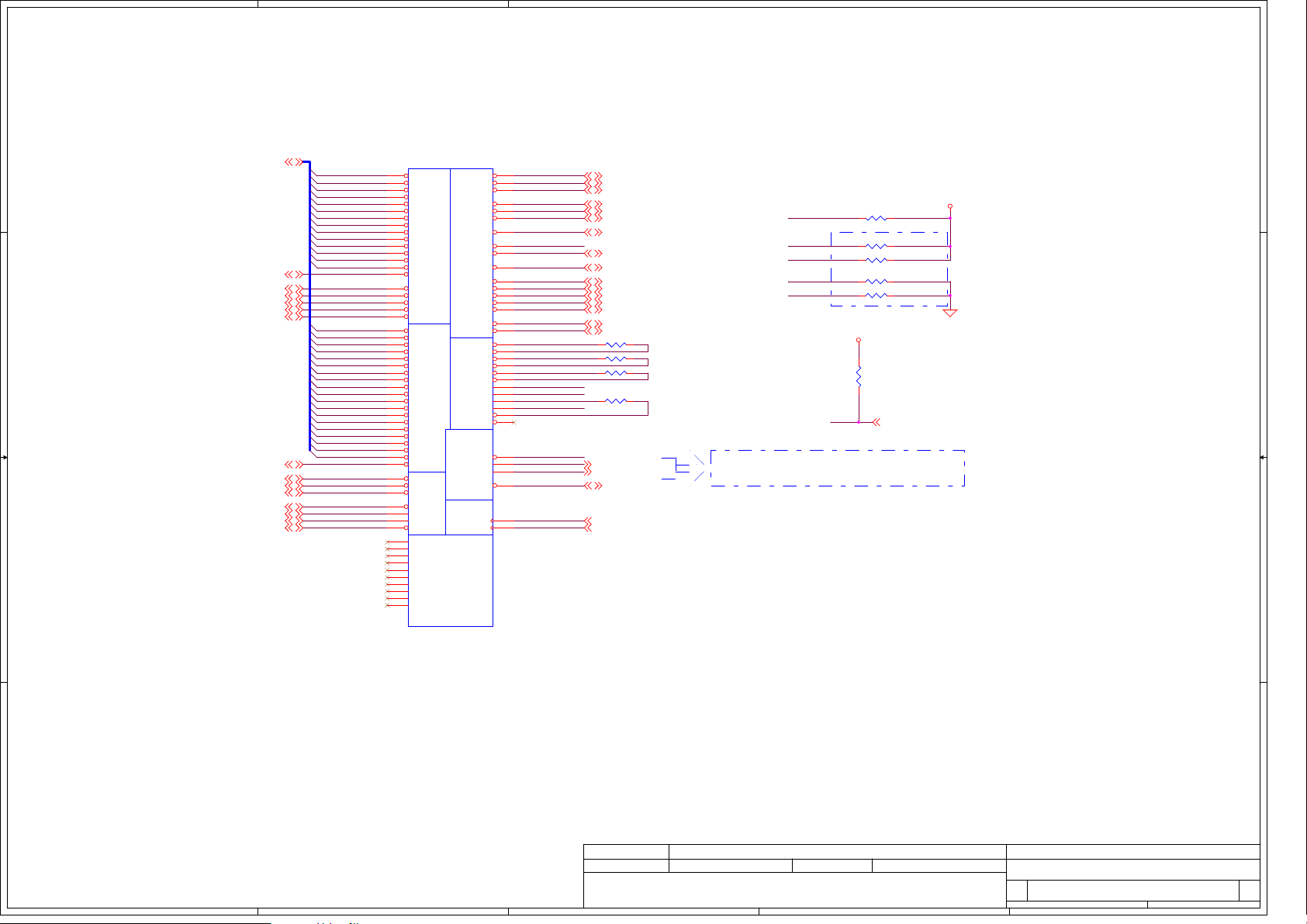

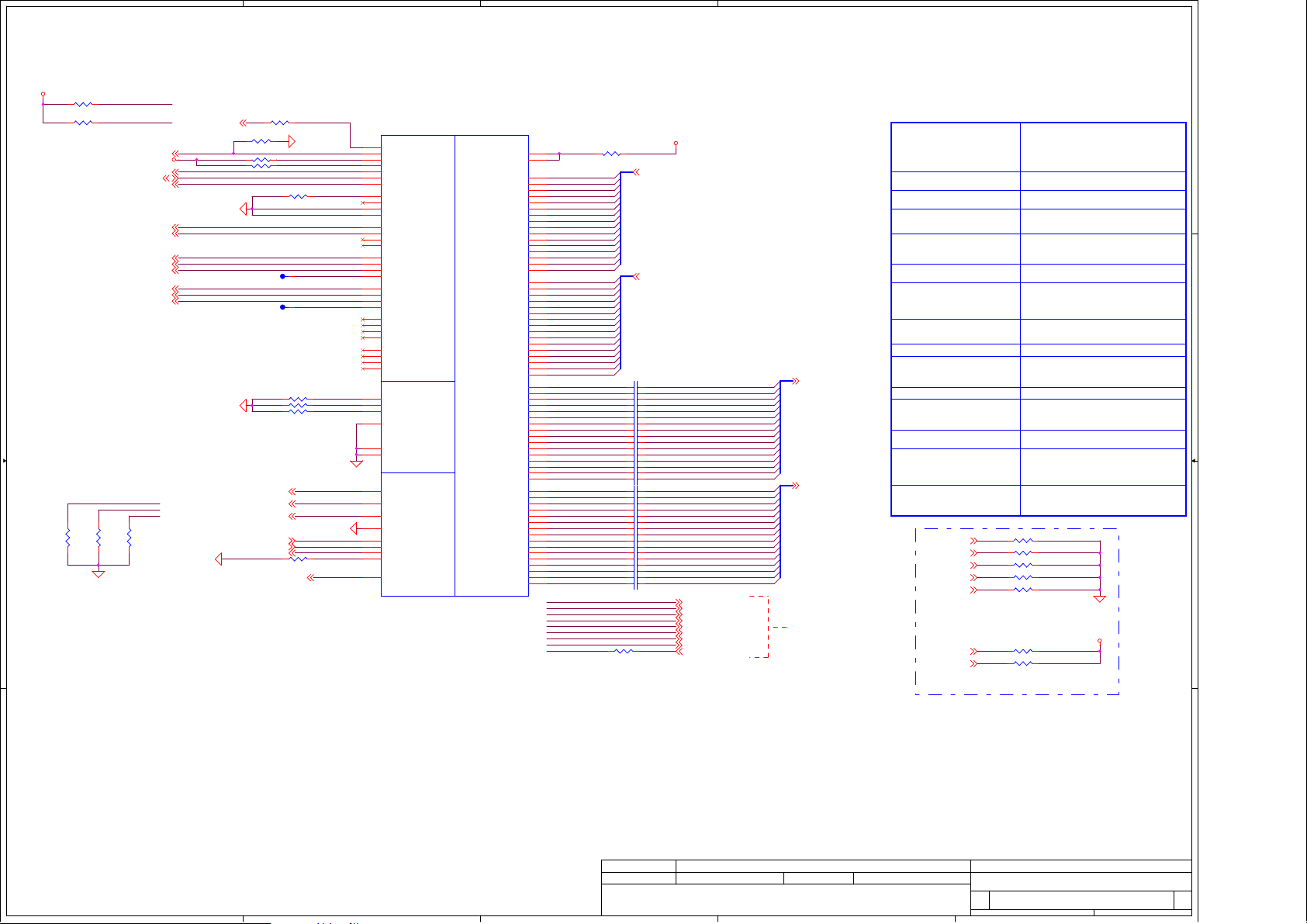

1

INVERTER

ADAPTER

D D

EN_WOL#

SUSP

BATTERY

EC_ON

TPS51427

(PU5)

+3VALW

(U41)

SI3456BDV

(Q128)

SI4800DY

(U40)

RT9013

+1.5V_HDA

+LAN_IO

+3VS

3VS_DELAY_ON

SI2301BDS

(QG1)

+3VS_DELAY

B+

BATT+

C C

+5VALW

RUNON

CHARGER

24751

(PU4)

2@

VGA_ON

ISL6268CAZ-T

(PU9)

+VGA_CORE

SI4800DY

(U39)

+5VS

CAM_ON/OFF#

TPS71718DCKR

(U59)

SI2301BDS

(Q15)

+5V_AVDD_HD

+5V_CAM

SYSON

B B

VR_ON'

SUSP#

A A

5

SUSP#

TPS51117RGYR

(PU7)

ISL6266ACRZ-T

(PU10)

TPS51117RGYR

(PU6)

TPS51117RGYR

(PU8)

4

+1.8V

+CPU_CORE

+VCCP

+1.5VS

1.1VS_GFX_ON

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

SUSP

VGA_PWROD#

MAX8794

(PU11)

RT9026GFP

(PU12)

SI4800DY

(UG41)

+1.1V_GFX_PCIEP

+0.9VS

+1.8VS

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Doc ument Number Re v

2

Date: Sheet of

Compal Electronics, Inc.

Power Rails

LA-5162P

4 60Monday, A pril 20, 2009

1

1.0

5

4

3

2

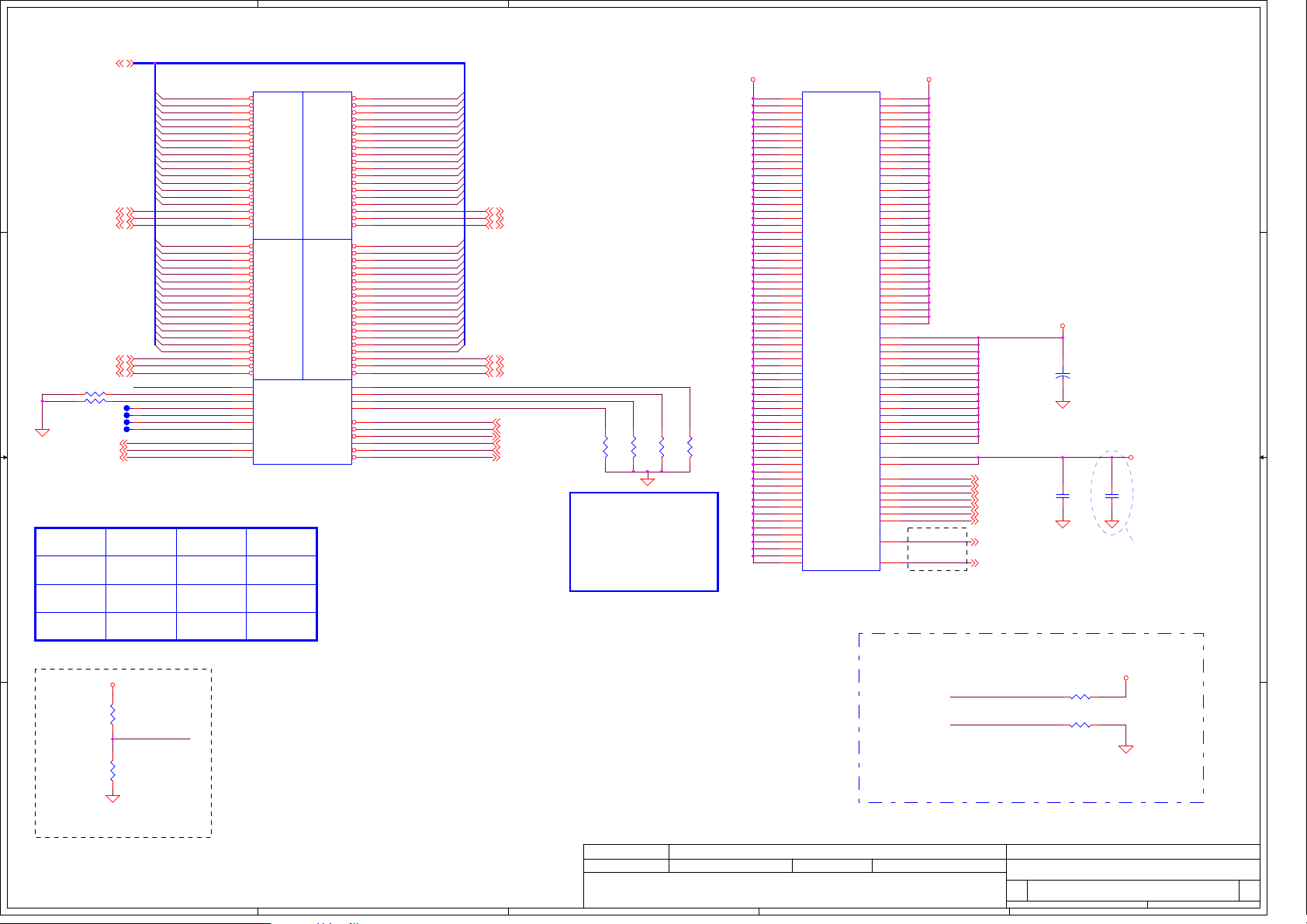

1

2.2K

2.2K

G16

D D

ICH9-M

C C

ICH_SMBCLK

A13 ICH_SMBDATA

4.7K

4.7K

EC_SMB_CK1 7

77

EC_SMB_DA1

78

ENE

2.2K

+3VALW

2N7002

+5VALW

100 ohm

100 ohm

ICH_SM_CLK

ICH_SM_DA

Battery

6

Connector

2.2K

2.2K

16

Colck

17

Generator

195

JDIMMA

197

JDIMMB

8

7

Express Card

32

30

WLAN Card

+3VS

KB926

+3VS

CLK_THERMAL

DATA_THERMAL

8

7

EMC

1402

79

SMB_CLK_THERMAL

80

SMB_DATA_THERMAL

2.2K

B B

2.2K

2.2K

ATI

U7 ATI_SMBCLK

ATI_SMBDATAU8

M92-S2

A A

+3V_DELAY

ATI_SMBCLK

ATI_SMBDATA

8

7

ADM

1032

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Doc ument Number Re v

5

4

3

2

Date: Sheet of

Compal Electronics, Inc.

SMBus Topology

LA-5162P

5 60Monday, A pril 20, 2009

1

1.0

5

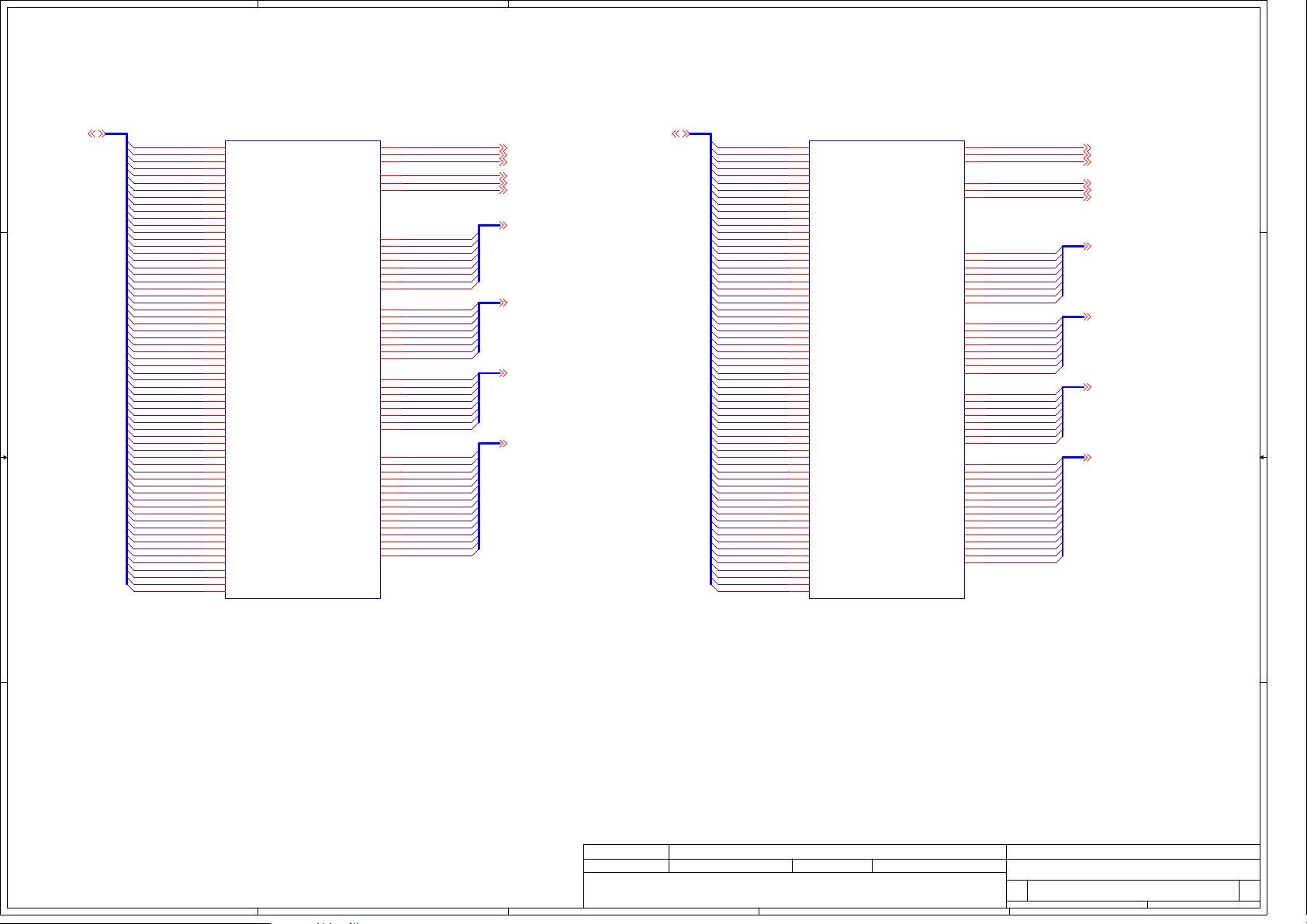

D D

4

+CK_VDD_M AIN+3VS

L1

1 2

BK2125HS601-T_0805~D

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C1

C9

2

0.1U_0402_16V4Z

1

1

C1011

2

2

1

C2

2

3

0.1U_0402_16V4Z

10U_0805_6.3V6-M~D

1

C4

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

C5

C6

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

C3

C7

2

2

2

FSB

FSC

CLKSEL2

0

0 1

*

0

1

1

FSA

CPU

SRC

MHz

100

100

PCI

MHz

33.3100

33.3

33.3

MHz

CLKSEL0CLKSEL1

266

00

200

0

166

1

R1222

1 2

0.047U_0402_16V 4Z~D

0.047U_0402_16V 4Z~D

1

1

C1012

Place close to U1 pin 18 and 40

C16

12

Place crystal w ithin

500 mils of CK505

C C

CLK_ICH_48M

10P_0402_50V8J~D

@

1

C1419

2

Place close to R21 pin2

+3VS

10K_0402_5%~D

B B

R45

1 2

TME

+3VS

10K_0402_5%~D

R1050

1 2

PCI _ICH

+3VS

10K_0402_5%~D

@

12

RG116

*

*

CLK_ICH_ 48M<23>

CPU_MCH_BSEL0<8,10>

CPU_MCH_BSEL1<8,10>

CPU_MCH_BSEL2<8,10>

CLK_DEBU G_PORT<28>

CLK_PC I_926<30>

CLK_ICH_ 14M<23>

MCH_ DREFCLK<10>

CLK_ATI_27M<35>

MCH_ DREFCLK#<10>

CLK_ATI_27M_SS<35>

CLK_P CI_ICH<21>

TME0PIN 32

Overclo cking enable

Overclo cking disable1

ITP_EN

PIN 37

Pin 5/6 as SRC_10

0

Pin 5/6 as CPU_ITP

1

33P_0402_50V8J~D

33P_0402_50V8J~D

CLK_ICH_48M

CPU_MCH_BSEL0

CPU_MCH_BSEL1

CPU_MCH_BSEL2

CLK_ICH_14M CLKRE F

MCH_ DREFCLK

CLK_ATI_27M

MCH_ DREFCLK#

CLK_ATI_27M_SS

CLK_P CI_ICH

12

CPN: SJ100005W0L

Y6

C17

14.318 18MHZ_20PF_1Y714318CE1B~D

12

R19 0_0402_5%

R21 33_0402_5%~D

R23 2.2K_0402_5%~D

R25 10K_0402_5%~D

R117 33_0402_5%~D

R1034 33_0402_5%~D

R9 33_0402_5%~D

R40 33_040 2_5%~D

RG44 61.9_0402_1%@

R41 33_040 2_5%~D

RG119 33_ 0402_5%~D@

R44 33_0402_5%~D

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

12

12

CLK_PW RGD<23>

ICH_SM _CLK< 16,17,23,27,28>

ICH_SM_DA<16,17 ,23,27,28>

C13

2

2

CLK_XTAL_IN

CLK_XTAL_OUT

FSA

FSC

FCT_SEL

CLK_DE BUGCLK_DEBU G_PORT

TME CLK_P CIE_LAN#

PCI_E CCLK_PC I_926

DOT96

DOT96#

PCI _ICH

CLK_PW RGD

ICH_SM_CLK

ICH_SM_DA

1

49

54

65

30

36

12

18

40

20

19

41

45

23

34

33

32

27

22

43

44

37

39

9

16

17

4

15

21

31

35

42

68

73

2.2_0603_5%~D

U1

VDD_SRC

VDD_SRC

VDD_SRC

VDD_SRC

VDD_PCI

VDD_PCI

VDD_CPU

VDD_REF

VDD_48

XTAL_IN

XTAL_OUT

USB_48MHz/FSLA

FSL_B/TEST_MODE

REF_0/FSL_C/TEST_SEL

PCICLK4/FCT_SEL

PCICLK3

PCICLK2/TME

PCICLK1

REF_1

DOT_96/27M

DOT_96#/27M_SS

PCICLK_F0/ITP_EN

CKPWRGD/PD#

NC

SMBCLK

SMBDAT

VSS_SRC

VSS_CPU

VSS_REF

VSS_PCI

VSS_PCI

VSS_48

VSS_SRC

THRM_PAD

SLG8LP554BVTR

FCT_SEL PIN44PIN43 PIN48PIN47

A A

FCT_SEL

10K_0402_5%~D

12

R58

1=DIS 27M SSout27M_out

5

DOT96T0=UMA

96/100M_C96/100M_TDOT96C

SRCC0SRCT0

4

SLG8LP554BVTR_QFN72_10X10~D

CIS Link:OK

CPN:SA000026T0L

PROPR IETARY NOTE : THI S SHEE T OF ENGIN EERIN G DRAW ING A ND SP ECIFIC ATION S CON TAINS CONFIDENTIAL

TRADE SECRE T AND OTHE R PROP RIETA RY IN FORMA TION O F DEL L INC . ("DE LL") THIS DOCUME NT MAY NOT

BE TR ANSFER RED O R COP IED WI THOUT THE EXPRE SS WRI TTEN AUTHO RIZATI ON OF DELL . IN ADDITION,

NEITH ER THI S SHE ET NO R THE INFOR MATIO N IT CONTAI NS WA Y BE USED B Y OR DISCL OSED T O ANY THIRD

PARTY WITHO UT DE LL'S EXPRES S WRI TTEN CONSENT.

3

+CK_VDD_A

VDD_A

VSS_A

PCI_STP#

CPU_STP#

CPU_1

CPU_1#

CPU_0

CPU_0#

CPU_ITP/SRC_10

CPU_ITP#/SRC_10#

SRC_9

SRC_9#

CLKREQ_9#

SRC_8

SRC_8#

CLKREQ_8#

SRC_7

SRC_7#

CLKREQ_7#

SRC_6

SRC_6#

CLKREQ_6#

SRC_5

SRC_5#

CLKREQ_5#

SRC_4

SRC_4#

CLKREQ_4#

SRC_3

SRC_3#

CLKREQ_3#

SRC_2

SRC_2#

CLKREQ_2#

SRC_1/SATA

SRC_1#/SATA#

CLKREQ_1#

LCD_CLK/SRC_0

LCD_CLK#/SRC_0#

7

8

25

24

11

10

14

13

6

5

3

2

72

70

69

71

66

67

38

63

64

62

60

61

29

58

59

57

55

56

28

52

53

26

50

51

46

47

48

4.7U_0603_6.3V6M~D

1

C14

C15

2

H_STP_PCI#

H_STP_CPU#

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_CP U_BCLK

CLK_CP U_BCLK#

CLK_P CIE_WLAN

CLK_P CIE_WLAN#

WLAN _CLK_REQ#

CLK_P CIE_LAN

LAN_CLK_RE Q#

CLK_P CIE_ICH

CLK_P CIE_ICH#

CLK_P CIE_CR

CLK_P CIE_CR#

CR_CL K_REQ#

CLK_P CIE_VGA_R

CLK_P CIE_VGA#_R

VGA_CLK_R EQ#_R

CLK_PCIE_EXP

CLK_PCIE_EXP#

EXP_CLK_REQ#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_3GPLLR EQ#_R

CLK_PCIE_SATA

CLK_PCIE_SATA#

SATA_CLK_REQ#_R

DREF_ SSCLK_R

DREF_ SSCLK#_R

0.047U_0402_16V 4Z~D

H_STP_PCI# <23>

H_STP_CPU# <23>

CLK_MCH_BCLK <10>

CLK_MCH_BCLK# <10>

CLK_CP U_BCLK <7>

CLK_CP U_BCLK# <7>

CLK_P CIE_WLAN <28>

CLK_P CIE_WLAN# <28>

WLAN _CLK_REQ# <28>

CLK_P CIE_LAN <26>

CLK_P CIE_LAN# <26>

LAN_CLK_RE Q# <26>

CLK_P CIE_ICH <23>

CLK_P CIE_ICH# <23>

CLK_P CIE_CR <27>

CLK_P CIE_CR# <27>

CR_CL K_REQ# <27>

1 2

RG53 0_0402_5%2@

1 2

RG59 0_0402_5%2@

1 2

RG120 0_0402_5%2@

CLK_PCIE_EXP <27>

CLK_PCIE_EXP# <27>

EXP_CLK_REQ# <27>

CLK_MCH_3GPLL <10>

CLK_MCH_3GPLL# <10>

1 2

R51 475_0402_1%~D

CLK_PCIE_SATA <22>

CLK_PCIE_SATA# <22>

1 2

R1155 475_0402_1%~D

1 2

R54 0_0402_5%

1 2

R60 0_0402_5%

2

CLK_PCIE_ATI <34>

CLK_PCIE_ATI# <34>

ATI_CLK_REQ# <35>

CLK_3GPLLREQ# <10>

SATA_CLK_REQ# <23>

DREF_ SSCLK <10>

DREF_ SSCLK# <10>

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Doc ument Number Re v

Date: Sheet of

WLAN _CLK_REQ#

LAN_CLK_RE Q#

CR_CL K_REQ#

EXP_CLK_REQ#

CLK_3GPLLREQ#

SATA_CLK_REQ#

R6 10K_0402_5%~D

1 2

1 2

1 2

1 2

1 2

1 2

R10 10K_ 0402_5%~D

R7 10K_0402_5%~D

R121 10K_0402_5%~D

R122 10K_0402_5%~D

R127 10K_0402_5%~D

Compal Electronics, Inc.

Clock GEN. with internal terminations

LA-5162P

1

+3VS

1.0

6 60Monday, A pril 20, 2009

5

D D

4

3

2

1

H_A#[ 3..35]<10>

H_ADSTB#0<10>

H_REQ#0<10>

H_REQ#1<10>

H_REQ#2<10>

H_REQ#3<10>

H_REQ#4<10>

C C

H_ADSTB#1<10>

H_A20M#<22>

H_FER R#<22>

H_IGNN E#<22>

H_STPCLK#<22>

H_INTR<22>

H_NMI<22>

H_SMI#<22>

B B

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_ADSTB#0

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADSTB#1

H_A20M#

H_FER R#

H_IGNN E#

H_STPCLK#

H_INT R

H_NMI

H_SMI#

ME@

JCPU1A

ADDR GROUP 0 ADDR GROUP 1

J4

A[3]#

L5

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L2

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U1

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W2

A[27]#

W5

A[28]#

Y4

A[29]#

U2

A[30]#

V4

A[31]#

W3

A[32]#

AA4

AB2

AA3

V1

A6

A5

C4

D5

C6

B4

A3

M4

N5

T2

V3

B2

C3

D2

D22

D3

F6

TH ERMAL

A[33]#

A[34]#

PROCHOT#

A[35]#

ADSTB[1]#

ICH

A20M#

FERR#

THERMTRIP#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

RESERVED

RSVD[10]

FOX_PZ4782A-274R-41_M erom

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

XDP/ITP SIGNALS

DBR#

THERMDA

THERMDC

H CLK

BCLK[0]

BCLK[1]

H_ADS#

H1

H_BNR #

E2

H_BPR I#

G5

H_DEF ER#

H5

H_D RDY#

F21

H_ DBSY#

E1

H_BR0#

F1

H_IER R#

D20

B3

H_LOCK#

H4

H_RESET#

C1

H_RS#0

F3

H_RS#1

F4

H_RS#2

G3

H_ TRDY#

G2

H_HIT#

G6

H_HITM#

E4

AD4

AD3

AD1

AC4

AC2

AC1

XDP_TCK

AC5

XDP_TDI

AA6

TDI

AB3

XDP_TMS

AB5

XDP_TRST#

AB6

C20

VR_TT#

D21

H_THERMDA

A24

H_THERMDC

B25

H_THERMTRIP#

C7

CLK_CP U_BCLK

A22

CLK_CP U_BCLK#

A21

H_ADS# <10>

H_BNR # <10>

H_BPR I# <10>

H_DEF ER# <10>

H_D RDY# <10>

H_D BSY# <10>

H_BR0# <10>

H_INIT# < 22>

H_LOCK# <10>

H_RESET# <10>

H_RS#0 <10>

H_RS#1 <10>

H_RS#2 <10>

H_T RDY# <10>

H_HIT# <10>

H_HITM# <10>

R68

@

1 2

0_0402_5%

R69

@

1 2

0_0402_5%

R71

@

1 2

0_0402_5%

R87

@

1 2

0_0402_5%

H_THERMDA <18>

H_THERM DC <18>

H_THERMTRIP# <10,22>

CLK_CP U_BCLK <6>

CLK_CP U_BCLK# <6>

H_IER R#

XDP_TDI

XDP_TMS

XDP_TRST#

XDP_TCK

R18 56_0402_5%

R5 54.9_0402_1%

R4 54.9_0402_1%

R11 54.9_0402_1%

R35 54.9_0402_1%

This shall place near CPU

+VCCP

VR_TT#

1 2

1 2

1 2

1 2

12

R92

68_0402_1%~D

VR_TT# <48>

+VCCP

12

H_THERMDA, H_THERMDC routing together,

Trace width / Spacing = 10 / 10 mil

CIS Link:OK

12/29

A A

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2009/01/05 2009/01/05

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

2

Date: Sheet of

Compal Electronics, Inc.

Penryn(1/3)-AGTL+/ITP-XDP

LA-5162P

1

7 60Monday, A pril 20, 2009

0.2

5

4

3

2

1

H_D #[0..63]<10>

ME@

H_D#0

H_D#1

H_D#2

D D

H_DSTBN#0<10>

H_DSTBP#0<10>

H_DIN V#0<10>

C C

R52 1K_0402_5%~D@

R22 1K_0402_5%~D@

CPU_MCH_BSEL0<6,10>

CPU_MCH_BSEL1<6,10>

CPU_MCH_BSEL2<6,10>

H_DSTBN#1<10>

H_DSTBP#1<10>

H_DIN V#1<10>

1 2

1 2

T12

T13

T14

T15

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DIN V#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DIN V#1

+V_CPU_GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

CPU_MCH_BSEL0

CPU_MCH_BSEL1

CPU_MCH_BSEL2

layout note: Rout H_DPRSTP# from ICH9 to IMVP6 then to GMCH & CPU

layout note: Route TEST3 & TE ST5 tr aces on ground referenced layer to the TPs

FSB

Frequency

B B

667MHz

800MHz

BSEL[2] BSEL[1]

0 1

0 1

JCPU1B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H22

D[12]#

F26

D[13]#

K22

D[14]#

H23

D[15]#

J26

DSTBN[0]#

H26

DSTBP[0]#

H25

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

AD26

AF26

M24

M23

R24

N25

M26

N24

C23

D25

C24

AF1

C21

L23

L22

P25

P23

P22

T24

L25

T25

L26

A26

B22

B23

DATA GRP 1

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

MISC

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

BSEL[0]

BSEL[1]

BSEL[2]

FOX_PZ4782A-274R-41_M erom

BSEL[0]

1

0

DATA GRP 0

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

DATA GRP 2DATA GRP 3

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

*

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DIN V#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#3

H_DSTBP#3

H_DIN V#3

COMP0

COMP1

COMP2

COMP3

H_DPRSTP#

H_DPSLP#

H_DPW R#

H_PW RGOOD

H_CPUSLP #

H_PSI#

H_DSTBN#2 <10>

H_DSTBP#2 <10>

H_DIN V#2 <10>

H_DSTBN#3 <10>

H_DSTBP#3 <10>

H_DIN V#3 <10>

H_DPRSTP# <10,22,48>

H_DPSLP# <22>

H_DPW R# <10>

H_PW RGOOD <22>

H_CPUSLP # <10>

H_PSI# <48>

12

12

12

R1023

R24

54.9_0402_1%

27.4_0402_1%

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

mils away from any other

toggling signal.

COMP[0,2] trace width is

18 mils. COMP[1,3] trace

width is 4 mils

R26

R1025

27.4_0402_1%

54.9_0402_1%

+CPU_ CORE +CPU_CORE

12

ME@

JCPU 1C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

AB17

AB18

VCCSENSE

VCC[065]

VCC[066]

VCC[067]

VSSSENSE

FOX_PZ4782A-274R-41_M erom

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

VCCSENS E

VSSSENSE

CPU_V ID0 <48>

CPU_V ID1 <48>

CPU_V ID2 <48>

CPU_V ID3 <48>

CPU_V ID4 <48>

CPU_V ID5 <48>

CPU_V ID6 <48>

VCCSENS E <48>

VSSSENSE <48>

220U_ D2_4VY_R15M

+VCCP

C1110

10U_0805_6.3V6M

1

2

1

2

+

C1112

+1.5VS

1

C11

2

0.01U_0402_16V7K

Near pin B26

1066MHz 0 0 0

VCCSENSE, VSSSENSE-->Width=18mils,

Space=7mils, Space to other signals 25mils at least.

+VCCP

12

R27

1K_0402_1%

+V_CPU_GTLREF

12

R29

2K_0402_1%

A A

Close to CPU pin AD26

Length match within 25 mils.

Close to CPU pin

within 500mils.

within 500mils.

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2009/01/05 2009/01/05

Compal Secret Data

Deciphered Date

2

VCCSENS E

VSSSENSE

Title

Size Doc ument Number Re v

Cus tom

LA-5162P

Date: Sheet of

+CPU_C ORE

R28100_0402_1%

12

R30100_0402_1%

12

Compal Electronics, Inc.

Penryn(2/3)-AGTL+/ITP-XDP

1

8 60Monday, A pril 20, 2009

0.2

5

High Frequence Decoupling

10uF 0805 X5R -> 85 degree.

D D

C C

B B

A A

ME@

JCPU 1D

A4

A8

A11

A14

A16

A19

A23

AF2

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C11

C14

C16

C19

C2

C22

C25

D1

D4

D8

D11

D13

D16

D19

D23

D26

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G23

G26

H3

H6

H21

H24

J2

J5

J22

J25

K1

K4

K23

K26

L3

L6

L21

L24

M2

M5

M22

M25

N1

N4

N23

N26

FOX_PZ4782A-274R-41_M erom

VSS[082]

VSS[001]

VSS[002]

VSS[083]

VSS[003]

VSS[084]

VSS[004]

VSS[085]

VSS[005]

VSS[086]

VSS[006]

VSS[087]

VSS[007]

VSS[088]

VSS[008]

VSS[089]

VSS[009]

VSS[090]

VSS[010]

VSS[091]

VSS[011]

VSS[092]

VSS[012]

VSS[093]

VSS[013]

VSS[094]

VSS[014]

VSS[095]

VSS[015]

VSS[096]

VSS[016]

VSS[097]

VSS[017]

VSS[098]

VSS[018]

VSS[099]

VSS[019]

VSS[100]

VSS[020]

VSS[101]

VSS[021]

VSS[102]

VSS[022]

VSS[103]

VSS[023]

VSS[104]

VSS[024]

VSS[105]

VSS[025]

VSS[106]

VSS[026]

VSS[107]

VSS[027]

VSS[108]

VSS[028]

VSS[109]

VSS[029]

VSS[110]

VSS[030]

VSS[111]

VSS[031]

VSS[112]

VSS[032]

VSS[113]

VSS[033]

VSS[114]

VSS[034]

VSS[115]

VSS[035]

VSS[116]

VSS[036]

VSS[117]

VSS[037]

VSS[118]

VSS[038]

VSS[119]

VSS[039]

VSS[120]

VSS[040]

VSS[121]

VSS[041]

VSS[122]

VSS[042]

VSS[123]

VSS[043]

VSS[124]

VSS[044]

VSS[125]

VSS[045]

VSS[126]

VSS[046]

VSS[127]

VSS[047]

VSS[128]

VSS[048]

VSS[129]

VSS[049]

VSS[130]

VSS[050]

VSS[131]

VSS[051]

VSS[132]

VSS[052]

VSS[133]

VSS[053]

VSS[134]

VSS[054]

VSS[135]

VSS[055]

VSS[136]

VSS[056]

VSS[137]

VSS[057]

VSS[138]

VSS[058]

VSS[139]

VSS[059]

VSS[140]

VSS[060]

VSS[141]

VSS[061]

VSS[142]

VSS[062]

VSS[143]

VSS[063]

VSS[144]

VSS[064]

VSS[145]

VSS[065]

VSS[146]

VSS[066]

VSS[147]

VSS[148]

VSS[067]

VSS[068]

VSS[149]

VSS[069]

VSS[150]

VSS[070]

VSS[151]

VSS[071]

VSS[152]

VSS[072]

VSS[153]

VSS[073]

VSS[154]

VSS[074]

VSS[155]

VSS[075]

VSS[156]

VSS[076]

VSS[157]

VSS[077]

VSS[158]

VSS[078]

VSS[159]

VSS[079]

VSS[160]

VSS[080]

VSS[161]

VSS[081]P3VSS[162]

VSS[163]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

+VCCP

1

C213

0.1U_0402_16V7K~D

2

4

+CPU_ CORE

1

C204

10U_0805_4VAM~D

2

+CPU_ CORE

1

C180

10U_0805_4VAM~D

2

+CPU_ CORE

1

C501

10U_0805_4VAM~D

2

+CPU_ CORE

1

C502

10U_0805_4VAM~D

2

+CPU_C ORE

1

C196

+

2

1

C209

0.1U_0402_16V7K~D

2

3

2

1

Place these caps inside

the CPU socket.

1

C205

10U_0805_4VAM~D

2

1

C529

10U_0805_4VAM~D

2

1

C232

10U_0805_4VAM~D

2

1

C258

10U_0805_4VAM~D

2

1

C505

10U_0805_4VAM~D

2

1

C504

10U_0805_4VAM~D

2

1

C257

10U_0805_4VAM~D

2

1

C262

10U_0805_4VAM~D

2

1

( Left side on Top ).

C214

10U_0805_4VAM~D

2

Place these caps inside

the CPU socket.

1

C202

10U_0805_4VAM~D

2

1

C508

10U_0805_4VAM~D

2

1

C510

10U_0805_4VAM~D

2

330U_ D2_2.5VY_R9M

330U_ D2_2.5VY_R9M

1

C198

+

2

1

C259

+

2

1

C212

0.1U_0402_16V7K~D

2

330U_ D2_2.5VY_R9M

330U_ D2_2.5VY_R9M

1

C255

+

2

1

2

1

C254

10U_0805_4VAM~D

2

1

C514

10U_0805_4VAM~D

2

1

C515

10U_0805_4VAM~D

2

C188

0.1U_0402_16V7K~D

1

C190

10U_0805_4VAM~D

2

1

C519

10U_0805_4VAM~D

2

1

C520

10U_0805_4VAM~D

2

1

C183

0.1U_0402_16V7K~D

2

1

C203

10U_0805_4VAM~D

2

1

C523

10U_0805_4VAM~D

2

1

C528

10U_0805_4VAM~D

2

1

C200

10U_0805_4VAM~D

2

1

C533

10U_0805_4VAM~D

2

1

C532

10U_0805_4VAM~D

2

ESR <= 1.5m ohm

Capacitor > 880 uF

Plac e these inside

sock et cavity o n L8

(North side

Secon dary)

1

C185

0.1U_0402_16V7K~D

2

1

C184

10U_0805_4VAM~D

2

1

C199

10U_0805_4VAM~D

2

1

C208

10U_0805_4VAM~D

2

1

( Righ t side on Top ).

C1126

10U_0805_4VAM~D

2

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2009/01/05 2009/01/05

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

2

Date: Sheet of

Compal Electronics, Inc.

Penryn(3/3)-AGTL+/ITP-XDP

LA-5162P

1

9 60Monday, A pril 20, 2009

0.2

5

U4A

H_D# [0..63]<8>

D D

C C

H_RESET#<7>

H_CPU SLP#<8>

B B

Layout Note:

+H_RCO MP / +H_VREF / +H_SWING

trace width and spacing is 10/20

+VCCP

12

R1045

1K_0402_1%

A A

12

R46

2K_0402_1%

1

2

0.1U_0402_16V7K~D

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

+H_SW ING

+H_RCOMP

H_RESET#

H_CPUSLP #

+H_VREF

+H_VREF

C391

@

5

F2

H_D#_0

G8

H_D#_1

F8

H_D#_2

E6

H_D#_3

G2

H_D#_4

H6

H_D#_5

H2

H_D#_6

F6

H_D#_7

D4

H_D#_8

H3

H_D#_9

M9

H_D#_10

M11

H_D#_11

J1

H_D#_12

J2

H_D#_13

N12

H_D#_14

J6

H_D#_15

P2

H_D#_16

L2

H_D#_17

R2

H_D#_18

N9

H_D#_19

L6

H_D#_20

M5

H_D#_21

J3

H_D#_22

N2

H_D#_23

R1

H_D#_24

N5

H_D#_25

N6

H_D#_26

P13

H_D#_27

N8

H_D#_28

L7

H_D#_29

N10

H_D#_30

M3

H_D#_31

Y3

H_D#_32

AD14

H_D#_33

Y6

H_D#_34

Y10

H_D#_35

Y12

H_D#_36

Y14

H_D#_37

Y7

H_D#_38

W2

H_D#_39

AA8

H_D#_40

Y9

H_D#_41

AA13

H_D#_42

AA9

H_D#_43

AA11

H_D#_44

AD11

H_D#_45

AD10

H_D#_46

AD13

H_D#_47

AE12

H_D#_48

AE9

H_D#_49

AA2

H_D#_50

AD8

H_D#_51

AA3

H_D#_52

AD3

H_D#_53

AD7

H_D#_54

AE14

H_D#_55

AF3

H_D#_56

AC1

H_D#_57

AE3

H_D#_58

AC3

H_D#_59

AE11

H_D#_60

AE8

H_D#_61

AG2

H_D#_62

AD6

H_D#_63

C5

H_SWING

E3

H_RCOMP

C12

H_CPURST#

E11

H_CPUSLP#

A11

H_AVREF

B11

H_DVREF

CANTI GA ES_FCBGA1329

+H_RCOMP

12

R324

24.9_0402_1%

+VCCP

221_0603_1%

100_0402_1%

12

R322

12

R323

H_ADSTB#_0

H_ADSTB#_1

H_DEFER#

HOST

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

Near B3 pinwithin 100 mils from NB

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_BNR#

H_BPRI#

H_BREQ#

H_DBSY#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_RS#_0

H_RS#_1

H_RS#_2

+H_SW ING

1

2

0.1U_0402_16V7K~D

C386

A14

C15

F16

H13

C18

M16

J13

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

B18

K17

B20

F21

K21

L20

H12

B16

G17

A9

F11

G12

E9

B10

AH7

AH6

J11

F9

H9

E12

H11

C9

J8

L3

Y13

Y1

L10

M7

AA5

AE6

L9

M8

AA6

AE5

B15

K13

F13

B13

B14

B6

F12

C8

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR #

H_BPR I#

H_BR0#

H_DEF ER#

H_ DBSY#

CLK_MCH_BCLK

CLK_MCH_BCLK#

H_DPW R#

H_D RDY#

H_HIT#

H_HITM#

H_LOCK#

H_ TRDY#

H_DIN V#0

H_DIN V#1

H_DIN V#2

H_DIN V#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

4

H_A#[ 3..35] <7>

+SMRCOMP_VOH

+SMRCOMP_VOL

H_ADS# <7>

H_ADSTB#0 < 7>

H_ADSTB#1 < 7>

H_BNR # <7>

H_BPR I# <7>

H_BR0# <7>

H_DEF ER# <7>

H_D BSY# <7>

CLK_MCH_BCLK <6>

CLK_MCH_BCLK# <6>

H_DPW R# <8>

H_D RDY# <7>

H_HIT# <7>

H_HITM# <7>

H_LOCK# <7>

H_T RDY# <7>

H_DIN V#0 <8>

H_DIN V#1 <8>

H_DIN V#2 <8>

H_DIN V#3 <8>

H_DSTBN#0 <8>

H_DSTBN#1 <8>

H_DSTBN#2 <8>

H_DSTBN#3 <8>

H_DSTBP#0 <8>

H_DSTBP#1 <8>

H_DSTBP#2 <8>

H_DSTBP#3 <8>

H_REQ#0 <7>

H_REQ#1 <7>

H_REQ#2 <7>

H_REQ#3 <7>

H_REQ#4 <7>

H_RS#0 <7>

H_RS#1 <7>

H_RS#2 <7>

ICH_P WROK<23,30>

Layout Note:

+V_DDR _MCH_REF

trace width and

spacin g is 20/20.

4

3

T7

T11

T72

+1.8V

1

1

C398

2

2.2U_06 03_6.3V6K~D

1

C403

2

2.2U_06 03_6.3V6K~D

PLT_RST#<21,27,30,34>

DPRSLPVR<23,48>

1 2

R408 0_0402_5%

+V_DD R_MCH_REF +VCCP

0.1U_0402_16V7K~D

12

R331

C400

1K_0402_1%

0.01U_0402_16V7K

2

12

R332

3.01K_0402_1%

12

R333

1

1K_0402_1%

C404

2

0.01U_0402_16V7K

+3VS

10K_0402_5%~D

10K_0402_5%~D

R523 100_0402_5%~D

+V_DD R_MCH_REF

1

C121

2

R82

12

R83

12

C36

@

12

0.1U_0402_16V7K~D

CPU_MCH_BSEL0<6,8>

CPU_MCH_BSEL1<6,8>

CPU_MCH_BSEL2<6,8>

PM_BMBUSY#<23>

H_DPRSTP#<8,22,48>

PM_EXTTS#0<16>

PM_PWROK_R

PM_EXTTS#1<17>

H_THERMTRIP#<7,22>

+1.8V

1 2

PM_EXTTS#0

PM_EXTTS#1

H_DPRSTP#

CFG5<12>

CFG6<12>

CFG7<12>

CFG9<12>

CFG16<12>

CFG19<12>

CFG20<12>

12

R42

1K_0402_1%

12

R43

1K_0402_1%

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

T23

T74

T75

T136

T17

T18

T19

T20

T21

T22

T24

T25

T26

T27

T28

T41

T44

T73

T184

CPU_MCH_BSEL0

CPU_MCH_BSEL1

CPU_MCH_BSEL2

T8

T9

CFG5

CFG6

CFG7

T37

CFG9

T65

T40

CFG12

T67

CFG13

T47

T10

T66

CFG16

T68

T39

CFG19

CFG20

PM_BMBUSY#

H_DPRSTP#

PM_EXTTS#0

PM_EXTTS#1

PM_PWROK_R

PLT_RST#_NB

H_THERMTRIP#

DPRSLPVR

2009/01/05 2009/01/05

3

U4B

M36

RSVD1

N36

RSVD2

R33

RSVD3

T33

RSVD4

AH9

RSVD5

AH10

RSVD6

AH12

RSVD7

AH13

RSVD8

K12

RSVD9

AL34

RSVD10

AK34

RSVD11

AN35

RSVD12

AM35

RSVD13

T24

RSVD14

B31

RSVD15

B2

RSVD16

M1

RSVD17

AY21

RSVD20

BG23

RSVD22

BF23

RSVD23

BH18

RSVD24

BF18

RSVD25

T25

CFG_0

R25

CFG_1

P25

CFG_2

P20

CFG_3

P24

CFG_4

C25

CFG_5

N24

CFG_6

M24

CFG_7

E21

CFG_8

C23

CFG_9

C24

CFG_10

N21

CFG_11

P21

CFG_12

T21

CFG_13

R20

CFG_14

M20

CFG_15

L21

CFG_16

H21

CFG_17

P29

CFG_18

R28

CFG_19

T28

CFG_20

R29

PM_SYNC#

B7

PM_DPRSTP#

N33

PM_EXT_TS#_0

P32

PM_EXT_TS#_1

AT40

PWROK

AT11

RSTIN#

T20

THERMTRIP#

R32

DPRSLPVR

BG48

NC_1

BF48

NC_2

BD48

NC_3

BC48

NC_4

BH47

NC_5

BG47

NC_6

BE47

NC_7

BH46

NC_8

BF46

NC_9

BG45

NC_10

BH44

NC_11

BH43

NC_12

BH6

NC_13

BH5

NC_14

BG4

NC_15

BH3

NC_16

BF3

NC_17

BH2

NC_18

BG2

NC_19

BE2

NC_20

BG1

NC_21

BF1

NC_22

BD1

NC_23

BC1

NC_24

F1

NC_25

A47

NC_26

CANTI GA ES_FCBGA1329

Compal Secret Data

Deciphered Date

2

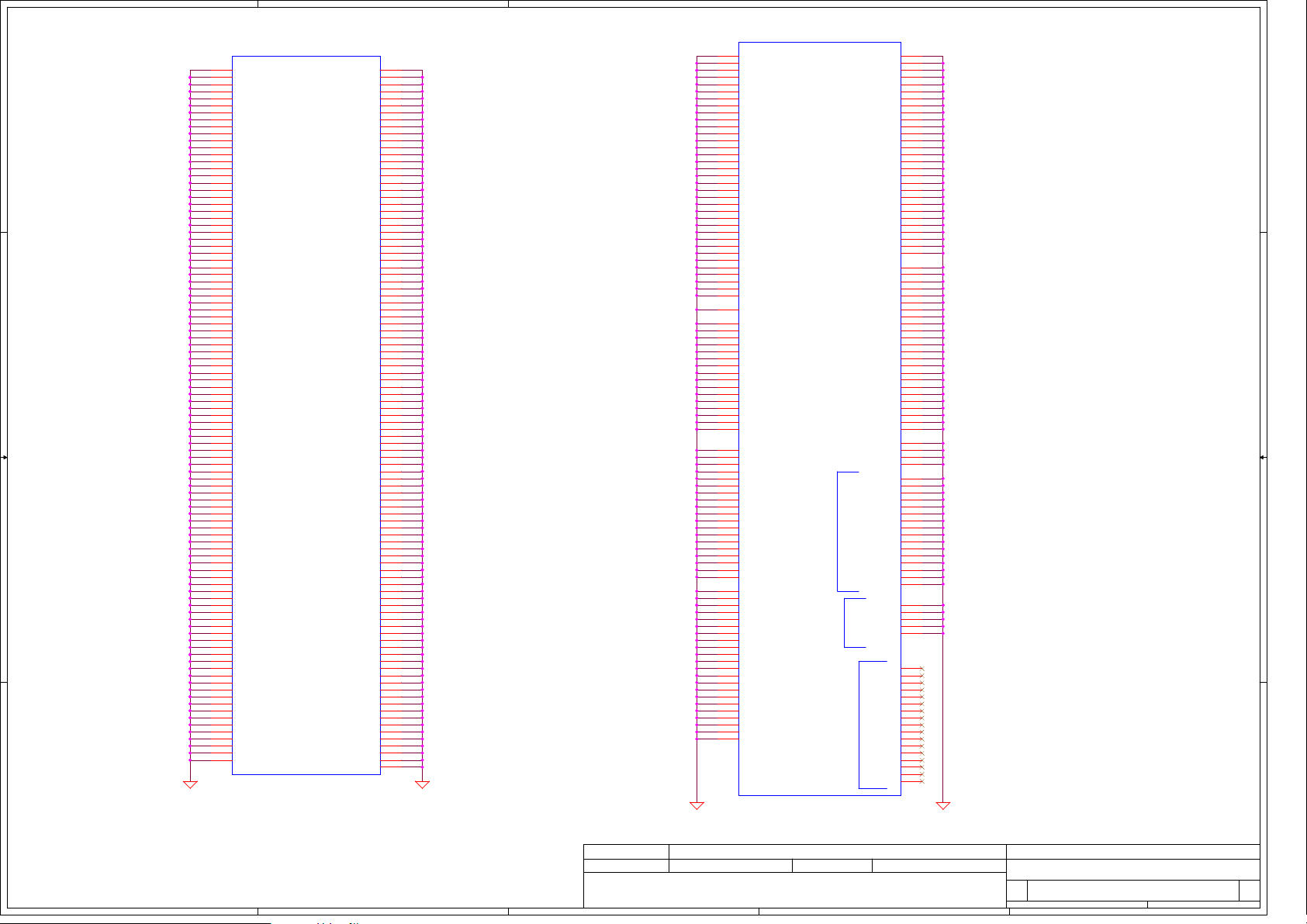

M_CLK_DD R0

AP24

SA_CK_0

SA_CK_1

SB_CK_0

SB_CK_1

SA_CK#_0

SA_CK#_1

SB_CK#_0

SB_CK#_1

SA_CKE_0

SA_CKE_1

SB_CKE_0

SB_CKE_1

SA_CS#_0

SA_CS#_1

SB_CS#_0

RSVD CFG PM NC

DDR CLK/ CONTROL/ COMPENSATIONHDA

CLKDMIGRAPHICS VIDMEMISC

SB_CS#_1

SA_ODT_0

SA_ODT_1

SB_ODT_O

SB_ODT_1

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_PWROK

SM_DRAMRST#

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

CL_PWROK

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

ICH_SYNC#

HDA_BCLK

HDA_RST#

HDA_SDO

HDA_SYNC

2

SM_VREF

SM_REXT

PEG_CLK

CL_CLK

CL_DATA

CL_RST#

CL_VREF

CLKREQ#

TSATN#

HDA_SDI

M_CLK_DD R1

AT21

M_CLK_DD R2

AV24

M_CLK_DD R3

AU20

M_CLK_DDR#0

AR24

M_CLK_DDR#1

AR21

M_CLK_DDR#2

AU24

M_CLK_DDR#3

AV20

DDR_CKE 0_DIMMA

BC28

DDR_CKE 1_DIMMA

AY28

DDR_CKE 2_DIMMB

AY36

DDR_CKE 3_DIMMB

BB36

DDR_C S0_DIMMA#

BA17

DDR_C S1_DIMMA#

AY16

DDR_C S2_DIMMB#

AV16

DDR_C S3_DIMMB#

AR13

M_ODT0

BD17

M_ODT1

AY17

M_ODT2

BF15

M_ODT3

AY13

SMRCOMP

BG22

SMRCOMP#

BH21

+SMRCOMP_VOH

BF28

+SMRCOMP_VOL

BH28

+V_DD R_MCH_REF

AV42

AR36

SM_REXT

BF17

TP_SM_DRAMRST#

BC36

MCH_ DREFCLK

B38

MCH_ DREFCLK#

A38

DREF_ SSCLK

E41

DREF_ SSCLK#

F41

CLK_MCH_3GPLL

F43

CLK_MCH_3GPLL#

E43

DMI_ITX_MRX_N0

AE41

DMI_ITX_MRX_N1

AE37

DMI_ITX_MRX_N2

AE47

DMI_ITX_MRX_N3

AH39

DMI_ITX_MRX_P0

AE40

DMI_ITX_MRX_P1

AE38

DMI_ITX_MRX_P2

AE48

DMI_ITX_MRX_P3

AH40

DMI_MTX_IRX_N0

AE35

DMI_MTX_IRX_N1

AE43

DMI_MTX_IRX_N2

AE46

DMI_MTX_IRX_N3

AH42

DMI_MTX_IRX_P0

AD35

DMI_MTX_IRX_P1

AE44

DMI_MTX_IRX_P2

AF46

DMI_MTX_IRX_P3

AH43

B33

B32

G33

F33

E33

C34

AH37

AH36

AN36

AJ35

AH34

N28

M28

G36

E36

K36

H36

B12

B28

B30

B29

C29

A28

T30

T31

T32

T33

T34

T35

CL_CLK0

CL_DATA0

M_PWROK

CL_RST#

+CL_VREF

CLK_3GPLLREQ#

MCH _ICH_SYNC #

TSATN#

ADC_A CZ_SDIN0_GMC H

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

M_CLK_DDR0 <16>

M_CLK_DDR1 <16>

M_CLK_DDR2 <17>

M_CLK_DDR3 <17>

M_CLK_DDR#0 <16>

M_CLK_DDR#1 <16>

M_CLK_DDR#2 <17>

M_CLK_DDR#3 <17>

DDR_CKE 0_DIMMA <16>

DDR_CKE 1_DIMMA <16>

DDR_CKE 2_DIMMB <17>

DDR_CKE 3_DIMMB <17>

DDR_CS0_D IMMA# <16>

DDR_CS1_D IMMA# <16>

DDR_CS2_D IMMB# <17>

DDR_CS3_D IMMB# <17>

M_ODT0 <16>

M_ODT1 <16>

M_ODT2 <17>

M_ODT3 <17>

R328 80.6_0402_1%

1 2

R329 80.6_0402_1%

1 2

+V_DD R_MCH_REF

R1040 499_0402_1%

1 2

T29

MCH_ DREFCLK <6>

MCH_ DREFCLK# <6>

DREF_ SSCLK <6>

DREF_ SSCLK# <6>

CLK_MCH_3GPLL <6>

CLK_MCH_3GPLL# <6>

DMI_ITX_MRX_N0 <23>

DMI_ITX_MRX_N1 <23>

DMI_ITX_MRX_N2 <23>

DMI_ITX_MRX_N3 <23>

DMI_ITX_MRX_P0 <23>

DMI_ITX_MRX_P1 <23>

DMI_ITX_MRX_P2 <23>

DMI_ITX_MRX_P3 <23>

DMI_MTX_IRX_N0 <23>

DMI_MTX_IRX_N1 <23>

DMI_MTX_IRX_N2 <23>

DMI_MTX_IRX_N3 <23>

DMI_MTX_IRX_P0 <23>

DMI_MTX_IRX_P1 <23>

DMI_MTX_IRX_P2 <23>

DMI_MTX_IRX_P3 <23>

MCH_ DREFCLK

MCH_ DREFCLK#

DREF_ SSCLK

DREF_ SSCLK#

CL_CLK0 <23>

CL_DATA0 <23>

M_PWROK <23>

CL_RST# <23>

T36

0.1U_0402_16V7K~D

T48

GMCH_ HDMICLK <20>

GMCH_HDM IDAT <20>

CLK_3GPLLREQ# <6>

MCH _ICH_SYNC# <23>

R521 56_0402_5%

GMCH_H DA_BITCLK <22>

GMCH_HDA _RST# <22>

1 2

R98 33_0402_5%~D1@

GMCH_H DA_SDOUT <22>

GMCH_ HDA_SYNC <22>

Compal Electronics, Inc.

Cantiga(1/6)-AGTL/DMI/DDR

LA-5162P

1

RG156

@

RG158

@

RG160

@

RG161

@

1

C181

2

12

1

+1.8V

1 2

0_0402_5%

1 2

0_0402_5%

1 2

0_0402_5%

1 2

0_0402_5%

+VCCP

12

R100

1K_0402_1%

0.35V

12

R99

511_0402_1%

ADC_G MCH_SDIN2 <22>

10 60Monday , April 20, 2009

0.2

5

4

3

2

1

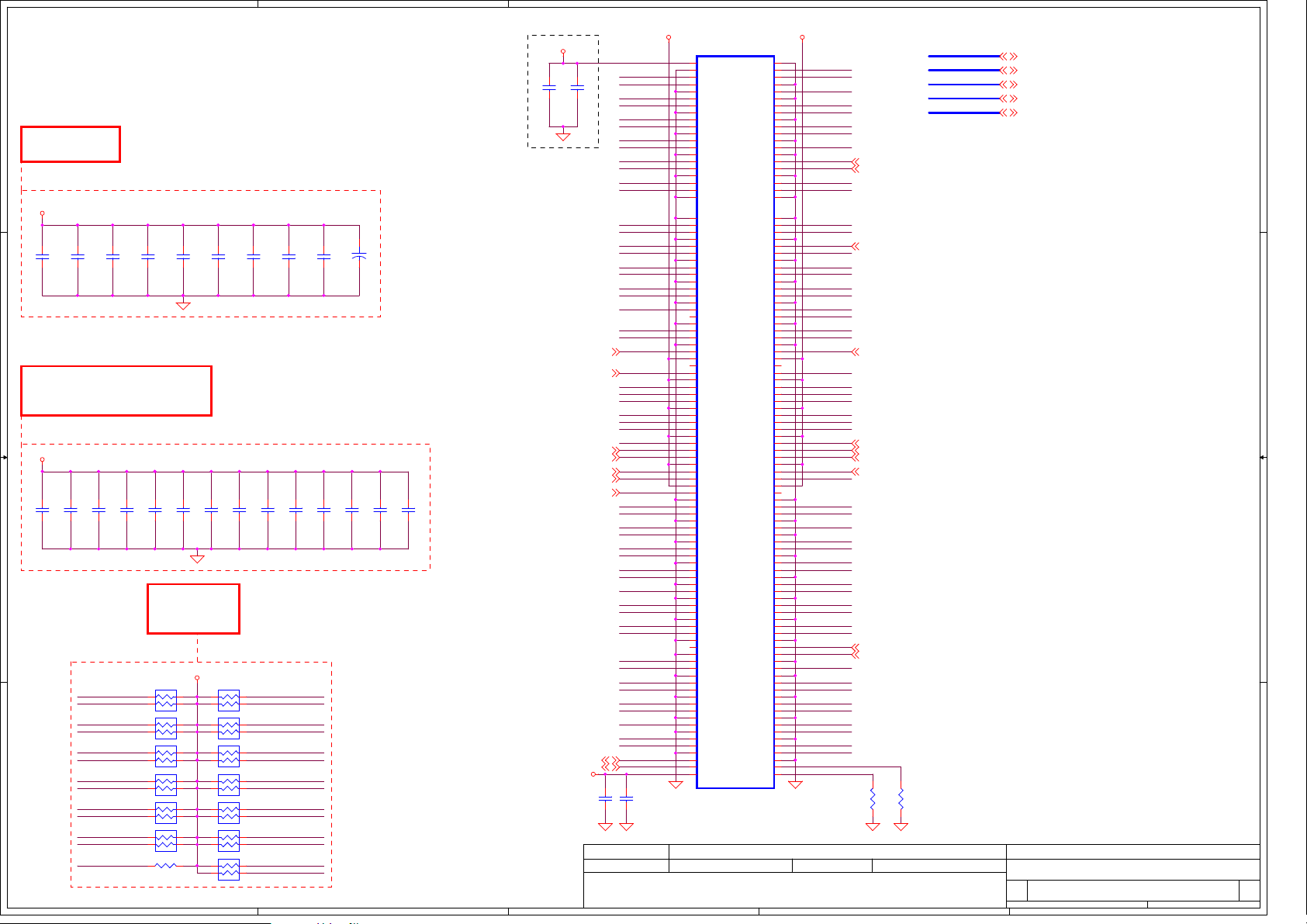

D D

U4D

DDR_A _D0

DDR_A _D1

DDR_A _D2

DDR_A _D3

DDR_A _D4

DDR_A _D5

DDR_A _D6

DDR_A _D7

DDR_A _D8

DDR_A _D9

DDR_A _D10

DDR_A _D11

DDR_A _D12

DDR_A _D13

DDR_A _D14

DDR_A _D15

DDR_A _D16

DDR_A _D17

DDR_A _D18

DDR_A _D19

DDR_A _D20

DDR_A _D21

DDR_A _D22

DDR_A _D23

DDR_A _D24

DDR_A _D25

DDR_A _D26

DDR_A _D27

C C

B B

DDR_A _D28

DDR_A _D29

DDR_A _D30

DDR_A _D31

DDR_A _D32

DDR_A _D33

DDR_A _D34

DDR_A _D35

DDR_A _D36

DDR_A _D37

DDR_A _D38

DDR_A _D39

DDR_A _D40

DDR_A _D41

DDR_A _D42

DDR_A _D43

DDR_A _D44

DDR_A _D45

DDR_A _D46

DDR_A _D47

DDR_A _D48

DDR_A _D49

DDR_A _D50

DDR_A _D51

DDR_A _D52

DDR_A _D53

DDR_A _D54

DDR_A _D55

DDR_A _D56

DDR_A _D57

DDR_A _D58

DDR_A _D59

DDR_A _D60

DDR_A _D61

DDR_A _D62

DDR_A _D63

AJ38

SA_DQ_0

AJ41

SA_DQ_1

AN38

SA_DQ_2

AM38

SA_DQ_3

AJ36

SA_DQ_4

AJ40

SA_DQ_5

AM44

SA_DQ_6

AM42

SA_DQ_7

AN43

SA_DQ_8

AN44

SA_DQ_9

AU40

SA_DQ_10

AT38

SA_DQ_11

AN41

SA_DQ_12

AN39

SA_DQ_13

AU44

SA_DQ_14

AU42

SA_DQ_15

AV39

SA_DQ_16

AY44

SA_DQ_17

BA40

SA_DQ_18

BD43

SA_DQ_19

AV41

SA_DQ_20

AY43

SA_DQ_21

BB41

SA_DQ_22

BC40

SA_DQ_23

AY37

SA_DQ_24

BD38

SA_DQ_25

AV37

SA_DQ_26

AT36

SA_DQ_27

AY38

SA_DQ_28

BB38

SA_DQ_29

AV36

SA_DQ_30

AW36

SA_DQ_31

BD13

SA_DQ_32

AU11

SA_DQ_33

BC11

SA_DQ_34

BA12

SA_DQ_35

AU13

SA_DQ_36

AV13

SA_DQ_37

BD12

SA_DQ_38

BC12

SA_DQ_39

BB9

SA_DQ_40

BA9

SA_DQ_41

AU10

SA_DQ_42

AV9

SA_DQ_43

BA11

SA_DQ_44

BD9

SA_DQ_45

AY8

SA_DQ_46

BA6

SA_DQ_47

AV5

SA_DQ_48

AV7

SA_DQ_49

AT9

SA_DQ_50

AN8

SA_DQ_51

AU5

SA_DQ_52

AU6

SA_DQ_53

AT5

SA_DQ_54

AN10

SA_DQ_55

AM11

SA_DQ_56

AM5

SA_DQ_57

AJ9

SA_DQ_58

AJ8

SA_DQ_59

AN12

SA_DQ_60

AM13

SA_DQ_61

AJ11

SA_DQ_62

AJ12

SA_DQ_63

CANTI GA ES_FCBGA1329

DDR_A_BS #0

BD21

SA_BS_0

SA_BS_1

SA_BS_2

SA_RAS#

SA_CAS#

SA_WE#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

DDR SYSTEM MEMORY A

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

BG18

AT25

BB20

BD20

AY20

AM37

AT41

AY41

AU39

BB12

AY6

AT7

AJ5

AJ44

AT44

BA43

BC37

AW12

BC8

AU8

AM7

AJ43

AT43

BA44

BD37

AY12

BD8

AU9

AM8

BA21

BC24

BG24

BH24

BG25

BA24

BD24

BG27

BF25

AW24

BC21

BG26

BH26

BH17

AY25

DDR_A_BS #1

DDR_A_BS #2

DDR_A _RAS#

DDR_A _CAS#

DDR_A_W E#

DDR_A_DM 0

DDR_A_DM 1

DDR_A_DM 2

DDR_A_DM 3

DDR_A_DM 4

DDR_A_DM 5

DDR_A_DM 6

DDR_A_DM 7

DDR_A _DQS0

DDR_A _DQS1

DDR_A _DQS2

DDR_A _DQS3

DDR_A _DQS4

DDR_A _DQS5

DDR_A _DQS6

DDR_A _DQS7

DDR_A _DQS#0

DDR_A _DQS#1

DDR_A _DQS#2

DDR_A _DQS#3

DDR_A _DQS#4

DDR_A _DQS#5

DDR_A _DQS#6

DDR_A _DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_BS #0 <16>

DDR_A_BS #1 <16>

DDR_A_BS #2 <16>

DDR_A _RAS# <16>

DDR_A _CAS# <16>

DDR_A_W E# <16>

DDR_A _DM[0..7] <16>

DDR_A _DQS[0..7 ] <16>

DDR_A _DQS#[0.. 7] <16>

DDR_A _MA[0..14] <16>

DDR_ B_D[0..63 ]<17>DDR_ A_D[0..63 ]<16>

DDR_B _D0

DDR_B _D1

DDR_B _D2

DDR_B _D3

DDR_B _D4

DDR_B _D5

DDR_B _D6

DDR_B _D7

DDR_B _D8

DDR_B _D9

DDR_B _D10

DDR_B _D11

DDR_B _D12

DDR_B _D13

DDR_B _D14

DDR_B _D15

DDR_B _D16

DDR_B _D17

DDR_B _D18

DDR_B _D19

DDR_B _D20

DDR_B _D21

DDR_B _D22

DDR_B _D23

DDR_B _D24

DDR_B _D25

DDR_B _D26

DDR_B _D27

DDR_B _D28

DDR_B _D29

DDR_B _D30

DDR_B _D31

DDR_B _D32

DDR_B _D33

DDR_B _D34

DDR_B _D35

DDR_B _D36

DDR_B _D37

DDR_B _D38

DDR_B _D39

DDR_B _D40

DDR_B _D41

DDR_B _D42

DDR_B _D43

DDR_B _D44

DDR_B _D45

DDR_B _D46

DDR_B _D47

DDR_B _D48

DDR_B _D49

DDR_B _D50

DDR_B _D51

DDR_B _D52

DDR_B _D53

DDR_B _D54

DDR_B _D55

DDR_B _D56

DDR_B _D57

DDR_B _D58

DDR_B _D59

DDR_B _D60

DDR_B _D61

DDR_B _D62

DDR_B _D63

U4E

AK47

SB_DQ_0

AH46

SB_DQ_1

AP47

SB_DQ_2

AP46

SB_DQ_3

AJ46

SB_DQ_4

AJ48

SB_DQ_5

AM48

SB_DQ_6

AP48

SB_DQ_7

AU47

SB_DQ_8

AU46

SB_DQ_9

BA48

SB_DQ_10

AY48

SB_DQ_11

AT47

SB_DQ_12

AR47

SB_DQ_13

BA47

SB_DQ_14

BC47

SB_DQ_15

BC46

SB_DQ_16

BC44

SB_DQ_17

BG43

SB_DQ_18

BF43

SB_DQ_19

BE45

SB_DQ_20

BC41

SB_DQ_21

BF40

SB_DQ_22

BF41

SB_DQ_23

BG38

SB_DQ_24

BF38

SB_DQ_25

BH35

SB_DQ_26

BG35

SB_DQ_27

BH40

SB_DQ_28

BG39

SB_DQ_29

BG34

SB_DQ_30

BH34

SB_DQ_31

BH14

SB_DQ_32

BG12

SB_DQ_33

BH11

SB_DQ_34

BG8

SB_DQ_35

BH12

SB_DQ_36

BF11

SB_DQ_37

BF8

SB_DQ_38

BG7

SB_DQ_39

BC5

SB_DQ_40

BC6

SB_DQ_41

AY3

SB_DQ_42

AY1

SB_DQ_43

BF6

SB_DQ_44

BF5

SB_DQ_45

BA1

SB_DQ_46

BD3

SB_DQ_47

AV2

SB_DQ_48

AU3

SB_DQ_49

AR3

SB_DQ_50

AN2

SB_DQ_51

AY2

SB_DQ_52

AV1

SB_DQ_53

AP3

SB_DQ_54

AR1

SB_DQ_55

AL1

SB_DQ_56

AL2

SB_DQ_57

AJ1

SB_DQ_58

AH1

SB_DQ_59

AM2

SB_DQ_60

AM3

SB_DQ_61

AH3

SB_DQ_62

AJ3

SB_DQ_63

CANTI GA ES_FCBGA1329

DDR_B_BS#0

BC16

SB_BS_0

SB_BS_1

SB_BS_2

SB_RAS#

SB_CAS#

SB_WE#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

DDR SYSTEM MEMORY B

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

BB17

BB33

AU17

BG16

BF14

AM47

AY47

BD40

BF35

BG11

BA3

AP1

AK2

AL47

AV48

BG41

BG37

BH9

BB2

AU1

AN6

AL46

AV47

BH41

BH37

BG9

BC2

AT2

AN5

AV17

BA25

BC25

AU25

AW25

BB28

AU28

AW28

AT33

BD33

BB16

AW33

AY33

BH15

AU33

DDR_B_BS #1

DDR_B_BS #2

DDR_B _RAS#

DDR_B _CAS#

DDR_B_W E#

DDR_B_DM 0

DDR_B_DM 1

DDR_B_DM 2

DDR_B_DM 3

DDR_B_DM 4

DDR_B_DM 5

DDR_B_DM 6

DDR_B_DM 7

DDR_B _DQS0

DDR_B _DQS1

DDR_B _DQS2

DDR_B _DQS3

DDR_B _DQS4

DDR_B _DQS5

DDR_B _DQS6

DDR_B _DQS7

DDR_B _DQS#0

DDR_B _DQS#1

DDR_B _DQS#2

DDR_B _DQS#3

DDR_B _DQS#4

DDR_B _DQS#5

DDR_B _DQS#6

DDR_B _DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_BS #0 <17>

DDR_B_BS #1 <17>

DDR_B_BS #2 <17>

DDR_B _RAS# <17>

DDR_B _CAS# <17>

DDR_B _WE# <17>

DDR_B _DM[0..7] <17>

DDR_ B_DQS[0.. 7] <17>

DDR_B _DQS#[0.. 7] <17>

DDR_B _MA[0..14] <17>

CPN:SA00002JT3L(GM45) for Discrete and UMA

A A

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2009/01/05 2009/01/05

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

2

Date: Sheet of

Compal Electronics, Inc.

Cantiga(2/6)-DDR2 A/B CH

LA-5162P

1

11 60Monday , April 20, 2009

0.2

5

+3VS

R57

1@

GMCH _EDID_CLK_ LCD

1 2

2.2K_0402_5%~D

R62

1@

GMCH _EDID_DAT_LC D

D D

C C

B B

1 2

2.2K_0402_5%~D

150_0402_1%

12

1@

R75

INVT_PWM< 19,30>

+3VS

GMCH_EN BKL

R81 10K_0402_5%~D1@

R80 10K_0402_5%~D1@

GMCH _EDID_CLK_ LCD

GMCH _EDID_DAT_LC D

GMCH _LVDDEN

GMCH_LV DSACGMCH_LV DSAC+

GMCH_LVDSA0GMCH_LVDSA1GMCH_LVDSA2-

GMCH_LVDSA0+

GMCH_LVDSA1+

GMCH_LVDSA2+

GMCH_ENBKL<19>

GMCH _EDID_CLK_L CD<19>

GMCH_ EDID_DAT_LCD<19>

GMCH_ LVDDEN<19>

GMCH_LVDS AC-<19>

GMCH_LVDSAC +<19>

GMCH_LVDSA0-<19>

GMCH_LVDSA1-<19>

GMCH_LVDSA2-<19>

GMCH_LVDSA0+<19>

GMCH_LVDSA1+<19>

GMCH_LVDSA2+<19>

CRT_B

CRT_G

CRT_R

150_0402_1%

150_0402_1%

12

12

1@

1@

R74

R76

@

0_0402_5%

1 2

R119

1@

1 2

100K_0402_5%~D

1 2

1 2

R94 2.4K_0402_1%~D1@

T38

T46

R37 75_0402_5%~D

R63 75_0402_5%~D

R50 75_0402_5%~D

CRT_B<19>

CRT_G<19>

CRT_R<19>

3VDD CCL<19>

3VDD CDA<19>

CRT _HSYNC<19>

R334 1K_0402_1%1@

CRT _VSYNC<19>

R314

1 2

1 2

1 2

1 2

INVT_PW M_GMCH

GMCH_LVDSA3-

GMCH_LVDSA3+

CRT_B

CRT_G

CRT_R

3VDD CCL

3VDD CDA

CRT _HSYNC

12

CTRL_CLK

CTRL_DATA

CRT _VSYNC

4

U4C

L32

L_BKLT_CT RL

G32

L_BKLT_EN

M32

L_CTRL_C LK

M33

L_CTRL_D ATA

K33

L_DDC_CL K

J33

L_DDC_DATA

M29

L_VDD_EN

C44

LVDS_IBG

B43

LVDS_VBG

E37

LVDS_VREFH

E38

LVDS_VREFL

C41

LVDSA_CLK#

C40

LVDSA_CLK

B37

LVDSB_CLK#

A37

LVDSB_CLK

H47

LVDSA_DATA#_0

E46

LVDSA_DATA#_1

G40

LVDSA_DATA#_2

A40

LVDSA_DATA#_3

H48

LVDSA_DATA_0

D45

LVDSA_DATA_1

F40

LVDSA_DATA_2

B40

LVDSA_DATA_3

A41

LVDSB_DATA#_0

H38

LVDSB_DATA#_1

G37

LVDSB_DATA#_2

J37

LVDSB_DATA#_3

B42

LVDSB_DATA_0

G38

LVDSB_DATA_1

F37

LVDSB_DATA_2

K37

LVDSB_DATA_3

F25

TVA_DAC

H25

TVB_DAC

K25

TVC_DAC

H24

TV_RTN

C31

TV_DCONSEL_0

E32

TV_DCONSEL_1

E28

CRT_BLUE

G28

CRT_GREEN

J28

CRT_RED

G29

CRT_IRTN

H32

CRT_DDC_ CLK

J32

CRT_DDC_ DATA

J29

CRT_HSYNC

E29

CRT_TVO_IREF

L29

CRT_VSYNC

CANTIGA ES_FCBGA1329

3

R95 wi thin 500 mils from

pin T 37,T36

T37

PEG_COMPI

T36

PEG_COMPO

H44

PEG_RX#_0

J46

PEG_RX#_1

L44

PEG_RX#_2

L40

PEG_RX#_3

N41

PEG_RX#_4

P48

PEG_RX#_5

N44

PEG_RX#_6

T43

PEG_RX#_7

U43

PEG_RX#_8

Y43

PEG_RX#_9

Y48

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PEG_TX#_11

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

Y36

AA43

AD37

AC47

AD39

H43

J44

L43

L41

N40

P47

N43

T42

U42

Y42

W47

Y37

AA42

AD36

AC48

AD40

J41

M46

M47

M40

M42

R48

N38

T40

U37

U40

Y40

AA46

AA37

AA40

AD43

AC46

J42

L46

M48

M39

M43

R47

N37

T39

U36

U39

Y39

Y46

AA36

AA39

AD42

AD46

LVDS TV VGA

PCI-EXPRESS GRAPHICS

1 2

R95 49.9_0402_1%

CG568 0.1U _0402_16V7K~D2@

CG537 0.1U _0402_16V7K~D2@

CG538 0.1U _0402_16V7K~D2@

CG539 0.1U _0402_16V7K~D2@

CG540 0.1U _0402_16V7K~D2@

CG541 0.1U _0402_16V7K~D2@

CG542 0.1U _0402_16V7K~D2@

CG543 0.1U _0402_16V7K~D2@

CG544 0.1U _0402_16V7K~D2@

CG545 0.1U _0402_16V7K~D2@

CG546 0.1U _0402_16V7K~D2@

CG547 0.1U _0402_16V7K~D2@

CG548 0.1U _0402_16V7K~D2@

CG549 0.1U _0402_16V7K~D2@

CG550 0.1U _0402_16V7K~D2@

CG551 0.1U _0402_16V7K~D2@

CG552 0.1U _0402_16V7K~D2@

CG553 0.1U _0402_16V7K~D2@

CG554 0.1U _0402_16V7K~D2@

CG555 0.1U _0402_16V7K~D2@

CG556 0.1U _0402_16V7K~D2@

CG557 0.1U _0402_16V7K~D2@

CG558 0.1U _0402_16V7K~D2@

CG559 0.1U _0402_16V7K~D2@

CG560 0.1U _0402_16V7K~D2@

CG561 0.1U _0402_16V7K~D2@

CG562 0.1U _0402_16V7K~D2@

CG563 0.1U _0402_16V7K~D2@

CG564 0.1U _0402_16V7K~D2@

CG565 0.1U _0402_16V7K~D2@

CG566 0.1U _0402_16V7K~D2@

CG567 0.1U _0402_16V7K~D2@

1 2

R93 0_0402_5%1@

PEG_NRX_G TX_N[0..15] <34>

PEG_NRX_G TX_P[0..15] <34>

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

PEG_NRX_GTX_N0

PEG_NRX_GTX_N1

PEG_NRX_GTX_N2

PEG_NRX_GTX_N3

PEG_NRX_GTX_N4

PEG_NRX_GTX_N5

PEG_NRX_GTX_N6

PEG_NRX_GTX_N7

PEG_NRX_GTX_N8

PEG_NRX_GTX_N9

PEG_NRX_GTX_N10

PEG_NRX_GTX_N11

PEG_NRX_GTX_N12

PEG_NRX_GTX_N13

PEG_NRX_GTX_N14

PEG_NRX_GTX_N15

PEG_NRX_GTX_P0

PEG_NRX_GTX_P1

PEG_NRX_GTX_P2

PEG_NRX_GTX_P3

PEG_NRX_GTX_P4

PEG_NRX_GTX_P5

PEG_NRX_GTX_P6

PEG_NRX_GTX_P7

PEG_NRX_GTX_P8

PEG_NRX_GTX_P9

PEG_NRX_GTX_P10

PEG_NRX_GTX_P11

PEG_NRX_GTX_P12

PEG_NRX_GTX_P13

PEG_NRX_GTX_P14

PEG_NRX_GTX_P15

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5 PEG_NTX_C_GRX_N5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4