Page 1

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

TFT LCD Approval Specification

MODEL NO.: V260B1-P12

Customer:

Approved by:

Note:

TV Head Division

Approved By

Chao-Chun Chung

Reviewed By

QA Dept. Product Development Div.

Hsin-Nan Chen WT Lin

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Prepared By

LCD TV Marketing and Product Management Div.

CY Chang Chi-Yao Lo

1

Version 2.0

www.panelook.com

Page 2

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

- CONTENTS -

REVISION HISTORY

-------------------------------------------------------

1. GENERAL DESCRIPTION

1.1 OVERVIEW

1.2 CHARACTERISTICS

1.3 MECHANICAL SPECIFICATIONS

-------------------------------------------------------

2. ABSOLUTE MAXIMUM RATINGS

2.1 ABSOLUTE RATINGS OF ENVIRONMENT (BASED ON CMO MODULE V260B1-L12)

2.2 ABSOLUTE RATINGS OF ENVIRONMENT (OPEN CELL)

2.3 ELECTRICAL ABSOLUTE RATINGS (OPEN CELL)

-------------------------------------------------------

3. ELECTRICAL CHARACTERISTICS

3.1 TFT LCD OPEN CELL

-------------------------------------------------------

4. BLOCK DIAGRAM

4.1 TFT LCD OPEN CELL

-------------------------------------------------------

5. INPUT TERMINAL PIN ASSIGNMENT

5.1 TFT LCD MODULE

5.2 BLOCK DIAGRAM OF INTERFACE

-------------------------------------------------------

3

4

5

7

8

9

5.3 LVDS INTERFACE

5.4 COLOR DATA INPUT ASSIGNMENT

6. INTERFACE TIMING

6.1 INPUT SIGNAL TIMING SPECIFICATIONS

6.2 POWER ON/OFF SEQUENCE

-------------------------------------------------------

14

7. OPTICAL CHARACTERISTICS

7.1 TEST CONDITIONS

7.2 OPTICAL SPECIFICATIONS

-------------------------------------------------------

17

8. PRECAUTIONS

8.1 ASSEMBLY AND HANDLING PRECAUTIONS

8.2 SAFETY PRECAUTIONS

9. PACKING

9.1 PACKING SPECIFICATIONS

9.2 PACKING METHOD

------------------------------------------------------- 22

------------------------------------------------------- 21

10. REGULATORY STANDARD

10.1 SAFETY

-------------------------------------------------------- 24

11. DEFINITION OF LABELS

11.1 OPEN CELL LABEL

11.2 CARTON LABEL

------------------------------------------------------- 25

12. MECHANICAL DRAWING ------------------------------------------------------- 26

2

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 3

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

REVISION HISTORY

Version Date

Ver 2.0 Dec, 16, 2009 All All Approval Specification was first issued.

Page

(New)

Section Description

3

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 4

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

1. GENERAL DESCRIPTION

1.1 OVERVIEW

V260B1- P12 is a 26-inch TFT LCD cell with driver ICs and a 1-ch LVDS interface. The product supports

1366 x 768 WXGA mode and can display true 16.2M colors (6-bits+FRC colors).The backlight unit is not built

in.

1.2 CHARACTERISTICS

CHARACTERISTICS ITEMS SPECIFICATIONS

Screen Diagonal [in] 26.0

Pixels [lines]

Active Area [mm]

Sub -Pixel Pitch [mm]

Pixel Arrangement RGB vertical stripe

Weight [g] TYP. 850

Physical Size [mm] Please refer to 2D Drawing

Display Mode TN, Normally White

Contrast Ratio 800:1 Typ.

Glass thickness (Array/CF) [mm] 0.7 / 0.7

Viewing Angle (CR>20) +80/-80(H),+80/-70(V) Typ.

Color Chromaticity R=(0.650, 0.328)

Cell Transparency [и]

Polarizer (CF side) Anti-glare coating,

Polarizer (TFT side) 587.4(H) x 335.2(w),

1366

768

575.769

0.1405(H)

(Typical value measured at CMO’s module)

(Typical value measured at CMO’s module)

G=(0.274,0.583)

B=(0.150,0.094)

W=(0.314,0.331)

*Please refer to “color chromaticity” on p.16

6.2%Typ.

(Typical value measured at CMO’s module)

587.4(H) x 335.2(w). Hardness: 3H

Hardness: 3H

323.712

0.4215(V)

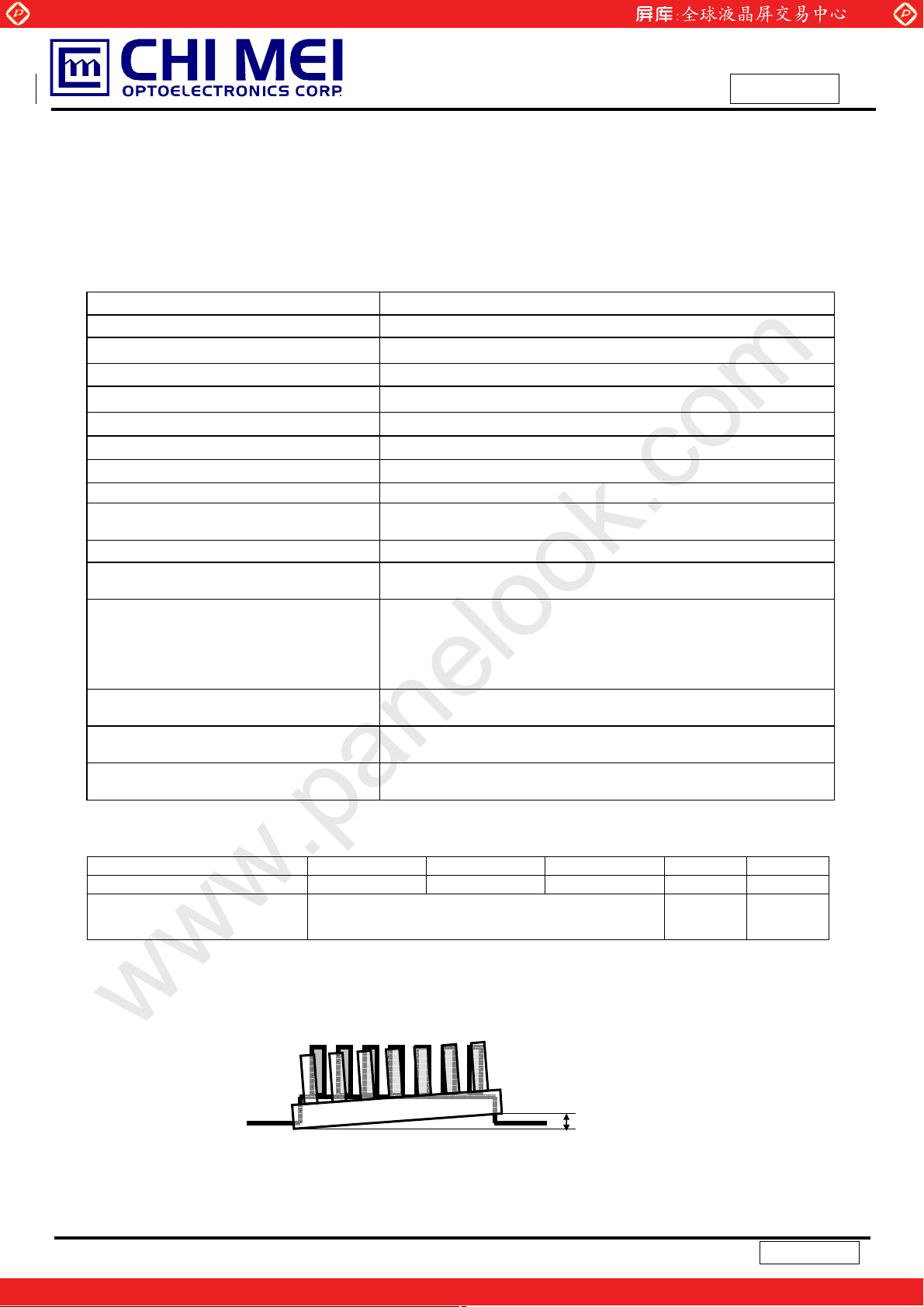

1.3 MECHANICAL SPECIFICATIONS

Item Min. Typ. Max. Unit Note

Weight 850 g

I/F connector mounting

position

Note (1) Please refer to the attached drawings for more information of front and back outline dimensions.

(2) Connector mounting position

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

The mounting inclination of the connector makes

the screen center within ±0.5mm as the horizontal.

+/- 0.5mm

4

(2)

Version 2.0

www.panelook.com

Page 5

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

2. ABSOLUTE MAXIMUM RATINGS

2.1 ABSOLUTE RATINGS OF ENVIRONMENT (BASED ON CMO MODULE V260B1-L12)

Item Symbol

Storage Temperature TST -20 +60 ºC (1), (3)

Operating Ambient Temperature TOP 0 50 ºC (1), (2), (3)

Altitude Operating A OP 0 5000 M (3)

Altitude Storage A ST 0 12000 M (3)

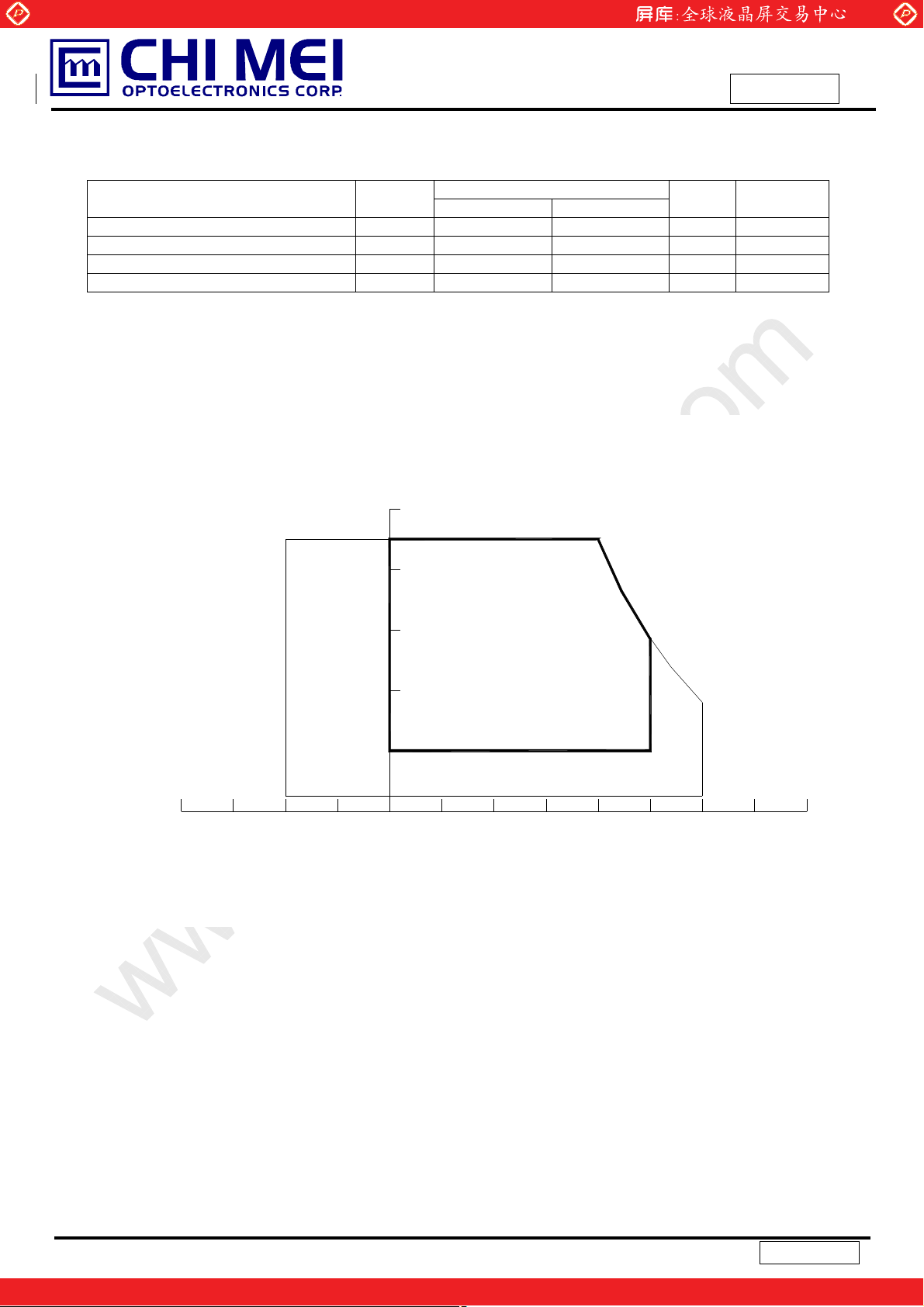

Note (1) Temperature and relative humidity range is shown in the figure below.

Min. Max.

Value

Unit Note

(a) 90 %RH Max. (Ta

(b) Wet-bulb temperature should be 39 ºC Max. (Ta > 40 ºC).

(c) No condensation.

Љ

40 ºC).

Relative Humidity (%RH)

100

90

80

60

Operating Range

40

20

10

Storage Range

Note (2) The maximum operating temperature is based on the test condition that the surface temperature of

display area is less than or equal to 65 ºC with LCD module alone in a temperature controlled

chamber. Thermal management should be considered in your product design to prevent the surface

temperature of display area from being over 65 ºC. The range of operating temperature may

degrade in case of improper thermal management in your product design.

Note (3) The rating of environment is base on LCD module. Leave LCD cell alone, this environment condition can’t

be guaranteed. Except LCD cell, the customer has to consider the ability of other parts of LCD module

and LCD module process.

Temperature (ºC)

5

Version 2.0

80 60 -20 40 0 20 -40

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

www.panelook.com

Page 6

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

2.2 ABSOLUTE RATINGS OF ENVIRONMENT (OPEN CELL)

Storage Condition: With shipping package.

Storage temperature range: 25±5

Storage humidity range: 50±10%RH

Shelf life: a month

2.3 ELECTRICAL ABSOLUTE RATINGS

2.3.1 TFT LCD MODULE

Item Symbol

Power Supply Voltage Vcc -0.3 13.0 V

Input Signal Voltage VIN -0.3 3.6 V

Note (1) Permanent damage to the device may occur if maximum values are exceeded. Functional operation

should be restricted to the conditions described under normal operating conditions.

Note (2) No moisture condensation or freezing.

Note (3) The control signals includes Backlight On/Off Control, Internal PWM Control and External PWM

Control.

к

Value

Min. Max.

Unit Note

(1)

6

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 7

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

Approval

3. ELECTRICAL CHARACTERISTICS

3.1 TFT LCD OPEN CELL

Parameter Symbol

Ta = 25 ± 2 ºC

Value

Min. Typ. Max.

Unit Note

Power Supply Voltage VCC 11.4 12.0 12.6 V (1)

Power Supply Ripple Voltage VRP

Rush Current I

RUSH

White

Power Supply Current

Black

ICC

Vertical Stripe

LVDS

Interface

CMOS

interface

Differential Input High

Threshold Voltage

Differential Input Low

Threshold Voltage

Common Input Voltage V

Terminating Resistor R

Input High Threshold Voltage VIH 2.7

Input Low Threshold Voltage V

V

V

LVT H

LVTL

LVC

T

IL

Ё

Ё

Ё

Ё

+100

Ё

1.125 1.25 1.375 V

Ё

0

Ё

Ё

300 mV

3.0 A (2)

0.2 0.25 A

0.5 0.55 A

0.4 0.45 A

Ё

Ё

100

Ё

Ё

Ё

mV

-100 mV

Ё

ohm

3.3 V

0.7 V

(3)

Ё

Note (1) The module should be always operated within above ranges.

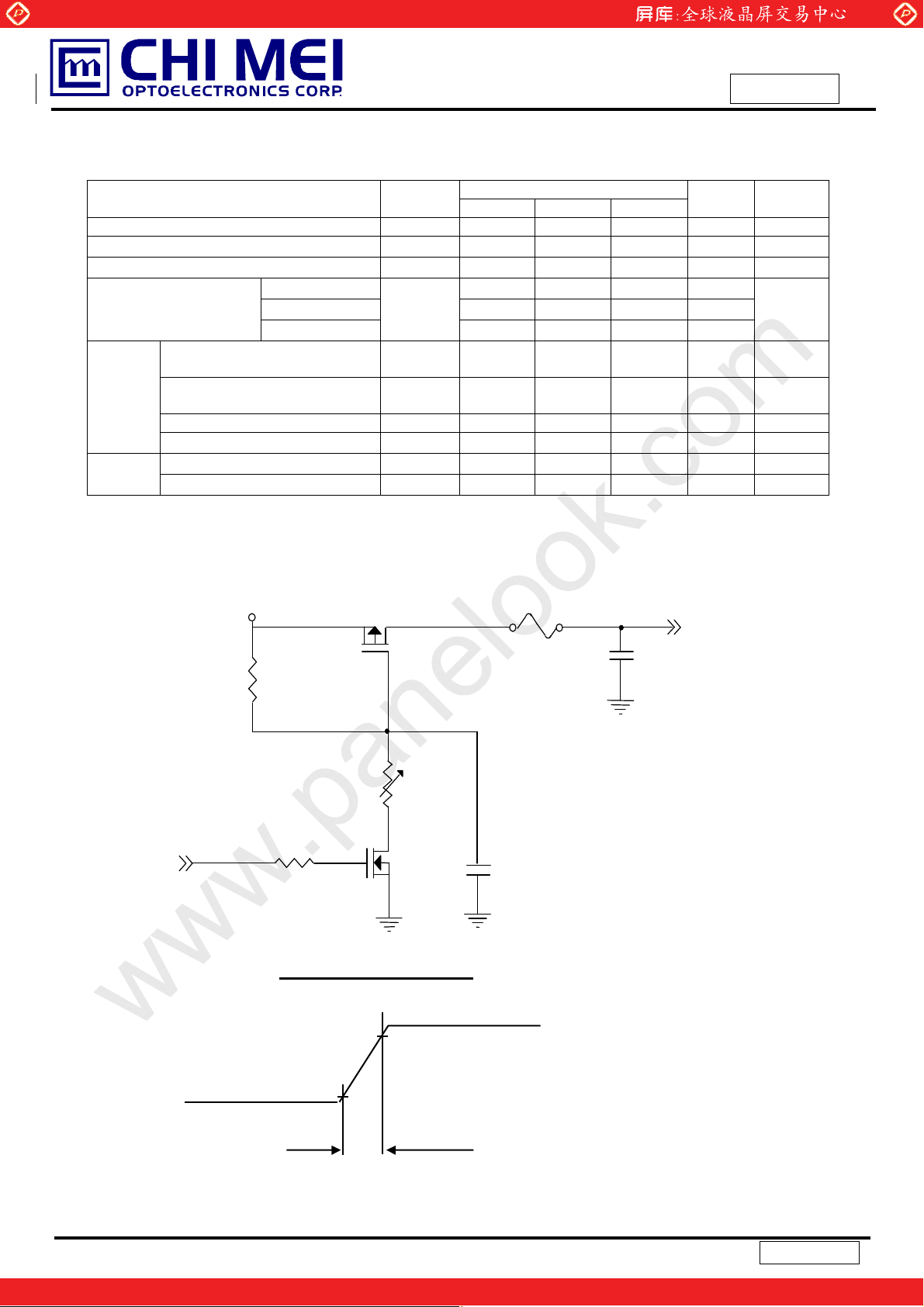

Note (2) Measurement Conditions:

+12.0V

R1

200K

Q1 AO4409

FUSE

C3

1uF

Vcc

(LCD Module Input)

(Low to High)

(Control Signal)

SW

R2

1K

VR1

47K

Q2

2N7002

C1

10uF

Vcc rising time is 470us

+12V

0.9Vcc

0.1Vcc

GND

470us

7

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 8

Global LCD Panel Exchange Center

(+/

)

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

Note (3) The specified power supply current is under the conditions at Vcc = 12 V, Ta = 25 ± 2 ºC, fv = 60 Hz,

whereas a power dissipation check pattern below is displayed.

a. White Pattern

Active Area

c. Vertical Stripe Pattern

b. Black Pattern

Active Area

R

G

R

B

G

B

B

R

R

G

G

B

B

R

4. BLOCK DIAGRAM

4.1 TFT LCD OPEN CELL

RX0(+/-)

RX1(+/-)

RX2(+/-)

RX3(+/-)

RXCLK

-

Vcc

GND

(P-TWO(

INPUT CONNECTOR

ك࣑

) 196185-30041)

Active Area

TIMING

CONTROLLER

DC/DC CONVERTER &

REFERENCE VOLTAGE

R

B

G

R R

G

SCAN DRIVER IC

R

G

B

B

B

G

B

TFT LCD PANEL

(1366x3x768)

DATA DRIVER IC

R

8

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 9

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

5. INPUT TERMINAL PIN ASSIGNMENT

5.1 TFT LCD MODULE

CNF1 Connector Pin Assignment

Pin No. Symbol Description Note

1 VCC Power supply: +12V

2 VCC Power supply: +12V

3 VCC Power supply: +12V

4 VCC Power supply: +12V

5 GND Ground

6 GND Ground

7 GND Ground

8 GND Ground

9 SELLVDS Select LVDS data format (2)

10 NC No connection (3)

11 GND Ground

12 RX0- Negative transmission data of pixel 0

13 RX0+ Positive transmission data of pixel 0

14 GND Ground

15 RX1- Negative transmission data of pixel 1

16 RX1+ Positive transmission data of pixel 1

17 GND Ground

18 RX2- Negative transmission data of pixel 2

19 RX2+ Positive transmission data of pixel 2

20 GND Ground

21 RXCLK- Negative of clock

22 RXCLK+ Positive of clock

23 GND Ground

24 RX3- Negative transmission data of pixel 3

25 RX3+ Positive transmission data of pixel 3

26 GND Ground

27 NC No connection (3)

28 NC No connection (3)

29 GND Ground

30 GND Ground

Note (1) CN2 Connector Part No.: P-TWO (ك࣑) 196185-30041 or Equal.

Note (2) Ground or OPEN: Normal, High: JEIDA LVDS format

Please refer to 5.3 LVDS INTERFACE (Page 11)

Note (3) Reserved for internal use. Please leave it open.

9

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 10

Global LCD Panel Exchange Center

p

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

5.2 BLOCK DIAGRAM OF INTERFACE

CNF1

Rx0+

-

R0-R7

-

B0-B7

DE

Rx1+

Rx1-

Rx2+

Rx2Rx3+

Rx3-

Host

Graphics

Controller

CLK+

CLK-

LVDS Transmitter

THC63LVDM83A

(LVDF83A)

51

Ө

100pF

51

Ө

51Ө

100

Ө

51

51

Ө

51

51

51

51

51

100pF

Ө

Ө

100pF

Ө

Ө

100pF

Ө

LVDS Receiver

THC63LVDF84A

RxOUT

R0-R7

G0-G7

F

B0-B7

DE

DCLK

Timing

Controller

R0~R7 : Pixel R Data

G0~G7 : Pixel G Data

B0~B7 : Pixel B Data

DE : Data Enable Signal

Note (1) The system must have the transmitter to drive the module.

Note (2) LVDS cable impedance shall be 50 ohms per signal line or about 100 ohms per twist-pair line when it is

used differentially.

10

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 11

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

5.3 LVDS INTERFACE

SIGNAL

TRANSMITTER

THC63LVDM83A

INTERFACE

CONNECTOR

RECEIVER

THC63LVDF84A

TFT CONTROL

INPUT

SELLVD=

L or OPEN

R0

R1

R2

R3

R4

R5

G0

G1

G2

G3

G4

G5

B0

B1

24

bit

B2

B3

B4

B5

DE

R6

R7

G6

G7

B6

B7

RSVD 1

RSVD 2

RSVD 3

DCLK 31 TxCLK IN TxCLK OUT+

R0~R7: Pixel R Data (7; MSB, 0; LSB)

SELLVDS

=H

R2

R3

R4

R5

R6

R7

G2

G3

G4

G5

G6

G7

B2

B3

B4

B5

B6

B7

DE

R0

R1

G0

G1

B0

B1

RSVD 1

RSVD 2

RSVD 3

PIN INPUT Host TFT-LCD PIN OUTPUT

51

52

54

55

56

3

4

6

7

11

12

14

15

19

20

22

23

24

30

50

2

8

10

16

18

25

27

28

TxIN0

TxIN1

TxIN2

TxIN3

TxIN4

TxIN6

TxIN7

TxIN8

TxIN9

TxIN12

TxIN13

TxIN14

TxIN15

TxIN18

TxIN19

TxIN20

TxIN21

TxIN22

TxIN26

TxIN27

TxIN5

TxIN10

TxIN11

TxIN16

TxIN17

TxIN23

TxIN24

TxIN25

TA OUT0+

TA OUT0-

TA OUT1+

TA OUT1-

TA OUT2+

TA OUT2-

TA OUT3+

TA OUT3-

TxCLK OUT-

Rx 0+

Rx 0-

Rx 1+

Rx 1-

Rx 2+

Rx 2-

Rx 3+

Rx 3-

RxCLK IN+

RxCLK IN-

SELLVD=

L or OPEN

Rx OUT0

27

Rx OUT1

29

Rx OUT2

30

Rx OUT3

32

Rx OUT4

33

Rx OUT6

35

Rx OUT7

37

Rx OUT8

38

Rx OUT9

39

Rx OUT12

43

Rx OUT13

45

Rx OUT14

46

Rx OUT15

47

Rx OUT18

51

Rx OUT19

53

Rx OUT20

54

Rx OUT21

55

Rx OUT22

1

Rx OUT26

6

Rx OUT27

7

Rx OUT5

34

Rx OUT10

41

Rx OUT11

42

Rx OUT16

49

Rx OUT17

50

Rx OUT23

2

Rx OUT24

3

Rx OUT25

5

26 RxCLK OUT DCLK

R0

R1

R2

R3

R4

R5

G0

G1

G2

G3

G4

G5

B0

B1

B2

B3

B4

B5

DE

R6

R7

G6

G7

B6

B7

NC

NC

NC

SELLVDS

=H

R2

R3

R4

R5

R6

R7

G2

G3

G4

G5

G6

G7

B2

B3

B4

B5

B6

B7

DE

R0

R1

G0

G1

B0

B1

NC

NC

NC

G0~G7: Pixel G Data (7; MSB, 0; LSB)

B0~B7: Pixel B Data (7; MSB, 0; LSB)

DE : Data enable signal

Notes (1) RSVD (reserved) pins on the transmitter shall be “H” or “L”.

11

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 12

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

5.4 COLOR DATA INPUT ASSIGNMENT

The brightness of each primary color (red, green and blue) is based on the 8-bit gray scale data input for

the color. The higher the binary input, the brighter the color. The table below provides the assignment of color

versus data input.

Data Signal

Color

R7 R6 R5 R4 R3 R2 R1 R0 G7 G6 G5 G4 G3 G2 G1 G0 B7 B6 B5 B4 B3 B2 B1 B0

0

Black

Red

Green

Basic

Colors

Gray

Scale

Of

Red

Gray

Scale

Of

Green

Gray

Scale

Of

Blue

Note (1) 0: Low Level Voltage, 1: High Level Voltage

Blue

Cyan

Magenta

Yellow

White

Red(0) / Dark

Red(1)

Red(2)

:

:

Red(253)

Red(254)

Red(255)

Green(0) / Dark

Green(1)

Green(2)

:

:

Green(253)

Green(254)

Green(255)

Blue(0) / Dark

Blue(1)

Blue(2)

:

:

Blue(253)

Blue(254)

Blue(255)

0

1

1

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

:

:

:

:

1

1

1

1

1

1

0

0

0

0

0

0

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

0

0

0

0

0

0

Red Green Blue

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

0

0

0

0

1

0

1

1

1

1

0

0

0

0

0

1

1

1

1

1

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

1

1

1

1

0

0

0

0

0

0

1

1

1

1

0

0

0

0

0

0

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

1

1

1

1

1

1

0

0

0

0

0

0

:

:

:

:

0

0

0

0

0

0

0

1

1

0

0

1

1

1

1

0

0

0

0

0

0

:

:

0

0

0

0

0

0

0

0

0

1

1

0

:

:

0

1

1

0

1

1

0

0

0

0

0

0

:

:

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

0

0

1

1

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

1

1

0

0

1

1

0

0

0

0

0

0

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

0

0

1

1

0

0

0

0

0

0

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

1

1

0

0

1

1

0

0

0

0

0

0

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

0

0

0

0

0

0

0

0

1

0

0

1

:

:

:

:

1

0

0

1

1

1

12

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 13

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

5.5 LVDS INTERFACE

SELLVDS = L or Open (VESA)

SELLVDS = H (JEIDA)

R0~R7: Pixel R Data (7; MSB, 0; LSB)

G0~G7: Pixel G Data (7; MSB, 0; LSB)

B0~B7: Pixel B Data (7; MSB, 0; LSB)

DE : Data enable signal

Notes(1) RSVD(reserved)pins on the transmitter shall be “H” or “L”.

13

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 14

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

6. INTERFACE TIMING

6.1 INPUT SIGNAL TIMING SPECIFICATIONS

The input signal timing specifications are shown as the following table and timing diagram.

Signal Item Symbol Min. Typ. Max. Unit Note

LVDS Receiver Clock

LVDS Receiver Data

Vertical Active Display Term

Horizontal Active Display Term

Frequency 1/Tc 60 76 82 MH

Input cycle to

cycle jitter

Setup Time Tlvsu 600

Hold Time Tlvhd 600

Frame Rate

Total Tv

Display Tvd

Blank Tvb

Tot a l T h

Display Thd

Blank Thb

Trcl

Fr5 47 50 53 Hz

6

57 60 63 Hz

Fr

Ё

778

768

10

1442

1366

76

Ё

Ё

Ё

806 888 Th Tv=Tvd+Tvb

768 768 Th -

38 120 Th 1560 1936 Tc Th=Thd+Thb

1366 1366 Tc -

194 570 Tc -

200 ps

Ё

Ё

Z

ps

ps

Note (1) Since this module is operated in DE only mode, Hsync and Vsync input signals should be set to low

logic level. Otherwise, this module would operate abnormally.

INPUT SIGNAL TIMING DIAGRAM

DE

Th

DCLK

Tvd

Tv

Tvb

Thd

DE

DATA

Valid Display Data (1366 clocks)

14

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 15

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

RXCLK+/-

RXn+/-

Tlvsu

Tlvhd

1T

14

LVDS RECEIVER INTERFACE TIMING DIAGRAM

Tc

3T

14

5T

14

7T

14

9T

14

11T

14

13T

14

15

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 16

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

Approval

6.2 POWER ON/OFF SEQUENCE

To prevent a latch-up or DC operation of LCD module, the power on/off sequence should be as the

diagram below.

0.5

ЉЉЉЉ

T

1

ЉЉЉЉ

ЉЉЉЉ

T

T

ЉЉЉЉ

ЉЉЉЉ

2

ЉЉЉЉ

3

ЉЉЉЉ

T4

0

0

1s

0V

10ms

50ms

50ms

0.1V

CC

T

3

T1

T

2

0.1V

T4

cc

LVDS Signals

0V

Power On

VALI D

Power Off

0

ЉЉЉЉ

T

7

ЉЉЉЉ

ЉЉЉЉ

T2

T

8

ЉЉЉЉ

T3

T7

8

T

0

Option Signals

(SELLVDS)

Backlight (Recommended)

ЉЉЉЉ

ЉЉЉЉ

T5

T

6

500ms

100ms

50%

5

T

50%

6

T

Note (1) The supply voltage of the external system for the module input should follow the definition of Vcc.

Note (2) Apply the lamp voltage within the LCD operation range. When the backlight turns on before the LCD

operation or the LCD turns off before the backlight turns off, the display may momentarily become

abnormal screen.

Note (3) In case of Vcc is in off level, please keep the level of input signals on the low or high impedance. If

T2<0,that maybe cause electrical overstress failure.

Note (4) T4 should be measured after the module has been fully discharged between power off and on period.

Note (5) Interface signal shall not be kept at high impedance when the power is on.

Power ON/OFF Sequence

16

Version 2.0

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

www.panelook.com

Page 17

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

Approval

7. OPTICAL CHARACTERISTICS

7.1 TEST CONDITIONS

Item Symbol Value Unit

Ambient Temperature Ta

Ambient Humidity Ha

25±2

50±10

Supply Voltage VCC 12.0 V

Input Signal According to typical value in "3. ELECTRICAL CHARACTERISTICS"

Lamp Current ( High side ) IL

Oscillating Frequency (Inverter) FW

7.5mA ± 0.5

58±3

Frame rate 60 Hz

7.2 OPTICAL SPECIFICATIONS

The relative measurement methods of optical characteristics are shown as below. The following items should

be measured under the test conditions described in 7.1 and stable environment shown in Note (5).

Item Symbol Condition Min. Typ. Max. Unit Note

o

C

%RH

mA

KHz

Red

Rcx 0.650 -

Rcy 0.328 -

Gcx 0.274 -

Color

Chromaticity

Green

Blue

Gcy 0.583 -

Viewing Angle at Normal

Bcx 0.150 -

Standard light source “C”

=0°, θY =0°

θ

x

Direction

-

-

(0),(5)

Bcy 0.094 -

Wcx 0.314 -

White

Wcy

Center Transmittance T% - 6.2 - % (1),(7)

Contrast Ratio CR

TR - 3 - ms

Response Time

T

F

White Variation

Horizontal

Viewing

Angle

Vertical

δW

θx+

θ

x

θY+

θ

Y

-

-

θ

=0°, θY =0°

x

with CMO module

θ

=0°, θY =0°

x

with CMO Module@60Hz

θ

=0°, θY =0°

x

with CMO module

CR≥10

With CMO module

0.331

800 - (1),(3)

- 5 - ms

- - 1.3 - (1),(6)

- 80 -

- 80 -

- 80 -

- 70 -

-

(4)

Deg. (1),(2)

17

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 18

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

Note (0) Light source is the standard light source ”C” which is defined by CIE and driving voltage are based on

suitable gamma voltages. The calculating method is as following :

1. Measure Module’s and BLU’s spectrum. White is without signal input and R,G,B are with signal input.

BLU(for V260B1-L12) is supplied by CMO.

2. Calculate cell’s spectrum.

3. Calculate cell’s chromaticity by using the spectrum of standard light source “C”.

Note (1) Light source is the BLU which is supplied by CMO and driving voltage are based on suitable gamma

voltages.

Note (2) Definition of Viewing Angle (θx, θy):

Viewing angles are measured by Autronic Conoscope Cono-80.

Note (3) Definition of Contrast Ratio (CR):

θX- = 90º

6 o’clock

θ

y-

= 90º

The contrast ratio can be calculated by the following expression.

Contrast Ratio (CR) = L255 / L0

x-

y-

Normal

θx = θy = 0º

θy- θy+

θx−

θx+

12 o’clock direction

y+

θ

y+

= 90º

x+

θX+ = 90º

L255: Luminance of gray level 255

L 0: Luminance of gray level 0

CR = CR (5), where CR (X) is corresponding to the Contrast Ratio of the point X at the figure in

Note (6).

Note (4) Definition of Response Time (T

, TF):

R

18

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 19

Global LCD Panel Exchange Center

T

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

Optical

Response

Note (5) Measurement Setup:

100%

90%

10%

0%

The LCD module should be stabilized at given temperature for 1 hour to avoid abrupt temperature

change during measuring. In order to stabilize the luminance, the measurement should be executed

after lighting Backlight for 1 hour in a windless room.

LCD Module

Gray Level 255

TR

LCD Panel

Gray Level 0

T

Gray Level 255

F

ime

CS-2000

Note (6) Definition of White Variation (δW):

Field of View = 1º

500 mm

Light Shield

(Ambient Luminance < 2 lux)

19

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 20

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

Measure the luminance of gray level 255 at 5 points

δW = Maximum [L (1), L (2), L (3), L (4), L (5)] / Minimum [L (1), L (2), L (3), L (4), L (5)]

Note (7) Definition of Transmittance (T%) :

Module is without signal input.

Transmittance = * 100%

Vertical Line

W/4

W/2

W

3W /4

Luminance of LCD module

Luminance of backlight

D/4 D/2 3D/4

1 2

3 4

Horizontal Line

D

5

Active Area

: Test Point

X

X=1 to 5

20

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 21

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

8. PRECAUTIONS

8.1 ASSEMBLY AND HANDLING PRECAUTIONS

(1) Do not apply rough force such as bending or twisting to the product during assembly.

(2) To assemble backlight or install module into user’s system can be only in clean working areas. The dust

and oil may cause electrical short or worsen the polarizer.

(3) It’s not permitted to have pressure or impulse on the module because the LCD panel will be damaged.

(4) Always follow the correct power sequence when the product is connecting and operating. This can

prevent damage to the CMOS LSI chips during latch-up.

(5) Do not pull the I/F connector in or out while the module is operating.

(6) Use a soft dry cloth without chemicals for cleaning, because the surface of polarizer is very soft and

easily scratched.

(7) It is dangerous that moisture come into or contacted the product, because moisture may damage the

product when it is operating.

(8) High temperature or humidity may reduce the performance of module. Please store this product within

the specified storage conditions.

(9) When ambient temperature is lower than 10ºC may reduce the display quality. For example, the

response time will become slowly.

8.2 SAFETY PRECAUTIONS

(1) If the liquid crystal material leaks from the panel, it should be kept away from the eyes or mouth. In case

of contact with hands, skin or clothes, it has to be washed away thoroughly with soap.

(2) After the product’s end of life, it is not harmful in case of normal operation and storage.

21

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 22

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

9. PACKAGING

9.1 PACKING SPECIFICATIONS

(1) 15 LCD TV Panels / 1 Box

(2) Box dimensions : 804 (L) X 565 (W) X 363 (H)

(3) Weight : approximately 25 Kg ( 15 panels per box)

9.2 PACKING METHOD

Figures 9-1 and 9-2 are the packing method

LCD Panel

Tray need not to revolve .

Carton

Tray need to rev olve stack

The design packin g top layer for empty tray

Figure.9-1 packing method

Carton Lab el

22

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 23

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

Sea Transportation

Corner Protector:L1650*50*50mm

L800*50*50mm

Pallet:L1150*W840*H140mm

Pallet Stack:L1150*W840*H1960mm

Gross:265kg

PE Sheet

Film

Carton Label

PP Belt

Air Transportation

Corner Protector:L1250*50*50mm

L800*50*50mm

Pallet:L1150*W840*H140mm

Pallet Stack:L1150*W840*H1597mm

Gross:215kg

Film

Carton Label

PP Belt

PE Sheet

23

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 24

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

10. REGULATORY STANDARDS

10.1

SAFETY

Information Technology equipment

Audio/Video Apparatus

Regulatory Item Standard

UL UL 60950-1: 2003

cUL CAN/CSA C22.2 No.60950-1-03

CB IEC 60950-1:2001

UL

UL 60065: 2003

cUL CAN/CSA C22.2 No.60065-03

CB

IEC 60065:2001

24

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 25

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

11. DEFINITION OF LABELS

11.1 OPEN CELL LABEL

The barcode nameplate is pasted on each open cell as illustration for CMO internal control.

XXXXXXXXXXXXXX

The barcode nameplate is pasted on Protector Film of each open cell as illustration for CMO internal control.

-

-

XXXXXXXXXXXXXX

11.2 CARTON LABEL

The barcode nameplate is pasted on each box as illustration, and its definitions are as following explanation

P.O. NO.

Parts ID.

Carton ID.

XXXXXXXXXXXXXX

Quantities 15

Made in Taiwan(China)

(a) Model Name: V260B1– P12

(b) Carton ID: CMO internal control

(c) Quantities: 15

25

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Page 26

Global LCD Panel Exchange Center

Issued Date: Dec. 16, 2009

Model No.: V260B1-P12

www.panelook.com

Approval

12. Mechanical Drawing

ڻႝηިҽԖ Ϧљ

CHI MEI

26

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 2.0

www.panelook.com

Loading...

Loading...