Page 1

EP9315 User’s Guide

http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 2004

(All Rights Reserved)

FEB ‘04

DS638UM1

Page 2

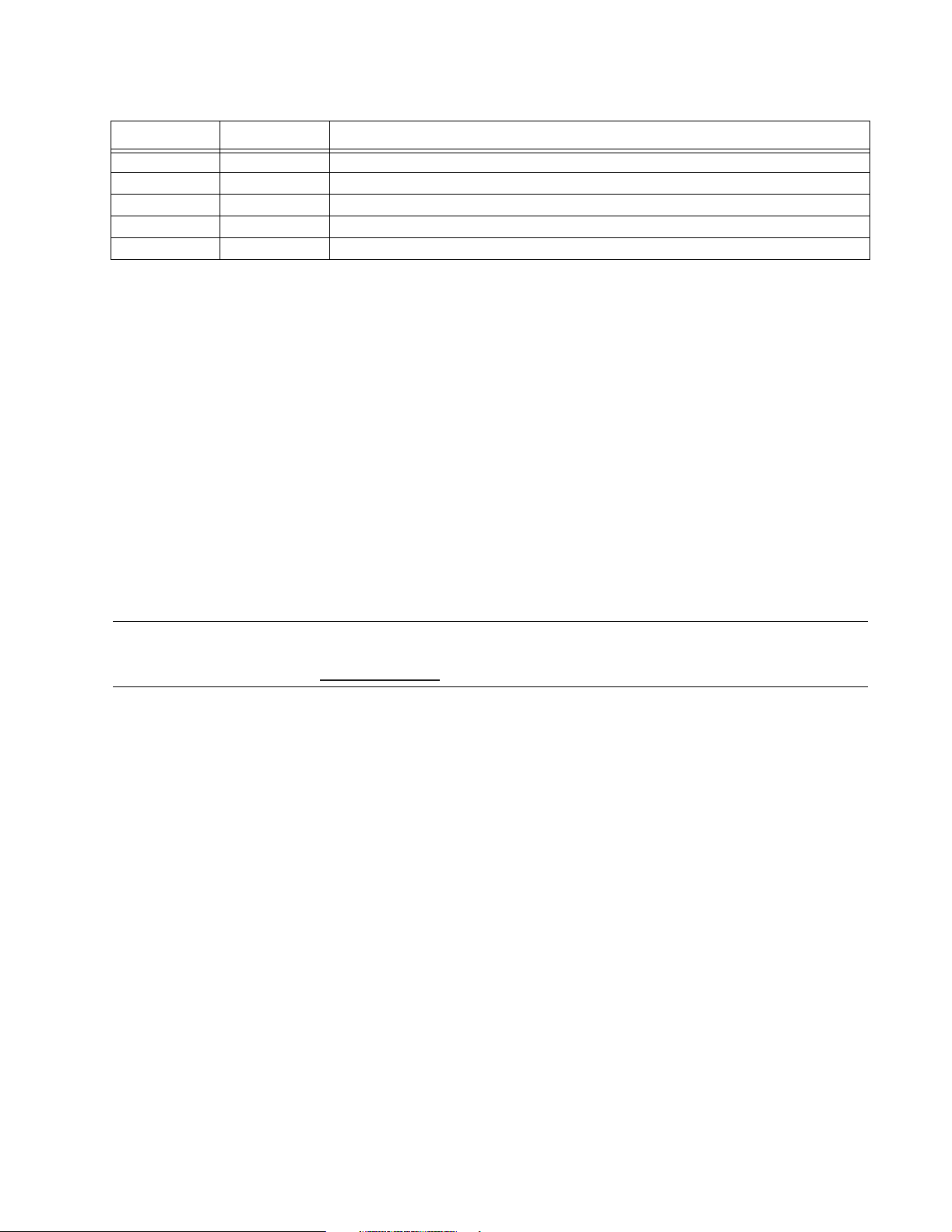

Revision Date Changes

1 February 2004 Initial Release

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative.

To find one nearest you go to www.cirrus.com

IMPORTANT NOTICE

“Preliminary” product information describes products that are in production, but for which full characterizati on data is not yet avai lable. Cirrus Logic, Inc. and

its subsidiaries (“Cirrus”) believe that the i nformati on contained in this document is accurate and reliabl e. However, the information is subject to change without

notice and is provided “AS IS” without warranty of any kind (express or implied). Customers are advised to obtain the latest versi on of r elevant information to

verify, before placing orders, that informati on being relied on is current and complete. All products are sold subject to the terms and condi tions of sale supplied

at the ti me of order acknowledgment, incl uding those pertai ning to warrant y, patent infringement, and limitatio n of liabili ty. No responsi bility is assumed by Cirr us

for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights

of third parties. This document is the property of Ci rrus and by furni shing this information, Cirrus grants no license, express or implied under any patents, mask

work rights, copyrights, tr ademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained

herein and gi ves consent for copies to be made of the information onl y for use with in your organizat ion with respect to Ci rrus integra ted circuit s or other product s

of Cirrus. This consent does not extend to other copying such as copying for general distr ibution, advertisi ng or promotional purposes, or for creating any work

for resale.

CERTAIN APPLICATIONS USI NG SEMI CONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE

PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS ( INCLUDING MEDICAL DEVICES, AIRCRAFT SYSTEMS OR COMPONENTS AND PERSONAL OR

AUTOMOTIVE SAFETY OR SECURITY DEVICES). I NCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT

THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED

WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN

SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, I NCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE I N CONNECTION

WITH THESE USES.

Cirrus Logic, Cirrus, MaverickCrunch, MaverickKey, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names

in this document may be trademarks or service marks of their respective owners.

Microsoft and Windows are registered trademarks of Microsoft Corporation.

MicrowireTM is a trademark of National Semiconductor Corp. Nati onal Semiconductor is a registered trademark of National Semiconductor Corp.

Texas Instruments is a registered trademark of Texas Instruments, Inc.

Motorola is a registered trademark of Motorola, Inc.

LINUX is a registered trademark of Linus Torval ds.

2 EP9315 User’s Manual - DS638UM1

Copyright 2004 Cirrus Logic

Page 3

About the EP9315 User’s Guide

This Guide describes the architecture, hardware, and operation of the Cirrus

Logic EP9315. It is intended to be used in conjunction with the EP9315

Datasheet, which contains the full electrical specifications for the device.

How to Use this Guide

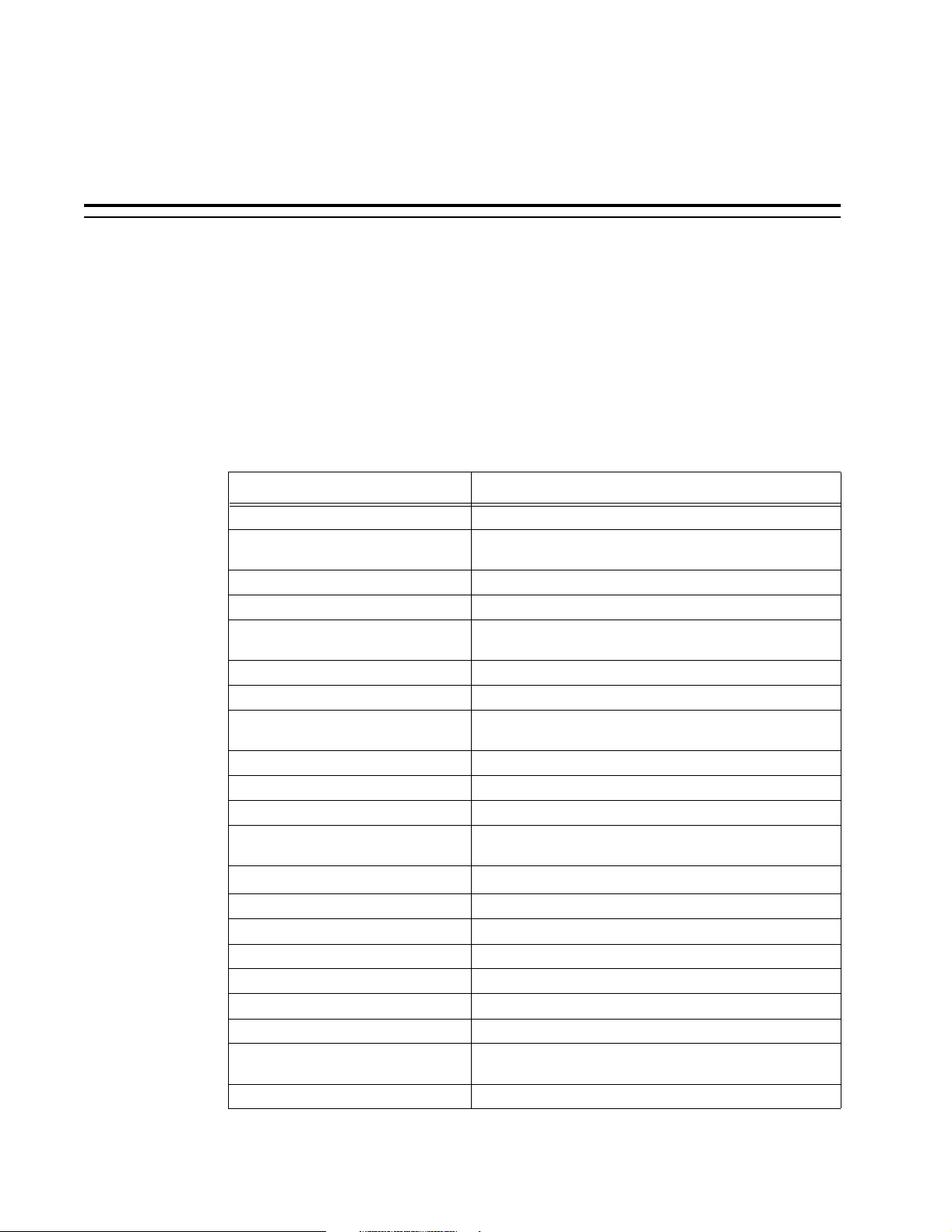

Subject Matter Location

AC’97 Chapter 22 - AC’97 Controller

ARM920T Processor

Boot ROM, Hardware and Software Chapter 4 - Boot ROM

Booting From SROM or SyncFlash Chapter 13 - SDRAM, SyncROM, and SyncFLASH Controller

Buses - AMBA, AHB, APB

Coprocessor Unit Chapter 3 - MaverickCrunch Coprocessor

DMA Controller Chapter 10 - DMA Controller

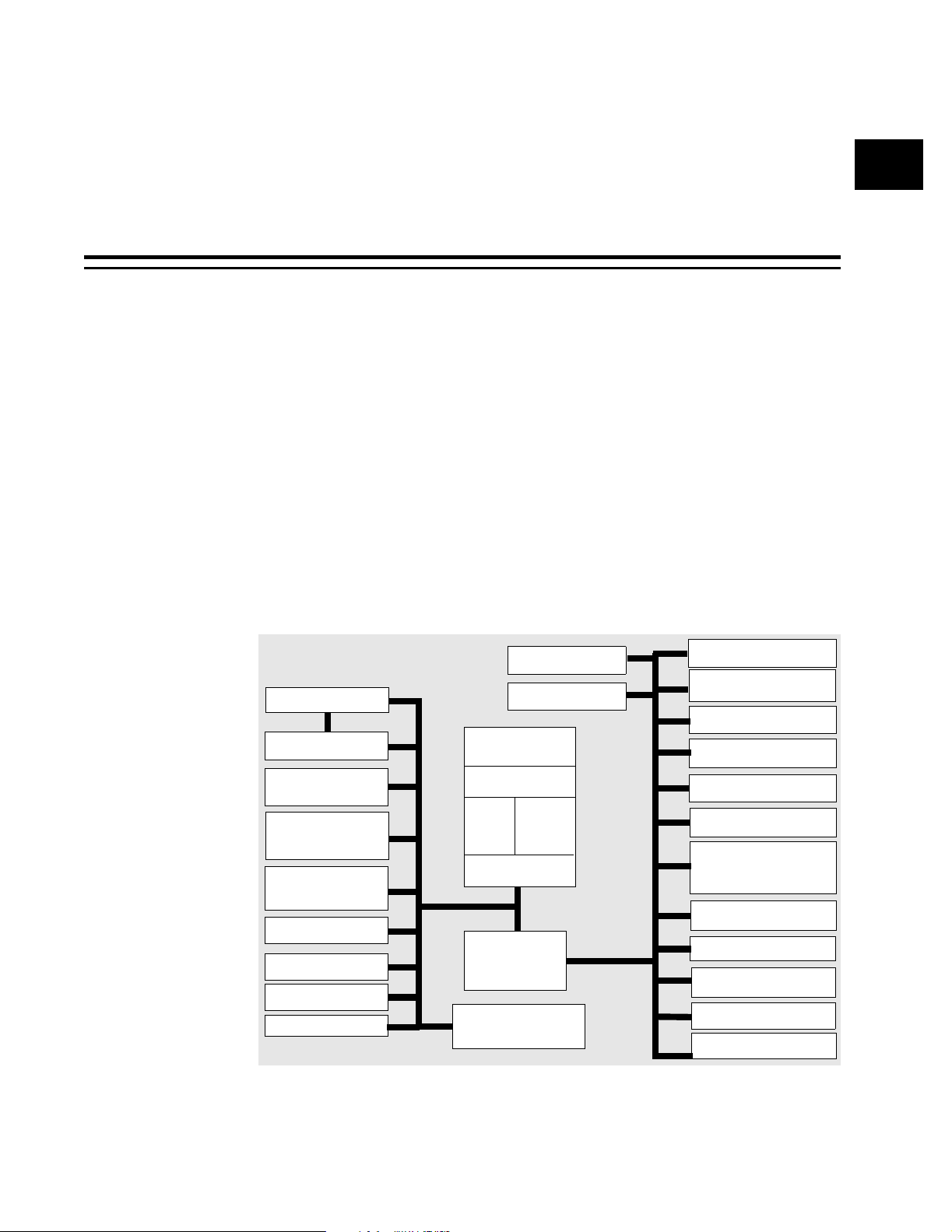

EP9315 Block Diagram

Ethernet Chapter 9 - 1/10/100 Mbps Ethernet LAN Controller

GPIO Chapter 28 - GPIO Interface

Graphics Accelerator Chapter 8 - Graphics Accelerator

HDLC

2

I

S

IDE Chapter 27 - IDE Interface

Infra-Red Interface Chapter 17 - IrDA

Interrupt Registers Chapter 6 - Vectored Interrupt Controller

Interrupts Chapter 6 - Vectored Interrupt Controller

IrDA Chapter 17 - IrDA

Key Pad Matrix Chapter 26 - Keypad Interface

LCD Interface

MAC Chapter 9 - 1/10/100 Mbps Ethernet LAN Controller

Chapter 2 - ARM920T Core and Advanced High-Speed Bus

(AHB)

Chapter 2 - ARM920T Core and Advanced High-Speed Bus

(AHB)

Chapter 2 - ARM920T Core and Advanced High-Speed Bus

(AHB)

Chapter 14 - UART1 With HDLC and Modem Control Signals

Chapter 16 - UART3 With HDLC Encoder

Chapter 21 - I2S Controller

Chapter 7 - Raster Engine With Analog/LCD Integrated Timing

and Interface

Preface

EP9315 User’s Manual - DS638UM1 3

Copyright 2004 Cirrus Logic

Page 4

Subject Matter Location

Memory Map

Modem Chapter 14 - UART1 With HDLC and Modem Control Signals

PCMCIA Chapter 12 - Static Memory Controller

Power Management Chapter 5 - System Controller

Programming Clocks Chapter 5 - System Controller

PWM Chapter 24 - Pulse Width Modulator

Raster Graphics

Real Time Clock Chapter 20 - Real Time Clock With Software Trim

Register List Chapter 1 - Introduction

RTC Chapter 20 - Real Time Clock With Software Trim

SDRAM Chapter 13 - SDRAM, SyncROM, and SyncFLASH Controller

Security Chapter 29 - Security

SMC Chapter 12 - Static Memory Controller

SSP Chapter 23 - Synchronous Serial Port

Static Memory Controller Chapter 12 - Static Memory Controller

System Configuration Chapter 5 - System Controller

System Registers Chapter 5 - System Controller

Timers Chapter 18 - Timers

Touch Screen Chapter 25 - Analog Touch Screen Interface

UART

USB Chapter 11 - Universal Serial Bus Host Controller

Vectored Interrupt Registers Chapter 6 - Vectored Interrupt Controller

Vectored Interrupts Chapter 6 - Vectored Interrupt Controller

Watchdog Timer Chapter 19 - Watchdog Timer

Chapter 2 - ARM920T Core and Advanced High-Speed Bus

(AHB)

Chapter 7 - Raster Engine With Analog/LCD Integrated Timing

and Interface

Chapter 14 - UART1 With HDLC and Modem Control Signals

Chapter 15 - UART2

Chapter 16 - UART3 With HDLC Encoder

Related Documents from Cirrus Logic

1. EP9315 Data Sheet, Document Number - DS638PP1

Reference Documents

1. ARM920T Technical Reference Manual

2. AMBA Specification (Rev. 2.0), ARM IHI 0011A, ARM Limited.

4 EP9315 User’s Manual - DS638UM1

Copyright 2004 Cirrus Logic

Page 5

3. AHB Example AMBA System (Addendum 01), ARM DDI 0170A, ARM

Limited.

4. The coprocessor instruction assembler notation can be referenced from

ARM programming manuals or the Quick Reference Card, document

number ARM QRC 0001D.

5. The MAC engine is compliant with the requirements of ISO/IEC 8802-3

(1993), Sections 3 and 4.

6. OpenHCI - Open Host Controller interface Specification for USB, Release

1.0a; Compaq, Microsoft, National Semiconductor.

7. ARM Coprocessor Quick Reference Card, document number ARM QRC

0001D.

8. Information Technology, AT Attachment with Packet Interface - 5

(ATA/ATAPI-5) ANSI NCITS document T13 1321D, Revision 3, 29

February 2000

9. OpenHCI - Open Host Controller Interface Specification for USB,

Release: 1.0a, Released - 09/14/99 2:33 PM

10. ARM PrimeCell PL190-Rel1v1 Revision 1.7 Technical Reference Manual

DDI0181C

11. Audio Codec ‘97, Revision 2.3, April 2002, Intel Corporation

Notational Conventions

This document uses the following conventions:

• Internal and external Signal Names, and Pin Names use mixed upper and

lower case alphanumeric, and are shown in bold font: RDLED.

• Register Bit Fields are named using upper and lower case alphanumeric:

that is, SBOOT, LCSn1.

• Registers are named using mixed upper and lower case alphanumeric:

that is, SysCfg or PxDDR. (Where there are multiple registers with similar

names, a lower case “x” is used as a place holder. For example, in the

PxDDR registers, x represents a letter between A and H, indicating the

specific port being discussed.)

Caution: In the Internal Register Map in Table 2-7 on page 7-53, some

memory locations are listed as Reserved. These memory

locations should not be used. Reading from these memory

locations will yield invalid data. Writing to these memory locations

may cause unpredictable results.

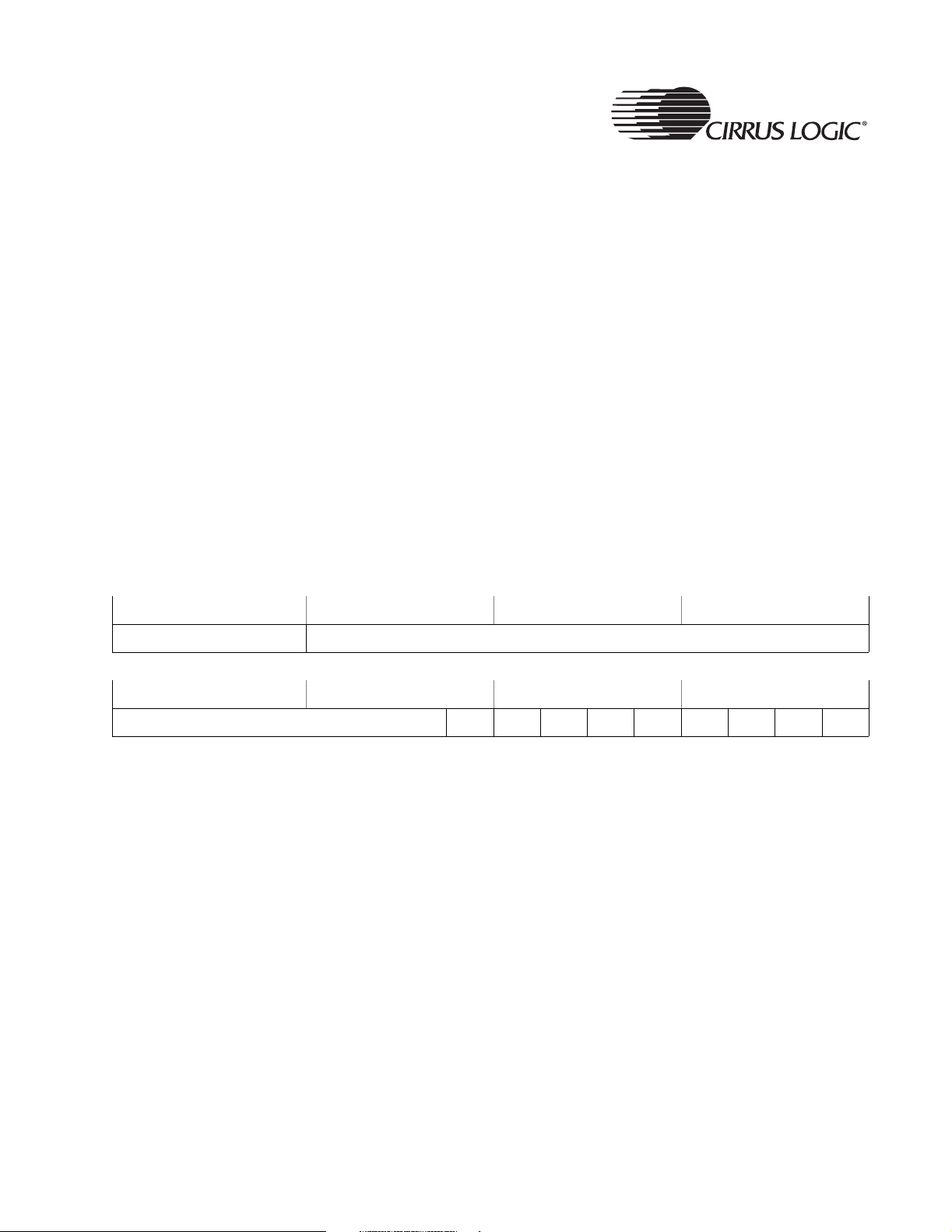

(An example register description is shown below. This description is used for

the following examples.)

EP9315 User’s Manual - DS638UM1 5

Copyright 2004 Cirrus Logic

Page 6

A specific bit may be specified in one of two ways:

By

register name[bit number]

or by

register name.bit field[bit number]

:

SysCfg[29]

Both of these representations refer to the same bit.

The following:

,

:

SysCfg.REV[1]

SysCfg[8]

, or

SysCfg.SBOOT

also refer to the same bit.

Hexidecimal numbers are referred to as

Binary numbers are referred to as

0x0000_0000

0000_0000b

.

.

Register Example

Note: This is only and example. For actual SysCfg register information, see “SysCfg”

on page 162.

SysCfg

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

REV RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD SBOOT LCSn7 LCSn6 LASDO LEEDA LEECLK RSVD LCSn2 LCSn1

Address:

0x8093_009C - Read/Write, Software locked

Default:

0x0000_0000

Definition:

System Configuration Register. Provides various system configuration

options.

Bit Descriptions:

RSVD: Reserved. Unknown During Read.

REV: Revision, reads chip Version number: 0 - Rev A, 1 - Rev B,

2 - Rev C, 3 - Rev D.

SBOOT: Serial Boot Flag. This bit is read-only.

1 hardware detected Serial Boot selection,

0 hardware detected Normal Boot.

6 EP9315 User’s Manual - DS638UM1

Copyright 2004 Cirrus Logic

Page 7

LCSn7, LCSn6: Latched version of CSn7 and CSn6 respectively. These

are used to define the external bus width for the boot code

boot.

LASDO: Latched version of ASDO pin. Used to select synchronous

versus asynchronous boot device.

LEEDA: Latched version of EEDAT pin.

LEECLK: Define Internal or external boot:

1 Internal

0 External

LCSn2, LCSn1: Define Watchdog startup action:

0 0 Watchdog disabled, Reset duration disabled

0 1 Watchdog disabled, Reset duration active

1 0 Watchdog active, Reset duration disabled

1 1 Watchdog active, Reset duration active

EP9315 User’s Manual - DS638UM1 7

Copyright 2004 Cirrus Logic

Page 8

This page intentionally blank.

8 EP9315 User’s Manual - DS638UM1

Copyright 2004 Cirrus Logic

Page 9

Table of Contents

Preface............................................................................................................. 3

About the EP9315 User’s Guide ............................................................................................................ 3

How to Use this Guide ...........................................................................................................................3

Related Documents from Cirrus Logic ...................................................................................................4

Reference Documents ...........................................................................................................................4

Notational Conventions ..........................................................................................................................5

Chapter 1 Introduction ............................................................................... 29

1.1 Introduction ...................................................................................................................................29

1.2 EP9315 Features ..........................................................................................................................30

1.3 EP9315 Applications .....................................................................................................................31

1.4 Overview of EP9315 Features ......................................................................................................32

1.4.1 High-Performance ARM920T Processor Core ....................................................................32

1.4.2 MaverickCrunch™ Coprocessor for Ultra-Fast Math Processing........................................32

1.4.3 MaverickKey™ Unique ID Secures Digital Content and OEM Designs ..............................32

1.4.4 Integrated Three-port USB 2.0 Full Speed Host with Transceivers.....................................33

1.4.5 Integrated Ethernet MAC Reduces BOM Costs ..................................................................33

1.4.6 8x8 Keypad Interface Reduces BOM Costs ........................................................................33

1.4.7 Multiple Booting Mechanisms Increase Flexibility ...............................................................33

1.4.8 Abundant General Purpose I/Os Build Flexible Systems ....................................................34

1.4.9 General-Purpose Memory Interface (SDRAM, SRAM, ROM and FLASH) .........................34

1.4.10 12-Bit Analog-to-Digital Converter (ADC) Provides an Integrated

Touch-Screen Interface or General ADC Functionality..............................................34

1.4.11 Graphics Accelerator .........................................................................................................34

1.4.12 PCMCIA Interface..............................................................................................................34

Chapter 2 ARM920T Core and Advanced High-Speed Bus (AHB) ......... 35

2.1 Introduction ...................................................................................................................................35

2.2 Overview: ARM920T Processor Core ...........................................................................................35

2.2.1 Features ..............................................................................................................................35

2.2.2 Block Diagram .....................................................................................................................36

2.2.3 Operations...........................................................................................................................36

2.2.3.1 ARM9TDMI Core........................................................................................................37

2.2.3.2 Memory Management Unit .........................................................................................38

2.2.3.3 Cache and Write Buffer..............................................................................................39

2.2.4 Coprocessor Interface .........................................................................................................40

2.2.5 AMBA AHB Bus Interface Overview....................................................................................41

2.2.6 EP9315 AHB Implementation Details..................................................................................42

2.2.7 Memory and Bus Access Errors ..........................................................................................43

2.2.8 Bus Arbitration .....................................................................................................................44

2.2.8.1 Main AHB Bus Arbiter ................................................................................................44

2.2.8.2 SDRAM Slave Arbiter.................................................................................................45

2.2.8.3 EBI Bus Arbiter...........................................................................................................45

2.3 AHB Decoder ................................................................................................................................45

2.3.1 AHB Bus Slave ....................................................................................................................46

2.3.2 AHB to APB Bridge..............................................................................................................46

2.3.2.1 Function and Operation of APB Bridge......................................................................46

2.3.3 APB Bus Slave ....................................................................................................................47

EP9315 User’s Manual - DS638UM1 9

Copyright 2004 Cirrus Logic

Page 10

2.3.4 Register Definitions............................................................................................................. 47

2.3.5 Memory Map ....................................................................................................................... 51

2.3.6 Internal Register Map.......................................................................................................... 52

2.3.6.1 Memory Access Rules............................................................................................... 52

Chapter 3 MaverickCrunch Coprocessor ................................................. 69

3.1 Introduction ................................................................................................................................... 69

3.1.1 Features.............................................................................................................................. 69

3.1.2 Operational Overview.......................................................................................................... 69

3.1.3 Pipelines and Latency......................................................................................................... 71

3.1.4 Data Registers .................................................................................................................... 71

3.1.5 Integer Saturation Arithmetic............................................................................................... 72

3.1.6 Comparisons....................................................................................................................... 74

3.2 Programming Examples ............................................................................................................... 75

3.2.1 Example 1 ........................................................................................................................... 75

3.2.1.1 Setup Code................................................................................................................ 76

3.2.1.2 C Code ...................................................................................................................... 76

3.2.1.3 Accessing MaverickCrunch with ARM Coprocessor Instructions .............................. 76

3.2.1.4 MaverickCrunch Assembly Language Instructions.................................................... 76

3.2.2 Example 2 ........................................................................................................................... 76

3.2.2.1 C Code ...................................................................................................................... 77

3.2.2.2 MaverickCrunch Assembly Language Instructions.................................................... 77

3.3 DSPSC Register........................................................................................................................... 78

3.4 ARM Coprocessor Instruction Format .......................................................................................... 81

3.5 Instruction Set for the MaverickCrunch Coprocessor ................................................................... 86

3.5.1 Load and Store Instructions ................................................................................................ 90

3.5.2 Move Instructions................................................................................................................ 94

3.5.3 Accumulator and DSPSC Move Instructions....................................................................... 98

3.5.4 Copy and Conversion Instructions .................................................................................... 102

3.5.5 Shift Instructions................................................................................................................ 106

3.5.6 Compare Instructions........................................................................................................ 108

3.5.7 Floating Point Arithmetic Instructions................................................................................ 110

3.5.8 Integer Arithmetic Instructions........................................................................................... 114

3.5.9 Accumulator Arithmetic Instructions.................................................................................. 118

Chapter 4 Boot ROM ................................................................................. 121

4.1 Introduction ................................................................................................................................. 121

4.1.1 Boot ROM Hardware Operational Overview ..................................................................... 121

4.1.1.1 Memory Map............................................................................................................ 121

4.1.2 Boot ROM Software Operational Overview....................................................................... 121

4.1.2.1 Image Header .......................................................................................................... 122

4.1.2.2 Boot Algorithm .........................................................................................................122

4.1.2.3 Flowchart................................................................................................................. 124

4.2 Boot Options............................................................................................................................... 125

4.2.1 UART Boot........................................................................................................................ 125

4.2.2 SPI Boot............................................................................................................................ 126

4.2.3 FLASH Boot ...................................................................................................................... 126

4.2.4 SDRAM or SyncFLASH Boot............................................................................................ 127

10 EP9315 User’s Manual - DS638UM1

Copyright 2004 Cirrus Logic

Page 11

4.2.5 Synchronous Memory Operation.......................................................................................127

Chapter 5 System Controller ................................................................... 129

5.1 Introduction .................................................................................................................................129

5.1.1 System Startup ..................................................................................................................129

5.1.2 System Reset ....................................................................................................................129

5.1.3 Hardware Configuration Control ........................................................................................130

5.1.4 Software System Configuration Options............................................................................132

5.1.5 Clock Control..................................................................................................................... 132

5.1.5.1 Oscillators and Programmable PLLs........................................................................132

5.1.5.2 Bus and Peripheral Clock Generation......................................................................133

5.1.5.3 Steps for Clock Configuration ..................................................................................137

5.1.6 Power Management ..........................................................................................................138

5.1.6.1 Clock Gatings...........................................................................................................138

5.1.6.2 System Power States...............................................................................................138

5.1.7 Interrupt Generation ..........................................................................................................140

5.2 Registers.....................................................................................................................................142

Chapter 6 Vectored Interrupt Controller................................................. 165

6.1 Introduction .................................................................................................................................165

6.1.1 Interrupt Priority.................................................................................................................166

6.1.2 Interrupt Descriptions ........................................................................................................168

6.2 Registers.....................................................................................................................................173

Chapter 7 Raster Engine With Analog/LCD Integrated Timing and

Interface....................................................................................................... 183

7.1 Introduction .................................................................................................................................183

7.2 Features......................................................................................................................................185

7.3 Raster Engine Features Overview ..............................................................................................185

7.3.1 Hardware Blinking .............................................................................................................185

7.3.2 Color Look-Up Tables........................................................................................................186

7.3.3 Grayscale/Color Generation for Monochrome/Passive Low Color Displays ..................... 186

7.3.4 Frame Buffer Organization ................................................................................................186

7.3.5 Frame Buffer Memory Size................................................................................................188

7.3.6 Pulse Width Modulated Brightness....................................................................................188

7.3.7 Hardware Cursor ...............................................................................................................189

7.4 Functional Details........................................................................................................................190

7.4.1 VILOSATI (Video Image Line Output Scanner and Transfer Interface) ............................ 190

7.4.2 Video FIFO ........................................................................................................................ 192

7.4.3 Video Pixel MUX................................................................................................................192

7.4.4 Blink Function .................................................................................................................... 192

7.4.5 Color Look-Up-Tables .......................................................................................................193

7.4.6 Color RGB Mux .................................................................................................................194

7.4.7 Pixel Shift Logic................................................................................................................. 194

7.4.8 Grayscale/Color Generator for Monochrome/Passive Low Color Displays .......................198

7.4.8.1 HORZ_CNT3, HORZ_CNT4 Counters ....................................................................199

7.4.8.2 VERT_CNT3, VERT_CNT4 Counters......................................................................199

7.4.8.3 FRAME_CNT3, FRAME_CNT4 Counters................................................................199

EP9315 User’s Manual - DS638UM1 11

Copyright 2004 Cirrus Logic

Page 12

7.4.8.4 HORZ_CNTx (pixel) timing...................................................................................... 199

7.4.8.5 VERT_CNTx (line) timing ........................................................................................ 199

7.4.8.6 FRAME_CNTx timing .............................................................................................. 199

7.4.8.7 Grayscale Look-Up Table (GrySclLUT)................................................................... 200

7.4.8.8 GrySclLUT Timing Diagram..................................................................................... 201

7.4.9 Hardware Cursor............................................................................................................... 210

7.4.9.1 Registers Used for Cursor ....................................................................................... 212

7.4.10 Video Timing ................................................................................................................... 213

7.4.10.1 Setting the Video Memory Parameters.................................................................. 216

7.4.10.2 PixelMode.............................................................................................................. 218

7.4.11 Blink Logic....................................................................................................................... 218

7.4.11.1 BlinkRate ............................................................................................................... 218

7.4.11.2 Defining Blink Pixels .............................................................................................. 219

7.4.11.3 Types of Blinking ................................................................................................... 219

7.4.12 Color Mode Definition...................................................................................................... 221

7.4.12.1 Pixel Look-up Table............................................................................................... 221

7.4.12.2 Triple 8-bit Mode.................................................................................................... 222

7.4.12.3 16-bit 565 Mode..................................................................................................... 222

7.4.12.4 16-bit 555 Mode..................................................................................................... 222

7.5 Registers .................................................................................................................................... 223

Chapter 8 Graphics Accelerator .............................................................. 265

8.1 Overview..................................................................................................................................... 265

8.2 Block Processing Modes ............................................................................................................ 265

8.2.1 Copy.................................................................................................................................. 265

8.2.2 Transparency .................................................................................................................... 266

8.2.3 Logical Mask ..................................................................................................................... 266

8.2.3.1 Logical Destination .................................................................................................. 266

8.2.3.2 Operation Precedence............................................................................................. 266

8.2.4 Remapping........................................................................................................................ 267

8.2.5 Block Fills .......................................................................................................................... 267

8.2.6 Packed Memory Transfer.................................................................................................. 267

8.3 Line Draws.................................................................................................................................. 267

8.3.1 Breshenham Line Draws................................................................................................... 268

8.3.2 Pixel Step Line Draws....................................................................................................... 268

8.4 Memory Organization for Graphics Accelerator ......................................................................... 268

8.4.1 Memory Organization for 1 Bit Per Pixel (bpp)................................................................. 269

8.4.2 Memory Organization for 4 Bit Per Pixel ........................................................................... 269

8.4.3 Memory Organization for 8 Bit Per Pixel ........................................................................... 269

8.4.4 Memory Organization for 24 Bit Per Pixel ......................................................................... 271

8.5 Register Programming................................................................................................................ 272

8.6 Word Count ................................................................................................................................ 272

8.6.1 Example: 8 BPP mode...................................................................................................... 273

8.6.2 Example: 24 BPP (packed) mode..................................................................................... 273

8.7 Pixel End and Start..................................................................................................................... 274

8.7.1 4 BPP mode ...................................................................................................................... 274

8.7.1.1 4 BPP Word Layout ................................................................................................. 274

8.7.1.2 8 BPP Word Layout ................................................................................................. 275

12 EP9315 User’s Manual - DS638UM1

Copyright 2004 Cirrus Logic

Page 13

8.7.1.3 16 BPP WORD Layout.............................................................................................275

8.7.1.4 24 BPP mode ...........................................................................................................275

8.8 Register Usage ...........................................................................................................................276

8.8.1 Line (Bresenham’s Algorithm) ...........................................................................................276

8.8.2 DX/DY Line Draw Function................................................................................................278

8.8.3 Block Fill ............................................................................................................................279

8.8.4 Block Copy ........................................................................................................................ 280

8.8.4.1 Source Memory Setup .............................................................................................280

8.8.4.2 Destination Memory Setup.......................................................................................280

8.9 Registers ....................................................................................................................................282

Chapter 9 1/10/100 Mbps Ethernet LAN Controller ............................... 297

9.1 Introduction .................................................................................................................................297

9.1.1 Detailed Description ..........................................................................................................297

9.1.1.1 Host Interface and Descriptor Processor .................................................................297

9.1.1.2 Reset and Initialization ............................................................................................. 298

9.1.1.3 Powerdown Modes...................................................................................................298

9.1.1.4 Address Space.........................................................................................................299

9.1.2 MAC Engine ......................................................................................................................299

9.1.2.1 Data Encapsulation..................................................................................................299

9.1.3 Packet Transmission Process ...........................................................................................300

9.1.3.1 Carrier Deference.....................................................................................................301

9.1.4 Transmit Back-Off..............................................................................................................303

9.1.4.1 Transmission............................................................................................................303

9.1.4.2 The FCS Field..........................................................................................................304

9.1.4.3 Bit Order...................................................................................................................304

9.1.4.4 Destination Address (DA) Filter................................................................................304

9.1.4.5 Perfect Address Filtering..........................................................................................304

9.1.4.6 Hash Filter................................................................................................................305

9.1.4.7 Flow Control .............................................................................................................306

9.1.4.8 Receive Flow Control...............................................................................................306

9.1.4.9 Transmit Flow Control ..............................................................................................307

9.1.4.10 Rx Missed and Tx Collision Counters....................................................................307

9.1.4.11 Accessing the MII...................................................................................................308

9.2 Descriptor Processor...................................................................................................................309

9.2.1 Receive Descriptor Processor Queues .............................................................................309

9.2.2 Receive Descriptor Queue ................................................................................................310

9.2.3 Receive Status Queue.......................................................................................................312

9.2.3.1 Receive Status Format.............................................................................................315

9.2.3.2 Receive Flow............................................................................................................318

9.2.3.3 Receive Errors .........................................................................................................319

9.2.3.4 Receive Descriptor Data/Status Flow ......................................................................320

9.2.3.5 Receive Descriptor Example....................................................................................321

9.2.3.6 Receive Frame Pre-Processing ...............................................................................321

9.2.3.7 Transmit Descriptor Processor.................................................................................322

9.2.3.8 Transmit Descriptor Queue ......................................................................................322

9.2.3.9 Transmit Descriptor Format .....................................................................................325

EP9315 User’s Manual - DS638UM1 13

Copyright 2004 Cirrus Logic

Page 14

9.2.3.10 Transmit Status Queue.......................................................................................... 326

9.2.3.11 Transmit Status Format......................................................................................... 328

9.2.3.12 Transmit Flow ........................................................................................................ 330

9.2.3.13 Transmit Errors...................................................................................................... 331

9.2.3.14 Transmit Descriptor Data/Status Flow................................................................... 332

9.2.4 Interrupts........................................................................................................................... 333

9.2.4.1 Interrupt Processing ................................................................................................ 333

9.2.5 Initialization ....................................................................................................................... 333

9.2.5.1 Interrupt Processing ................................................................................................ 334

9.2.5.2 Receive Queue Processing ..................................................................................... 334

9.2.5.3 Transmit Queue Processing .................................................................................... 334

9.2.5.4 Other Processing..................................................................................................... 335

9.2.5.5 Transmit Restart Process ........................................................................................ 335

9.3 Registers .................................................................................................................................... 337

Chapter 10 DMA Controller ...................................................................... 391

10.1 Introduction............................................................................................................................... 391

10.1.1 DMA Features List .......................................................................................................... 391

10.1.2 Managing Data Transfers Using a DMA Channel ........................................................... 392

10.1.3 DMA Operations.............................................................................................................. 394

10.1.3.1 Memory-to-Memory Channels ............................................................................... 394

10.1.3.2 Memory-to-Peripheral Channels............................................................................ 395

10.1.4 Internal M2P or P2M AHB Master Interface Functional Description ............................... 395

10.1.5 M2M AHB Master Interface Functional Description ........................................................ 396

10.1.5.1 Software Trigger Mode .......................................................................................... 396

10.1.5.2 Hardware Trigger Mode for Internal Peripherals (SSP and IDE) and

for External Peripherals without Handshaking Signals ..................................................... 396

10.1.5.3 Hardware Trigger Mode for External Peripherals with Handshaking Signals ........ 397

10.1.6 AHB Slave Interface Limitations...................................................................................... 397

10.1.7 Interrupt Interface............................................................................................................ 397

10.1.8 Internal M2P/P2M Data Unpacker/Packer Functional Description.................................. 397

10.1.9 Internal M2P/P2M DMA Functional Description.............................................................. 398

10.1.9.1 Internal M2P/P2M DMA Buffer Control Finite State Machine................................ 398

10.1.9.2 Data Transfer Initiation and Termination ............................................................... 400

10.1.10 M2M DMA Functional Description................................................................................. 401

10.1.10.1 M2M DMA Control Finite State Machine ............................................................. 401

10.1.10.2 M2M Buffer Control Finite State Machine............................................................ 403

10.1.10.3 Data Transfer Initiation ........................................................................................ 405

10.1.10.4 Data Transfer Termination................................................................................... 407

10.1.10.5 Memory Block Transfer ....................................................................................... 408

10.1.10.6 Bandwidth Control ............................................................................................... 408

10.1.10.7 External Peripheral DMA Request (DREQ) Mode ............................................... 408

10.1.11 DMA Data Transfer Size Determination........................................................................ 410

10.1.11.1 Software Initiated M2M and M2P/P2M Transfers ................................................ 410

10.1.11.2 Hardware Initiated M2M Transfers ...................................................................... 410

10.1.12 Buffer Descriptors ......................................................................................................... 411

10.1.12.1 Internal M2P/P2M Channel Rx Buffer Descriptors .............................................. 411

14 EP9315 User’s Manual - DS638UM1

Copyright 2004 Cirrus Logic

Page 15

10.1.12.2 Internal M2P/P2M Channel Tx Buffer Descriptors ...............................................411

10.1.12.3 M2M Channel Buffer Descriptors .........................................................................411

10.1.13 Bus Arbitration...............................................................................................................411

10.2 Registers...................................................................................................................................413

10.2.1 DMA Controller Memory Map..........................................................................................413

10.2.2 Internal M2P/P2M Channel Register Map .......................................................................413

Chapter 11 Universal Serial Bus Host Controller .................................. 441

11.1 Introduction ...............................................................................................................................441

11.1.1 Features ..........................................................................................................................441

11.2 Overview ...................................................................................................................................441

11.2.1 Data Transfer Types........................................................................................................442

11.2.2 Host Controller Interface..................................................................................................443

11.2.2.1 Communication Channels ......................................................................................443

11.2.2.2 Data Structures ......................................................................................................444

11.2.3 Host Controller Driver Responsibilities ............................................................................446

11.2.3.1 Host Controller Management .................................................................................446

11.2.3.2 Bandwidth Allocation..............................................................................................446

11.2.3.3 List Management....................................................................................................447

11.2.3.4 Root Hub................................................................................................................448

11.2.4 Host Controller Responsibilities.......................................................................................448

11.2.4.1 USB States.............................................................................................................448

11.2.4.2 Frame management...............................................................................................448

11.2.4.3 List Processing.......................................................................................................448

11.2.5 USB Host Controller Blocks.............................................................................................449

11.2.5.1 AHB Slave..............................................................................................................449

11.2.5.2 AHB Master............................................................................................................449

11.2.5.3 HCI Slave Block .....................................................................................................449

11.2.5.4 HCI Master Block ...................................................................................................450

11.2.5.5 USB State Control..................................................................................................450

11.2.5.6 Data FIFO ..............................................................................................................450

11.2.5.7 List Processor ........................................................................................................450

11.2.5.8 Root Hub and Host SIE..........................................................................................450

11.3 Registers...................................................................................................................................451

Chapter 12 Static Memory Controller ..................................................... 479

12.1 Introduction ...............................................................................................................................479

12.2 Static Memory Controller Operation..........................................................................................480

12.3 Byte Lane Write / Read Control ................................................................................................482

12.4 PCMCIA Interface Signals ........................................................................................................483

12.5 PCMCIA Card Memory Mode Enable Signals ..........................................................................484

12.6 PCMCIA Card Memory Mapping...............................................................................................485

12.7 Registers...................................................................................................................................489

Chapter 13 SDRAM, SyncROM, and SyncFLASH Controller................ 495

13.1 Introduction ...............................................................................................................................495

13.1.1 Booting (from SROM or SyncFLASH) .............................................................................495

13.1.1.1 Address Pin Usage ................................................................................................496

EP9315 User’s Manual - DS638UM1 15

Copyright 2004 Cirrus Logic

Page 16

13.1.1.2 SDRAM Initialization.............................................................................................. 498

13.1.1.3 Programming External Device Mode Register....................................................... 499

13.1.1.4 SDRAM Self Refresh............................................................................................. 502

13.1.1.5 SROM and SyncFlash ........................................................................................... 502

13.1.1.6 External Synchronous Memory System................................................................. 503

13.2 Registers .................................................................................................................................. 507

Chapter 14 UART1 With HDLC and Modem Control Signals ................ 515

14.1 Introduction............................................................................................................................... 515

14.2 UART Overview........................................................................................................................ 515

14.2.1 UART Functional Description.......................................................................................... 516

14.2.1.1 AMBA APB Interface ............................................................................................. 516

14.2.1.2 DMA Block.............................................................................................................516

14.2.1.3 Register Block ....................................................................................................... 517

14.2.1.4 Baud Rate Generator ............................................................................................ 518

14.2.1.5 Transmit FIFO ....................................................................................................... 518

14.2.1.6 Receive FIFO ........................................................................................................ 518

14.2.1.7 Transmit Logic ....................................................................................................... 518

14.2.1.8 Receive Logic ........................................................................................................ 518

14.2.1.9 Interrupt Generation Logic ..................................................................................... 518

14.2.1.10 Synchronizing Registers and Logic ..................................................................... 519

14.2.2 UART Operation.............................................................................................................. 519

14.2.2.1 Error Bits................................................................................................................ 520

14.2.2.2 Disabling the FIFOs............................................................................................... 520

14.2.2.3 System/diagnostic Loopback Testing .................................................................... 520

14.2.2.4 UART Character Frame......................................................................................... 520

14.2.3 Interrupts......................................................................................................................... 521

14.2.3.1 UARTMSINTR....................................................................................................... 521

14.2.3.2 UARTRXINTR ....................................................................................................... 521

14.2.3.3 UARTTXINTR........................................................................................................ 522

14.2.3.4 UARTRTINTR........................................................................................................ 522

14.2.3.5 UARTINTR ............................................................................................................ 522

14.3 Modem...................................................................................................................................... 522

14.4 HDLC........................................................................................................................................ 523

14.4.1 Overview of HDLC Modes............................................................................................... 523

14.4.2 Selecting HDLC Modes................................................................................................... 524

14.4.3 HDLC Transmit ............................................................................................................... 525

14.4.4 HDLC Receive ................................................................................................................ 526

14.4.5 CRCs............................................................................................................................... 527

14.4.6 Address Matching ........................................................................................................... 527

14.4.7 Aborts.............................................................................................................................. 528

14.4.8 DMA ................................................................................................................................ 528

14.4.9 Writing Configuration Registers ...................................................................................... 529

14.5 UART1 Package Dependency..................................................................................................529

14.5.1 Clocking Requirements ...................................................................................................530

14.5.2 Bus Bandwidth Requirements......................................................................................... 530

14.6 Registers .................................................................................................................................. 532

16 EP9315 User’s Manual - DS638UM1

Copyright 2004 Cirrus Logic

Page 17

Chapter 15 UART2 .................................................................................... 553

15.1 Introduction ...............................................................................................................................553

15.2 IrDA SIR Block..........................................................................................................................553

15.2.1 IrDA SIR Encoder/decoder Functional Description .........................................................553

15.2.1.1 IrDA SIR Transmit Encoder....................................................................................554

15.2.1.2 IrDA SIR Receive Decoder ....................................................................................554

15.2.2 IrDA SIR Operation..........................................................................................................555

15.2.2.1 System/diagnostic Loopback Testing.....................................................................556

15.2.3 IrDA Data Modulation ......................................................................................................556

15.2.4 Enabling Infrared (Ir) Modes ............................................................................................557

15.3 UART2 Package Dependency ..................................................................................................557

15.3.1 Clocking Requirements ...................................................................................................557

15.3.2 Bus Bandwidth Requirements .........................................................................................558

15.4 Registers...................................................................................................................................559

Chapter 16 UART3 With HDLC Encoder ................................................. 571

16.1 Introduction ...............................................................................................................................571

16.2 Implementation Details..............................................................................................................571

16.2.1 UART3 Package Dependency.........................................................................................571

16.2.2 Clocking Requirements ...................................................................................................572

16.2.3 Bus Bandwidth Requirements .........................................................................................572

16.3 Registers...................................................................................................................................573

Chapter 17 IrDA ........................................................................................ 591

17.1 Introduction ...............................................................................................................................591

17.2 IrDA Interfaces ..........................................................................................................................591

17.3 Shared IrDA Interface Feature..................................................................................................592

17.3.1 Overview..........................................................................................................................592

17.3.2 Functional Description .....................................................................................................592

17.3.2.1 General Configuration ............................................................................................593

17.3.2.2 Transmitting Data................................................................................................... 593

17.3.2.3 Receiving Data.......................................................................................................596

17.3.2.4 Special Conditions .................................................................................................598

17.3.3 Control Information Buffering...........................................................................................598

17.4 Medium IrDA Specific Features ................................................................................................599

17.4.1 Introduction ......................................................................................................................599

17.4.1.1 Bit Encoding...........................................................................................................599

17.4.1.2 Frame Format ........................................................................................................599

17.4.2 Functional Description .....................................................................................................601

17.4.2.1 Baud Rate Generation ...........................................................................................601

17.4.2.2 Receive Operation .................................................................................................602

17.4.2.3 Transmit Operation ................................................................................................603

17.5 Fast IrDA Specific Features ......................................................................................................604

17.5.1 Introduction ......................................................................................................................604

17.5.1.1 4PPM Modulation...................................................................................................604

17.5.1.2 4.0 Mbps FIR Frame Format..................................................................................606

17.5.2 Functional Description .....................................................................................................607

17.5.2.1 Baud Rate Generation ...........................................................................................608

EP9315 User’s Manual - DS638UM1 17

Copyright 2004 Cirrus Logic

Page 18

17.5.2.2 Receive Operation................................................................................................. 608

17.5.2.3 Transmit Operation................................................................................................ 610

17.5.3 IrDA Connectivity ............................................................................................................ 611

17.5.4 IrDA Integration Information............................................................................................612

17.5.4.1 Enabling Infrared Modes ....................................................................................... 612

17.5.4.2 Clocking Requirements ......................................................................................... 612

17.5.4.3 Bus Bandwidth Requirements ............................................................................... 613

17.6 Registers .................................................................................................................................. 614

Chapter 18 Timers..................................................................................... 629

18.1 Introduction............................................................................................................................... 629

18.1.1 Features .......................................................................................................................... 629

18.1.2 16 and 32-bit Timer Operation ........................................................................................ 629

18.1.2.1 Free Running Mode ............................................................................................... 630

18.1.2.2 Pre-load Mode ....................................................................................................... 630

18.1.3 40-bit Timer Operation .................................................................................................... 630

18.2 Registers .................................................................................................................................. 631

Chapter 19 Watchdog Timer .................................................................... 637

19.1 Introduction............................................................................................................................... 637

19.1.1 Watchdog Activation ....................................................................................................... 638

19.1.2 Clocking Requirements ...................................................................................................638

19.1.3 Reset Requirements ....................................................................................................... 638

19.1.4 Watchdog Status............................................................................................................. 638

19.2 Registers .................................................................................................................................. 640

Chapter 20 Real Time Clock With Software Trim................................... 643

20.1 Introduction............................................................................................................................... 643

20.1.1 Software Trim.................................................................................................................. 643

20.1.1.1 Software Compensation ........................................................................................ 644

20.1.1.2 Oscillator Frequency Calibration............................................................................ 644

20.1.1.3 RTCSWComp Value Determination ...................................................................... 644

20.1.1.4 Example - Measured Value Split Into Integer and Fractional Component............. 645

20.1.1.5 Maximum Error Calculation vs. Real Time Clock Accuracy................................... 645

20.1.1.6 Real-Time Interrupt................................................................................................ 646

20.1.2 Reset Control.................................................................................................................. 646

20.2 Registers .................................................................................................................................. 647

Chapter 21 I2S Controller ......................................................................... 651

21.1 Introduction............................................................................................................................... 651

2

21.2 I

21.3 I

21.4 I

21.5 I

21.6 I

S Transmitter Channel Overview ........................................................................................... 653

2

S Receiver Channel Overview ............................................................................................... 657

21.3.1 Receiver FIFO’s .............................................................................................................. 657

2

S Configuration and Status Registers.................................................................................... 659

2

S Master Clock Generation.................................................................................................... 659

2

S Bit Clock Rate Generation .................................................................................................. 661

21.6.1 Example of the Bit Clock Generation. ............................................................................. 662

21.6.2 Example of Right Justified LRCK format......................................................................... 662

18 EP9315 User’s Manual - DS638UM1

Copyright 2004 Cirrus Logic

Page 19

21.7 Interrupts...................................................................................................................................663

21.8 Registers...................................................................................................................................665

21.8.1 I

21.8.2 I

21.8.3 I

21.8.4 I

2

S TX Registers..............................................................................................................665

2

S RX Registers .............................................................................................................672

2

S Configuration and Status Registers...........................................................................678

2

S Global Status Registers.............................................................................................682

Chapter 22 AC’97 Controller.................................................................... 685

22.1 Introduction ...............................................................................................................................685

22.2 Interrupts...................................................................................................................................687

22.2.1 Channel Interrupts ...........................................................................................................687

22.2.1.1 RIS .........................................................................................................................687

22.2.1.2 TIS..........................................................................................................................688

22.2.1.3 RTIS.......................................................................................................................688

22.2.1.4 TCIS.......................................................................................................................688

22.2.2 Global Interrupts..............................................................................................................688

22.2.2.1 CODECREADY......................................................................................................688

22.2.2.2 WINT......................................................................................................................688

22.2.2.3 GPIOINT ................................................................................................................689

22.2.2.4 GPIOTXCOMPLETE..............................................................................................689

22.2.2.5 SLOT2INT..............................................................................................................689

22.2.2.6 SLOT1TXCOMPLETE ...........................................................................................689

22.2.2.7 SLOT2TXCOMPLETE ...........................................................................................689

22.3 System Loopback Testing .........................................................................................................689

22.4 Registers...................................................................................................................................690

Chapter 23 Synchronous Serial Port ...................................................... 709

23.1 Introduction ...............................................................................................................................709

23.2 Features....................................................................................................................................709

23.3 SSP Functionality......................................................................................................................710

23.4 SSP Pin Multiplex......................................................................................................................710

23.5 Configuring the SSP..................................................................................................................710

23.5.1 Enabling SSP Operation..................................................................................................711

23.5.2 Master/Slave Mode..........................................................................................................711

23.5.3 Serial Bit Rate Generation...............................................................................................711

23.5.4 Frame Format.................................................................................................................711

23.5.5 Texas Instruments® Synchronous Serial Frame Format ................................................712