Page 1

EP9307 User’s Guide

http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 2004

(All Rights Reserved)

AUG ‘04

DS667UM1

Page 2

Revision Date Changes

1 August 2004 Initial Release

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative.

To find one nearest you go to www.cirrus.com

IMPORTANT NOTICE

“Preliminary” product information describes products that are in production, but for which full characterizati on data is not yet avai lable. Cirrus Logic, Inc. and

its subsidiaries (“Cirrus”) believe that the i nformati on contained in this document is accurate and reliabl e. However, the information is subject to change without

notice and is provided “AS IS” without warranty of any kind (express or implied). Customers are advised to obtain the latest versi on of r elevant information to

verify, before placing orders, that informati on being relied on is current and complete. All products are sold subject to the terms and condi tions of sale supplied

at the ti me of order acknowledgment, incl uding those pertai ning to warrant y, patent infringement, and limitatio n of liabili ty. No responsi bility is assumed by Cirr us

for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights

of third parties. This document is the property of Ci rrus and by furni shing this information, Cirrus grants no license, express or implied under any patents, mask

work rights, copyrights, tr ademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained

herein and gi ves consent for copies to be made of the information onl y for use with in your organizat ion with respect to Ci rrus integra ted circuit s or other product s

of Cirrus. This consent does not extend to other copying such as copying for general distr ibution, advertisi ng or promotional purposes, or for creating any work

for resale.

CERTAIN APPLICATIONS USI NG SEMI CONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE

PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS ( INCLUDING MEDICAL DEVICES, AIRCRAFT SYSTEMS OR COMPONENTS AND PERSONAL OR

AUTOMOTIVE SAFETY OR SECURITY DEVICES). I NCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT

THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED

WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN

SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, I NCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE I N CONNECTION

WITH THESE USES.

Cirrus Logic, Cirrus, MaverickCrunch, MaverickKey, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names

in this document may be trademarks or service marks of their respective owners.

Microsoft and Windows are registered trademarks of Microsoft Corporation.

MicrowireTM is a trademark of National Semiconductor Corp. Nati onal Semiconductor is a registered trademark of National Semiconductor Corp.

Texas Instruments is a registered trademark of Texas Instruments, Inc.

Motorola is a registered trademark of Motorola, Inc.

LINUX is a registered trademark of Linus Torval ds.

2 EP9307 User’s Manual - DS667UM1

Copyright 2004 Cirrus Logic

Page 3

About the EP9307 User’s Guide

This Guide describes the architecture, hardware, and operation of the Cirrus

Logic EP9307. It is intended to be used in conjunction with the EP9307

Datasheet, which contains the full electrical specifications for the device.

How to Use this Guide

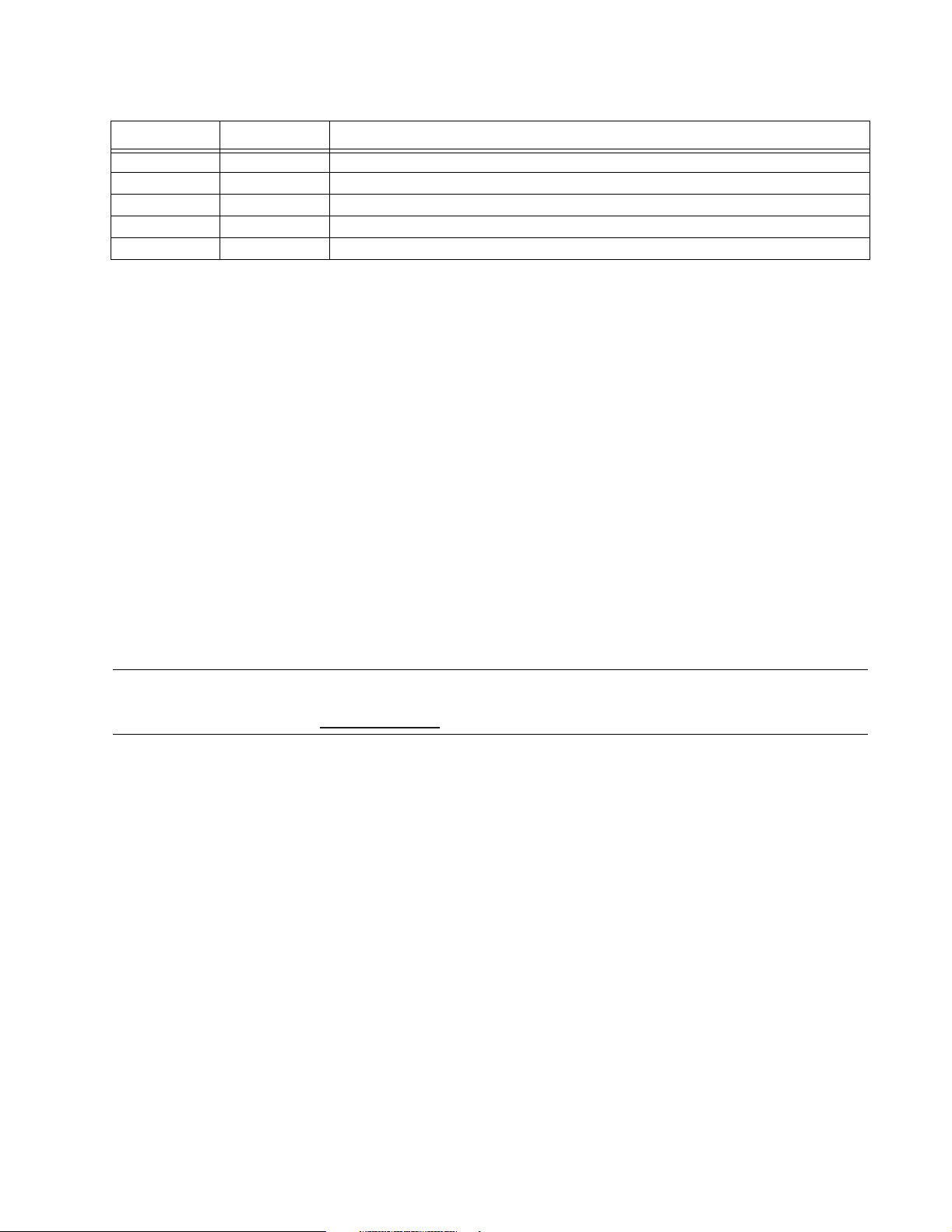

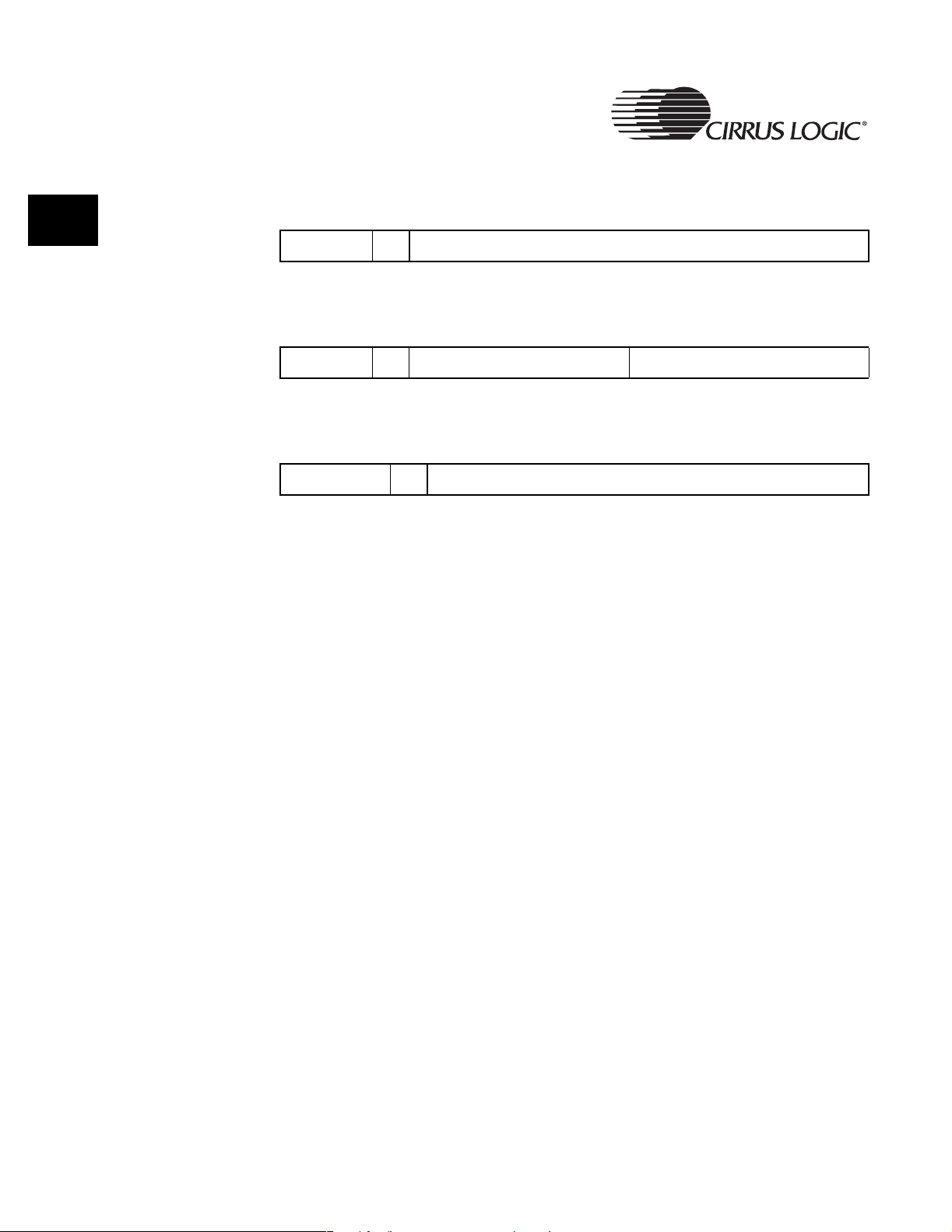

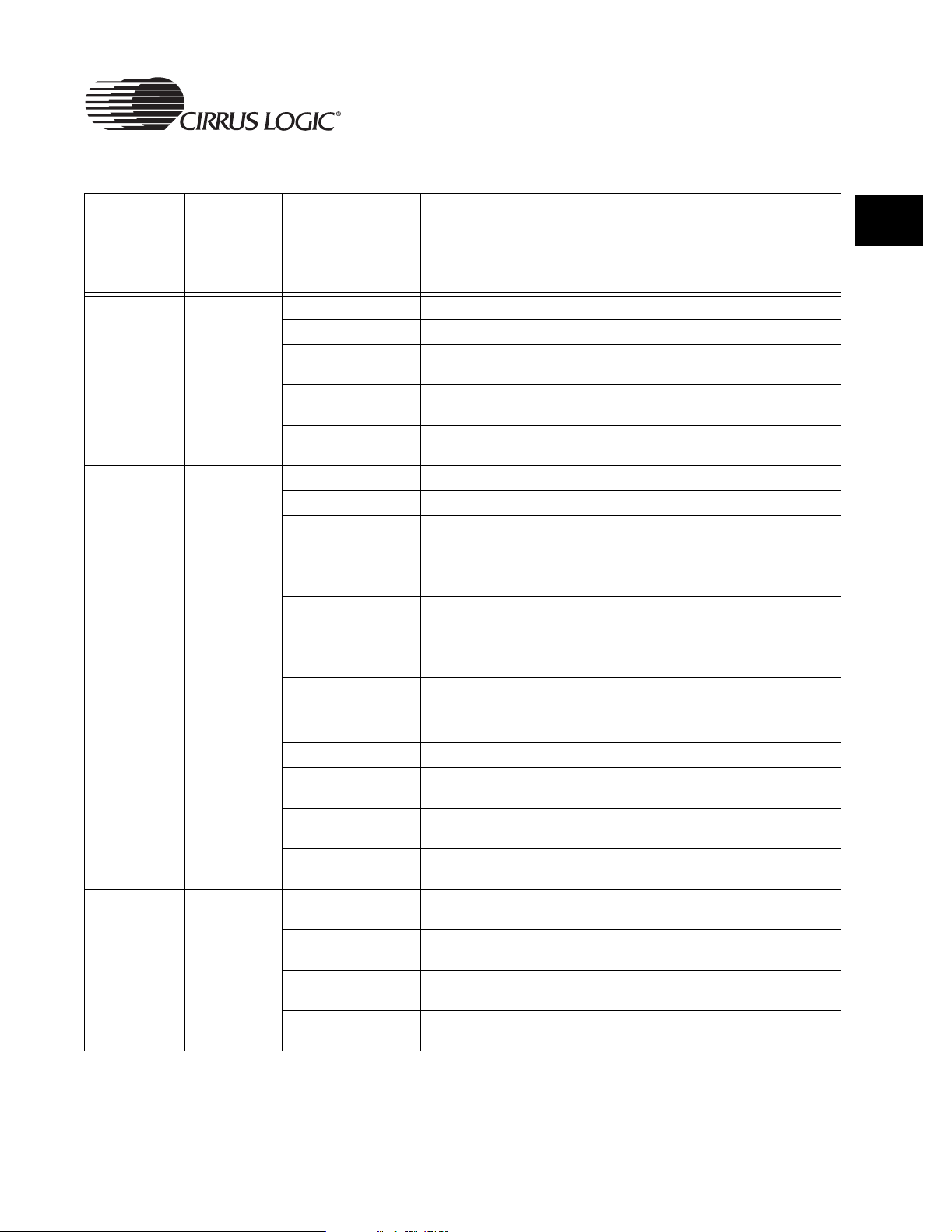

Subject Matter Location

AC’97 Chapter 22 - AC’97 Controller

ARM920T Processor

Boot ROM, Hardware and Software Chapter 3 - Boot ROM

Booting From SROM or SyncFlash Chapter 12 - SDRAM, SyncROM, and SyncFLASH Controller

Buses - AMBA, AHB, APB

Coprocessor Unit Chapter 2 - MaverickCrunch Coprocessor

DMA Controller Chapter 9 - DMA Controller

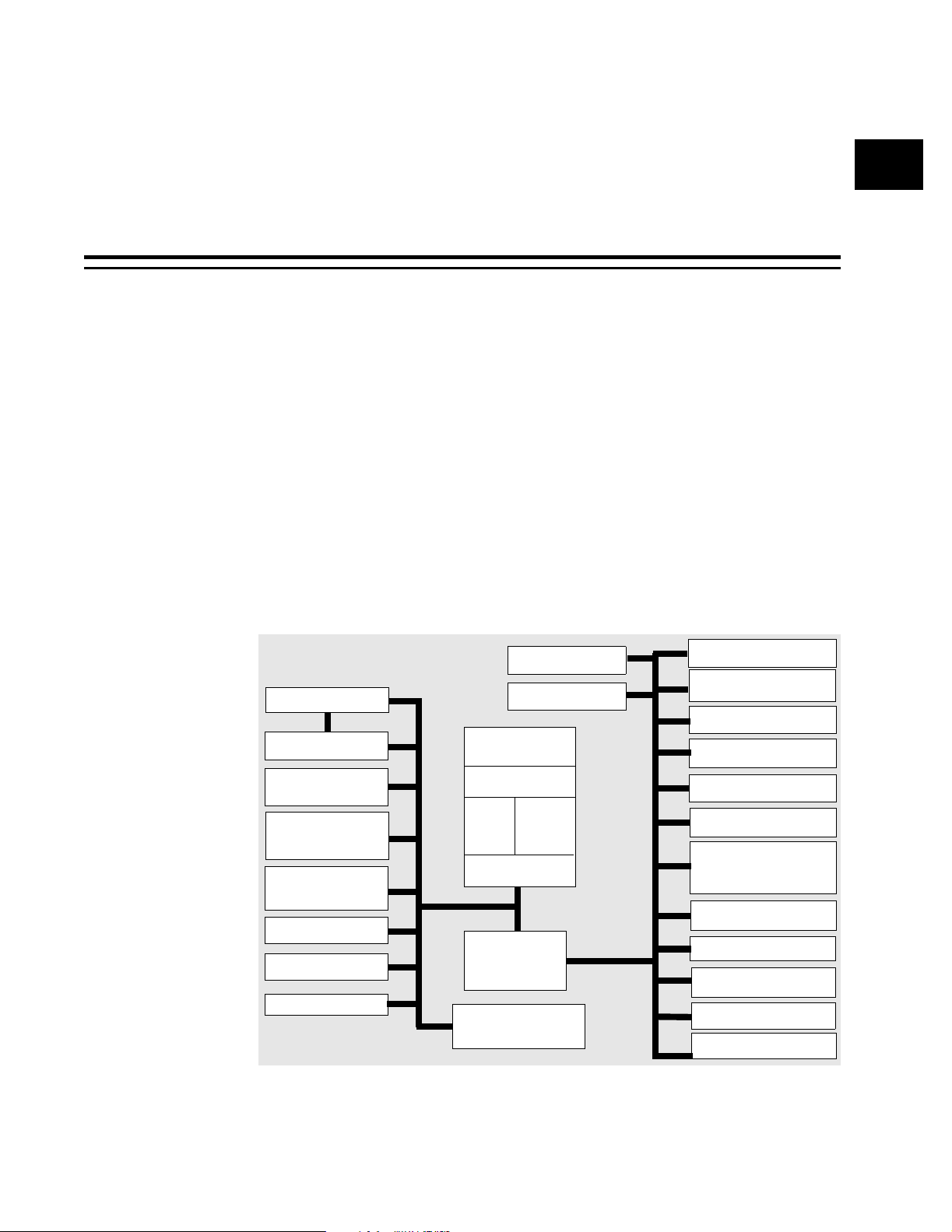

EP9307 Block Diagram

Ethernet Chapter 8 - 1/10/100 Mbps Ethernet LAN Controller

GPIO Chapter 27 - GPIO Interface

Graphics Accelerator Chapter 7 - Graphics Accelerator

HDLC

2

I

S Chapter 21 - I2S Controller

Infra-Red Interface Chapter 17 - IrDA

Interrupt Registers Chapter 5 - Vectored Interrupt Controller

Interrupts Chapter 5 - Vectored Interrupt Controller

IrDA Chapter 17 - IrDA

Key Pad Matrix Chapter 26 - Keypad Interface

LCD Interface

MAC Chapter 8 - 1/10/100 Mbps Ethernet LAN Controller

Chapter 13 - ARM920T Core and Advanced High-Speed Bus

(AHB)

Chapter 13 - ARM920T Core and Advanced High-Speed Bus

(AHB)

Chapter 13 - ARM920T Core and Advanced High-Speed Bus

(AHB)

Chapter 14 - UART1 With HDLC and Modem Control Signals

Chapter 16 - UART3 With HDLC Encoder

Chapter 6 - Raster Engine With Analog/LCD Integrated Timing

and Interface

Preface

EP9307 User’s Manual - DS667UM1 3

Copyright 2004 Cirrus Logic

Page 4

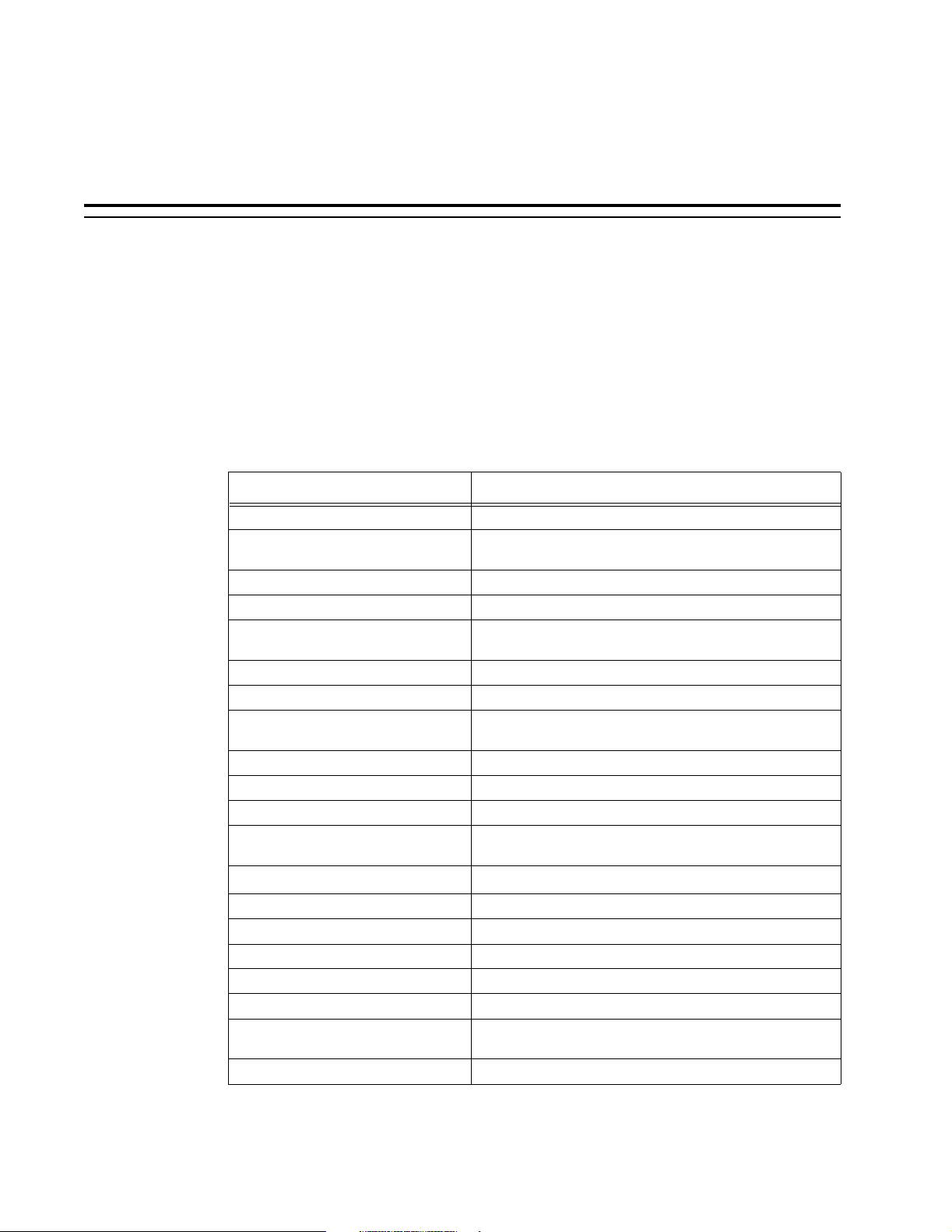

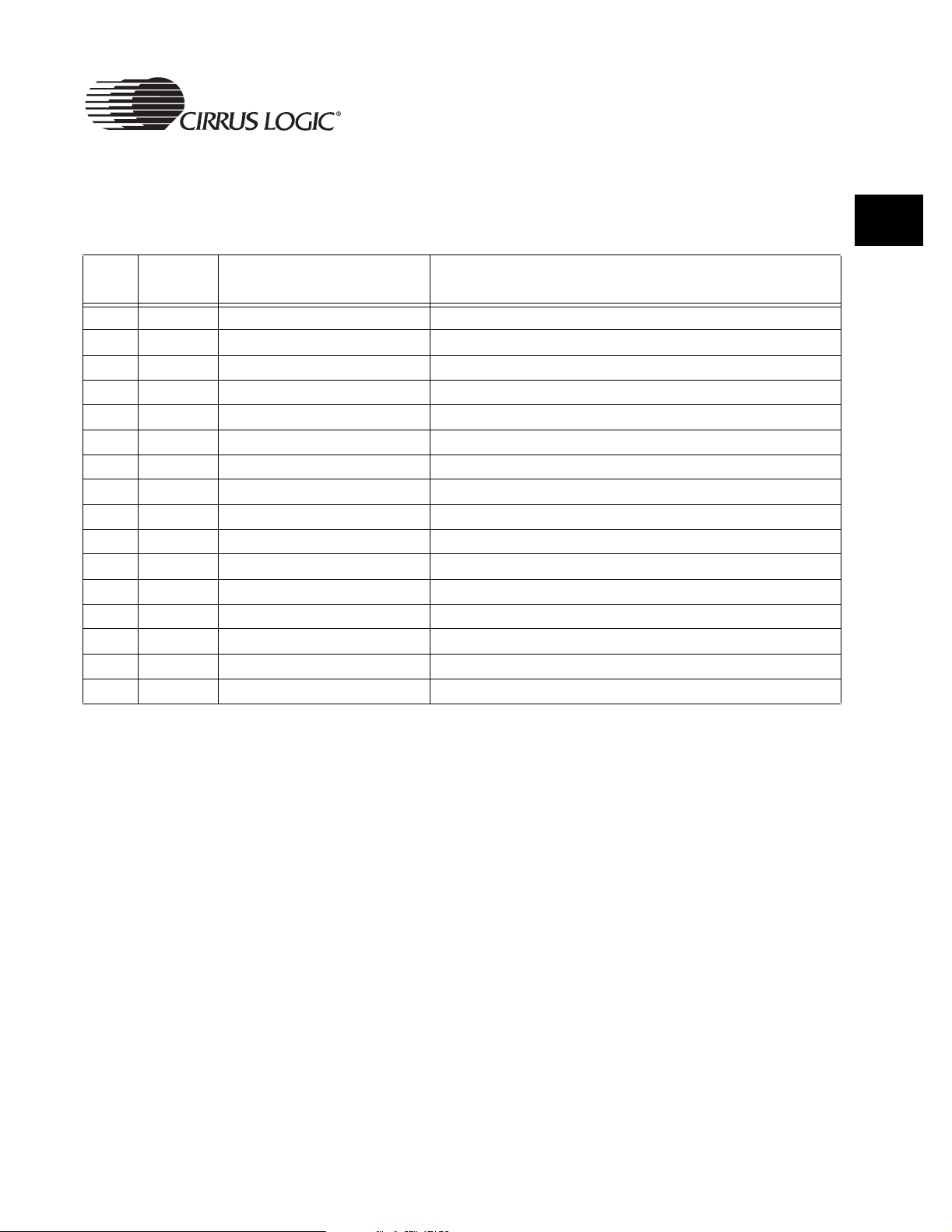

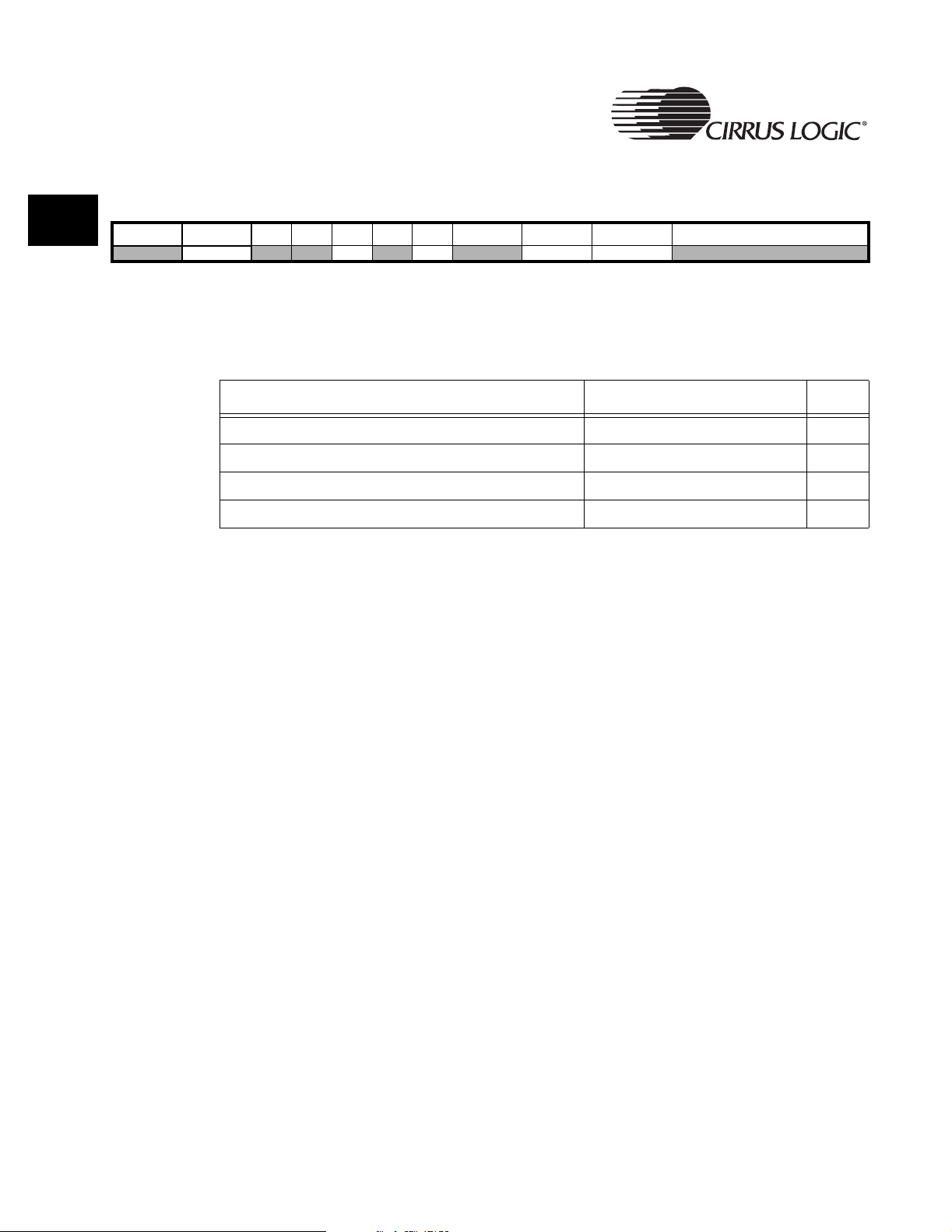

Subject Matter Location

Memory Map

Modem Chapter 14 - UART1 With HDLC and Modem Control Signals

Power Management Chapter 4 - System Controller

Programming Clocks Chapter 4 - System Controller

PWM Chapter 24 - Pulse Width Modulator

Raster Graphics

Real Time Clock Chapter 20 - Real Time Clock With Software Trim

Register List Chapter 1 - Introduction

RTC Chapter 20 - Real Time Clock With Software Trim

SDRAM Chapter 12 - SDRAM, SyncROM, and SyncFLASH Controller

Security Chapter 28 - Security

SMC Chapter 11 - Static Memory Controller

SSP Chapter 23 - Synchronous Serial Port

Static Memory Controller Chapter 11 - Static Memory Controller

System Configuration Chapter 4 - System Controller

System Registers Chapter 4 - System Controller

Timers Chapter 18 - Timers

Touch Screen Chapter 25 - Analog Touch Screen Interface

UART

USB Chapter 10 - Universal Serial Bus Host Controller

Vectored Interrupt Registers Chapter 5 - Vectored Interrupt Controller

Vectored Interrupts Chapter 5 - Vectored Interrupt Controller

Watchdog Timer Chapter 19 - Watchdog Timer

Chapter 13 - ARM920T Core and Advanced High-Speed Bus

(AHB)

Chapter 6 - Raster Engine With Analog/LCD Integrated Timing

and Interface

Chapter 14 - UART1 With HDLC and Modem Control Signals

Chapter 15 - UART2

Chapter 16 - UART3 With HDLC Encoder

Related Documents from Cirrus Logic

1. EP9307 Data Sheet, Document Number - DS667

Reference Documents

1. ARM920T Technical Reference Manual

2. AMBA Specification (Rev. 2.0), ARM IHI 0011A, ARM Limited.

3. AHB Example AMBA System (Addendum 01), ARM DDI 0170A, ARM

Limited.

4 EP9307 User’s Manual - DS667UM1

Copyright 2004 Cirrus Logic

Page 5

4. The coprocessor instruction assembler notation can be referenced from

ARM programming manuals or the Quick Reference Card, document

number ARM QRC 0001D.

5. The MAC engine is compliant with the requirements of ISO/IEC 8802-3

(1993), Sections 3 and 4.

6. OpenHCI - Open Host Controller interface Specification for USB, Release

1.0a; Compaq, Microsoft, National Semiconductor.

7. ARM Coprocessor Quick Reference Card, document number ARM QRC

0001D.

8. Information Technology, AT Attachment with Packet Interface - 5

(ATA/ATAPI-5) ANSI NCITS document T13 1321D, Revision 3, 29

February 2000

9. OpenHCI - Open Host Controller Interface Specification for USB,

Release: 1.0a, Released - 09/14/99 2:33 PM

10. ARM PrimeCell PL190-Rel1v1 Revision 1.7 Technical Reference Manual

DDI0181C

11. Audio Codec ‘97, Revision 2.3, April 2002, Intel Corporation

Notational Conventions

This document uses the following conventions:

• Internal and external Signal Names, and Pin Names use mixed upper and

lower case alphanumeric, and are shown in bold font: RDLED.

• Register Bit Fields are named using upper and lower case alphanumeric:

that is, SBOOT, LCSn1.

• Registers are named using mixed upper and lower case alphanumeric:

that is, SysCfg or PxDDR. (Where there are multiple registers with similar

names, a lower case “x” is used as a place holder. For example, in the

PxDDR registers, x represents a letter between A and H, indicating the

specific port being discussed.)

Caution: In the Internal Register Map in Table 13-7 on page 18-491, some

memory locations are listed as Reserved. These memory

locations should not be used. Reading from these memory

locations will yield invalid data. Writing to these memory locations

may cause unpredictable results.

(An example register description is shown below. This description is used for

the following examples.)

A specific bit may be specified in one of two ways:

EP9307 User’s Manual - DS667UM1 5

Copyright 2004 Cirrus Logic

Page 6

By

register name[bit number]: SysCfg[29]

or by

register name.bit field[bit number]: SysCfg.REV[1]

Both of these representations refer to the same bit.

The following:

,

SysCfg[8]

, or

SysCfg.SBOOT

also refer to the same bit.

Hexidecimal numbers are referred to as

Binary numbers are referred to as

0000_0000b

0x0000_0000

.

.

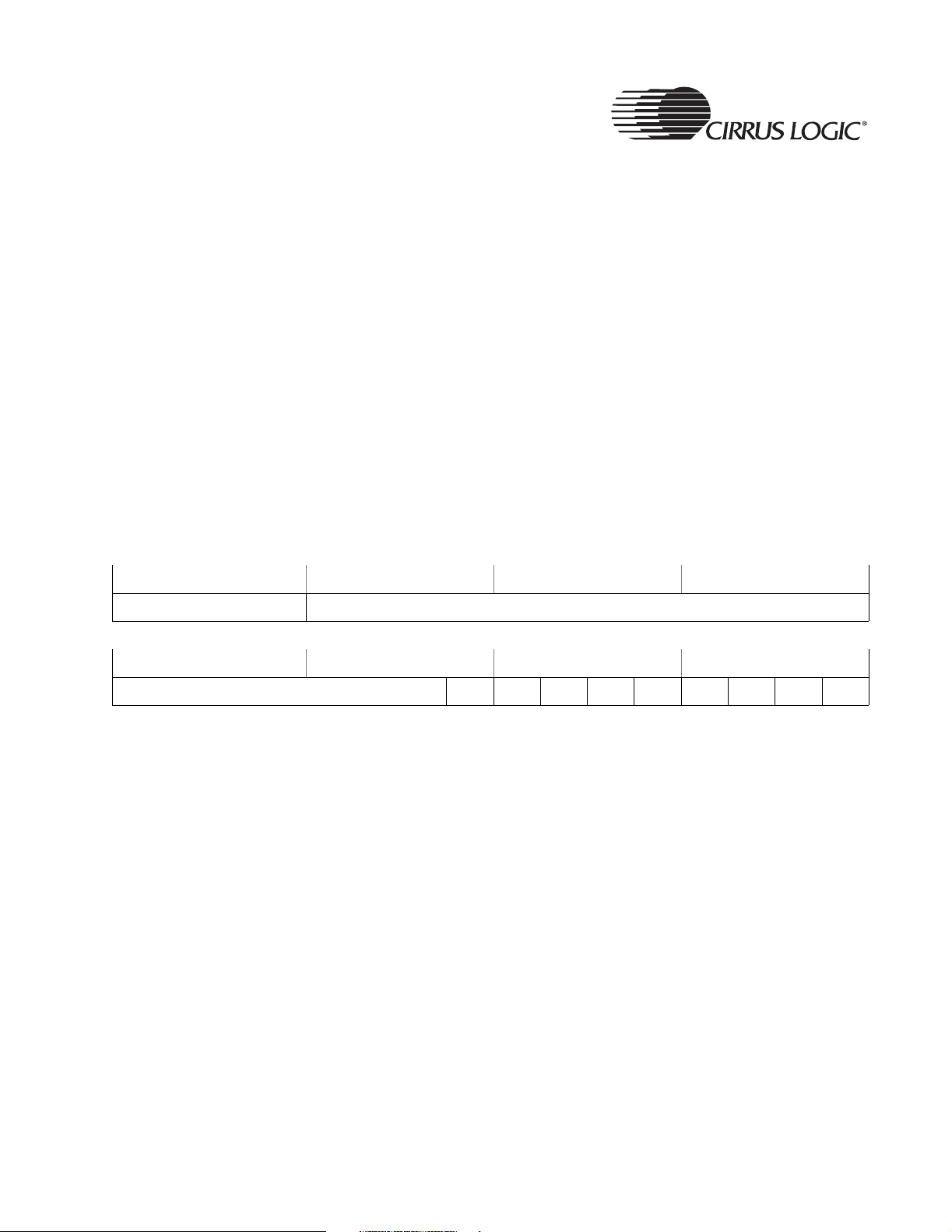

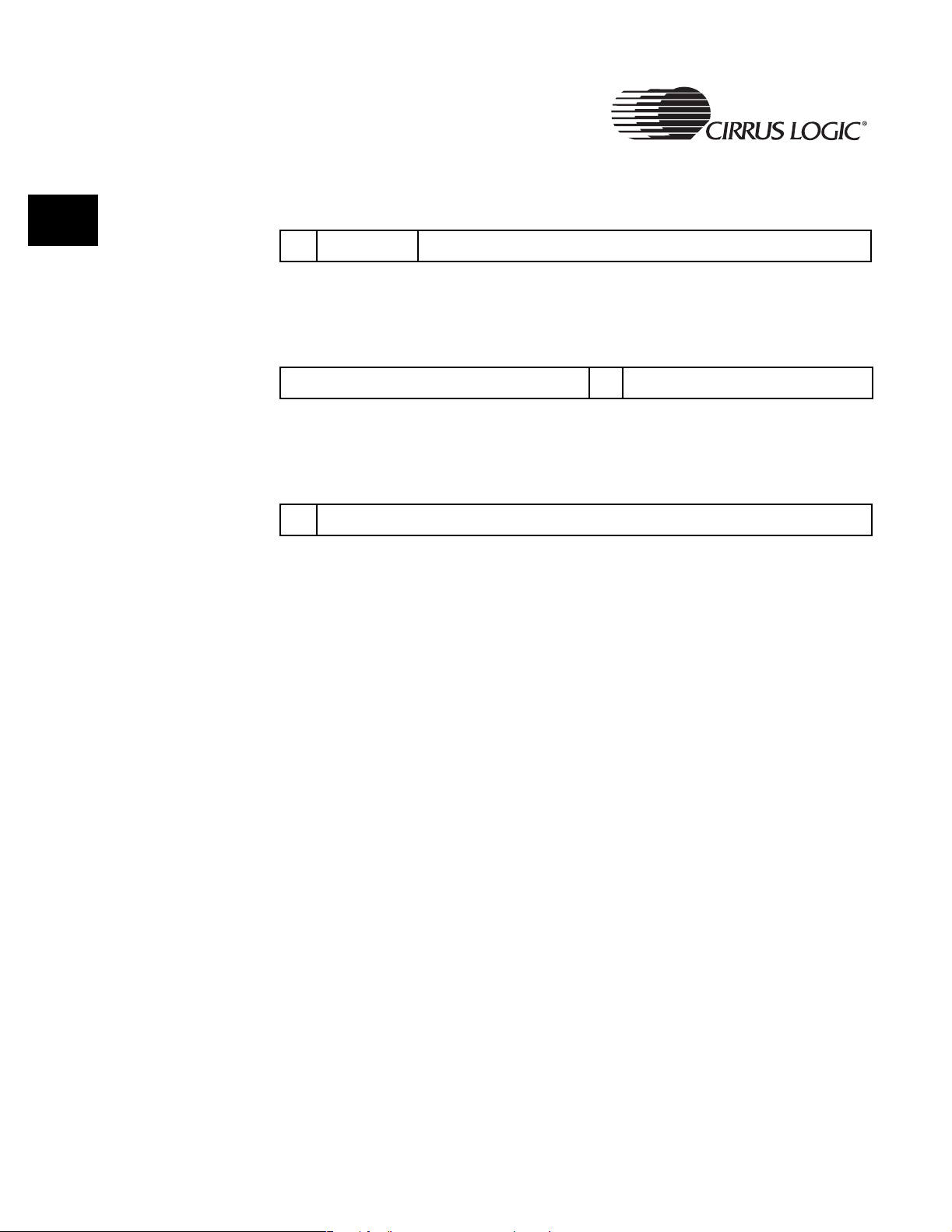

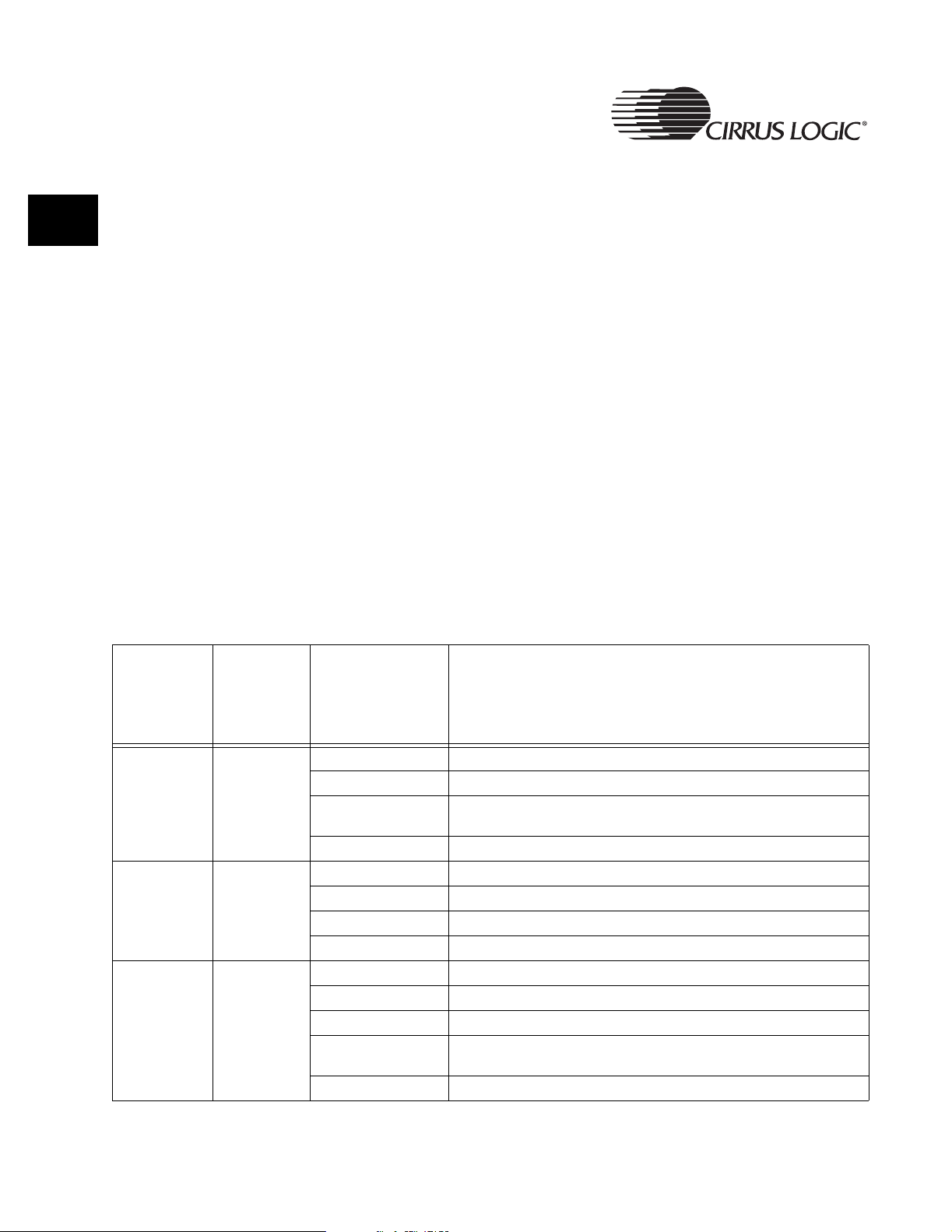

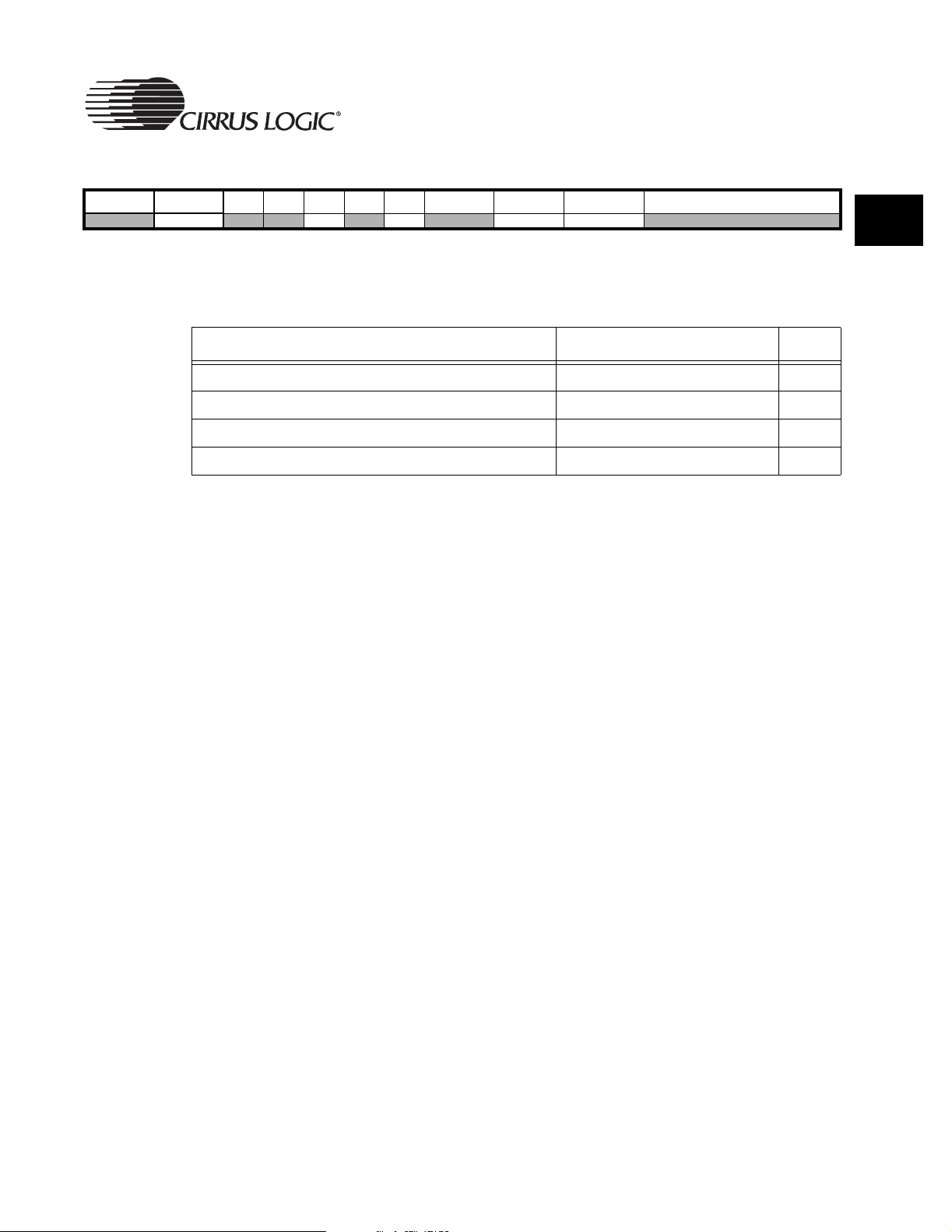

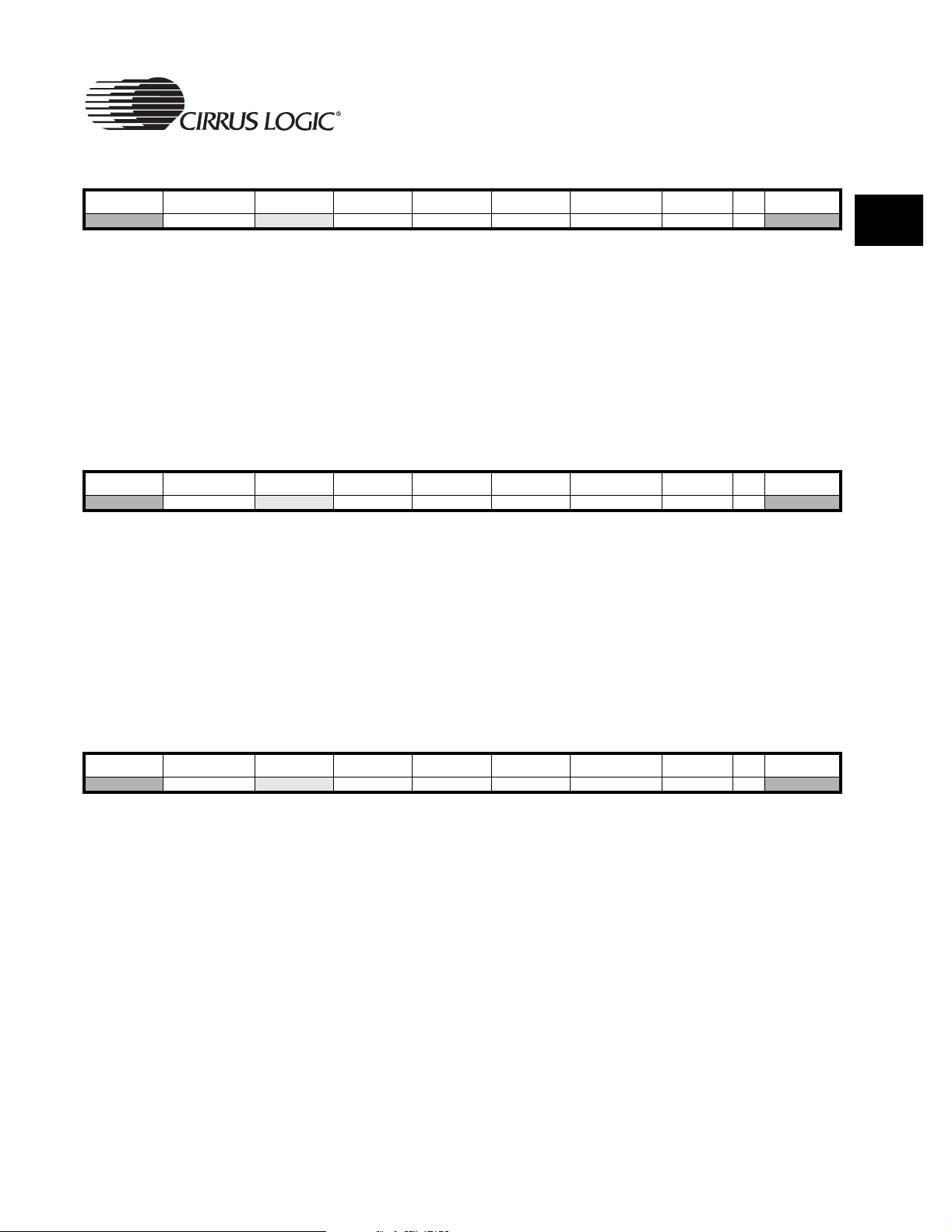

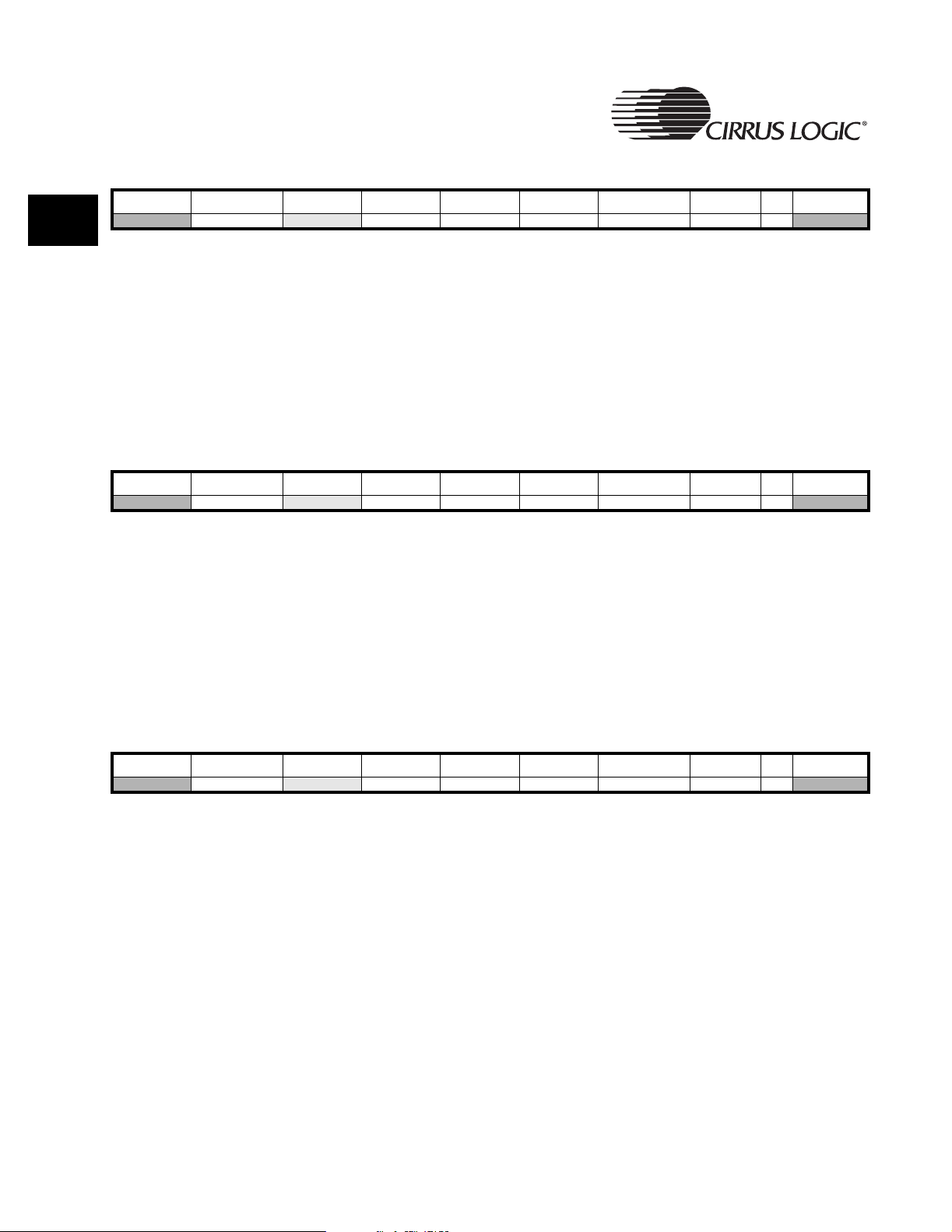

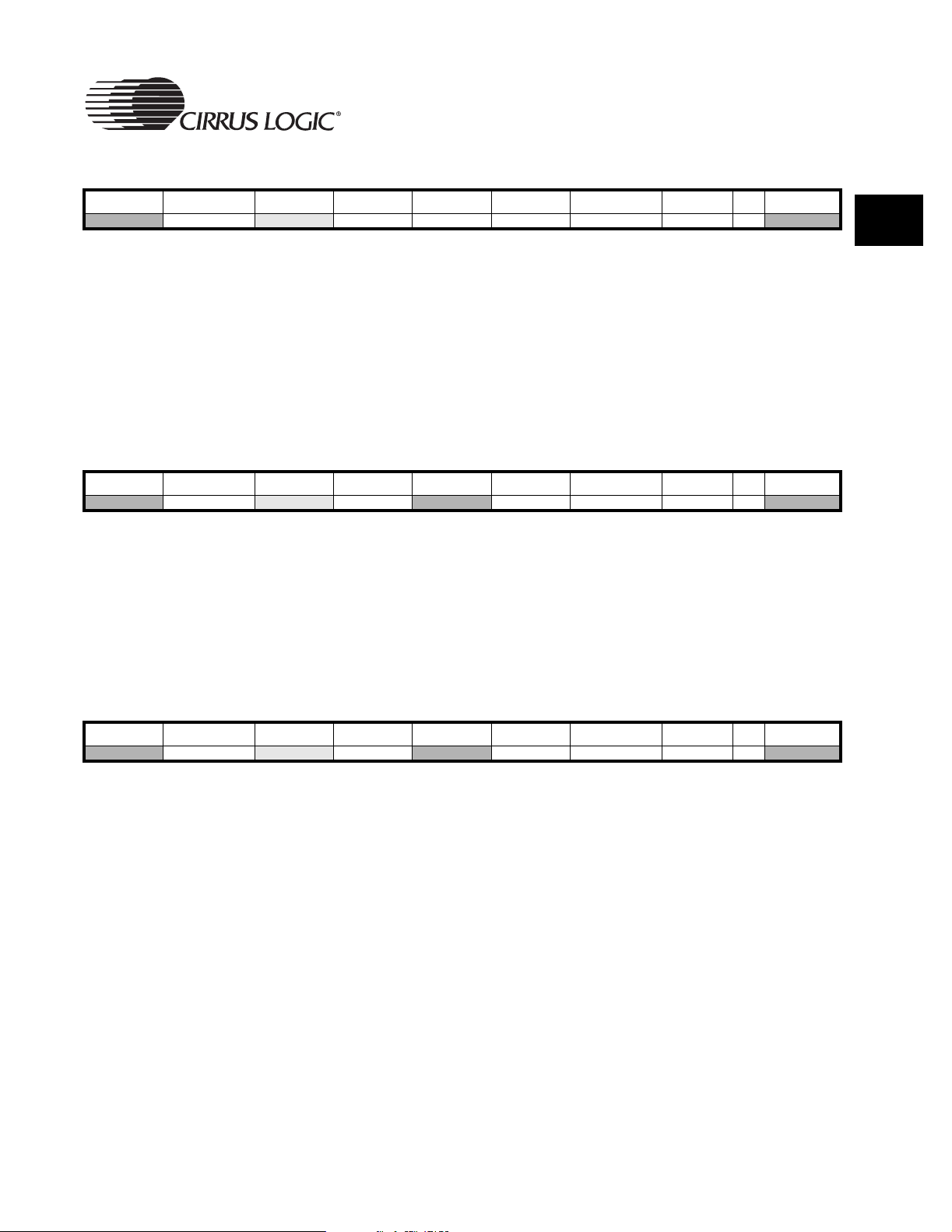

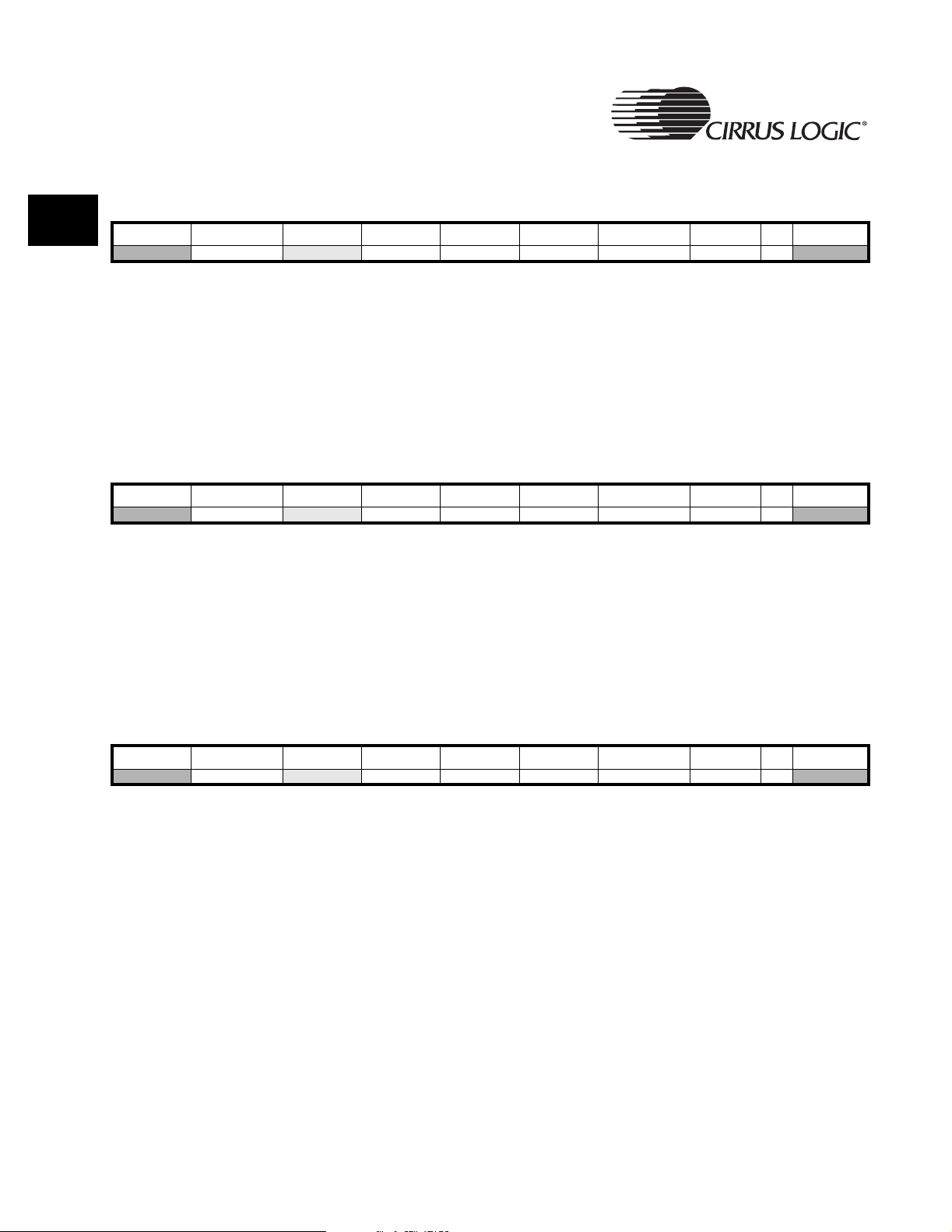

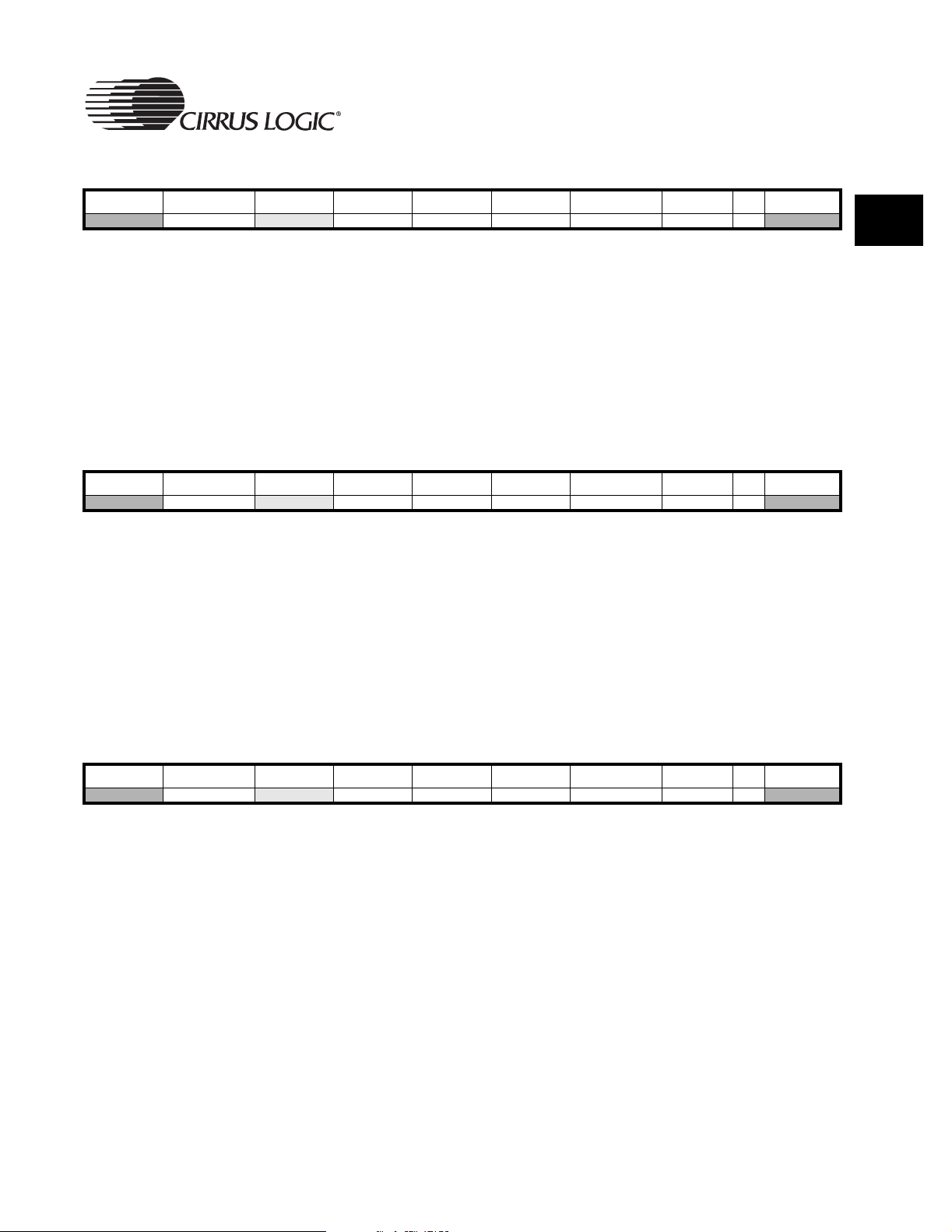

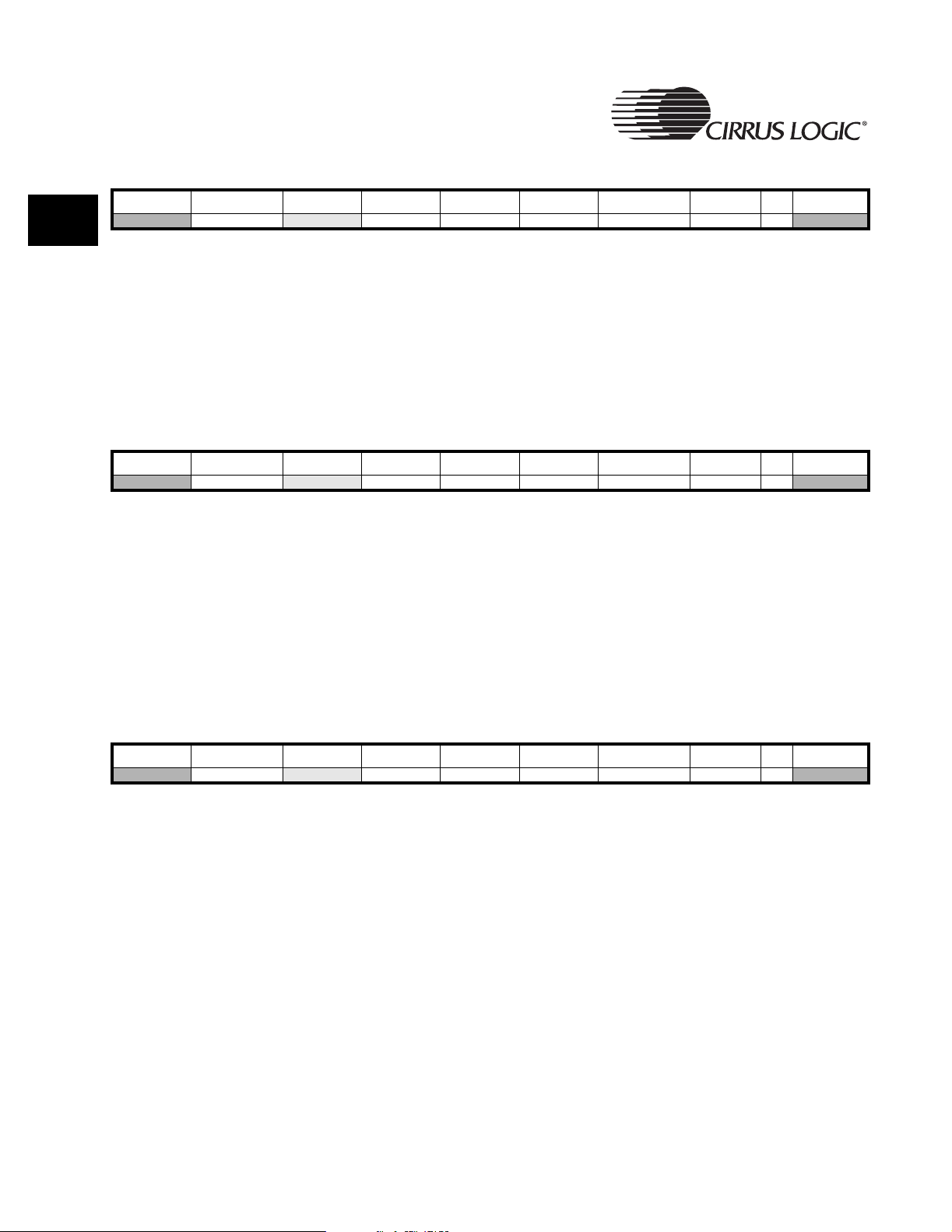

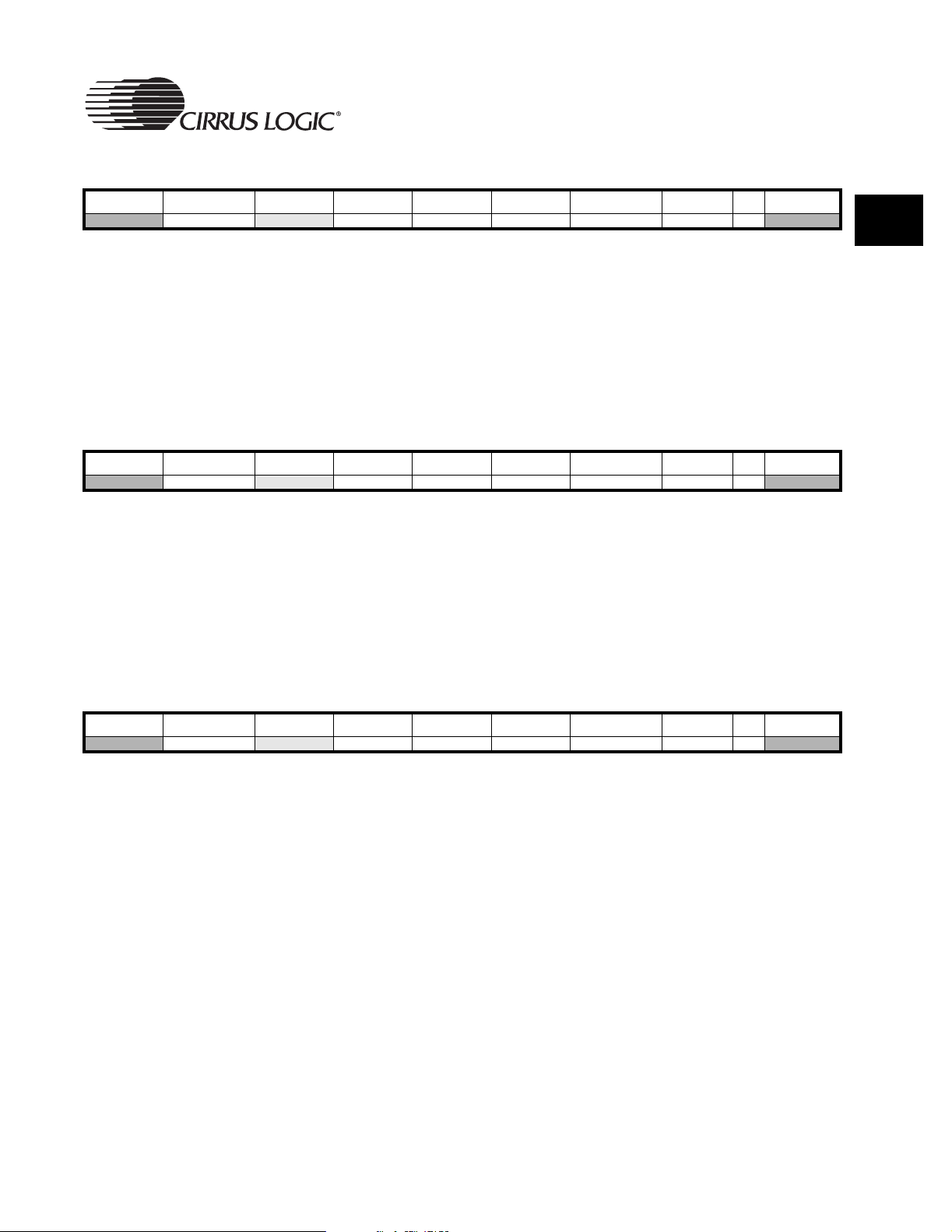

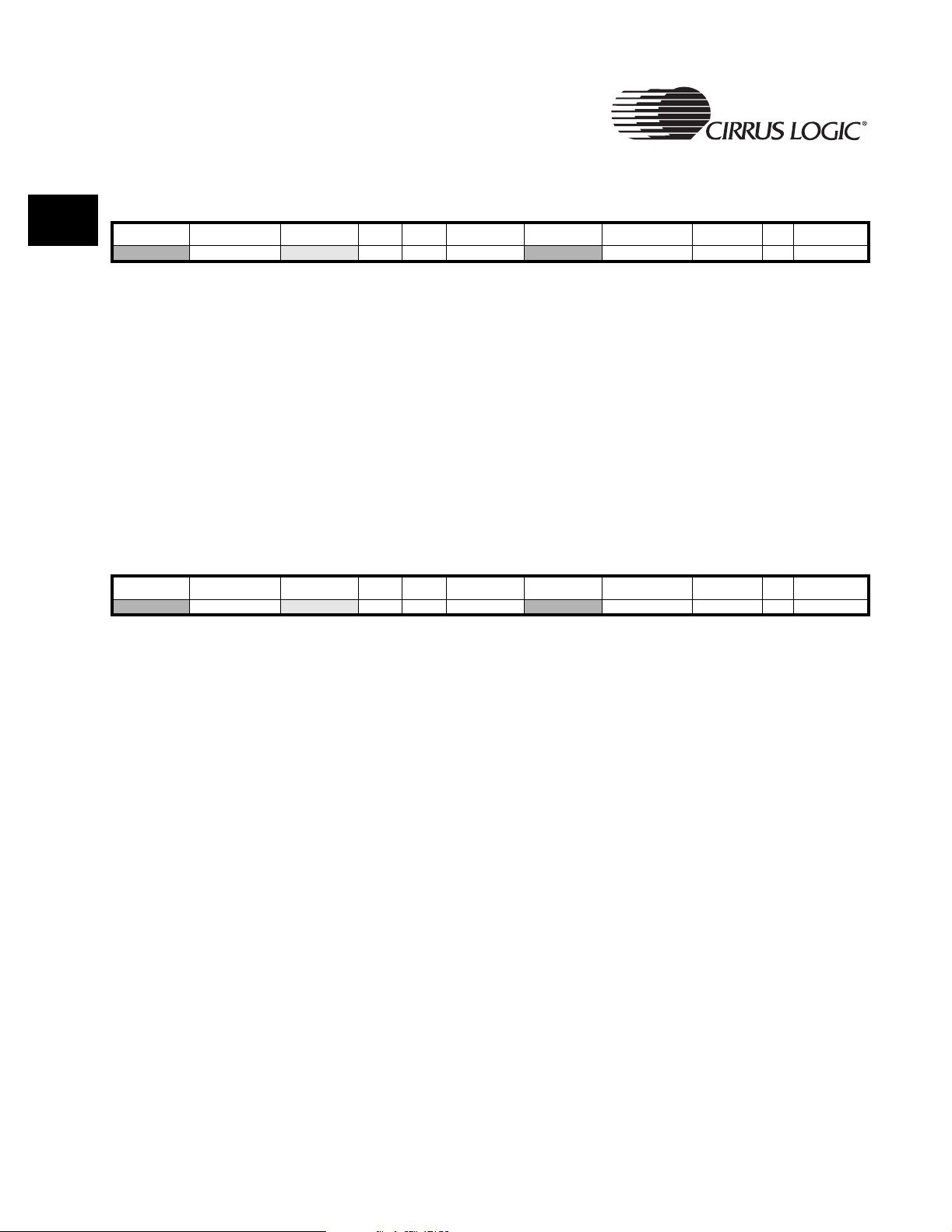

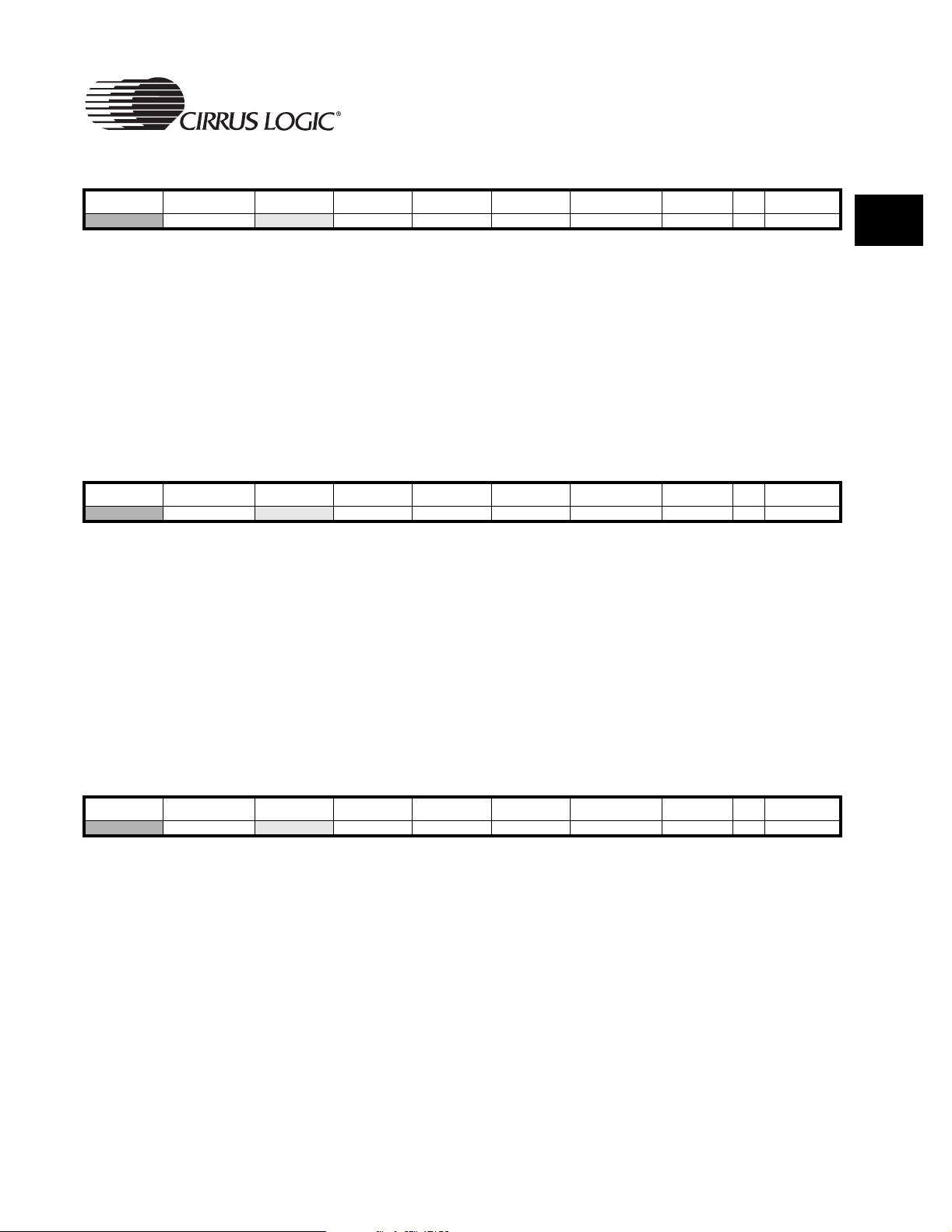

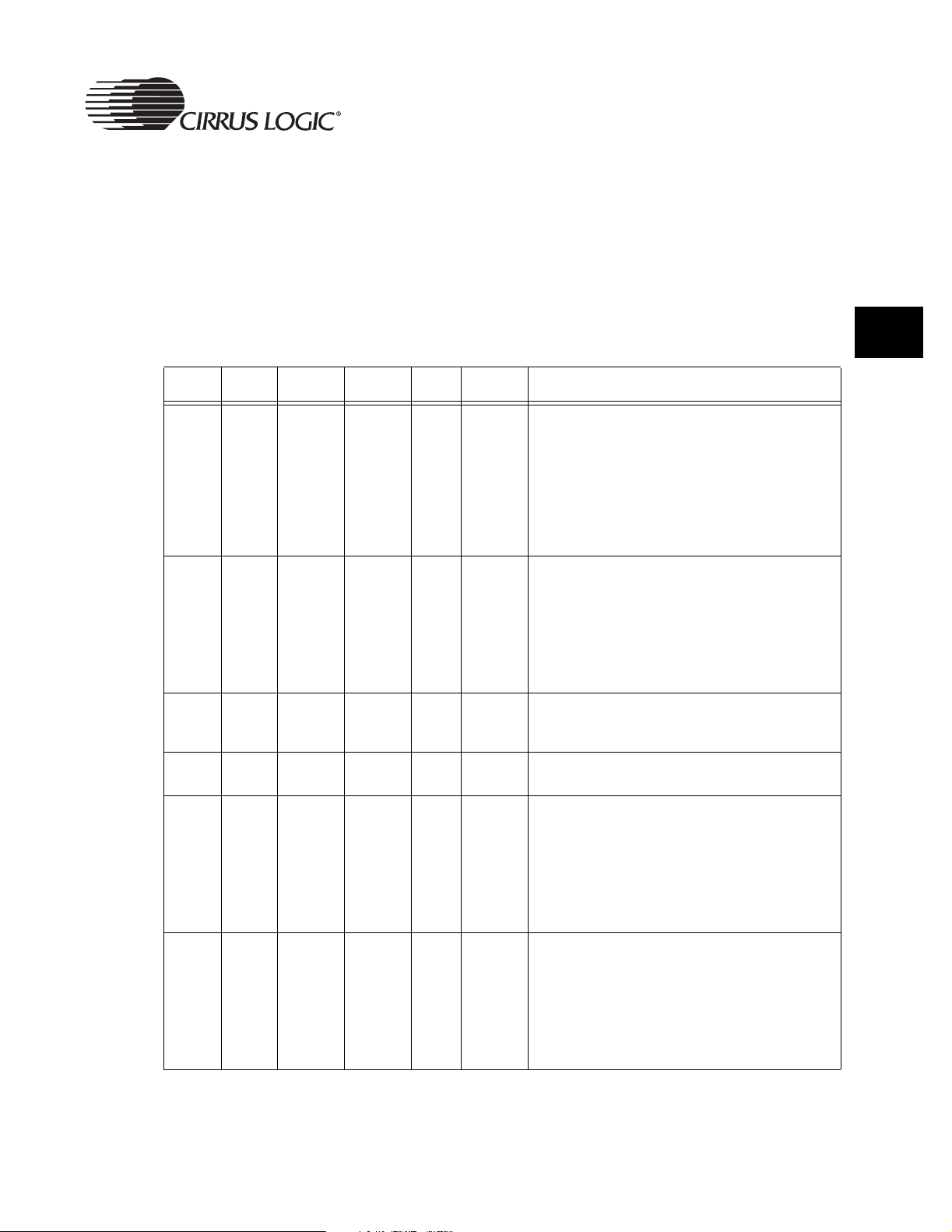

Register Example

Note: This is only an example. For actual SysCfg register information, see “SysCfg” on

page 128.

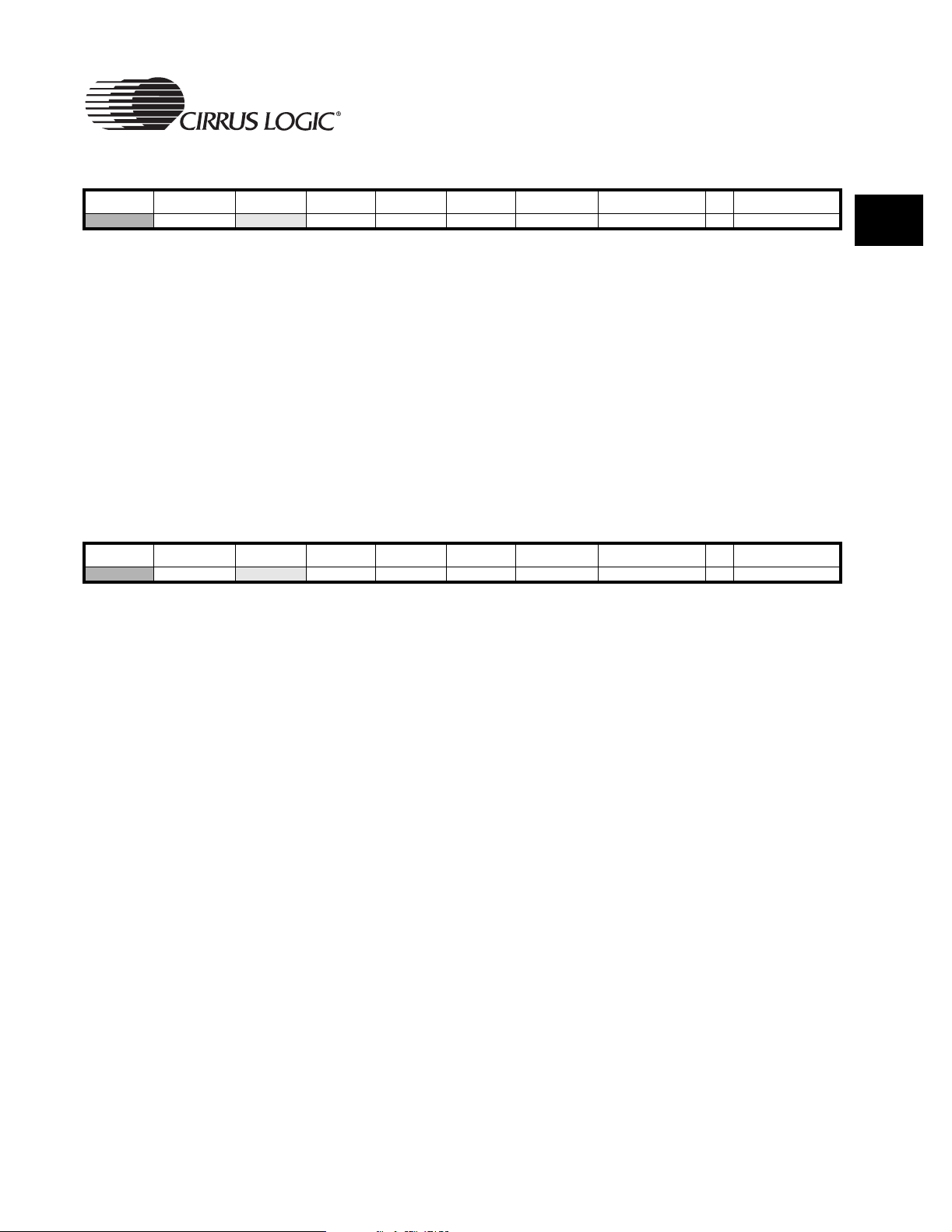

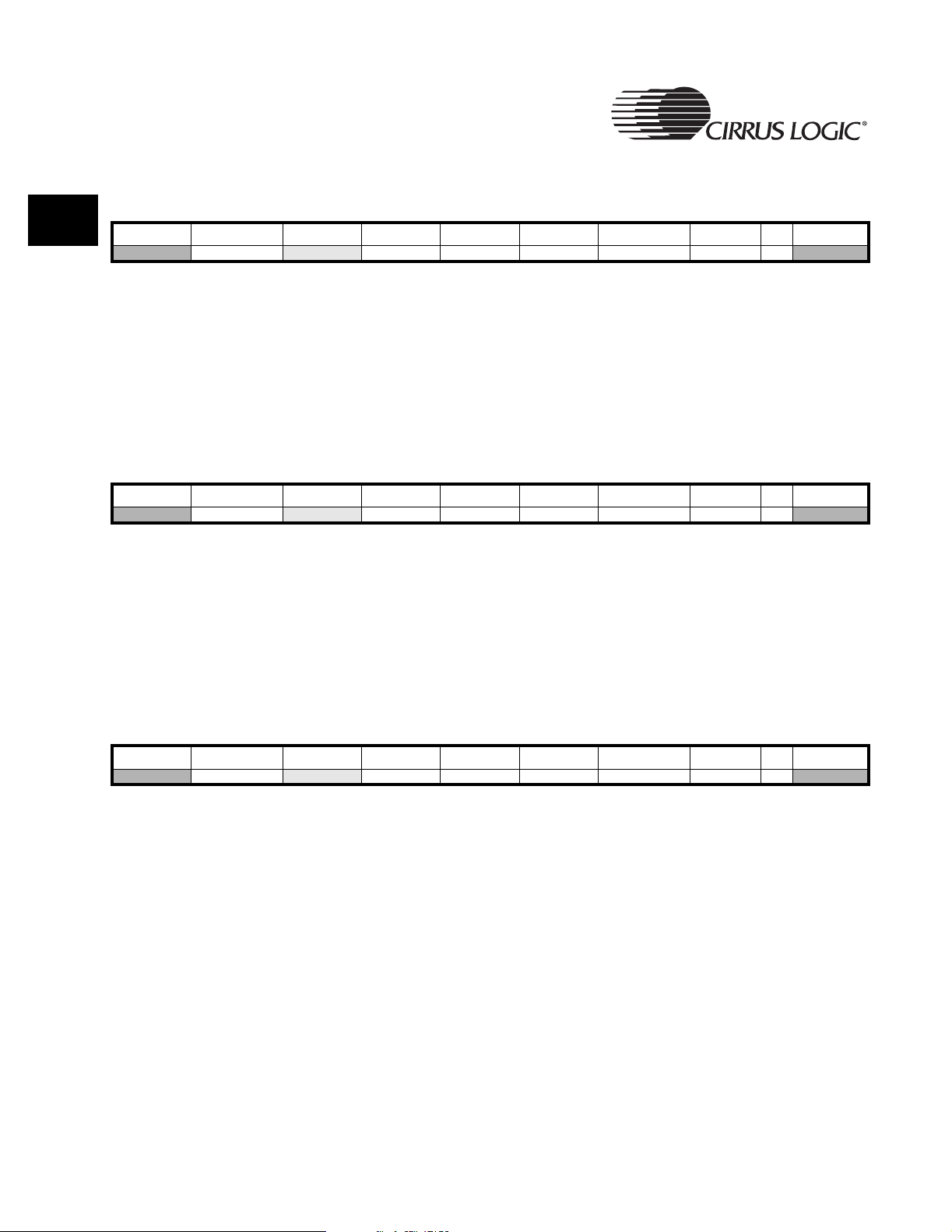

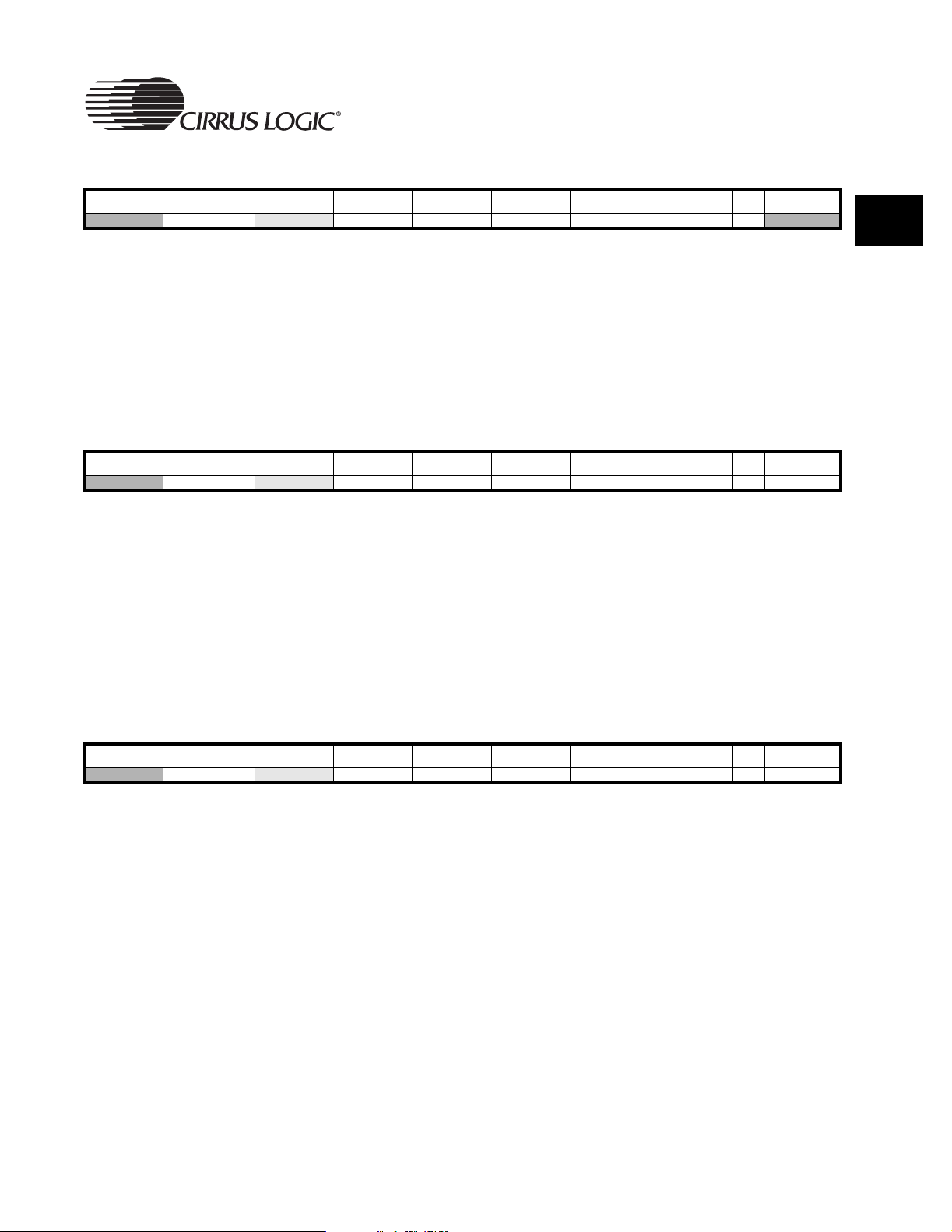

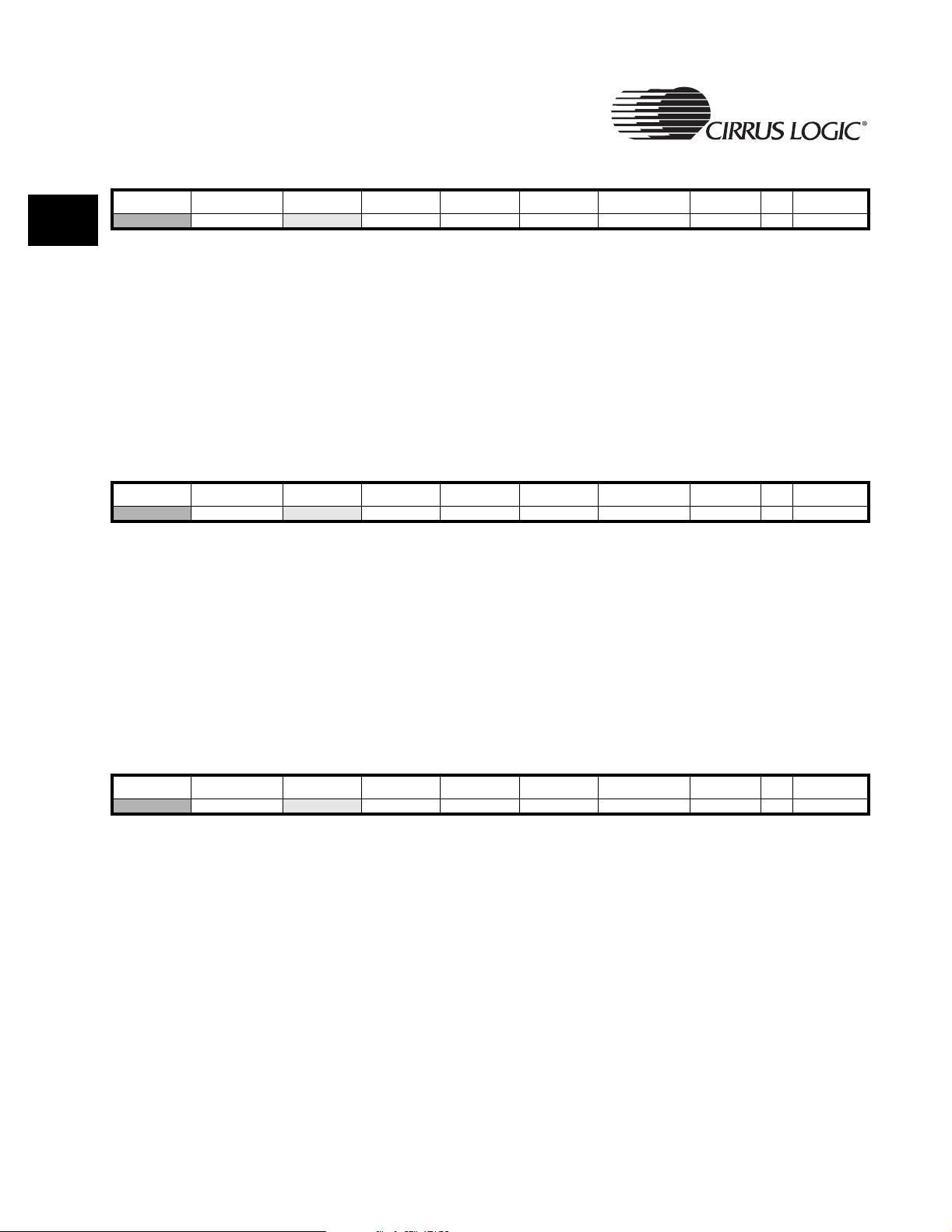

SysCfg

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

REV RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD SBOOT LCSn7 LCSn6 LASDO LEEDA LEECLK RSVD LCSn2 LCSn1

Address:

0x8093_009C - Read/Write, Software locked

Default:

0x0000_0000

Definition:

System Configuration Register. Provides various system configuration

options.

Bit Descriptions:

RSVD: Reserved. Unknown During Read.

REV: Revision, reads chip Version number: 0 - Rev A, 1 - Rev B,

2 - Rev C, 3 - Rev D.

SBOOT: Serial Boot Flag. This bit is read-only.

1 hardware detected Serial Boot selection,

0 hardware detected Normal Boot.

6 EP9307 User’s Manual - DS667UM1

Copyright 2004 Cirrus Logic

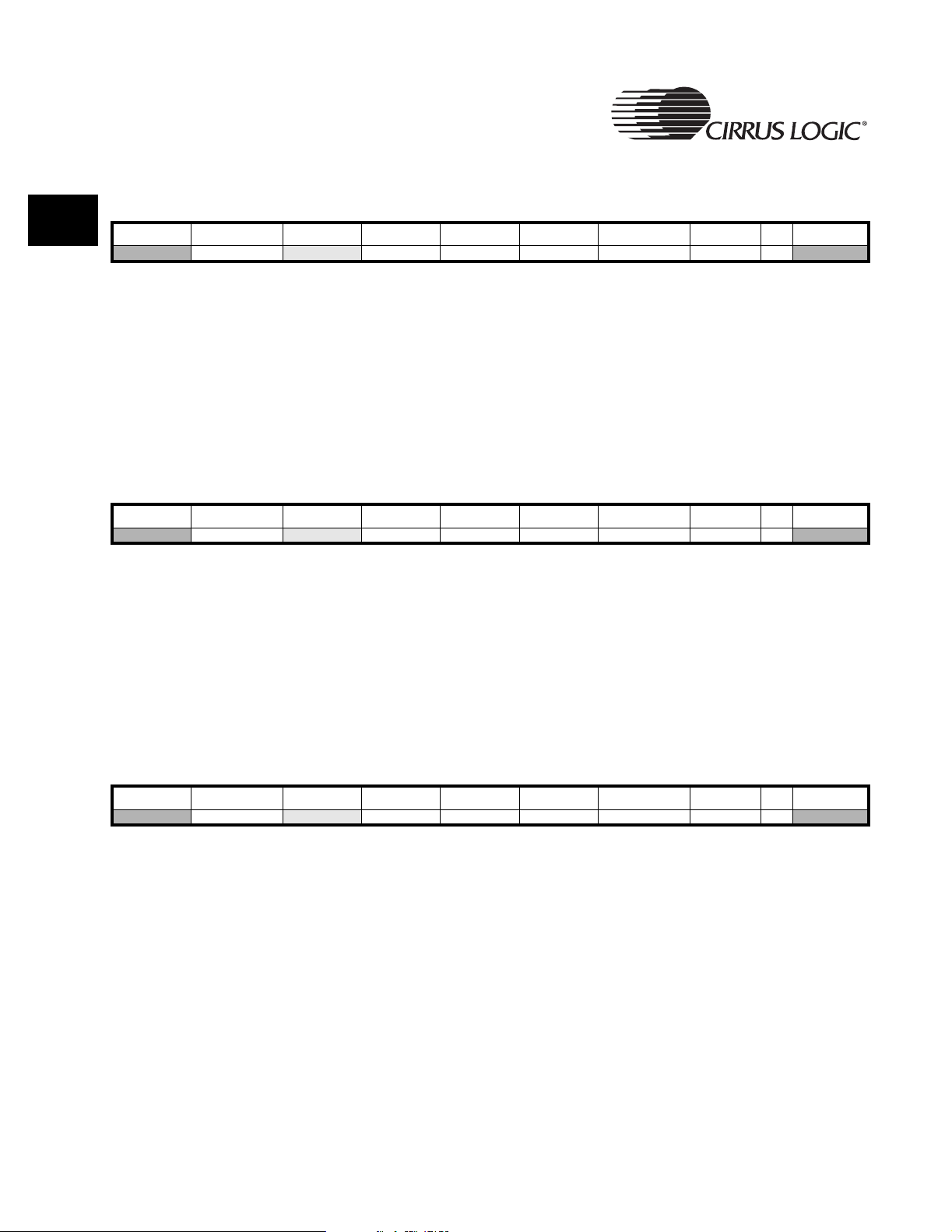

Page 7

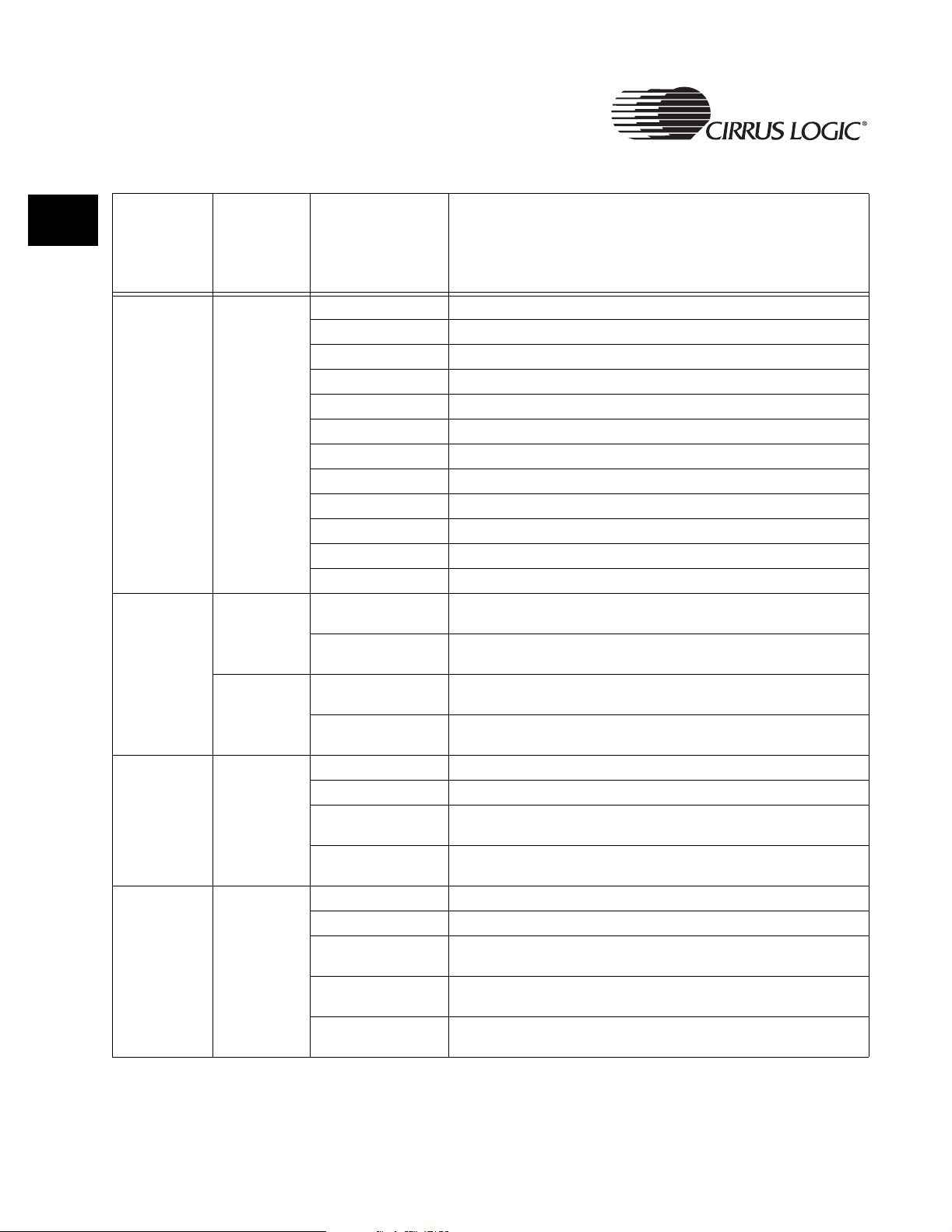

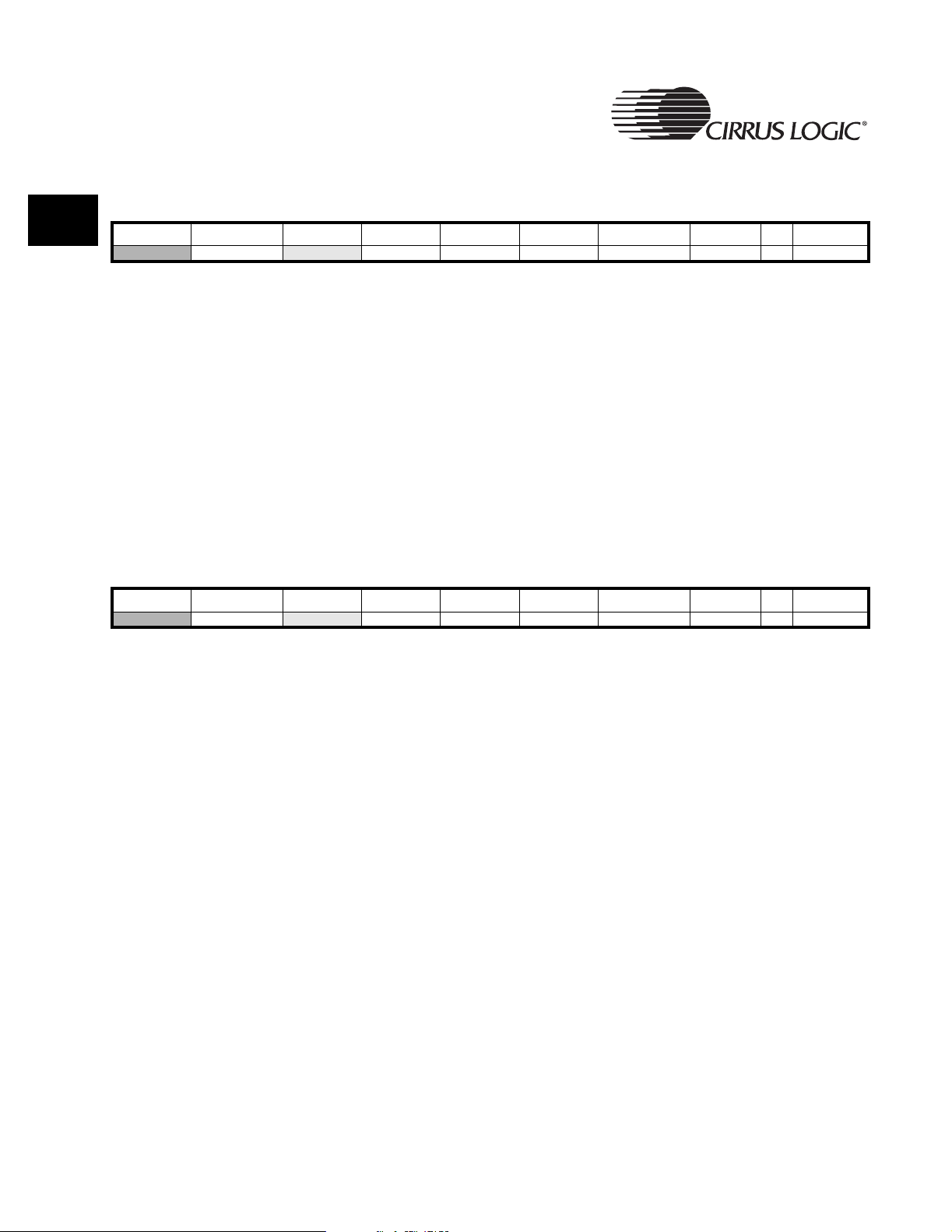

LCSn7, LCSn6: Latched version of CSn7 and CSn6 respectively. These

are used to define the external bus width for the boot code

boot.

LASDO: Latched version of ASDO pin. Used to select synchronous

versus asynchronous boot device.

LEEDA: Latched version of EEDAT pin.

LEECLK: Define Internal or external boot:

1 Internal

0 External

LCSn2, LCSn1: Define Watchdog startup action:

0 0 Watchdog disabled, Reset duration disabled

0 1 Watchdog disabled, Reset duration active

1 0 Watchdog active, Reset duration disabled

1 1 Watchdog active, Reset duration active

EP9307 User’s Manual - DS667UM1 7

Copyright 2004 Cirrus Logic

Page 8

This page intentionally blank.

8 EP9307 User’s Manual - DS667UM1

Copyright 2004 Cirrus Logic

Page 9

Table of Contents

Preface............................................................................................................. 3

About the EP9307 User’s Guide ............................................................................................................ 3

How to Use this Guide ...........................................................................................................................3

Related Documents from Cirrus Logic ...................................................................................................4

Reference Documents ...........................................................................................................................4

Notational Conventions ..........................................................................................................................5

Chapter 1 Introduction ............................................................................... 29

1.1 Introduction ...................................................................................................................................29

1.2 EP9307 Features ..........................................................................................................................30

1.3 EP9307 Applications .....................................................................................................................31

1.4 Overview of EP9307 Features ...................................................................................................... 32

1.4.1 High-Performance ARM920T Processor Core ....................................................................32

1.4.2 MaverickCrunch™ Coprocessor for Ultra-Fast Math Processing........................................32

1.4.3 MaverickKey™ Unique ID Secures Digital Content and OEM Designs ..............................32

1.4.4 Integrated Three-port USB 2.0 Full Speed Host with Transceivers.....................................33

1.4.5 Integrated Ethernet MAC Reduces BOM Costs ..................................................................33

1.4.6 8x8 Keypad Interface Reduces BOM Costs ........................................................................33

1.4.7 Multiple Booting Mechanisms Increase Flexibility ...............................................................33

1.4.8 Abundant General Purpose I/Os Build Flexible Systems ....................................................34

1.4.9 General-Purpose Memory Interface (SDRAM, SRAM, ROM and FLASH) .........................34

1.4.10 12-Bit Analog-to-Digital Converter (ADC) Provides an Integrated

Touch-Screen Interface or General ADC Functionality..............................................34

1.4.11 Graphics Accelerator .........................................................................................................34

Chapter 2 MaverickCrunch Coprocessor ................................................. 35

2.1 Introduction ...................................................................................................................................35

2.1.1 Features ..............................................................................................................................35

2.1.2 Operational Overview..........................................................................................................35

2.1.3 Pipelines and Latency .........................................................................................................37

2.1.4 Data Registers.....................................................................................................................37

2.1.5 Integer Saturation Arithmetic ...............................................................................................38

2.1.6 Comparisons .......................................................................................................................40

2.2 Programming Examples................................................................................................................41

2.2.1 Example 1............................................................................................................................41

2.2.1.1 Setup Code ................................................................................................................42

2.2.1.2 C Code.......................................................................................................................42

2.2.1.3 Accessing MaverickCrunch with ARM Coprocessor Instructions...............................42

2.2.1.4 MaverickCrunch Assembly Language Instructions ....................................................42

2.2.2 Example 2............................................................................................................................42

2.2.2.1 C Code.......................................................................................................................43

2.2.2.2 MaverickCrunch Assembly Language Instructions ....................................................43

2.3 DSPSC Register ...........................................................................................................................44

2.4 ARM Coprocessor Instruction Format........................................................................................... 47

2.5 Instruction Set for the MaverickCrunch Coprocessor....................................................................52

2.5.1 Load and Store Instructions.................................................................................................56

2.5.2 Move Instructions ................................................................................................................60

2.5.3 Accumulator and DSPSC Move Instructions .......................................................................64

EP9307 User’s Manual - DS667UM1 9

Copyright 2004 Cirrus Logic

Page 10

2.5.4 Copy and Conversion Instructions ...................................................................................... 68

2.5.5 Shift Instructions.................................................................................................................. 72

2.5.6 Compare Instructions.......................................................................................................... 74

2.5.7 Floating Point Arithmetic Instructions.................................................................................. 76

2.5.8 Integer Arithmetic Instructions............................................................................................. 80

2.5.9 Accumulator Arithmetic Instructions.................................................................................... 84

Chapter 3 Boot ROM ...................................................................................87

3.1 Introduction ................................................................................................................................... 87

3.1.1 Boot ROM Hardware Operational Overview ....................................................................... 87

3.1.1.1 Memory Map.............................................................................................................. 87

3.1.2 Boot ROM Software Operational Overview......................................................................... 87

3.1.2.1 Image Header ............................................................................................................ 88

3.1.2.2 Boot Algorithm ........................................................................................................... 88

3.1.2.3 Flowchart................................................................................................................... 90

3.2 Boot Options................................................................................................................................. 91

3.2.1 UART Boot.......................................................................................................................... 91

3.2.2 SPI Boot.............................................................................................................................. 92

3.2.3 FLASH Boot ........................................................................................................................ 92

3.2.4 SDRAM or SyncFLASH Boot.............................................................................................. 93

3.2.5 Synchronous Memory Operation ........................................................................................ 93

Chapter 4 System Controller .....................................................................95

4.1 Introduction ................................................................................................................................... 95

4.1.1 System Startup.................................................................................................................... 95

4.1.2 System Reset...................................................................................................................... 95

4.1.3 Hardware Configuration Control.......................................................................................... 96

4.1.4 Software System Configuration Options ............................................................................. 98

4.1.5 Clock Control....................................................................................................................... 98

4.1.5.1 Oscillators and Programmable PLLs ......................................................................... 98

4.1.5.2 Bus and Peripheral Clock Generation ....................................................................... 99

4.1.5.3 Steps for Clock Configuration.................................................................................. 103

4.1.6 Power Management .......................................................................................................... 104

4.1.6.1 Clock Gatings ..........................................................................................................104

4.1.6.2 System Power States .............................................................................................. 104

4.1.7 Interrupt Generation .......................................................................................................... 106

4.2 Registers .................................................................................................................................... 108

Chapter 5 Vectored Interrupt Controller ................................................. 131

5.1 Introduction ................................................................................................................................. 131

5.1.1 Interrupt Priority................................................................................................................. 132

5.1.2 Interrupt Descriptions ........................................................................................................ 134

5.2 Registers .................................................................................................................................... 139

Chapter 6 Raster Engine With Analog/LCD Integrated Timing and

Interface ....................................................................................................... 149

6.1 Introduction ................................................................................................................................. 149

6.2 Features ..................................................................................................................................... 151

10 EP9307 User’s Manual - DS667UM1

Copyright 2004 Cirrus Logic

Page 11

6.3 Raster Engine Features Overview ..............................................................................................151

6.3.1 Hardware Blinking .............................................................................................................151

6.3.2 Color Look-Up Tables........................................................................................................152

6.3.3 Grayscale/Color Generation for Monochrome/Passive Low Color Displays ..................... 152

6.3.4 Frame Buffer Organization ................................................................................................152

6.3.5 Frame Buffer Memory Size................................................................................................154

6.3.6 Pulse Width Modulated Brightness....................................................................................154

6.3.7 Hardware Cursor ...............................................................................................................155

6.4 Functional Details........................................................................................................................156

6.4.1 VILOSATI (Video Image Line Output Scanner and Transfer Interface) ............................ 156

6.4.2 Video FIFO ........................................................................................................................ 158

6.4.3 Video Pixel MUX................................................................................................................158

6.4.4 Blink Function .................................................................................................................... 158

6.4.5 Color Look-Up-Tables .......................................................................................................159

6.4.6 Color RGB Mux .................................................................................................................160

6.4.7 Pixel Shift Logic................................................................................................................. 160

6.4.8 Grayscale/Color Generator for Monochrome/Passive Low Color Displays .......................164

6.4.8.1 HORZ_CNT3, HORZ_CNT4 Counters ....................................................................165

6.4.8.2 VERT_CNT3, VERT_CNT4 Counters......................................................................165

6.4.8.3 FRAME_CNT3, FRAME_CNT4 Counters................................................................165

6.4.8.4 HORZ_CNTx (pixel) timing ...................................................................................... 165

6.4.8.5 VERT_CNTx (line) timing.........................................................................................165

6.4.8.6 FRAME_CNTx timing...............................................................................................165

6.4.8.7 Grayscale Look-Up Table (GrySclLUT) ...................................................................166

6.4.8.8 GrySclLUT Timing Diagram .....................................................................................167

6.4.9 Hardware Cursor ...............................................................................................................176

6.4.9.1 Registers Used for Cursor........................................................................................ 178

6.4.10 Video Timing....................................................................................................................179

6.4.10.1 Setting the Video Memory Parameters ..................................................................182

6.4.10.2 PixelMode ..............................................................................................................184

6.4.11 Blink Logic .......................................................................................................................184

6.4.11.1 BlinkRate................................................................................................................184

6.4.11.2 Defining Blink Pixels...............................................................................................185

6.4.11.3 Types of Blinking.................................................................................................... 185

6.4.12 Color Mode Definition......................................................................................................187

6.4.12.1 Pixel Look-up Table ...............................................................................................187

6.4.12.2 Triple 8-bit Mode ....................................................................................................188

6.4.12.3 16-bit 565 Mode .....................................................................................................188

6.4.12.4 16-bit 555 Mode .....................................................................................................188

6.5 Registers.....................................................................................................................................189

Chapter 7 Graphics Accelerator.............................................................. 231

7.1 Overview .....................................................................................................................................231

7.2 Block Processing Modes.............................................................................................................231

7.2.1 Copy ..................................................................................................................................231

7.2.2 Transparency.....................................................................................................................232

7.2.3 Logical Mask...................................................................................................................... 232

EP9307 User’s Manual - DS667UM1 11

Copyright 2004 Cirrus Logic

Page 12

7.2.3.1 Logical Destination .................................................................................................. 232

7.2.3.2 Operation Precedence............................................................................................. 232

7.2.4 Remapping........................................................................................................................ 233

7.2.5 Block Fills .......................................................................................................................... 233

7.2.6 Packed Memory Transfer.................................................................................................. 233

7.3 Line Draws.................................................................................................................................. 233

7.3.1 Breshenham Line Draws................................................................................................... 234

7.3.2 Pixel Step Line Draws....................................................................................................... 234

7.4 Memory Organization for Graphics Accelerator ......................................................................... 234

7.4.1 Memory Organization for 1 Bit Per Pixel (bpp)................................................................. 235

7.4.2 Memory Organization for 4 Bit Per Pixel ........................................................................... 235

7.4.3 Memory Organization for 8 Bit Per Pixel ........................................................................... 235

7.4.4 Memory Organization for 24 Bit Per Pixel ......................................................................... 237

7.5 Register Programming................................................................................................................ 238

7.6 Word Count ................................................................................................................................ 238

7.6.1 Example: 8 BPP mode ...................................................................................................... 239

7.6.2 Example: 24 BPP (packed) mode..................................................................................... 239

7.7 Pixel End and Start..................................................................................................................... 240

7.7.1 4 BPP mode ...................................................................................................................... 240

7.7.1.1 4 BPP Word Layout ................................................................................................. 240

7.7.1.2 8 BPP Word Layout ................................................................................................. 241

7.7.1.3 16 BPP WORD Layout ............................................................................................ 241

7.7.1.4 24 BPP mode .......................................................................................................... 241

7.8 Register Usage........................................................................................................................... 242

7.8.1 Line (Bresenham’s Algorithm)........................................................................................... 242

7.8.2 DX/DY Line Draw Function ............................................................................................... 244

7.8.3 Block Fill............................................................................................................................ 245

7.8.4 Block Copy........................................................................................................................ 246

7.8.4.1 Source Memory Setup............................................................................................. 246

7.8.4.2 Destination Memory Setup ...................................................................................... 246

7.9 Registers ................................................................................................................................... 248

Chapter 8 1/10/100 Mbps Ethernet LAN Controller ................................ 263

8.1 Introduction ................................................................................................................................. 263

8.1.1 Detailed Description.......................................................................................................... 263

8.1.1.1 Host Interface and Descriptor Processor................................................................. 263

8.1.1.2 Reset and Initialization ............................................................................................ 264

8.1.1.3 Powerdown Modes .................................................................................................. 264

8.1.1.4 Address Space ........................................................................................................ 265

8.1.2 MAC Engine...................................................................................................................... 265

8.1.2.1 Data Encapsulation ................................................................................................. 265

8.1.3 Packet Transmission Process........................................................................................... 266

8.1.3.1 Carrier Deference .................................................................................................... 267

8.1.4 Transmit Back-Off ............................................................................................................. 269

8.1.4.1 Transmission ...........................................................................................................269

8.1.4.2 The FCS Field ......................................................................................................... 270

8.1.4.3 Bit Order .................................................................................................................. 270

8.1.4.4 Destination Address (DA) Filter ............................................................................... 270

12 EP9307 User’s Manual - DS667UM1

Copyright 2004 Cirrus Logic

Page 13

8.1.4.5 Perfect Address Filtering..........................................................................................270

8.1.4.6 Hash Filter................................................................................................................271

8.1.4.7 Flow Control .............................................................................................................272

8.1.4.8 Receive Flow Control...............................................................................................272

8.1.4.9 Transmit Flow Control ..............................................................................................273

8.1.4.10 Rx Missed and Tx Collision Counters....................................................................273

8.1.4.11 Accessing the MII...................................................................................................274

8.2 Descriptor Processor...................................................................................................................275

8.2.1 Receive Descriptor Processor Queues .............................................................................275

8.2.2 Receive Descriptor Queue ................................................................................................276

8.2.3 Receive Status Queue.......................................................................................................278

8.2.3.1 Receive Status Format.............................................................................................281

8.2.3.2 Receive Flow............................................................................................................284

8.2.3.3 Receive Errors .........................................................................................................285

8.2.3.4 Receive Descriptor Data/Status Flow ......................................................................286

8.2.3.5 Receive Descriptor Example....................................................................................287

8.2.3.6 Receive Frame Pre-Processing ...............................................................................287

8.2.3.7 Transmit Descriptor Processor.................................................................................288

8.2.3.8 Transmit Descriptor Queue ......................................................................................288

8.2.3.9 Transmit Descriptor Format .....................................................................................291

8.2.3.10 Transmit Status Queue ..........................................................................................292

8.2.3.11 Transmit Status Format..........................................................................................294

8.2.3.12 Transmit Flow.........................................................................................................296

8.2.3.13 Transmit Errors ......................................................................................................297

8.2.3.14 Transmit Descriptor Data/Status Flow ...................................................................298

8.2.4 Interrupts ...........................................................................................................................299

8.2.4.1 Interrupt Processing.................................................................................................299

8.2.5 Initialization........................................................................................................................299

8.2.5.1 Interrupt Processing.................................................................................................300

8.2.5.2 Receive Queue Processing......................................................................................300

8.2.5.3 Transmit Queue Processing.....................................................................................300

8.2.5.4 Other Processing .....................................................................................................301

8.2.5.5 Transmit Restart Process.........................................................................................301

8.3 Registers.....................................................................................................................................303

Chapter 9 DMA Controller........................................................................ 357

9.1 Introduction .................................................................................................................................357

9.1.1 DMA Features List.............................................................................................................357

9.1.2 Managing Data Transfers Using a DMA Channel .............................................................358

9.1.3 DMA Operations ................................................................................................................359

9.1.3.1 Memory-to-Memory Channels..................................................................................360

9.1.3.2 Memory-to-Peripheral Channels ..............................................................................360

9.1.4 Internal M2P or P2M AHB Master Interface Functional Description..................................361

9.1.5 M2M AHB Master Interface Functional Description...........................................................362

9.1.5.1 Software Trigger Mode.............................................................................................362

9.1.5.2 Hardware Trigger Mode for Internal Peripherals (SSP) and for External

Peripherals without Handshaking Signals .........................................................................362

EP9307 User’s Manual - DS667UM1 13

Copyright 2004 Cirrus Logic

Page 14

9.1.5.3 Hardware Trigger Mode for External Peripherals with Handshaking Signals .......... 362

9.1.6 AHB Slave Interface Limitations........................................................................................ 363

9.1.7 Interrupt Interface.............................................................................................................. 363

9.1.8 Internal M2P/P2M Data Unpacker/Packer Functional Description.................................... 363

9.1.9 Internal M2P/P2M DMA Functional Description................................................................ 364

9.1.9.1 Internal M2P/P2M DMA Buffer Control Finite State Machine.................................. 364

9.1.9.2 Data Transfer Initiation and Termination ................................................................. 366

9.1.10 M2M DMA Functional Description................................................................................... 367

9.1.10.1 M2M DMA Control Finite State Machine ............................................................... 367

9.1.10.2 M2M Buffer Control Finite State Machine.............................................................. 369

9.1.10.3 Data Transfer Initiation .......................................................................................... 371

9.1.10.4 Data Transfer Termination..................................................................................... 373

9.1.10.5 Memory Block Transfer ......................................................................................... 374

9.1.10.6 Bandwidth Control ................................................................................................. 374

9.1.10.7 External Peripheral DMA Request (DREQ) Mode ................................................. 374

9.1.11 DMA Data Transfer Size Determination.......................................................................... 376

9.1.11.1 Software Initiated M2M and M2P/P2M Transfers.................................................. 376

9.1.11.2 Hardware Initiated M2M Transfers ........................................................................ 376

9.1.12 Buffer Descriptors ........................................................................................................... 377

9.1.12.1 Internal M2P/P2M Channel Rx Buffer Descriptors ................................................ 377

9.1.12.2 Internal M2P/P2M Channel Tx Buffer Descriptors................................................. 377

9.1.12.3 M2M Channel Buffer Descriptors........................................................................... 377

9.1.13 Bus Arbitration................................................................................................................. 377

9.2 Registers .................................................................................................................................... 379

9.2.1 DMA Controller Memory Map............................................................................................ 379

9.2.2 Internal M2P/P2M Channel Register Map......................................................................... 379

Chapter 10 Universal Serial Bus Host Controller .................................. 407

10.1 Introduction............................................................................................................................... 407

10.1.1 Features .......................................................................................................................... 407

10.2 Overview................................................................................................................................... 407

10.2.1 Data Transfer Types ....................................................................................................... 408

10.2.2 Host Controller Interface ................................................................................................. 409

10.2.2.1 Communication Channels ..................................................................................... 409

10.2.2.2 Data Structures...................................................................................................... 410

10.2.3 Host Controller Driver Responsibilities............................................................................ 412

10.2.3.1 Host Controller Management................................................................................. 412

10.2.3.2 Bandwidth Allocation ............................................................................................. 412

10.2.3.3 List Management ................................................................................................... 413

10.2.3.4 Root Hub ............................................................................................................... 414

10.2.4 Host Controller Responsibilities ...................................................................................... 414

10.2.4.1 USB States............................................................................................................414

10.2.4.2 Frame management .............................................................................................. 414

10.2.4.3 List Processing ...................................................................................................... 414

10.2.5 USB Host Controller Blocks ............................................................................................ 415

10.2.5.1 AHB Slave .............................................................................................................415

10.2.5.2 AHB Master ........................................................................................................... 415

14 EP9307 User’s Manual - DS667UM1

Copyright 2004 Cirrus Logic

Page 15

10.2.5.3 HCI Slave Block .....................................................................................................415

10.2.5.4 HCI Master Block ...................................................................................................416

10.2.5.5 USB State Control..................................................................................................416

10.2.5.6 Data FIFO ..............................................................................................................416

10.2.5.7 List Processor ........................................................................................................416

10.2.5.8 Root Hub and Host SIE..........................................................................................416

10.3 Registers...................................................................................................................................417

Chapter 11 Static Memory Controller ..................................................... 445

11.1 Introduction ...............................................................................................................................445

11.2 Static Memory Controller Operation..........................................................................................446

11.3 Byte Lane Write / Read Control ................................................................................................448

11.4 Registers...................................................................................................................................450

Chapter 12 SDRAM, SyncROM, and SyncFLASH Controller................ 453

12.1 Introduction ...............................................................................................................................453

12.1.1 Booting (from SROM or SyncFLASH) .............................................................................453

12.1.1.1 Address Pin Usage ................................................................................................454

12.1.1.2 SDRAM Initialization ..............................................................................................456

12.1.1.3 Programming External Device Mode Register .......................................................457

12.1.1.4 SDRAM Self Refresh .............................................................................................460

12.1.1.5 SROM and SyncFlash............................................................................................460

12.1.1.6 External Synchronous Memory System .................................................................461

12.2 Registers...................................................................................................................................465

Chapter 13 ARM920T Core and Advanced High-Speed Bus (AHB) ..... 473

13.1 Introduction ...............................................................................................................................473

13.2 Overview: ARM920T Processor Core.......................................................................................473

13.2.1 Features ..........................................................................................................................473

13.2.2 Block Diagram .................................................................................................................474

13.2.3 Operations ....................................................................................................................... 474

13.2.3.1 ARM9TDMI Core....................................................................................................475

13.2.3.2 Memory Management Unit.....................................................................................476

13.2.3.3 Cache and Write Buffer..........................................................................................477

13.2.4 Coprocessor Interface .....................................................................................................478

13.2.5 AMBA AHB Bus Interface Overview................................................................................479

13.2.6 EP9307 AHB Implementation Details..............................................................................480

13.2.7 Memory and Bus Access Errors ......................................................................................481

13.2.8 Bus Arbitration.................................................................................................................482

13.2.8.1 Main AHB Bus Arbiter............................................................................................482

13.2.8.2 SDRAM Slave Arbiter.............................................................................................483

13.2.8.3 EBI Bus Arbiter.......................................................................................................483

13.3 AHB Decoder ............................................................................................................................483

13.3.1 AHB Bus Slave ................................................................................................................484

13.3.2 AHB to APB Bridge..........................................................................................................484

13.3.2.1 Function and Operation of APB Bridge ..................................................................484

13.3.3 APB Bus Slave ................................................................................................................485

13.3.4 Register Definitions .........................................................................................................485

EP9307 User’s Manual - DS667UM1 15

Copyright 2004 Cirrus Logic

Page 16

13.3.5 Memory Map ................................................................................................................... 489

13.3.6 Internal Register Map...................................................................................................... 490

13.3.6.1 Memory Access Rules........................................................................................... 490

Chapter 14 UART1 With HDLC and Modem Control Signals ................ 505

14.1 Introduction............................................................................................................................... 505

14.2 UART Overview........................................................................................................................ 505

14.2.1 UART Functional Description.......................................................................................... 506

14.2.1.1 AMBA APB Interface ............................................................................................. 506

14.2.1.2 DMA Block.............................................................................................................506

14.2.1.3 Register Block ....................................................................................................... 507

14.2.1.4 Baud Rate Generator ............................................................................................ 508

14.2.1.5 Transmit FIFO ....................................................................................................... 508

14.2.1.6 Receive FIFO ........................................................................................................ 508

14.2.1.7 Transmit Logic ....................................................................................................... 508

14.2.1.8 Receive Logic ........................................................................................................ 508

14.2.1.9 Interrupt Generation Logic ..................................................................................... 508

14.2.1.10 Synchronizing Registers and Logic ..................................................................... 509

14.2.2 UART Operation.............................................................................................................. 509

14.2.2.1 Error Bits................................................................................................................ 510

14.2.2.2 Disabling the FIFOs............................................................................................... 510

14.2.2.3 System/diagnostic Loopback Testing .................................................................... 510

14.2.2.4 UART Character Frame......................................................................................... 510

14.2.3 Interrupts......................................................................................................................... 511

14.2.3.1 UARTMSINTR....................................................................................................... 511

14.2.3.2 UARTRXINTR ....................................................................................................... 511

14.2.3.3 UARTTXINTR........................................................................................................ 512

14.2.3.4 UARTRTINTR........................................................................................................ 512

14.2.3.5 UARTINTR ............................................................................................................ 512

14.3 Modem...................................................................................................................................... 512

14.4 HDLC........................................................................................................................................ 513

14.4.1 Overview of HDLC Modes............................................................................................... 513

14.4.2 Selecting HDLC Modes................................................................................................... 514

14.4.3 HDLC Transmit ............................................................................................................... 515

14.4.4 HDLC Receive ................................................................................................................ 516

14.4.5 CRCs............................................................................................................................... 517

14.4.6 Address Matching ........................................................................................................... 517

14.4.7 Aborts.............................................................................................................................. 518

14.4.8 DMA ................................................................................................................................ 518

14.4.9 Writing Configuration Registers ...................................................................................... 519

14.5 UART1 Package Dependency..................................................................................................519

14.5.1 Clocking Requirements ...................................................................................................520

14.5.2 Bus Bandwidth Requirements......................................................................................... 520

14.6 Registers .................................................................................................................................. 522

Chapter 15 UART2 .................................................................................... 543

15.1 Introduction............................................................................................................................... 543

15.2 IrDA SIR Block.......................................................................................................................... 543

16 EP9307 User’s Manual - DS667UM1

Copyright 2004 Cirrus Logic

Page 17

15.2.1 IrDA SIR Encoder/decoder Functional Description .........................................................543

15.2.1.1 IrDA SIR Transmit Encoder....................................................................................544

15.2.1.2 IrDA SIR Receive Decoder ....................................................................................544

15.2.2 IrDA SIR Operation..........................................................................................................545

15.2.2.1 System/diagnostic Loopback Testing.....................................................................546

15.2.3 IrDA Data Modulation ......................................................................................................546

15.2.4 Enabling Infrared (Ir) Modes ............................................................................................547

15.3 UART2 Package Dependency ..................................................................................................547

15.3.1 Clocking Requirements ...................................................................................................547

15.3.2 Bus Bandwidth Requirements .........................................................................................548

15.4 Registers...................................................................................................................................549

Chapter 16 UART3 With HDLC Encoder ................................................. 561

16.1 Introduction ...............................................................................................................................561

16.2 Implementation Details..............................................................................................................561

16.2.1 UART3 Package Dependency.........................................................................................561

16.2.2 Clocking Requirements ...................................................................................................562

16.2.3 Bus Bandwidth Requirements .........................................................................................562

16.3 Registers...................................................................................................................................563

Chapter 17 IrDA ........................................................................................ 581

17.1 Introduction ...............................................................................................................................581

17.2 IrDA Interfaces ..........................................................................................................................581

17.3 Shared IrDA Interface Feature..................................................................................................582

17.3.1 Overview..........................................................................................................................582

17.3.2 Functional Description .....................................................................................................582

17.3.2.1 General Configuration ............................................................................................583

17.3.2.2 Transmitting Data................................................................................................... 583

17.3.2.3 Receiving Data.......................................................................................................586

17.3.2.4 Special Conditions .................................................................................................588

17.3.3 Control Information Buffering...........................................................................................588

17.4 Medium IrDA Specific Features ................................................................................................589

17.4.1 Introduction ......................................................................................................................589

17.4.1.1 Bit Encoding...........................................................................................................589

17.4.1.2 Frame Format ........................................................................................................589

17.4.2 Functional Description .....................................................................................................591

17.4.2.1 Baud Rate Generation ...........................................................................................591

17.4.2.2 Receive Operation .................................................................................................592

17.4.2.3 Transmit Operation ................................................................................................593

17.5 Fast IrDA Specific Features ......................................................................................................594

17.5.1 Introduction ......................................................................................................................594

17.5.1.1 4PPM Modulation...................................................................................................594

17.5.1.2 4.0 Mbps FIR Frame Format..................................................................................596

17.5.2 Functional Description .....................................................................................................597

17.5.2.1 Baud Rate Generation ...........................................................................................598

17.5.2.2 Receive Operation .................................................................................................598

17.5.2.3 Transmit Operation ................................................................................................600

17.5.3 IrDA Connectivity.............................................................................................................601

EP9307 User’s Manual - DS667UM1 17

Copyright 2004 Cirrus Logic

Page 18

17.5.4 IrDA Integration Information............................................................................................602

17.5.4.1 Enabling Infrared Modes ....................................................................................... 602

17.5.4.2 Clocking Requirements ......................................................................................... 602

17.5.4.3 Bus Bandwidth Requirements ............................................................................... 603

17.6 Registers .................................................................................................................................. 604

Chapter 18 Timers..................................................................................... 619

18.1 Introduction............................................................................................................................... 619

18.1.1 Features .......................................................................................................................... 619

18.1.2 16 and 32-bit Timer Operation ........................................................................................ 619

18.1.2.1 Free Running Mode ............................................................................................... 620

18.1.2.2 Pre-load Mode ....................................................................................................... 620

18.1.3 40-bit Timer Operation .................................................................................................... 620

18.2 Registers .................................................................................................................................. 621

Chapter 19 Watchdog Timer .................................................................... 627

19.1 Introduction............................................................................................................................... 627

19.1.1 Watchdog Activation ....................................................................................................... 628

19.1.2 Clocking Requirements ...................................................................................................628

19.1.3 Reset Requirements ....................................................................................................... 628

19.1.4 Watchdog Status............................................................................................................. 628

19.2 Registers .................................................................................................................................. 630

Chapter 20 Real Time Clock With Software Trim................................... 633

20.1 Introduction............................................................................................................................... 633

20.1.1 Software Trim.................................................................................................................. 633

20.1.1.1 Software Compensation ........................................................................................ 634

20.1.1.2 Oscillator Frequency Calibration............................................................................ 634

20.1.1.3 RTCSWComp Value Determination ...................................................................... 634

20.1.1.4 Example - Measured Value Split Into Integer and Fractional Component............. 635

20.1.1.5 Maximum Error Calculation vs. Real Time Clock Accuracy................................... 635

20.1.1.6 Real-Time Interrupt................................................................................................ 636

20.1.2 Reset Control.................................................................................................................. 636

20.2 Registers .................................................................................................................................. 637

Chapter 21 I2S Controller ......................................................................... 641

21.1 Introduction............................................................................................................................... 641

2

21.2 I

21.3 I

21.4 I

21.5 I

21.6 I

21.7 Interrupts .................................................................................................................................. 653

21.8 Registers .................................................................................................................................. 655

18 EP9307 User’s Manual - DS667UM1

S Transmitter Channel Overview ........................................................................................... 643

2

S Receiver Channel Overview ............................................................................................... 647

21.3.1 Receiver FIFO’s .............................................................................................................. 647

2

S Configuration and Status Registers.................................................................................... 649

2

S Master Clock Generation.................................................................................................... 649

2

S Bit Clock Rate Generation .................................................................................................. 651

21.6.1 Example of the Bit Clock Generation. ............................................................................. 652

21.6.2 Example of Right Justified LRCK format......................................................................... 652

2

21.8.1 I

21.8.2 I

S TX Registers ............................................................................................................. 655

2

S RX Registers............................................................................................................. 662

Copyright 2004 Cirrus Logic

Page 19

21.8.3 I2S Configuration and Status Registers...........................................................................668

21.8.4 I

2

S Global Status Registers.............................................................................................672

Chapter 22 AC’97 Controller.................................................................... 675

22.1 Introduction ...............................................................................................................................675

22.2 Interrupts...................................................................................................................................677

22.2.1 Channel Interrupts ...........................................................................................................677

22.2.1.1 RIS .........................................................................................................................677

22.2.1.2 TIS..........................................................................................................................678

22.2.1.3 RTIS.......................................................................................................................678

22.2.1.4 TCIS.......................................................................................................................678

22.2.2 Global Interrupts..............................................................................................................678

22.2.2.1 CODECREADY......................................................................................................678

22.2.2.2 WINT......................................................................................................................678

22.2.2.3 GPIOINT ................................................................................................................679

22.2.2.4 GPIOTXCOMPLETE..............................................................................................679

22.2.2.5 SLOT2INT..............................................................................................................679

22.2.2.6 SLOT1TXCOMPLETE ...........................................................................................679

22.2.2.7 SLOT2TXCOMPLETE ...........................................................................................679

22.3 System Loopback Testing .........................................................................................................679

22.4 Registers...................................................................................................................................680

Chapter 23 Synchronous Serial Port ...................................................... 699

23.1 Introduction ...............................................................................................................................699

23.2 Features....................................................................................................................................699

23.3 SSP Functionality......................................................................................................................700

23.4 SSP Pin Multiplex......................................................................................................................700

23.5 Configuring the SSP..................................................................................................................700

23.5.1 Enabling SSP Operation..................................................................................................701

23.5.2 Master/Slave Mode..........................................................................................................701

23.5.3 Serial Bit Rate Generation...............................................................................................701

23.5.4 Frame Format.................................................................................................................701

23.5.5 Texas Instruments® Synchronous Serial Frame Format ................................................702

23.5.6 Motorola® SPI Frame Format .........................................................................................703

23.5.6.1 SPO Clock Polarity.................................................................................................703

23.5.6.2 SPH Clock Phase...................................................................................................703

23.5.7 Motorola SPI Format with SPO=0, SPH=0......................................................................703

23.5.8 Motorola SPI Format with SPO=0, SPH=1.....................................................................705