Page 1

EP9301 User’s Guide

http://www.cirrus.com

Release 1.00

Copyright © Cirrus Logic, Inc. 2004

(All Rights Reserved)

FEB ‘04

DS636UM2

Page 2

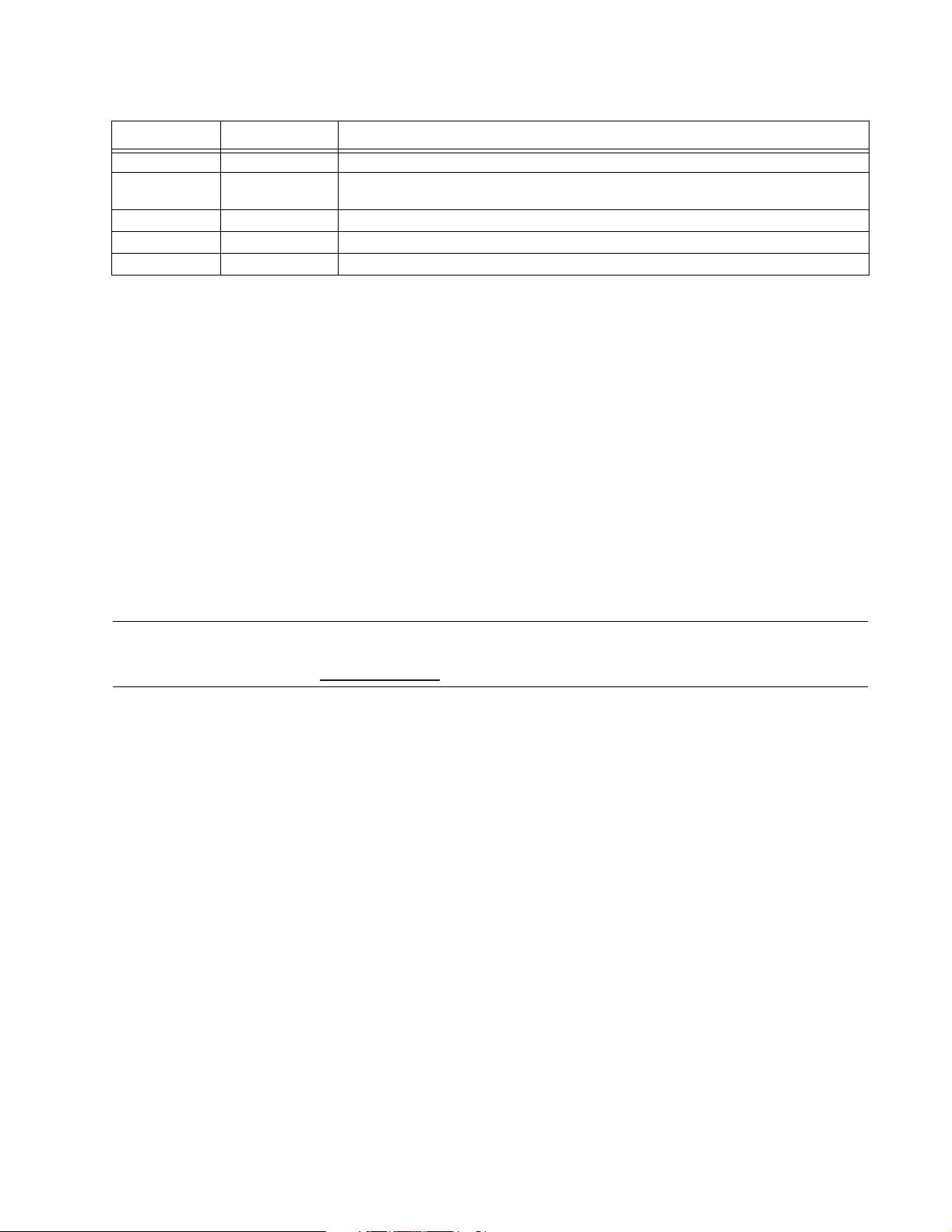

Revision Date Changes

1 12 December 2003 Initial Release

2 12 February 2004

Updated ChipID, SysCfg and DeviceCfg register information.

Added ExtensionID register information to the Security section.

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative.

To find one nearest you go to www.cirrus.com

IMPORTANT NOTICE

Cirrus Logic, Inc. and i ts subsidiaries (“Ci rrus”) beli eve that the informati on contai ned in this document is accurate and reli able. However, the information is

subject to change without notice and is provided “AS IS” without warranty of any kind (express or implied). Customers are advised to obtain the latest version

of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and

conditions of sale supplied at the ti me of order acknowledgment, including those pertaini ng to warranty, patent infringement, and limitation of li ability. No responsibility i s assumed by Cirrus for the use of this information, incl uding use of this informati on as the basis for manufacture or sale of any items, or for i nfringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express

or implied under any patents, mask work rights , copyrights, trademarks, trade secret s or other int ellectual pr operty right s. Cirrus owns the copyrights associated

with the informati on contained herein and gives consent for copies to be made of the information only for use within your organi zation with respect to Cirrus

integrated circui ts or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution, adverti sing or promotional

purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USI NG SEMI CONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE

PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS ( INCLUDING MEDICAL DEVICES, AIRCRAFT SYSTEMS OR COMPONENTS AND PERSONAL OR

AUTOMOTIVE SAFETY OR SECURITY DEVICES). I NCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT

THE CUSTOMER’ S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, I NCLUDI NG THE I MPLIED

WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN

SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER’S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS’ FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION

WITH THESE USES.

Cirrus Logi c, Cirrus, MaverickKey, and the Cirrus Logic logo de signs are trademarks of Cirrus Logic, I nc. All other brand and product names in thi s document

may be trademarks or service marks of their respective owners.

Microsoft and Windows are registered trademarks of Microsoft Corporation.

Microwire is a trademark of National Semiconductor Corp. National Semiconductor is a registered trad emark of National Semiconductor Corp.

Texas Instruments is a registered trademark of Texas Instruments, Inc.

Motorola is a registered trademark of Motorola, Inc.

LINUX is a registered trademark of Linus Torval ds.

2 EP9301 User’s Manual - DS636UM2

Copyright 2004 Cirrus Logic

Page 3

About the EP9301 User’s Guide

This Guide describes the architecture, hardware and operation of the Cirrus

Logic EP9301. It is intended to be used in conjunction with the EP9301

Datasheet, which contains the full electrical specifications for the device.

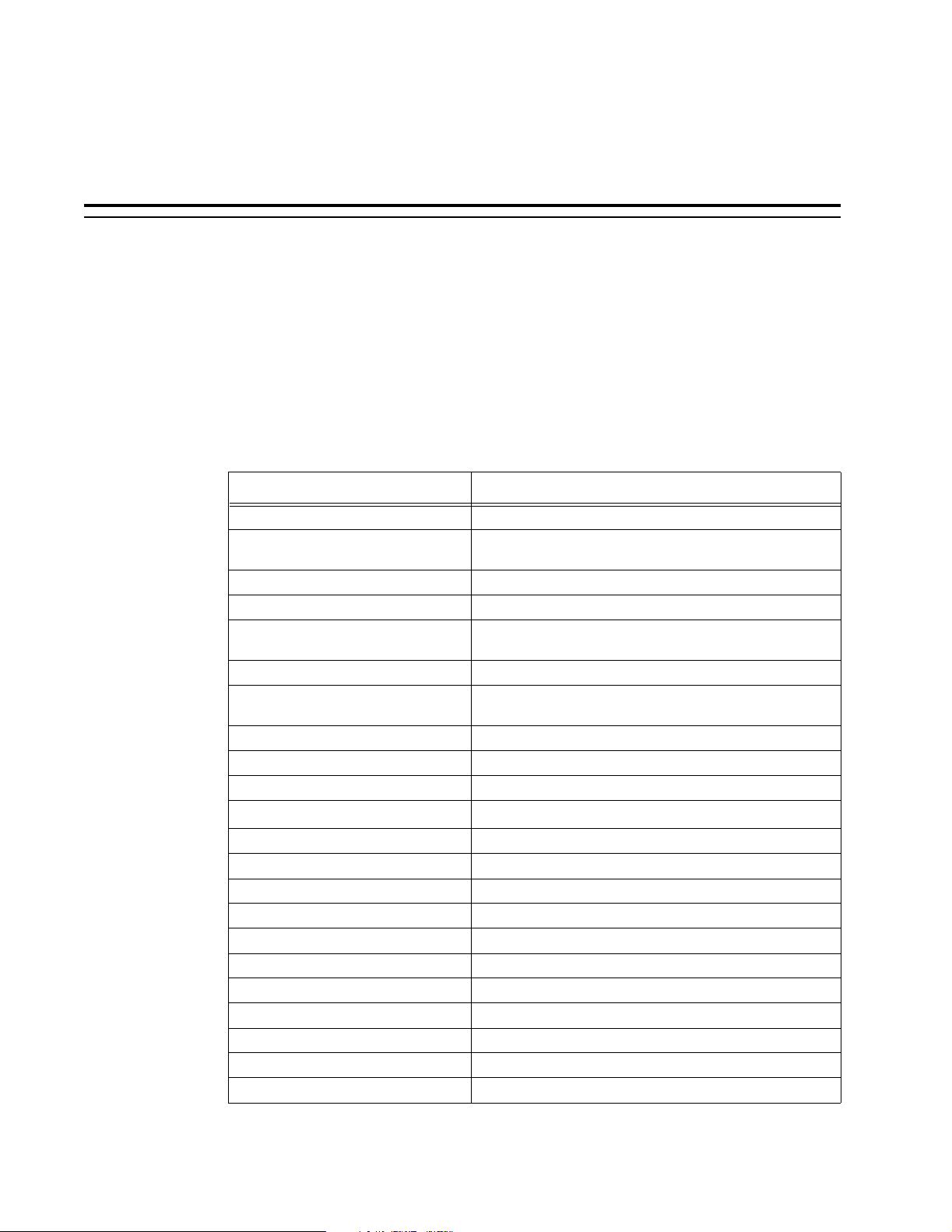

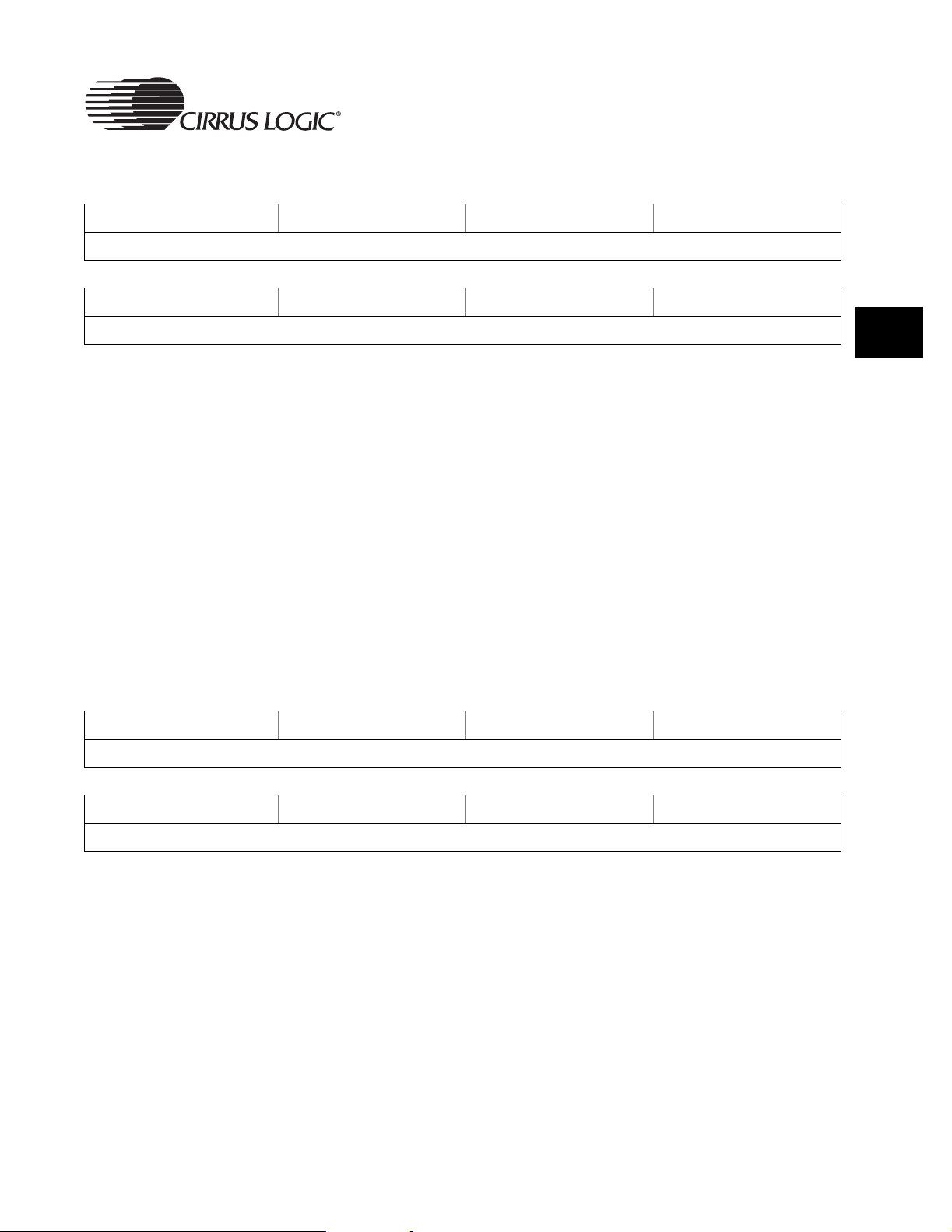

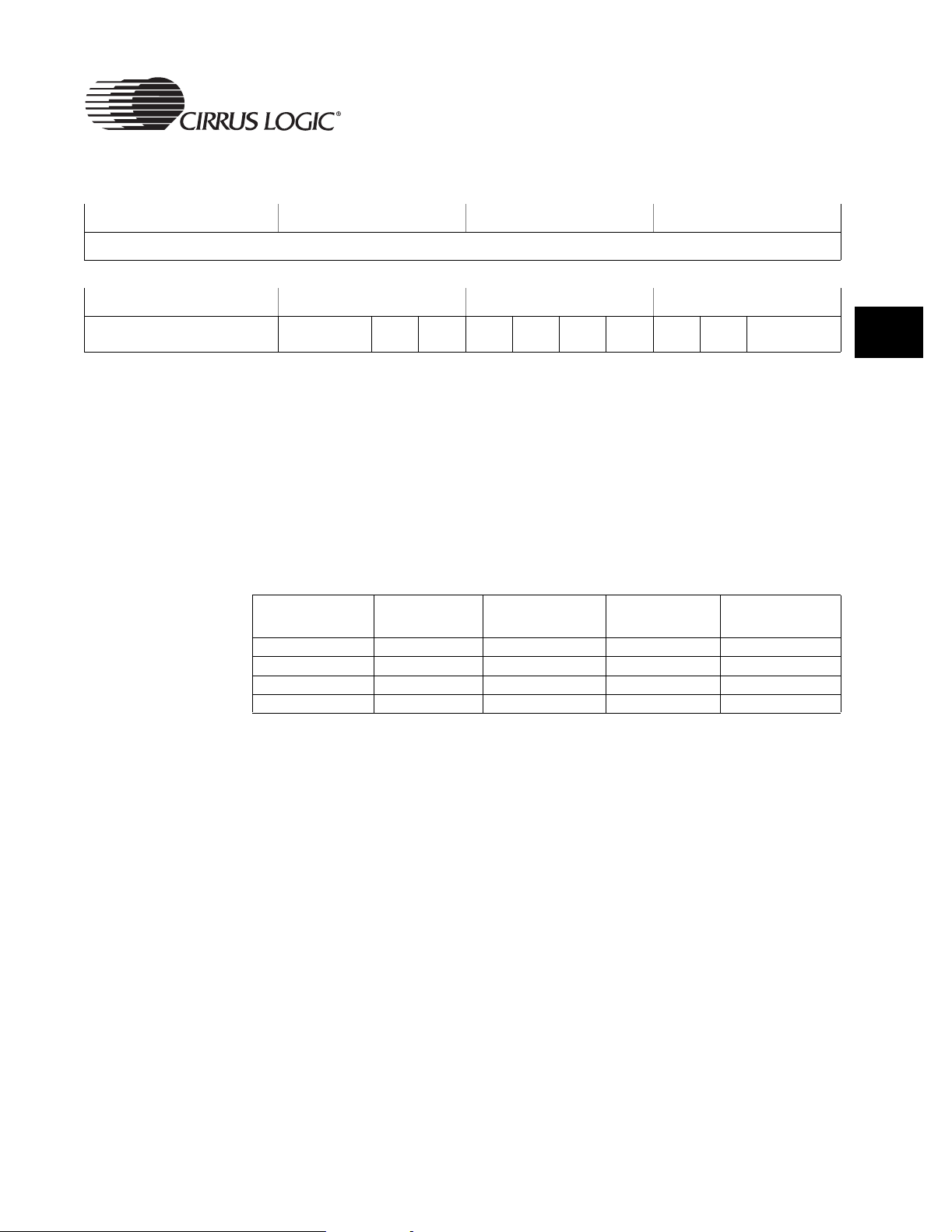

How to Use this Guide

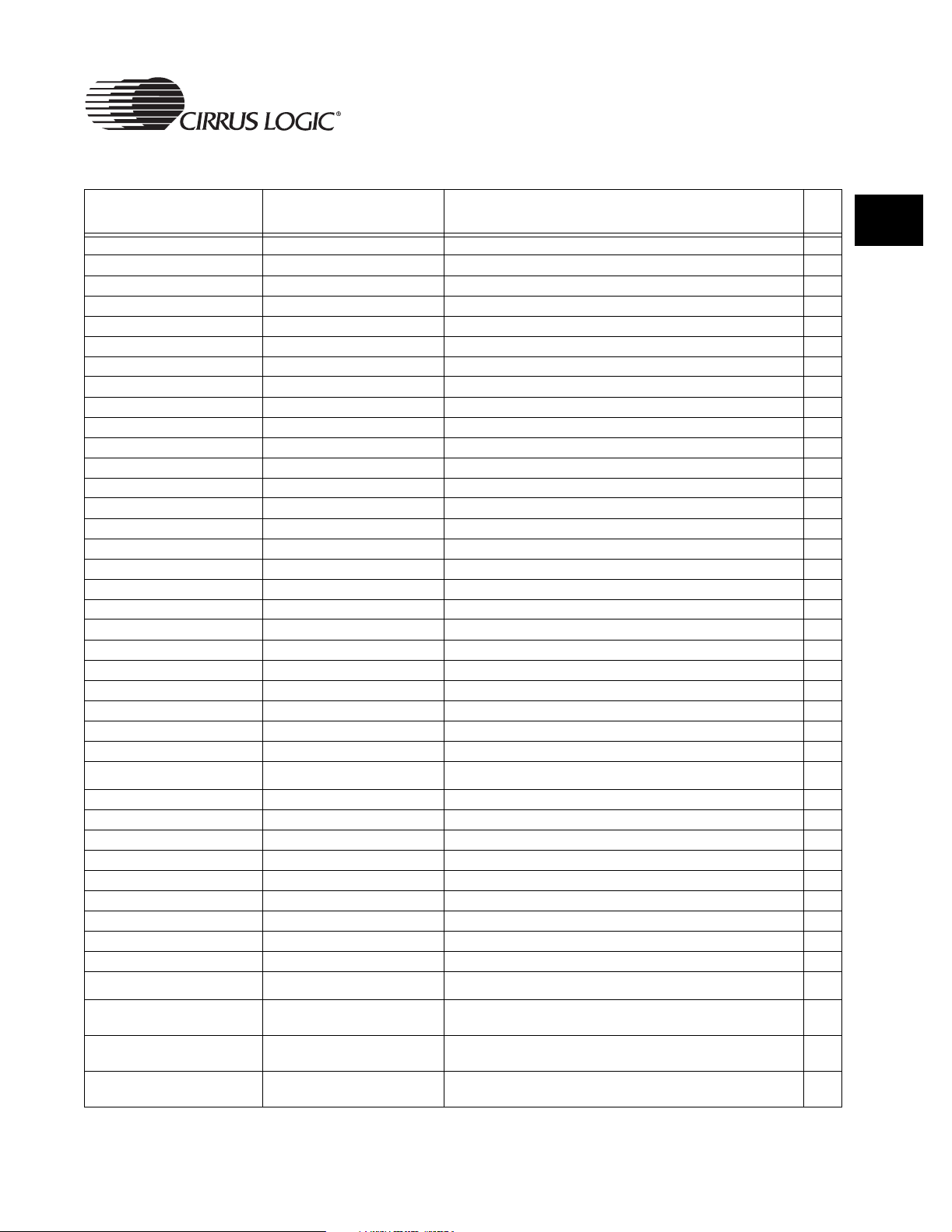

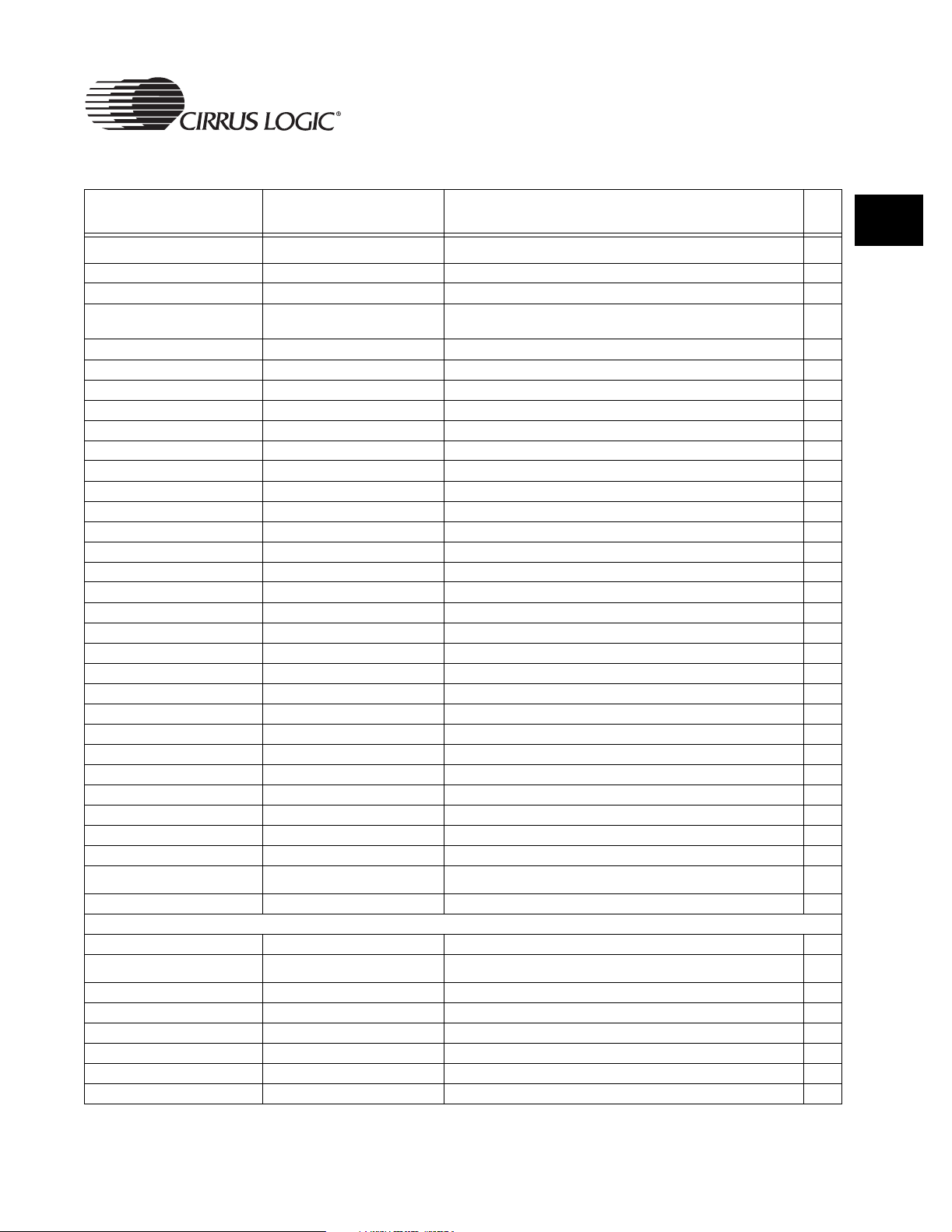

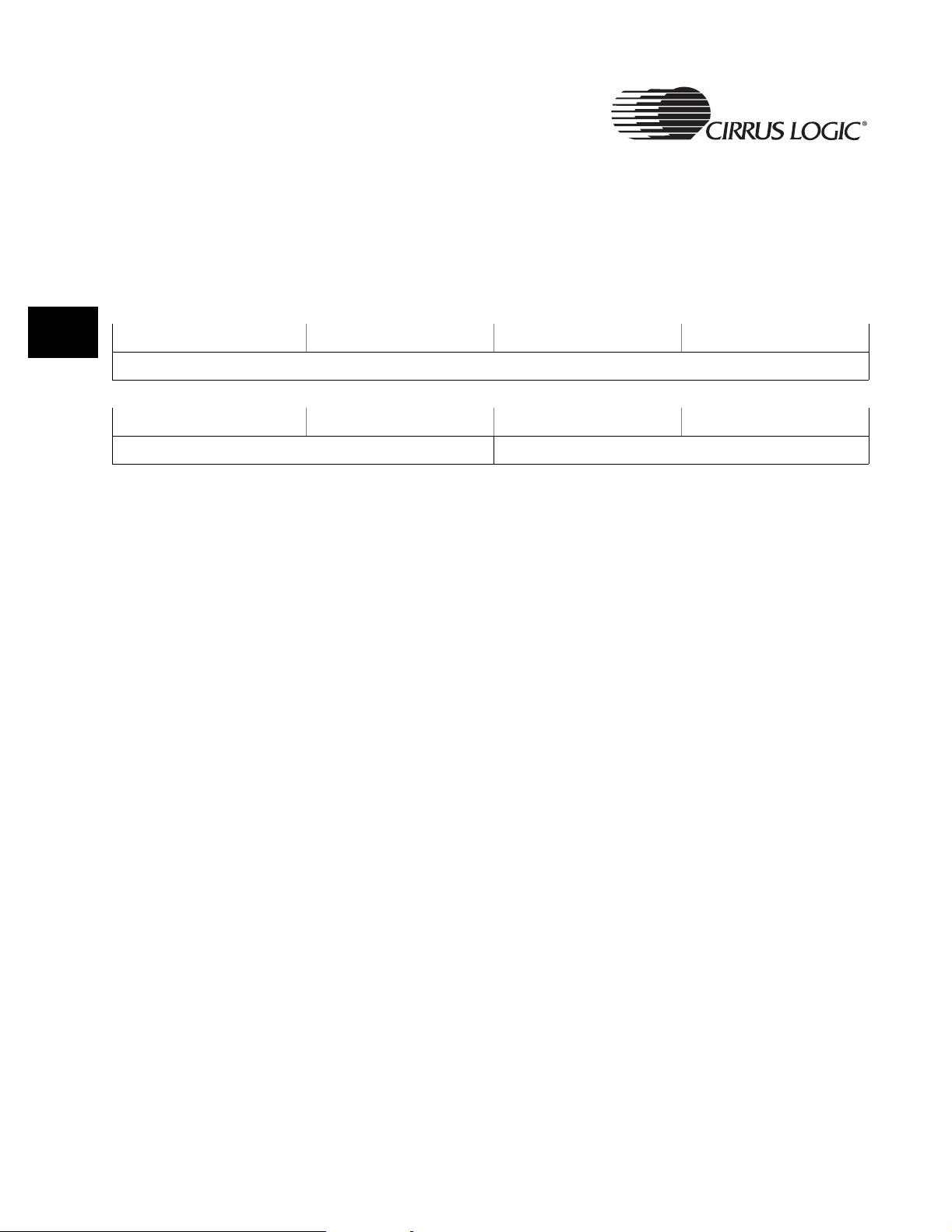

Subject Matter Location

AC’97 Chapter 18 - AC’97 Controller

ARM920T Processor

Boot ROM, Hardware and Software Chapter 3 - Boot ROM

Booting From SROM or SyncFlash Chapter 10 - SDRAM, SyncROM, and SyncFLASH Controller

Buses - AMBA, AHB, APB

DMA Controller Chapter 7 - DMA Controller

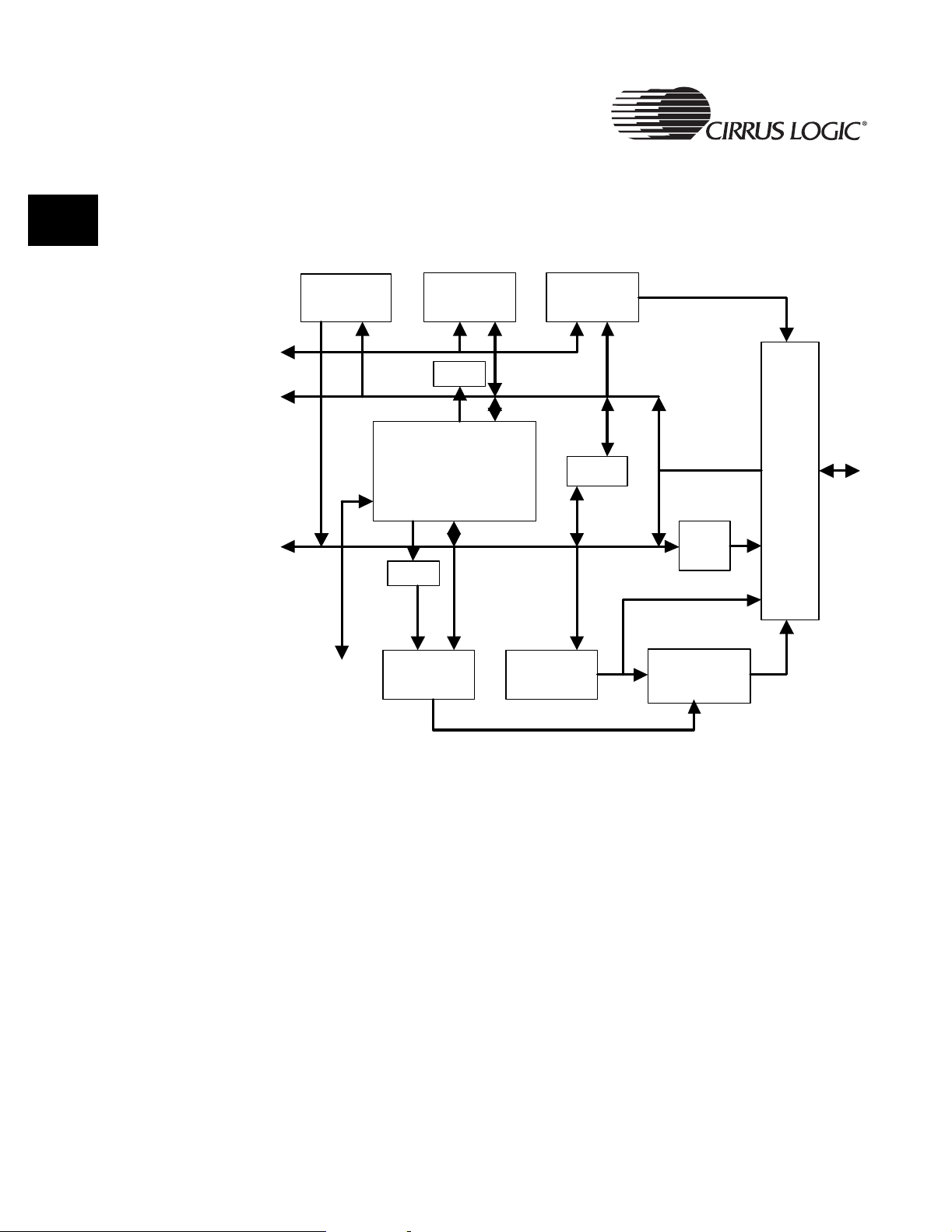

EP9301 Block Diagram

Ethernet Chapter 6 - 1/10/100 Mbps Ethernet LAN Controller

GPIO Chapter 21 - GPIO Interface

HDLC Chapter 11 - UART1 With HDLC and Modem Control Signals

2

I

S Chapter 17 - I2S Controller

Infra-Red Interface Chapter 13 - IrDA

Interrupt Registers Chapter 5 - Vectored Interrupt Controller

Interrupts Chapter 5 - Vectored Interrupt Controller

IrDA Chapter 13 - IrDA

MAC Chapter 6 - 1/10/100 Mbps Ethernet LAN Controller

Memory Map Chapter 1 - Introduction

Modem Chapter 11 - UART1 With HDLC and Modem Control Signals

Power Management Chapter 4 - System Controller

Programming Clocks Chapter 4 - System Controller

Real Time Clock Chapter 16 - Real Time Clock With Software Trim

Register List Chapter 1 - Introduction

Chapter 2 - ARM920T Core and Advanced High-Speed Bus

(AHB)

Chapter 2 - ARM920T Core and Advanced High-Speed Bus

(AHB)

Chapter 2 - ARM920T Core and Advanced High-Speed Bus

(AHB)

Preface

EP9301 User’s Manual - DS636UM2 3

Copyright 2004 Cirrus Logic

Page 4

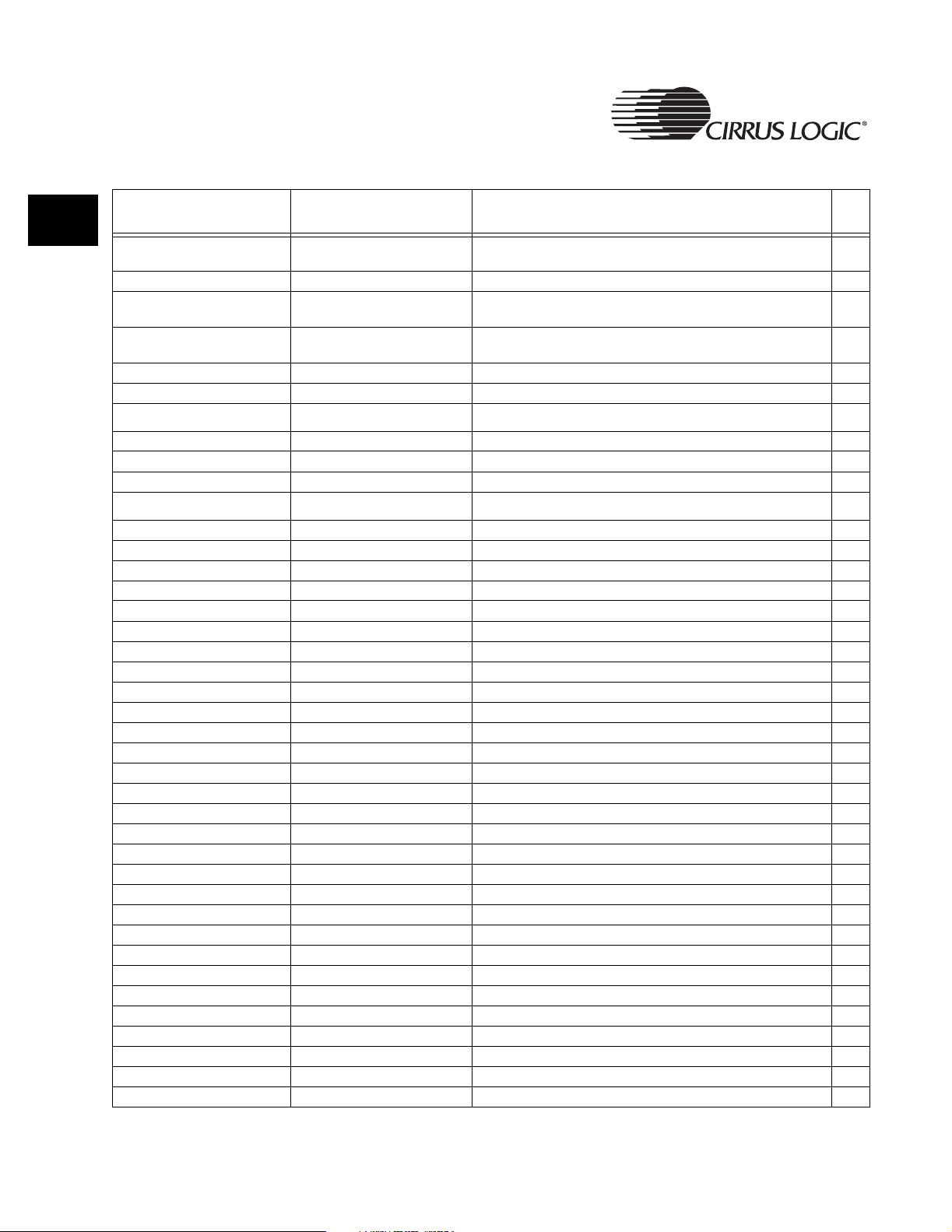

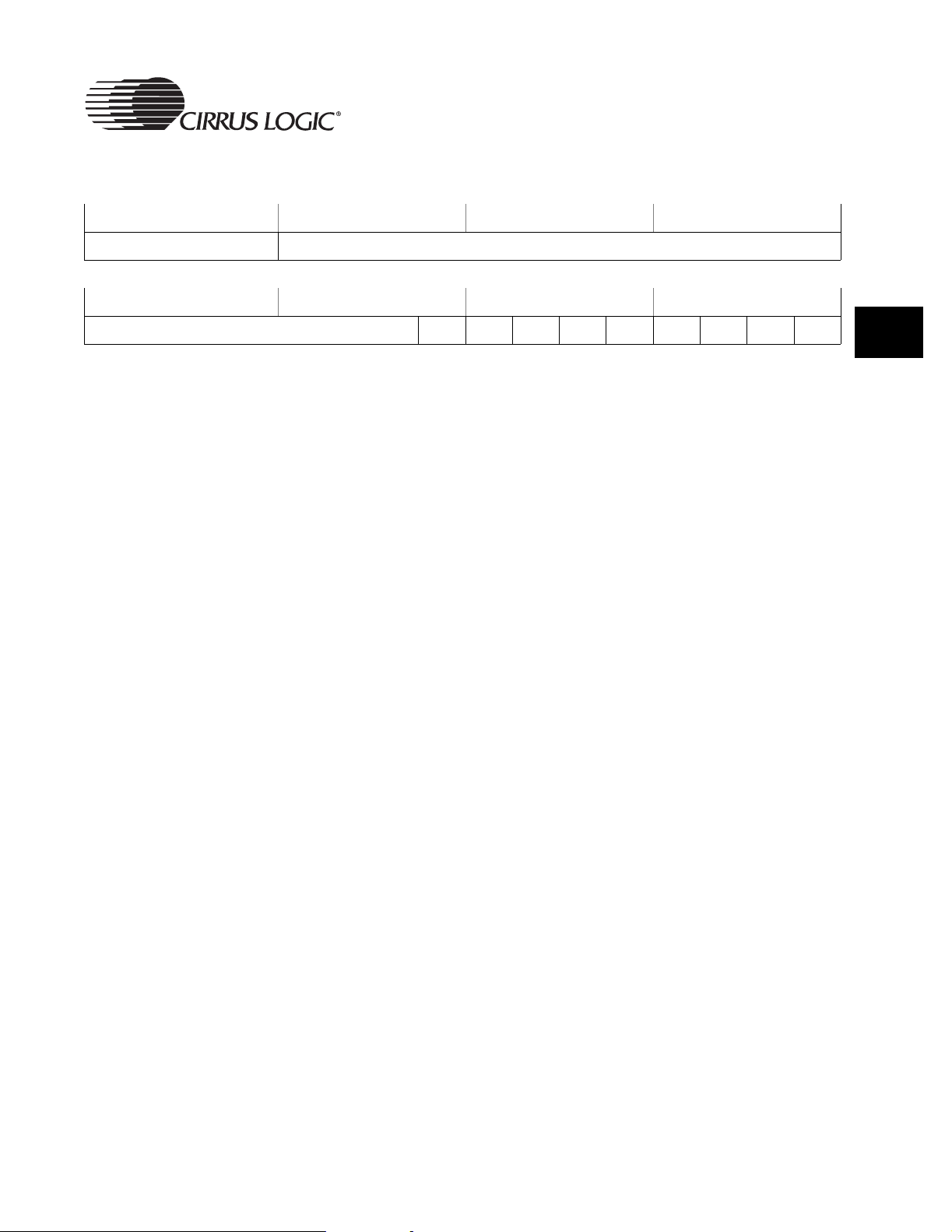

Subject Matter Location

RTC Chapter 16 - Real Time Clock With Software Trim

SDRAM Chapter 10 - SDRAM, SyncROM, and SyncFLASH Controller

Security Chapter 22 - Security

SMC Chapter 9 - Static Memory Controller

SSP Chapter 19 - Synchronous Serial Port

Static Memory Controller Chapter 9 - Static Memory Controller

System Configuration Chapter 4 - System Controller

System Registers Chapter 4 - System Controller

Timers Chapter 14 - Timers

Touch Screen Chapter 20 - Analog-to-Digital Converter (ADC) Interface

UART

USB Chapter 8 - Universal Serial Bus Host Controller

Vectored Interrupt Registers Chapter 5 - Vectored Interrupt Controller

Vectored Interrupts Chapter 5 - Vectored Interrupt Controller

Watchdog Timer Chapter 15 - Watchdog Timer

Chapter 11 - UART1 With HDLC and Modem Control Signals

Chapter 12 - UART2

Related Documents from Cirrus Logic

1. EP9301 Datasheet, document number - DS636PP1

Reference Documents

1. ARM920T Technical Reference Manual

2. AMBA Specification (Rev. 2.0), ARM IHI 0011A, ARM Limited.

3. AHB Example AMBA System (Addendum 01), ARM DDI 0170A, ARM

Limited.

4. The coprocessor instruction assembler notation can be referenced from

ARM programming manuals or the Quick Reference Card, document

number ARM QRC 0001D.

5. The MAC engine is compliant with the requirements of ISO/IEC 8802-3

(1993), Sections 3 and 4.

6. OpenHCI - Open Host Controller interface Specification for USB, Release

1.0a; Compaq, Microsoft, National Semiconductor.

7. ARM Coprocessor Quick Reference Card, document number ARM QRC

0001D.

4 EP9301 User’s Manual - DS636UM2

Copyright 2004 Cirrus Logic

Page 5

8. Information Technology, AT Attachment with Packet Interface - 5

(ATA/ATAPI-5) ANSI NCITS document T13 1321D, Revision 3, 29

February 2000

9. OpenHCI - Open Host Controller Interface Specification for USB,

Release: 1.0a, Released - 09/14/99 2:33 PM

10. ARM PrimeCell PL190-Rel1v1 Revision 1.7 Technical Reference Manual

DDI0181C

11. Audio Codec ‘97, Revision 2.3, April 2002, Intel Corporation

Notational Conventions

This document uses the following conventions:

• Internal and external Signal Names, and Pin Names use mixed upper and

lower case alphanumeric, and are shown in bold font: RDLED.

• Register Bit Fields are named using upper and lower case alphanumeric:

that is, SBOOT, LCSn1.

• Registers are named using mixed upper and lower case alphanumeric:

that is, SysCfg or PxDDR. (Where there are multiple registers with similar

names, a lower case “x” is used as a place holder. For example, in the

PxDDR registers, x represents a letter between A and H, indicating the

specific port being discussed.)

Caution: In the Internal Register Map in Table 2-7 on page 7-47, some

memory locations are listed as Reserved. These memory

locations should not be used. Reading from these memory

locations will yield invalid data. Writing to these memory locations

may cause unpredictable results.

(An example register description is shown below. This description is used for

the following examples.)

A specific bit may be specified in one of two ways:

register name[bit number]: SysCfg[29]

By

or by

register name.bit field[bit number]: SysCfg.REV[1]

Both of these representations refer to the same bit.

The following:

SysCfg[8]

, or

,

SysCfg.SBOOT

also refer to the same bit.

Hexidecimal numbers are referred to as

0x0000_0000

.

EP9301 User’s Manual - DS636UM2 5

Copyright 2004 Cirrus Logic

Page 6

Binary numbers are referred to as

0000_0000b

.

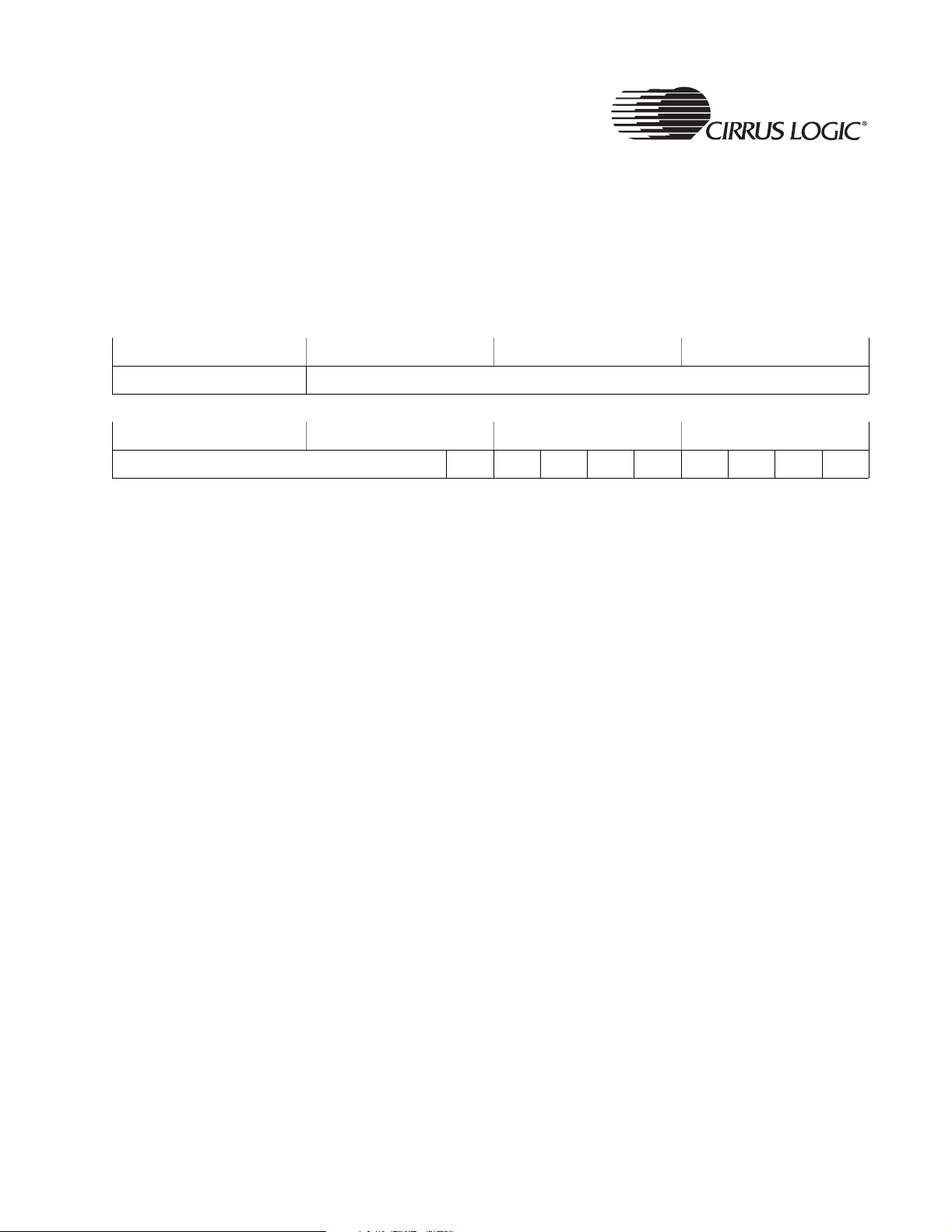

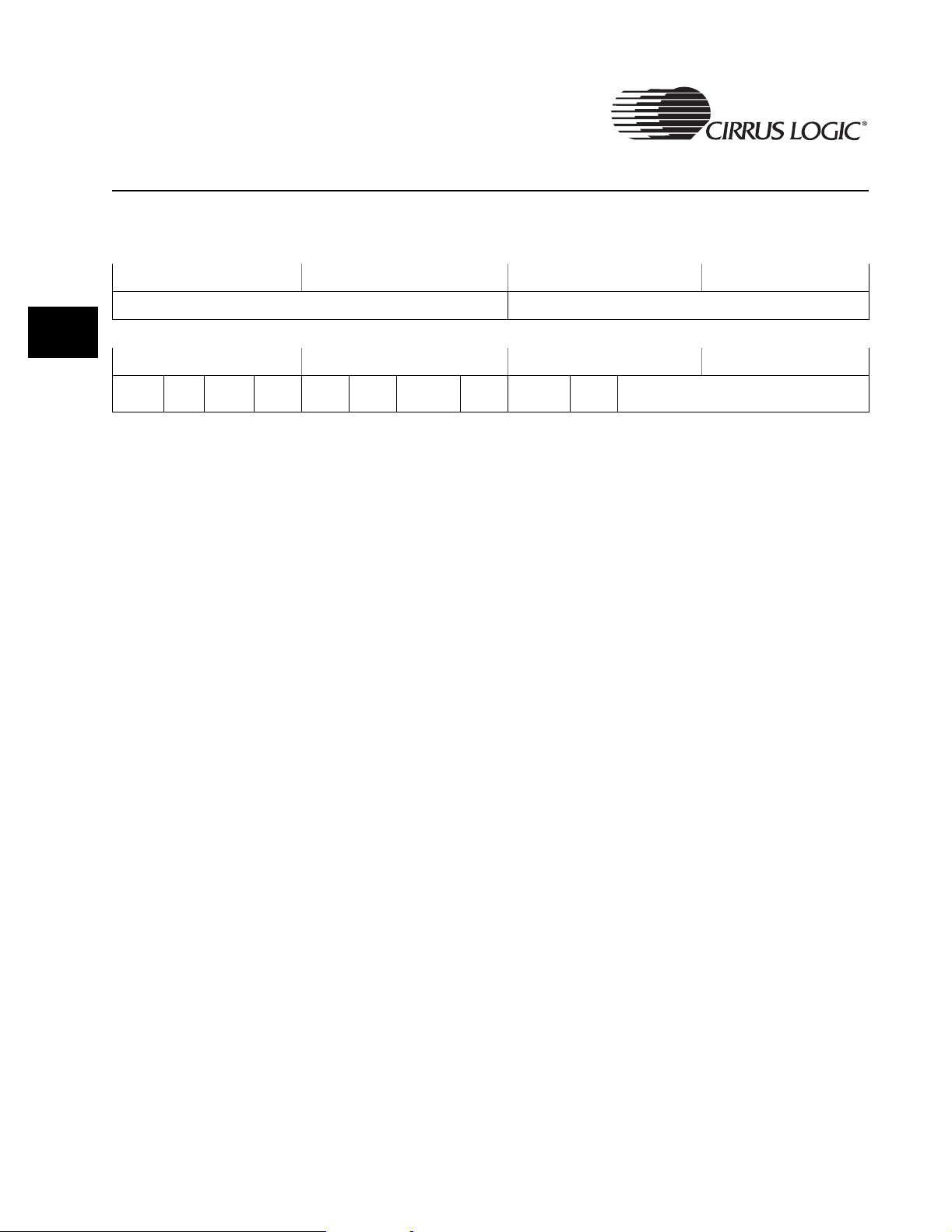

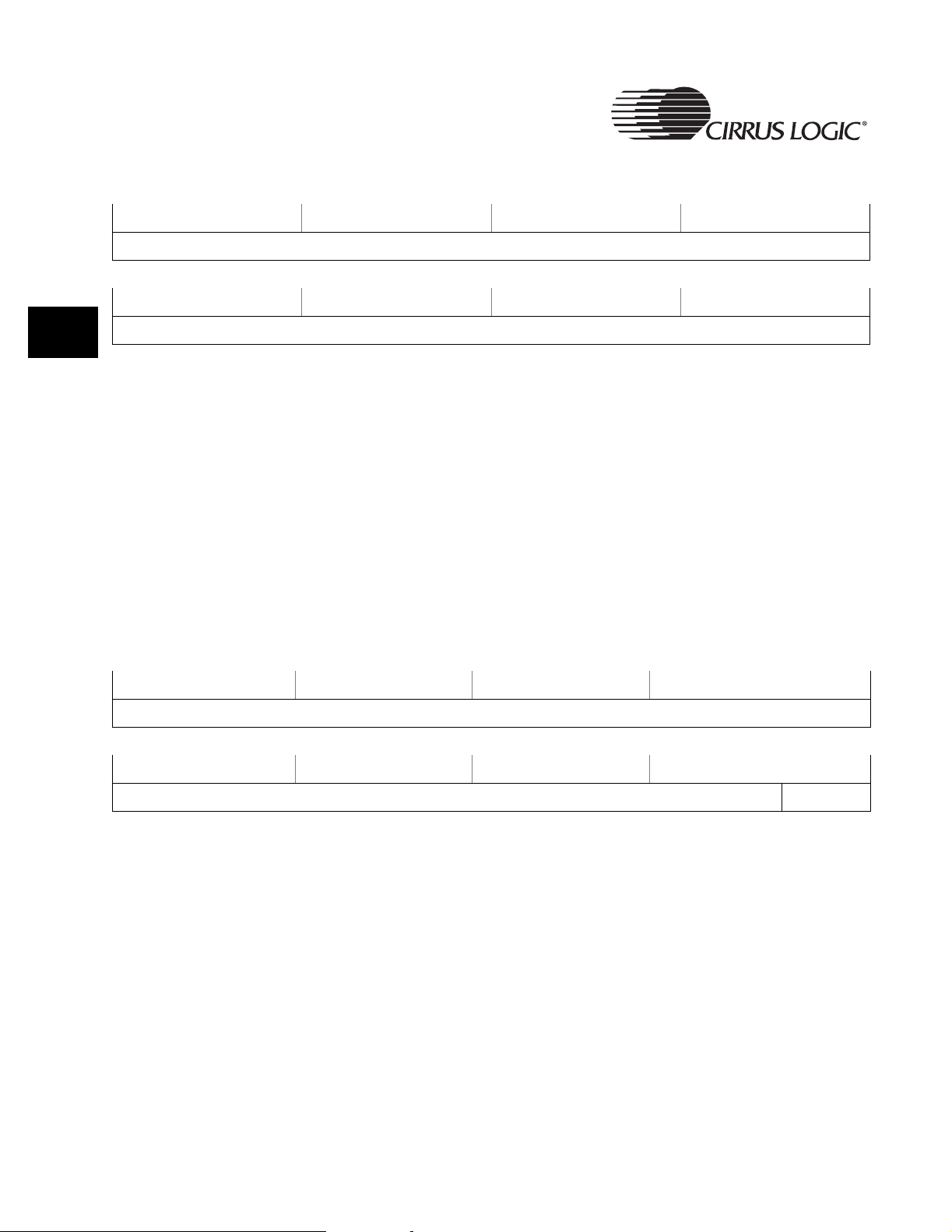

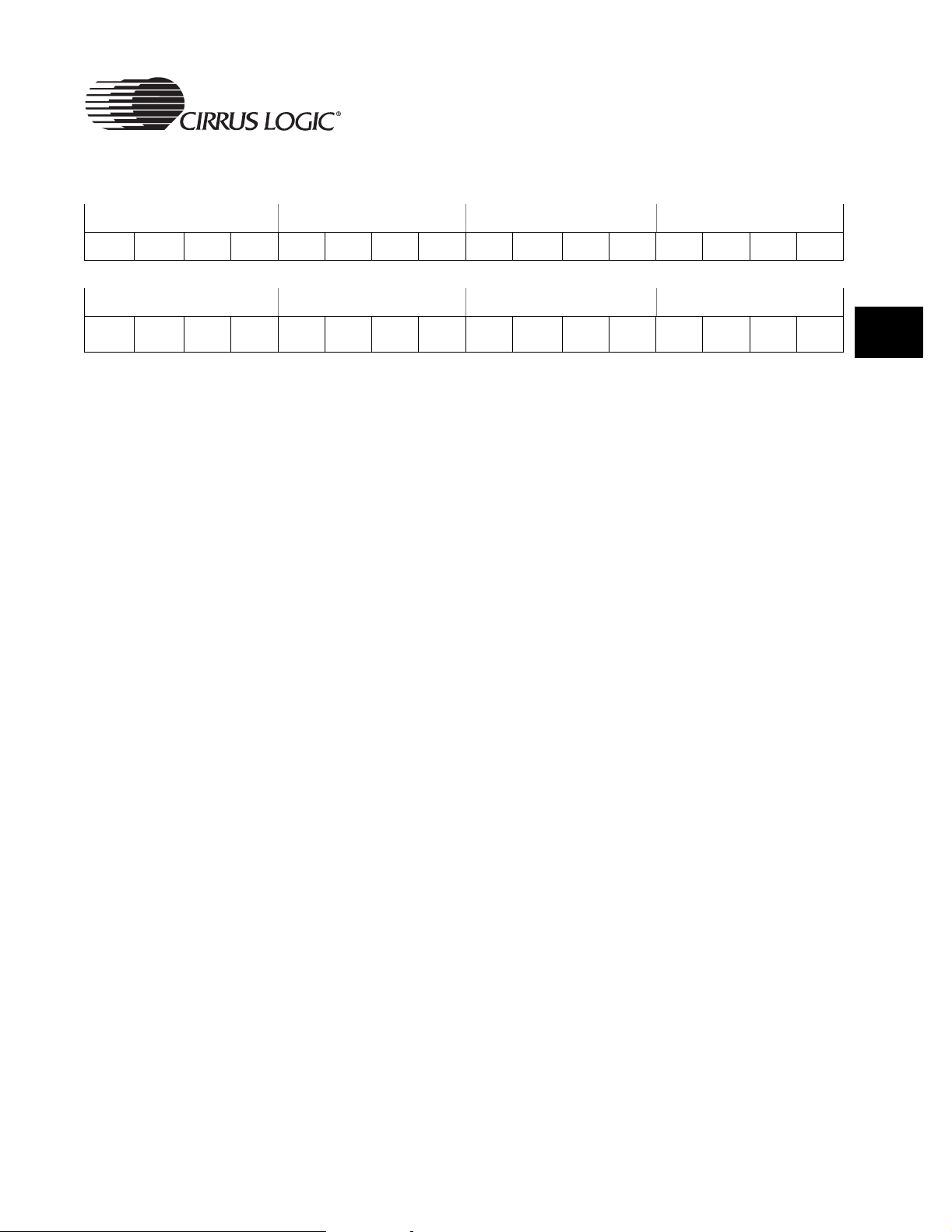

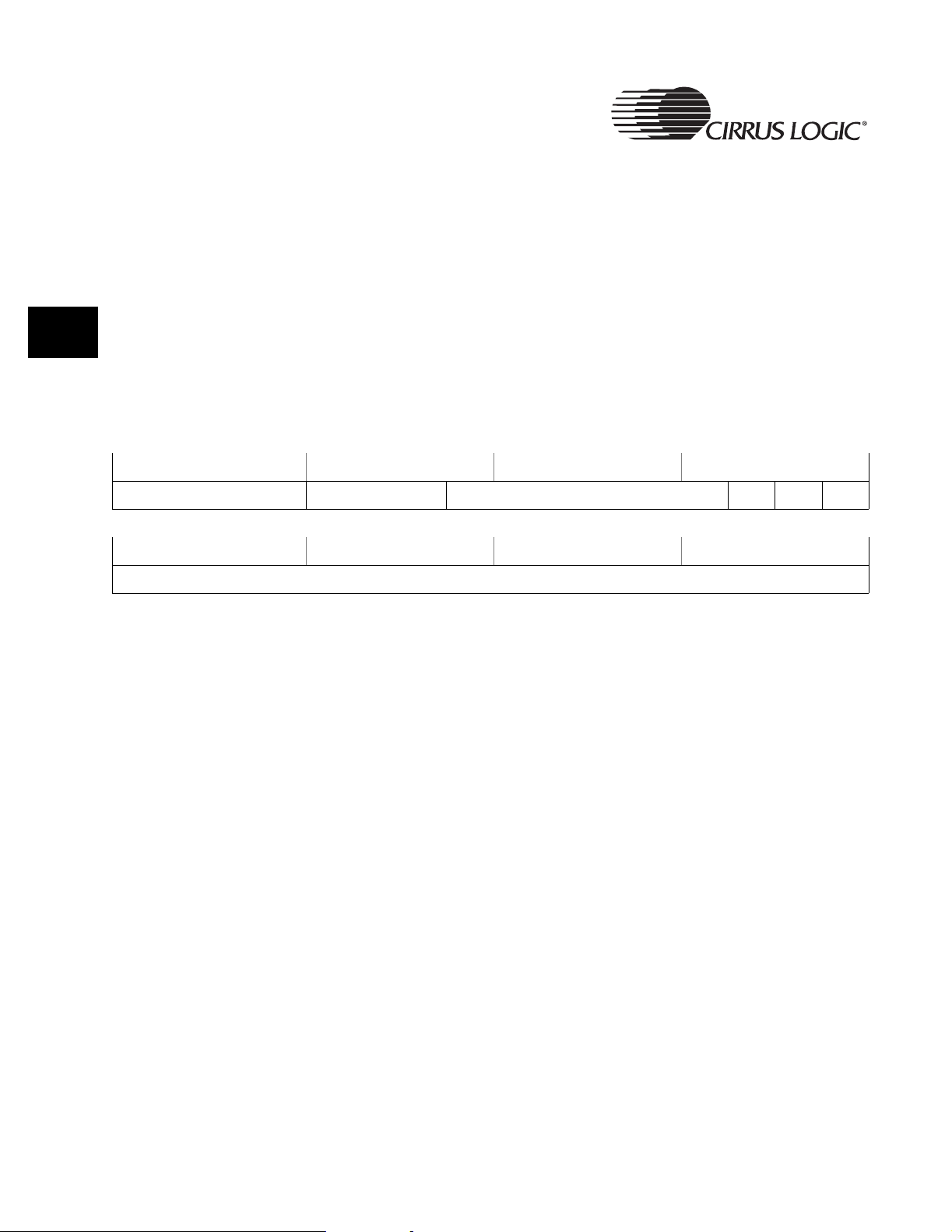

Register Example

Note: This is only and example. For actual SysCfg register information, see “SysCfg”

on page 97.

SysCfg

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

REV RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD SBOOT LCSn7 LCSn6 LASDO LEEDA LEECLK RSVD LCSn2 LCSn1

Address:

0x8093_009C - Read/Write, Software locked

Default:

0x0000_0000

Definition:

System Configuration Register. Provides various system configuration

options.

Bit Descriptions:

RSVD: Reserved. Unknown During Read.

REV: Revision, reads chip Version number: 0 - Rev A, 1 - Rev B,

2 - Rev C, 3 - Rev D.

SBOOT: Serial Boot Flag. This bit is read-only.

1 hardware detected Serial Boot selection,

0 hardware detected Normal Boot.

LCSn7, LCSn6: Latched version of CSn7 and CSn6 respectively. These

are used to define the external bus width for the boot code

boot.

LASDO: Latched version of ASDO pin. Used to select synchronous

versus asynchronous boot device.

LEEDA: Latched version of EEDAT pin.

LEECLK: Define Internal or external boot:

1 Internal

0 External

6 EP9301 User’s Manual - DS636UM2

Copyright 2004 Cirrus Logic

Page 7

LCSn2, LCSn1: Define Watchdog startup action:

0 0 Watchdog disabled, Reset duration disabled

0 1 Watchdog disabled, Reset duration active

1 0 Watchdog active, Reset duration disabled

1 1 Watchdog active, Reset duration active

EP9301 User’s Manual - DS636UM2 7

Copyright 2004 Cirrus Logic

Page 8

This page intentionally blank.

8 EP9301 User’s Manual - DS636UM2

Copyright 2004 Cirrus Logic

Page 9

Table of Contents

Preface............................................................................................................. 3

About the EP9301 User’s Guide ............................................................................................................ 3

How to Use this Guide ...........................................................................................................................3

Related Documents from Cirrus Logic ...................................................................................................4

Reference Documents ...........................................................................................................................4

Notational Conventions ..........................................................................................................................5

Chapter 1 Introduction ............................................................................... 23

1.1 Introduction ...................................................................................................................................23

1.2 EP9301 Features ..........................................................................................................................23

1.3 EP9301 Applications .....................................................................................................................25

1.4 Overview of EP9301 Features ......................................................................................................25

1.4.1 High-Performance ARM920T Processor Core ....................................................................25

1.4.2 MaverickKey™ Unique ID Secures Digital Content and OEM Designs ..............................26

1.4.3 Integrated Two-port USB 2.0 Full Speed Host with Transceivers .......................................26

1.4.4 Integrated Ethernet MAC Reduces BOM Costs ..................................................................26

1.4.5 Multiple Booting Mechanisms Increase Flexibility ...............................................................26

1.4.6 Abundant General Purpose I/Os Build Flexible Systems ....................................................27

1.4.7 General-Purpose Memory Interface (SDRAM, SRAM, ROM and FLASH) .........................27

1.4.8 12-Bit Analog-to-Digital Converter (ADC) Functionality....................................................... 27

Chapter 2 ARM920T Core and Advanced High-Speed Bus (AHB) ......... 29

2.1 Introduction ...................................................................................................................................29

2.2 Overview: ARM920T Processor Core ...........................................................................................29

2.2.1 Features ..............................................................................................................................29

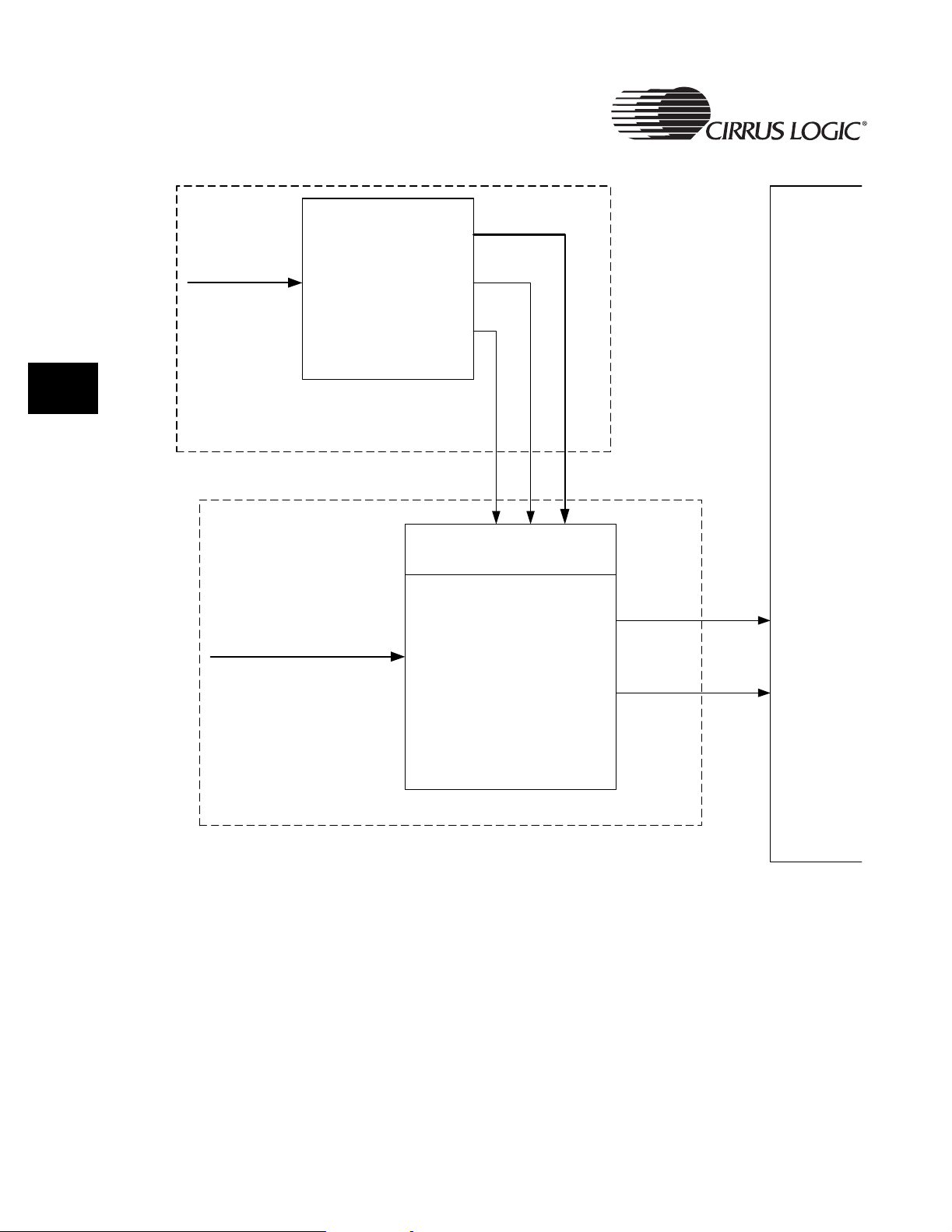

2.2.2 Block Diagram .....................................................................................................................30

2.2.3 Operations...........................................................................................................................30

2.2.3.1 ARM9TDMI Core........................................................................................................31

2.2.3.2 Memory Management Unit .........................................................................................32

2.2.3.3 Cache and Write Buffer..............................................................................................33

2.2.4 AMBA AHB Bus Interface Overview....................................................................................34

2.2.5 EP9301 AHB Implementation Details..................................................................................36

2.2.6 Memory and Bus Access Errors ..........................................................................................37

2.2.7 Bus Arbitration .....................................................................................................................37

2.2.7.1 Main AHB Bus Arbiter ................................................................................................38

2.2.7.2 EBI Bus Arbiter...........................................................................................................39

2.3 AHB Decoder ................................................................................................................................39

2.3.1 AHB Bus Slave ....................................................................................................................40

2.3.2 AHB to APB Bridge..............................................................................................................40

2.3.2.1 Function and Operation of APB Bridge......................................................................41

2.3.3 APB Bus Slave ....................................................................................................................41

2.3.4 Register Definitions .............................................................................................................42

2.3.5 Memory Map........................................................................................................................45

2.3.6 Internal Register Map ..........................................................................................................46

2.3.6.1 Memory Access Rules ...............................................................................................46

Chapter 3 Boot ROM .................................................................................. 59

3.1 Introduction ...................................................................................................................................59

EP9301 User’s Manual - DS636UM2 9

Copyright 2004 Cirrus Logic

Page 10

3.1.1 Boot ROM Hardware Operational Overview ....................................................................... 59

3.1.1.1 Memory Map.............................................................................................................. 59

3.1.2 Boot ROM Software Operational Overview......................................................................... 59

3.1.2.1 Image Header ............................................................................................................ 60

3.1.2.2 Boot Algorithm ........................................................................................................... 60

3.1.2.3 Flowchart................................................................................................................... 62

3.2 Boot Options................................................................................................................................. 62

3.2.1 UART Boot.......................................................................................................................... 63

3.2.2 SPI Boot.............................................................................................................................. 63

3.2.3 FLASH Boot ........................................................................................................................ 64

3.2.4 SDRAM or SyncFLASH Boot.............................................................................................. 64

3.2.5 Synchronous Memory Operation ........................................................................................ 65

Chapter 4 System Controller .....................................................................67

4.1 Introduction ................................................................................................................................... 67

4.1.1 System Startup.................................................................................................................... 67

4.1.2 System Reset...................................................................................................................... 67

4.1.3 Hardware Configuration Control.......................................................................................... 68

4.1.4 Software System Configuration Options ............................................................................. 69

4.1.5 Clock Control....................................................................................................................... 69

4.1.5.1 Oscillators and Programmable PLLs ......................................................................... 70

4.1.5.2 Bus and Peripheral Clock Generation ....................................................................... 71

4.1.5.3 Steps for Clock Configuration.................................................................................... 74

4.1.6 Power Management ............................................................................................................ 75

4.1.6.1 Clock Gatings ............................................................................................................ 75

4.1.6.2 System Power States ................................................................................................ 75

4.1.7 Interrupt Generation ............................................................................................................ 77

4.2 Registers ...................................................................................................................................... 79

Chapter 5 Vectored Interrupt Controller ................................................... 99

5.1 Introduction ................................................................................................................................... 99

5.1.1 Interrupt Priority................................................................................................................. 100

5.1.2 Interrupt Descriptions ........................................................................................................ 102

5.2 Registers .................................................................................................................................... 106

Chapter 6 1/10/100 Mbps Ethernet LAN Controller ................................ 119

6.1 Introduction ................................................................................................................................. 119

6.1.1 Detailed Description.......................................................................................................... 119

6.1.1.1 Host Interface and Descriptor Processor................................................................. 119

6.1.1.2 Reset and Initialization ............................................................................................ 120

6.1.1.3 Powerdown Modes .................................................................................................. 120

6.1.1.4 Address Space ........................................................................................................ 121

6.1.2 MAC Engine...................................................................................................................... 121

6.1.2.1 Data Encapsulation ................................................................................................. 121

6.1.3 Packet Transmission Process........................................................................................... 122

6.1.3.1 Carrier Deference .................................................................................................... 123

6.1.4 Transmit Back-Off ............................................................................................................. 125

6.1.4.1 Transmission ...........................................................................................................125

10 EP9301 User’s Manual - DS636UM2

Copyright 2004 Cirrus Logic

Page 11

6.1.4.2 The FCS Field..........................................................................................................126

6.1.4.3 Bit Order...................................................................................................................126

6.1.4.4 Destination Address (DA) Filter................................................................................126

6.1.4.5 Perfect Address Filtering..........................................................................................126

6.1.4.6 Hash Filter................................................................................................................127

6.1.4.7 Flow Control .............................................................................................................128

6.1.4.8 Receive Flow Control...............................................................................................128

6.1.4.9 Transmit Flow Control ..............................................................................................129

6.1.4.10 Rx Missed and Tx Collision Counters....................................................................129

6.1.4.11 Accessing the MII...................................................................................................130

6.2 Descriptor Processor...................................................................................................................131

6.2.1 Receive Descriptor Processor Queues .............................................................................131

6.2.2 Receive Descriptor Queue ................................................................................................132

6.2.3 Receive Status Queue.......................................................................................................134

6.2.3.1 Receive Status Format.............................................................................................137

6.2.3.2 Receive Flow............................................................................................................140

6.2.3.3 Receive Errors .........................................................................................................141

6.2.3.4 Receive Descriptor Data/Status Flow ......................................................................142

6.2.3.5 Receive Descriptor Example....................................................................................143

6.2.3.6 Receive Frame Pre-Processing ...............................................................................143

6.2.3.7 Transmit Descriptor Processor.................................................................................144

6.2.3.8 Transmit Descriptor Queue ......................................................................................144

6.2.3.9 Transmit Descriptor Format .....................................................................................147

6.2.3.10 Transmit Status Queue ..........................................................................................148

6.2.3.11 Transmit Status Format..........................................................................................150

6.2.3.12 Transmit Flow.........................................................................................................152

6.2.3.13 Transmit Errors ......................................................................................................153

6.2.3.14 Transmit Descriptor Data/Status Flow ...................................................................154

6.2.4 Interrupts ...........................................................................................................................155

6.2.4.1 Interrupt Processing.................................................................................................155

6.2.5 Initialization........................................................................................................................155

6.2.5.1 Interrupt Processing.................................................................................................156

6.2.5.2 Receive Queue Processing......................................................................................156

6.2.5.3 Transmit Queue Processing.....................................................................................156

6.2.5.4 Other Processing .....................................................................................................157

6.2.5.5 Transmit Restart Process.........................................................................................157

6.3 Registers.....................................................................................................................................159

Chapter 7 DMA Controller........................................................................ 213

7.1 Introduction .................................................................................................................................213

7.1.1 DMA Features List.............................................................................................................213

7.1.2 Managing Data Transfers Using a DMA Channel .............................................................214

7.1.3 DMA Operations ................................................................................................................215

7.1.3.1 Memory-to-Memory Channels..................................................................................216

7.1.3.2 Memory-to-Peripheral Channels ..............................................................................216

7.1.4 Internal M2P or P2M AHB Master Interface Functional Description..................................217

7.1.5 M2M AHB Master Interface Functional Description...........................................................218

EP9301 User’s Manual - DS636UM2 11

Copyright 2004 Cirrus Logic

Page 12

7.1.5.1 Software Trigger Mode ............................................................................................ 218

7.1.5.2 Hardware Trigger Mode for Internal Peripherals (SSP) and

for External Peripherals without Handshaking Signals ..................................................... 218

7.1.5.3 Hardware Trigger Mode for External Peripherals with Handshaking Signals .......... 219

7.1.6 AHB Slave Interface Limitations........................................................................................ 219

7.1.7 Interrupt Interface.............................................................................................................. 219

7.1.8 Internal M2P/P2M Data Unpacker/Packer Functional Description.................................... 219

7.1.9 Internal M2P/P2M DMA Functional Description................................................................ 220

7.1.9.1 Internal M2P/P2M DMA Buffer Control Finite State Machine.................................. 220

7.1.9.2 Data Transfer Initiation and Termination ................................................................. 222

7.1.10 M2M DMA Functional Description................................................................................... 223

7.1.10.1 M2M DMA Control Finite State Machine ............................................................... 223

7.1.10.2 M2M Buffer Control Finite State Machine.............................................................. 225

7.1.10.3 Data Transfer Initiation .......................................................................................... 227

7.1.10.4 Data Transfer Termination..................................................................................... 229

7.1.10.5 Memory Block Transfer ......................................................................................... 230

7.1.10.6 Bandwidth Control ................................................................................................. 230

7.1.10.7 External Peripheral DMA Request (DREQ) Mode ................................................. 230

7.1.11 DMA Data Transfer Size Determination.......................................................................... 232

7.1.11.1 Software Initiated M2M and M2P/P2M Transfers.................................................. 232

7.1.11.2 Hardware Initiated M2M Transfers ........................................................................ 232

7.1.12 Buffer Descriptors ........................................................................................................... 233

7.1.12.1 Internal M2P/P2M Channel Rx Buffer Descriptors ................................................ 233

7.1.12.2 Internal M2P/P2M Channel Tx Buffer Descriptors................................................. 233

7.1.12.3 M2M Channel Buffer Descriptors........................................................................... 233

7.1.13 Bus Arbitration................................................................................................................. 233

7.2 Registers .................................................................................................................................... 235

7.2.1 DMA Controller Memory Map............................................................................................ 235

7.2.2 Internal M2P/P2M Channel Register Map......................................................................... 235

Chapter 8 Universal Serial Bus Host Controller .................................... 263

8.1 Introduction ................................................................................................................................. 263

8.1.1 Features............................................................................................................................ 263

8.2 Overview..................................................................................................................................... 263

8.2.1 Data Transfer Types ......................................................................................................... 264

8.2.2 Host Controller Interface ................................................................................................... 265

8.2.2.1 Communication Channels ....................................................................................... 265

8.2.2.2 Data Structures........................................................................................................266

8.2.3 Host Controller Driver Responsibilities.............................................................................. 268

8.2.3.1 Host Controller Management................................................................................... 268

8.2.3.2 Bandwidth Allocation ............................................................................................... 268

8.2.3.3 List Management ..................................................................................................... 269

8.2.3.4 Root Hub ................................................................................................................. 270

8.2.4 Host Controller Responsibilities ........................................................................................ 270

8.2.4.1 USB States.............................................................................................................. 270

8.2.4.2 Frame management ................................................................................................ 270

8.2.4.3 List Processing ........................................................................................................270

12 EP9301 User’s Manual - DS636UM2

Copyright 2004 Cirrus Logic

Page 13

8.2.5 USB Host Controller Blocks...............................................................................................271

8.2.5.1 AHB Slave................................................................................................................271

8.2.5.2 AHB Master..............................................................................................................271

8.2.5.3 HCI Slave Block .......................................................................................................271

8.2.5.4 HCI Master Block .....................................................................................................272

8.2.5.5 USB State Control....................................................................................................272

8.2.5.6 Data FIFO ................................................................................................................272

8.2.5.7 List Processor ..........................................................................................................272

8.2.5.8 Root Hub and Host SIE............................................................................................272

8.3 Registers.....................................................................................................................................273

Chapter 9 Static Memory Controller ....................................................... 305

9.1 Introduction .................................................................................................................................305

9.2 Static Memory Controller Operation............................................................................................306

9.3 Byte Lane Write / Read Control ..................................................................................................308

9.4 Registers.....................................................................................................................................310

Chapter 10 SDRAM, SyncROM, and SyncFLASH Controller................ 313

10.1 Introduction ...............................................................................................................................313

10.1.1 Booting (from SROM or SyncFLASH) .............................................................................313

10.1.1.1 Address Pin Usage ................................................................................................314

10.1.1.2 SDRAM Initialization ..............................................................................................316

10.1.1.3 Programming External Device Mode Register .......................................................317

10.1.1.4 SDRAM Self Refresh .............................................................................................319

10.1.1.5 SROM and SyncFlash............................................................................................320

10.1.1.6 External Synchronous Memory System .................................................................320

10.2 Registers...................................................................................................................................324

Chapter 11 UART1 With HDLC and Modem Control Signals................ 331

11.1 Introduction ...............................................................................................................................331

11.2 UART Overview ........................................................................................................................331

11.2.1 UART Functional Description ..........................................................................................332

11.2.1.1 AMBA APB Interface..............................................................................................332

11.2.1.2 DMA Block .............................................................................................................332

11.2.1.3 Register Block........................................................................................................333

11.2.1.4 Baud Rate Generator.............................................................................................334

11.2.1.5 Transmit FIFO........................................................................................................334

11.2.1.6 Receive FIFO .........................................................................................................334

11.2.1.7 Transmit Logic........................................................................................................334

11.2.1.8 Receive Logic.........................................................................................................334

11.2.1.9 Interrupt Generation Logic .....................................................................................334

11.2.1.10 Synchronizing Registers and Logic......................................................................335

11.2.2 UART Operation ..............................................................................................................335

11.2.2.1 Error Bits................................................................................................................336

11.2.2.2 Disabling the FIFOs ...............................................................................................336

11.2.2.3 System/diagnostic Loopback Testing.....................................................................336

11.2.2.4 UART Character Frame .........................................................................................336

11.2.3 Interrupts .........................................................................................................................337

EP9301 User’s Manual - DS636UM2 13

Copyright 2004 Cirrus Logic

Page 14

11.2.3.1 UARTMSINTR....................................................................................................... 337

11.2.3.2 UARTRXINTR ....................................................................................................... 337

11.2.3.3 UARTTXINTR........................................................................................................ 338

11.2.3.4 UARTRTINTR........................................................................................................ 338

11.2.3.5 UARTINTR ............................................................................................................ 338

11.3 Modem...................................................................................................................................... 338

11.4 HDLC........................................................................................................................................ 339

11.4.1 Overview of HDLC Modes............................................................................................... 339

11.4.2 Selecting HDLC Modes................................................................................................... 340

11.4.3 HDLC Transmit ............................................................................................................... 341

11.4.4 HDLC Receive ................................................................................................................ 342

11.4.5 CRCs............................................................................................................................... 343

11.4.6 Address Matching ........................................................................................................... 343

11.4.7 Aborts.............................................................................................................................. 344

11.4.8 DMA ................................................................................................................................ 344

11.4.9 Writing Configuration Registers ...................................................................................... 345

11.5 UART1 Package Dependency..................................................................................................345

11.5.1 Clocking Requirements ...................................................................................................346

11.5.2 Bus Bandwidth Requirements......................................................................................... 346

11.6 Registers .................................................................................................................................. 348

Chapter 12 UART2 .................................................................................... 369

12.1 Introduction............................................................................................................................... 369

12.2 IrDA SIR Block.......................................................................................................................... 369

12.2.1 IrDA SIR Encoder/decoder Functional Description ......................................................... 369

12.2.1.1 IrDA SIR Transmit Encoder ................................................................................... 370

12.2.1.2 IrDA SIR Receive Decoder.................................................................................... 370

12.2.2 IrDA SIR Operation ......................................................................................................... 371

12.2.2.1 System/diagnostic Loopback Testing .................................................................... 372

12.2.3 IrDA Data Modulation...................................................................................................... 372

12.2.4 Enabling Infrared (Ir) Modes ........................................................................................... 373

12.3 UART2 Package Dependency..................................................................................................373

12.3.1 Clocking Requirements ...................................................................................................373

12.3.2 Bus Bandwidth Requirements......................................................................................... 374

12.4 Registers .................................................................................................................................. 375

Chapter 13 IrDA......................................................................................... 387

13.1 Introduction............................................................................................................................... 387

13.2 IrDA Interfaces.......................................................................................................................... 387

13.3 Shared IrDA Interface Feature ................................................................................................. 388

13.3.1 Overview ......................................................................................................................... 388

13.3.2 Functional Description..................................................................................................... 388

13.3.2.1 General Configuration ........................................................................................... 389

13.3.2.2 Transmitting Data .................................................................................................. 389

13.3.2.3 Receiving Data ...................................................................................................... 392

13.3.2.4 Special Conditions ................................................................................................. 394

13.3.3 Control Information Buffering .......................................................................................... 394

13.4 Medium IrDA Specific Features................................................................................................ 395

14 EP9301 User’s Manual - DS636UM2

Copyright 2004 Cirrus Logic

Page 15

13.4.1 Introduction ......................................................................................................................395

13.4.1.1 Bit Encoding...........................................................................................................395

13.4.1.2 Frame Format ........................................................................................................395

13.4.2 Functional Description .....................................................................................................397

13.4.2.1 Baud Rate Generation ........................................................................................... 397

13.4.2.2 Receive Operation .................................................................................................398

13.4.2.3 Transmit Operation ................................................................................................399

13.5 Fast IrDA Specific Features ......................................................................................................400

13.5.1 Introduction ......................................................................................................................400

13.5.1.1 4PPM Modulation...................................................................................................400

13.5.1.2 4.0 Mbps FIR Frame Format..................................................................................402

13.5.2 Functional Description .....................................................................................................403

13.5.2.1 Baud Rate Generation ........................................................................................... 404

13.5.2.2 Receive Operation .................................................................................................404

13.5.2.3 Transmit Operation ................................................................................................406

13.5.3 IrDA Connectivity.............................................................................................................407

13.5.4 IrDA Integration Information ............................................................................................408

13.5.4.1 Enabling Infrared Modes ........................................................................................408

13.5.4.2 Clocking Requirements ..........................................................................................408

13.5.4.3 Bus Bandwidth Requirements................................................................................ 409

13.6 Registers...................................................................................................................................410

Chapter 14 Timers .................................................................................... 425

14.1 Introduction ...............................................................................................................................425

14.1.1 Features ..........................................................................................................................425

14.1.2 16 and 32-bit Timer Operation.........................................................................................425

14.1.2.1 Free Running Mode ...............................................................................................426

14.1.2.2 Pre-load Mode........................................................................................................426

14.1.3 40-bit Timer Operation.....................................................................................................426

14.2 Registers...................................................................................................................................427

Chapter 15 Watchdog Timer.................................................................... 433

15.1 Introduction ...............................................................................................................................433

15.1.1 Watchdog Activation........................................................................................................434

15.1.2 Clocking Requirements ...................................................................................................434

15.1.3 Reset Requirements........................................................................................................434

15.1.4 Watchdog Status .............................................................................................................434

15.2 Registers...................................................................................................................................435

Chapter 16 Real Time Clock With Software Trim .................................. 439

16.1 Introduction ...............................................................................................................................439

16.1.1 Software Trim ..................................................................................................................439

16.1.1.1 Software Compensation.........................................................................................440

16.1.1.2 Oscillator Frequency Calibration ............................................................................440

16.1.1.3 RTCSWComp Value Determination.......................................................................440

16.1.1.4 Example - Measured Value Split Into Integer and Fractional Component .............441

16.1.1.5 Maximum Error Calculation vs. Real Time Clock Accuracy...................................441

16.1.1.6 Real-Time Interrupt................................................................................................442

EP9301 User’s Manual - DS636UM2 15

Copyright 2004 Cirrus Logic

Page 16

16.1.2 Reset Control.................................................................................................................. 442

16.2 Registers .................................................................................................................................. 443

Chapter 17 I2S Controller ......................................................................... 447

17.1 Introduction............................................................................................................................... 447

2

17.2 I

17.3 I

S Transmitter Channel Overview ........................................................................................... 449

2

S Receiver Channel Overview ............................................................................................... 452

17.3.1 Receiver FIFO................................................................................................................. 453

2

17.4 I

17.5 I

17.6 I

S Configuration and Status Registers.................................................................................... 455

2

S Master Clock Generation.................................................................................................... 455

2

S Bit Clock Rate Generation .................................................................................................. 457

17.6.1 Example of the Bit Clock Generation. ............................................................................. 458

17.6.2 Example of Right Justified LRCK format......................................................................... 458

17.7 Interrupts .................................................................................................................................. 459

17.8 Registers .................................................................................................................................. 461

2

17.8.1 I

17.8.2 I

17.8.3 I

17.8.4 I

S TX Registers ............................................................................................................. 461

2

S RX Registers............................................................................................................. 465

2

S Configuration and Status Registers .......................................................................... 469

2

S Global Status Registers ............................................................................................ 472

Chapter 18 AC’97 Controller .................................................................... 475

18.1 Introduction............................................................................................................................... 475

18.2 Interrupts .................................................................................................................................. 477

18.2.1 Channel Interrupts........................................................................................................... 477

18.2.1.1 RIS......................................................................................................................... 477

18.2.1.2 TIS ......................................................................................................................... 477

18.2.1.3 RTIS ...................................................................................................................... 477

18.2.1.4 TCIS ...................................................................................................................... 478

18.2.2 Global Interrupts.............................................................................................................. 478

18.2.2.1 CODECREADY ..................................................................................................... 478

18.2.2.2 WINT ..................................................................................................................... 478

18.2.2.3 GPIOINT................................................................................................................ 478

18.2.2.4 GPIOTXCOMPLETE ............................................................................................. 478

18.2.2.5 SLOT2INT ............................................................................................................. 479

18.2.2.6 SLOT1TXCOMPLETE........................................................................................... 479

18.2.2.7 SLOT2TXCOMPLETE........................................................................................... 479

18.3 System Loopback Testing ........................................................................................................ 479

18.4 Registers .................................................................................................................................. 480

Chapter 19 Synchronous Serial Port ...................................................... 497

19.1 Introduction............................................................................................................................... 497

19.2 Features ................................................................................................................................... 497

19.3 SSP Functionality ..................................................................................................................... 498

19.4 SSP Pin Multiplex..................................................................................................................... 498

19.5 Configuring the SSP ................................................................................................................. 498

19.5.1 Enabling SSP Operation ................................................................................................. 499

19.5.2 Master/Slave Mode ......................................................................................................... 499

19.5.3 Serial Bit Rate Generation ..............................................................................................499

19.5.4 Frame Format ................................................................................................................ 499

16 EP9301 User’s Manual - DS636UM2

Copyright 2004 Cirrus Logic

Page 17

19.5.5 Texas Instruments® Synchronous Serial Frame Format ................................................500

19.5.6 Motorola® SPI Frame Format .........................................................................................501

19.5.6.1 SPO Clock Polarity.................................................................................................501

19.5.6.2 SPH Clock Phase...................................................................................................501

19.5.7 Motorola SPI Format with SPO=0, SPH=0......................................................................501

19.5.8 Motorola SPI Format with SPO=0, SPH=1.....................................................................503

19.5.9 Motorola SPI Format with SPO=1, SPH=0......................................................................504

19.5.10 Motorola SPI Format with SPO=1, SPH=1....................................................................506

19.5.11 National Semiconductor® Microwire® Frame Format ...................................................507

19.5.11.1 Setup and Hold Time Requirements on SFRMIN with

Respect to SCLKIN in Microwire Mode.............................................................................509

19.6 Registers...................................................................................................................................510

Chapter 20 Analog-to-Digital Converter (ADC) Interface ...................... 517

20.1 Introduction ...............................................................................................................................517

20.2 ADC Operation..........................................................................................................................517

20.3 Registers...................................................................................................................................518

Chapter 21 GPIO Interface ....................................................................... 523

21.1 Introduction ...............................................................................................................................523

21.1.1 Memory Map....................................................................................................................524

21.1.2 Functional Description .....................................................................................................524

21.1.3 Reset ...............................................................................................................................529

21.1.4 GPIO Pin Map .................................................................................................................529

21.2 Registers...................................................................................................................................531

Chapter 22 Security .................................................................................. 553

22.1 Introduction ...............................................................................................................................553

22.2 Features....................................................................................................................................553

22.3 Contact Information...................................................................................................................553

22.4 Registers...................................................................................................................................554

Chapter 23 Glossary................................................................................. 555

EP9301 User’s Manual - DS636UM2 17

Copyright 2004 Cirrus Logic

Page 18

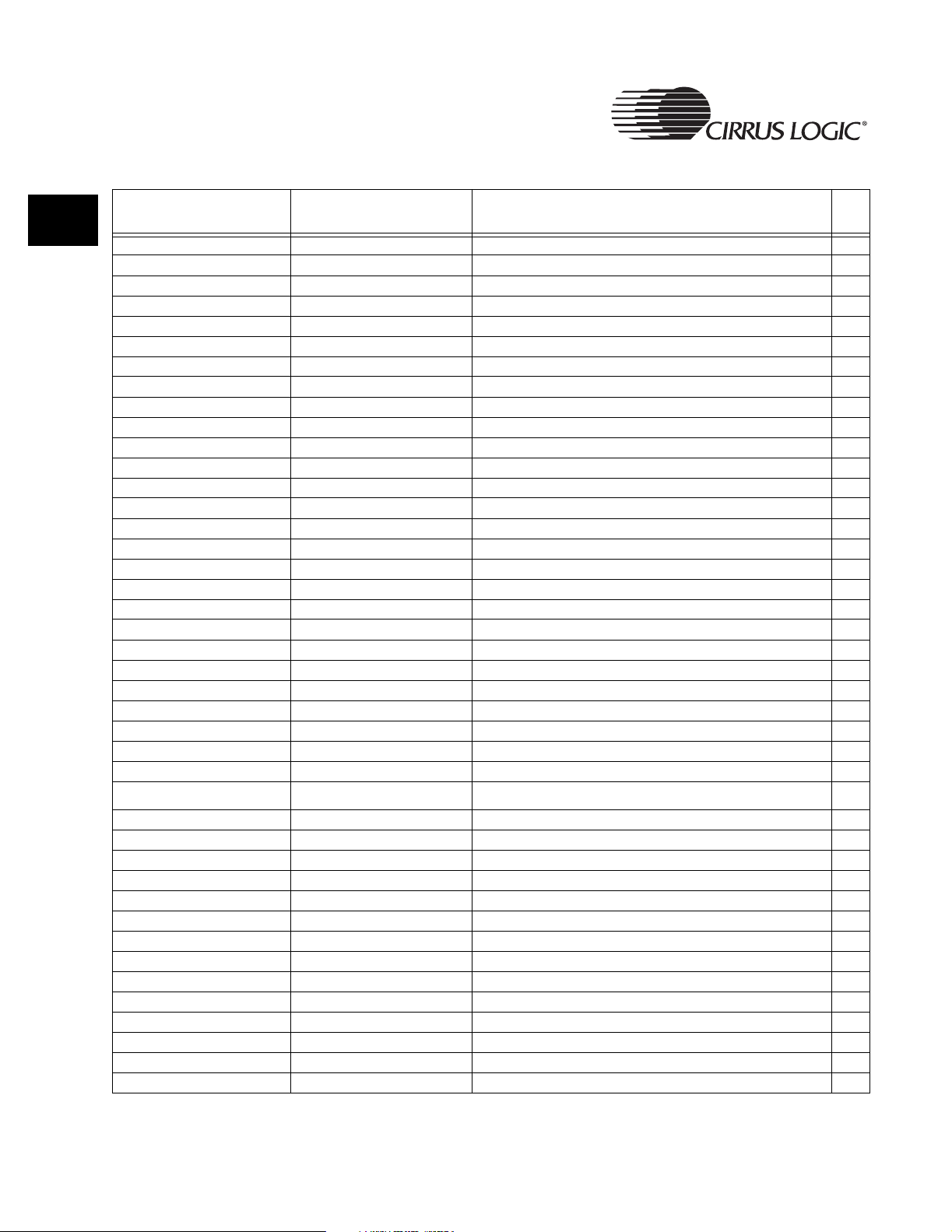

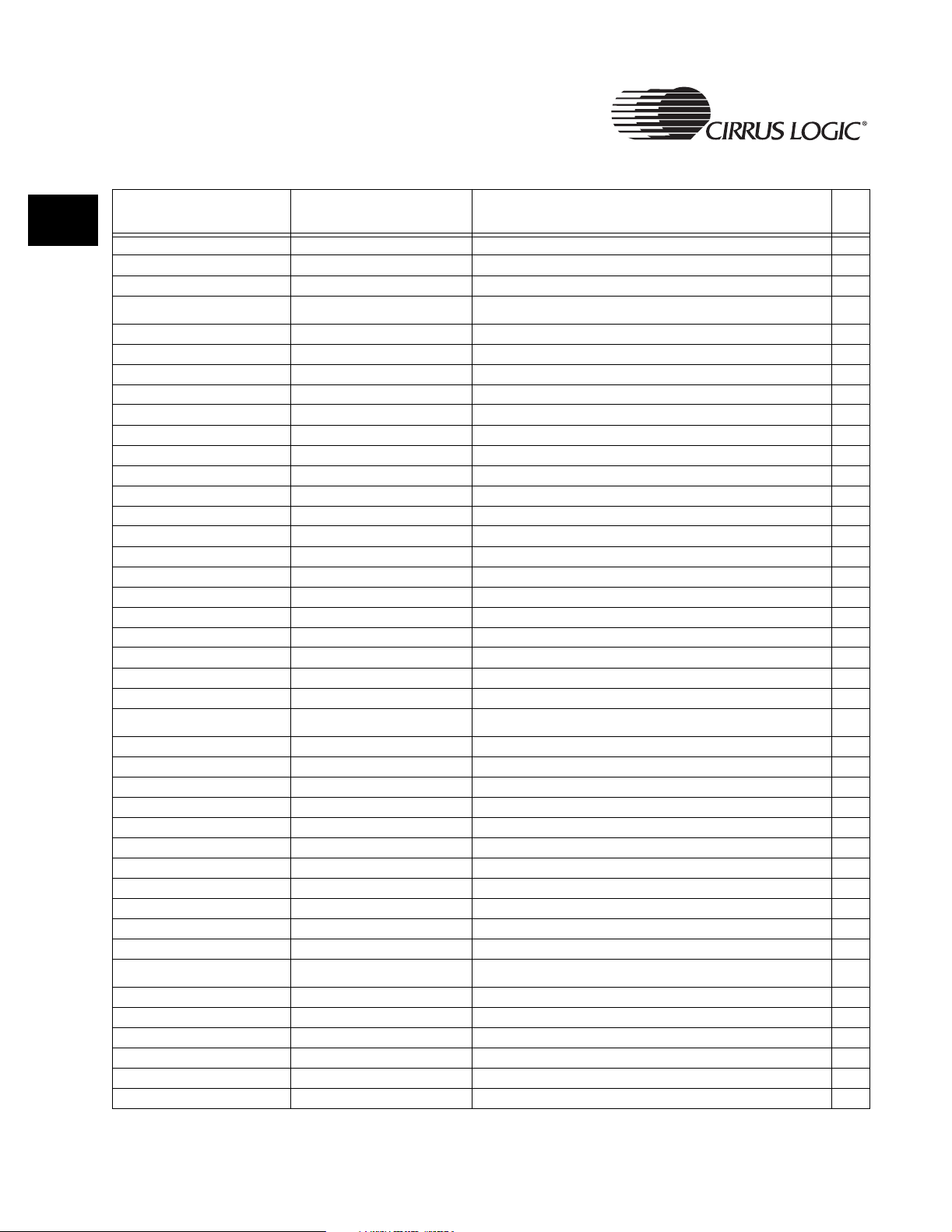

List of Figures

Figure 1-1. EP9301 Block Diagram .................................................................................. 23

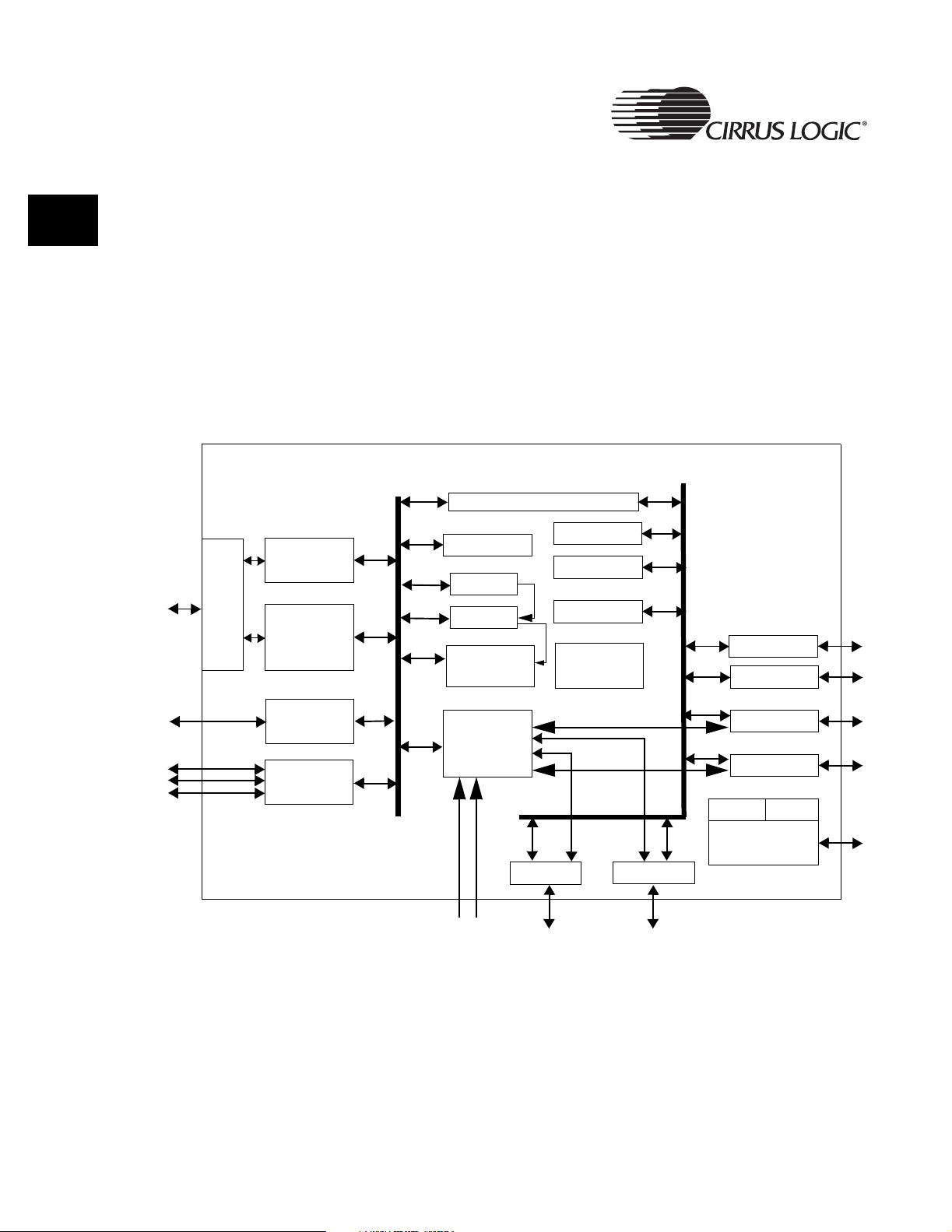

Figure 2-1. ARM920T Block Diagram ................................................................................. 30

Figure 2-2. Typical AMBA AHB System ............................................................................ 35

Figure 2-3. EP9301 Main Data Paths ................................................................................. 36

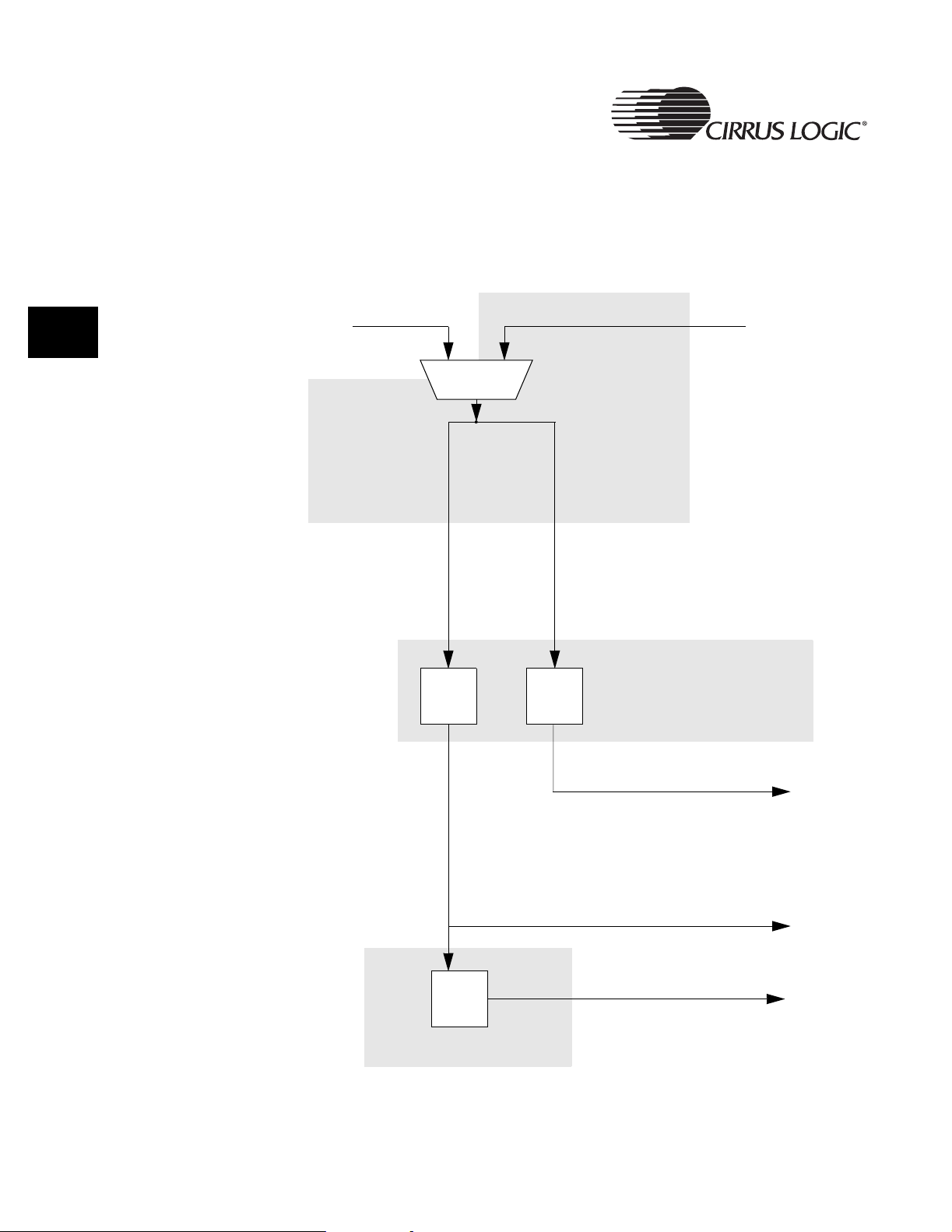

Figure 3-1. Flow Chart of Boot ROM Software ................................................................ 62

Figure 3-2. Flow chart of Boot Sequence for 16-bit SDRAM Devices ............................... 65

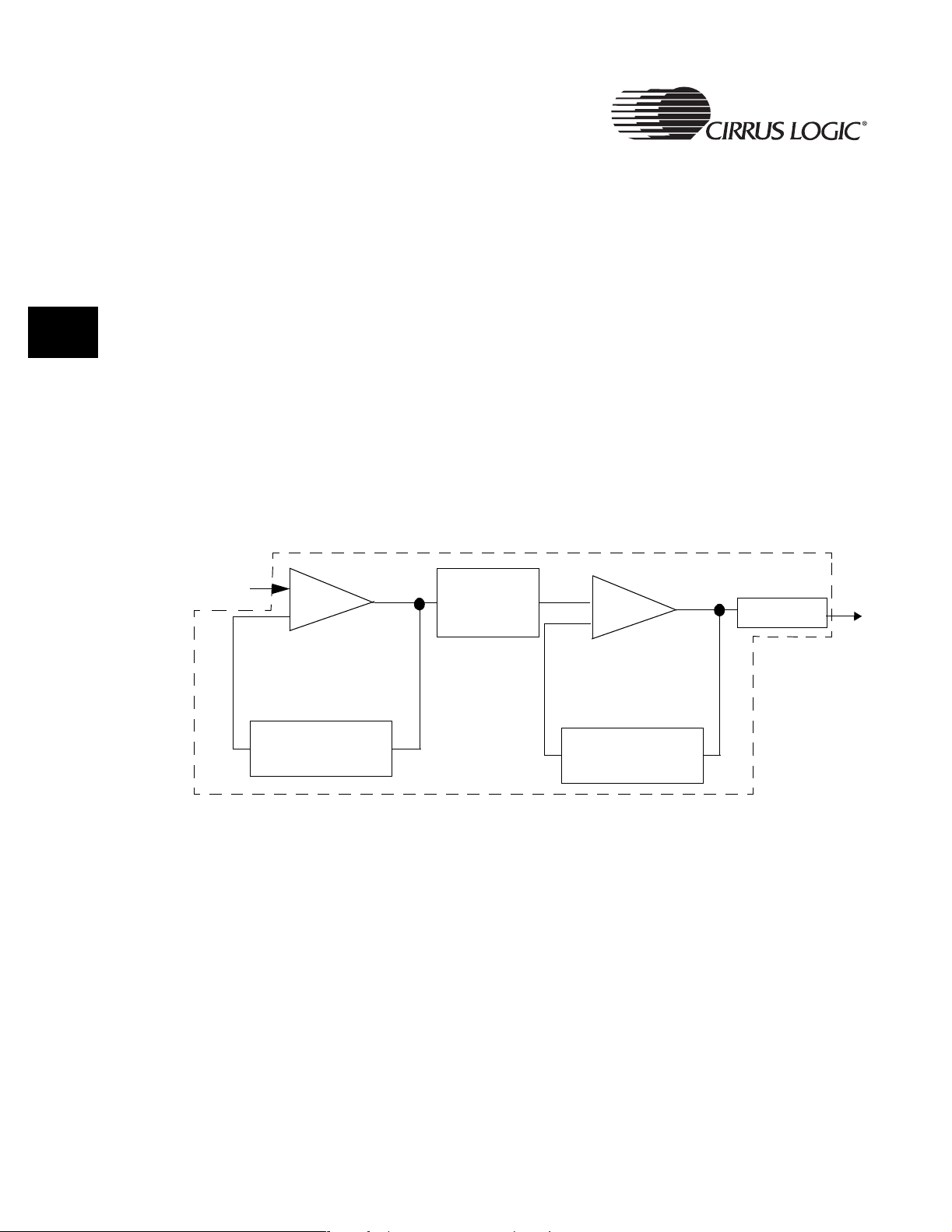

Figure 4-1. Phase Locked Loop (PLL) Structure .............................................................. 70

Figure 4-2. EP9301 Clock Generation System.................................................................... 71

Figure 4-3. Bus Clock Generation ..................................................................................... 72

Figure 4-4. EP9301 Power States and Transitions ........................................................... 76

Figure 5-1. Vectored Interrupt Controller Block Diagram ................................................ 100

Figure 6-1. Block Diagram ................................................................................................ 119

Figure 6-2. Ethernet Frame / Packet Format (Type II only) ............................................... 122

Figure 6-3. Packet Transmission Process ......................................................................... 123

Figure 6-4. Carrier Deference State Diagram .................................................................... 124

Figure 6-5. Data Bit Transmission Order .......................................................................... 126

Figure 6-6. CRC Logic .................................................................................................... 127

Figure 6-7. Receive Descriptor Format and Data Fragments ......................................... 133

Figure 6-8. Receive Status Queue .................................................................................. 136

Figure 6-9. Receive Flow Diagram ................................................................................. 140

Figure 6-10. Receive Descriptor Data/Status Flow ........................................................... 142

Figure 6-11. Receive Descriptor Example ........................................................................ 143

Figure 6-12. Receive Frame Pre-processing .................................................................. 144

Figure 6-13. Transmit Descriptor Format and Data Fragments ........................................ 146

Figure 6-14. Multiple Fragments Per Transmit Frame ...................................................... 146

Figure 6-15. Transmit Status Queue ............................................................................... 149

Figure 6-16. Transmit Flow Diagram .............................................................................. 152

Figure 6-17. Transmit Descriptor Data/Status Flow ........................................................ 154

Figure 7-1. DMA M2P/P2M Finite State Machine.............................................................. 220

Figure 7-2. M2M DMA Control Finite State Machine ......................................................... 223

Figure 7-3. M2M DMA Buffer Finite State Machine .......................................................... 225

Figure 7-4. Edge-triggered DREQ Mode ........................................................................... 231

Figure 8-1. USB Focus Areas ............................................................................................ 264

Figure 8-2. Communication Channels .............................................................................. 265

Figure 8-3. Typical List Structure ...................................................................................... 266

Figure 8-4. Interrupt Endpoint Descriptor Structure .......................................................... 267

Figure 8-5. Sample Interrupt Endpoint Schedule ............................................................. 268

Figure 8-6. Frame Bandwidth Allocation ........................................................................... 269

Figure 8-7. USB Host Controller Block Diagram ................................................................ 271

Figure 9-1. 16-bit read, 16-bit Memory, 0 wait cycles, RBLE = 1,

WAITn Inactive ................................................................................................................ 306

Figure 9-2. 16-bit write, 16-bit Memory, 0 wait cycles, RBLE = 1,

WAITn Inactive ............................................................................................................... 307

Figure 9-3. 16-bit read, 16-bit Memory, RBLE = 1, WAITn Active ..................................... 307

EP9301 User’s Manual - DS636UM2 18

Copyright 2004 Cirrus Logic

Page 19

Figure 9-4. 16-bit write, 16-bit Memory, RBLE = 1, WAITn Active..................................... 308

Figure 11-1. UART Block Diagram ................................................................................... 333

Figure 11-2. UART Character Frame ................................................................................ 337

Figure 12-1. IrDA SIR Encoder/decoder Block Diagram ................................................... 370

Figure 12-2. IrDA Data Modulation (3/16) ......................................................................... 372

Figure 13-1. RZ1/NRZ Bit Encoding Example .................................................................. 395

Figure 13-2. 4PPM Modulation Encoding ......................................................................... 401

Figure 13-3. 4PPM Modulation Example .......................................................................... 401

Figure 13-4. IrDA (4.0 Mbps) Transmission Format .......................................................... 402

2

Figure 17-1. Architectural Overview of the I

S Controller ............................................... 448

Figure 17-2. Transmitter FIFO ........................................................................................ 450

Figure 17-3. Bit Clock Generation Example ................................................................. 458

Figure 17-4. Frame Format for Right Justified Data ................................................... 459

Figure 19-1. Texas Instruments Synchronous Serial Frame Format (Single Transfer) ..... 500

Figure 19-2. TI Synchronous Serial Frame Format (Continuous Transfer) ....................... 501

Figure 19-3. Motorola SPI Frame Format (Single Transfer) with SPO=0 and SPH=0....... 502

Figure 19-4. Motorola SPI Frame Format (Continuous Transfer)

with SPO=0 and SPH=0.................................................................................................. 502

Figure 19-5. Motorola SPI Frame Format with SPO=0 and SPH=1 .................................. 503

Figure 19-6. Motorola SPI Frame Format (Single Transfer) with SPO=1 and SPH=0....... 504

Figure 19-7. Motorola SPI Frame Format (Continuous Transfer)

with SPO=1 and SPH=0.................................................................................................. 505

Figure 19-8. Motorola SPI Frame Format with SPO=1 and SPH=1 .................................. 506

Figure 19-9. Microwire Frame Format (Single Transfer).................................................... 507

Figure 19-10. Microwire Frame Format (Continuous Transfers)........................................ 508

Figure 19-11. Microwire Frame Format, SFRMIN Input Setup and Hold Requirements.... 509

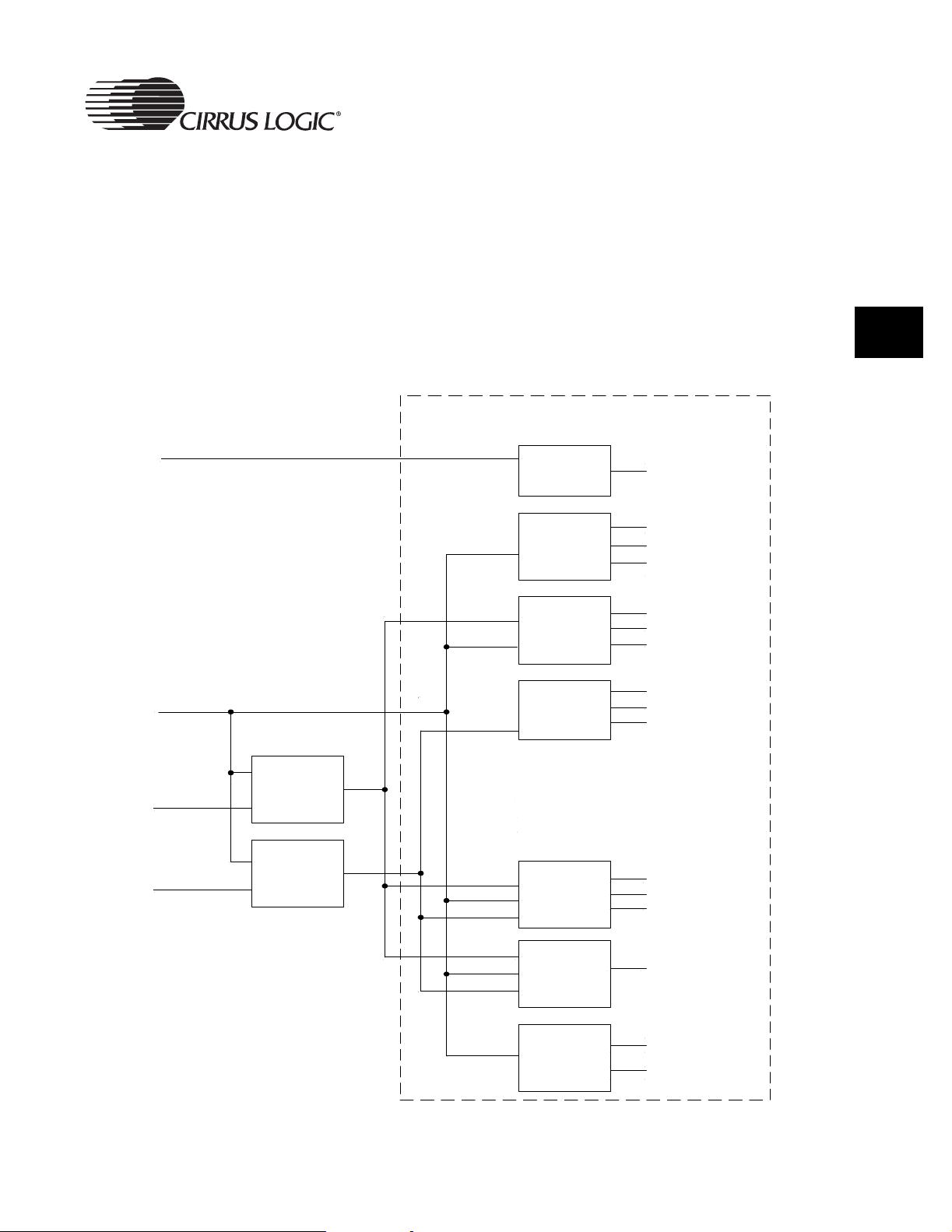

Figure 21-1. System Level GPIO Connectivity ............................................................... 524

Figure 21-2. Signal Connections Within GPIO Port C Control Logic ............................... 526

Figure 21-3. Signal Connections Within GPIO Port E Control Logic ............................... 526

Figure 21-4. Signal Connections Within GPIO Port G Control Logic ............................... 527

Figure 21-5. Signal Connections Within GPIO Port H Control Logic ............................... 527

Figure 21-6. Signal Connections Within the Enhanced GPIO Port A and B Control Logic ....

528

Figure 21-7. Signal Connections Within the Enhanced GPIO Port F Control Logic ........ 529

EP9301 User’s Manual - DS636UM2 19

Copyright 2004 Cirrus Logic

Page 20

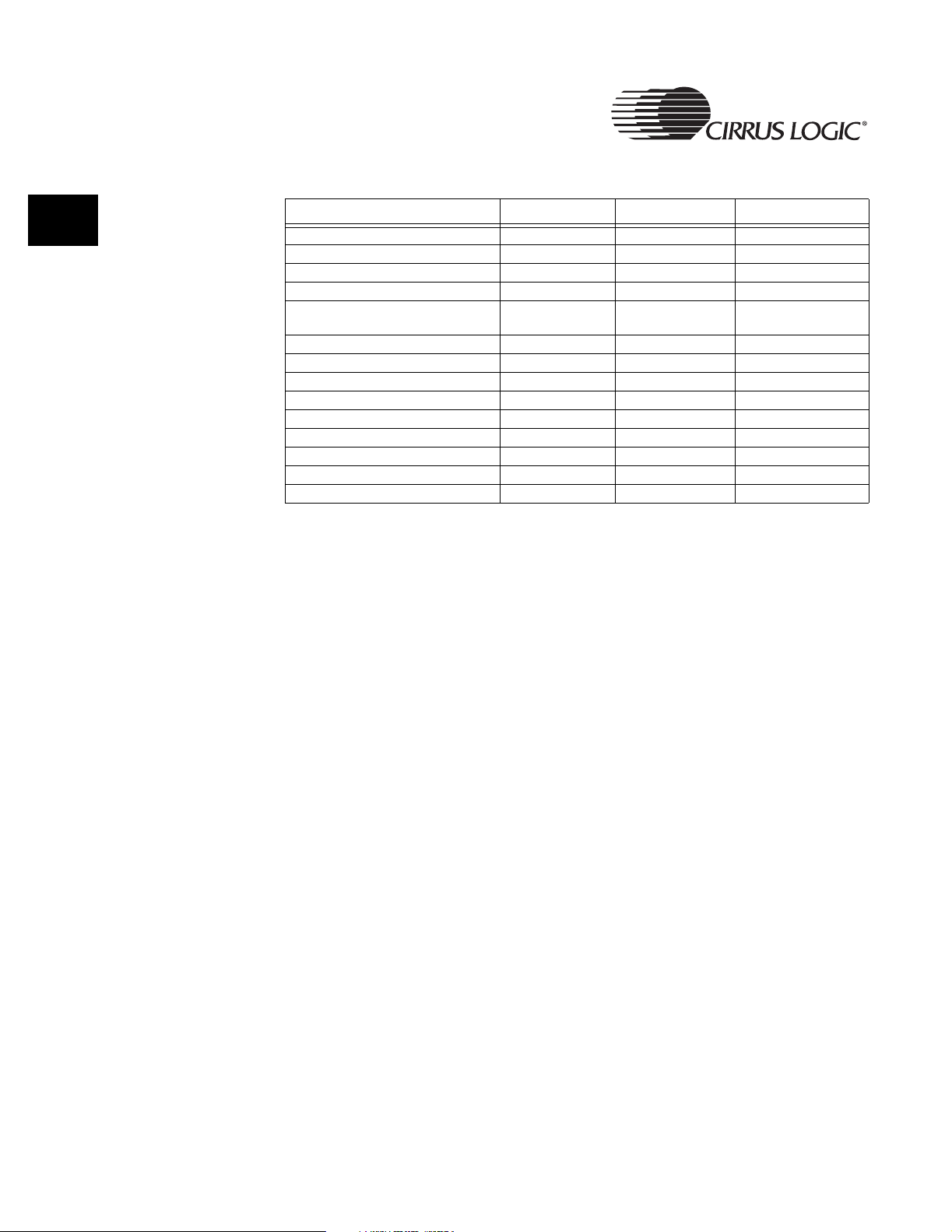

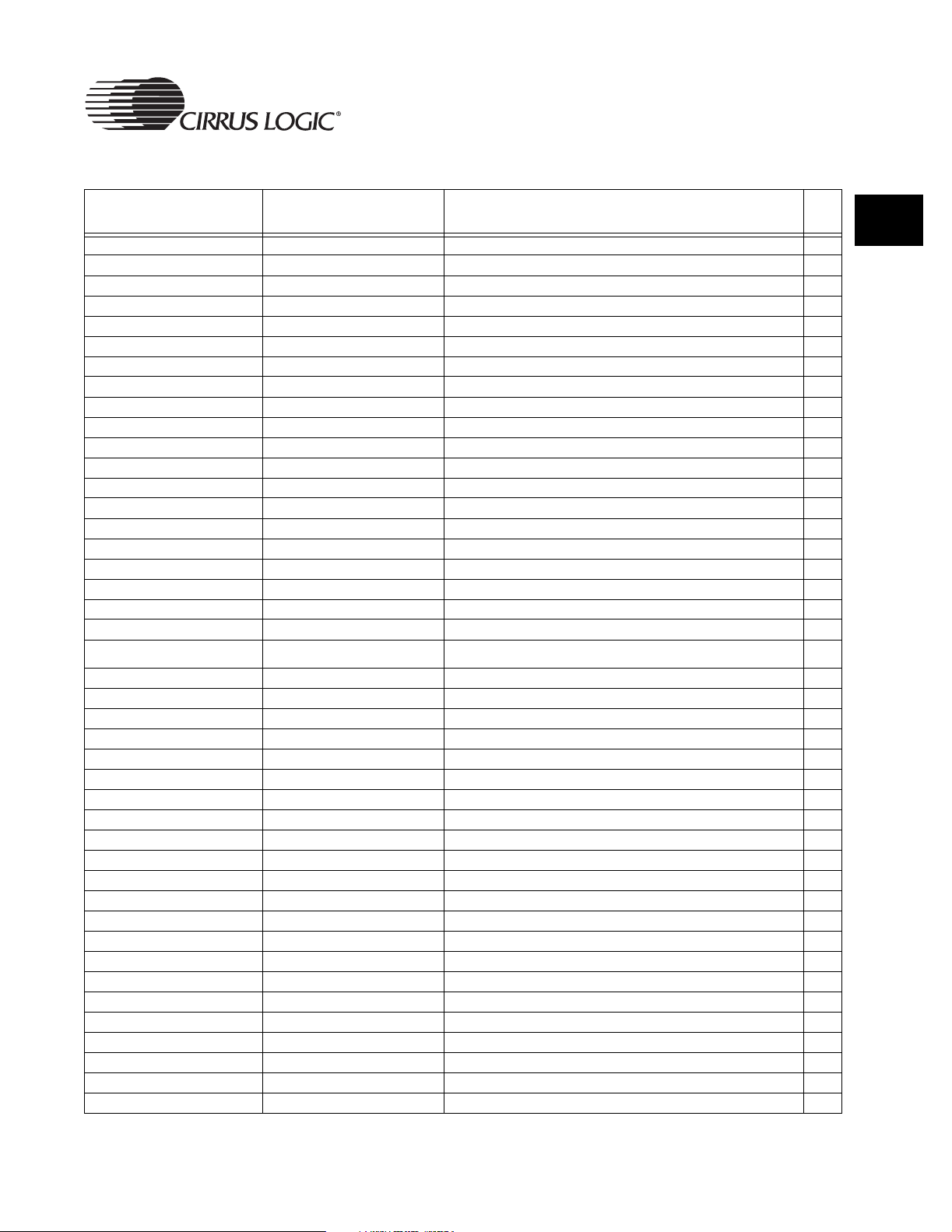

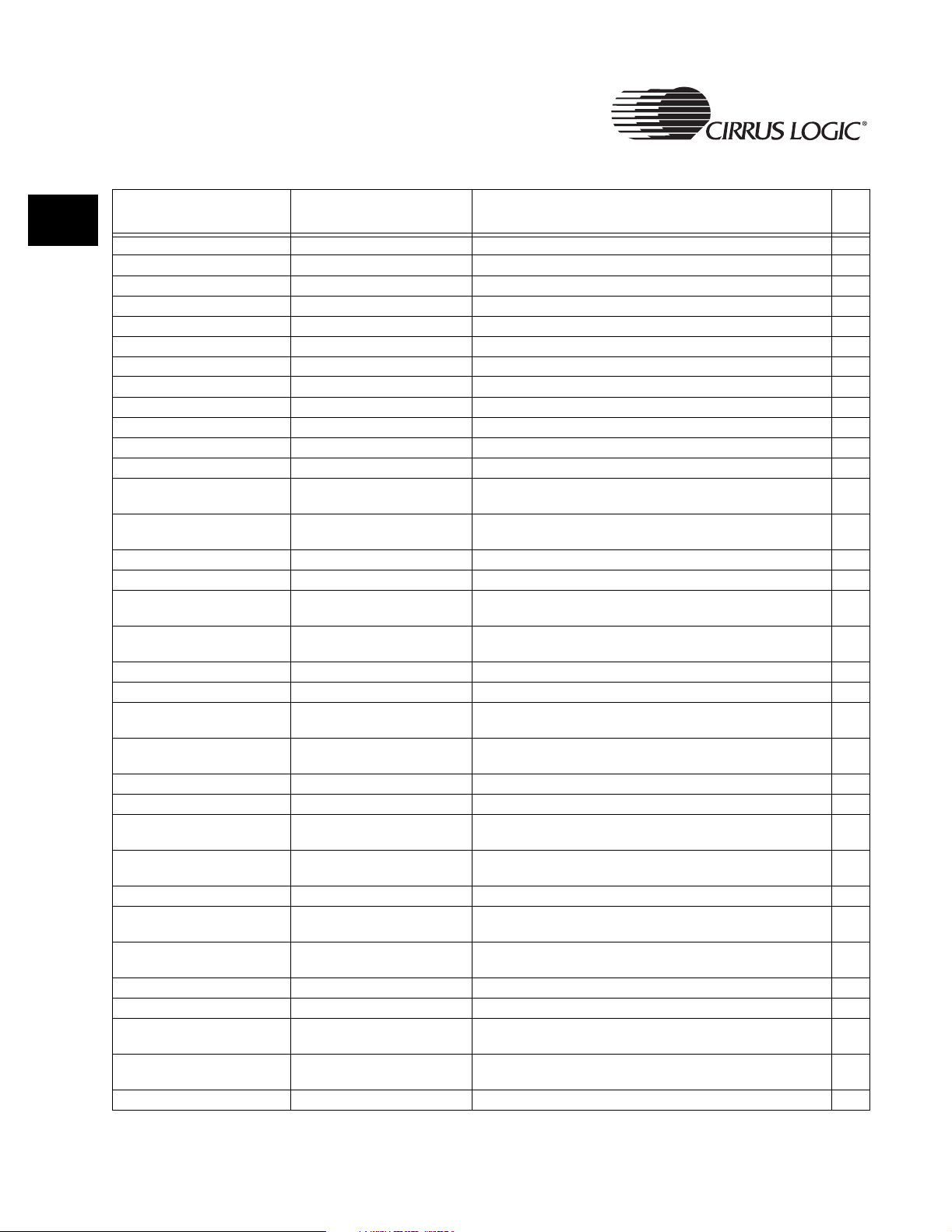

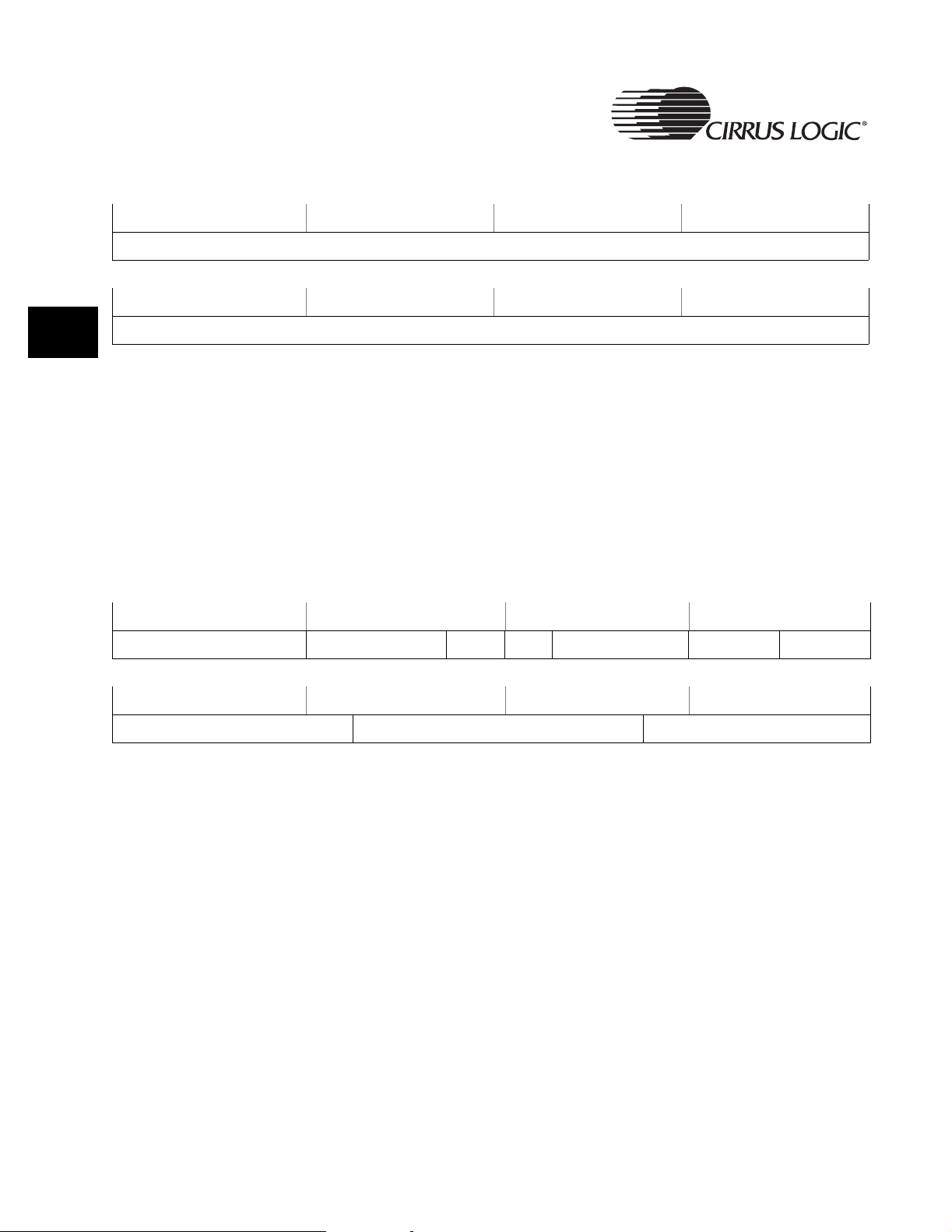

List of Tables

Table 2-1: AHB Arbiter Priority Scheme ......................................................................... 38

Table 2-2: AHB Peripheral Address Range ...................................................................... 40

Table 2-3: APB Peripheral Address Range ..................................................................... 41

Table 2-4: Register Organization Summary ........................................................................ 43

Table 2-5: CP15 ARM920T Register Description ................................................................ 44

Table 2-6: Global Memory Map for the Two Boot Modes .................................................... 45

Table 2-7: Internal Register Map ........................................................................................ 47

Table 3-1: Boot Configuration Options (Normal Boot) ....................................................... 63

Table 4-1: Boot Configuration Options .............................................................................. 69

Table 4-2: Clock Speeds and Sources ............................................................................. 74

Table 4-3: Peripherals with PCLK gating .......................................................................... 75

Table 4-4: Syscon Register List ......................................................................................... 79

Table 4-5: Audio Interfaces Pin Assignment ....................................................................... 92

Table 5-1: Interrupt Configuration...................................................................................... 101

Table 5-2: VICx Register Summary ................................................................................... 106

Table 6-1: FIFO RAM Address Map ................................................................................. 121

Table 6-2: RXCtl.MA and RXCtl.IAHA[0] Relationships .................................................. 128

Table 6-3: Ethernet Register List .................................................................................... 159

Table 6-4: Individual Accept, RxFlow Control Enable and Pause Accept Bits ................ 161

Table 6-5: Address Filter Pointer .................................................................................... 171

Table 7-1: Data Transfer Size............................................................................................ 232

Table 7-2: M2P DMA Bus Arbitration................................................................................. 234

Table 7-3: DMA Memory Map............................................................................................ 235

Table 7-4: Internal M2P/P2M Channel Register Map ........................................................ 236

Table 7-5: PPALLOC Register Bits Decode for a Transmit Channel ............................ 239

Table 7-6: PPALLOC Register Bits Decode for a Receive Channel ................................. 239

Table 7-7: PPALLOC Register Reset Values ................................................................... 239

Table 7-8: M2M Channel Register Map ......................................................................... 245

Table 7-9: BWC Decode Values........................................................................................ 248

Table 7-10: DMA Global Interrupt (DMAGlInt) Register .................................................... 260

Table 8-1: OpenHCI Register Addresses ......................................................................... 273

Table 9-1: nXBLS[1:0] Multiplexing.................................................................................... 308

Table 9-2: WRITING to an External Memory System........................................................ 309

Table 9-3: SMC Register Map ........................................................................................... 310

Table 10-1: Boot Device Selection..................................................................................... 314

Table 10-2: Synchronous Memory Address Decoding ..................................................... 316

Table 10-3: General SDRAM Initialization Sequence ........................................................ 316

Table 10-4: Mode Register Command Decoding............................................................... 318

Table 10-5: Sync Memory CAS Settings ........................................................................... 318

Table 10-6: Sync Memory RAS, (Write) Burst Type Settings ............................................ 319

Table 10-7: Burst Length Settings ..................................................................................... 319

Table 10-8: Chip Select Decoding ..................................................................................... 321