Page 1

EP73xx User’s Guide

http://www.cirrus.com

CopyrightCirrusLogic,Inc. 2003

(All Rights Reserved)

Jan ‘04

DS508UM4

Page 2

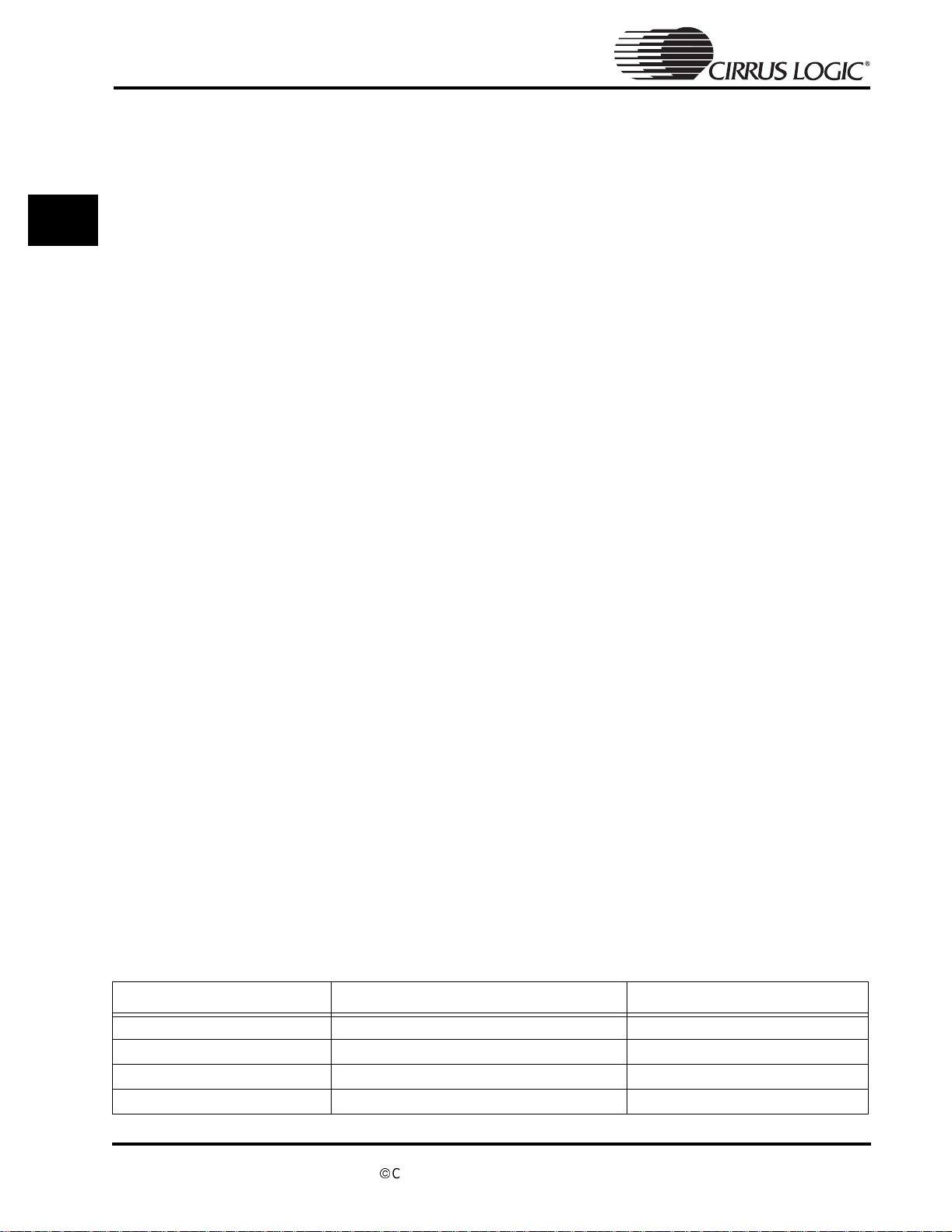

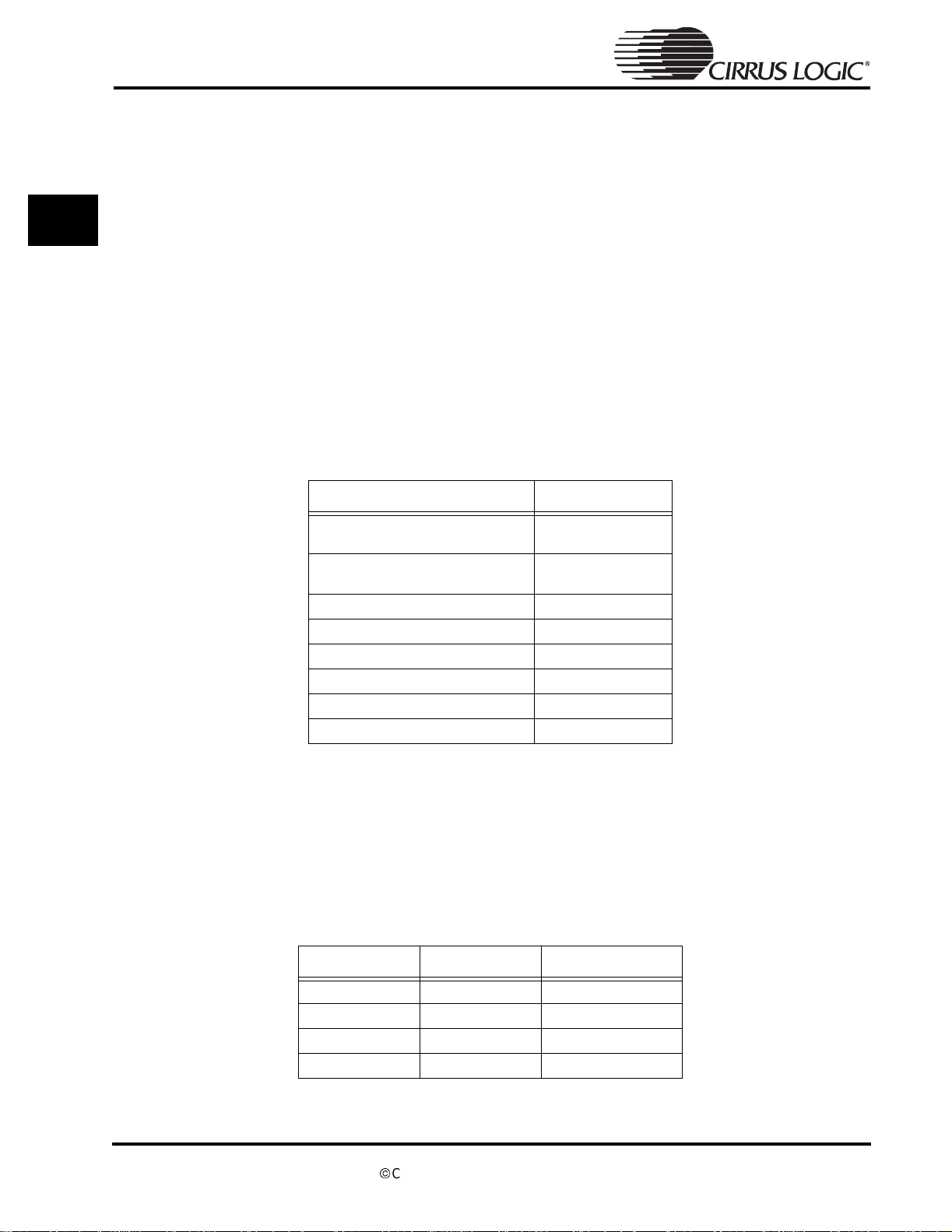

EP73xx User’s Guide Change Control Log

22 Jan 2004

Reason for entry

The Users Guide has changed from Revision 3 (UM3) to Revision 4 (UM4).

Significant Changes:

1. Typographical errors corrected.

2. Manual adapted for 90 MHz operation.

3. Crystal and PLL precision increased to 4 decimal points where applicable.

4. Distinction between 18-74 MHz (PLL) “mode” and precise “operation” frequency made. Example, at 90.3168

operating frequency the processor is in PLL, or 18-74 MHz, mode with a higher PLL Multiplier value.

5. Programming example on page 10-1 updated for consistency.

Updated Tables and Figures:

1. Revision 3, Chapter 5, ADCKSEL table on page 5-5 to 5-6 updated (Revision 4, new table is Table 5-3 on page 5-6.)

2. Revision 3, Chapter 8, Wait State tables on page 8-4 updated (Revision 4, new tables are Tabl e 8 -3 and Table 8-4 on

page 8-4.)

3. Revision 3, Chapter 9, Figure 9-2 on page 8-4, LCD Data to Pixel Mapping updated (Revision 4, new figure is Figure

9-2 on page 9-6.)

4. Revision 3, Chapter 15, Table 15-A on page 15-3, ADC Interface Operation Frequencies updated (Revision 4, new

table is Table 15-2 on page 15-3.)

5. Revision 3, Chapter 16, Table 16-A on page 16-3, Matrix for Programming the MUX updated (Revision 4, new table

is Table 16-2 on page 16-3.)

6. Revision 3, Chapter 16, Figure 16-2 on page 18-5), Digital Audio Clock Generation updated (Revision 4, new figure

is Figure 16-2 on page 16-3.)

7. Revision 3, Chapter 16, Table 16-D on page 16-5, Programmable Audio Divisors for 74 MHz updated (Revision 4,

new table is Table 16-5 on page 16-5.)

8. Revision 4, Chapter 16, Table 16-6 on page 16-6, Programmable Audio Divisors for 90 MHz added.

9. Revision 4, Chapter 17, Table 17-2 on page 17-2, UART Bit Rate at 90 MHz added.

Note: In the online version of this manual, you can click on cross-references that appear in blue text to jump

to the targetedreference.

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative.

To find the one nearest to you go to www.cirrus.com

IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsid iaries ("Cirrus") believe that the information contained in this document is accurate and reliab le. However, the

information is subj ect to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised

to obtain the latest v ersion of relevant information to verify, before placing orders, that information be ing relied on is current and complete. All

products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to

warranty, patent infringement, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use of this

information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the

property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights,

copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained

herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits

or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional

purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY,

OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). CIRRUS PRODUCTS ARE NOT DESIGNED,

AUTHORIZED OR WARRANTED FOR USE IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED

INTO THE BODY, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS (INCLUDING MEDICAL DEVICES, AIRCRAFT

SYSTEMS OR COMPONENTS AND PERSONAL OR AUTOMOTIVE SAFETY OR SECURITY DEVICES). INCLUSION OF CIRRUS

PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK AND CIRRUS DISCLAIMS AND

MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND

FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE

CUSTOMER OR CUSTOMER’S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS,

CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND

OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS’ FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN

CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, the Cirrus Logic logo designs, MaverickKey ar e trademarks of Cirrus Logic, Inc. All other brand and product names in this

document may be trademarks or service marks of their respective owners.

Microsoft Windows and Microsoft are registered trademarks of Microsoft Corporation.

LINUX is a registered trademark of Linus Torvalds.

ii EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

Page 3

EP7309/11/12 User’s Manual - DS508UM4 iii

Copyright Cirrus Logic, Inc. 2003

Page 4

Table of Contents

Chapter 1. Introduction

Overview............................................................................................................................................................ 1-1

Processor ..................................................................................................................................................... 1-1

Peripherals .................................................................................................................................................. 1-1

Memory Map and Register List............................................................................................................... 1-2

Pin Description........................................................................................................................................... 1-6

Block Diagrams ............................................................................................................................................... 1-11

References ................................................................................................................................................. 1-12

Chapter 2. CPU Core

Introduction....................................................................................................................................................... 2-1

Features .............................................................................................................................................................. 2-1

Programming Register List.............................................................................................................................. 2-1

Block Diagram...................................................................................................................................................2-2

Programming Examples ..................................................................................................................................2-2

Operational Overview...................................................................................................................................... 2-4

MMU............................................................................................................................................................ 2-4

TLB............................................................................................................................................................... 2-5

Cache ........................................................................................................................................................... 2-5

Write Buffer ................................................................................................................................................ 2-6

Debug Interface.......................................................................................................................................... 2-7

CPU Register Definitions................................................................................................................................. 2-7

ARM720T Core Coprocessor Registers................................................................................................... 2-8

CPU Clocks ................................................................................................................................................. 2-9

PLL Multiplier Write Register (PLLW) .............................................................................................. 2-11

PLL Multiplier Read Register (PLLR)............................................................................................... 2-11

CPU State Control.................................................................................................................................... 2-12

State Control Register Descriptions ............................................................................................................. 2-13

Enter the Standby State Register (STDBY)..................................................................................... 2-13

Enter the Idle State Register (HALT) ............................................................................................... 2-14

Power Up Sequence................................................................................................................................. 2-14

RESET ........................................................................................................................................................ 2-15

1Contents

Chapter 3. Timers

Introduction....................................................................................................................................................... 3-1

Features .............................................................................................................................................................. 3-1

Timer Register List............................................................................................................................................ 3-1

Programming Example .................................................................................................................................... 3-1

Operational Overview...................................................................................................................................... 3-2

Free Running Mode................................................................................................................................... 3-2

Prescale Mode ............................................................................................................................................ 3-3

RTC Timer...................................................................................................................................................3-3

EP7309/11/12 User’s Manual - DS508UM4 iii

CopyrightCirrusLogic,Inc.2003

Page 5

Contents

Timer Register Descriptions............................................................................................................................ 3-3

Timer Counter 1 Data Register (TC1D) ..............................................................................................3-3

Timer Counter 2 Data Register(TC2D)...............................................................................................3-3

Real Time Clock Data Register (RTCDR) ..........................................................................................3-3

Real Time Clock Match Register (RTCMR)........................................................................................3-4

Chapter 4. Interrupt Controller

Introduction....................................................................................................................................................... 4-1

Features .............................................................................................................................................................. 4-1

Interrupt Register List...................................................................................................................................... 4-1

Programming Examples .................................................................................................................................. 4-2

Operational Overview...................................................................................................................................... 4-3

Interrupt Types and Priorities ................................................................................................................. 4-4

Interrupt Operation................................................................................................................................... 4-4

Interrupt Listing......................................................................................................................................... 4-5

Interrupt Latencies in Different States.................................................................................................... 4-6

Interrupt Register Descriptions ...................................................................................................................... 4-8

Interrupt Status Register 1 (INTSR1) .................................................................................................4-8

Interrupt Mask Register 1 (INTMR1) ................................................................................................4-10

Interrupt Mask Register 2 (INTMR2) ................................................................................................4-12

Interrupt Status Register 3 (INTSR3) ...............................................................................................4-12

Interrupt Mask Register 3 (INTMR3) ................................................................................................4-13

Battery Low End of Interrupt (BLEOI) ...............................................................................................4-13

Media Change End of Interrupt (MCEOI) .........................................................................................4-13

Tick End of Interrupt (TEOI) .............................................................................................................4-13

TC1 End of Interrupt (TC1EOI).........................................................................................................4-13

TC1 End of Interrupt (TC2EOI).........................................................................................................4-14

RTC Match End of Interrupt (RTCEOI).............................................................................................4-14

UART1 Modem Status Changed End of Interrupt (UMSEOI)...........................................................4-14

CODEC End of Interrupt (COEOI) ....................................................................................................4-14

Keyboard End of Interrupt (KBDEOI) ...............................................................................................4-14

SSI2 FIFO Overflow End of Interrupt (SRXEOF) .............................................................................4-14

Chapter 5. System Registers

Introduction....................................................................................................................................................... 5-1

Features .............................................................................................................................................................. 5-1

System Register List ......................................................................................................................................... 5-2

Programming Example.................................................................................................................................... 5-2

Operational Overview...................................................................................................................................... 5-3

Buzzer.......................................................................................................................................................... 5-3

Debug Mode............................................................................................................................................... 5-3

System Control Register Descriptions ........................................................................................................... 5-4

System Control Register 1 (SYSCON1) .............................................................................................5-4

System Control Register 2 (SYSCON2) .............................................................................................5-7

System Control Register 3 (SYSCON3) .............................................................................................5-8

System Flag Register 1 (SYSFLG1)...................................................................................................5-9

System Flag Register 2 (SYSFLG2).................................................................................................5-12

Clear all Start-up Reason Flag Register (STFCLR) .........................................................................5-13

32-bit Unique ID Register (UNIQID) .................................................................................................5-13

Random ID 0 Register, bits 31-0 (RANDID0) ...................................................................................5-13

Random ID 1 Register, bits 63-32 (RANDID1) .................................................................................5-13

Random ID 2 Register, bits 95-64 (RANDID2) .................................................................................5-13

Random ID 3 Register, bits 127-96 (RANDID3) ...............................................................................5-13

iv EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

Page 6

Chapter 6. Processor Support

Introduction....................................................................................................................................................... 6-1

Features .............................................................................................................................................................. 6-1

Operational Overview...................................................................................................................................... 6-1

Internal Boot Mode.................................................................................................................................... 6-2

External Boot Mode................................................................................................................................... 6-2

Endianess .................................................................................................................................................... 6-4

Chapter 7. SDRAM Controller

Introduction....................................................................................................................................................... 7-1

Features .............................................................................................................................................................. 7-1

SDRAM Register List........................................................................................................................................ 7-1

Programming Example .................................................................................................................................... 7-2

Operational Overview...................................................................................................................................... 7-2

System Initialization..................................................................................................................................7-2

Byte Masks .................................................................................................................................................. 7-3

SDRAM Register Descriptions........................................................................................................................ 7-3

SDRAM Control Register (SDCONF) ................................................................................................ 7-3

SDRAM Refresh Period Register (SDRFPR) .................................................................................... 7-4

Contents

Chapter 8. SRAM/Expansion Bus Controller

Introduction....................................................................................................................................................... 8-1

Features .............................................................................................................................................................. 8-1

SRAM / Expansion Bus Register List ............................................................................................................ 8-1

Programming Example .................................................................................................................................... 8-1

Operational Overview...................................................................................................................................... 8-2

SRAM / Expansion Bus Register Descriptions ............................................................................................ 8-3

Memory Configuration Register 1 (MEMCFG1)................................................................................. 8-3

Memory Configuration Register 2 (MEMCFG2)................................................................................. 8-5

Chapter 9. LCD Interface

Introduction....................................................................................................................................................... 9-1

Features .............................................................................................................................................................. 9-1

LCD Register List.............................................................................................................................................. 9-1

Programming Example .................................................................................................................................... 9-2

Operational Overview...................................................................................................................................... 9-2

LCD Controller External Memory........................................................................................................... 9-2

LCD DMA Controller................................................................................................................................ 9-3

Gray Scale ...................................................................................................................................................9-4

Hardware Interface.................................................................................................................................... 9-6

Color LCDs ................................................................................................................................................. 9-6

LCD Register Descriptions .............................................................................................................................. 9-7

LCD Control Register (LCDCON)...................................................................................................... 9-7

LCD Palette Registers ....................................................................................................................... 9-8

LCD Frame Buffer Start Address (FBADDR)..................................................................................... 9-9

Chapter 10. Keyboard Interface

Introduction..................................................................................................................................................... 10-1

Features ............................................................................................................................................................ 10-1

Register List ..................................................................................................................................................... 10-1

Programming Example .................................................................................................................................. 10-1

Operational Overview.................................................................................................................................... 10-2

Keyboard Interrupt Matrix..................................................................................................................... 10-2

EP7309/11/12 User’s Manual - DS508UM4 v

CopyrightCirrusLogic,Inc.2003

Page 7

Contents

Chapter 11. General Purpose I/O (GPIO)

Introduction..................................................................................................................................................... 11-1

Features ............................................................................................................................................................ 11-1

General Purpose I/O (GPIO) Register List................................................................................................. 11-1

Programming Example.................................................................................................................................. 11-2

Operational Overview.................................................................................................................................... 11-2

Register Descriptions ..................................................................................................................................... 11-2

Chapter 12. PWM Interface

Introduction..................................................................................................................................................... 12-1

Features ............................................................................................................................................................ 12-1

Block Diagram................................................................................................................................................. 12-1

PWM (Pulse Width Modulator) Register List ............................................................................................12-2

Programming Example.................................................................................................................................. 12-2

Operational Overview.................................................................................................................................... 12-2

PWM Register Descriptions .......................................................................................................................... 12-3

Pump Control Register (PMPCON) ..................................................................................................12-3

Chapter 13. Dedicated LED Flasher

Introduction..................................................................................................................................................... 13-1

LED Flasher Register List .............................................................................................................................. 13-1

Programming Example.................................................................................................................................. 13-1

Operational Overview.................................................................................................................................... 13-1

Register Definitions ........................................................................................................................................ 13-2

LED Flasher Register (LEDFLSH) ....................................................................................................13-2

Chapter 14. JTAG Interface

Introduction..................................................................................................................................................... 14-1

Features ............................................................................................................................................................ 14-1

Operational Overview.................................................................................................................................... 14-1

Boundary Scan ......................................................................................................................................... 14-2

Debug Modes ........................................................................................................................................... 14-3

Software Selectable Test Functionality................................................................................................. 14-4

Chapter 15. SSI Port

Introduction..................................................................................................................................................... 15-1

Features ............................................................................................................................................................ 15-1

SSI Port Register List ...................................................................................................................................... 15-1

Programming Example.................................................................................................................................. 15-1

Operational Overview.................................................................................................................................... 15-2

SSI1/ADC Interface................................................................................................................................. 15-2

SSI Port Register Descriptions ...................................................................................................................... 15-4

Synchronous Serial ADC Interface Data Register (SYNCIO)...........................................................15-4

Chapter 16. DAI/CODEC/SSI2

Introduction..................................................................................................................................................... 16-1

Features ............................................................................................................................................................ 16-1

Block Diagram................................................................................................................................................. 16-2

DAI/CODEC/SSI2 Register List.................................................................................................................. 16-2

Programming Example.................................................................................................................................. 16-2

vi EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

Page 8

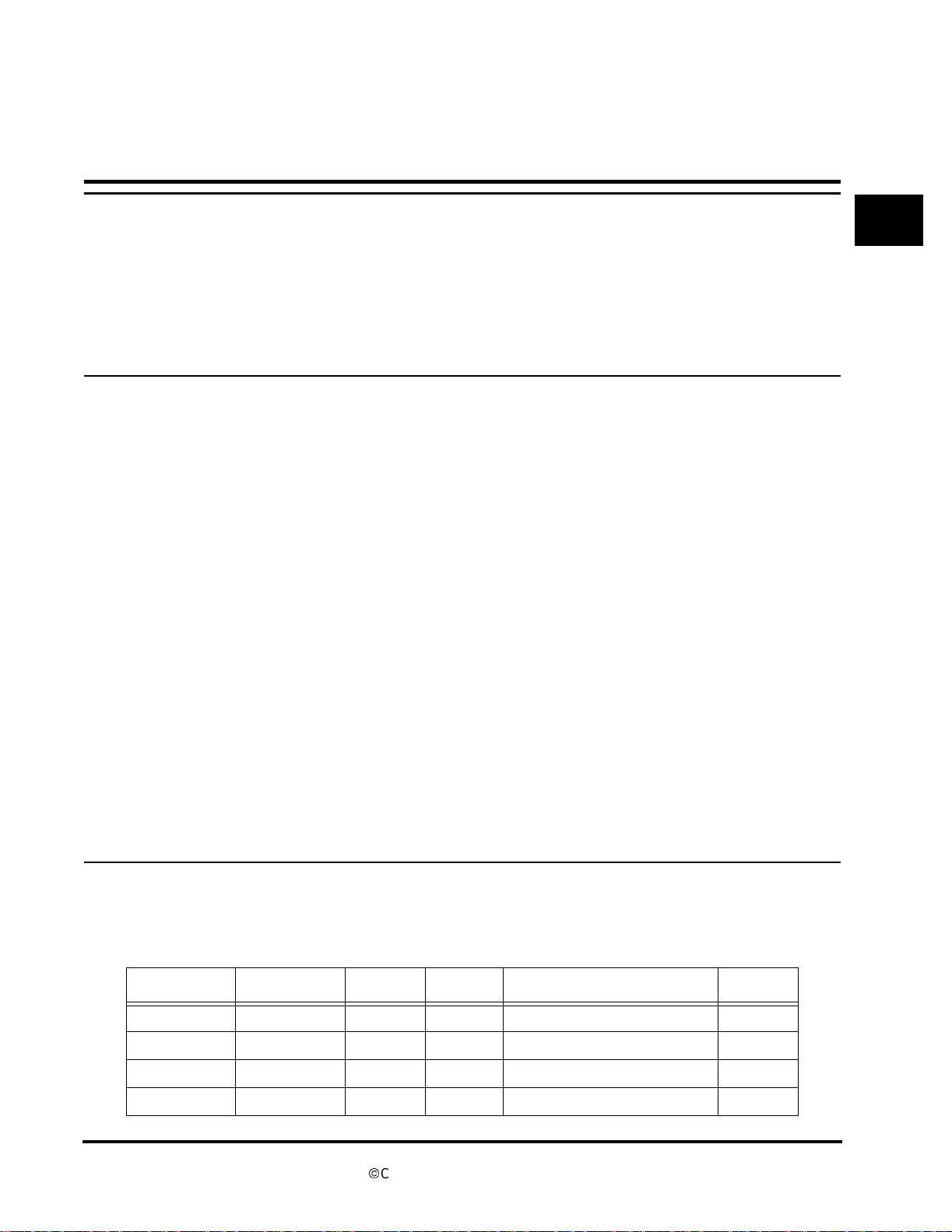

Operational Overview.................................................................................................................................... 16-3

DAI/CODEC/SSI2 MUX ....................................................................................................................... 16-3

DAI Interface ............................................................................................................................................ 16-4

Master/Slave SSI2 Interface ................................................................................................................... 16-7

CODEC Sound Interface ....................................................................................................................... 16-10

DAI/CODEC/SSI2 Register Descriptions ................................................................................................ 16-11

DAI Mode Control Register (DAI64FS) .......................................................................................... 16-11

DAI Control Register (DAIR).......................................................................................................... 16-12

DAI Data Register 0 (DAIDR0) ...................................................................................................... 16-14

DAI Data Register 1 (DAIDR1) ...................................................................................................... 16-15

DAI Status Register (DAISR)......................................................................................................... 16-16

Synchronous Serial Interface 2 Data Register (SS2DR) ............................................................... 16-20

Synchronous Serial Interface 2 Pop Residual Byte (SS2POP) ..................................................... 16-20

CODEC Interface Data Register (CODR)...................................................................................... 16-20

Chapter 17. UART and SIR Encoder

Introduction..................................................................................................................................................... 17-1

Features ............................................................................................................................................................ 17-1

UART and SIR Encoder Register List .......................................................................................................... 17-1

Programming Example .................................................................................................................................. 17-1

Operational Overview.................................................................................................................................... 17-2

UART1....................................................................................................................................................... 17-3

SIR Encoder .............................................................................................................................................. 17-4

UART2....................................................................................................................................................... 17-4

UART and SIR Encoder Register Descriptions...........................................................................................17-5

UART Data Registers (UARTDR1 and UARTDR2) ......................................................................... 17-5

Bit Rate and Line Control Registers (UBRLCR1 and UBRLCR2) ................................................... 17-6

Contents

Appendix A. Boot Code

Index ................................................................................................................................................................... 1-1

EP7309/11/12 User’s Manual - DS508UM4 vii

CopyrightCirrusLogic,Inc.2003

Page 9

Contents

This page intentionally blank.

viii EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

Page 10

List of Figures

Figure 1-1. EP73xx Block Diagram ............................................................................................................... 1-11

Figure 1-2. Typical EP73xx System Block Diagram ................................................................................... 1-12

Figure 2-1. ARM720T B lock Diagram ............................................................................................................ 2-2

Figure 2-2. ARM720T Cache Organization. .................................................................................................. 2-6

Figure 2-3. Register Organization Summary ................................................................................................ 2-8

Figure 2-4. State Diagram .............................................................................................................................. 2-12

Figure 9-1. Pixel Gray Scale Mapping............................................................................................................ 9-5

Figure 9-2. LCD Data to Pixel Mapping ........................................................................................................ 9-6

Figure 12-1. Block Diagram of a Power Supply Using Two PWM Drives ............................................. 12-1

Figure 16-1. Portion of the EP73xx Block Diagram Showing Multiplexed Feature .............................. 16-2

Figure 16-2. Digital Audio Clock Generation ............................................................................................. 16-5

Figure 16-3. SSI2 Port Directions in Slave and Master Mode ................................................................... 16-8

Figure 16-4. Residual Byte Reading.............................................................................................................. 16-9

EP7309/11/12 User’s Manual - DS508UM4 ix

CopyrightCirrusLogic,Inc.2003

Page 11

This page intentionally blank.

x EP7309/11/12 User’s Manual - DS508UM4

Copyright 2001, 2002 Cirrus Logic

Page 12

List of Tables

Table 1-1: EP73xx Memory Map in External Boot Mode ............................................................................ 1-2

Table 1-2: EP73xx Internal Registers (Little Endian Mode) ........................................................................ 1-4

Table 1-3: EP73xx Internal Registers (Big Endian Mode)............................................................................ 1-6

Table 1-4: External Signal Functions .............................................................................................................. 1-7

Table 1-5: SSI/CODEC/DAI Pin Multiplexing .......................................................................................... 1-10

Table 1-6: Output Bi-Directional Pins .......................................................................................................... 1-10

Table 2-1: Programming Registers ................................................................................................................. 2-1

Table 2-2: ARM720T Core Coprocessor Registers........................................................................................2-9

Table 2-3: Status of Peripherals and Clocks by Operating State .............................................................. 2-14

Table 3-1: Timer Registers................................................................................................................................ 3-1

Table 4-1: Interrupt Registers .......................................................................................................................... 4-1

Table 4-2: Vector Addresses by Interrupt Type............................................................................................4-3

Table 4-3: Exception Priority Handling ......................................................................................................... 4-4

Table 4-4: Interrupt Allocation in the First Interrupt Register ................................................................... 4-5

Table 4-5: Interrupt Allocation in the Second Interrupt Register .............................................................. 4-5

Table 4-6: Interrupt Allocation in the Third Interrupt Register ................................................................. 4-5

Table 4-7: External Interrupt Sources............................................................................................................. 4-7

Table 5-1: System Registers ............................................................................................................................. 5-2

Table 5-2: Keyboard Column Drive State...................................................................................................... 5-4

Table 5-3: ADC Sample Clock Settings.......................................................................................................... 5-6

Table 5-4: ARM720T Clock Speed Settings ................................................................................................... 5-9

Table 5-5: Default (Power-on Reset) Bus Width Settings.......................................................................... 5-11

Table 6-1: Chip Select Address Ranges for On-Chip Boot ROM ............................................................... 6-2

Table 6-2: Boot Options .................................................................................................................................... 6-2

Table 6-3: Memory Map in External Boot Mode .......................................................................................... 6-3

Table 6-4: Effect of Endianess on Read Operations......................................................................................6-4

Table 6-5: Effect on Endianess on Write Operations.................................................................................... 6-4

Table 7-1: SDRAM Registers ........................................................................................................................... 7-1

Table 8-1: SRAM / Expansion Bus Registers................................................................................................ 8-1

Table 8-2: Bus Width Selection Settings......................................................................................................... 8-3

Table 8-3: Wait States at 13 / 18 MHz Operation......................................................................................... 8-4

Table 8-4: Wait States at 36 MHz Operation ................................................................................................. 8-4

Table 9-1: LCD Registers..................................................................................................................................9-1

Table 9-2: Gray Scale Value to Color Mapping ............................................................................................ 9-9

Table 11-1: General Purpose I/O (GPIO) Registers ................................................................................... 11-1

Table 12-1: PWM (Pulse Width Modulator) Registers .............................................................................. 12-2

Table 12-2: PWM Pump Drive Settings ....................................................................................................... 12-3

Table 13-1: LED Flasher Registers ................................................................................................................ 13-1

Table 14-1: Instructions Supported in JTAG Mode.................................................................................... 14-2

Table 14-2: EP73xx Hardware Test Modes.................................................................................................. 14-3

Table 14-3: Oscillator and PLL Test Mode Signals.................... ....................................... .......................... 14-4

Table 14-4: Software Selectable Test Functionality .................................................................................... 14-4

Table 15-1: SSI Port Registers ........................................................................................................................ 15-1

Table 15-2: ADC Interface Operation Frequencies..................................................................................... 15-3

Table 16-1: DAI/CODEC/SSI2 Registers.................................................................................................... 16-2

Table 16-2: Matrix for Programming the MUX........................................................................................... 16-3

Table 16-3: Pin Sharing for Multiplexor....................................................................................................... 16-4

Table 16-4: Communication Interface Performance................................................................................... 16-4

Table 16-5: Programmable Audio Divisors at 74 MHz ............................................................................. 16-5

EP7309/11/12 User’s Manual - DS508UM4 xi

Copyright Cirrus Logic, Inc. 2003

Page 13

Table 16-6: Programmable Audio Divisors at 90 MHz ............................................................................. 16-6

Table 17-1: UART and SIR Encoder Registers ............................................................................................17-1

Table 17-2: UART Bit Rates at 90 MHz ........................................................................................................ 17-2

Table 17-3: UART Bit Rate in PLL Clock Mode (74 MHz) ........................................................................ 17-3

Table 17-4: UART Bit Rate from 13 MHz Clock ......................................................................................... 17-3

Table 17-5: Word Length Selection............................................................................................................... 17-6

EP7309/11/12 User’s Manual - DS508UM4 xii

Copyright Cirrus Logic, Inc. 2003

Page 14

EP7309/11/12 User’s Manual - DS508UM4 xiii

Copyright Cirrus Logic, Inc. 2003

Page 15

Overview

Processor

Chapter 1

1Introduction

This chapter describes the EP73xx ARM processor, mem ory map, registers, an d

signals. See the data sheet that is associated with a specific EP73xx device for more

informationaboutpinassignmentsforthatproduct.

The EP73xx incorporates an ARM 32-bit RISC m icro controller that controls a wide

range of on-chip peripherals.The ARM720T includes a a 8 Kbytes unified cache and a

MMU compatible with operating systems like Windows

®

CE and Linux®.

11

1

Peripherals

See the A RM 720T Technical Reference Manual, as cited on page 1-12.

On-chip EP73xx peripherals are product-specific for each chip. The supersetof

available features includes:

• 48 Kbytes of on-chip SRAM th at can be shared b etween the LCD controller

and general application use

• Memory interfaces (chip selects) for up to six independent 256 M byte

expansion segments with programmable width and wait states

• 27 general purpose Input/Outputs.

• Digital Audio Interface (DAI) to interface with CD-quality DACs and

CODECs

• Interrupt Controller

• Advanced system state controller and power management

• Two full-duplex 16550 A compatible UARTs with 16-byte transmit and

receive FIFOs.

• IrDA SIR protocol controller capable of speeds up to 115.2 kbps

• Programmable LCD controller for 1,2 or 4-bit-per-pixel with 16-level

grayscaler and frame buffer start address.

• On-chip boot ROM programmed for serial port download of boot code.

EP7309/11/12 User’s Manual - DS508UM4 1-1

Copyright Cirrus Logic, Inc. 2003

Page 16

Introduction

• Two 16-bit general purpose timer counters

• 32-bit RTC (Real-Time-Clock) timer and comparator

• Dedicated LED flasher pin driven from the RTC with programmable du ty

ratio (Multiplexed with GPIO pin)

1

• Two synchronous serial interfaces for M icro-wire or SPI interfaces s uch as

ADCs, one supporting both the master and slave and other supporting

only master mode.

• Two programmable PWM (Pulse Width Modulation) interfaces

• SDRAM i nterface for direct interface to a maximum of two external banks

of SDRAM memory. Each bank can be up to 256 Mbit in size and

configurable for 32 or 16-bit wide accesses.

• PLL (Phase Lock Loop) oscillator for generating core speeds of 18-90 MHz

from an external 3.6864 MHz crystal.

• Low power 32.768 kHz RTC (Real Time Clock)

• MaverickKey - Unique and Random IDs for SDMI compliance

Memory Map and Register List

The lower 2 GByte of the address space is allocated to memory. The 64 MByte of

address space from 0xC000.0000 to 0xCFFF.FFFF is allocated to SDRAM. About

1.5 GBytes of address space, less 8 Kbytes for internal registers, is not accessible in the

EP73xx. The M MU in the EP73xx should be programmed to g enerate an abort

exception for access to this area.

Internal peripherals are addressed through a set of internal memory l oca tions from

hex address 0x8000.0000 to 0x8000.3FFF. These are known as the internal registers in

the EP73xx. In Table 1-1 also shows how the 4-Gbyte address range of the ARM720T

processor (as configured within this chip) is mapped in the EP73xx. The external boot

ROM is not fully decoded (i.e., the b oot code will repeat within the 256-Mbyte space

from 0x7000.0000 to 0x8000.0000). See Table 6-1 on page 6-2 for the m emory map

when booted from on-chip boot ROM. The SRAM is fully decoded up to a maximum

size of 48 Kbytes. Access to any location above this range will be wrapped to within

the range.

Global Memory Map

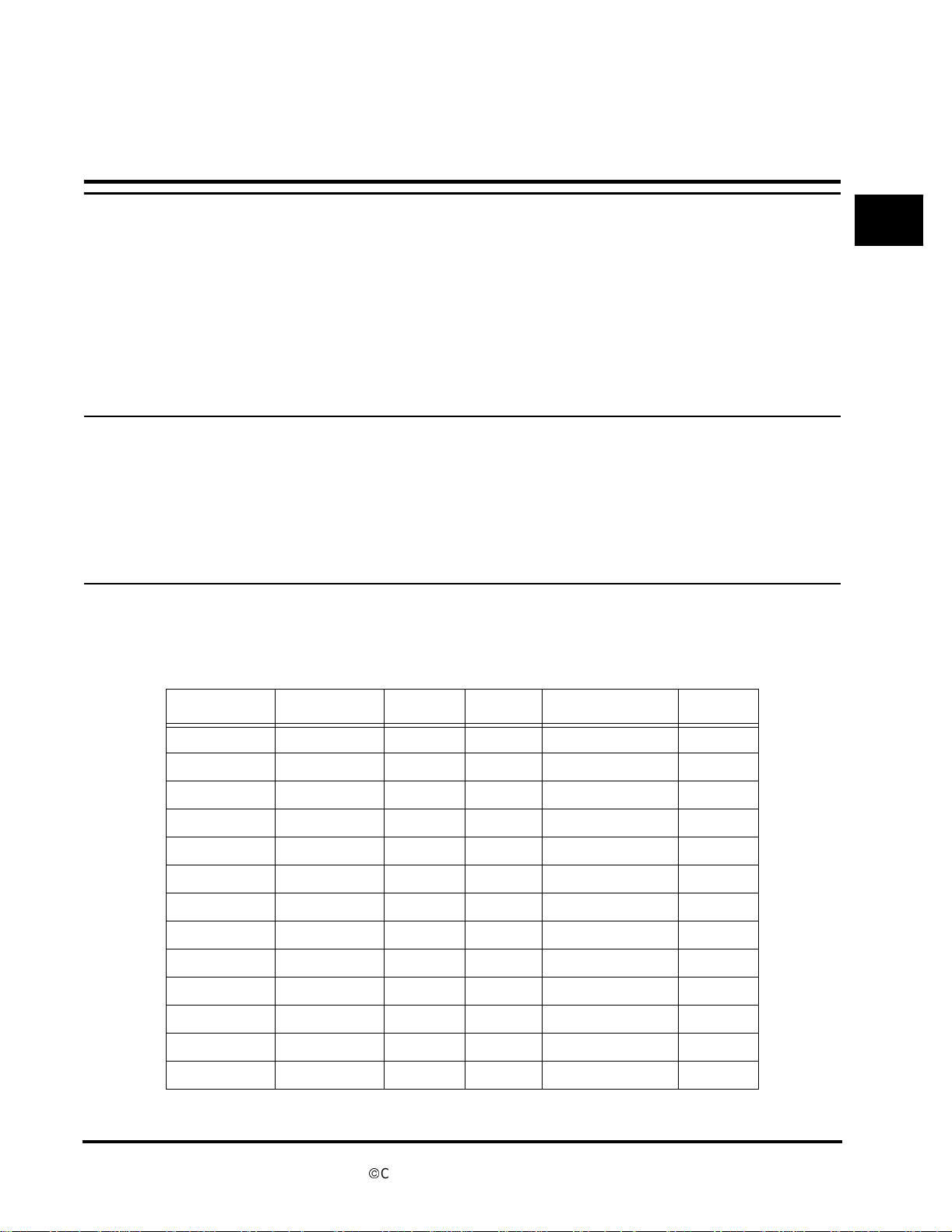

Table 1-1: EP73xx Memory Map in External Boot Mode

Address Contents Size

0xF000.0000 Reserved 256 Mbytes

0xE000.0000 Reserved 256 Mbytes

0xD000.0000 Reserved 256 Mbytes

0xC000.0000 SDRAM 64 Mbytes

1-2 EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

Page 17

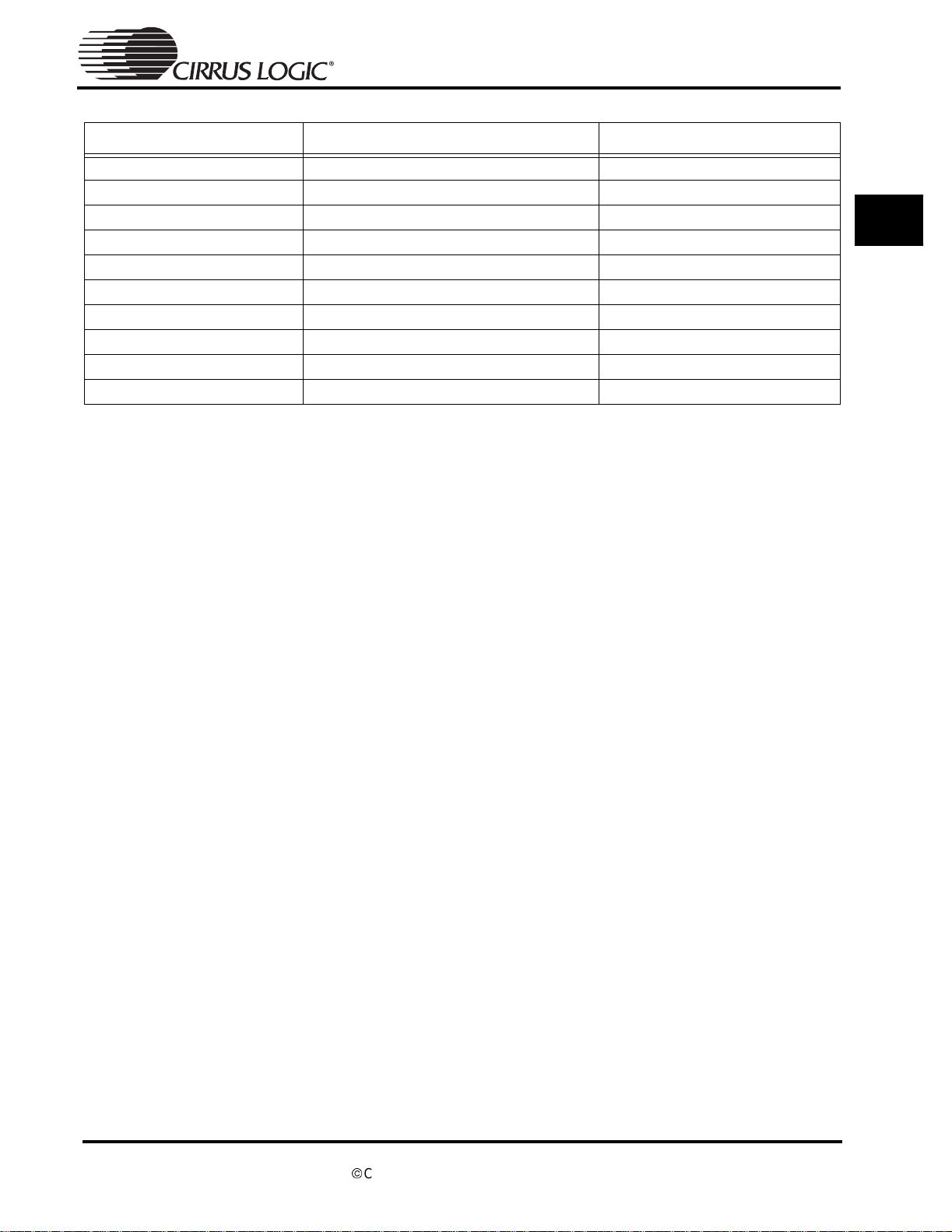

Table 1-1: EP73xx Memory Map in External Boot Mode (Continued)

Address Contents Size

0x8000.4000 Unused ~1 Gbyte

0x8000.0000 Internal registers 8 Kbytes

0x7000.0000 Boot ROM (nCS[7]) 128 bytes

0x6000.0000 SRAM (nCS[6]) 48 Kbytes

0x5000.0000 Expansion (nCS[5]) 256 Mbytes

0x4000.0000 Expansion (nCS[4]) 256 Mbytes

0x3000.0000 Expansion (nCS[3]) 256 Mbytes

0x2000.0000 Expansion (nCS[2]) 256 Mbytes

0x1000.0000 ROM Bank 1 (nCS[1]) 256 Mbytes

0x0000.0000 ROM Bank 0 (nCS[0]) 256 Mbytes

Internal Register Map

Table 1-2 on page 1-4 shows the Internal Registers of the EP73xx when the CPU is

configured to a little endian memory system. Table 1-3 on page 1-6 shows the

differences that occur when the CPU is configuredto a big endian memorysystemfor

byte-wide access to Ports A, B, an d D. All the internal registers are inherently little

endian (i.e., the least significant byte is attached to bits 7 to 0 of the data bus). Hence,

the system Endianness affects the addresses required for byte accesses to the internal

registers, resulting in a reversal of th e byte address required to read/write a

particular byte within a register.

Introduction

11

1

There is no effect on the register addresses for word accesses. Bits

internal address bus are only decoded for Ports A, B, and D (to allow read/write to

individual ports). For all other registers,bits

will return the whole register contents onto the E P 73xx’s intern al bus, from where the

appropriate byte (according to the en dianness) will be read by the CPU. To avoid the

additional c omplexity, it is preferable to perform all internal register accesses as word

operations, except for ports A to D which are explicitly designed to operate with byte

accesses, as well as with w ord ac cesses.

An 8 Kbytes segment of memory in the range 0x8000.0000 to 0x8000.3FFF is reserved

for internal use in the EP73xx. Accesses in this range will not cause any external bus

activity unless debug mode is enabled. Writes to bits that are not explicitly defined in

the internal area are legal and will have no effect. Reads from bits not explicitly

defined in the internal area are legal but will read undefined values. A ll the internal

addresses s hould only be ac cessed as 32-bit words an d are always on a word

boundary, except for the GPIO port registers, which can be accessed as bytes. A ddress

bits in the range

internal register is valid for 64 bytes (i.e., the SYSFLG1 register appears at locations

0x8000.0140 to 0x8000.017C). There are some gaps in the register map for backward

compatibility reasons, but registers located next to a gap are still only decoded for

64 bytes.

The GPIO port registers are byte-wide and can be accessed as a word but not as a halfword. These registers additionally decode

notation.

A[0-5] are not decoded (except for Ports A–D), this means each

A[0-1] arenot decoded, s o that byte reads

A[0-1]. All addresses are in hexadecimal

A[0-1] of the

EP7309/11/12 User’s Manual - DS508UM4 1-3

Copyright Cirrus Logic, Inc. 2003

Page 18

1

Introduction

Note: All byte-wideregisters should be accessed as words (except Port A to Port D

registers, which are designed to work in both word and byte modes).

All registers bit alignment starts from the LSB of the register (i.e., they are all

right shift justified). The registers which interact with the 32 kHz clock or which

could change during readback (i.e., RTC data registers, SYSFLG1 register

(lower 6-bits only), the TC1D and TC2D data registers,port registers, and

interrupt status registers), should be read twice and comparedto ensure that a

stable value has been read back.

All internal registers in the EP73xx are reset (cleared to zero) by a system reset (i.e.,

nPOR, nRESET,ornPWRFL signals becoming active), and the Real Time Clock data

register (RTCDR) and match register (RTCMR), which are only reset by

nPOR

becoming active. This ensures that the system time preserved through a user reset or

power fail condition. In the following register descriptions, little endian is assumed.

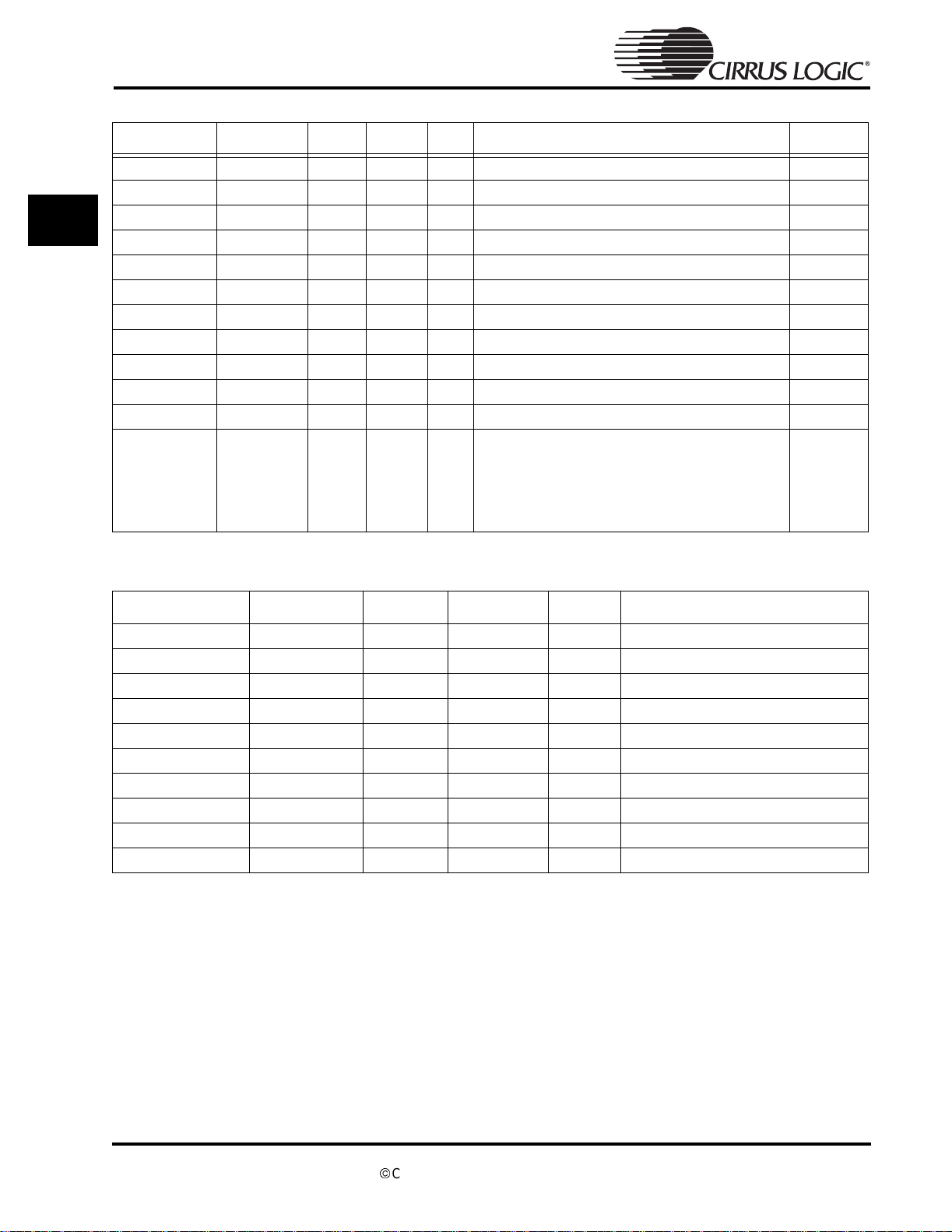

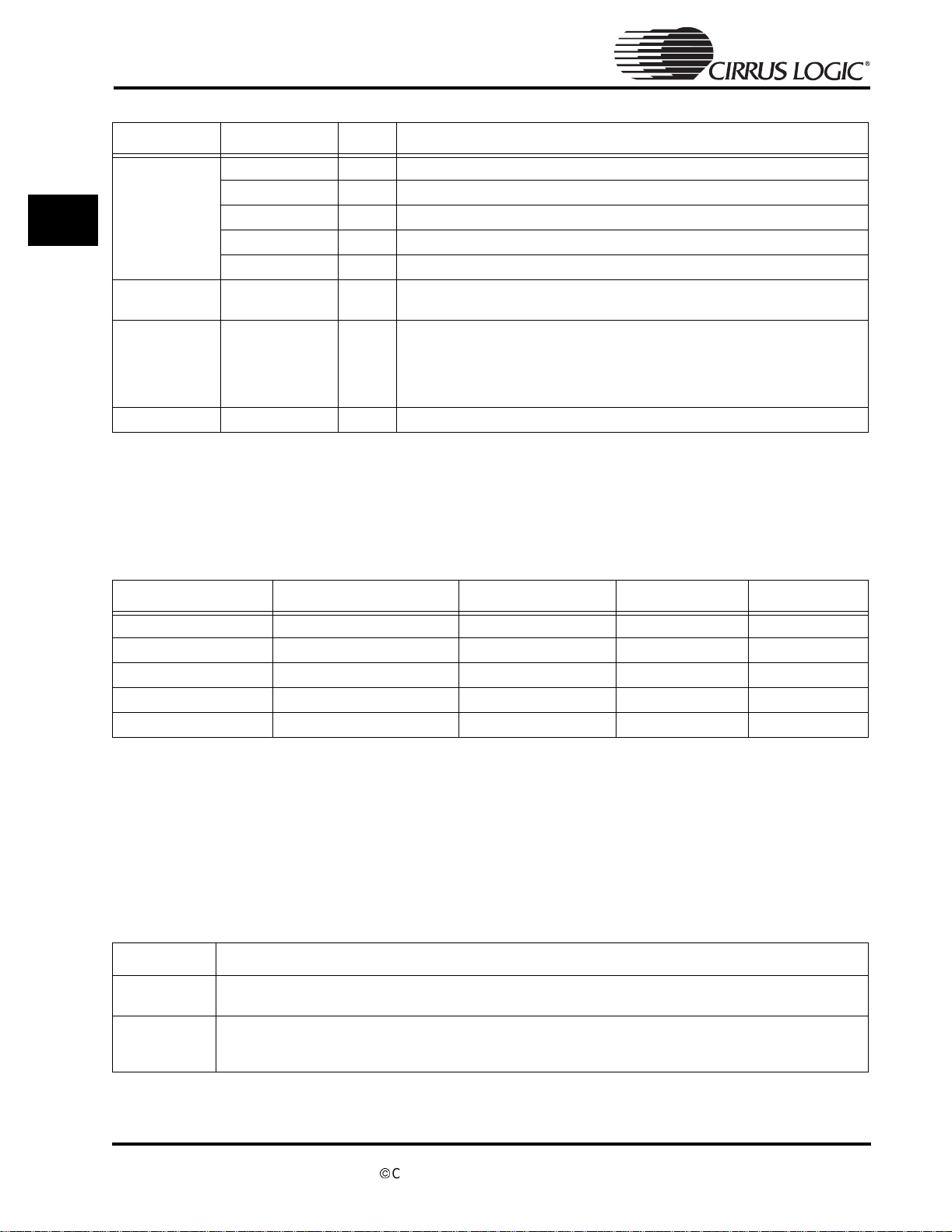

Table 1-2: EP73xx Internal Registers (Little Endian Mode)

Address Name Default RD/WR Size Comments Page

0x8000.0000 PADR 0 RW 8 Port A data register page 11-1

0x8000.0001 PBDR 0 RW 8 Port B data register page 11-1

0x8000.0002 ——8Reserved

0x8000.0003 PDDR 0 RW 8 Port D data register page 11-1

0x8000.0040 PADDR 0 RW 8 Port A data direction register page 11-1

0x8000.0041 PBDDR 0 RW 8 Port B data direction register page 11-1

0x8000.0042 ——8Reserved

0x8000.0043 PDDDR 0 RW 8 Port D data direction register page 11-1

0x8000.0080 PEDR 0 RW 3 Port E data register page 11-1

0x8000.00C0 PEDDR 0 RW 3 Port E data direction register page 11-1

0x8000.0100 SYSCON1 0 RW 32 System control register 1 page 5-4

0x8000.0140 SYSFLG1 0 RD 32 System status flags register 1 page 5-9

0x8000.0180 MEMCFG1 0 RW 32 Expansion memory configuration register 1 page 8-3

0x8000.01C0 MEMCFG2 0 RW 32 Expansion memory configuration register 2 page 8-5

0x8000.0200 0 RW 32 Reserved

0x8000.0240 INTSR1 0 RD 32 Interrupt status register 1 page 4-8

0x8000.0280 INTMR1 0 RW 32 Interrupt mask register 1 page 4-10

0x8000.02C0 LCDCON 0 RW 32 LCD control register page 9-7

0x8000.0300 TC1D 0 RW 16 Read / Write register sets and reads data to TC1 page 3-3

0x8000.0340 TC2D 0 RW 16 Read / Write register sets and reads data to TC2 page 3-3

0x8000.0380 RTCDR — RW 32 Real Time Clock data register page 3-3

0x8000.03C0 RTCMR — RW 32 Real Time Clock match register page 3-4

0x8000.0400 PMPC ON 0 RW 12 PWM pump control register page 12-3

0x8000.0440 CODR 0 RW 8 CODEC data I/O register page 16-20

0x8000.0480 UARTDR1 0 RW 16 UART1 FIFO data register page 17-5

0x8000.04C0 UBRLCR1 0 RW 32 UART1 bit rate and line control register page 17-6

0x8000.0500 SYNCIO 0 RW 32 Synchronous serial I/O data register for master only SSI page 15-4

1-4 EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

Page 19

Introduction

Table 1-2: EP73xx Internal Registers (Little Endian Mode) (Continued)

Address Name Default RD/WR Size Comments Page

0x8000.0540 PALLSW 0 RW 32 Least significant 32-bit word of LCD palette register page 9-8

0x8000.0580 PALMSW 0 RW 32 Most significant 32-bit word of LCD palette register page 9-8

0x8000.05C0 STFCLR — WR — Write to clear all start up reason flags page 5-13

0x8000.0600 BLEOI — WR — Write to clear battery low interrupt page 4-13

0x8000.0640 MCEOI — WR — Write to clear media changed interrupt page 4-13

0x8000.0680 TEOI — WR — Write to clear tick and watchdog interrupt page 4-13

0x8000.06C0 TC1EOI — WR — Write to clear TC1 interrupt page 4-13

0x8000.0700 TC2EOI — WR — Write to clear TC2 interrupt page 4-14

0x8000.0740 RTCEOI — WR — Write to clear RTC match interrupt page 4-14

0x8000.0780 UMSEOI — WR — Write to clear UART modem status changed interrupt page 4-14

0x8000.07C0 COEOI — WR — Write to clear CODEC sound interrupt page 4-14

0x8000.0800 HALT — WR — Write to enter the Idle State page 2-14

0x8000.0840 STDBY — WR — Write to enter the Standby State page 2-13

0x8000.0880–

0x8000.0FFF

0x8000.1000 FBADDR 0xC RW 4 LCD frame buffer start address page 9-9

0x8000.1100 SYSCON2 0 RW 16 System control register 2 page 5-7

0x8000.1140 SYSFLG2 0 RD 24 System status register 2 page 5-12

0x8000.1240 INTSR2 0 RD 16 Interrupt status register 2 page 4-11

0x8000.1280 INTMR2 0 RW 16 Interrupt mask register 2 page 4-12

0x8000.12C0–

0x8000.147F

0x8000.1480 UARTDR2 0 RW 16 UART2 Data Register page 17-5

0x8000.14C0 UBRLCR2 0 RW 32 UART2 bit rate and line control register page 17-6

0x8000.1500 SS2DR 0 RW 16 Master / slave SSI2 data Register page 16-20

0x8000.1600 SRXEOF — WR — Write to clear RX FIFO overflow flag page 4-14

0x8000.16C0 SS2POP — WR — Write to pop SSI2 residual byte into RX FIFO page 16-20

0x8000.1700 KBDEOI — WR — Write to clear keyboard interrupt page 4-14

0x8000.1800 Reserved — WR —

0x8000.1840–

0x8000.1FFF

0x8000.2000 DAIR 0 RW 32 DAI control register page 16-12

0x8000.2040 DAIR0 0 RW 32 DAI data register 0 page 16-14

0x8000.2080 DAIDR1 0 RW 32 DAI data register 1 page 16-15

0x8000.20C0 DAIDR2 0 WR 21 DAI data register 2 page 16-16

0x8000.2100 DAISR 0 RW 32 DAI status register page 16-16

0x8000.2200 SYSCON3 0 RW 16 System control register 3 page 5-8

0x8000.2240 INTSR3 0 RD 32 Interrupt status register 3 page 4-12

0x8000.2280 INTMR3 0 RW 8 Interrupt mask register 3 page 4-13

Reser ved Write will have no effect, read is undefined

Reser ved Write will have no effect, read is undefined

Do not write to this location. A write will cause the

processor to go into an unsupported power savings

state.

Reserved — Write will have no effect, read is undefined

11

1

EP7309/11/12 User’s Manual - DS508UM4 1-5

Copyright Cirrus Logic, Inc. 2003

Page 20

1

Introduction

Table 1-2: EP73xx Internal Registers (Little Endian Mode) (Continued)

Address Name Default RD/WR Size Comments Page

0x8000.22C0 LEDFLSH 0 RW 7 LED Flash register page 13-2

0x8000.2300 SDCONF 2 RW 32 SDRAM Configuration Register page 7-3

0x8000.2340 SDRFPR 128 RW 16 SDRAM Refresh Register page 7-4

0x8000.2440 UNIQID 0 R 32 32-bit unique ID for the EP73xx device page 5-13

0x8000.2600 DAI64Fs 0 RW 32 DAI 64Fs Control Register page 16-11

0x8000.2610 PLLW W 8 Write Register for PLL Multiplier page 2-11

0x8000.A5A8 PLLR R Read Register for PLL Multiplier page 2-11

0x8000.2700 RANDID0 0 R 32 Bits 31-0 of 128-bit random ID for the EP73xx device page 5-13

0x8000.2704 RANDID1 0 R 32 Bits 63-32 of 128-bit random ID for the EP73xx device page 5-13

0x8000.2708 RANDID2 0 R 32 Bits 95-64 of 128-bit random ID for the EP73xx device page 5-13

0x8000.270C RANDID3 0 R 32 Bits 127-96 of 128-bit random ID for the EP73xx device page 5-13

All other address

space that is not

assigned to a

register listed in

this table

Reserved

All addresses that are outside the address space of the

registers listed in this table are reserved. The undefined

areas contain test registers used during manufacturing

tests. Writes to this area should never be attempted

during normal operation as this may cause unexpected

behavior. Any read from this register will be undefined.

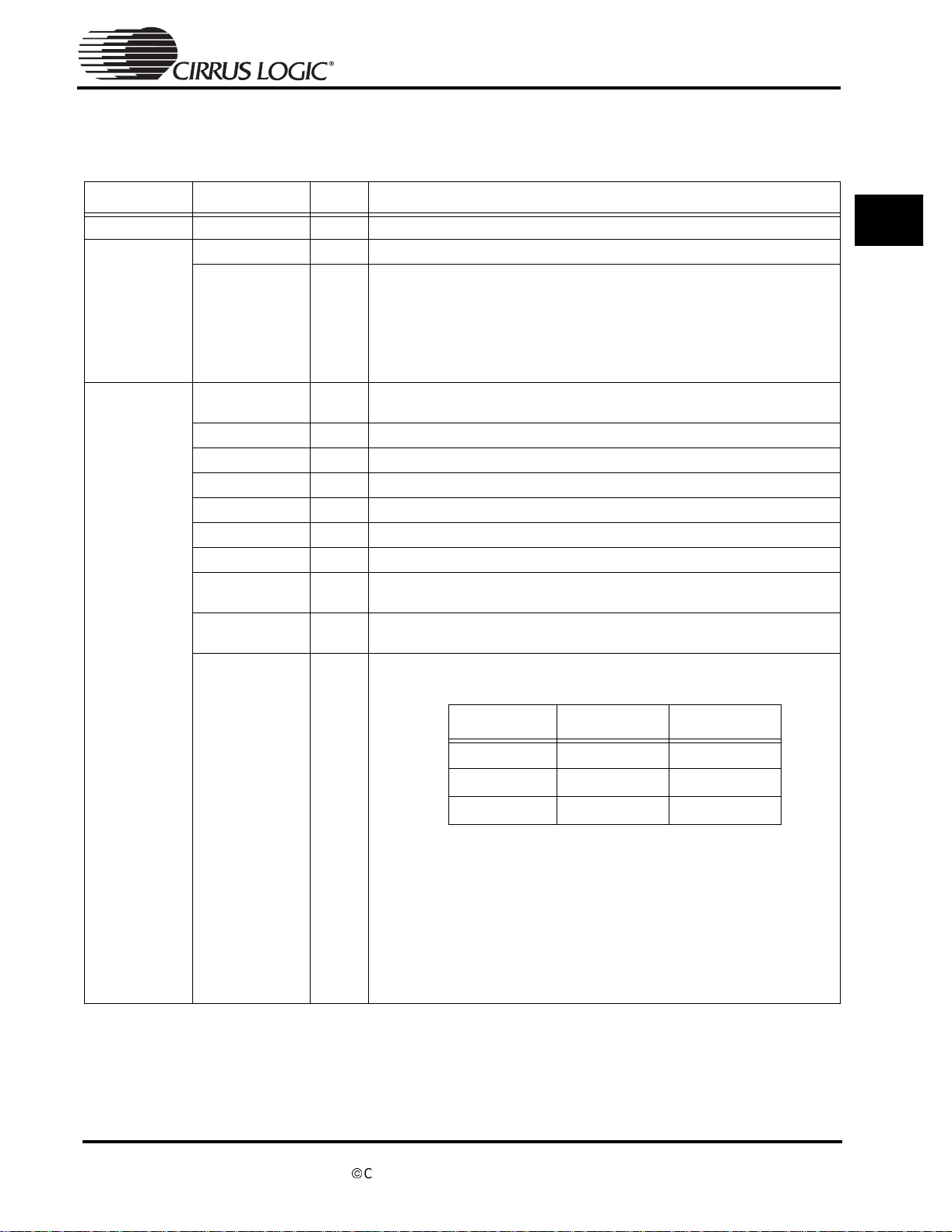

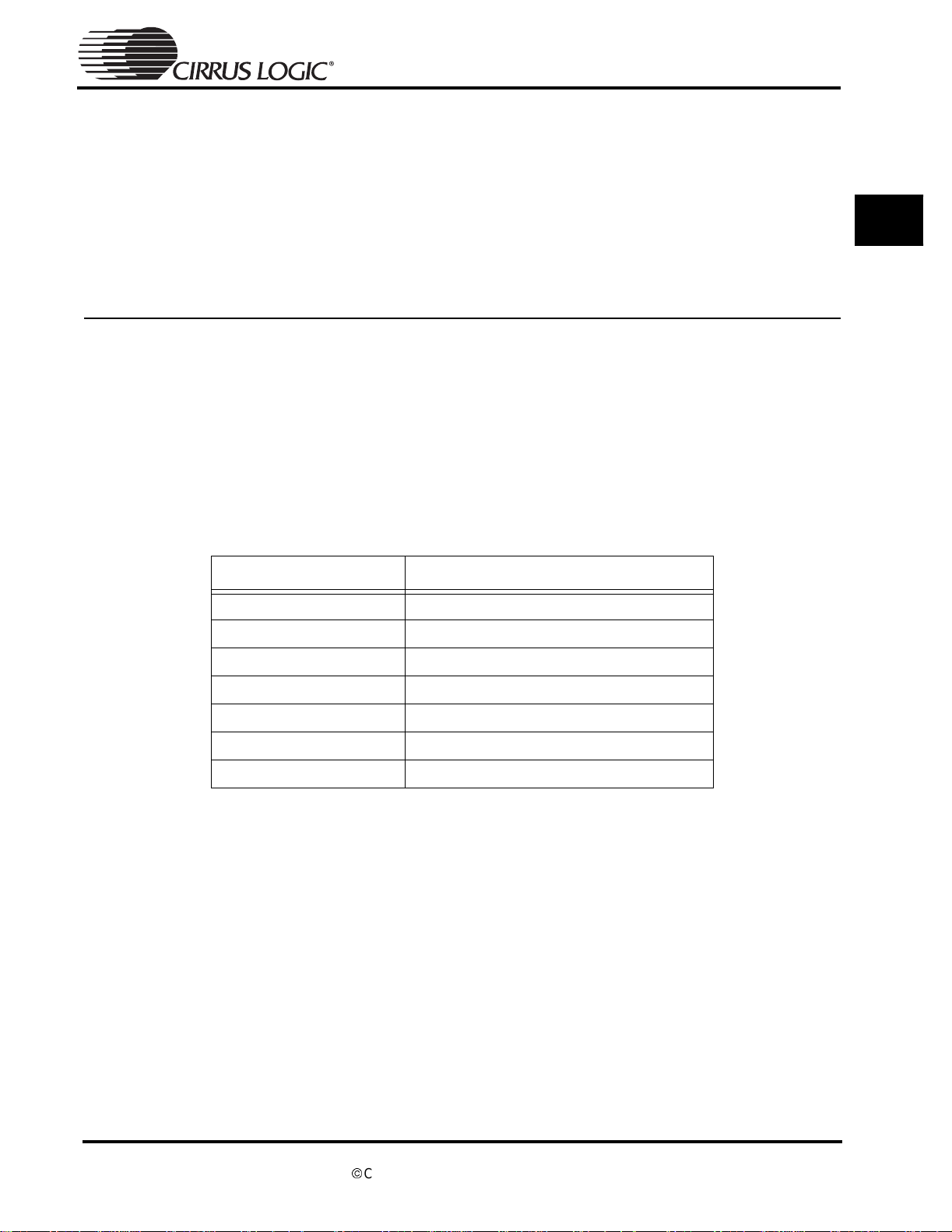

Table 1-3: EP73xx Internal Registers (Big Endian Mode)

Big Endian Mode Name Default RD/WR Size Comments

0x0000.0083 PEDR 0 RW 3 Port E Data Register

0X8000.00C3 PEDDR 0 RW 3 Port E Data Direction Register

0x8000.0000 PDDR 0 RW 8 Port D Data Register

0x8000.0001 ——8Reserved

0x8000.0002 PBDR 0 RW 8 Port B Data Register

0x8000.0003 PADR 0 RW 8 Port A Data Register

0x8000.0040 PDDDR 0 RW 8 Port D Data Direction Register

0x8000.0041 ——8Reserved

0x8000.0042 PBDDR 0 RW 8 Port B Data Direction Register

0x8000.0043 PADDR 0 RW 8 Port A data Direction Register

Pin Description

Table 1-4 on page 1-7 describes the function of all external signals to the EP 73xx. Note

that all output signals and all I/O pins ( when acting as ou tputs) are High-Z capable.

This is to enable the High-Z test modes to be supported.

1-6 EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

Page 21

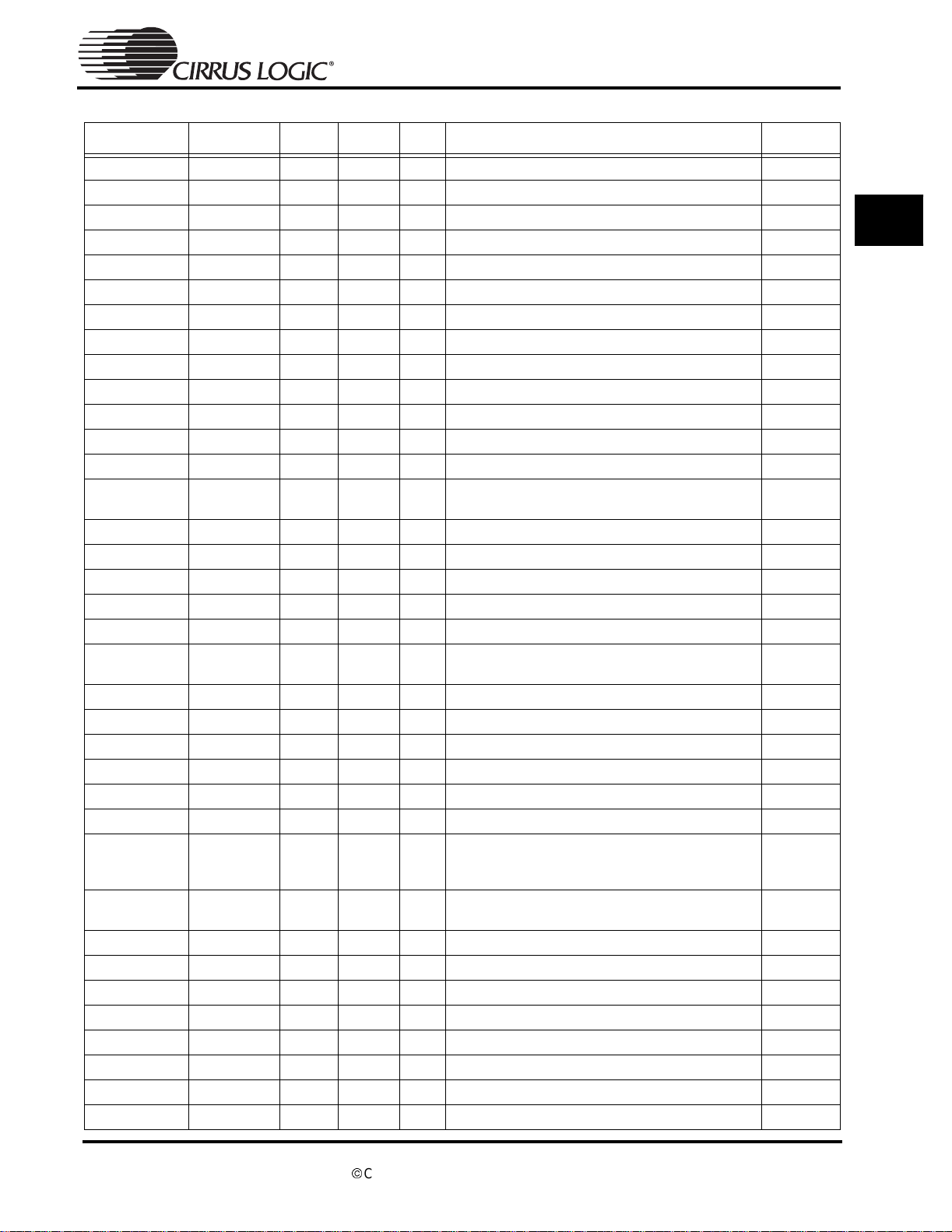

External Signal Functions

Table 1-4: External Signal Functions

Function Signal Name Signal Description

Introduction

11

Data bus D[0-31] I/O 32-bit system data bus for memory, SDRAM, and I/O interface

A[0-31] O 32 bits of system byte address during memory and expansion cycles

DRA[0-14] are multiplexed with A[27-13] for SDRAM memory accesses. A27

corresponds to DRA0 on SDRAM device. This offers additional power savings since

Address bus

Memory Interface

A[27-13]/

DRA[0-14]

BA[0-1]/

A[13-14]

nMOE/nSDCAS O ROM expansion OP enable/ SDRAM CAS control signal

nMWE/nSDWE O ROM expansion write enable/ SDRAM write enable control signal

nCS[0-5] O Chip select; active low, SRAM-like chip selects for expansion

SDQM[0-1] O LDQM; lower byte masks for SDRAM accesses

SDQM[2-3] O UDQM; upper byte masks for SDRAM/ multiplexed with PD[6-7]. See GPIO section

SDCS[0-1] O SDRAM chip selects

EXPRDY I

WRITE/nSDRAS O

the lightest loading is expected on the high order ROM address lines.

Whenever the EP73xx is in the Standby State, the external address and data buses

O

are driven low. The RUN signal is used internally to force these buses to be driven

low. This is done to prevent peripherals that are powered-down from draining current.

Also, the internal peripheral’s signals get set to their Reset State.

I/O A13 and A14, during SDRAM accesses, become bank select pins BA0 and BA1.

Expansion port ready; external expansion devices dr ive this low to extend the bus

cycle. This is used to inser t wait states for an external bus cycle.

Transfer Direction for expansion bus/SDRAM RAS control signal during SDRAM

access

To do write accesses of different sizes Word and Half-Word must be externally

decoded. The encoding of these signals is as follows:

1

Access Size Word Half-Word

Word 1 0

Half-Word 0 1

WORD/

HALFWORD

EP7309/11/12 User’s Manual - DS508UM4 1-7

O

The core will generate an address. When doing a read, the ARM core will select the

appropriate byte channels. When doing a write, the correct bytes will have to be

enabled depending on the above signals and the least significant bits of the address

bus.

The ARM architecture does not support unaligned accesses. For a read using x 32

memor y, it is assumed that you will ignore bits 1 and 0 of the address bus and

perform a word read (or in power critical systems decode the relevant bits depending

on the size of the access). If an unaligned read takes place, the core will rotate the

resulting data in the register. For more information on this behavior see the LDR

instruction in the ARM7TDMI data sheet.

Copyright Cirrus Logic, Inc. 2003

Byte 0 0

Page 22

1

Introduction

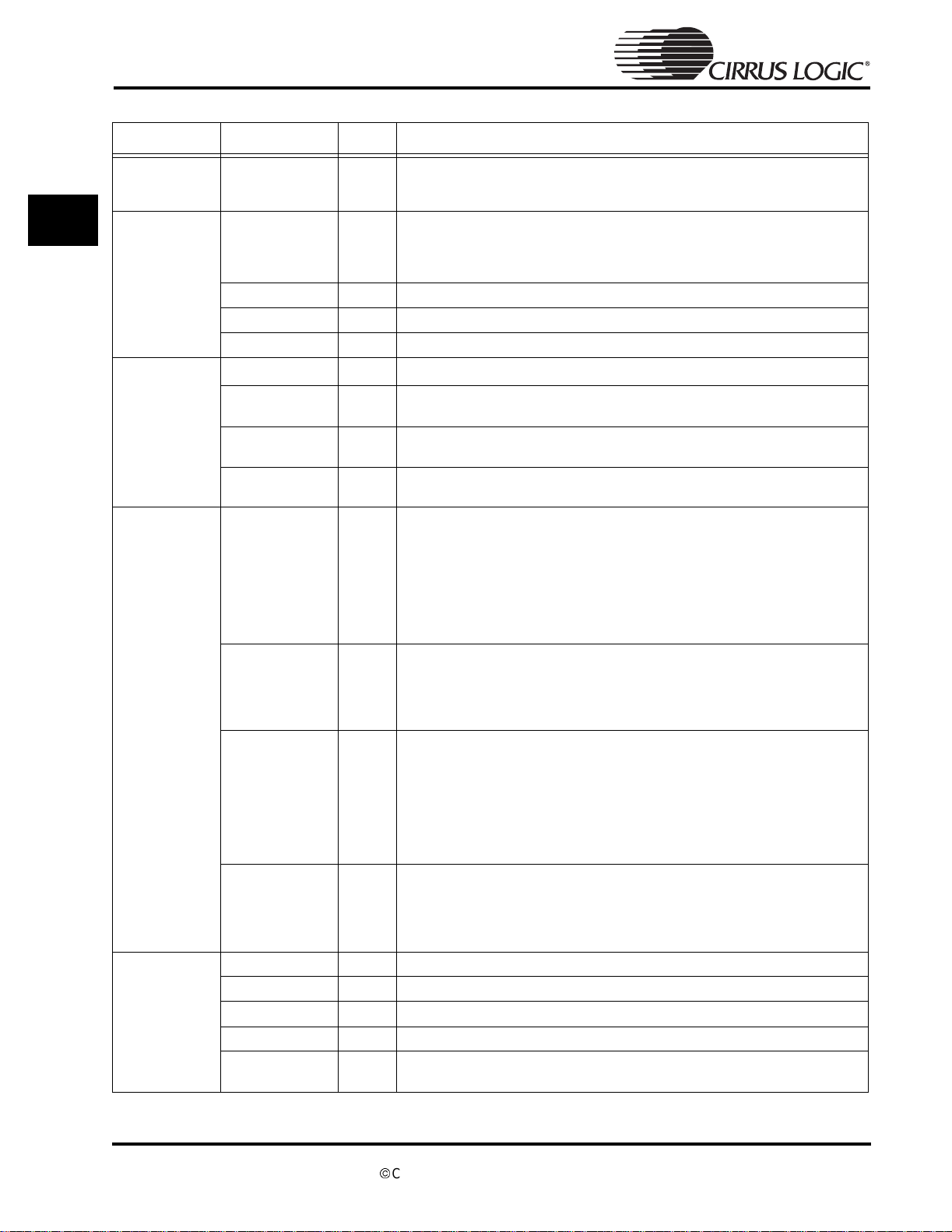

Table 1-4: External Signal Functions (Continued)

Function Signal Name Signal Description

Expansion clock rate is the same as the CPU clock for 13 MHz and 18 MHz. It runs

External Clock EXPCLK I/O

nMEDCHG/

nBROM

Interrupts

Power

Management

State Control

nEXTFIQ I External active low fast interrupt request input

EINT[3] I External active high interrupt request input

nEINT[1-2] I Two general purpose, active low interrupt inputs

nPWRFL

nEXTPWR I

nBATCHG

RUN/CLKEN O

WAKEUP

1

1

BATOK

1

nPOR I

1

at 36.864 MHz for 36,49 and 74 MHz modes; in 13 MHz mode this pin is used as the

clock input.

Media changed input; active low, deglitched. Used as a general purpose FIQ

interrupt during normal operation. It is also used on power up to configure the

I

processor to either boot from the internal Boot ROM, or from external memory.

When low, the chip will boot from the internal Boot ROM.

I Power fail input; active low, deglitched input to force system into the Standby State

Main battery OK input; falling edge generates a FIQ, a low level in the Standby State

I

inhibits system star t up; deglitched input

External power sense; must be driven low if the system is powered by an external

source

New battery sense; driven low if battery voltage falls below the "no-battery"

I

threshold; it is a deglitched input

Power-on reset input. This signal is not deglitched. When active it completely resets

the entire system, including all the RTC registers. Upon power-up, the signal must be

held active low for a minimum of 100 µsec. after V

operation, nPOR needs to be held low for at least one clock cycle of the selected

clock speed (i.e., when running at 13 MHz, the pulse width of nPOR needs to be >

77 nsec).

Note that nURESET, TEST[0], TEST[1], PE[0], PE[1], PE[2], DRIVE[0], DRIVE[1],

nMEDCHG, are all latched on the rising edge of nPOR.

This pin is programmed to either output the RUN signal or the CLKEN signal. The

CLKENSL bit is used to configure this pin. When RUN is selected, the pin will be

high when the system is active or idle, low while in the Standby State. When CLKEN

is selected, the pin will only be driven low when in the Standby State (For RUN, see

Table 1-6 on page 1-10).

Wake up is a deglitched input signal. It must also be held high for at least 125 µsec to

guarantee its detection. Once detected it forces the system into the Operating State

from the Standby State. It is only active when the system is in the Standby State.

This pin is ignored when the system is in the Idle or Operating State. It is used to

I

wakeup the system after first power-up, or after software has forced the system into

the Standby State. WAKEUP will be ignored for up to two seconds after nPOR goes

HIGH. Therefore, the external WAKEUP logic must be designed to allow it to rise and

stay HIGH for at least 125 usec, two seconds after nPOR goes HIGH.

User reset input; active low deglitched input from user reset button.

has settled. During normal

DD

DAI, CODEC or

SSI2 Interface

(See Table 1-5 on

page 1-10 for pin

assignment and

direction following

multiplexing)

nURESET

SSICLK I/O DAI/CODEC/SSI2 clock signal

SSITXFR I/O DAI/CODEC/SSI2 serial data output frame/synchronization pulse output

SSITXDA O DAI/CODEC/SSI2 serial data output

SSIRXDA I DAI/CODEC/SSI2 serial data input

SSIRXFR I/O

1

I

This pin is also latched upon the rising edge of nPOR and read along with the input

pins nTEST[0-1] to force the device into special test modes. nURESET does not

reset the RTC.

SSI2 serial data input frame/synchronization pulse

DAI/CODEC external clock input

1-8 EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

Page 23

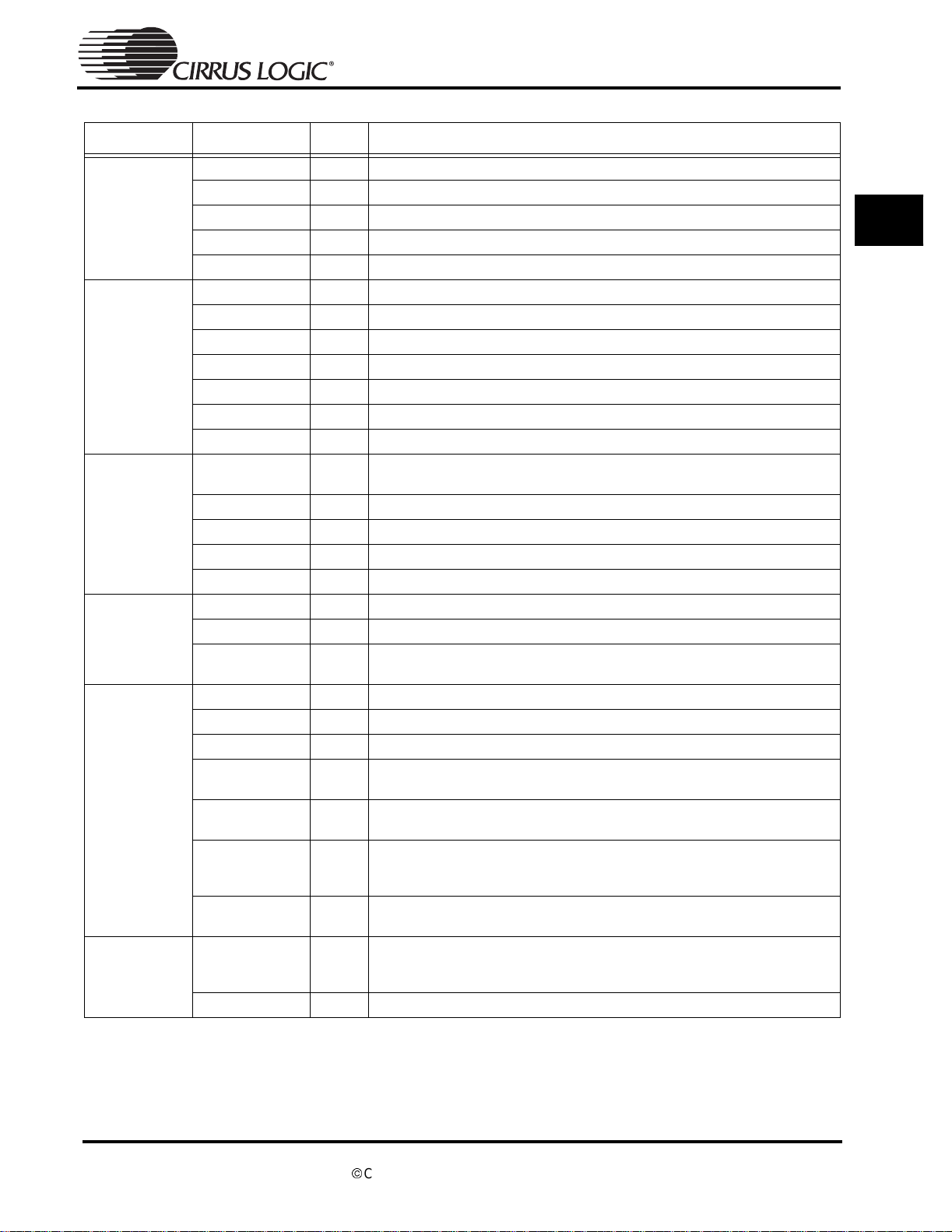

Table 1-4: External Signal Functions (Continued)

Function Signal Name Signal Description

ADCCLK O Serial clock output

ADC

Interface

(SSI1)

IrDA and

RS232

Interfaces

LCD

Keyboard &

Buzzer drive

LED Flasher

General

Purpose I/O

PWM

Drives

nADCCS O Chip select for ADC interface

ADCOUT O Serial data output

ADCIN I Serial data input

SMPCLK O Sample clock output

LEDDRV O Infrared LED drive output (UART1)

PHDIN I Photo diode input (UART1)

TXD[1-2] O RS232 UART1 and 2 TX outputs

RXD[1-2] I RS232 UART1 and 2 RX inputs

DSR I RS232 DSR input

DCD I RS232 DCD input

CTS I RS232 CTS input

DD[0-3] I/O

CL[1] O LCD line clock

CL[2] O LCD pixel clock

FRM O LCD frame synchronization pulse output

M O LCD AC bias drive

COL[0-7] O Keyboard column drives (SYSCON1)

BUZ O Buzzer drive output (SYSCON1)

PD[0]/

LEDFLSH

PA[0-7] I/O Port A I/O (bit 6 for boot clock option); also used as keyboard row inputs

PB[0-7] I/O Port B I/O. All eight Port B bits can be used as GPIOs.

PD[0-5] I/O Port D I/O / PD0 multiplexed at LEDFLSH. See above.

PD[6-7]/SDQM

[0-1]

PE[0]/

BOOTSEL[0]

PE[1]/

BOOTSEL[1]

PE[2]/

CLKSEL

DRIVE[0-1] I/O

FB[0-1] I PWM feedback inputs

LCD serial display data; pins can be used on power up to read the ID of some LCD

modules (See Table 1-6 on page 1-10).

LED flasher driver — multiplexed with Port D bit 0. This pin can provide up to 4 mA

O

of drive current.

I/O Port D I/O/dedicated byte mask select for SDRAM

Port E I/O (3 bits only). Can be used as general purpose I/O dur ing normal

I/O

operation.

During power-on reset, PE[0] and PE[1] are inputs and are latched by the rising edge

I/O

of nPOR to select the memory width that the EP73xx will use to read from the boot

code storage device (i.e., external 8-bit-wide FLASH bank).

During power-on reset, PE[2] is latched by the rising edge of nPOR to select the

I/O

clock mode of operation (i.e., either the PLL or external 13 MHz clock mode).

PWM drive outputs. These pins are inputs on power up to determine what polarity

the output of the PWM should be when active. Otherwise, these pins are always an

output (See Table 1-6 on page 1-10).

Introduction

11

1

EP7309/11/12 User’s Manual - DS508UM4 1-9

Copyright Cirrus Logic, Inc. 2003

Page 24

1

Introduction

Table 1-4: External Signal Functions (Continued)

Function Signal Name Signal Description

TDI I JTAG data in

TDO O JTAG data out

Boundary

Scan

Test nTEST[0-1] I

Oscillators

No Connects N/C No connects should be left as no connects; do not connect to ground

1. All deglitched inputs are via the 16.384 kHz clock. Each deglitched signal must be held active for at least two clock

periods. Therefore, the input signal must be active for at least ~125 µs to be detected cleanly.

The RTC crystal must be populated for the device to function properly.

TMS I JTAG mode select

TCLK I JTAG clock

nTRST I JTAG async reset

Test mode select inputs. These pins are used in conjunction with the power-on

latched state of nURESET to select between the various device test models.

MOSCIN

MOSCOUT

RTCIN

RTCOUT

I

Main 3.6864 MHz oscillator for 18.432 MHz–90.3168 MHz PLL

O

I

Real Time Clock 32.768 kHz oscillator

O

DAI/CODEC/SSI2 Pin Multiplexing

Table 1-5: SSI/CODEC/DAI Pin Multiplexing

SSI2 CODEC DAI Direction Strength

SSICLK PCMCLK SCLK I/O 1

SSITXFR PCMSYNC LRCK I/O 1

SSITXDA PCMOUT SDOUT Output 1

SSIRXDA PCMIN SDIN Input

SSIRXFR p/u* MCLK I/O 1

* p/u = use an ~10 k pull-up

The selection between SSI2 an d the CO DEC is controlled by the state of the SER SEL

bit in SYSCON2 (See SYSCON2 System Control Register 2). The choice between the

SSI2, CODEC, and the DAI is controlled by the DAISEL bit in SYSCON3 (See “System

Control Register 3 (SYSCON3)” on page 5-8).

Output B i-Directional Pins

Table 1-6: Output Bi-Directional Pins

RUN

The RUN pin is looped back in to skew the address and data bus from each other.

Drive [0-1]

DD[0-3]

The above output pins are implemented as bi-directional pins to enable the output side of the pad to be monitored and

1-10 EP7309/11/12 User’s Manual - DS508UM4

Drive 0 and 1 are looped back in on power up to determine what polarity the output of the PWM should be when

active.

DD[0-3] are looped back on power up to bits 7:4 of the SYSFLG1 register. Pin values are latched upon the enabling of

the LCD Controller via the LCDEN bit. This is useful for reading the panel ID of some LCD modules. When some LCD

modules are reset, they will output a panel ID onto these pins. See the SYSFLG1 register for more information.

hence provide more accurate control of timing or duration.

Copyright Cirrus Logic, Inc. 2003

Page 25

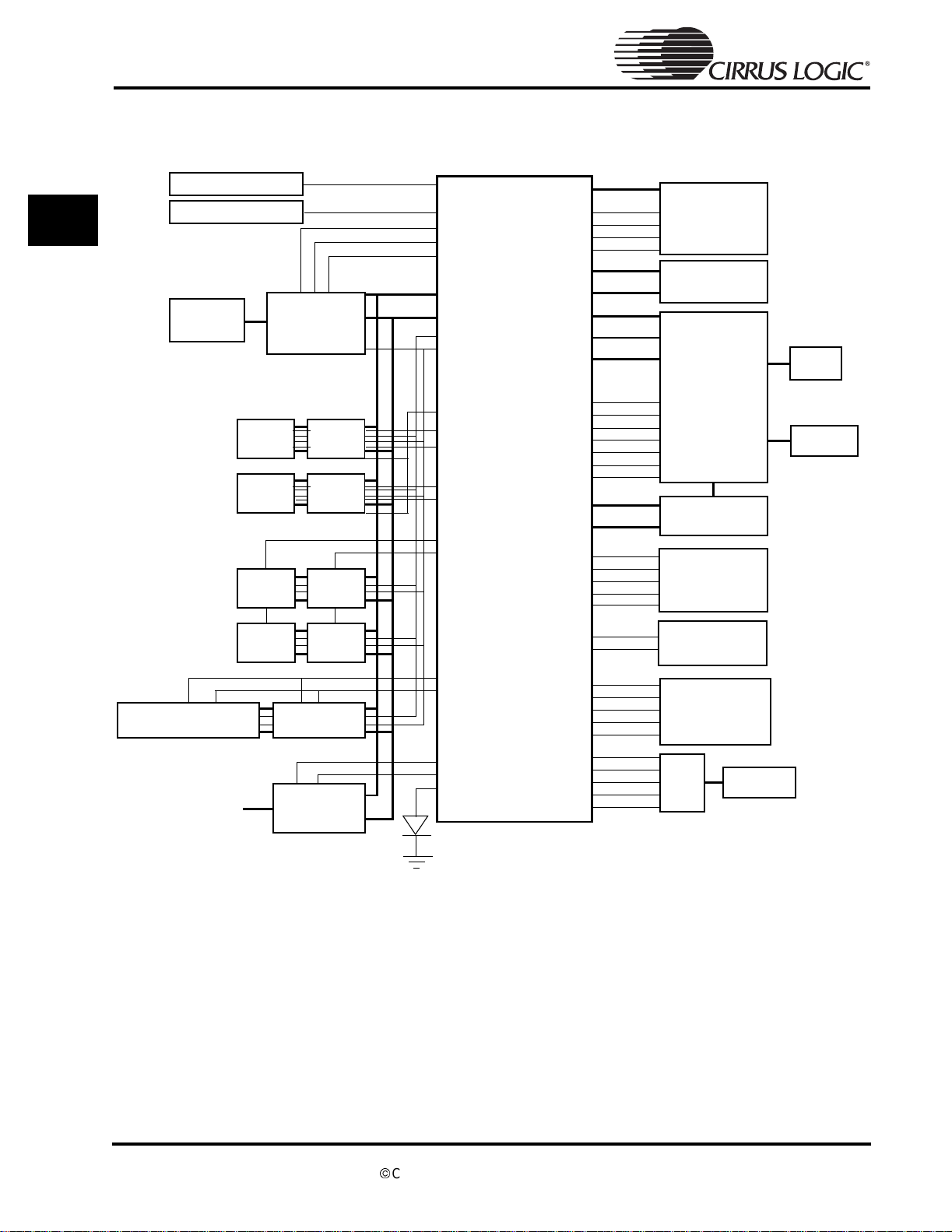

Block Diagrams

Introduction

11

13-MHz INPUT

3.6864 MHz

32.768 kHz

nPOR, RUN,

RESET, WAKEUP

BATOK, EXTPWR

PWRFL, BATCHG

EINT[1-3], FIQ,

MEDCHG

FLASHING LED DRIVE

PORTS A, B, D (8-BIT)

PORT E (3-BIT)

KEYBD DRIVERS (0-7)

DC TO DC

ADCCLK, ADCIN,

ADCOUT,

SMPCLK, ADCCS

SSICLK, SSITXFR,

SSITXDA, SSIRXDA,

SSIRSFR

PLL

32.768-kHz

OSCILLATOR

STATE

CONTROL

POWER

MANAGEMENT

INTERRUPT

CONTROLLER

RTC

GPIO

PWM

SSI1

DAI

SSI2

CODEC

INTERNAL DATA BUS

ARM720T

ARM7TDMI

CPU CORE

8-KBYTE

CACHE

MMU

WRITE

BUFFER

TIMER

COUNTERS(2)

ON-CHIP

BOOT ROM

EPB BRIDGE

EPB BUS

Figure 1-1. EP73xx Block Diagram

MEMORY CONTROLLER

EXPANSION CNTRL

SDRAM CNTRL

INTERNAL ADDRESS BUS

LCD

MaverickKey™

LCD

CONTROLLER

ON-CHIP

SRAM

48 KBYTES

UART1

UART2

ICE-JTAG

IrDA

D[0-31]

1

EXPCLK, WORD, nCS[0-3],

EXPRDY, WRITE

MOE, MWE, SDCLK,

SDQM[0-3], SDRAS,

SDCAS

A[0-27],

DRA[0-14]

TEST AND

DEVELOPMENT

LCD DRIVE

LED AND

PHOTODIODE

ASYNC

INTERFACE 1

ASYNC

INTERFACE 2

EP7309/11/12 User’s Manual - DS508UM4 1-11

Copyright Cirrus Logic, Inc. 2003

Page 26

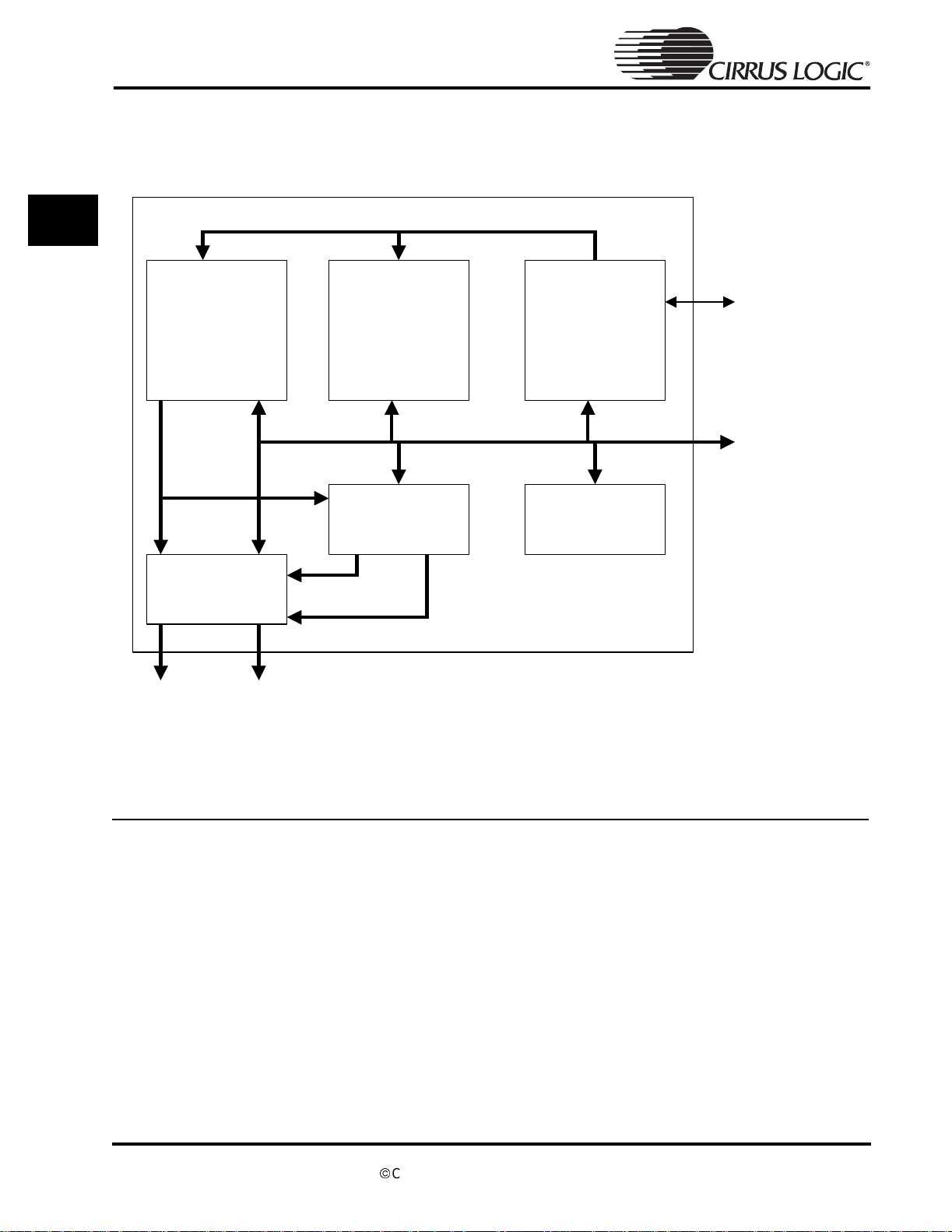

Introduction

1

CRYSTAL

CRYSTAL

PC CARD

SOCKET

SDRAM

EXTERNAL MEMORY-

MAPPED EXPANSION

ADDITIONAL I/O

CONTROLLER

×16

SDRAM

×16

×16

FLASH

×16

FLASH

PC CARD

×16

SDRAM

×16

SDRAM

×16

FLASH

×16

FLASH

BUFFERS

BUFFERS

AND

LATCHES

MOSCIN

RTCIN

nCS[4]

PB0

EXPCLK

D[0-31]

A[0-27]

nMOE

WRITE

SDRAS/

SDCAS

SDCS[0]

SDQM[0-3]

SDCS[1]

SDQM[0-3]

nCS[0]

nCS[1]

CS[n]

WORD

nCS[2]

nCS[3]

LEDFLSH

DD[0-3]

COL[0-7]

PA[0-7]

PB[0 -7]

PD[0-7]

PE[0-2]

nPOR

nPWRFL

BATOK

nEXTPWR

EP73XX

nBATCHG

WAKEUP

DRIVE [0-1]

FB[0-1]

SSICLK

SSITXFR