Cirrus Logic CS5467 User Manual

CS5467

VA+ VD+

IIN1+

IIN1-

VIN2+

VIN2-

VREFIN

VREFOUT

AGND

XIN XOUT CPUCLK DGND

CS

SDO

SDI

SCLK

INT

Voltage

Reference

System

Clock

/K

Clock

Generator

Serial

Interface

E-to-F

Power

Monitor

PFMON

x1

RESET

Digital

Filter

Calibration

MODE

Power

Calculation

Engine

4th Order

Modulator

2nd Order

Modulator

Temperature

Sensor

Digital

Filter

PGA

HPF

Option

HPF

Option

E1

E2

E3

x10

IIN2+

IIN2-

4th Order

Modulator

Digital

Filter

PGA

HPF

Option

VIN1+

VIIN1-

Digital

Filter

2nd Order

Modulator

HPF

Option

x10

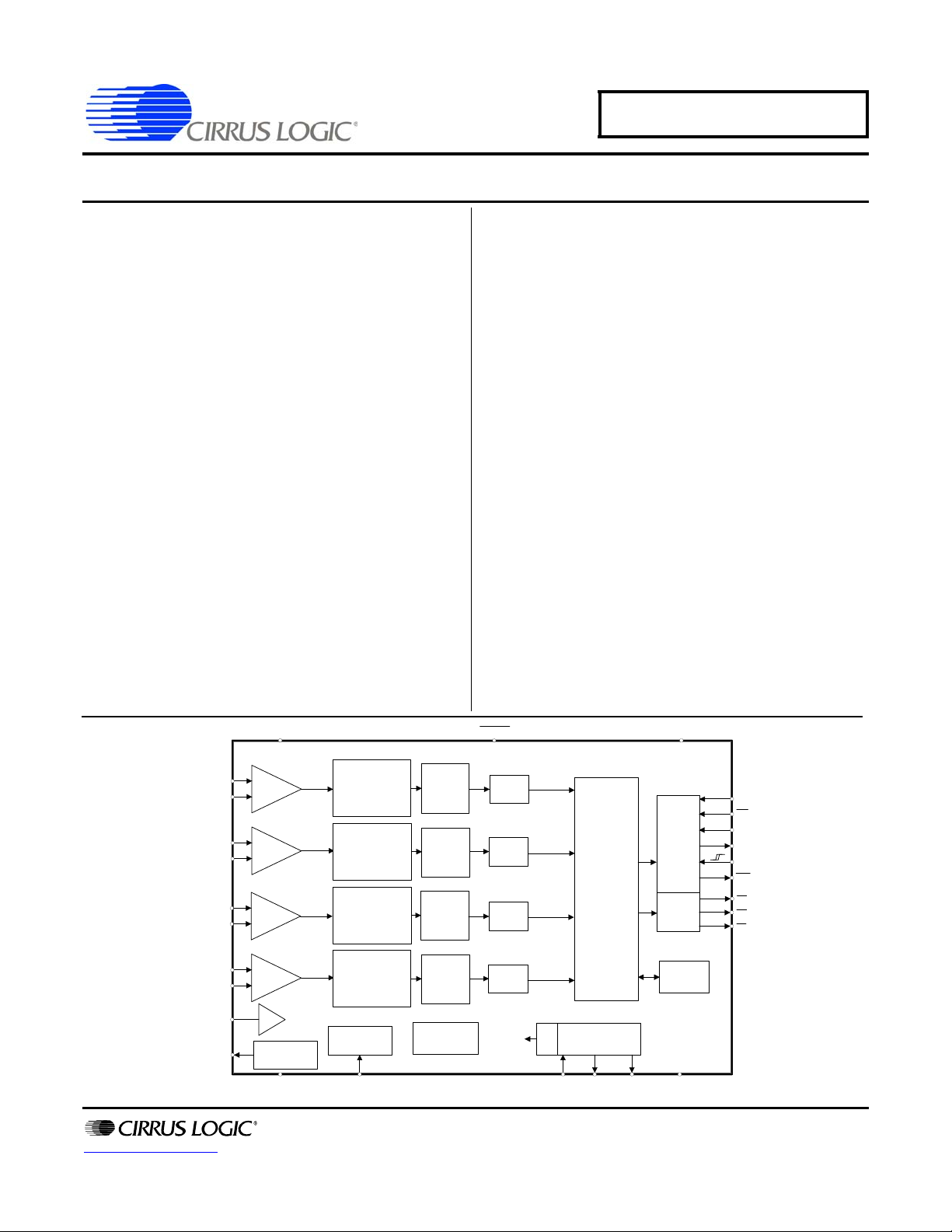

Four-channel Power/Energy IC

Features & Description

• Energy Linearity: ±0.1% of Reading over 1000:1

Dynamic Range

• On-chip Functions:

- Voltage and Current Measurement

- Active, Reactive, and Apparent Power/Energy

- RMS Voltage and Current Calculations

- Current Fault and Voltage Sag Detection

- Calibration

- Phase Compensation

- Temperature Sensor

- Energy Pulse Outputs

• Meets Accuracy Spec for IEC, ANSI, & JIS

• Low Power Consumption

• Voltage Tamper Correction

• Ground-referenced Inputs with Single Supply

• On-chip 2.5 V Reference (40 ppm / °C typ.)

• Power Supply Monitor Function

• Three-wire Serial Interface to Microcontroller or

2

E

PROM

• Power Supply Configurations

GND: 0 V, VA+: +5 V, VD+: +3.3 V to +5 V

Description

The CS5467 is a watt-hour meter on a chip. It

measures line voltage and current and calculates active, reactive, apparent power, energy,

power factor, and RMS voltage and current.

An internal RMS voltage reference can be used

if voltage measurement is disabled by

tampering.

Four analog-to-digital converters are used to

measure two voltages and two currents. Optionally, voltage2 channel can be used for

temperature measurement.

The CS5467 is designed to interface to a variety

of voltage and current sensors.

Additional features include system-level calibration, voltage sag and current fault detection,

peak detection, phase compensation, and energy pulse outputs.

ORDERING INFORMATION

See Page 45.

Copyright Cirrus Logic, Inc. 2011

(All Rights Reserved)

http://www.cirrus.com

JAN ‘11

DS714F3

CS5467

TABLE OF CONTENTS

1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2. Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Clock Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Control Pins and Serial Data I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Analog Inputs/Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Power Supply Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

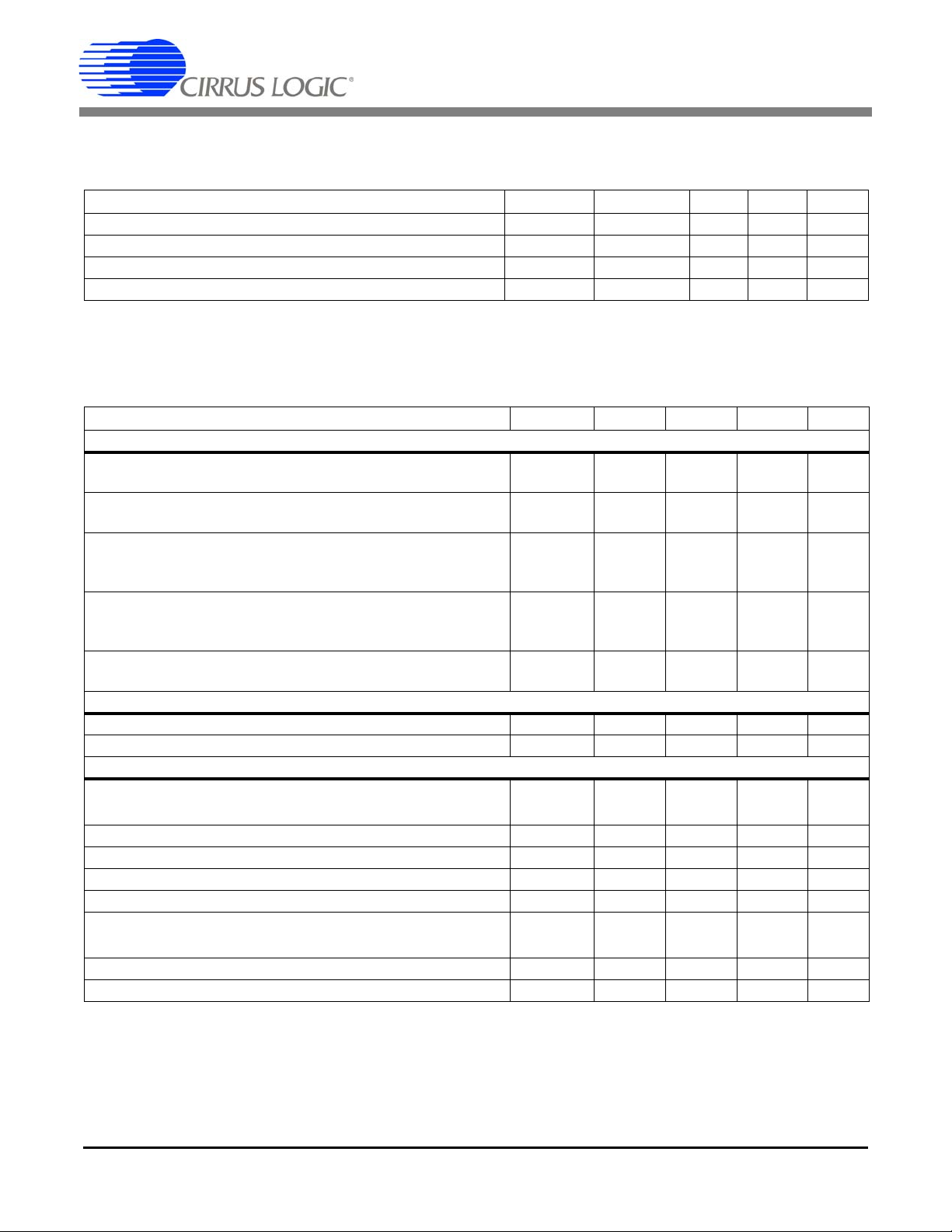

3. Characteristics & Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Analog Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Analog Inputs (All Inputs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Analog Inputs (Current Inputs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Analog Inputs (Voltage Inputs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Power Supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Voltage Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Reference Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Reference Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Digital Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Master Clock Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Filter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Input/Output Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Start-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Serial Port Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

SDI Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

SDO Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

E2PROM mode Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

E1

, E2, and E3 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4. Signal Path Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.1 Analog-to-Digital Converters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.2 Decimation Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.3 Phase Compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.4 DC Offset and Gain Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4.5 High-pass Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4.6 Low-Rate Calculations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4.7 RMS Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4.8 Power and Energy Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4.9 Peak Voltage and Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

4.10 Power Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5. Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.1 Analog Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.1.1 Voltage1 & Voltage2 Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.1.2 Current1 & Current2 Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.1.3 Power Fail Monitor Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2 DS714F3

CS5467

5.1.4 Voltage Reference Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.1.5 Voltage Reference Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.1.6 Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.2 Digital Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.2.1 Reset Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.2.2 CPU Clock Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.2.3 Interrupt Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.2.4 Energy Pulse Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.2.5 Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

6. Setting Up the CS5467 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6.1 Clock Divider . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6.2 CPU Clock Inversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6.3 Interrupt Pin Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6.4 Current Input Gain Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6.5 High-pass Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6.6 Cycle Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6.7 Energy Pulse Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6.8 No Load Threshold . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

6.9 Energy Pulse Width . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

6.10 Energy Pulse Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

6.11 Voltage Sag/Current Fault Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

6.12 Epsilon . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

6.13 Temperature Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

7. Using the CS5467 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

7.1 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

7.2 Power-down States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

7.3 Voltage Tamper Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

7.4 Command Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

7.5 Register Paging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

7.6 Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

8. Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

8.1 Page Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

8.2 Page 0 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

8.3 Page 1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

8.4 Page 2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

8.5 Page 5 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

9. System Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

9.1 Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

9.1.1 Offset Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

9.1.1.1 DC Offset Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

9.1.1.2 AC Offset Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

9.1.2 Gain Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

9.1.2.1 AC Gain Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

9.1.2.2 DC Gain Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

DS714F3 3

CS5467

9.1.3 Calibration Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

9.1.4 Temperature Sensor Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

9.1.4.1 Temperature Offset Calibration . . . . . . . . . . . . . . . . . . . . . . . 41

9.1.4.2 Temperature Gain Calibration . . . . . . . . . . . . . . . . . . . . . . . . 41

10. E2PROM Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.1 E2PROM Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.2 E2PROM Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.3 Which E2PROMs Can Be Used? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

11. Basic Application Circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

12. Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

13. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

14. Environmental, Manufacturing, & Handling Information . . . . . . . . . . . . . . . . . 45

15. Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

LIST OF FIGURES

Figure 1. CS5467 Read and Write Timing Diagrams ................................................................. 12

Figure 2. Timing Diagram for

Figure 3. Signal Flow for V1, I1, P1, Q1 Measurements ............................................................ 14

Figure 4. Signal Flow for V2, I2, P2, Q2 Measurements ............................................................ 14

Figure 5. Low-rate Calculations.................................................................................................. 16

Figure 6. Two-channel Power Summation.................................................................................. 16

Figure 7. Oscillator Connections................................................................................................. 18

Figure 8. Sag and Fault Detect................................................................................................... 22

Figure 9. Fixed RMS Voltage Selection...................................................................................... 23

Figure 10. Calibration Data Flow................................................................................................40

Figure 11. System Calibration of Offset ...................................................................................... 40

Figure 12. System Calibration of Gain. ....................................................................................... 41

Figure 13. Typical Interface of E

Figure 14. Typical Connection Diagram ..................................................................................... 43

E1, E2, and E3.............................................................................. 13

2

PROM to CS5467 .................................................................. 42

LIST OF TABLES

Table 1. Interrupt Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 2. Current Input Gain Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 3. High-pass Filter Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 4. E2

Table 5. E3

Table 6. E1

Table 7. E3

4 DS714F3

Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

/ E2 Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Pin with E1MODE enabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

CS5467

1. OVERVIEW

The CS5467 is a CMOS power measurement integrated circuit utilizing four analog-to-digital convert-

ers to measure two line voltages and two currents. Optionally, voltage2 channel can be used for temperature measurement. It calculates active, reactive, and apparent power as well as RMS and peak voltage

and current. It handles other system-related functions, such as pulse output conversio n, voltage sag, current fault, voltage zero crossing, line frequency, and voltage tamper correction.

The CS5467 is optimized to interface to current transformers or shunt resistors for current measurement,

and to resistive dividers or voltage transformers for voltage measurement. Two full-scale ranges are provided on the current inputs to accommodate both types of current sensors. The CS5467’s four differ ential

inputs have a common-mode input range from analog ground (AGND) to the positive analog supply

(VA+).

An additional analog input (PFMON) is provided to allow the application to determine when a power failure

is in progress. By monitoring the unregulated power supply, the application can take any required action

when a power loss occurs.

An on-chip voltage reference (nominally 2.5 volts) is generated and provided at analog output, VREFOUT.

This reference can be supplied to the chip by connecting it to the reference voltage input, VREFIN. Alternatively, an external voltage reference can be supplied to the reference input.

Three digital outputs (E1

ed, provide energy pulses, power failure indication, or other choices.

The CS5467 includes a three-wire serial host interface to an external microcontroller or serial E

Signals include serial data input (SDI), serial data output (SDO), serial clock (SCLK), and optionally a chip

select (CS

to control whether an E

), which allows the CS5467 to share the SDO signal with other devices. A MODE input is used

, E2, E3) provide a variety of output signals and, depending on the mode select-

2

PROM.

2

PROM will be used instead of a host microcontroller.

DS714F3 5

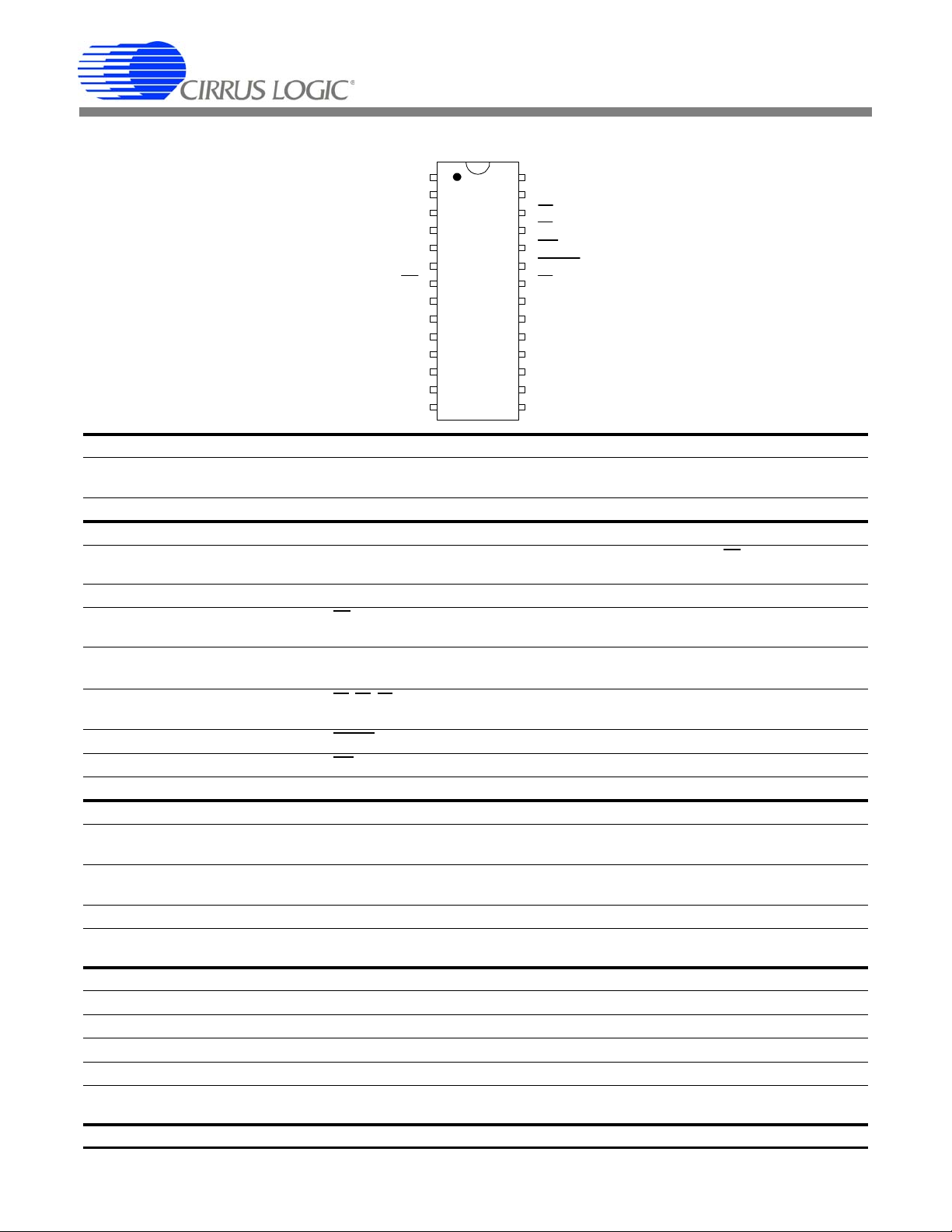

2. PIN DESCRIPTION

VREFIN 12Voltage Reference Input

VREFOUT 11Voltage Reference Output

VIN1- 10Differential Voltage Input

VIN1+ 9Differential Voltage Input

MODE 8Mode Select

CS 7Chip Select

SDO 6Serial Data Ouput

SCLK 5Serial Clock

DGND 4Digital Ground

VD+ 3Positive Digital Supply

CPUCLK 2CPU Clock Output

XOUT 1Crystal Out

AGND17 Analog Ground

VA+18 Positive Analog Supply

IIN1-19 Differential Current Input

IIN1+20 Differential Current Input

PFMON21 Power Fail Monitor

E322 Energy Output 3

RESET23 Reset

INT24 Interrupt

E125 Energy Output 1

26

SDI27 Serial Data Input

XIN28 Crystal In

E2

Energy Output 2

VIN2- 14Differential Voltage Input

VIN2+ 13Differential Voltage Input

IIN2-15 Differential Current Input

IIN2+16 Differential Current Input

Clock Generator

Crystal Out

Crystal In

CPU Clock Output 2

Control Pins and Serial Data I/O

Serial Clock 5

Serial Data Output 6

Chip Select 7

XOUT, XIN — Connect to an external quartz crystal. Alternatively, an external clock can be sup-

1,28

plied to the XIN pin to provide the system clock for the device.

CPUCLK — Logic-level output from crystal oscillator. Can be used to clock an external CPU.

SCLK — Clocks serial data from the SDI pin and to the SDO pin when CS is low. SCLK is a

Schmitt-trigger input when MODE is low and a driven output when MODE is high.

SDO — Serial data output. Data is clocked out by SCLK.

CS — An input that enables the serial interface when MODE is low and a driven output when

MODE is high.

CS5467

Mode Select 8

Energy Output

22, 25,

Reset 23

Interrupt 24

Serial Data Input 27

MODE — High selects external E2PROM, Low selects external microcontroller. MODE includes a

weak internal pull-down and therefore selects microcontroller mode if not connected.

E3, E1, E2 — Primarily active-low energy pulse outputs. These can be programmed to output

other conditions.

26

RESET — An active-low Schmitt-trigger input used to reset the chip.

INT — Active-low output, indicates that an enabled condition has occurred.

SDI — Serial data input. Data is clocked in by SCLK.

Analog Inputs/Outputs

Differential V ol tage Inputs

Differential Current Inputs

Voltage Reference Output 11

Voltage Reference Input 12

Power Supply Connections

Positive Digital Supply 3

Digital Ground 4

Positive Analog Supply 18

Analog Ground 17

Power Fail Monitor 21

6 DS714F3

9,10

13, 14

20,19,

16,15

VIN1+, VIN1-, VIN2+, VIN2- — Differential analog inputs for the voltage channels.

IIN1+, IIN1-, IIN2+, IIN2- — Differential analog inputs for the current channels.

VREFOUT — The on-chip voltage reference output. Nominally 2.5 V, referenced to AGND.

VREFIN — The voltage reference input. Can be connected to VREFOUT or external 2.5 V refer-

ence.

VD+ — The positive digital supply.

DGND — Digital ground.

VA+ — The positive analog supply.

AGND — Analog ground.

PFMON — Used to monitor the unregulated power supply via a resistive divider. If the PFMON

voltage drops below its low limit, the low-supply detect (LSD) bit is set in the Status register.

CS5467

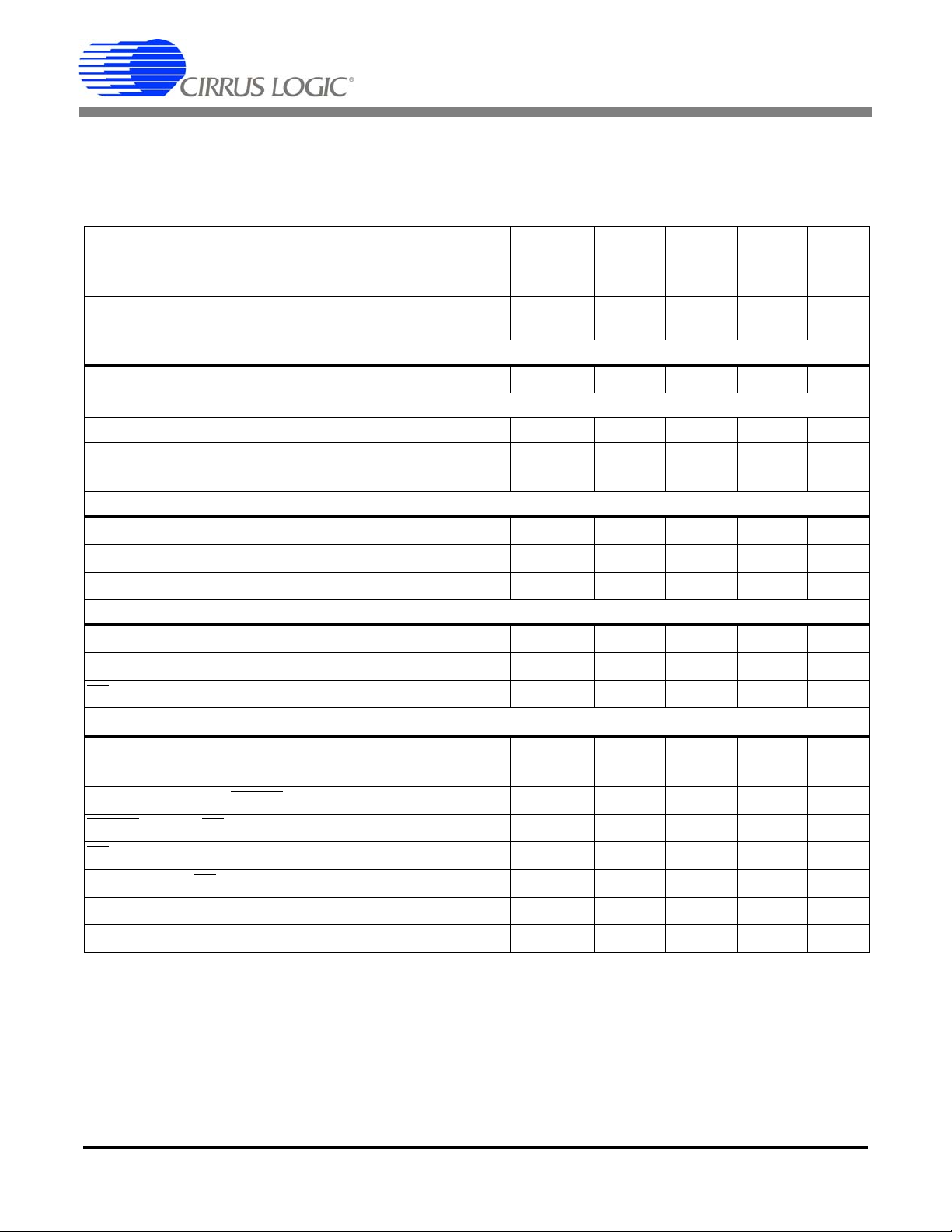

3. CHARACTERISTICS & SPECIFICATIONS

RECOMMENDED OPERATING CONDITIONS

Parameter Symbol Min Typ Max Unit

Positive Digital Power Supply VD+ 3.135 5.0 5.25 V

Positive Analog Power Supply VA+ 4.75 5.0 5.25 V

Voltage Reference VREFIN - 2.5 - V

Specified Temperature Range T

A

ANALOG CHARACTERISTICS

• Min / Max characteristics and specifications are guaranteed over all Recommended Operating Conditions.

• Typical characteristics and specifications are measured at nominal supply voltages and TA = 25 °C.

• VA+ = VD+ = 5 V ±5%; AGND = DGND = 0 V; VREFIN = +2.5 V. All voltages with respect to 0 V.

• DCLK = 4.096 MHz.

Parameter Symbol Min Typ Max Unit

Accuracy

Active Power

(Note 1) Input Range 0.1% - 100%

Reactive Power

(Note 1 and 2) Input Range 0.1% - 100%

Power Factor

(Note 1 and 2) Input Range 1.0% - 100%

Input Range 0.1% - 1.0%

Current RMS

(Note 1) Input Range 1.0% - 100%

Input Range 0.1% - 1.0%

Volt age RMS

(Note 1) Input Range 5% - 100%

Analog Inputs (All Inputs)

Common Mode Rejection

Common Mode + Signal -0.25 - VA+ V

Analog Inputs (Current Inputs)

Differential Input Range

[(IIN+) – (IIN-)] (Gain = 50)

Total Harmonic Distortion (Gain = 50) THD 80 94 - dB

Crosstalk from Voltage input at Full Scale

Input Capacitance IC - 27 - pF

Effective Input Impedance EII 30 - - k

Noise (Referred to Input)

Offset Drift (Without the High-pass Filter) OD - 4.0 - µV/°C

Gain Error

Notes: 1. Applies when the HPF option is enabled.

2. Applies when the line frequency is equal to the product of the output word rate (OWR) and the value of

Epsilon.

All Gain Ranges

All Gain Ranges

All Gain Ranges

P

ACTIVE

Q

AVG

PF -

All Gain Ranges

I

RMS

All Gain Ranges

(DC, 50, 60 Hz) CMRR 80 - - dB

(Gain = 10)

(50, 60 Hz) --115-dB

(Gain = 10)

(Gain = 50)

(Note 3) GE - ±0.4 %

V

RMS

IIN

N

I

-40 - +85 °C

-±0.1-%

-±0.2-%

±0.2

-

±0.27

-

-

%

%

%

-

-

±0.1

±0.17

-

-

%

%

-±0.1-%

-

-

-

-

500

100

-

-

-

-

22.5

4.5

mV

mV

µV

µV

P-P

P-P

rms

rms

DS714F3 7

CS5467

PSRR 20

150

V

eq

--------- -

log=

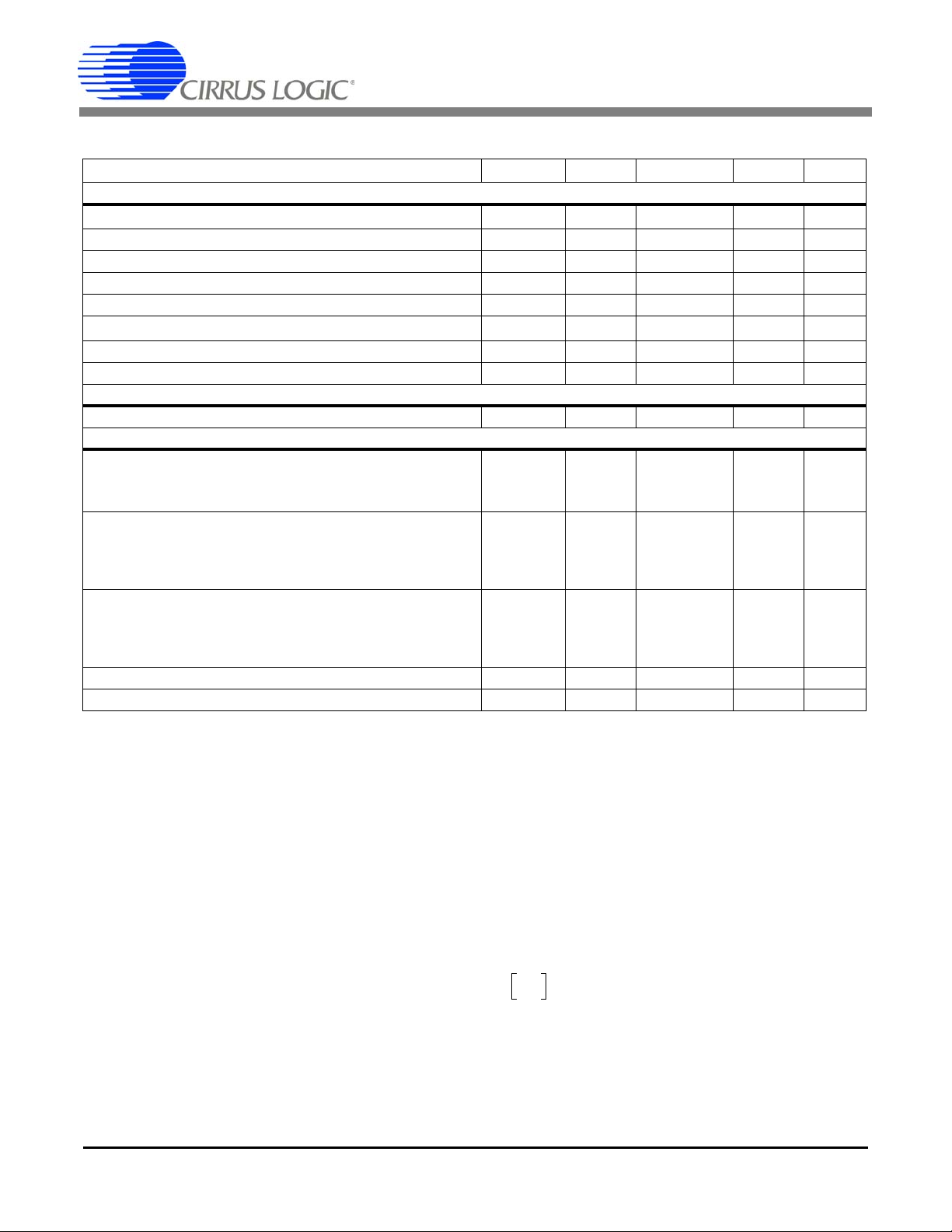

ANALOG CHARACTERISTICS (Continued)

Parameter Symbol Min Typ Max Unit

Analog Inputs (Voltage Inputs)

Differential Input Range

Total Harmonic Distortion THD 65 75 - dB

Crosstalk from Current inputs at Full Scale

Input Capacitance

Effective Input Impedance EII 2 - - M

Noise (Referred to Input) N

Offset Drift (Without the High-pass Filter) OD - 16.0 - µV/°C

Gain Error

Temperature

Temperature Accuracy T - ±5 - °C

Power Supplies

Power Supply Currents (Active State)

I

(VA+ = 5V, VD+ = 3.3V)

D+

Power Consumption

(Note 4) Active State (VA+ = 5 V, VD+ = 3.3 V)

Power Supply Rejection Ratio

(Note 5)

Active State (VA+ = VD+ = 5 V)

(50, 60 Hz)

PFMON Low-voltage Trigger Threshold

PFMON High-voltage Power-on Trip Point

[(VIN+) – (VIN-)] VIN - 500 - mV

(50, 60 Hz) --70-dB

All Gain Ranges IC - 2.0 - pF

--140µV

-

-

-

-

-

-

-

48

68

60

1.5

3.5

2.3

25

15

7

10

55

75

65

33

20

(Note 3) GE - ±3.0 %

I

I

(VA+ = VD+ = 5V)

D+

Stand-by State

Sleep State

Voltage

Current

(Gain = 50x)

Current (Gain = 10x)

(Note 6) PMLO 2.3 2.45 - V

(Note 7) PMHI - 2.55 2.7 V

V

PSCA

A+

PSCD

PSCD

PC

PSRR

rms

-

-

-

mA

mA

mA

mW

mW

-

-

-

-

-

mW

uW

dB

dB

dB

P-P

Notes: 3. Applies before system calibration.

4. All outputs unloaded. All inputs CMOS level.

5. Measurement method for PSRR: VREFIN tied to VREFOUT, VA+ = VD+ = 5 V, a 150 mV

(zero-to-peak) (60 Hz) sinewave is imposed onto the +5 V DC supply voltage at VA+ and VD+ pins. The

“+” and “-” input pins of both input ch annels a re sh or ted to AGND. T he CS5 467 is then command ed to

continuous conversion acquisition mode, and digital output data is collected for the chan nel under test.

The (zero-to-peak) value of the digital sinusoidal out put signal is determined, and this value is converted

into the (zero-to-peak) value of the sinusoidal voltage (me asured in m V) that would need to be applied

at the channel’s inputs, in order to cause the sa me digital sinusoidal output. This voltage is then defined

as Veq. PSRR is (in dB)

:

6. When the voltage level on PFMON is sagging and LSD bit = 0, this is the voltage at which LSD is set to 1.

7. If the LSD bit has been set to 1 (because PFMON voltage fell below PMLO), this is the voltage level on

PFMON at which the LSD bit can be permanently reset back to 0.

8 DS714F3

CS5467

(VREFOUTMAX - VREFOUTMIN)

VREFOUT

AVG

(

(

1

T

A

MAX

- T

A

MIN

(

(

1.0 x 10

(

(

6

TC

VREF

=

VOLTAGE REFERENCE

Parameter Symbol Min Typ Max Unit

Reference Output

Output Voltage VREFOUT +2.4 +2.5 +2.6 V

Temperature Coefficient

Load Regulation

Reference Input

Input Voltage Range VREFIN +2.4 +2.5 +2.6 V

Input Capacitance - 4 - pF

Input CVF Current - 100 - nA

Notes: 8. The voltage at VREFOUT is measured across the temperature range. From these measurements the

following formula is used to calculate the VREFOUT temperature coefficient.

9. Specified at maximum recommended output of 1 µA, source or sink.

(Note 8) TC

(Note 9) V

VREF

R

- 40 - ppm/°C

-610mV

DS714F3 9

CS5467

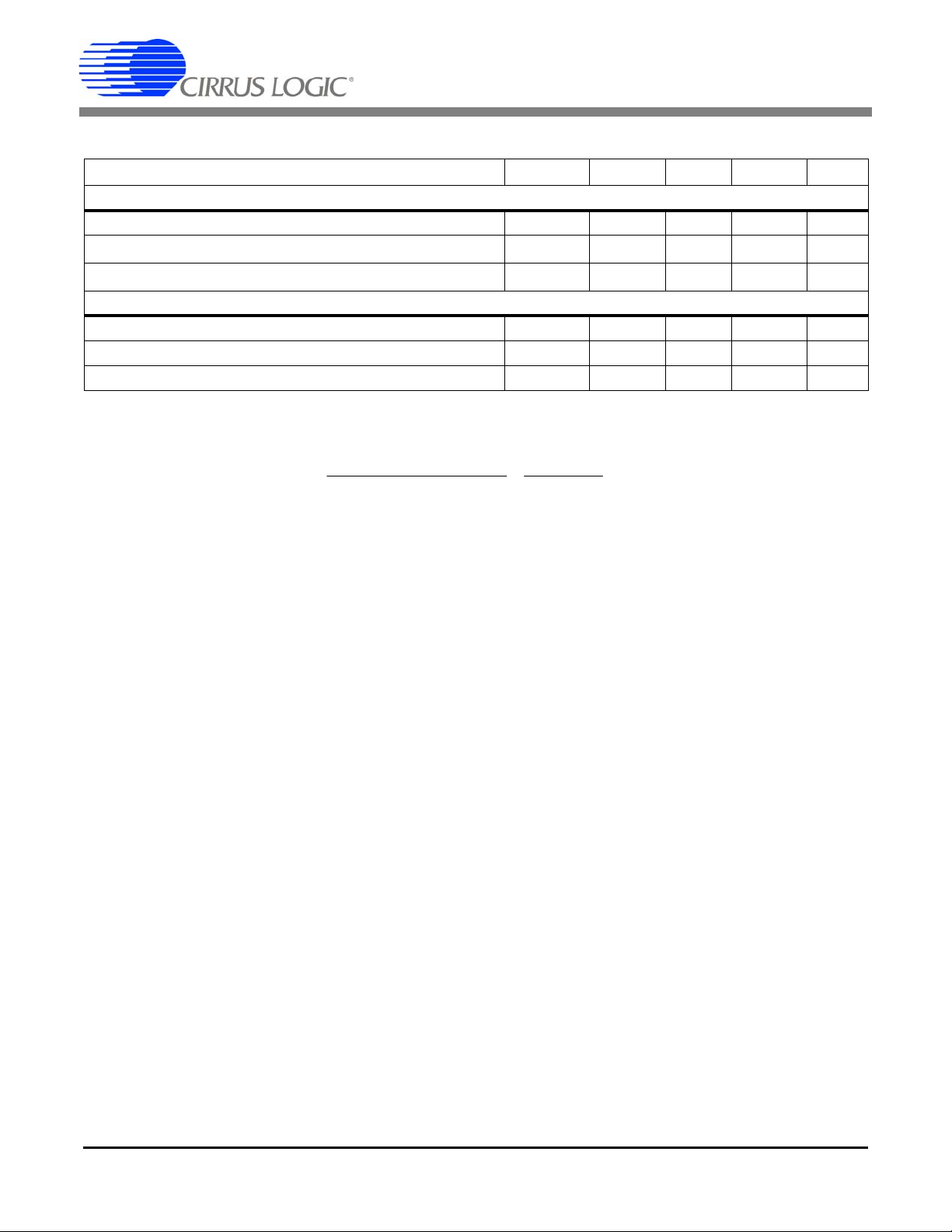

DIGITAL CHARACTERISTICS

• Min / Max characteristics and specifications are guaranteed over all Recommended Operating Conditions.

• Typical characteristics and specifications are measured at nominal supply voltages and TA = 25 °C.

• VA+ = VD+ = 5V ±5%; AGND = DGND = 0 V. All voltages with respect to 0 V.

• DCLK = 4.096 MHz.

Parameter Symbol Min Typ Max Unit

Master Clock Characteristics

Master Clock Frequency

Master Clock Duty Cycle 40 - 60 %

CPUCLK Duty Cycle

Filter Characteristics

Phase Compensation Range

Input Sampling Rate

Digital Filter Output Word Rate

High-pass Filter Corner Frequency

Full-scale DC Calibration Range (Referred to Input)

Channel-to-channel Time-shift Error

Input/Output Characteristics

High-level Input Voltage

All Pins Except XIN and SCLK and RESET

Low-level Input Voltage (VD = 5 V)

All Pins Except XIN and SCLK and RESET

Low-level Input Voltage (VD = 3.3 V)

All Pins Except XIN and SCLK and RESET

High-level Output Voltage

Low-level Output Voltage

Input Leakage Current

3-state Leakage Current I

Digital Output Pin Capacitance C

Internal Gate Oscillator (Note 11) DCLK 2.5 4.096 20 MHz

(Note 12 and 13) 40 - 60 %

(60 Hz, OWR = 4000 Hz) -5.4 - +5.4 °

DCLK = MCLK/K - DCLK/8 - Hz

(Both channels) OWR - DCLK/1024 - Hz

-3 dB -0.5-Hz

(Note 14) FSCR 25 - 100 %FS

(Note 15) 1.0 µs

SCLK and RESET

SCLK and RESET

SCLK and RESET

I

out

I

=-5mA(VD=+5V)

out

= -2.5 mA (VD = +3.3V)

I

out

XIN

XIN

XIN

= +5 mA V

(Note 16) I

V

IH

0.6 VD+

(VD+) – 0.5

0.8VD+

V

IL

-

-

-

V

IL

-

-

-

(VD+) - 1.0 - - V

OH

V

OL

-

-

in

OZ

out

-±1±10µA

--±10µA

-5-pF

-

-

-

-

-

-

-

-

-

-

-

-

-

-

0.8

1.5

0.2VD+

0.48

0.3

0.2VD+

0.4

0.4

V

V

V

V

V

V

V

V

V

V

V

Notes: 10. All measurements performed under static conditions.

11. If a crystal is used, XIN frequency must remain between 2.5 MHz - 5.0 MHz. If an external oscillator is

used, XIN frequency range is 2.5 MHz - 20 MHz, but K must be set so that MCLK is between

2.5 MHz - 5.0 MHz.

12. If external MCLK is used, the duty cycle must be between 45% and 55% to maintain this specification.

13. The frequency of CPUCLK is equal to MCLK.

14. The minimum FSCR is limited by the maximum allowed gain register value. The maximum FSCR is

limited by the full-scale signal applied to the input.

15. Configuration register (Config) bits PC[6:0] are set to “0000000”.

16. The MODE pin is pulled low by an internal resistor.

10 DS714F3

CS5467

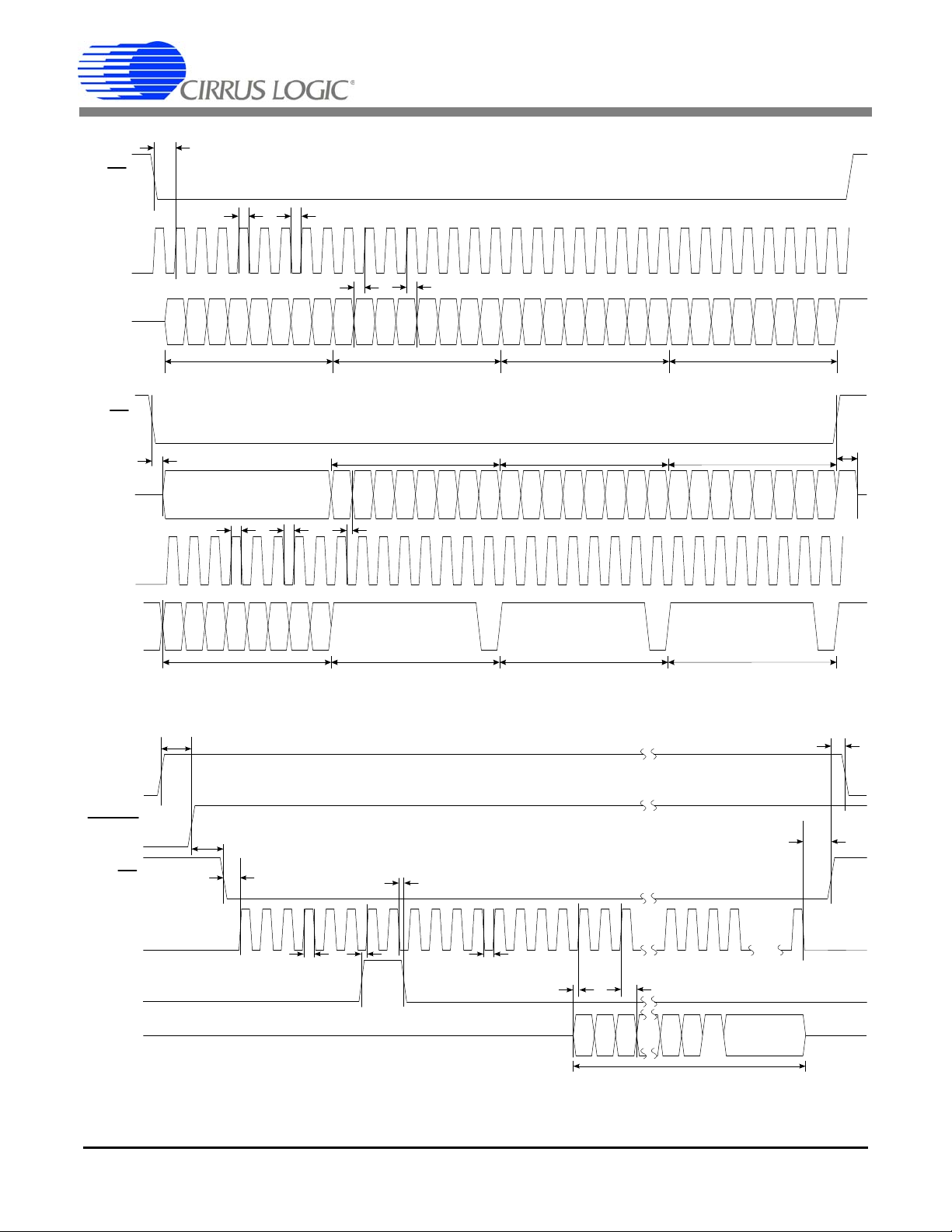

SWITCHING CHARACTERISTICS

• Min / Max characteristics and specifications are guaranteed over all Recommended Operating Conditions.

• Typical characteristics and specifications are measured at nominal supply voltages and TA = 25 °C.

• VA+ = 5 V ±5% VD+ = 3.3 V ±5% or 5 V ±5%; AGND = DGND = 0 V. All voltages with respect to 0 V.

• Logic Levels: Logic 0 = 0 V, Logic 1 = VD+.

Parameter Symbol Min Typ Max Unit

Rise Times

(Note 17)

Any Digital Output

Fall Times

(Note 17)

Any Digital Output

Start-up

Oscillator Start-up Time

XTAL = 4.096MHz (Note 18) t

Serial Port Timing

Serial Clock Frequency SCLK - - 2 MHz

Serial Clock

Pulse Width High

Pulse Width Low

SDI Timing

CS

Falling to SCLK Rising t

Data Set-up Time Prior to SCLK Rising t

Data Hold Time After SCLK Rising t

SDO Timing

Falling to SDO Driving t

CS

SCLK Falling to New Data Bit (hold time) t

Rising to SDO Hi-Z t

CS

2

E

PROM mode Timing

Serial Clock

MODE setup time to RESET

RESET

CS

SCLK falling to CS

CS

rising to CS falling t

falling to SCLK rising t

rising t

rising to driving MODE low t

Rising t

Pulse Width Low

Pulse Width High

SDO setup time to SCLK rising t

Notes: 17. Specified using 10% and 90% points on waveform of interest. Output loaded with 50 pF.

18. Oscillator start-up time varies with crystal parameters. This specification does not apply when using an

external clock source.

t

rise

t

t

fall

ost

t

t

t

10

11

12

13

14

15

16

-

-

-

-

50

50

-

-

1.0

-

1.0

-

µs

ns

µs

ns

-60-ms

1

2

3

4

5

6

7

8

9

200

200

50 - - ns

50 - - ns

100 - - ns

-2050ns

-2050ns

-2050ns

-

-

8

8

-

-

ns

ns

DCLK

DCLK

50 ns

48 DCLK

100 8 DCLK

16 DCLK

50 ns

100 ns

DS714F3 11

t

1

t

2

t

3

t

4

t

5

MSB

MSB-1

LSB

MSB

MSB-1

LSB

MSB

MSB-1

LSB

MSB

MSB-1

LSB

Com m and Tim e 8 SC LKs H igh Byte Mid Byte Low Byte

CS

SCLK

SDI

t

10

t

9

RESET

SDO

SCLK

CS

Last 8

Bits

SDI

MODE

STOP bit

D a ta fro m E E P R O M

t

16

t

4

t

5

t

14

t

15

t

7

t

13

t

12

t

11

(INPUT)

(INPUT)

(O UT P U T )

(O UT P U T )

(O UT P U T )

(INPUT)

t

1

t

2

MSB

MSB-1

LSB

Comm and Time 8 SC LKs

SYNC0 or SYNC1

Command

SYNC0 or SYNC1

Comm and

MSB

MSB-1

LSB

MSB

MSB-1

LSB

MSB

MSB-1

LSB

Hig h Byte Mid Byte Low B yte

CS

SDO

SCLK

SDI

t

6

t

7

t

8

SYNC0 or SYNC1

Comm and

UNKNOWN

SDI Write Timing (Not to Scale)

SDO Read Timing (Not to Scale)

Figure 1. CS5467 Read and Write Timing Diagrams

E2PROM mode Sequence Timing (Not to Scale)

CS5467

12 DS714F3

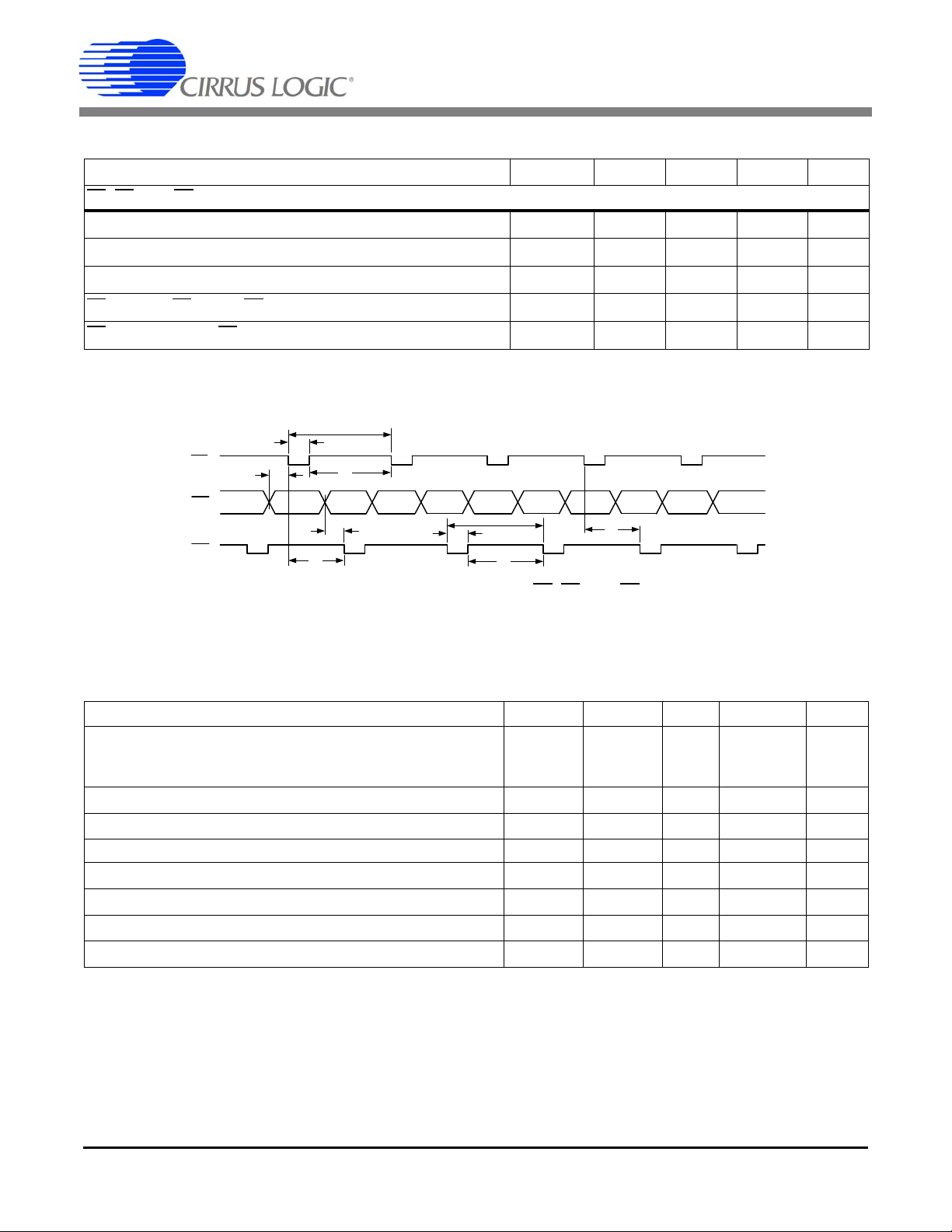

CS5467

t

period

E1

t

3

t

4

t

5

t

3

t

5

t

4

E2

E3

t

pw

t

period

t

pw

Figure 2. Timing Diagram for E1, E2, and E3

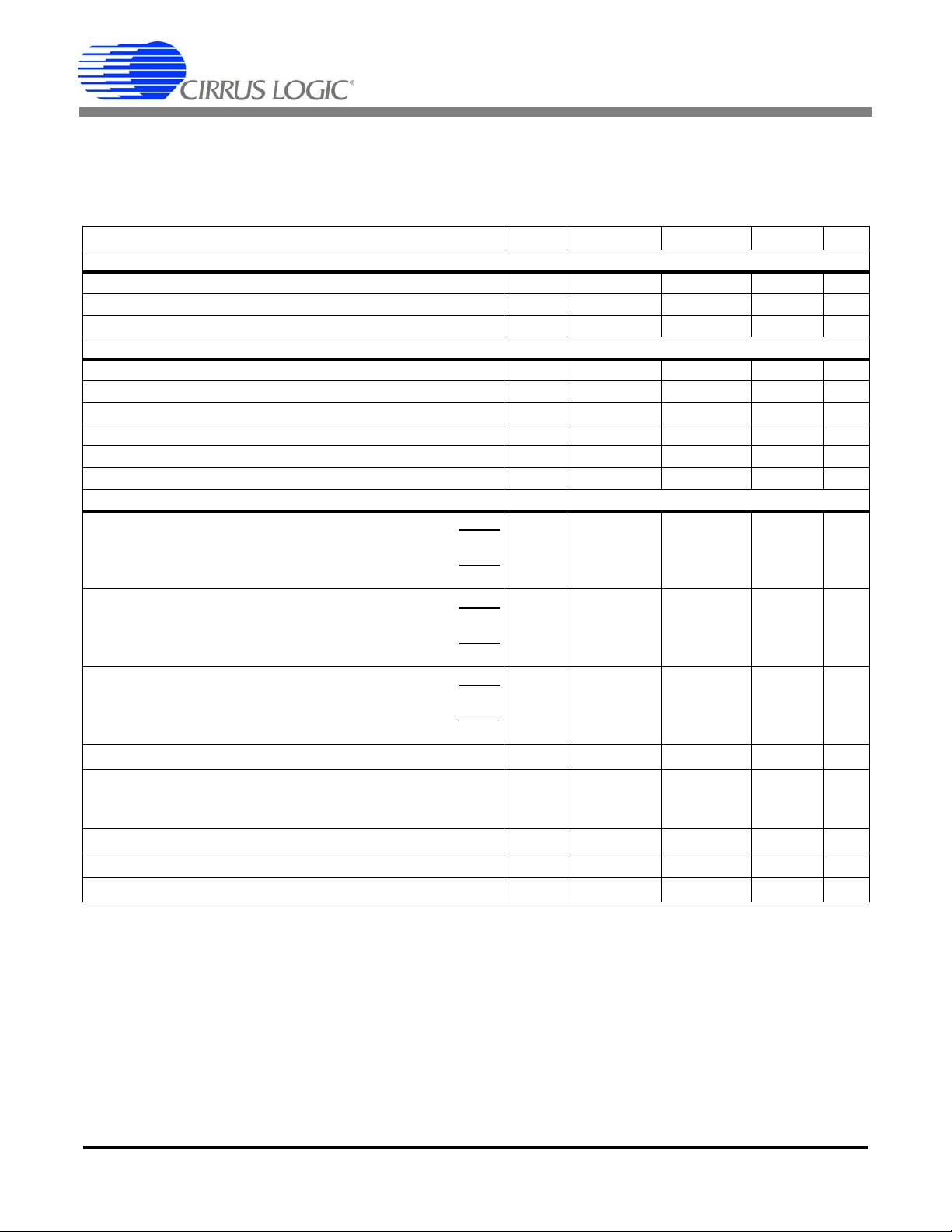

SWITCHING CHARACTERISTICS (Continued)

Parameter Symbol Min Typ Max Unit

E1

, E2, and E3 Timing (Note 19 and 20)

Period t

Pulse Width t

Rising Edge to Falling Edge t

Setup to E1 and/or E3 Falling Edge t

E2

Falling Edge to E3 Falling Edge t

E1

period

pw

3

4

5

Notes: 19. Pulse output timing is specified at DCLK = 4.096 MHz, E2MODE = 0, and E3MODE[1:0] = 0. Refer to

6.7 Energy Pulse Outputs on page 20 for more information on pulse output pins.

20. Timing is proportional to the frequency of DCLK.

500 - - s

244 - - s

6--s

1.5 - - s

248 - - s

ABSOLUTE MAXIMUM RATINGS

WARNING: Operation at or beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes

Parameter Symbol Min Typ Max Unit

DC Power Supplies

Input Current, Any Pin Except Supplies

(Notes 21 and 22)

Positive Digital

Positive Analog

(Notes 23, 24, 25) I

Output Current, Any Pin Except VREFOUT I

Power Dissipation

Analog Input Voltage

Digital Input Voltage

(Note 26) PD --500mW

All Analog Pins V

All Digital Pins V

Ambient Operating Temperature T

Storage Temperature T

Notes: 21. VA+ and AGND must satisfy [(VA+) - (AGND)] + 6.0 V.

22. VD+ and AGND must satisfy [(VD+) - (AGND)] + 6.0 V.

23. Applies to all pins including continuous over-voltage conditions at the analog input pins.

24. Transient current of up to 100 mA will not cause SCR latch-up.

25. Maximum DC input current for a power supply pin is ±50 mA.

26. Total power dissipation, including all input currents and output currents.

.

VD+

VA+

IN

OUT

INA

IND

A

stg

-0.3

-0.3

--±10mA

--100mA

- 0.3 - (VA+) + 0.3 V

-0.3 - (VD+) + 0.3 V

-40 - 85 °C

-65 - 150 °C

-

-

+6.0

+6.0

V

V

DS714F3 13

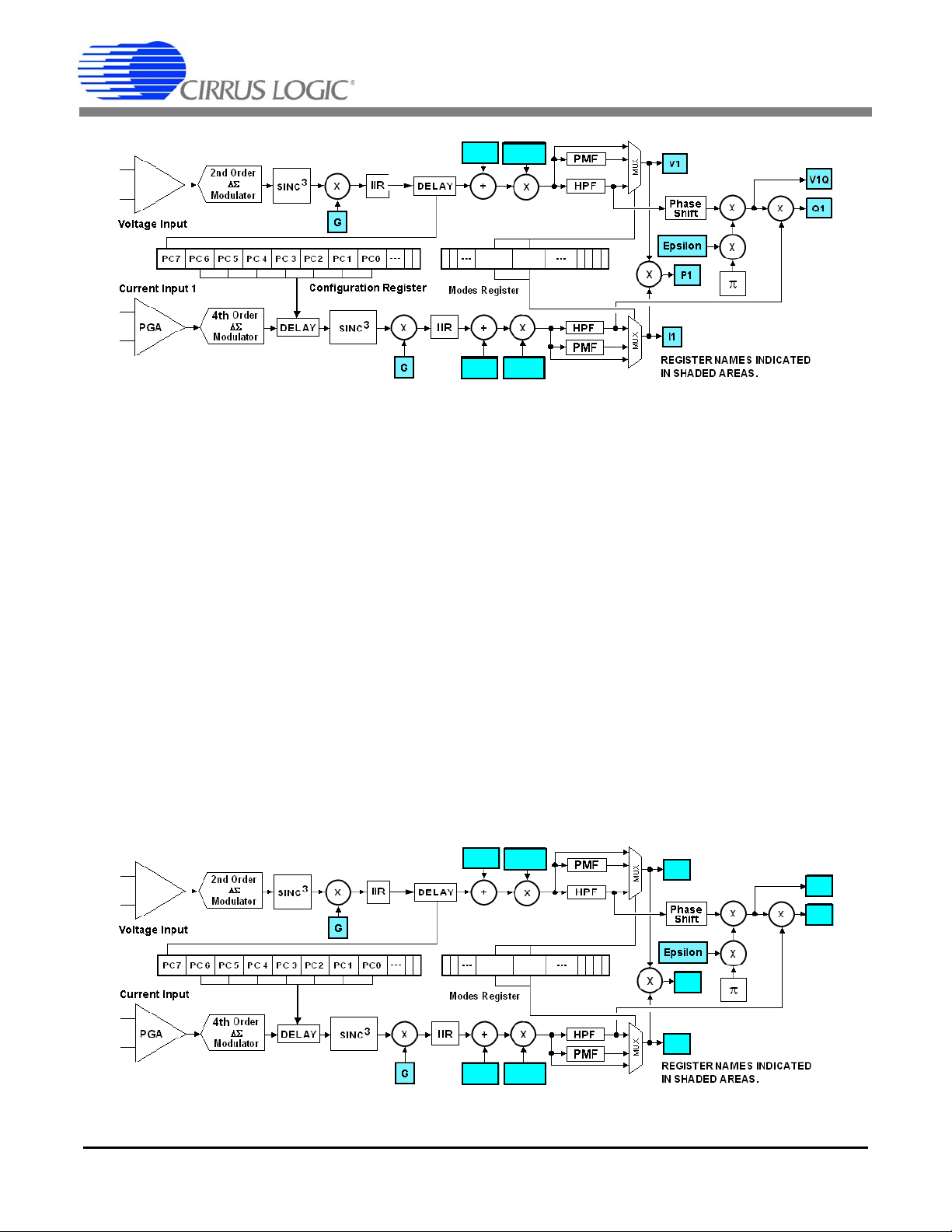

4. SIGNAL PATH DESCRIPTION

Figure 3. Signal Flow for V1, I1, P1, Q1 Measurements

FGA

1

VHPF1

IHPF1

V1

GAIN

V1

OFF

I1

GAIN

I1

OFF

Figure 4. Signal Flow for V2, I2, P2, Q2 Measurements

FGA

2

2

V2Q

Q2

P2

V2

V2

GAIN

V2

OFF

I2

I2

GAIN

I2

OFF

Control Register

VHPF2

IHPF2

The data flow for voltage and current measurement and

the other calculations are shown in Figures 3, 4, and 5.

CS5467

IIR “anti-sinc” filters, used to compensate for the amplitude roll-off of the decimation filters.

4.1 Analog-to-Digital Converters

Voltage1 channel and voltage2/temperature channel

use second-order delta-sigma modulators and the two

current channels use fourth-order delta-sigma modulators to convert the analog inputs to single-bit digital data

streams. The converters sample at a rate of DCLK /8.

This high sampling provides a wide dynamic range and

simplifies anti-alias filter design.

4.2 Decimation Filters

The single-bit modulator output data is widened to 24

bits and down-sampled to DCLK/1024 with low-pass

decimation filters. These decimation filters are third-order Sinc. Their outputs are passed through third-order

4.3 Phase Compensation

Phase compensation changes the ph ase of curren t relative to voltage by changing the sampling time in the

decimation filters. The amount of phase shift is set by

bits PC[7:0] in the Configuration register

channel 1 and bits PC[7:0] in the Control register (

for channel 2.

Phase compensation, PC[7:0] is a signed two’s complement binary value in the rang e of -1.0 to almost +1.0

output word rate (OWR) samples. Fo r a sample rate of

4000 Hz, the delay range is ±250 uS, a phase shift of

±4.5° at 50 Hz and ±5.4° at 60 Hz. The step size would

be 0.0352° at 50 Hz and 0.0422° at 60 Hz at this sample

rate.

(Config) for

Ctrl)

14 DS714F3

Loading...

Loading...