Page 1

CS5460A

Single Phase Bi-Directional Power/Energy IC

Features

Energy Data Linearity: ±0.1% of Reading

over 1000:1 Dynamic Range.

On-Chip Functions: (Real) Energy, I ∗ V,

and V

I

RMS

Smart “Auto-Boot” Mode from Serial

EEPROM Enables Use without MCU.

AC or DC System Calibration

Mechanical Counter/Stepper Motor Driver

Meets Accuracy Spec for IEC 687/1036, JIS

Power Consumption <12 mW

Interface Optimized for Shunt Sensor

V vs. I Phase Compensation

Ground-Referenced Signals with Single

Supply

On-chip 2.5 V Reference (MAX 60 ppm/°C

drift)

Simple Three-Wire Digital Serial Interface

Watch Dog Timer

Power Supply Monitor

Power Supply Configurations

VA+ = +5 V; VA- = 0 V; VD+ = +3.3 V to +5 V

, Energy-to-Pulse Conversion

RMS

Description

The CS5460A is a highly integrated ∆Σ Analog-to-Digital

Converter (ADC) which combines two ∆Σ ADCs, high

speed power calculation functions, and a serial interface

on a single chip. It is designed to accurately measure

and calculate: Real (True) Energy, Instantaneous Power, I

metering applications. The CS5460A interfaces to a

low-cost shunt resistor or transformer to measure current, and resistive divider or potential transformer to

measure voltage. The CS5460A features a bi-directional

serial interface for communication with a micro-controller and a pulse output engine for which the average

pulse frequency is proportional to the real power.

CS5460A has on-chip functionality to facilitate AC or DC

system-level calibration.

The “Auto-Boot” feature allows the CS5460A to function

‘stand-alone’ and to initialize itself on system power-up.

In Auto-Boot Mode, the CS5460A reads the calibration

data and start-up instructions from an external EEPROM. In this mode, the CS5460A can operate without

a microcontroller, in order to lower the total bill-of-materials cost, when the meter is intended for use in

high-volume/residential metering applications.

ORDERING INFORMATION:

RMS

,andV

for single phase 2- or 3-wire power

RMS

CS5460A-BS -40°Cto+85°C 24-pin SSOP

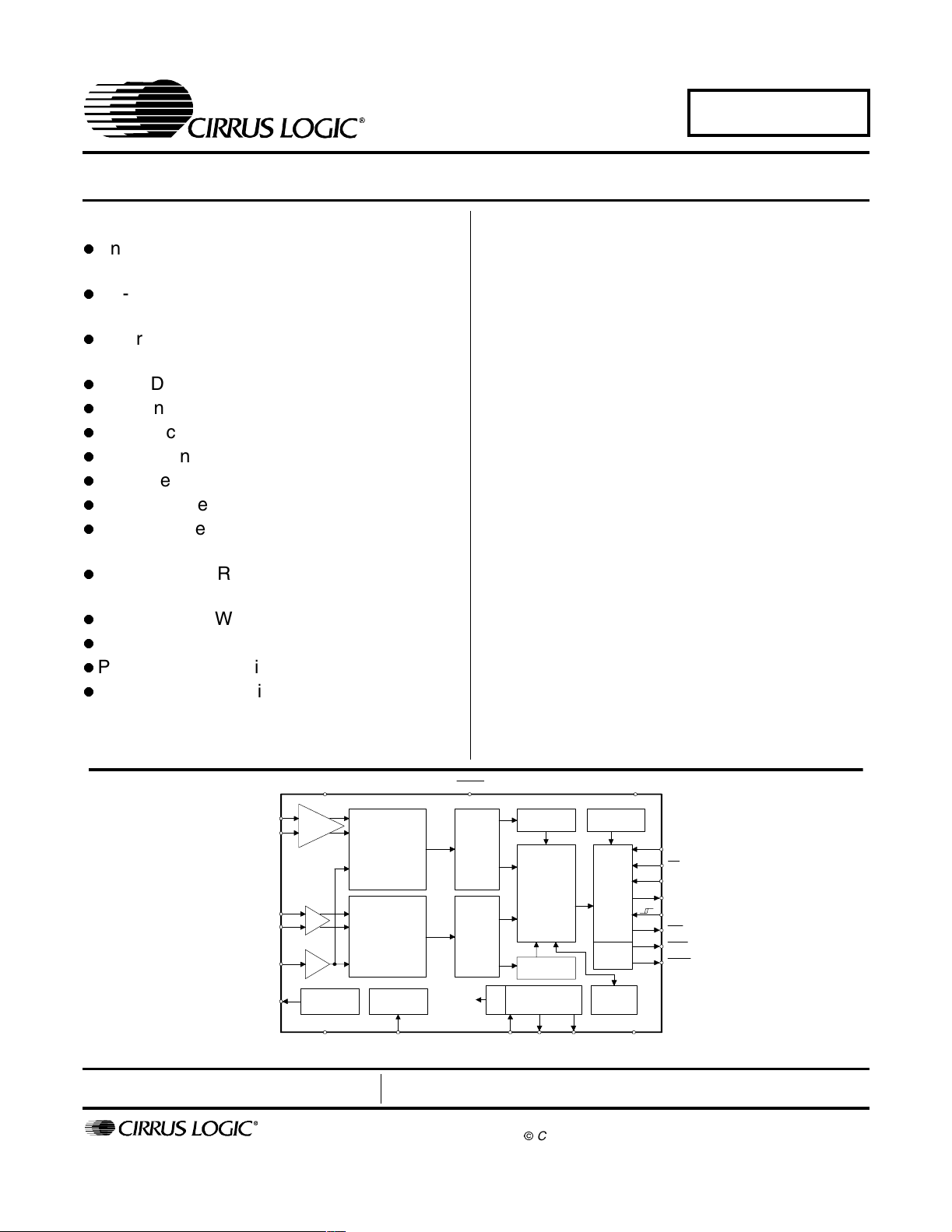

VA+ VD+

IIN+

PGA

x10,x50

IIN-

VIN+

VIN-

VREFIN

VREFOUT

x10

x1

Voltage

Refe rence

VA- XIN XOUT CPUC LK DGND

Preliminary Product Information

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.cirrus.com

RESET

th

4 Order

πΓ

Modulator

nd

2 Order

πΓ

Modulator

Power

Monitor

PFMON

System

Clock

Digital

Filter

Digital

Filter

/K

High Pass

Filter

Power

Calculation

Engine

(Energy

I*V

I,V )

RMS RMS

High Pass

Filter

Clock

Generator

Watch Dog

Timer

Control /

Serial

Interface

Ener gy-to-

Pulse

Converter

Calibration

SRAM

MODE

CS

SDI

SDO

SCLK

INT

EDIR

EOUT

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2001

(All Rights Reserved)

OCT ‘01

DS487PP4

1

Page 2

TABLE OF CONTENTS

1. CHARACTERISTICS AND SPECIFICATIONS ........................................................................ 5

ANALOG CHARACTERISTICS ................................................................................................ 5

VREFOUT REFERENCE OUTPUT VOLTAGE........................................................................ 7

3.3 V DIGITAL CHARACTERISTICS........................................................................................ 8

ABSOLUTE MAXIMUM RATINGS ........................................................................................... 8

SWITCHING CHARACTERISTICS .......................................................................................... 9

2. GENERAL DESCRIPTION ..................................................................................................... 12

2.1 Theory of Operation ......................................................................................................... 12

2.1.1 DS Modulators ................................................................................................... 12

2.1.2 High-Rate Digital Low-Pass Filters ..................................................................... 12

2.1.3 Digital Compensation Filters ............................................................................... 13

2.1.4 Digital High-Pass Filters ...................................................................................... 13

2.1.5 Overall Filter Response ....................................................................................... 13

2.1.6 Gain and DC Offset Adjustment .......................................................................... 13

2.1.7 Real Energy and RMS Computations ................................................................. 13

2.2 Performing Measurements ............................................................................................... 13

2.2.1 CS5460A Linearity Performance ......................................................................... 15

2.2.2 Single Computation Cycle (C=0) ......................................................................... 16

2.2.3 Continuous Computation Cycles (C=1) ............................................................... 16

2.3 Basic Application Circuit Configurations .......................................................................... 17

3. SERIAL PORT OVERVIEW .................................................................................................... 18

3.1 Commands (Write Only) .................................................................................................. 20

3.2 Serial Port Interface .........................................................................................................23

3.3 Serial Read and Write ...................................................................................................... 23

3.3.1 Register Write ..................................................................................................... 23

3.3.2 Register Read ..................................................................................................... 23

3.4 System Initialization .........................................................................................................24

3.5 Serial Port Initialization .................................................................................................... 24

3.6 CS5460A Power States ................................................................................................... 25

4. FUNCTIONAL DESCRIPTION ............................................................................................... 26

4.1 Pulse-Rate Output ...........................................................................................................26

4.2 Pulse Output for Normal, Stepper Motor and Mechanical Counter Format ..................... 28

4.2.1 Normal Format .................................................................................................... 28

4.2.2 Mechanical Counter Format ................................................................................ 29

4.2.3 Stepper Motor Format ......................................................................................... 29

4.3 Auto-Boot Mode Using EEPROM .................................................................................... 30

4.3.1 Auto-Boot Configuration ...................................................................................... 30

4.3.2 Auto-Boot Data for EEPROM ..............................................................................30

CS5460A

Contacting Cirrus Logic Support

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at:

http://www.cirrus.com/corporate/contacts/sales/cfm

Microwire is a trademark of National Semiconductor Corporation.

Preliminary product i nformation describes products which are in production, but for which full characterization data is not yet availabl e. Advance product information describes products which are in development and subject to development changes. Cir rus Logic, Inc. has made best efforts to ensure that the information

contained in this document is accurate and reli able. However, the information is subject to change without notice and is provided “AS IS” without warranty of

any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this i nformation, nor for infri ngements of patents or other rights

of third parties. This document is the property o f Ci rrus Logic, Inc. and implies no license under patents, copyrights, t rademarks, or trade secr ets. No part of

this publication may be copied, reproduced, stored in a retrieval system, or transmitted, i n any form or by any means (electronic, mechanical, photographic, or

otherwise) without the prior written consent of Cirrus Logic, Inc. Items from any Cirrus Logic website or disk may be printed for use by the user. However, no

part of the print out or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical,

photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Furthermore, no part of this publication may be used as a basis for manufacture

or sale of any items without the pri or written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendor s and suppliers appearing

in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. tr ademarks and service marks can be found at http://www.cirrus.com.

2 DS487PP4

Page 3

CS5460A

4.3.3 Which EEPROMs Can Be Used? ....................................................................... 31

4.4 Interrupt and Watchdog Timer ......................................................................................... 33

4.4.1 Interrupt ............................................................................................................... 33

4.4.1.1 Clearing the Status Register ............................................................... 33

4.4.1.2 Typical use of the INT pin ................................................................... 33

4.4.1.3 INT Active State .................................................................................. 34

4.4.1.4 Exceptions .......................................................................................... 34

4.4.2 Watch Dog Timer ................................................................................................ 34

4.5 Oscillator Characteristics ................................................................................................. 34

4.6 Analog Inputs ................................................................................................................... 35

4.7 Voltage Reference ........................................................................................................... 35

4.8 Calibration ....................................................................................................................... 36

4.8.1 Overview of Calibration Process ......................................................................... 36

4.8.2 The Calibration Registers ................................................................................... 37

4.8.3 Calibration Sequence .......................................................................................... 37

4.8.4 Calibration Signal Input Level ............................................................................. 38

4.8.5 Calibration Signal Frequency .............................................................................. 38

4.8.6 Input Configurations for Calibrations ................................................................... 38

4.8.7 Description of Calibration Algorithms .................................................................. 39

4.8.7.1 AC Offset Calibration Sequence ......................................................... 39

4.8.7.2 DC Offset Calibration Sequence ......................................................... 40

4.8.7.3 AC Gain Calibration Sequence ........................................................... 40

4.8.7.4 DC Gain Calibration Sequence .......................................................... 40

4.8.8 Duration of Calibration Sequence ....................................................................... 41

4.8.9 Is Calibration Required? ............................................................................. 41

4.8.10 Order of Calibration Sequences ........................................................................ 42

4.8.11 Calibration Tips ................................................................................................. 43

4.9 Phase Compensation ...................................................................................................... 43

4.10 Time-Base Calibration Register ..................................................................................... 44

4.11 Power Offset Register ................................................................................................... 44

4.12 Input Protection - Current Limit ...................................................................................... 45

4.13 Input Filtering ................................................................................................................. 46

4.14 Protection Against High-Voltage and/or High-Current Surges ...................................... 50

4.15 Improving RFI Immunity ................................................................................................ 50

4.16 PCB Layout ...................................................................................................................52

5. REGISTER DESCRIPTION ................................................................................................... 53

5.1 Configuration Register...................................................................................................... 53

5.2 Current Channel DC Offset Register and Voltage Channel DC Offset Register .............. 55

5.3 Current Channel Gain Register and Voltage Channel Gain Register............................... 55

5.4 Cycle Count Register........................................................................................................ 55

5.5 Pulse-Rate Register ......................................................................................................... 56

5.6 I,V,P,E Signed Output Register Results........................................................................... 56

5.7 IRMS, VRMS Unsigned Output Register Results............................................................. 56

5.8 Timebase Calibration Register ......................................................................................... 56

5.9 Power Offset Register ...................................................................................................... 57

5.10 Current Channel AC Offset Register and Voltage Channel AC Offset Register............. 57

5.11 Status Register and Mask Register ................................................................................ 57

5.12 Control Register.............................................................................................................. 59

6. PIN DESCRIPTION ................................................................................................................. 60

7. PACKAGE DIMENSIONS ...................................................................................................... 62

DS487PP4 3

Page 4

LIST OF FIGURES

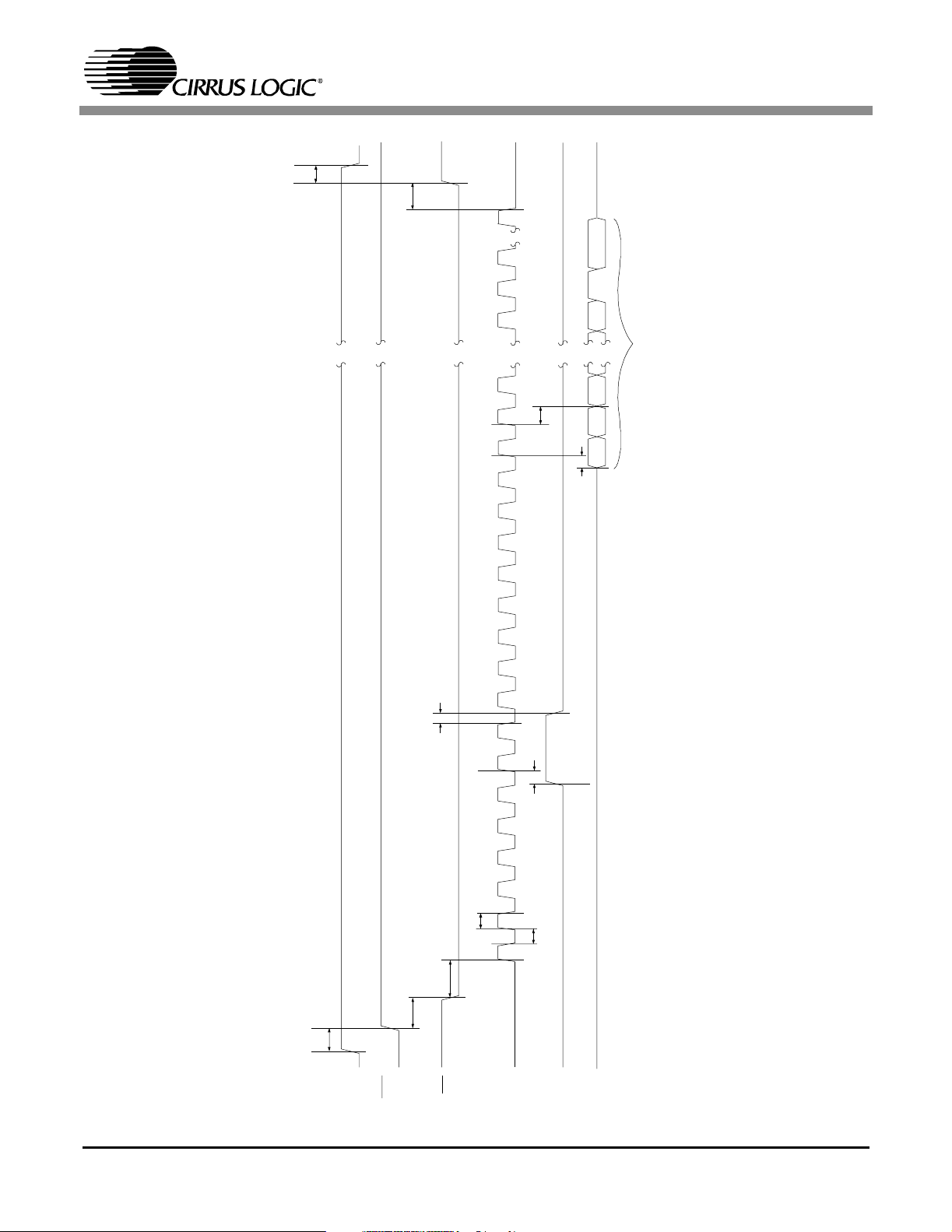

Figure 1. CS5460A Read and Write Timing Diagrams.................................................................. 10

Figure 2. CS5460A Auto-Boot Sequence Timing.......................................................................... 11

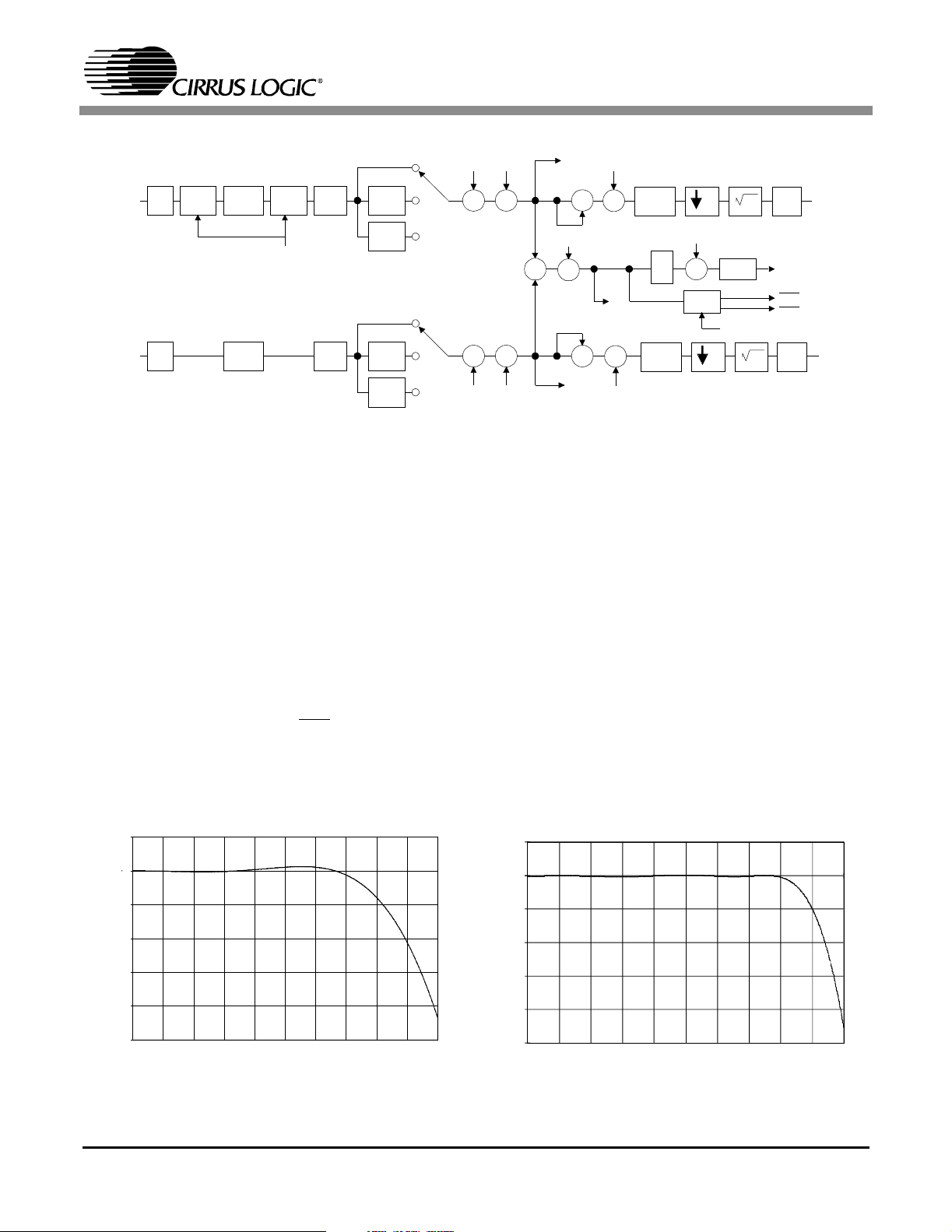

Figure 3. Data Flow....................................................................................................................... 14

Figure 4. Voltage Input Filter Characteristics ................................................................................14

Figure 5. Current Input Filter Characteristics ................................................................................ 14

Figure 6. Typical Connection Diagram (One-Phase 2-Wire, Direct Connect to Power Line) ........ 18

Figure 7. Typical Connection Diagram (One-Phase 2-Wire, Isolated from Power Line) ............... 18

Figure 8. Typical Connection Diagram (One-Phase 3-Wire).........................................................19

Figure 9. Typical Connection Diagram (One-Phase 3-Wire - No Neutral Available)..................... 19

Figure 10. Time-plot representation of pulse output for a typical burst of pulses (Normal Format)28

Figure 11. Mechanical Counter Format on EOUT and EDIR ........................................................ 29

Figure 12. Stepper Motor Format on EOUT and EDIR ................................................................. 29

Figure 13. Typical Interface of EEPROM to CS5460A.................................................................. 30

Figure 14. Timing Diagram for Auto-Boot Sequence .................................................................... 31

Figure 15. CS5460A Auto-Boot Configuration: Automatic Restart After Power Failure ................ 33

Figure 16. Oscillator Connection ...................................................................................................35

Figure 17. VREFOUT Voltage vs. Temperature characteristic for a typical CS5460A sample. .... 35

Figure 18. System Calibration of Gain. ......................................................................................... 39

Figure 19. System Calibration of Offset. ....................................................................................... 39

Figure 20. Calibration Data Flow................................................................................................... 40

Figure 21. Example of AC Gain Calibration .................................................................................. 41

Figure 22. Another Example of AC Gain Calibration..................................................................... 41

Figure 23. Example of DC Gain Calibration ..................................................................................41

Figure 24. Input Protection for Single-Ended Input Configurations ............................................... 51

Figure 25. CS5460A Register Diagram ......................................................................................... 53

CS5460A

LIST OF TABLES

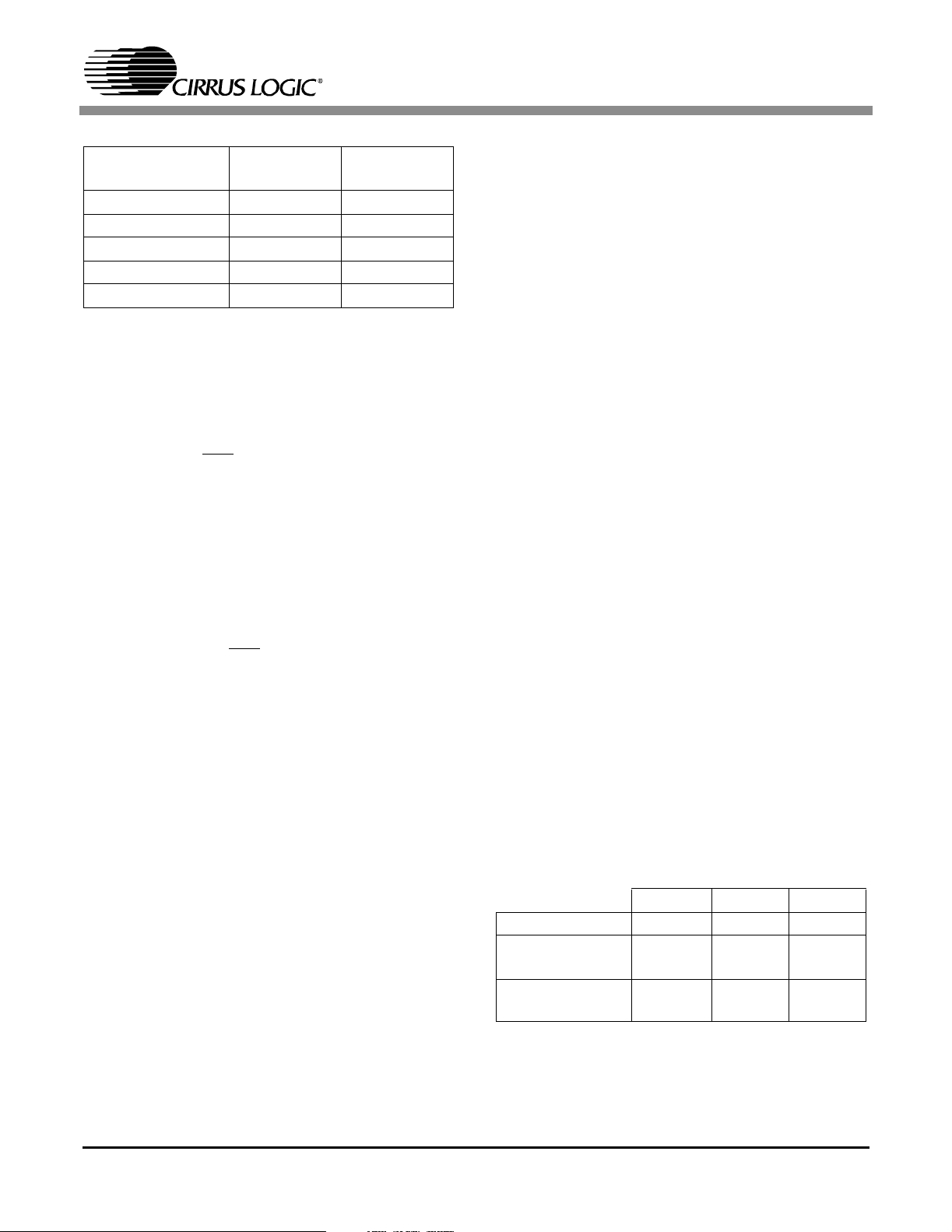

Table 1. Differential Input Voltage vs. Output Code ............................................................................ 15

Table 2. Available range of ±0.1% output linearity, with default settings in the gain/offset registers... 15

Table 3. Default Register Values upon Reset Event ........................................................................... 24

4 DS487PP4

Page 5

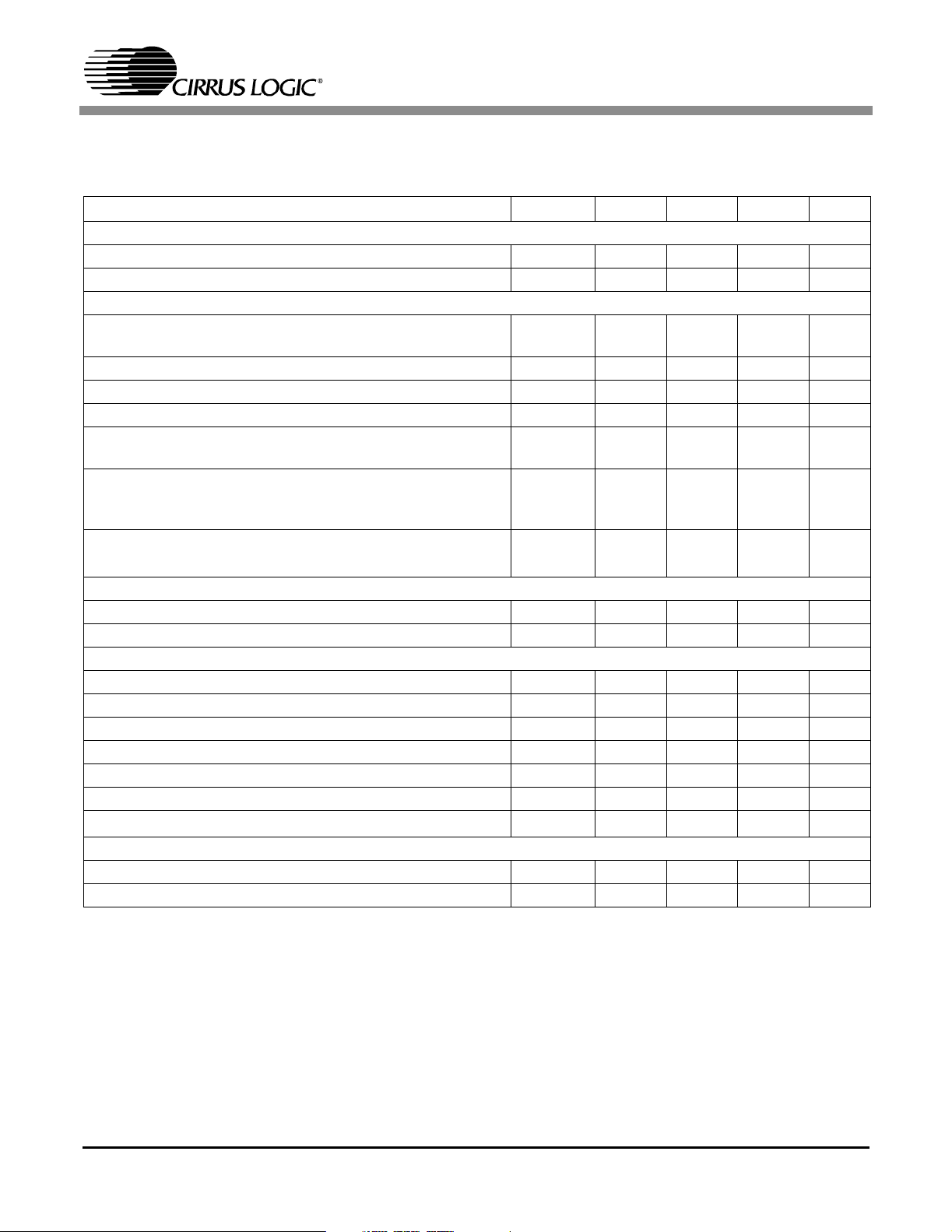

1. CHARACTERISTICS AND SPECIFICATIONS

CS5460A

ANALOG CHARACTERISTICS (T

= -40° C to +85° C; VA+ = VD+ = +5 V ±10%; VREFIN = +2.5 V;

A

VA- = AGND = 0 V; MCLK = 4.096 MHz, K = 1; N = 4000 ==> OWR = 4000 Sps.)(See Notes 1, 2, 3, 4, and 5.)

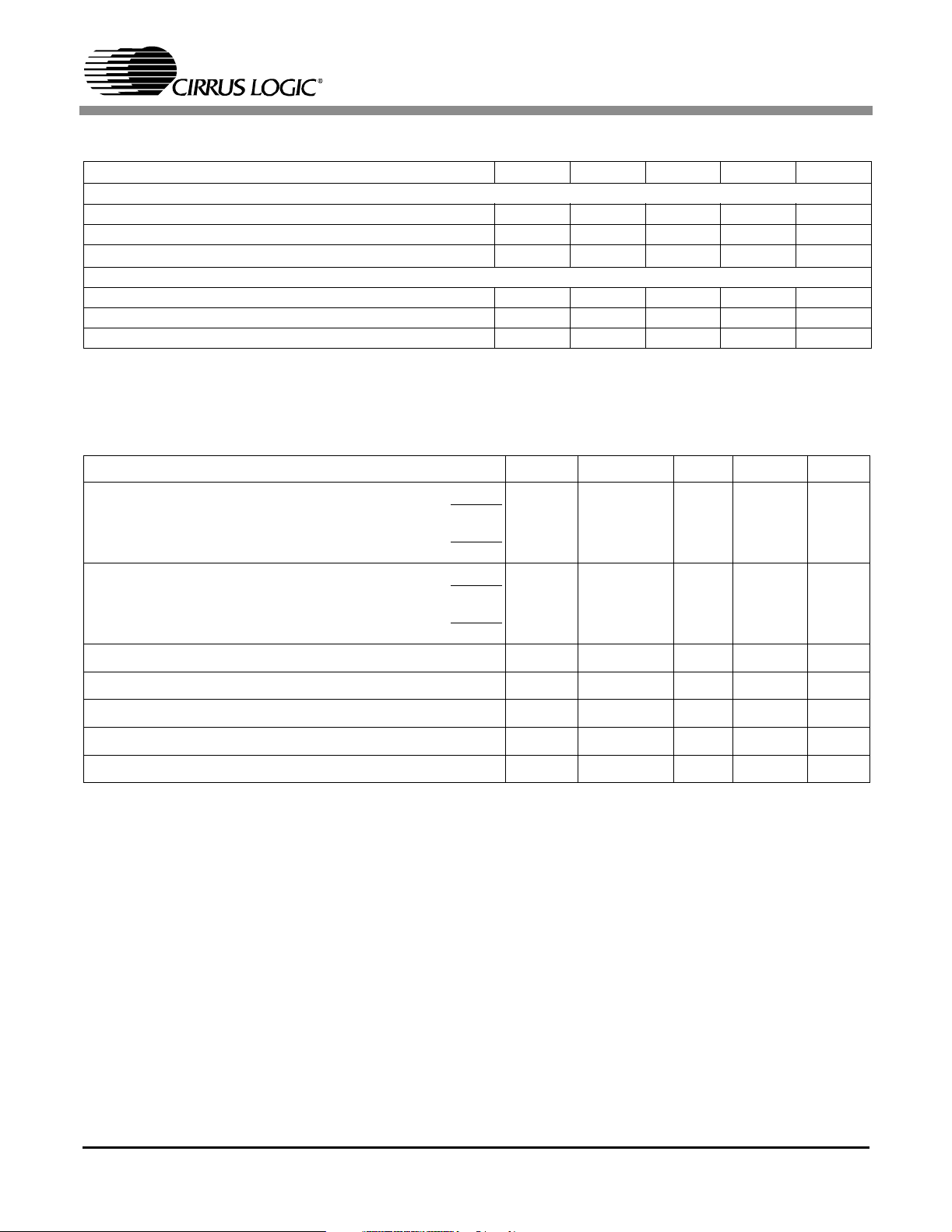

Parameter Symbol Min Typ Max Unit

Accuracy (Both Channels)

Common Mode Rejection (DC, 50, 60 Hz) CMRR 80 - - dB

Offset Drift (Without the High Pass Filter) - 5 - nV/°C

Analog Inputs (Current Channel)

Maximum Differential Input Voltage Range (Gain = 10)

{(V

IIN+)-(VIIN-)} (Gain = 50)

Total Harmonic Distortion THD

IN -

I

-

I 74 - - dB

±250

±50

-

-

mV

mV

Common Mode + Signal on IIN+ or IIN- (Gain = 10 or 50) -0.25 - VA+ V

Crosstalk with Voltage Channel at Full Scale (50, 60 Hz) - - -115 dB

Input Capacitance (Gain = 10)

(Gain = 50)

in -

C

-

25

25

-

-

pF

pF

Effective Input Impedance (Note 6)

(Gain = 10)

(Gain = 50)

Noise(ReferredtoInput) (Gain=10)

(Gain = 50)

Z

ZinI

inI

-

-

-

-

30

30

-

-

-

-

20

4

µV

µV

kΩ

kΩ

rms

rms

Accuracy (Current Channel)

Bipolar Offset Error (Note 1) VOS

Full-Scale Error (Note 1) FSE

I -±0.001-%F.S.

I -±0.001-%F.S.

Analog Inputs (Voltage Channel)

Maximum Differential Input Voltage Range {(V

Total Harmonic Distortion THD

VIN+)-(VVIN-)} VIN - ±250 - mV

V 62 - - dB

Common Mode + Signal on VIN+ or VIN- -0.25 - VA+ V

Crosstalk with Current Channel at Full Scale (50, 60 Hz) - - -70 dB

Input Capacitance C

Effective Input Impedance (Note 6) Z

Noise(ReferredtoInput) - - 250 µV

inV -0.2-pF

inV -5-MΩ

rms

Accuracy (Voltage Channel)

Bipolar Offset Error (Note 1) VOS

Full-Scale Error (Note 1) FSE

V - ±0.01 - %F.S.

V - ±0.01 - %F.S.

Notes: 1. Bipolar Offset Errors and Full-Scale Gain Errors for the current and voltage channels refer to the

respective Irms Register and Vrms Register output, when the device is operating in ‘continuous

computation cycles’ data acquisition mode, after offset/gain system calibration sequences have been

executed. These specs do not apply to the error of the Instantaneous Current/Voltage Register output.

2. Specifications guaranteed by design, characterization, and/or test.

3. Analog signals are relative to VA- and digital signals to DGND unless otherwise noted.

4. In requiring VA+=VD+=5V ±10%, note that it is allowable for VA+, VD+ to differ by as much as ±200mV,

as long as VA+ > VD+.

5. Note that “Sps” is an abbreviation for units of “samples per second”.

6. Effective Input Impedance (Z

Z

in = 1/(IC*DCLK/4). Note that DCLK = MCLK / K.

in) is determined by clock frequency (DCLK) and Input Capacitance (IC).

DS487PP4 5

Page 6

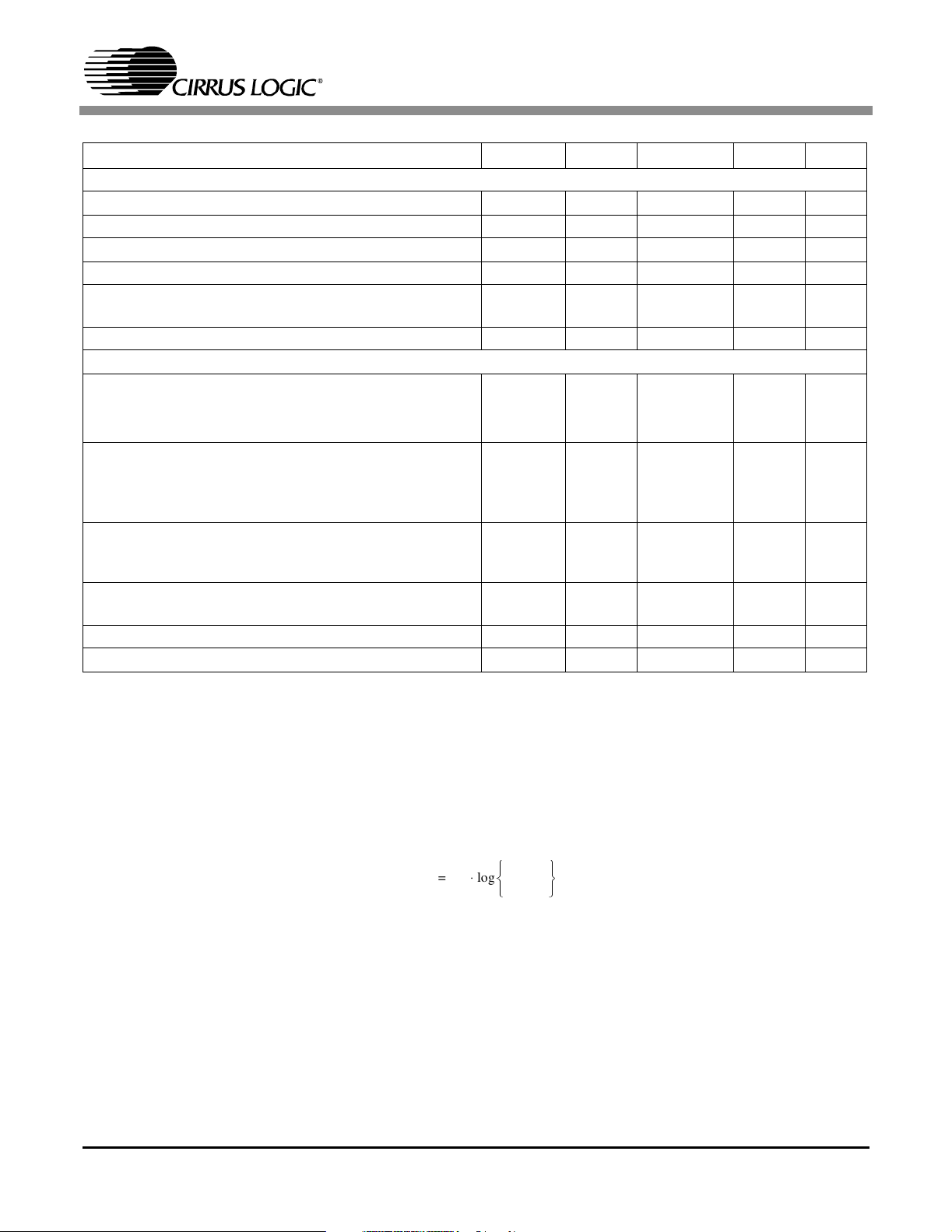

CS5460A

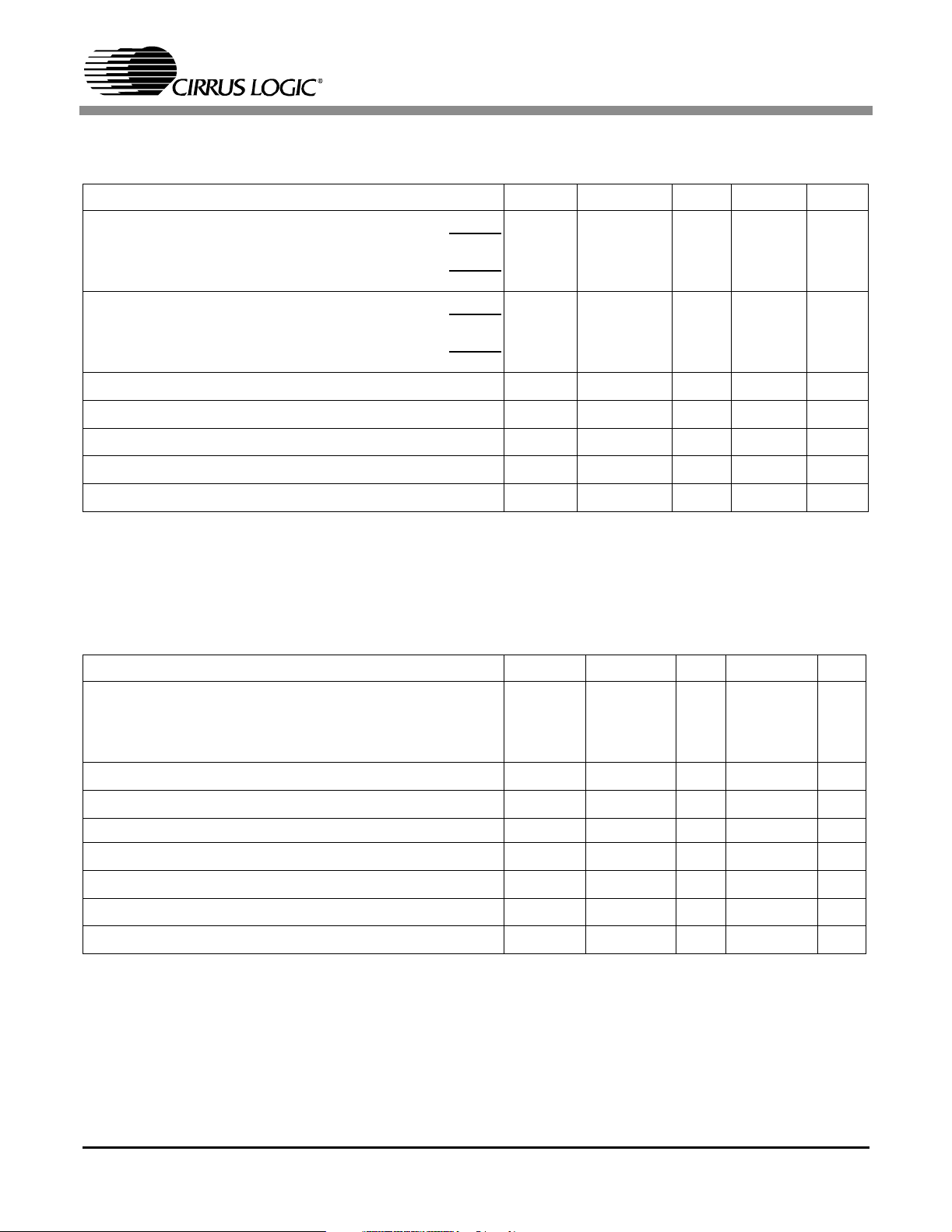

ANALOG CHARACTERISTICS (Continued)

Parameter Symbol Min Typ Max Unit

Dynamic Characteristics

Phase Compensation Range (Voltage Channel, 60 Hz) -2.4 - +2.5 °

High Rate Filter Output Word Rate (Both Channels) OWR - DCLK/1024 - Sps

Input Sample Rate DCLK = MCLK/K - DCLK/8 - Sps

Full Scale DC Calibration Range (Note 7) FSCR 25 - 100 %F.S.

Channel-to-Channel Time-Shift Error

(when PC[6:0] bits are set to “0000000”)

High Pass Filter Pole Frequency -3 dB - 0.5 - Hz

Power Supplies

Power Supply Currents (Active State) I

ID+(VD+ = 5 V)

I

(VD+ = 3.3 V)

D+

Power Consumption Active State (VD+ = 5 V)

(Note 8) Active State (VD+ = 3.3 V)

Stand-By State

Sleep State

A+

PSCA

PSCD

PSCD

PC -

-

-

-

-

-

-

Power Supply Rejection Ratio (50, 60 Hz)

for Current Channel (Gain = 10)

(Note 9) (Gain = 50)

PSRR

PSRR

56

70

Power Supply Rejection Ratio (50, 60 Hz)

for Voltage Channel (Note 9) PSRR 50 - - dB

PFMON Power-Fail Detect Threshold (Note 10) PMLO 2.3 2.45 - V

PFMON “Power-Restored” Detect Threshold (Note 11) PMHI - 2.55 2.7 V

1.0 µs

1.3

2.9

1.7

21

11.6

6.75

10

-

-

25

-

-

-

mA

mA

mA

mW

-

-

-

mW

mW

µW

-

-

dB

dB

Notes: 7. The minimum FSCR is limited by the maximum allowed gain register value.

8. All outputs unloaded. All inputs CMOS level.

9. Definition for PSRR: VREFIN tied to VREFOUT, VA+ = VD+ = 5V, a 150mV zero-to-peak sinewave

(frequency = 60Hz) is imposed onto the +5V supply voltage at VA+ and VD+ pins. The “+” and “-” input

pins of both input channels are shorted to VA-. Then the CS5460A is commanded to ’continuous

computation cycles’ data acquisition mode, and digital output data is collected for the channel under

test. The zero-peak value of the digital sinusoidal output signal is determined, and this value is

converted into the zero-peak value of the sinusoidal voltage that would need to be applied at the

channel’s inputs, in order to cause the same digital sinusoidal output. This voltage is then defined as

Veq. PSRR is then (in dB):

0.150V

PSRR 20

--------- ---------

log⋅=

V

eq

10. When voltage level on PFMON is sagging, and LSD bit is at 0, the voltage at which LSD bit is set to 1.

11. Assuming that the LSD bit has been set to 1 (because PFMON voltage fell below PMLO), then if/when

the PFMON voltage starts to rise again, PMHI is the voltage level (on PFMON pin) at which the LSD bit

can be permanently reset back to 0 (without instantaneously changing back to 1). Attempts (by the

user) to reset the LSD bit before this condition is true will not be successful. This condition indicates

that power has been restored. Typically, for a given sample, the PMHI voltage will be ~100mV above

the PMLO voltage.

6 DS487PP4

Page 7

CS5460A

VREFOUT REFERENCE OUTPUT VOLTAGE

Parameter Symbol Min Typ Max Unit

Reference Output

Output Voltage REFOUT +2.4 - +2.6 V

VREFOUT Temperature Coefficient (Note 12) T

Load Regulation (Output Current 1 µA Source or Sink) ∆V

Reference Input

Input Voltage Range VREFIN +2.4 +2.5 +2.6 V

Input Capacitance - 4 - pF

Input CVF Current - 25 - nA

Notes: 12. See Section 4.7 for definition of VREFOUT Temperature Coefficient spec.

VREFO UT - 25 - ppm/°C

R

-610mV

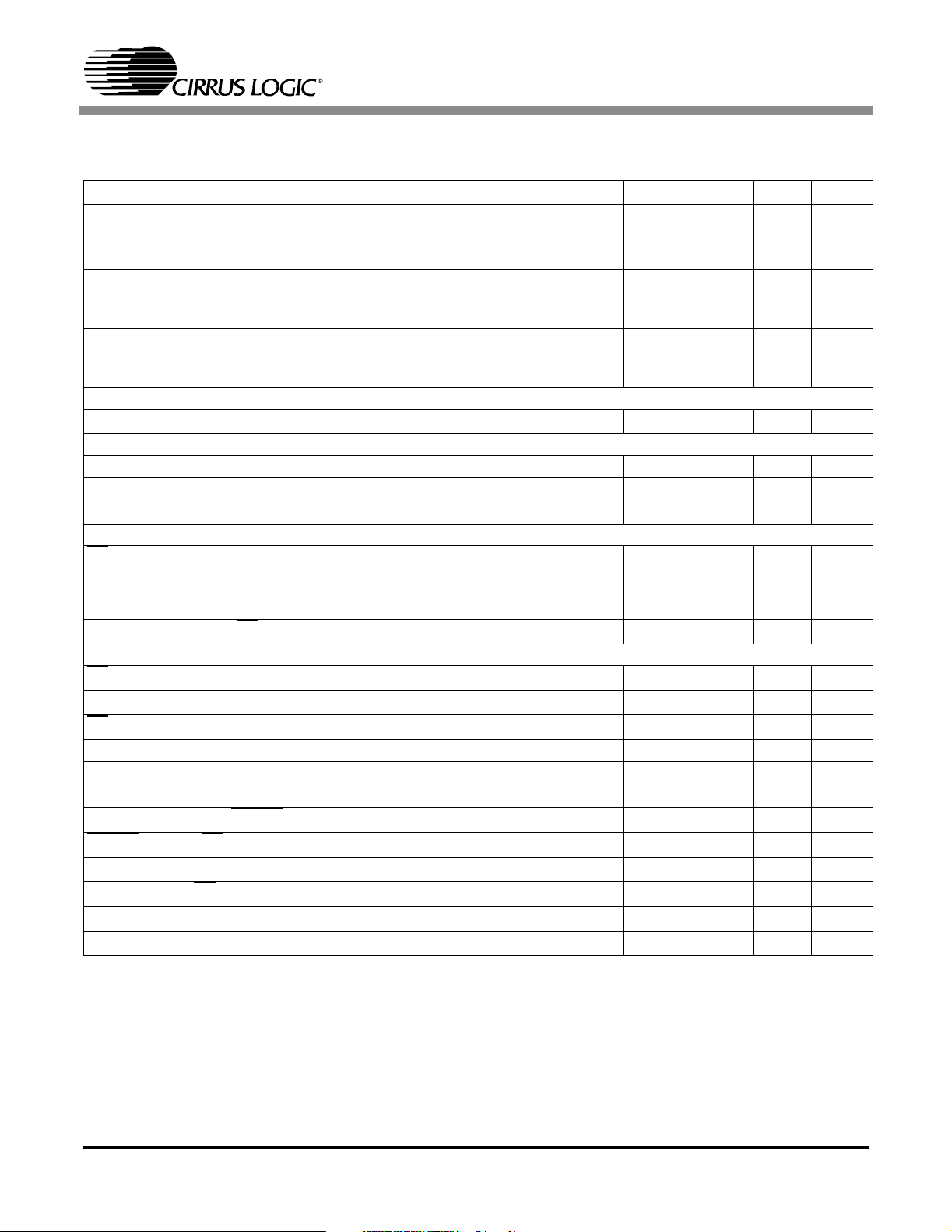

5V DIGITAL CHARACTERISTICS (T

= -40° C to +85° C; VA+ = VD+ = 5 V ±10% VA-, DGND =

A

0 V) (See Notes 3, 4, and 13)

Parameter Symbol Min Typ Max Unit

High-Level Input Voltage

All Pins Except XIN, SCLK and RESET

XIN

SCLK and RESET

Low-Level Input Voltage

All Pins Except XIN, SCLK, and RESET

XIN

SCLK and RESET

High-Level Output Voltage (except XOUT) I

Low-Level Output Voltage (except XOUT) I

=+5mA V

out

=-5mA V

out

Input Leakage Current (Note 14) I

3-State Leakage Current I

Digital Output Pin Capacitance C

13. Note that the 5V characteristics are guaranteed by characterization. Only the more rigorous 3.3 V digital

characteristics are actually verified during production test.

14. Applies to all INPUT pins except XIN pin (leakage current < 50 µA) and MODE pin (leakage current <

25 µA).

V

V

OH

OL

in

OZ

out

IH

IL

0.6 VD+

(VD+) - 0.5

0.8 VD+

-

-

-

-

-

-

-

-

-

(VD+) - 1.0 - - V

--0.4V

-±1±10µA

--±10µA

-5-pF

-

-

-

0.8

1.5

0.2 VD+

V

V

V

V

V

V

DS487PP4 7

Page 8

CS5460A

3.3 V DIGITAL CHARACTERISTICS (T

= -40° C to +85° C; VA+ = 5 V ±10%, VD+ = 3.3 V ±10%;

A

VA-, DGND = 0 V) (See Notes 3, 4, and 13)

Parameter Symbol Min Typ Max Unit

High-Level Input Voltage

All Pins Except XIN, XOUT, SCLK, and RESET

XIN

SCLK and RESET

Low-Level Input Voltage

AllPinsExceptXIN,XOUT,SCLK,andRESET

XIN

SCLK and RESET

High-Level Output Voltage (except XIN, XOUT) I

Low-Level Output Voltage (except XIN, XOUT) I

=+5mA V

out

=-5mA V

out

Input Leakage Current (Note 14) I

3-State Leakage Current I

Digital Output Pin Capacitance C

Notes: 15. All measurements performed under static conditions.

16. If VD+ = 3V and if XIN input is generated using crystal, then XIN frequency must remain between 2.5

MHz - 5.0 MHz. If using oscillator, full XIN frequency range is available, see Switching Characteristics.

V

V

OH

OL

in

OZ

out

IH

IL

0.6 VD+

(VD+) - 0.5

0.8 VD+

-

-

-

-

-

-

-

-

-

(VD+) - 1.0 - - V

--0.4V

-±1±10µA

--±10µA

-5-pF

-

-

-

0.48

0.3

0.2 VD+

V

V

V

V

V

V

ABSOLUTE MAXIMUM RATINGS (DGND = 0 V; See Note 17) WARNING: Operation at or beyond

these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

Parameter Symbol Min Typ Max Unit

DC Power Supplies (Notes 18 and 19)

Positive Digital

Positive Analog

Negative Analog

Input Current, Any Pin Except Supplies(Note 20, 21, and 22) I

Output Current I

Power Dissipation (Note 23) P

Analog Input Voltage All Analog Pins V

Digital Input Voltage All Digital Pins V

Ambient Operating Temperature T

Storage Temperature T

Notes: 17. All voltages with respect to ground.

18. VA+ and VA- must satisfy {(VA+) - (VA-)} ≤ +6.0 V.

19. VD+ and VA- must satisfy {(VD+) - (VA-)} ≤ +6.0 V.

20. Applies to all pins including continuous over-voltage conditions at the analog input (AIN) pins.

21. Transient current of up to 100 mA will not cause SCR latch-up.

22. Maximum DC input current for a power supply pin is ±50 mA.

23. Total power dissipation, including all input currents and output currents.

VD+

VA+

VA-

IN

OUT

D --500mW

INA

IND

A

stg

-0.3

-0.3

+0.3

-

-

-

+6.0

+6.0

-6.0

--±10mA

--±25mA

(VA-) - 0.3 - (VA+) + 0.3 V

DGND - 0.3 - (VD+) + 0.3 V

-40 - 85 °C

-65 - 150 °C

V

V

V

8 DS487PP4

Page 9

CS5460A

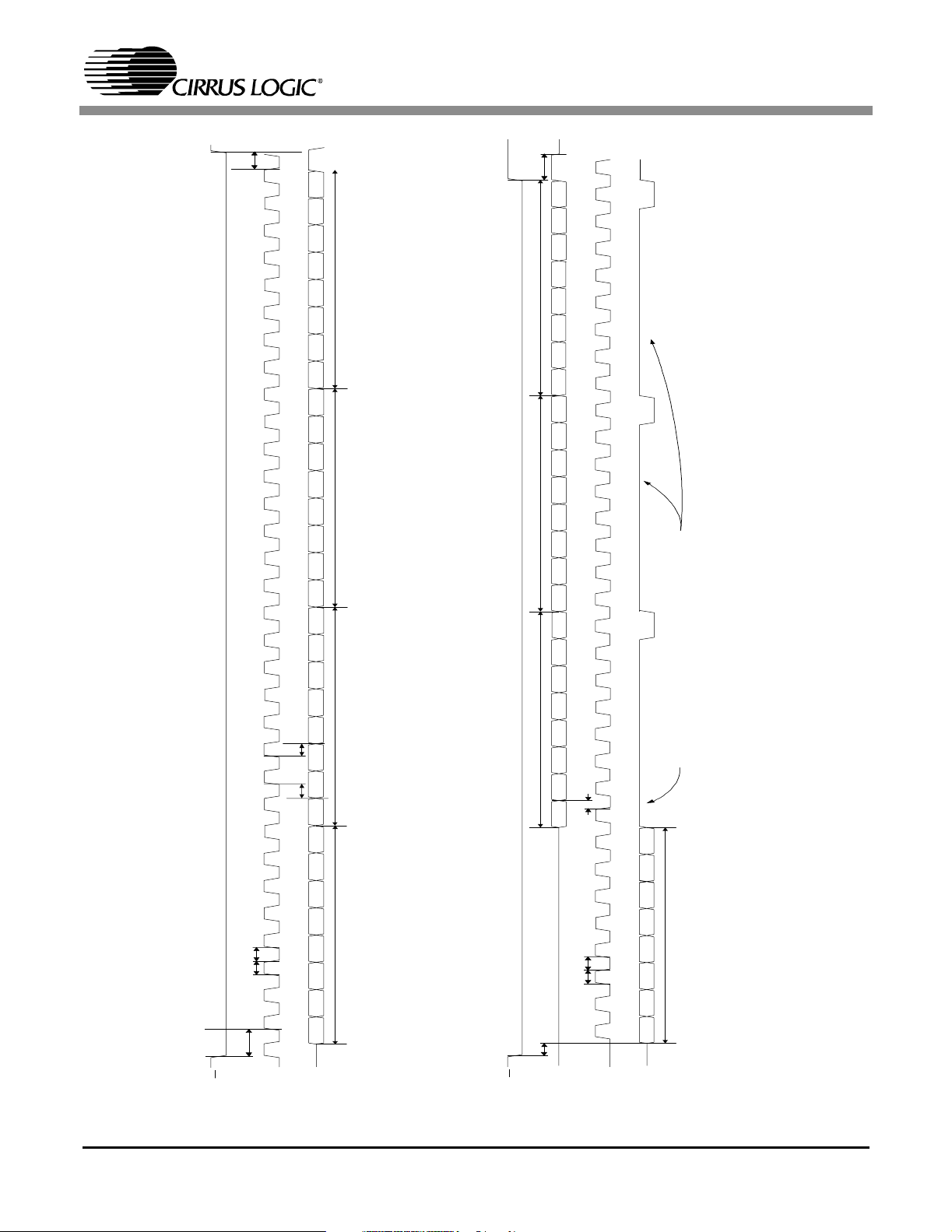

SWITCHING CHARACTERISTICS (T

= -40° C to +85 °C; VA+ = 5.0 V ±10%; VD+ = 3.0 V ±10%

A

or 5.0 V ±10%; VA- = 0.0 V; Logic Levels: Logic 0 = 0.0 V, Logic 1 = VD+; CL = 50 pF))

Parameter Symbol Min Typ Max Unit

Master Clock FrequencyCrystal/Internal Gate Oscillator (Note 24) MCLK 2.5 4.096 20 MHz

Master Clock Duty Cycle 40 - 60 %

CPUCLK Duty Cycle (Note 25) 40 60 %

Rise Times Any Digital Input Except SCLK (Note 26)

SCLK

Any Digital Output

Fall Times Any Digital Input Except SCLK (Note 26)

SCLK

Any Digital Output

t

t

rise

fall

-

-

-

-

-

-

50

50

-

-

-

-

1.0

100

-

1.0

100

-

µs

µs

ns

µs

µs

ns

Start-up

Oscillator Start-Up Time XTAL = 4.096 MHz (Note 27) t

ost

-60-ms

Serial Port Timing

Serial Clock Frequency SCLK - - 2 MHz

Serial Clock Pulse Width High

Pulse Width Low

t

1

t

2

200

200

-

-

-

-

ns

ns

SDI Timing

CS

Falling to SCLK Rising t

Data Set-up Time Prior to SCLK Rising t

Data Hold Time After SCLK Rising t

SCLK Falling Prior to CS

Disable t

3

4

5

6

50 - - ns

50 - - ns

100 - - ns

100 - - ns

SDO Timing

Falling to SDO Driving t

CS

SCLK Falling to New Data Bit t

Rising to SDO Hi-Z t

CS

7

8

9

-2050ns

-2050ns

-2050ns

Auto-Boot Timing

Serial Clock Pulse Width High

Pulse Width Low

MODEsetuptimetoRESET

RESET

CS

SCLK falling to CS

CS

rising to CS falling t

falling to SCLK rising t

rising t

rising to driving MODE low (to end auto-boot sequence). t

Rising t

SDO guaranteed setup time to SCLK rising t

t

10

t

11

12

13

14

15

16

17

50 ns

48 MCLK

100 8 MCLK

50 ns

100 ns

8

8

16 MCLK

MCLK

MCLK

Notes: 24. Device parameters are specified with a 4.096 MHz clock, however, clocks between 3 MHz to 20 MHz

can be used. However, for input frequencies over 5 MHz, an external oscillator must be used, or if a

crystal over 5 MHz is to be used, then VD+ must be set to 5V (not 3V).

25. If external MCLK is used, then duty cycle must be between 45% and 55% to maintain this specification.

26. Specified using 10% and 90% points on wave-form of interest. Output loaded with 50 pF.

27. Oscillator start-up time varies with crystal parameters. This specification does not apply when using an

external clock source.

DS487PP4 9

Page 10

CS5460A

6

t

LSB

9

t

LSB

Low Byte

MSB MSB - 1

LSB

MSB MSB - 1

LSB

High Byte Mid Byte Low Byte

t

45

t

MSB MSB - 1

LSB

MSB MSB - 1

LSB

.

I

O

D

D

S

S

n

m

o

o

r

d

f

n

a

a

MSB MSB - 1

LSB

SDI Write Timing (Not to Scale)

High Byte Mid Byte

8

t

MSB MSB -1

LSB

t

a

m

d

m

f

o

o

c

e

t

"

y

0

b

C

h

N

c

Y

a

S

e

"

g

e

n

b

i

o

d

r

t

a

e

s

r

t

s

n

u

e

h

M

w

SDO Read Timing (Not to Scale)

2

t

1

t

3

t

CS

SCLK

Command Time 8 S CLKs

MSB MSB - 1

SDI

CS

2

t

1

t

7

t

SDO

SCLK

CommandTime8SCLKs

MSB MSB - 1

SDI

Figure 1. CS5460A Read and Write Timing Diagrams

10 DS487PP4

Page 11

CS5460A

16

t

15

t

LAST 8 BITS

BIT

STOP

5

t

4

t

8

t

17

t

Data from EEPROM

Figure 2. CS5460A Auto-Boot Sequence Timing

10

t

14

t

13

t

12

t

RES

(Input)

(Input)

MODE

CS

(Output)

1

1

t

SDI

SCLK

SDO

(Output)

(Input)

(Output)

DS487PP4 11

Page 12

CS5460A

2. GENERAL DESCRIPTION

The CS5460A is a CMOS monolithic power measurement device with a real power/energy computation engine. The CS5460A combines two

programmable gain amplifiers, two ∆Σ modulators,

two high rate filters, system calibration, and

rms/power calculation functions to provide instantaneous voltage/current/power data samples as well

as periodic computation results for real (billable)

energy, V

lower cost metering applications, the CS5460A can

also generate pulse-train signals on certain output

pins, for which the number of pulses emitted on the

pins is proportional to the quantity of real (billable)

energy registered by the device.

The CS5460A is optimized for power measurement

applications and is designed to interface to a shunt

or current transformer to measure current, and a resistive divider or potential transformer to measure

voltage. To accommodate various input voltage

levels, the current channel includes a programmable gain amplifier (PGA) which provides either

±250 mV or ±50 mV as the full-scale input level.

The voltage channel’s PGA provides a single input

voltage range of

ply across VA+/VA- the pins, the differential input

pins of both input channels accommodate common

mode + signal levels between -0.25 V and +5V.

Note that the designer can realize true differential

bipolar input configurations on either/both channels, in which the common-mode level of the input

signal is at AGND potential (if desired).

The CS5460A includes two high-rate digital filters

(one per channel), which decimate/integrate the output from the 2 ∆Σ modulators. The filters yield

24-bit output data at a (MCLK/K)/1024 output word

rate (OWR). The OWR can be thought of as the effective sample frequency of the voltage channel and

the current channel.

To facilitate communication to a microcontroller,

the CS5460A includes a simple three-wire serial

RMS

, and I

±250 mV. With single +5 V sup-

. In order to accommodate

RMS

interface which is SPI™ and Microwire™ compatible. The serial port has a Schmitt Trigger input on

its SCLK (serial clock) and RESET

pins to allow

for slow rise time signals.

2.1 Theory of Operation

A computational flow diagram for the two data

paths is shown in Fig. 3. The reader should refer to

this diagram while reading the following data processing description, which is covered

block-by-block.

2.1.1 ∆Σ Modulators

The analog waveforms at the voltage/current channel inputs are subject to the gains of the input PGAs

(not shown in Figure 3). These waveforms are then

sampled by the delta-sigma modulators at a rate of

(MCLK/K)/8 Sps.

2.1.2 High-Rate Digital Low-Pass Filters

The data is then low-pass filtered, to remove

high-frequency noise from the modulator output.

Referring to Figure 3, the high rate filter on the

voltage channel is implemented as a fixed Sinc

ter. The current channel uses a Sinc

4

filter, which

allows the current channel to make accurate measurements over a wider span of the total input

range, in comparison to the accuracy range of the

voltage channel. (This subject is discussed more in

Section 2.2.1)

Also note from Figure 3 that the digital data on the

voltage channel is subjected to a variable time-delay filter. The amount of delay depends on the value of the seven phase compensation bits (see Phase

Compensation), which can be set by the user. Note

that when the phase compensation bits PC[6:0] are

set to their default setting of “0000000” (and if

MCLK/K = 4.096MHz) then the nominal time delay that is imposed on the original analog voltage

input signal, with respect to the original analog current input signal, is ~1.0

µs. This translates into a

delay of ~0.0216 degrees at 60Hz.

2

fil-

12 DS487PP4

Page 13

CS5460A

2.1.3 Digital Compensation Filters

The data from both channels is then passed through

two FIR compensation filters, whose purpose is to

compensate for the magnitude roll-off of the

low-pass filtering operation (mentioned earlier).

2.1.4 Digital High-Pass Filters

Both channels provide an optional high-pass filter

(denoted as “HPF” in Figure 3) which can be engaged into the signal path, to remove the DC content

from the current/voltage signal before the RMS/energy calculations are made. These filters are activated by enabling certain bits in the Configuration

Register.

If the user wants to engage the high-pass filter in

only one of the two channels, then the all-pass filter

(see “APF” in Figure 3) will be enabled on the other channel, in order to preserve the relative phase

relationship between the voltage-sense and current-sense input signals. For example, if the HPF is

engaged for the voltage channel, but not the current

channel, then the APF will be engaged in the current

channel, to nullify the additional phase delay introduced by the high-pass filter in the current channel.

2.1.5 Overall Filter Response

When the CS5460A is driven with a 4.096 MHz

clock (K=1), the composite magnitude response

(over frequency) of the voltage channel’s input filter network is shown in Figure 4, while the composite magnitude response of the current channel’s

input filter network is given in Figure 5. Note that

the composite filter response of both channels

scales with MCLK frequency and K.

2.1.6 Gain and DC Offset Adjustment

After the filtering, the instantaneous voltage and

current digital codes are both subjected to offset/gain adjustments, based on the values in the DC

offset registers (additive) and the gain registers

(multiplicative). These registers are used for calibration of the device (see Section 4.8, Calibration).

After offset and gain, the 24-bit instantaneous data

sample values are stored in the Instantaneous Voltage and Current Registers, from which the user can

read out the data samples (via the serial interface).

2.1.7 Real Energy and RMS Computations

The digital instantaneous voltage and current data

is then processed further. Referring to Figure 3, the

instantaneous voltage/current data samples are

multiplied together (one multiplication for each

pair of voltage/current samples) to form instantaneous (real) power samples. After each A/D conversion cycle, the new instantaneous power sample

is stored (and can be read by the user) in the Instantaneous Power Register.

The instantaneous power samples are then grouped

into sets of N samples (where N = value in Cycle

Count Register). The cumulative sum of each successive set of N instantaneous power is used to

compute the result stored in the Energy Register,

which will be proportional to the amount of real energy registered by the device during the most recent

N A/D conversion cycles. Note from Figure 3 that

the bits in this running energy sum are right-shifted

12 times (divided by 4096) to avoid overflow in the

Energy Register. RMS calculations are also performed on the data using the last N instantaneous

voltage/current samples, and these results can be

read from the RMS Voltage Register and the RMS

Current Register.

2.2 Performing Measurements

To summarize Section 2.1, the CS5460A performs

measurements of instantaneous current and instantaneous voltage, and from this, performs computations of the corresponding instantaneous power, as

well as periodic calculations of real energy, RMS

current, and RMS voltage. These measurement/calculation results are available to the user in the form

of 24-bit signed and unsigned words. The scaling

of all output words is normalized to unity

full-scale. Note that the 24-bit signed output words

DS487PP4 13

Page 14

CS5460A

VOLTAGE

CURRENT

∆Σ

∆Σ

DELAY

REG

DELAY

2

SINC

SINC

REG

Confi guratio n Register *

PC[6:0] Bits

4

FIR HPF

AP F

FIR

HPF

AP F

Figure 3. Data Flow.

are expressed in two’s complement format. The

24-bit data words in the CS5460A output registers

represent values between 0 and 1 (for unsigned output registers) or between -1 and +1 (for signed output registers). A register value of 1 represents the

maximum possible value. Note that a value of 1.0

is never actually obtained in the registers of the

CS5460A. As an illustration, in any of the signed

output registers, the maximum register value is

[(2^23 - 1) / (2^23)] = 0.999999880791. After each

A/D conversion, the CRDY bit will be asserted in

the Status Register, and the INT

pin will also be-

come active if the CRDY bit is unmasked (in the

V

DCoff

I

DCoff

+

+

V*

*

I*

*

gn

x

x

gn

*

V

V

*

ACoff

x

-

*

P

off

x x

+

*

P

x

-

*

I

I

ACoff

* DENOTES REGISTER NAME

2

SINC

TBC *

N

Σ

2

SINC

*

N

EtoF

÷÷÷÷

4096

PULSE-RATE*

N

÷

E*

E

E

N

out

dir

N

÷

Mask Register). The assertion of the CRDY bit indicates that new instantaneous 24-bit voltage and

current samples have been collected, and these two

samples have also been multiplied together to provide a corresponding instantaneous 24-bit power

sample .

Table 1 conveys the typical relationship between

the differential input voltage (across the “+” and

“-” input pins of the voltage channel input) and the

corresponding output code in the Instantaneous

Voltage Register. Note that this table is applicable

for the current channel if the current channel’s

PGA gain is set for the “10x” gain mode.

V*

RMS

I*

RMS

0.5

0.0

-0.5

-1.0

Gain (dB)

-1.5

-2.0

-2.5

0 200 400 600 800 1000 1200 1400 1600 1800 2000

Frequency (Hertz)

Figure 4. Voltage Input Filter Characteristics

0.5

0

-0.5

-1

Gain (dB)

-1.5

-2

-2.5

0 200 400 600 800 1000 1200 1400 1600 1800 2000

Frequency (Hertz)

Figure 5. Current Input Filter Characteristics

14 DS487PP4

Page 15

Output Code

Input Voltage (DC)

+250mV 7FFFFF 8388607

14.9nV to 44.7nV 000001 1

-14.9nV to 14.9nV 000000 0

-44.7nV to -14.9nV FFFFFF -1

-250mV 800000 -8388608

Table 1. Differential Input Voltage vs. Output Code

The V

RMS,IRMS

(hexidecimal)

, and energy calculations are up-

Output Code

(decimal)

dated every N conversions (which is known as 1

“computation cycle”), where N is the value in the

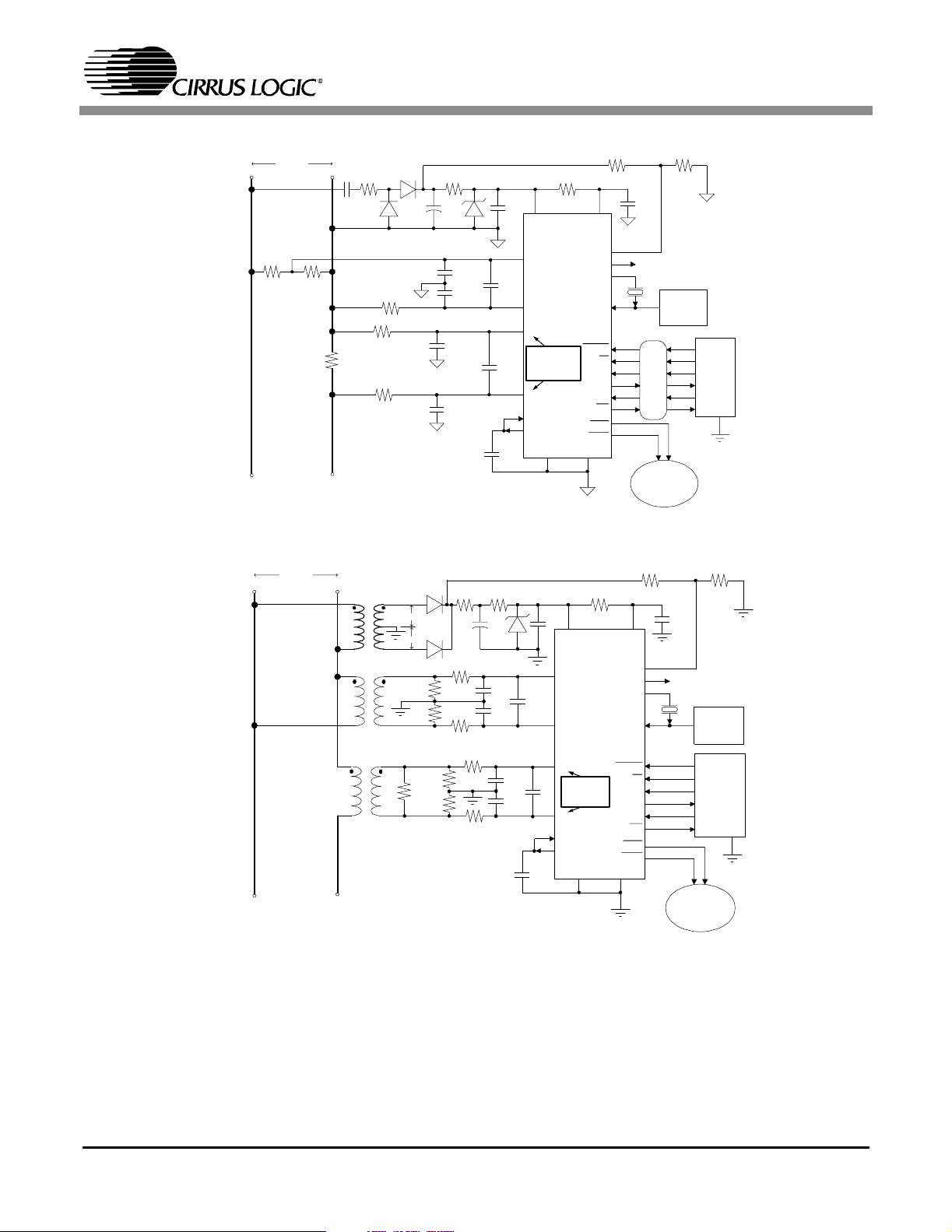

Cycle Count Register. At the end of each computation cycle, the DRDY bit in the Mask Register will

be set, and the INT

pin will become active if the

DRDY bit is unmasked.

DRDY is set only after each computation cycle has

completed, whereas the CRDY bit is asserted after

each individual A/D conversion. After any time

that these bits are asserted by the CS5460A, they

must be cleared (by the user) before they can be asserted again, so that they can trigger another interrupt event on the INT pin. If the Cycle Count

Register value (N) is set to 1, all output calculations

are instantaneous, and DRDY will indicate when

instantaneous calculations are finished, just like the

CRDY bit. For the RMS results to be valid, the Cycle-Count Register must be set to a value greater

than 10.

The computation cycle frequency is derived from

the master clock, and has a value of

(MCLK/K)/(1024*N). Under default conditions,

with a 4.096 Mhz clock at XIN, and K = 1, instantaneous A/D conversions for voltage, current, and

power are performed at a 4000 Sps rate, whereas

I

RMS

,V

, and energy calculations are per-

RMS

formed at a 1 Sps rate.

2.2.1 CS5460A Linearity Performance

Table 2 lists the range of input levels (as a percentage of full-scale registration in the Energy, Irms,

and Vrms Registers) over which the (linearity +

CS5460A

variation) of the results in the Vrms, Irms and Energy Registers are guaranteed to be within

reading, after the completion of each successive

computation cycle. Note that until the CS5460A is

calibrated (see Calibration) the accuracy of the

CS5460A (with respect to a reference line-voltage

and line-current level on the power mains) is not

guaranteed to within

±0.1%. But the linearity of

any given sample of CS5460A, before calibration,

will indeed be to within ±0.1% of reading over the

ranges specified, with respect to the input voltage

levels required (on the voltage and current channels) to cause full-scale readings in the Irms/Vrms

Registers. After both channels of the device are

calibrated for offset/gain, the ±0.1% of reading

spec will also reflect accuracy of the Vrms, Irms,

and Energy Register results. Finally, observe that

the typical maximum (full-scale) differential input

voltage for the voltage channel (and current channel, when its PGA is set for 10x gain) is 250mV

(nominal). If the gain registers of both channels

aresetto1(default)andthetwoDCoffsetregisters are set to zero (default), then a 250mV dc

signal applied to the voltage/current inputs will

measure at (or near) the maximum value of

0.9999... in the RMS Current/Voltage Registers.

Remember that the RMS value of a 250mV (dc)

signal is also 250mV. However, for either input

channel, it would not be practical to inject a sinusoidal voltage with RMS value of 250mV. This is because when the instantaneous value of such a sine

Energy Vrms Irms

Range (% of FS)

Max. Differential

Input

Linearity

Table 2. Available range of ±0.1% output linearity, with

default settings in the gain/offset registers.

0.1% - 100%

not applicable

0.1% of

reading

50% - 100% 0.2% - 100%

V-channel:

±250mV

0.1% of

reading

±0.1% of

I-channel:

±250mV 10x

±50mV 50x

0.1% of

reading

DS487PP4 15

Page 16

CS5460A

wave is at or near the level of its positive/negative

peak regions (over each cycle), the voltage level of

this signal would exceed the maximum differential

input voltage range of the input channels. The largest sine wave voltage signal that can be presented

across the inputs, with no saturation of the inputs,

is (typically) 250mV / sqrt(2) = ~176.78 mV

(RMS), which is at ~70.7% of full-scale. This

would imply that for the current channel, the (linearity+variation) tolerance of the RMS measurements for a purely sinusoidal 60 Hz input signal

could be measured to within

a magnitude range of 0.2% - 70.7% (of the maximum full-scale differential input voltage level).

The range over which the (linearity + variation)

will remain within ±0.1% of reading can often be

increased by selecting a value for the Cycle-Count

Register such that the time duration of one computation cycle is equal to (or very close to) a

whole-number of power-line cycles (and N must be

greater than or equal to 4000). For example, with

the cycle count set to 4200, the ±0.1% of reading

(linearity + variation) range for measurement of a

60 Hz sinusoidal current-sense voltage signal (created by sensing the current on a power line) can be

increased beyond the range of 0.2% - 70.7%. The

accuracy range will be increased because (4200

samples / 60 Hz) is a whole number of cycles (70).

Note that this increase in the measurement range

refers to an extension of the low end of the input

scale (i.e., this does not extend the high-end of the

range above 100% of full-scale). This enables accurate measurement of even smaller power-line

current levels, thereby extending the load range

over which the power meter can make accurate energy measurements. Increasing the accuracy range

can be beneficial for power metering applications

which require accurate power metering over a very

large load range.

±0.1% of reading over

2.2.2 Single Computation Cycle (C=0)

Note that ‘C’ refers to the value of the C bit, contained in the ‘Start Conversions’ command (see

Section 3.1). This commands instructs the

CS5460A to perform conversions in ‘single computation cycle’ data acquisition mode. Based on

the value in the Cycle Count Register, a single

computation cycle is performed after the user transmits the ‘Start Conversions’ command to the serial

interface. After the computations are complete,

DRDY is set. 32 SCLKs are then needed to read out

a calculation result from one of several result registers. The first 8 SCLKs are used to clock in the

command to determine which register is to be read.

The last 24 SCLKs are used to read the desired register. After reading the data, the serial port remains

in the active state, and waits for a new command to

be issued. (See Section 3 for more details on reading register data from the CS5460A).

2.2.3 Continuous Computation Cycles (C=1)

When C=1, the CS5460A will perform conversions

in ‘continuous computation cycles’ data acquisition

mode. Based on the information provided in the Cycle Count Register, computation cycles are repeatedly performed on the voltage and current channels

(after every N conversions). Computation cycles

cannot be started/stopped on a ‘per-channel’ basis.

After each computation cycle is completed, DRDY

is set. Thirty-two SCLKs are then needed to read a

register. The first 8 SCLKs are used to clock in the

command to determine which results register is to be

read. The last 24 SCLKs are used to read out the

24-bit calculation result. While in this acquisition

mode, the designer/programmer may choose to acquire (read) only those calculations required for

their particular application, as DRDY repeatedly indicates the availability of new data. Note again that

the user’s MCU firmware must reset the DRDY bit

to “0” before it can be asserted again.

Referring again to Figure 3, note that within the

Irms and Vrms data paths, prior to the square-root

16 DS487PP4

Page 17

CS5460A

operation, the instantaneous voltage/current data is

2

low-pass filtered by a Sinc

filter. Then the data is

decimated to every Nth sample. Because of the

2

Sinc

filter operation, the first output for each channel will be invalid (i.e. all RMS calculations are invalid in the ‘single computation cycle’ data

acquisition mode and the first RMS calculation results will be invalid in the ‘continuous computation

cycles’ data acquisition mode). However, all energy calculations will be valid since energy calcula-

2

tions do not require this Sinc

operation.

After the user issues the ’Start Conversions’ command to the CS5460A (see Section 3.1, Commands

(Write Only)), and if the ‘C’ bit in this command is

set to a value of ‘1’, the device will remain in its ac-

tive state. Once commanded into continuous computation cycles data acquisition mode, the

CS5460A will continue to perform A/D conversions on the voltage/current channels, as well as all

subsequent calculations, until a) the ‘Power-Up/Halt’ command is received through the serial

interface, or b) the device looses power, or c) the

RS bit in the Configuration Register is asserted by

the user (‘software reset’), or d) the /RESET pin is

asserted and then de-asserted (‘hardware reset’).

2.3 Basic Application Circuit Configurations

Figure 6 shows the CS5460A connected to a service to measure power in a single-phase 2-wire system operating from a single power supply. Note

that in this diagram the shunt resistor used to monitor the line current is connected on the “Line” (hot)

side of the power mains. In most residential power

metering applications, the power meter’s current-sense shunt resistor is intentionally placed on

the ‘hot’ side of the power mains in order to help

detect any attempt by the subscriber to steal power.

In this type of shunt-resistor configuration, note

that the common-mode level of the CS5460A must

be referenced to the hot side of the power line. This

means that the common-mode potential of the

CS5460A will typically oscillate to very high positive voltage levels, as well as very high negative

voltage levels, with respect to earth ground potential. The designer must therefore be careful when

attempting to interface the CS5460A’s digital output lines to an external digital interface (such as a

LAN connection or other communication network). Such digital communication networks may

require that the CMOS-level digital interface to the

meter is referenced to an earth-ground. In such cases, the CS5460A’s digital serial interface pins must

be isolated from the external digital interface, so

that there is no conflict between the ground references of the meter and the external interface. The

CS5460A and associate circuitry should be enclosed in a protective insulated case when used in

this configuration, to avoid risk of harmful electric

shock to humans/animals/etc.

Figure 7 shows how the same single-phase

two-wire system can be metered while achieving

complete isolation from the power lines. This isolation is achieved using three transformers. One

transformer is a general-purpose voltage transformer, used to supply the on-board DC power to

the CS5460A. A second transformer is a high-precision, low-impedance voltage transformer (often

called a ‘potential transformer’) with very little

roll-off/phase delay, even at the higher harmonics.

A current transformer is then used to sense the line

current. A burden resistor placed across the secondary of the current transformer creates the current-sense voltage signal, for the CS5460A’s

current channel inputs. Because the CS5460A is

not directly connected to the power mains, isolation

is not required for the CS5460A’s digital interface.

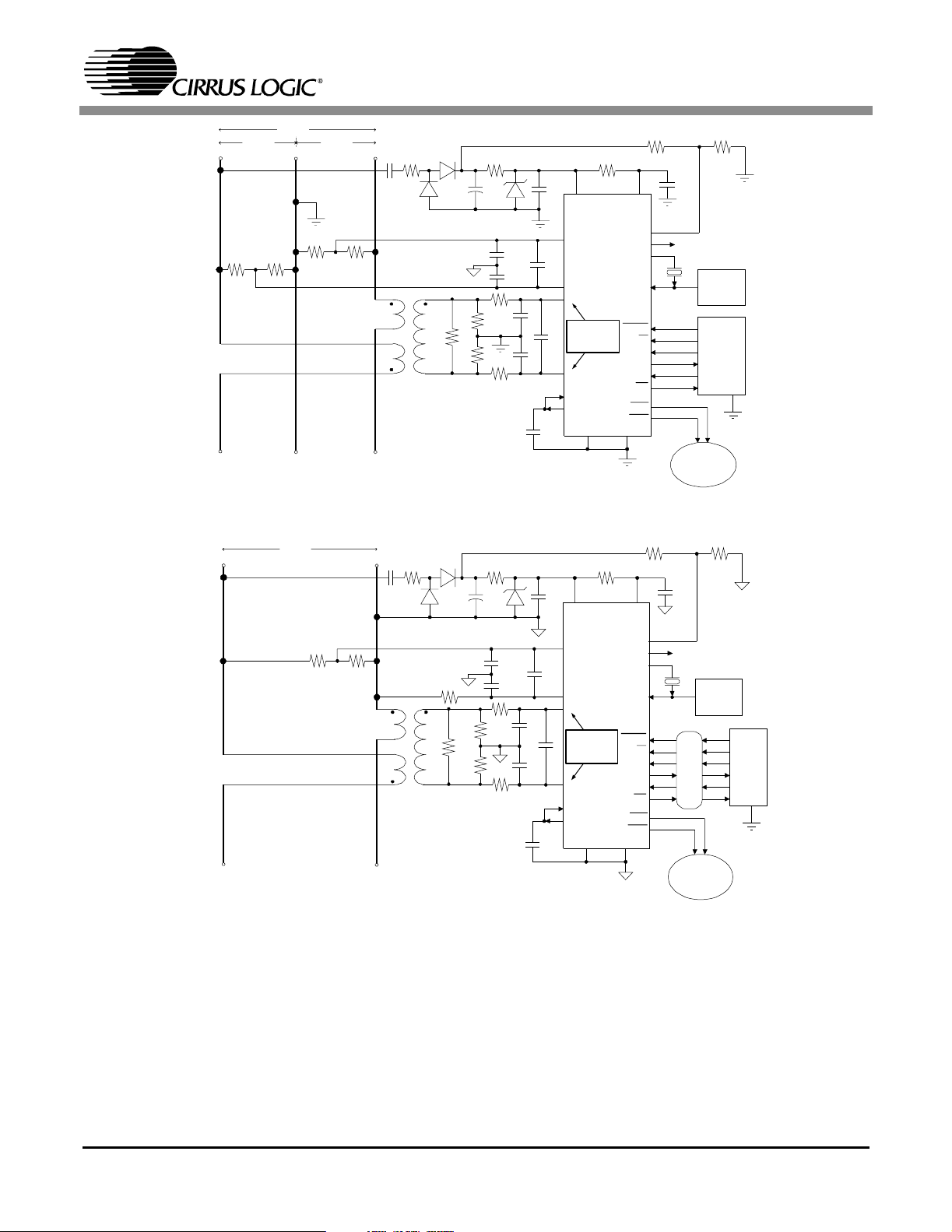

Figure 8 shows the CS5460A configured to measure power in a single-phase 3-wire system. In

many 3-wire residential power systems within the

United States, only the two Line terminals are

available (neutral is not available). Figure 9 shows

how the CS5460A can be configured to meter a

3-wire system when no neutral is available.

DS487PP4 17

Page 18

CS5460A

N

120 VAC

R

2

To Service

Ω

5k

L

Ω

500

470 nF

R

1

R

*

R

I-

R

Shunt

*

R

I+

* Re fer to Input Pr otecti on

** Re fer to Input Fi ltering

*

V-

Ω

500

*

*

C

V+

**

C

V-

I+

0.1 µF

- Secti on 4.12

- Section 4.13

0.1 µF100 µF

9

**

C

Vdiff

10

15

**

C

Idiff

16

12

11

+

**

C

I-

**

C

Ω

10

14

VA+ VD+

CS5460A

VIN+

VIN-

IIN-

NOTE: Currentchannel

inputm easures voltage

(just likevoltage input).

IIN+

VREFIN

VREFOUT

PFMON

CPUCLK

RESET

VA- DGND

13 4

XOUT

EOUT

XIN

SDI

SDO

SCLK

INT

EDIR

3

17

2

1

24

19

7

CS

23

6

5

20

22

21

0.1 µF

2.5 MHz to

20 MHz

ISOLATION

Me ch. C ounter

or

Stepper Mot or

10 k

Optional

Clock

Source

Ω

Serial

Data

Interface

Figure 6. Typical Connection Diagram (One-Phase 2-Wire, Direct Connect to Power Line)

N

120 VAC

To Service

L

Voltage

Transformer

M:1

Low Phase-Shift

Pot entia l Tr ansfo rmer

N:1

Current

Transformer

200

Ω

12 VAC

12 VAC

1k

Ω

1k

Ω

R

Burden

* Refer to Input Protection

** Re fer to I nput Fi lteri ng

+

*

R

V+

*

R

V-

1k

Ω

1k

Ω

R

200

200

µF

**

C

V+

**

C

V-

*

R

I-

C

C

*

I+

0.1 µF

- Section 4.12

- Secti on 4.13

Ω

5k

Ω

Ω

0.1µF

**

C

Vdiff

10

15

**

I+

**

C

Idiff

**

16

I-

12

11

10

14

VA+ VD+

CS5460A

9

VIN+

VIN-

IIN-

NOTE: Currentchannel

inputmeasures voltage

(just likev oltage input).

IIN+

VREFIN

VREFOUT

VA- DGND

13 4

PFMON

CPUCL K

XOUT

XIN

RESET

SDI

SDO

SCLK

INT

EDIR

EOUT

3

17

2

1

24

19

7

CS

23

6

5

20

22

21

0.1 µF

2.5 MHz to

20 MHz

Mec h. C ounte r

or

Stepper Mo tor

10 k

Ω

Optional

Clock

Source

Serial

Data

Interface

Figure 7. Typical Connection Diagram (One-Phase 2-Wire, Isolated from Power Line)

3. SERIAL PORT OVERVIEW

The CS5460A's serial port incorporates a state machine with transmit/receive buffers. The state machine interprets 8 bit command words on the rising

edge of SCLK. Upon decoding of the command

word, the state machine performs the requested

command or prepares for a data transfer of the addressed register. Request for a read requires an internal register transfer to the transmit buffer, while

a write waits until the completion of 24 SCLKs before performing a transfer. The internal registers

are used to control the ADC's functions. All regis-

18 DS487PP4

Page 19

CS5460A

240 VAC

120 VAC 120 VAC

L

1

R

R

1

2

To Service

N

Earth

Ground

R

3

To Service

L

2

470 nF

500

Ω

100 µF

Ω

500

+

0.1 µF

10

14

VA+ VD+

CS5460A

9

**

C

Vdiff

10

16

**

C

I+

**

C

Idif f

**

C

I-

15

12

11

- Sec tion 4. 12

VIN+

VIN-

IIN+

NOTE: Currentchannel

inputm easures voltage

(just likevoltage input).

IIN-

VREFIN

VREFOUT

VA-

13 4

**

C

R

4

1k

R

Burden

1k

Ω

* Ref er to Input P rotect ion

** Re fer to Input Filt ering

V+

**

C

V-

Ω

*

R

I+

*

R

I-

0.1 µF

- Secti on 4.13

Ω

PFMON

CPUCLK

RESET

DGND

XOUT

SDO

SCLK

EDIR

EOUT

XIN

SD

INT

5k

Ω

3

17

2

1

24

19

7

CS

23

I

6

5

20

22

21

0.1 µF

2.5 MHz to

20 MHz

Mech. Count er

or

Stepper Motor

10 k

Opti onal

Clock

Source

Serial

Dat a

Inte rface

Ω

Figure 8. Typical Connection Diagram (One-Phase 3-Wire)

5k

L

1

To Service

240 VAC

Ω

L

2

k

Ω

1

235 nF

R

R

1

2

To Service

100 µF

*

R

V-

R

Burden

* Ref er to I nput Prote ction

** Re fer to Input F iltering

Ω

500

*

*

C

V+

**

C

V-

*

I+

*

I-

0.1 µF

- Section 4.13

0.1 µF

**

C

Vdiff

10

16

**

C

I+

**

C

Idif f

**

C

I-

15

12

11

- Sec tion 4. 12

9

+

R

1k

Ω

1k

Ω

R

Ω

10

14

VA+ VD+

CS5460A

VA-

13 4

PFMON

CPUCLK

XOUT

RESET

SCLK

EOUT

DGND

VIN+

VINIIN+

NOTE: Currentchannel

inputm easures voltage

(justlike voltageinput).

IIN-

VREF IN

VREF OUT

XIN

CS

SDI

SDO

INT

EDIR

3

17

2

1

24

19

7

23

6

5

20

22

21

0.1 µF

2.5 MHz to

20 MHz

ISOLATION

Mech. Co unter

or

Stepper Motor

10 k

Optional

Clock

Source

Ω

Serial

Data

Interface

Figure 9. Typical Connection Diagram (One-Phase 3-Wire - No Neutral Available)

ters are 24-bits in length. Figure 25 summarizes the

internal registers available to the user.

The CS5460A is initialized and fully operational in

its active state upon power-on. After a power-on,

the device will wait to receive a valid command

(the first 8-bits clocked into the serial port). Upon

receiving and decoding a valid command word, the

state machine instructs the converter to either perform a system operation, or transfer data to or from

an internal register. The user should refer to the

“Commands” section to decode all valid commands.

DS487PP4 19

Page 20

CS5460A

3.1 Commands (Write Only)

All command words are 1 byte in length. Commands that write to a register must be followed by 3 bytes of register

data. Commands that read from registers initiate 3 bytes of register data. Commands that read data can be ‘chained’

with other commands (e.g., while reading data, a new command can be sent to SDI which can execute before the

original read is completed). This allows for ‘chaining’ commands.

3.1.1 Start Conversions

B7 B6 B5 B4 B3 B2 B1 B0

1110C000

This command indicates to the state machine to begin acquiring measurements and calculating results. The device

has two modes of acquisition.

C Modes of acquisition/measurement

0 = Perform a single computation cycle

1 = Perform continuous computation cycles

3.1.2 SYNC0 Command

B7 B6 B5 B4 B3 B2 B1 B0

11111110

This command is the end of the serial port re-initialization sequence. It can also be used as a NOP command. The

serial port is resynchronized to byte boundaries by sending three or more consecutive SYNC1 commands followed

by a SYNC0 command.

3.1.3 SYNC1 Command

B7 B6 B5 B4 B3 B2 B1 B0

11111111

This command is part of the serial port re-initialization sequence. It can also serve as a NOP command.

3.1.4 Power-Up/Halt

B7 B6 B5 B4 B3 B2 B1 B0

10100000

If the device is powered-down into either stand-by or sleep power saving mode (See 3.1.5), this command will power-up the device. After the CS5460 is initially powered-on, no conversions/computations will be running. If the device

is already powered on and the device is running either ‘single computation cycle’ or ‘continuous computation cycles’

data acquisition modes, all computations will be halted once this command is received.

20 DS487PP4

Page 21

CS5460A

3.1.5 Power-Down

B7 B6 B5 B4 B3 B2 B1 B0

100S1S0000

The device has two power-down states to conserve power. If the chip is put in stand-by state, all circuitry except the

analog/digital clock generators is turned off. In the sleep state, all circuitry except the digital clock generator and the

instruction decoder is turned off. Waking up the CS5460A out of sleep state requires more time than waking the

device out of stand-by state, because of the extra time needed to re-start and re-stabilize the analog clock signal.

[S1 S]0 Power-down state

00 = Reserved

01 = Halt and enter stand-by power saving state. This state allows quick power-on time

10 = Halt and enter sleep power saving state. This state requires a slow power-on time

11 = Reserved

3.1.6 Calibration

B7 B6 B5 B4 B3 B2 B1 B0

110VIRGO

The device has the capability of performing a system AC offset calibration, DC offset calibration, AC gain calibration,

and DC gain calibration. The user can calibrate the voltage channel, the current channel, or both channels at the

same time. Offset and gain calibrations should NOT be performed at the same time (must do one after the other).

For a given application, if DC gain calibrations are performed, then AC gain calibration should not be performed (and

vice-versa). The user must supply the proper inputs to the device before initiating calibration.

[V I] Designates calibration channel

00 = Not allowed

01 = Calibrate the current channel

10 = Calibrate the voltage channel

11 = Calibrate voltage and current channel simultaneously

R Specifies AC calibration (R=1) or DC calibration (R=0)

G Designates gain calibration

0 = Normal operation

1 = Perform gain calibration

O Designates offset calibration

0 = Normal operation

1 = Perform offset calibration

DS487PP4 21

Page 22

CS5460A

3.1.7 Register Read/Write

B7 B6 B5 B4 B3 B2 B1 B0

0W/R

This command informs the state machine that a register access is required. On reads the addressed register is loaded into the output buffer and clocked out by SCLK. On writes the data is clocked into the input buffer and transferred

to the addressed register on the 24

RA4RA3RA2RA1RA0 0

th

SCLK.

W/R

Write/Read control

0 = Read register

1 = Write register

RA[4:0] Register address bits. Binary encoded 0 to 31. All registers are 24 bits in length.

Address Abbreviation Name/Description

00000 Config Configuration Register.

00001 I

00010 I

00011 V

00100 V

DCoff Current Channel DC Offset Register.

gn Current Channel Gain Register.

DCoff Voltage Channel DC Offset Register.

gn Voltage Channel Gain Register.

00101 Cycle Count Number of A/D cycles per computation cycle.

00110 Pulse-Rate Used to set the energy-to-pulse ratio on EOUT

(and EDIR).

00111 I Instantaneous Current Register (most recent current sample).

01000 V Instantaneous Voltage Register (most recent voltage sample).

01001 P Instantaneous Power Register (most recent power sample).

01010 E Energy Register (accumulated over latest computation cycle).

01011 I

01100 V

RMS

RMS

RMS Current Register (computed over latest computation cycle).

RMS Voltage Register (computed over latest computation cycle).

01101 TBC Timebase Calibration Register.

01110 Poff Power Offset Register.

01111 Status Status Register.

10000 I

10001 V

ACoff Current Channel AC Offset Register.

ACoff Voltage Channel AC Offset Register.

10010 Res Reserved †

.. .

.. .

10111 Res Reserved †

11000 Res Reserved †

11001 Test Reserved †

11010 Mask Mask Register.

11011 Res Reserved †

11100 Ctrl Control Register.

11101 Res Reserved †

.. .

.. .

11111 Res Reserved †

† These registers are for Internal Use only and should not be written to.

22 DS487PP4

Page 23

CS5460A

3.2 Serial Port Interface

The CS5460A’s slave-mode serial interface consists of two control lines and two data lines, which

have the following pin-names: CS

SDO. Each control line is now described.

CS

Chip Select (input pin), is the control line

which enables access to the serial port. When CS

is set to logic 1, the SDI, SDO, and SCLK pins will

be held at high impedance. When the CS

to logic 0, the SDI, SDO, and SCLK pins have the

following functionality:

SDI Serial Data In (input pin), is the user-generated signal used to transfer (send) data/command/address/etc. bits into the device.

SDO Serial Data Out (output pin), is the data signal used to read output data bits from the device’s

registers.

SCLK Serial Clock (input pin), is the serial

bit-clock which controls the transfer rate of data

to/from the ADC’s serial port. To accommodate

opto-isolators, SCLK is designed with a

Schmitt-trigger input to allow an opto-isolator with

slower rise and fall times to directly drive the pin.

Additionally, SDO is capable of sinking or sourcing up to 5 mA to directly drive an opto-isolator

LED. SDO will have less than a 400 mV loss in the

drive voltage when sinking or sourcing 5 mA.

,SCLK,SDI,

pin is set

3.3 Serial Read and Write

The state machine decodes the command word as it

is received. Data is written to and read from the

CS5460A by using the Register Read/Write command. Figure 1 illustrates the serial sequence necessary to write to or read from the serial port

buffers. As shown in Figure 1, a transfer of data is

always initiated by sending the appropriate 8-bit

command (MSB first) to the serial port (SDI pin).

It is important to note that some commands use information from the Cycle-Count Register and Configuration Register to perform the function. For

those commands, it is important that the correct information is written to those registers first.

3.3.1 Register Write

When a command involves a write operation, the

serial port will continue to clock in the data bits

(MSB first) on the SDI pin for the next 24 SCLK

cycles. Command words instructing a register

write must be followed by 24 bits of data. For instance, to write the Configuration Register, the user

would transmit the command (0x40) to initiate a

write to the Configuration Register. The CS5460A

will then acquire the serial data input from the

(SDI) pin when the user pulses the serial clock

(SCLK) 24 times. Once the data is received, the

state machine writes the data to the Configuration

Register and then waits to receive another valid

command.

3.3.2 Register Read

When a read command is initiated, the serial port

will start transferring register content bits (MSB

first) on the SDO pin for the next 8, 16, or 24 SCLK

cycles. Command words instructing a register read

may be terminated at 8-bit boundaries (e.g., read

transfers may be 8, 16, or 24 bits in length). Also

data register reads allow “command chaining”.

This means that the micro-controller is allowed to

send a new command while reading register data.

The new command will be acted upon immediately

and could possibly terminate the first register read.

For example, if a command word is sent to the state

machine to read one of the output registers, then after the user pulses SCLK for 16-bits of data, a second write command word (e.g., to clear the Status

Register) may be pulsed on to the SDI line at the

same time the last 8-bits of data (from the first read

command) are pulsed from the SDO line. As another example, suppose that the user is only interested in acquiring the 16-most significant bits of

data from the first read. In this case, the user can

begin to strobe a second read command on SDI after the first 8 data bits have been read from SDO.

DS487PP4 23

Page 24

CS5460A

During the read cycle, the SYNC0 command

(NOP) should be strobed on the SDI port while

clocking the data from the SDO port.

3.4 System Initialization

A software or hardware reset can be initiated at any

time. The software reset is initiated by writing a

logic 1 to the RS (Reset System) bit in the Configuration Register, which automatically returns to

logic 0 after reset. At the end of the 32ndSCLK

(i.e., 8 bit command word and 24 bit data word) internal synchronization delays the loading of the

Configuration Register by 3 or 4 DCLK cycles.

Then the reset circuit initiates the reset routine on

st

the 1

A hardware reset is initiated when the RESET

is forced low for at least 50 ns. The RESET

is asynchronous, requiring no MCLKs for the part

to detect and store a reset event. The RESET