Page 1

MUR160

F1

4A

t

NTC1

30

NO POP - SHORT WITH 28 AWG WIRE

C1

2200pF

C2

2200pF

C3

0.22uF

C4

0.22uF

+

-

BR1

GBU4J-BP

600V

C5

NO POP

D1

C6

0.33uF

D2

MUR460G

600V

t

NTC2

30

NO POP, SHORT WITH AWG28 WIRE

R8 20K

1

2

CON2

TERM BLK

1

2

3

CON1

TERM BLK

R3

1M

R20

1K

R6

48.7K

R2

1M

R13

1M

R18

1.78K

VZ

V300LA20AP

300V

1

2

3

4

L1

IND-5MH-TSD-2796

5mH

NO POP, SHORT PIN 1-2 & PIN 3-4 wi th 28 AWG wire

L2

IND-5MH-TSD-2796

5mH

1

2

3

CON3

TERM BLK

A1

1PAD-H78P108A21PAD-H78P108

R19 100

C7

100uF

ELEC

R12

0

R11

1K

C10

4.7uF

1

VBIAS2

2

STBY

3

IRECT

4

ILINK5GND

6

GD

7

VDD

8

VBIAS1

U2

CS1500-FSZ

NO POP

HS1

12.5W

C12

100pF

SDG

Q1

STP12NM50FP

L3

L4

NO POP, SHORT WITH AWG28 WIRE

L5

380uH

RLCS-1007

R17

NO POP

C8

NO POP

C9

NO POP

R21

NO POP

R22

NO POP

R4

NO POP

R10

NO POP

D3

LL4148

1

IFB

2

NC

3

IAC

4

CS5ZCD

6

GND

7

GD

8

VDD

U1

CS1501-FSZ

C11

33pF

R14

1M

R7

4.7 OHM

TP8

TP2

TP3

TP4

TP5

TP6

TP7

R5

NO POP

R16 0

R23

0

R15

1M

JP1

0.800" WIRE JUMPER

C14

1000pF

X7R

NO POP

C13

1000pF

X7R

C15

1000pF

X7R

NO POP

R1

1M

R9

0.1

1W

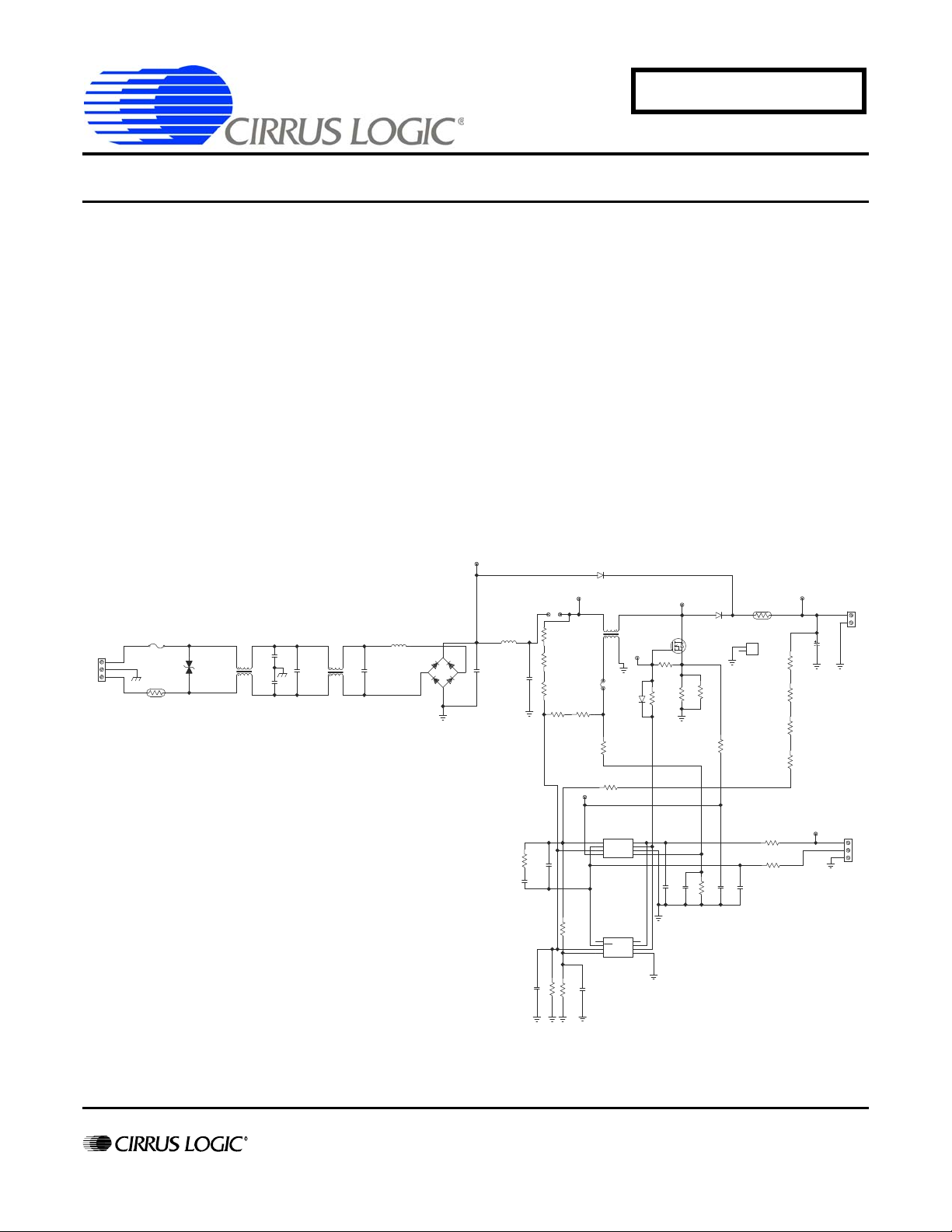

AN346

Application Note

CS150x & CS160x PCB LAYOUT GUIDELINES

1. INTRODUCTION

The CS150x & CS160x are high-performance variable frequency discontinuous conduction mode (VFDCM), active digital power factor correction (PFC) controllers. The CS1500/CS1501 are intended for use

in power supplies, and the CS1600/CS1601 are targeted for lighting applications.

This document describes best layout practices for these devices, using the CS1500/CS1600 &

CS1501/CS1601 90W PFC demonstration board, CDB150x as an example. This board has dual

footprints to allow either the CS1500/CS1600 or CS1501/CS1601 to be fitted. The layout guidelines

presented in this application note are also applicable to lighting designs. In th is docu ment, all refere nces

will be to the CS1500 and CS1501.

Note: The CS1501 uses two additional pins. Pin 4 (CS) is used for current sense. Pin 5 (ZCD) is used for

zero current detection (valley switching detection). These pins are not present on the CS1500 and are not

connected. Although these functions are not present on the CS1500, the gen eral layout principles are the

same. For a full description of these functions, please refer to the CS1501 & CS1601 data sheets

Figure 1. Schematic of a 90W PFC System with CS1500/CS1501

In the schematic above U1 refers to CS1501 and U2 refers to CS1500. Assembly instructions are

provided for using either the CS1500 or CS1501.

Copyright Cirrus Logic, Inc. 2011

http://www.cirrus.com

(All Rights Reserved)

APR ‘11

AN346REV1

Page 2

AN346

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative. To fi nd the one nearest to you

go to www.cirrus.com

IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") b eli eve that the information contained in this d oc um e nt i s accu ra te and reliable. However, the information is subject

to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant

information to verify, before placing or ders, that inform ation be ing r elied on is curren t and com plete. A ll pro ducts are sold su bject to the term s and con dition s of sale

supplied at the time of order ackno wledgment, includin g those pertaining to w arranty, indemnificatio n, and limitation of li ability. No responsibility is assumed by Cirrus

for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third

parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights,

copyrights, trade marks, tra de secrets or other int ellectual property r ights. Cirr us owns the co pyrights a ssociated wit h the inf ormation co ntained her ein and gi ves

consent for copies to be made of the informa tion only for use within yo ur or gani zation w ith resp ect to Cirru s inte grated cir cuits or other p rodu cts of C irrus. This co nsent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (" CRITICAL APPLICATI ONS"). CIRRUS PRODUCT S ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR

USE IN PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK

AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER

OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE,

TO FULLY INDEMNIFY CIRRUS , ITS OFFI CERS, DI RECTORS, EMPLOY EES, DISTRI BUTORS AND OTHER AGENTS F ROM ANY AND ALL LIA BILITY, IN CLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks

or service marks of their respective owners.

IMPORTANT SAFETY INSTRUCTIONS

Read and follow all safety instructions prior to using this demonstration board.

This Engineering Evaluation Unit or Demonstration Board must only be used for assessing IC performance in a

laboratory setting. This product is not intended for any other use or incorporation into products for sale.

This product must only be used by qualified technicians or professionals who are trained in the safety procedures

associated with the use of demonstration boards.

Risk of Electric Shock

• The direct connection to the AC power line and the open and unprotected boards present a serious risk of electric

shock and can cause serious injury or death. Extreme caution needs to be exercised while handling this board.

• Avoid contact with the exposed conductor or terminals of components on the board. High voltage is present on

exposed conductor and it may be present on terminals of any components directly or indirectly connected to the AC

line.

• Dangerous voltages and/or currents may be internally generated and accessible at various points across the board.

• Charged capacitors store high voltage, even after the circuit has been disconnected from the AC line.

• Make sure that the power source is off before wiring any connection. Make sure that all connectors are well

connected before the power source is on.

• Follow all laboratory safety procedures established by your employer and relevant safety regulations and guidelines,

such as the ones listed under, OSHA General Industry Regulations - Subpart S and NFPA 70E.

Suitable eye protection must be worn when working with or around demonstration boards. Always

comply with your employer’s policies regarding the use of personal protective equipment.

All components, heat sinks or metallic parts may be extremely hot to touch when electrically active.

Heatsinking is required for Q1. The end product should use tar pitch or an equivalent compound for this

purpose. For lab evaluation purposes, a fan is recommended to provide adequate cooling.

2

Page 3

AN346

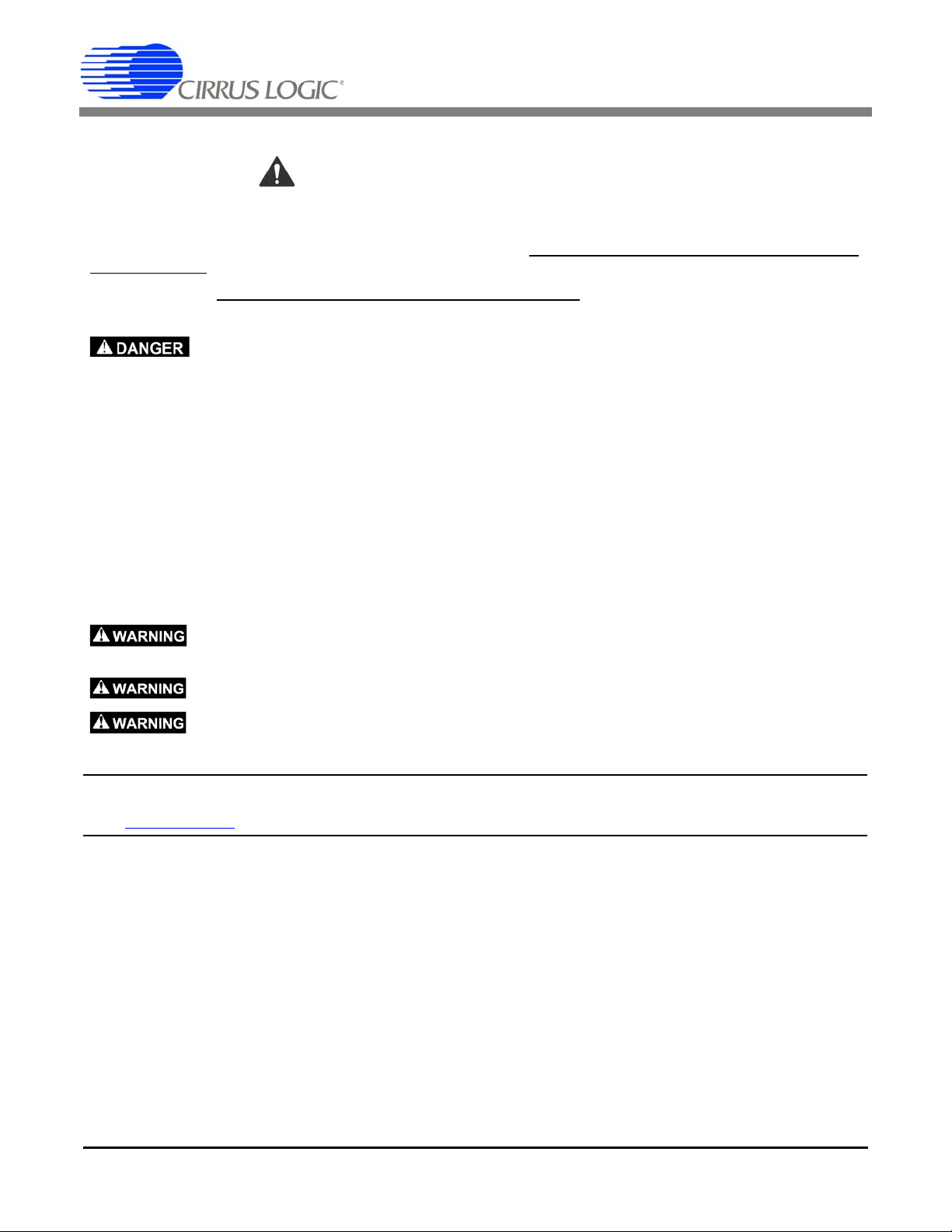

EMI Filter Boost PFC Sect ion

Low Voltage IC Section

2. PCB LAYOUT

Figure 1 and Figure 2 show a schematic and layout for a 90W PFC stage. The board is a single-layer PCB

with through-hole components on the top side, surface-mou nt components & signal routing on the bottom.

Figure 2. Single-layer PCB Layout for a 120W PFC-only Application Using the CS1500

The following sections demonstrate the best layout practices when designing a system using the

CS1500/CS1501.

2.1 Power Layout Recommendations

The following are good layout guidelines for a PFC stage or fluorescent ballast.

– Keep the main power components such as inductor, FET, diode, and outpu t bulk capacitor as close

together as possible. Minimize trace impedance by keeping connections as short & wide as

possible. Fast power switching currents generate noise in proportion to the trace impedance.

– The power-stage ground and the signal ground must be separated.

– Input decoupling capacitors should be placed close to the inductor.

– EMI filter should be placed as close to AC inlet as possible.

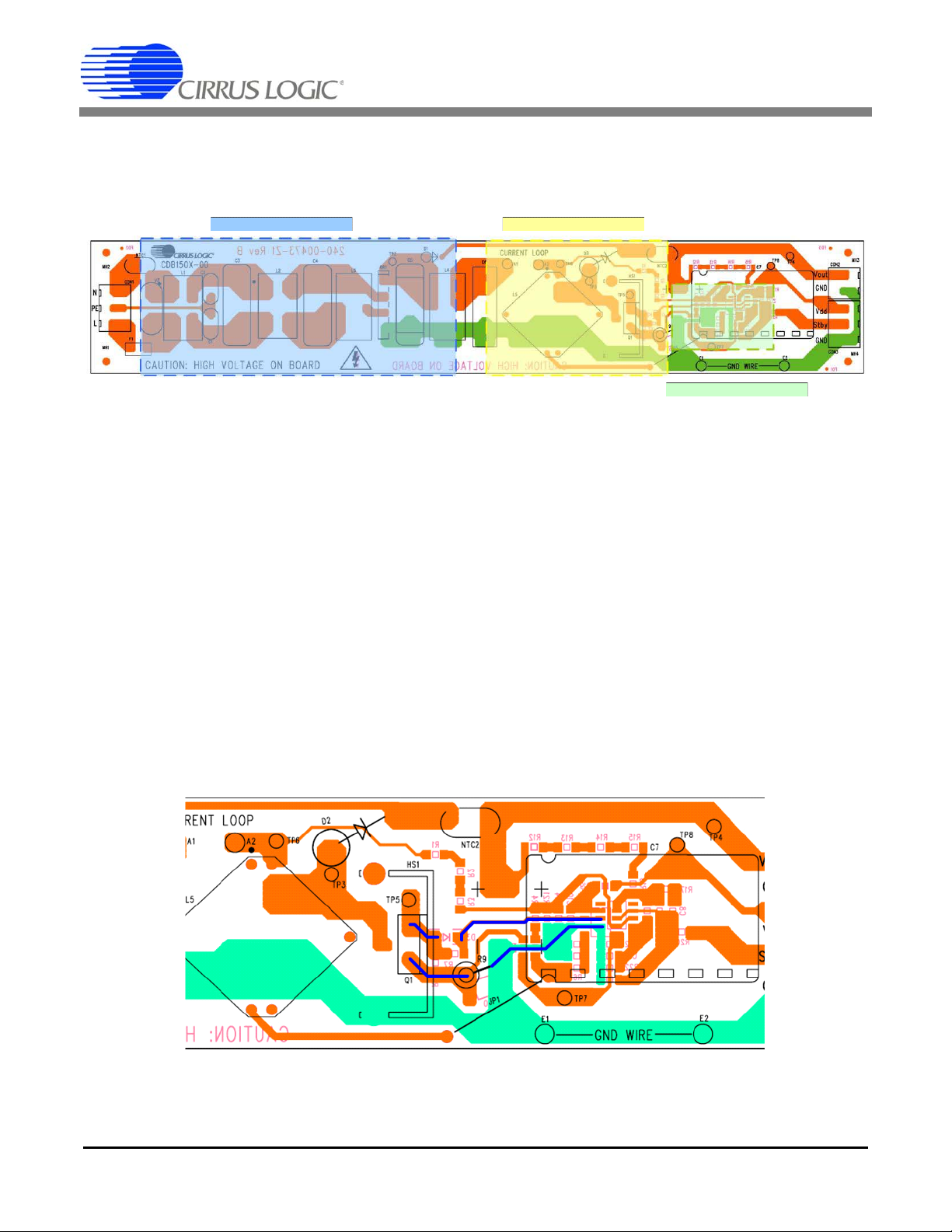

– The MOSFET gate drive loop length should be minimized, as shown in Figure 3. This applies to

both the positive (drive) path & return (GND).

– Current sense resistor return (GND) should be close to the output bulk capacitor negative (GND)

to reduce interference with the IC.

Figure 3. Gate-to-Ground Current Paths Between CS1501 and MOSFET

3

Page 4

AN346

Dirty G r ound car r ying gate

current

Clean Anal og Ground f o r

Decoupling Sensitive Nodes

Link Capacit or

Negative

2.2 Placement of the CS1501 Relative to the Power Stage

– The IC should be placed away from power switching devices & traces.

– Placing the IC directly under the boost inductor is not recommended. Air-gapped cores radiate

magnetic flux which can cause noise on signal traces.

– Placing the IC immediately after the PFC output capacitors as shown in Figure 3, 4, and 5 offers a

good trade-off between power and signal integrity. This is because all the signals beyond the bulk

capacitor can be considered DC.

3. IC GROUNDING PRACTICES

Signal ground should be separate from the power ground. It is recommended that the sensitive IC ground

be referenced to the negative of the bulk capacitor C14 at the PFC output as shown in Figure 4.

The ground under the IC should be maximized. This ground can be divided into two sections:

– Gate drive ground, which is noisy and can carry currents up to 1A.

– Decoupling for sense lines. Figure 4 shows that these are separated.

As shown in Figure 4, the noisy current from the gate drive return enters the IC pin. The ground trace that

continues beyond the gate drive is clean and is strictly used for decoupling the sense lines. By maximizing

the signal ground around the IC and especially those pertaining to the high di/dt currents on the gate

return, the IC can have a clean reference.

4

Figure 4. Ground Routing Around the IC and VDD Path & Location of Decoupling Capacitor

Page 5

AN346

Pin

Number Designator Recommended Decoupling

1 IFB

1nF high-frequency ceramic capacitor recommended between pin 1

and GND or VDD.

2 STBY

Pull high through a resistor as shown in schematic. A 1nF decoupling

capacitor to ground is recommended if the pin is not used.

3 IAC

1nF high-frequency ceramic capacitor recommended between pin 3

and GND or VDD.

4 CS

100pF to 1nF high-frequency capacitor recommended between pin 4

pin and GND, depending on noise injection.

5 ZCD 33pF high-frequency ceramic capacitor between pin 5 and GND.

8 VDD

4.7uF high-frequency ceramic capacitor between pin 8 and GND. It is

highly recommended to place this capacitor directly between the pins

of CS1501. If VDD is generated from the 2

nd

stage DC-DC, a 10 to

100 ohm resistor in series with VDD will further reduce noise.

C13

C14

C10

C15

C11

C12

3.1 Decoupling of Sensitive Pins for CS1501

PFC Controllers have certain pins that are considered noise sensitive. For the CS1501 these are:

–Pin 1 IFB

–Pin 3 IAC

– Pin 4 CS (Current Sense)

– Pin 5 ZCD (Zero Current Detect)

Care must be taken to route these signals away from noise sources. The following table shows the

recommended decoupling capacitors for each pin. Figure 5 shows good decoupling practices. These

traces must be as narrow as possible because the currents carried by them are on the orde r of 1 A. Wide

traces are prone to the capacitive coupling of noisy signals.

Table 1. Recommended Decoupling for CS1501

Figure 5. Decoupling Layout for CS1501 Sensitive Signals

5

Page 6

AN346

Pin

Number Designator Recommended Decoupling

1 NC Leave as no connect.

2 STBY

Pull high through a resistor as shown in schematic. A 1nF decoupling

capacitor to ground is recommended if the pin is not used.

3 IAC

Routing should be as clean as possible. Decoupling capacitance

should be minimal. 100pF to 1nF is acceptable.

4 FB

1nF high-frequency ceramic capacitor recommended between pin 1

and GND or VDD.

7 VDD

4.7uF high-frequency ceramic capacitor between pin 8 and GND. It is

highly recommended to place this component directly between the

pins of CS1501. If the VDD is generated from the 2

nd

stage DC-DC, a

10-100 ohm resistor in series with VDD will further reduce noise.

C13

C14

C10

C15

C11

C12

3.2 Decoupling of Sensitive Pins for CS1500

IAC (pin 3) and FB (pin 4) are noise-sensitive pins. Again, care must be taken to route t hese signals away

from noise sources. The following table shows the recommended decoupling for each pin.

Table 2. Recommended Decoupling for CS1500

Figure 6. Decoupling Layout for CS1500 Sensitive Signals

6

Page 7

AN346

3.3 Routing for ZCD and CS Pins for CS1501

The ZCD and the CS pins are the most sensitive pins on the IC. Since the sources of these signals are

close to the switching activity of the gate drive pin (GD), care must be taken to route these signals away

from noise sources. Since the ZCD pin is very close to the ground pin, which is th e retu rn current path of

the noisy gate switching currents, it is important to use a high-frequency decoupling capacitor to prevent

noise from being injected into the node. The currents of the CS pin signals can be high. As the signal

comes from the source of the power MOSFET, it can be considerably noisy.

The pros and cons of common decoupling practices are examined below. In all figures, pin 1 is at the top

left-hand corner of the image.

3.3.1 Option 1

The ground return hits the decoupling capacitor with 2 branches — one going to the GND pin and the

other going to the 33 pF capacitor. This is the least desirable since the high frequency ground current can

easily find a low impedance path through the 33 pF decoupling capacitor instead of the GND path itself.

This layout is not recommended.

Figure 7. Decoupling Option 1 — Not Recommended

3.3.2 Option 2

A larger ground plane fills the area between the ground pad, the VDD capacitor negative and the 33 pF

capacitor of the ZCD pin. This decoupling practice should work in most designs. In some rare cases where

the gate return current is large and the gate loop area is high, option 3 is preferred. If there is no space

for an extra decoupling capacitor as in option 3, the gate resistance can be increased to limit the

magnitude of high-frequency, noisy current flowing through the IC.

Figure 8. Decoupling Option 2 — Good Performance

7

Page 8

AN346

3.3.3 Option 3

This is very similar to option 2, but in this case, a 33 pF capacitor is added in parallel to a 4.7 uF VDD

decoupling capacitor. This guarantees that the ZCD decoupling capacitor cannot provide a lowimpedance path for high-frequency gate currents due to the presence of the additional VDD 33 pF

capacitor.

Option 2 and option 3 provide a clean ground for the CS pin. The ground can be continued under the IC

and the CS decoupling capacitor can be placed below the IC and decoupled close to the pin itself. This is

shown clearly in Figure 9.

Figure 9 demonstrates the best trade-off between signal integrity, manufacturability, and utility.

Figure 9. Decoupling Option 3 — Better Performance

3.3.4 Option 4

This provides the quietest layout for the ZCD pin since the ZCD capacitor is placed away from the gateGND current loop. Because the ZCD current is low, the distance between the ZCD ground capacitor and

the ground pin of the IC does not affect signal integrity.

The ground return of the CS pin should be decoupled away from the ground return of the ZCD pin. In this

arrangement, it is reasonable to use the ZCD ground region for decoupling the remainder of the sense

signals, such as IAC, IFB, and CS. The trace running from the back side should be as wide as possible

to ensure low-impedance.

Figure 10. Decoupling Option 4 — Best Performance

8

Loading...

Loading...