Page 1

AN364

Application Note

Design Guide for a CS1610 and CS1611

Dimmer-Compatible SSL Circuit

1 Overview of the CS1610/11

The CS1610 and CS1611 are digital control ICs engineered to deliver a high-efficiency, cost-effective, flicker-free,

phase-dimmable, solid-state lighting (SSL) solution for the incandescent lamp replacement market. The CS1610/11

is designed to control a quasi-resonant flyback topology. The CS1610 and CS1611 are designed for 120VAC and

230VAC line voltage applications, respectively.

The CS1610/11 integrates a critical conduction mode (CRM) boost converter that provides power factor correction

and dimmer compatibility with a constant output current, quasi-resonant second stage. An adaptive dimmer

compatibility algorithm controls the boost stage and dimmer compatibility operation mode to enable flicker-free

operation to 2% output current with leading-edge, trailing-edge, and digital dimmers (dimmers with an integrated

power supply).

1.1 Features

• Best-in-Class Dimmer Compatibility

- Leading-edge (TRIAC) Dimmers

- Trailing-edge Dimmers

- Digital Dimmers (with Integrated Power Supply)

• Up to 90% Efficiency

• Flicker-free Dimming

• 0% Minimum Dimming Level

• Quasi-resonant Second Stage with Constant-current Output

- Flyback for 1610/ 11

• Fast Startup

• Tight LED Current Regulation: Better than ±5%

• Primary-side Regulation (PSR)

• >0.9 Power Factor

• IEC-61000-3-2 Compliant

• Soft Start

• Protections:

- Output Open/Short

- Current-sense Resistor Open /Short

- External Overtemperature Using NTC

Cirrus Logic, Inc.

http://www.cirrus.com

Copyright Cirrus Logic, Inc. 2012

(All Rights Reserved)

AUG’12

AN364REV3

Page 2

AN364

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative. To find the one nearest to you

go to www.cirrus.com

IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject

to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant

information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale

supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus

for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third

parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights,

copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives

consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR

USE IN PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK

AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER

OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE,

TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, the Cirrus Logic logo designs, EXL Core, the EXL Core logo design, TruDim, and the TruDim logo design are trademarks of Cirrus Logic, Inc.

All other brand and product names in this document may be trademarks or service marks of their respective owners.

IMPORTANT SAFETY INSTRUCTIONS

Read and follow all safety instructions prior to using this demonstration board.

This Engineering Evaluation Unit or Demonstration Board must only be used for assessing IC performance in a

laboratory setting. This product is not intended for any other use or incorporation into products for sale.

This product must only be used by qualified technicians or professionals who are trained in the safety procedures

associated with the use of demonstration boards.

Risk of Electric Shock

• The direct connection to the AC power line and the open and unprotected boards present a serious risk of electric

shock and can cause serious injury or death. Extreme caution needs to be exercised while handling this board.

• Avoid contact with the exposed conductor or terminals of components on the board. High voltage is present on

exposed conductor and it may be present on terminals of any components directly or indirectly connected to the AC

line.

• Dangerous voltages and/or currents may be internally generated and accessible at various points across the board.

• Charged capacitors store high voltage, even after the circuit has been disconnected from the AC line.

• Make sure that the power source is off before wiring any connection. Make sure that all connectors are well

connected before the power source is on.

• Follow all laboratory safety procedures established by your employer and relevant safety regulations and guidelines,

such as the ones listed under, OSHA General Industry Regulations - Subpart S and NFPA 70E.

Suitable eye protection must be worn when working with or around demonstration boards. Always

comply with your employer’s policies regarding the use of personal protective equipment.

All components and metallic parts may be extremely hot to touch when electrically active.

2 AN364REV3

Page 3

AN364

2 Introduction

This application note is a guide to designing a Solid State Lighting (SSL) LED lamp circuit using Cirrus Logic's

CS1610/11. The first half of the document presents a step-by-step design procedure for calculating the required

components for each stage of the system. The second half of the document supports the design effort by showing

an example of a CS1611 design. The CS1611 example will be based on the Cirrus Logic CRD1611-8W reference

design. See the CS1610/11/12/13 TRIAC Dimmable LED Driver IC data sheet for more details about the CS1610/11

IC. See the CRD1610-8W 8 Watt Reference Design and CRD1611-8W 8 Watt Reference Design data sheets for

more details regarding the reference design.

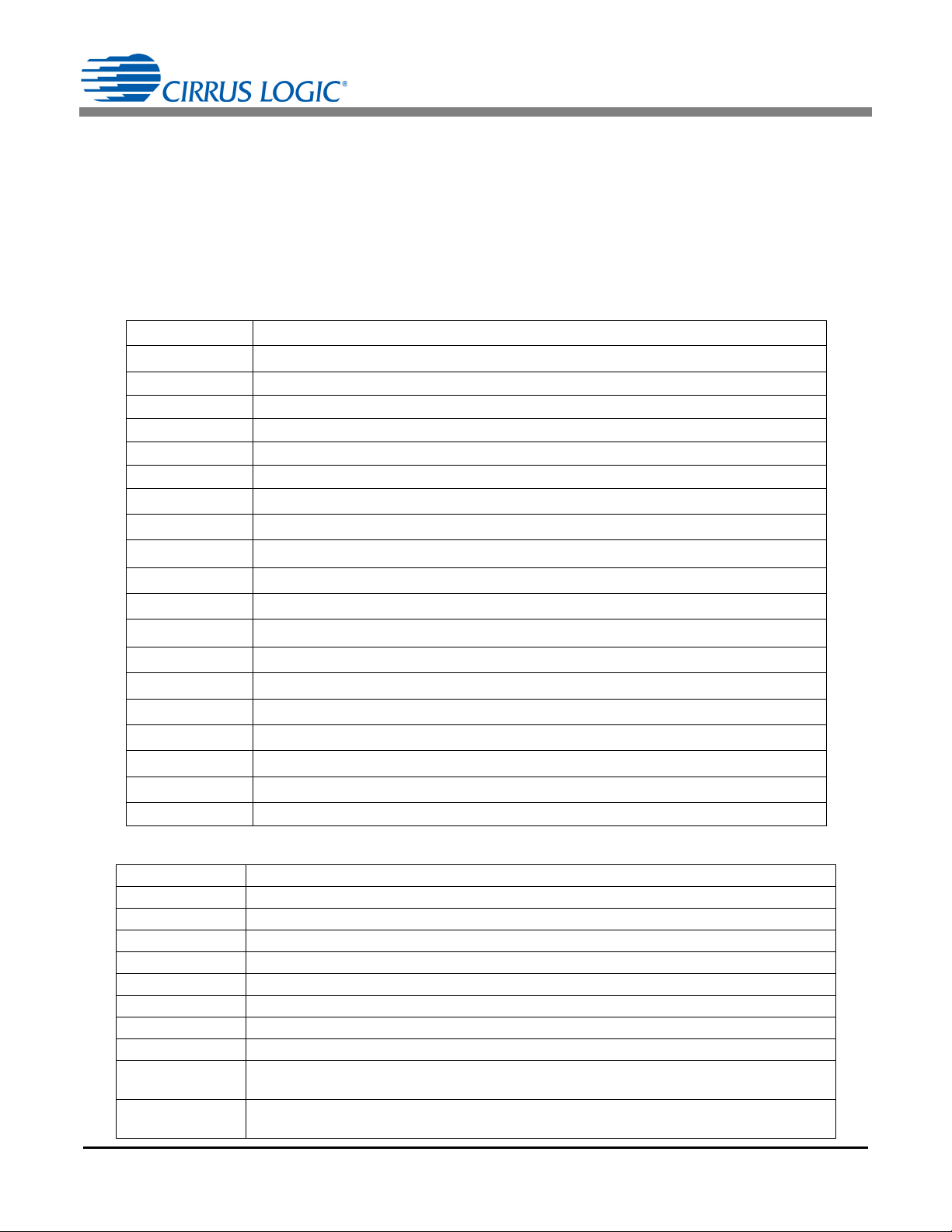

2.1 Definition of Symbols

Symbol Description

F

sw

TT Switching period

T1 Primary FET ‘ON’ time

T2 Secondary rectifier diode conduction time

T3 Time when the FET and diode are OFF

D Duty ratio (T1/TT)

V

Reflected

V

CLAMP

I

PK(FB)

R

FBGAIN

R

Sense

I

PK(BST)

L

P

L

BST

V

BST

N

V

OUT

P

OUT

Power stage efficiency

Switching frequency

Voltage across secondary winding reflected onto primary

Primary clamping voltage above boost output voltage (V

Peak current in primary-side FET

A resistor used to program the switching period TT

Primary current sense resistor

Maximum boost inductor current

Flyback transformer primary inductance

Boost inductance

Boost output voltage

Flyback transformer turns ratio N

Secondary output voltage DC = the LED string supply voltage

Load power = Power to the LED string

P/NS

BST

)

2.2 Definition of Acronyms

Acronym Description

PFC Power Factor Correction

OVP Overvoltage Protection

eOTP External Overtemperature Protection

OCP Overcurrent Protection

iOTP Internal Overtemperature Protection

OLP Open Loop Protection

LED Light Emitting Diode

TXF Transformer

TRIAC

SSL

AN364REV3 3

TRIode for Alternating Current, which is an electronic component that can conduct current in

either direction when it is triggered. It is formally called a bidirectional triode thyristor.

Solid State Lighting. Refers to a type of lighting that uses semiconductor LEDs as a source of

illumination rather than electrical filaments, plasma, or gas.

Page 4

AN364

T1

D3

LED +

LED -

Z2

L1

L3

R8

R11

R3

R7

R1

R2

Q3

L2

Z1

C2

D7

D6

Q1

R17R13

Q2

D5

R18

NTC

R14

R15

R22

R23

Q4

R21

R19

R9

BR1

F1

R12

D8

R4

CS1610 /11

FBGAIN

IAC

FBAUX

BSTOUT

GNDSGNDIPK

CLAMP

GD

FBSEN SE

eOTP

VDD

SOURCE

CY

D2

L

N

AC Main s

D4

R10

R16

R6

R20

R5

D1

BSTAUX

R24

Boost

Gate Bias

Steady State

Supply

Active

Clamp

FlybackEMI

C11

C8 C10

C9

C7

C6

C5

C4

C3

C1

C12

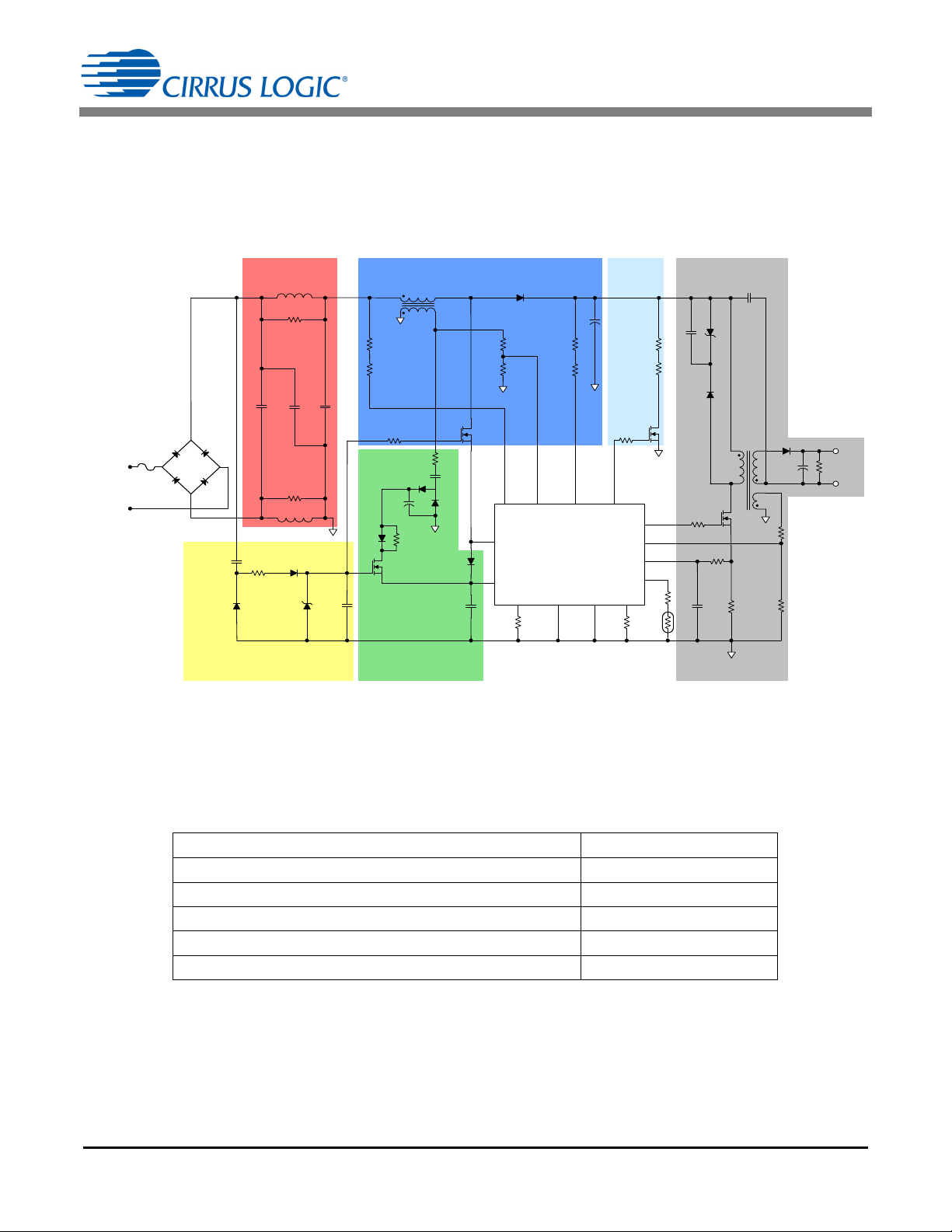

Figure 1. Block Diagram of CS1610/11 Design

3 Design Process

The design process for a two-stage power converter system can be partitioned into six circuit blocks (see Figure 1).

The AC line voltage is passed through an electromagnetic interference (EMI) filter to suppress conducted interference found on the power line. The output of the EMI filter is then converted to the desired DC output by a boostflyback converter. The power converter system includes the Gate Bias, Steady State Supply, and Active Clamp support circuitry.

3.1 Operating Parameters

To initiate the design procedure, a set of operating parameters are required. Operating parameters required

for the analytical process are outlined in the table below. Parameters critical to the overall design, but not

specifically addressed in this document, include: EMI compliance, efficiency, form factor, layout, and operating

temperature.

Output Power

AC line Input Voltage

Output Voltage

Load Current

Parameters Symbol

Maximum Switching Frequency*

4 AN364REV3

* Increasing Fsw may reduce the size of the magnetics but increase switching losses in the FET.

P

OUT

V

IN

V

OUT

I

OUT

F

sw(max)

Page 5

3.2 Overview of Design Steps

The CS1610/11 LED driver IC controls a power converter system that has two distinct power conversion

stages. The IC requires supporting circuitry to provide a steady state power supply with gate bias, a clamp

circuit, and EMI filtering. The recommended design process is outlined below:

1. Start with the flyback stage.

2. Design for full power at minimum V

operating parameters.

3. Optimize the flyback stage through validation and design iteration.

4. Base the boost stage design on the power requirement of the flyback stage.

5. Start the boost stage design in No-dimmer Mode.

6. Determine the peak current in the boost inductor, I

7. Determine a boost inductance, L

Consider the impact on the EMI.

8. Pick the boost FET based on peak current ratings.

9. Choose the power supply components.

10.Complete the non-power-converting circuitry: ZCD, OVP, eOTP, Clamp Circuit, Charge Pumps, and Bias

Circuits.

11. Design the EMI filter.

12.Lay out the PCB.

. Note that any design may require design trade-offs for different

BST

PK(BST)

, that adjusts the switching frequency within the defined range.

BST

.

AN364

The flyback stage design is carried out at the full brightness (full load) point. To achieve an optimal solution,

several iterations of the design process may be required. The EMI filter is particularly critical because there is

a small degree of freedom in selecting the EMI component values that meet the requirements below:

• Comply with EMI regulations

• Achieve compatibility with the largest variety of dimmers

• Smooth dimming, no flicker with a variable number of identical lamps controlled by one dimmer

AN364REV3 5

Page 6

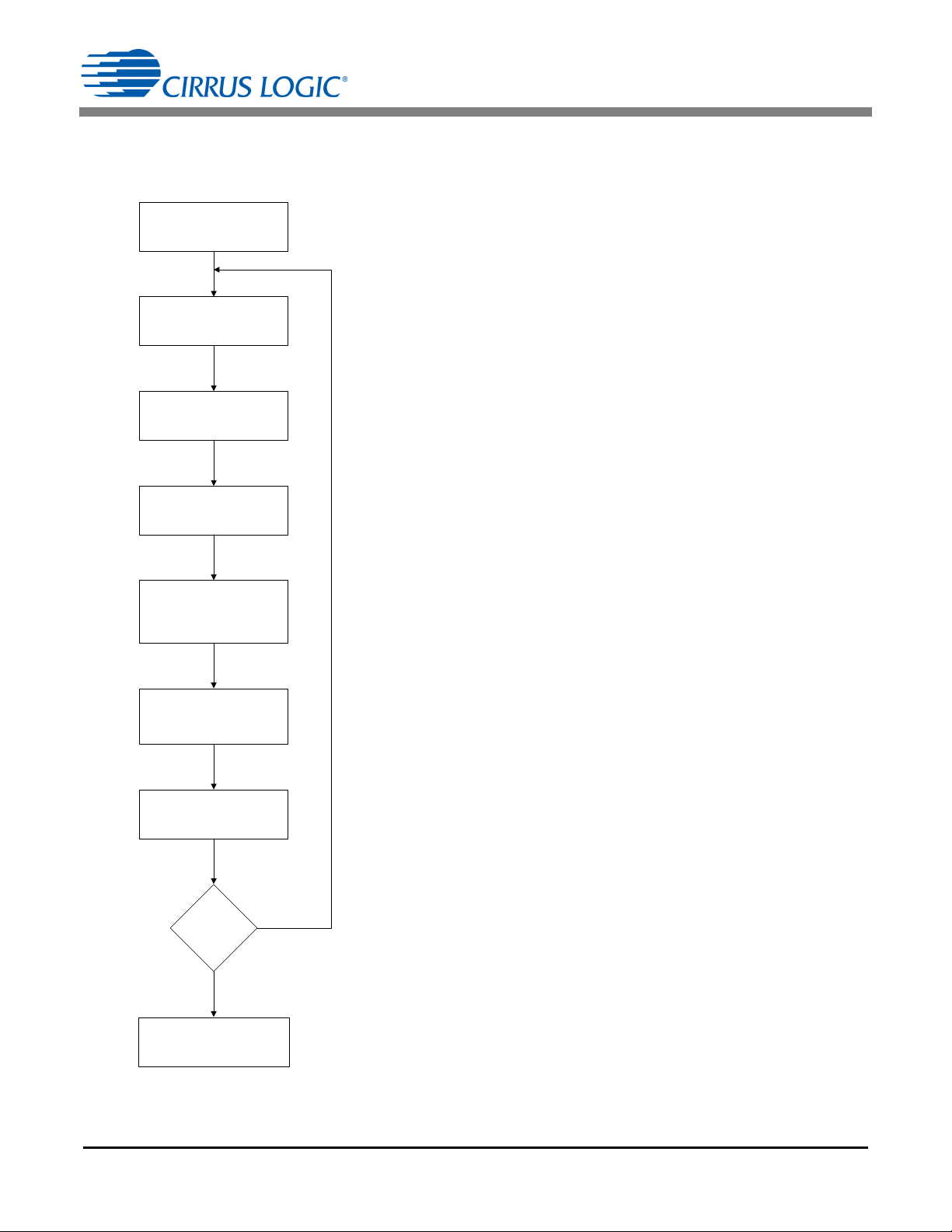

3.3 Flyback Stage Design

Flyback Specification

Determine N, Fsw,

V

Refle cted

, and V

CLAMP

Estimate T3

Calculate TT

fb

Calculate R

Sense

,

R

FBG AIN

, and Primary

Inductance

R

Sense,RFBG AIN

Fit?

Yes

No

Calculate T1,

T2, and I

PK(FB)

Calculate RMS Current

and Output Capacitor

Transformer Core

Steps for the Flyback Design

1. Set boost output voltage V

BST

.

2. Select a MOSFET that aligns with the quality standards of

the designer’s company.

3. Determine the transformer turns ratio from the

V

BST

, FET

voltage, and reflected voltage V

Reflected

.

4. Use the nominal switching frequency and an initial

estimate for time T3 to determine the value of time TT at

full brightness.

5. Use V

BST

, TT, and V

Reflected

to determine time T1 and T2.

6. Use time T2 and TT, turns ratio N and load current to

determine the value of peak primary current I

PK(FB)

.

7. Use I

PK(FB)

to determine R

Sense

.

8. Calculate the primary side inductance using time T1.

9. Calculate flyback gain resistor R

FBGAIN

using full load

conditions. Ensure linearity of the load versus the dim

curve.

10. Calculate primary and secondary RMS currents using

I

PK(FB)

and duty cycle.

11. Select an output capacitor.

12. Determine the flyback transformer specifications.

13. Determine if the flyback transformer fits into specified form

factor after designing and constructing flyback transformer.

Repeat steps 3 to 12 until form factor criteria is met.

14. Refine the circuit using the final flyback transformer

design.

15. Validate that the system meets the operating criteria.

Figure 2 illustrates the steps for designing the flyback stage.

AN364

6 AN364REV3

Figure 2. Flyback Stage Design

Page 7

AN364

V

Drain maxVBST maxVCLAMP max

+=

[Eq. 1]

V

OvershootVCLAMPVReflecteed

–=

[Eq. 2]

Overshoot is a brief condition

above V

Reflected

, required to

quickly dissipate the energy stored

in the transformer leakage

inductance.

During this time, the primary

current is kept from transferring to

the secondary, siphoning energy

from the load to the clamp zener

(snubber).

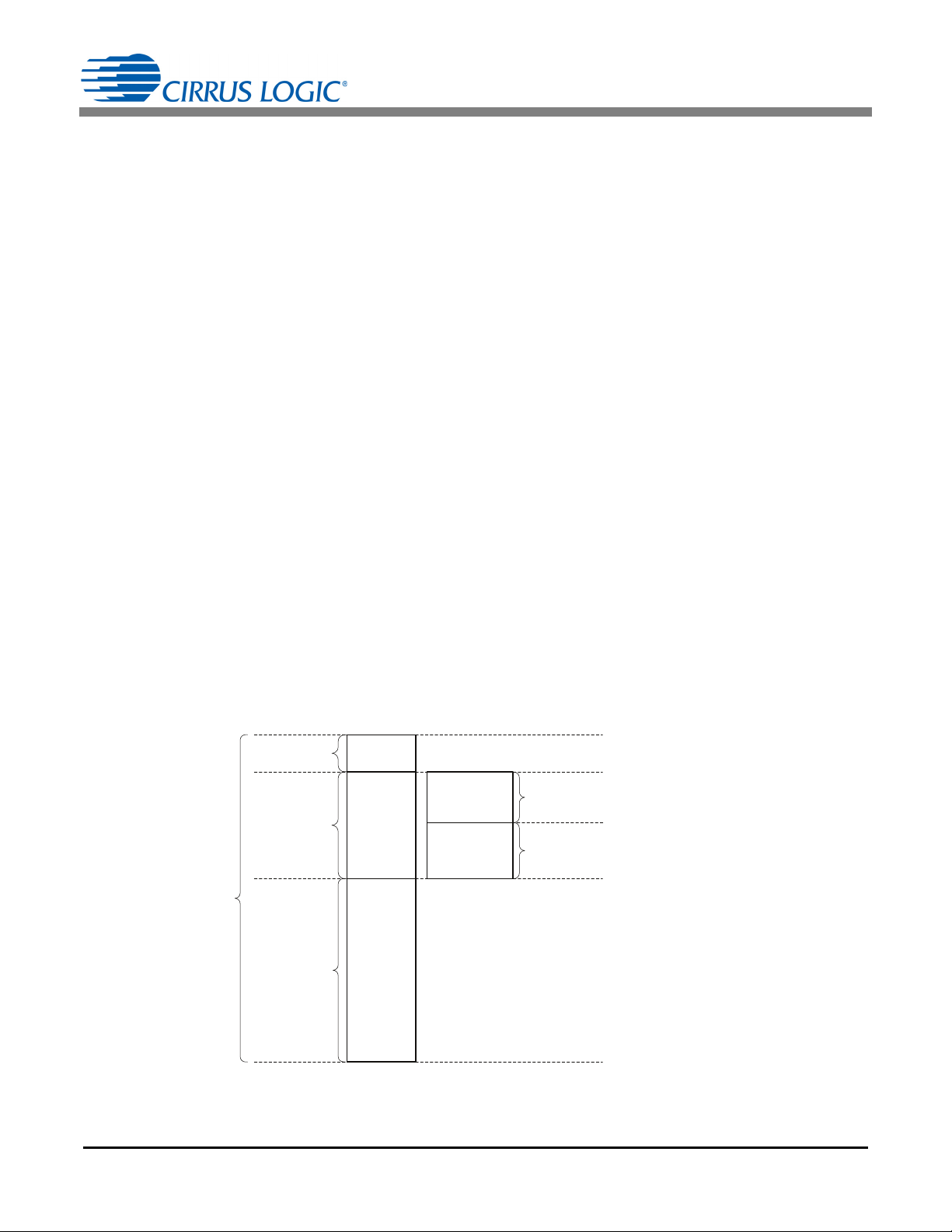

Figure 3. FET Breakdown Voltage

V

Margin

V

CLAMP

V

BST

V

Overshoot

V

Reflected

ET Breakdown

Voltage Rating

Clamp

Voltage

Boost Output

Voltage

Margin

Reflected

Voltage

Overshoot

Voltage

Step 1) Select a Value for Boost Output Voltage

The value of the boost output voltage, V

The maximum V

voltage, V

BST

BST(max)

requirement within economical constraints.

V

is determined by an internal parameter and changes slightly depending on the type of dimmer detected.

BST

With sense resistors R7, R8, R14, and R15 set to 1.5M, the resulting V

system. For a 120V system, sense resistors R7, R8, R14, and R15 are set to 750k each, and the resulting

V

is approximately 200V. V

BST

each half line-cycle. V

droops to its lowest value towards the end of each half line-cycle until the boosting

BST

is regulated by charging the boost output capacitor to its nominal value

BST

process starts again in the next half line-cycle.

Step 2) Select an Appropriate FET

Determine the FET breakdown voltage, V

voltage, V

Drain(max)

, is calculated using Equation 1.

The ringing associated with the transformer leakage inductance usually does not have enough energy to

cause a destructive avalanche breakdown. Voltages closely approaching the FET breakdown voltage are

acceptable.

Ideally, V

Reflected

should have nearly the same value as V

duty cycle optimizes the transformer efficiency. Alternatively, V

to rapidly discharge the energy stored in the transformer leakage inductance.

The FET breakdown voltage is constrained by cost and performance. A compromise must be reached in

partitioning voltage between V

divide V

CLAMP

into V

Reflected

, V

BST

CLAMP

and a reasonable overshoot voltage portion, V

The losses caused by the leakage inductance are inversely proportional to V

Equation 2.

, must be greater than the maximum input AC line voltage peak.

BST

, should be kept as low as possible to help maintain the FET breakdown

is approximately 405V for a 230V

BST

Breakdown

, and V

, and reflected voltage, V

because operating the transformer near 50%

BST

CLAMP

. A second compromise will then determine how to

Margin

Reflected

should be much greater than V

Overshoot

. The FET maximum drain

.

Overshoot

, which is determined by

Reflected

AN364REV3 7

F

Page 8

AN364

V

Breakdown

V

BSTVReflected

V+

CLAMP

V

Reflected

– V

Minarg

++=

[Eq. 3]

N

V

Reflected

V

OUT max

----------------------------=

[Eq. 4]

T1 T2+

1

F

sw

---------

T3–=

[Eq. 5]

T1

T2

-------

V

Reflected

V

BST

--------------------------=

[Eq. 6]

For optimum efficiency, the increase in transformer losses (created by an uneven duty cycle) must balance the

reduction of the losses caused by discharging the leakage inductance (obtained by increasing the overshoot

voltage). Equation 3 is used to balance all voltages contributing to the FET voltage drain and source.

where

V

Overshoot

Step 3) Determine the Flyback Transformer Turns Ratio

Select a turns ratio based on the output voltage, V

where

V

OUT(max)

Step 4) Select the Full Brightness Switching Frequency

The CS1611 maximum switching frequency is 200kHz. Test results indicate that optimal performance is

obtained in the range of 75kHz to 120kHz. Higher frequencies allow the use of smaller magnetics, but

switching losses increase. Transformer size versus switching frequency is limited by designs that require

isolation. Selecting too low a full brightness switching frequency risks impairing dimmer compatibility while also

allowing the minimum frequency to drop into the audible range.

From the full brightness frequency, determine the value of (T1 +T2) using Equation 5.

= V

CLAMP

- V

Reflected

OUT

, and V

= the maximum LED string forward voltage V

Reflected

at full current plus the rectifying diode voltage VF.

OUT

using Equation 4.

where

T3 is 1/2 the transformer resonant period

The transformer primary inductance resonates with the total parasitic capacitance of the drain node. For initial

calculations, T3 is estimated as 1s and must be measured for final accuracy.

Step 5) Determine the Flyback Nominal Timing T1 and T2

From the reflected voltage and the turns ratio, determine T1 and T2. Equation 6 ensures zero DC voltage

across the transformer T1 magnetizing inductance.

8 AN364REV3

Page 9

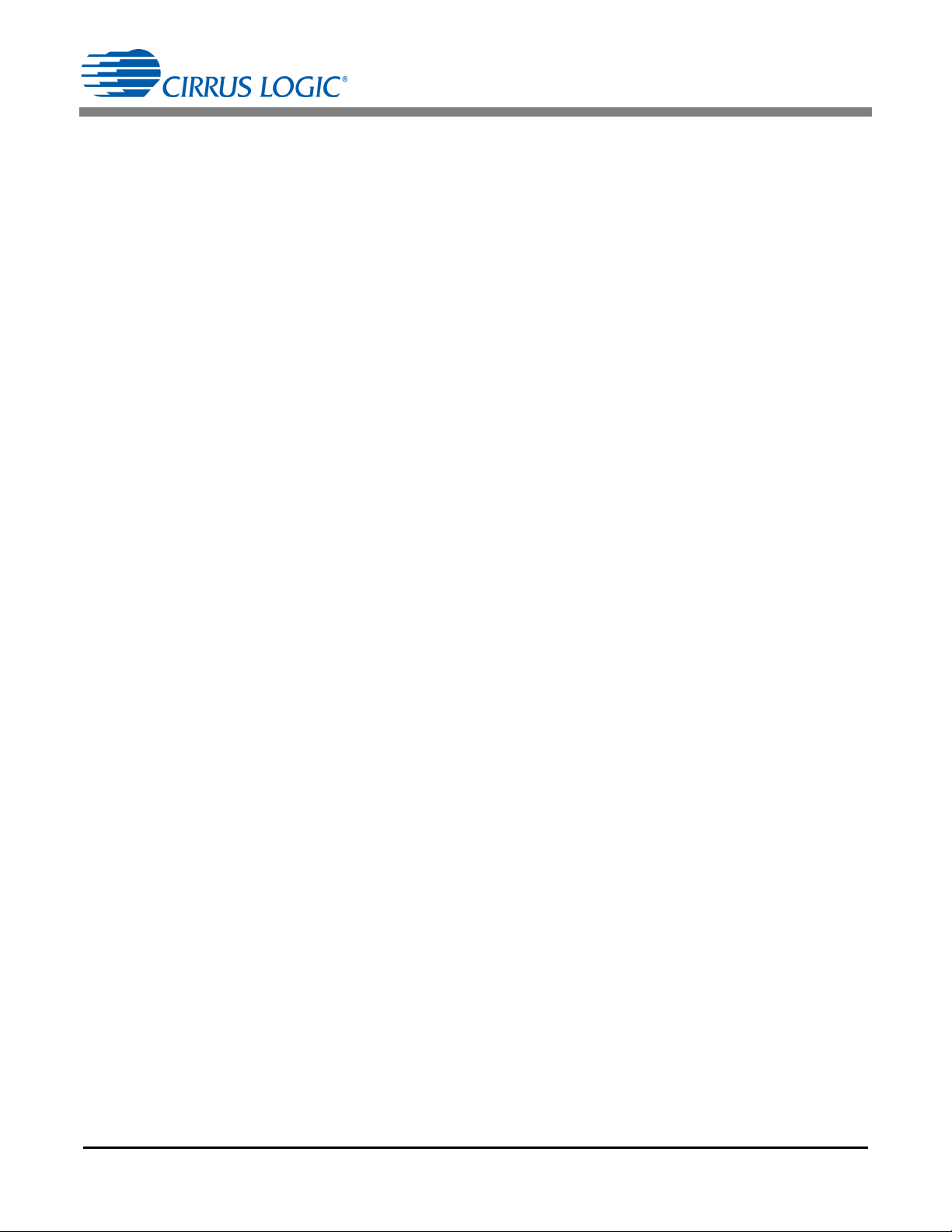

Figure 4 illustrates the switching frequency used in the system design.

t

i(t)

T1 T2

TT

No Curr ent

T3

Peak Primary Current, I

PK(FB)

Primar y

Current

Secondary

Current

Figure 4. Timing Diagram of T1, T2, T3, and TT

T1

1

F

sw

--------- T 3–

V

Reflected

V

ReflectedVBST

+

----------------------------------------------------

=

[Eq. 7]

T2

1

F

sw

--------- T 3–

V

BST

V

ReflectedVBST

+

----------------------------------------------------

=

[Eq. 8]

I

PK FB

2P

OUT max

TT

fb

V

BST

T1fb

----------------------------------------------

=

[Eq. 9]

R

Sense

1.4V

I

PK FB

------------------=

[Eq. 10]

L

P

V

BST

T1

I

PK FB

---------------------------

=

[Eq. 11]

Solve for T1 and T2 using Equation 7 and Equation 8:

AN364

Period T1 is limited to a maximum duration of 8.8s by the IC algorithm. Verify that period T1 at full power is

less that 7.8s, leaving sufficient time for a probe cycle, which requires a slightly longer T1 period.

Step 6) Calculate Peak Current on the Flyback Primary-side

Calculate I

using Equation 9:

PK(FB)

where

TT

= switching period at full brightness (full load condition)

fb

T1

= period T1 at full brightness (full load condition)

fb

Step 7) Calculate R

Calculate sense resistor R

Sense

Sense

(R23)

(R23) for flyback using Equation 10:

where

R23 = R

Sense

in

Step 8) Calculate the Flyback Primary-side Inductance

AN364REV3 9

Page 10

AN364

R

FBGAIN

4M

TT

fb

T2

fb

----------- -

128

64–

----------------------------------------------

=

[Eq. 12]

I

RMSIPK FB

T

current

3TT

--------------------

=

[Eq. 13]

I

PK FB

V

BST

T1

L

P

--------------------------------

=

[Eq. 14]

T2

I

PK FBLP

NV

O

-------------------------------

=

[Eq. 15]

Step 9) Calculate R

FBGAIN

Use Equation 12 to calculate the flyback gain resistor, R

(R17)

FBGAIN

(R17).

where

R17 = R

TT

T2

FBGAIN

= switching period TT at full brightness (full load condition)

fb

= period T2 at full brightness (full load condition)

fb

in

Step 10) Determine the RMS Current in the Winding

Determining RMS current I

time when the current is present in the winding, T

is necessary to properly define the wire size. Current I

RMS

. Use Equation 13 to calculate I

current

is dependent on the

RMS

:

RMS

where

T

current

T

current

= T1 when calculating the I

= T2 when calculating the I

current in the primary winding

RMS

current in the secondary winding

RMS

TT = T1+T2+T3 (see Figure 4)

The factor 3 accounts for the current triangular shape.

Step 11) Determine Output Capacitor

The flyback output capacitor, which is usually electrolytic, must provide a low impedance to the switching

frequency. When using an electrolytic capacitor, the choice is based on its ability to carry the ripple current so

that it provides a long service life. A capacitor that fulfills the ripple, voltage, temperature and life requirements

results in a capacitor with a large capacitance that is often much greater than what is necessary to smooth the

load current. In flyback applications, the voltage ripple across the output electrolytic capacitor is determined

mostly by the ESR rather than the reactance.

Step 12) Flyback Transformer Specification

This step is the first iteration of the transformer design. Due to design constraints, the following requirements

must be met:

• The core must be big enough to fit the windings.

• The number of turns required must fit in the bobbin, along with insulation material.

• The transformer must meet insulation, creepage, and safety requirements.

• The finished transformer must not overheat in the environment.

• Magnetic and geometric constraints may not yield the exact value of L

Once the first iteration of the design is done, calculate the new I

using the actual value of L

, as shown in Equation 14.

P

PK(FB)

and N calculated.

P

to maintain the same T1 time as earlier

Calculate the new T2 value using the new I

and N, as shown in Equation 15:

PK(FB)

10 AN364REV3

Page 11

AN364

FB

Gain

TT

fb

T2

fb

------------=

[Eq. 16]

1FB

Gain

2.5

[Eq. 17]

T2fbTTfb2.5 T 2

fb

0V

Reflected

1.5 V

BST

15.6k R

FBGAIN

62.5k

[Eq. 18]

First Valley

Flyback FET

Voltage

V

CLAM P

V

BST

V

Reflec ted

Figure 5. Switching Waveform of Flyback FET Drain

Step 13) Circuit Adjustments

Circuit adjustments are required after the transformer has been designed and constructed. Recalculate

R

FBGAIN

Flyback gain FB

FB

which has the following implications:

using Equation 12.

is an internal constant that is programmable by R

Gain

is used in the flyback algorithm to control switching period TT. The range of FB

Gain

FBGAIN.

is limited to:

Gain

If FB

situation, a high I

the FET breakdown voltage. If the value of FB

range of V

lower I

is close to 1, the duty cycle will be low, which will cause a low reflected voltage V

Gain

PK(FB)

to (1.5V

BST

, requiring a higher FET breakdown voltage.

current is required to reach full brightness, and the only advantage would be to lower

PK(FB)

), resulting in a duty cycle that is between 50% and 60%. This setting causes a

BST

were in the range of 2 to 2.5, then V

Gain

The duration of T1 is determined by the time it takes the primary current to reach I

Reflected

Reflected

, and the duration of

PK(FB)

. In this

would be in the

T2 is dependent on the time it takes the secondary current to reach 0. To achieve the best full power efficiency,

adjust switching period TT, which will start a new switching cycle after the flyback FET drain voltage has

reached the valley (see Figure 5). Once the flyback transformer is built, R

TT to allow it to cycle at the valley. Adjusting R

FBGAIN

changes the switching frequency slightly.

can be adjusted to change

FBGAIN

Although R

could be used to control the load current, its primary purpose is to control the valley-

FBGAIN

switching range. It is recommended to adjust the load current by changing primary current sense resistor

R

, which is connected to the FBSENSE pin of the IC and then use R

Sense

Step 14) Recalculate R

The flyback primary current is controlled by comparing the voltage across R

internal threshold of 1.4V. To guarantee the rated LED current under worst-case conditions, when the LED

string has maximum voltage, the V

R

to obtain the nominal LED current, then adjust R

Sense

AN364REV3 11

Sense

is at its minimum point and R

BST

to hit the valley.

FBGAIN

FBGAIN

is at its highest tolerance. Adjust

Sense

to control valley switching.

at pin FBSENSE to an

Sense

Page 12

AN364

5% Light

100% Light

(F ull Brigh t)

F

sw(fb)

>F

MIN

Switching Frequency, F

sw

Further peak current reduction

and frequency increase

still reducing aver age curr ent

Increasing T2 at reduced peak current

CRM with valley switching region. Reducing peak

current for ces a frequency incr ease.

Increasing T2 at minimum peak curr ent

Dimming

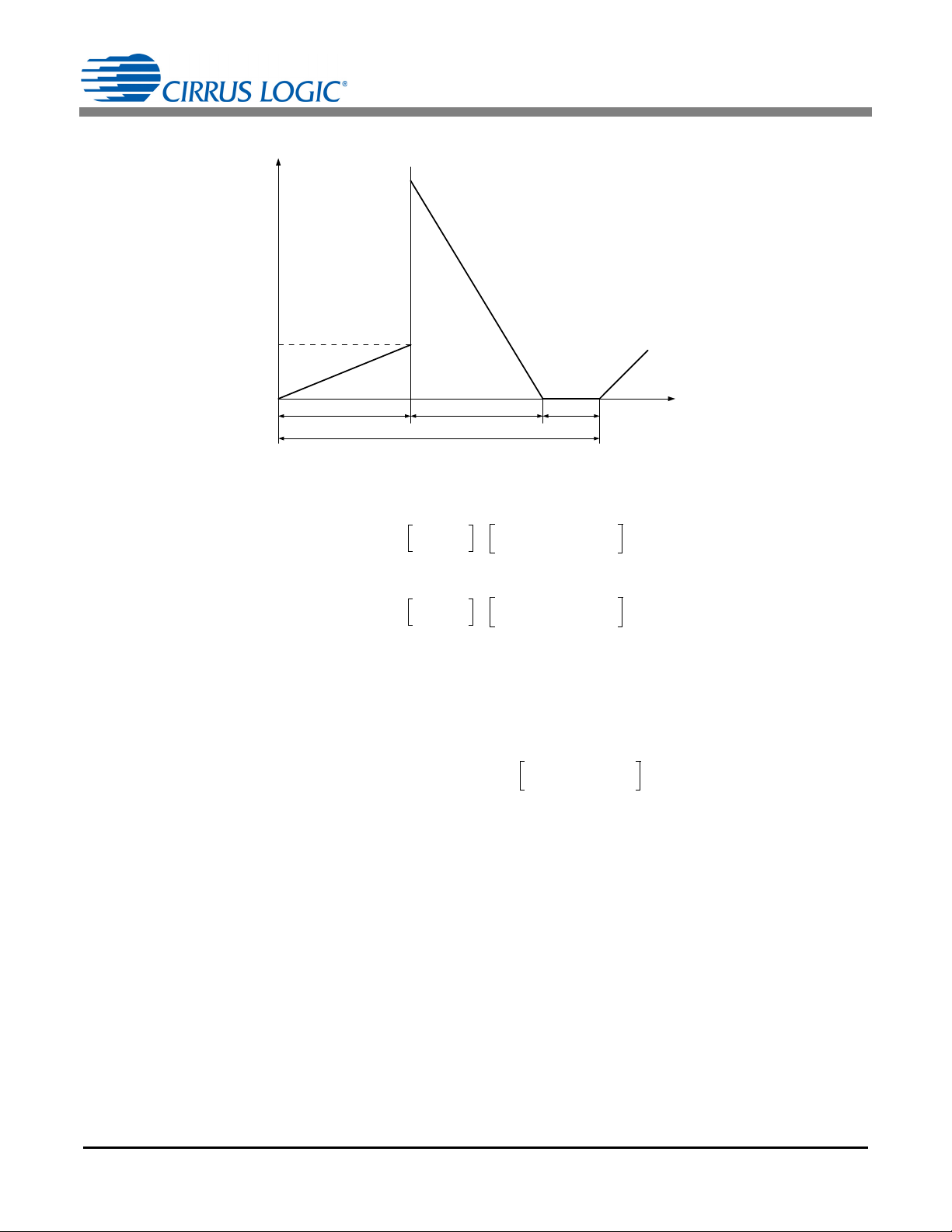

Figure 6. Flyback Switching Frequency Profile vs. Dimming

Notes on Circuit Fine Tuning

• Going beyond the R

• R

Sense

and R

FBGAIN

are frequently adjusted simultaneously to reach the desired operating point.

FBGAIN

• The optimized final design will have a slightly different switching frequency variation than the first design

iteration.

• When the load is increased or decreased by 10%, then R

than 10%, respectively. Adjusting R

‘ON’ hits the resonant voltage valley.

• Figure 6 illustrates a typical frequency profile with dimming. This is only one typical profile. The breakpoints

can move depending on various tolerances and specific design choices.

limitation will not have any further effect on the design.

needs to be decreased or increased by less

is required when the load changes so that the flyback FET turn

FBGAIN

Sense

At this point, full power and valley switching are close to the target frequency. Further adjustment of the

frequency is done by changing flyback transformer primary inductance L

. The core gap can be changed for

P

small inductance variations.

3.4 Boost Stage Design

The design process for the boost stage is outlined below:

1. Determine I

2. Determine Boost Inductor Specifications

3. Calculate Boost Input and Output Capacitors

The boost stage is designed in No-dimmer Mode, which has a considerable degree of freedom in its design

PK(BST)

parameters. For the boost stage to operate in dimmer mode and with the largest variety of dimmers, the design

is constrained within a more limited set of parameters. Even in No-dimmer Mode, the several operating states

of the boost stage leave an exclusively formula-based design impractical.

12 AN364REV3

and a tentative I

PK(BST)

resistor value R

(R13)

IPK

Page 13

AN364

I

PK BST

3.64 PIN

V

RMS

-------------------------- -

=

[Eq. 19]

Step 15) Determine I

PK(BST)

, I

SAT

, and R

IPK

(R13)

The boost stage peak current has two distinct values:

• I

PK(BST)

is related to input power PIN. The boost inductor current reaches this value during a substantial

portion of the line-cycle, affecting the RMS value of the inductor and line current.

• I

is a constant value of 0.6 A and is independent of the power level. I

SAT

dimmer TRIAC in the conduction mode. I

is a brief duration that immediately follows the dimmer firing

SAT

is necessary to maintain the

SAT

and has a minimal impact on RMS current and its heating effects. The boost inductor must be capable of

carrying the current I

without saturating.

SAT

The factor 3.64 accounts for a factor of 2 due to the triangular waveform, a factor of 1.41 due to voltage

sinusoidal shape, and a factor of 1.29 derived by simulation accounting for the line current envelope profile.

The current envelope profile approximates a sine wave in a stepped fashion according to the following

conditional rules:

• IF V

• IF V

• IF 45° < Phase < 135° AND V

• IF 45° < Phase < 135° AND V

• IF V

Boost output voltage V

< 60V THEN I

LINE

> 60V AND Phase > 20° THEN the boost inductor peak current equals 0.75 I

LINE

< 60V OR Phase > 160° THEN I

LINE

PK(BST)

is regulated by controlling the time when the current is held equal to I

BST

equals 0

< V

BST

> V

BST

THEN the inductor current peak equals I

MAX

THEN the inductor current peak equals 0.75 I

MAX

PK(BST)

equals 0

PK(BST)

PK(BST)

PK(BST)

PK(BST)

during

the central portion of the period between 45° and 135°.

Figure 7 shows the inductor peak current envelope and the AC line current waveform at nominal voltage in Nodimmer Mode.

AN364REV3 13

Page 14

AN364

0.00

0.02

0.04

0.06

0.08

0.10

0.12

0.14

0 15 30 45 60 75 90 105 120 135 150 165 180

Current (A)

Phase Angle (°)

AC Line Current

Inductor Peak Current

Figure 7. Current vs Phase Angle

[Eq. 20]

R

IPK

15.625 103V

I

PK BST

------------------------------------------ -

=

The AC line current does not follow the inductor peak current envelope because the circuit operates in CRM

and DCM. The switching frequency and duty cycle changes across the AC line phase resulting in a changing

average value after the EMI filter smoothing.

Once I

PK(BST)

is determined, R

must be calculated. I

IPK

drive current sink, which is equal to I

PK(BST)

. See Equation 20.

PK(BST)

sets the maximum value for the internal source

During circuit adjustment, connect an electronic load in CV mode for testing and clamp protection. Set the

electronic load so that the boost output voltage is 425V for a 230V system or 215V for a 120V system.

Measure switching frequency at a fixed V

voltage. Adjust I

rect

PK(BST)

to obtain the desired waveform at the mid

voltage, as shown in Equation 7.

Step 16) Boost Inductor Specifications

The CS1610/11 controls I

PK(BST)

and keeps the boost stage operating in CRM. Boost inductance L

controls the average switching frequency. The instantaneous frequency changes to meet the I

by the controller and the duty cycle imposed by the CRM/DCM algorithm.

The boost inductor should be designed for 600mA at 3000 Gauss. For a given input voltage design, the product

of L

product, and divide the product by P

BST

P

is constant. Choose the frequency range on Figure 8 to find the corresponding L

IN

to obtain L

IN

BST

.

14 AN364REV3

PK(BST)

BST

only

BST

imposed

P

IN

Page 15

AN364

0

10

20

30

40

50

60

70

80

90

100

110

120

130

140

10 20 30 40 50 60 70 80 90 100 110 120 130 140

120V Min Freq

120V Max Freq

230V Min Freq

230V Max Freq

Power Multiplied by Inductance (Watts Multiplied by mH)

Switching Frequency (kHz)

Figure 8. Switching Frequency vs Power Inductance

The frequency range should be as high as possible without exceeding 75kHz. This strategy will keep the

fundamental and second harmonic below the 150kHz EMI requirements.

In most low-power designs, the boost inductor peak current I

PK(BST)

Specify the boost inductor turns such that the core will reach 3000Gauss when the current equals 600 mA. To

protect against runaway, set the artificial load to a constant voltage to achieve nominal

value of R

to obtain nominal boost output current I

IPK

BST(nominal)

Measure the switching frequency in the high current region in the 45° to 90° AC phase angle range. Adjust the

boost inductor value to determine the desired frequency. Adjustments to the inductor value are made by

changing the gap. Increasing the gap is always safe, but reducing the gap may saturate the core. It may be

beneficial to redesign the boost inductor if changes to the inductor gap are greater than 20%.

Step 17) Determine Boost Output Capacitor

is much higher than the RMS value.

.

V

, then adjust the

BST

The boost stage output capacitor is also the flyback stage input capacitor. Determine the size of the boost

output capacitor using the following points:

• For a 120V line input system, capacitor C4 > 2F/Watt of input power

• For a 230V line input system, capacitor C4 > 0.5F/Watt of input power

Proper capacitor size is required to ensure that the following dimmer algorithms execute properly:

• Transition CCM to CRM properly

• No erroneous CCM events

• No CCM operation with trailing-edge dimmers

• No CCM operation in No-dimmer Mode

• Boost and flyback stages loop stability

AN364REV3 15

Page 16

Step 18) Determine Boost Input Capacitor

V

DD

VZ1V

Q2 thVD6

––=

[Eq. 21]

V

DD

VZ1V

Q1 th

–VZ1V

Q2 thVD6

––=

[Eq. 22]

N

P

N

AUX

--------------

V

BST

22

--------------=

[Eq. 23]

To be compatible with a wide range of dimmers, the boost input capacitance should be minimized. Large input

capacitance impacts the ability of the controller to properly sustain the current required by the dimmer and may

cause oscillation. Capacitors should not be connected to the AC line side of the bridge rectifier. Added AC lineside capacitance alters the dimmer behavior in multi-lamp configurations and shifts the dimming curve.

Excessive capacitance on capacitor C1 after the bridge rectifier generates current spikes that may introduce

ringing. The ringing will cause a TRIAC to prematurely open its switches.

3.5 Completing the Design

Step 19) Choose Power Components

The voltage rating of boost FET Q4 and diode D1 can be estimated by adding 20% to the V

20% is a standard margin for safety purposes and prevents damage to the components during abnormal or

transient conditions. Lower voltage ratings can be used, but sufficient testing is necessary to ensure proper

operation.

V

is 405V or 200V for an AC input voltage of 230 VAC or 120VAC, respectively. The breakdown voltage

BST

for both the FET and the boost diode ≥

1.2 V

. The boost diode must be ultrafast with a recovery time no

BST

greater than 50ns and rated for a DC current, as calculated using Equation 19.

Step 20) Bias Circuit

The bias circuit is built using components C2, C8, C12, R4, D4, D7, and Z1 (see Figure 1 on page 4). When

AC power is first applied, current flows through capacitor C2 charging capacitor C8, which biases boost

transistor Q2 into conduction. Once the bias circuit turns ‘ON’ the boost transistor Q2, a current is applied to

pin VDD through diode D6.

The initial supply current I

the charge on capacitor C8.The initial supply voltage V

flows through transistor Q2 onto capacitors C10 and C6. Zener diode Z1 limits

DD

applied to pin VDD is defined by Equation 21.

DD

. A margin of

BST

AN364

Resistor R4 limits the current in capacitor C2. Once the voltage applied to pin VDD has exceeded the UVLO

voltage, the CS1610/11 starts to operate, and voltage appears at the boost inductor L3 auxiliary winding.

When transistor Q2 is ‘ON’, capacitor C9 charges from diode D5 to pin GND. When transistor Q2 is OFF,

capacitor C9 reroutes the charge into capacitor C6 from diode D5. As the voltage develops across capacitor

C6 and exceeds V

supplies V

to the device with the larger current required during normal operation. See Equation 22.

DD

, transistor Q1 turns ‘ON’, and diode D6 reverse biases. After startup, transistor Q1

DD

The inequality in Equation 22 indicates that diode D6 is back-biased after start up.

Step 21) Zero-current Detection

The CS1610/11 uses zero-current detection (ZCD) to minimize switching losses. The ZCD algorithm is

designed to turn ‘ON’ the FET when the resonant voltage across the FET is at a low point (see Figure 5). Valley

switching reduces the CV

2

power losses associated with rerouting charge from the body capacitance of the

FET. Similar approaches are taken when turning ‘ON’ the boost FET Q2 and the flyback FET Q4. Pin BSTAUX

and FBAUX are designed to monitor the resonant voltage from the auxiliary winding of the boost inductor L3

and the flyback transformer T1, respectively. The flyback ZCD and the boost ZCD function exactly the same.

As described in step 20, the auxiliary winding of the boost inductor L3 is also used to drive the charge pump

circuit to develop the supply voltage, V

. It is recommended to use the boost auxiliary winding for the boost

DD

ZCD. The flyback transformer T1 auxiliary winding monitors output overvoltage and the ZCD function. The

auxiliary winding turns ratio must be designed to develop ~22V peak-to-peak under nominal conditions. The

turns ratio for L3 is calculated using Equation 23:

16 AN364REV3

Page 17

AN364

CS1610/11

+

-

I

CONNECT

V

CONNECT

(th )

Comp_Out

eOTP

Control

eOTP

R

S

C

NTC

NTC

V

DD

10

(Optional )

Figure 9. eOTP Functional Diagram

I

CONNECT

V

CONNECT th

R

-------------------------------------=

[Eq. 24]

CODE

I

CONNECT

2

N

-------------------------- -

V

CONNECT th

R

NTCRS

+

-------------------------------------=

[Eq. 25]

The BSTAUX pin and FBAUX pin currents must be limited to less than 1mA. A series resistor of at least 22 k

must be used to limit the current.

Step 22) Overvoltage Protection

Output open circuit protection and output overvoltage protection (OVP) are implemented by monitoring the

output voltage through the flyback transformer auxiliary winding. During switching time T2, the voltage across

the flyback transformer T1 auxiliary winding is representative of the output voltage using a turns ratio

relationship. The flyback auxiliary winding voltage is applied to the FBAUX pin. If the voltage on the FBAUX

pin exceeds threshold V

the controller attempts to restart after one second.

Since the flyback auxiliary winding does not supply V

constraints. A flyback auxiliary output voltage of 10V to 20 V during switching period T2 is appropriate. The

resistive divider between the flyback auxiliary winding and the FBAUX pin must be sized to produce 1.25V

when an overvoltage fault occurs at the desired load. The FBAUX pin current must be limited to less than 1mA.

Step 23) External Overtemperature Protection

The external overtemperature protection (eOTP) pin is used to implement overtemperature protection using a

negative temperature coefficient (NTC) thermistor. The total resistance on the eOTP pin is converted to an 8bit digital ‘CODE’ (which gives an indication of the temperature) using a digital feedback loop, adjusting the

current (I

(V

CONNECT(th)

CONNECT

) into the NTC and series resistor RS to maintain a constant reference voltage of 1.25V

). Figure 9 illustrates the functional block diagram when connecting an optional NTC

temperature sensor to the eOTP circuit.

, which is set to 1.25V, a fault condition occurs. The IC output is disabled and

OVP(th)

, the auxiliary winding circuit has fewer design

DD

Current I

CONNECT

is generated from an 8-bit controlled current source with a full-scale current of 80A. See

Equation 24:

When the loop is in equilibrium, the voltage on the eOTP pin fluctuates around V

‘CODE’ output by the ADC is used to generate I

CONNECT

. In normal operating mode, the I

CONNECT(th)

. The digital

CONNECT

updated once every seventh half line-cycle by a single ±LSB step. See Equation 25:

AN364REV3 17

current is

Page 18

Solving Equation 25 for ‘CODE’:

CODE

2

N

V

CONNECT th

I

CONNECTRNTCRS

+

-------------------------------------------------------------------

=

256 1.25 V

80AR

NTCRS

+

-----------------------------------------------------------

=

4M

R

NTCRS

+

---------------------------------

=

[Eq. 26]

Temperature (°C)

Current (I

LED

, Nom.)

125

95

50%

100%

0

25

Figure 10. LED Current vs. Temperature

AN364

The tracking range of this resistance ADC is approximately 15.5k to 4M. The series resistor R

is used to

S

adjust the resistance of the NTC to fall within this ADC tracking range so that the entire 8-bit dynamic range of

the ADC is used. A 14 k (±1% tolerance) series resistor is required to allow measurements of up to 130°C to

be within the eOTP tracking range when a 100k NTC with a Beta of 4334 is used. The eOTP tracking circuit

is designed to function accurately with an external capacitance of up to 470pF. A higher 8-bit code output

reflects a lower resistance and hence a higher external temperature.

The ADC output code is filtered to suppress noise and compared against a reference code that corresponds

to 125/130 °C. If the temperature exceeds this threshold, the chip enters an overtemperature state and shuts

down. This is not a latched protection state, and the ADC keeps tracking the temperature in this state in order

to clear the fault state once the temperature drops below 110 °C. If an external overtemperature protection

thermistor is not used, connect the eOTP pin to GND using a 50k to 500 k resistor to disable the eOTP

feature.

When exiting reset, the chip enters startup and the ADC quickly (<5ms) tracks the external temperature to

check if it is below the 110°C reference code before the boost and second stages are powered up. If this check

fails, the chip will wait until this condition becomes true before initializing the rest of the system.

For external overtemperature protection, a second low-pass filter with a time constant of 2 minutes filters the

ADC output and uses it to scale down the internal dim level of the system (and hence the LED current, I

LED

if the temperature exceeds 95 °C (see Figure 10).

)

The large time constant for this filter ensures that the dim scaling does not happen spontaneously and is not

noticeable (suppress spurious glitches). The I

starts reducing when R

LED

~ 6.3k (assuming a 14k1%

NTC

tolerance, series resistor), which corresponds to a temperature of 95°C for a 100k NTC (100 k at 25°C).

The I

value to scale output LED current I

current is scaled until the NTC value reaches 2.5k (125°C). The CS1610 /11 uses this calculated

LED

, as shown in Figure 10. Beyond this temperature, the IC shuts down. If

LED

the external overtemperature protection feature is not required, connect the eOTP pin to GND using a 50k-

to-500k resistor to disable the eOTP feature.

Step 24) Clamp Circuit

To keep dimmers conducting and prevent misfiring, a minimum power needs to be delivered from the dimmer

to the load. This power is nominally around 2W for 230 V and 120V TRIAC dimmers. At low dim angles (≤90°),

this excess power cannot be converted into light by the output stage because of dim mapping at light loads.

V

can rise above the safe operating voltage of the primary-side bulk capacitor C4. The clamp circuit drains

BST

18 AN364REV3

Page 19

AN364

excess charge from capacitor C4 by turning ‘ON’ transistor Q3, dissipating the power into load resistors R6

and R16. The clamp load resistors R6 and R16 must each be 2k 2W resistors for 230 V and 500 2W

resistors for 120V systems.

Step 25) Designing the EMI Filter

The switching frequency of the CS1610/11 can cause resonance in the EMI filter, so it is important to carefully

design it. Resonance can cause undue noise, oscillation, and impact power factor. The resonant frequencies

on the LC filters must be less than 1/10 of the minimum switching frequency of the boost stage. There is a

variety of dimmers, and each behaves differently. All dimmers are sensitive to the presence of EMI filters with

large capacitance or inductance. Capacitance on the AC side of the rectifier should be avoided. Capacitance

to the immediate output of the rectifier bridge should be minimized for optimal dimmer compatibility.

The EMI filter and the reactances associated with the dimmer constitute a complex reactive network that has

minimal damping. This reactive network will ring as it is excited by the dimmer turn on and the boost stage

conduction. Should the current in the dimmer's TRIAC reverse, the TRIAC will open, disturbing the dimmer

timing, which results in flicker. For this reason limitations are imposed on the values assigned to the EMI

components.

Step 26) Layout

Basics for any power layout:

• Keep power traces as short as possible.

• Keep the controller away from power components and traces if possible. Keep sensitive traces (all sense

inputs) away from high dv/dt traces such as FET drain, FET gate drive, and auxiliary windings.

• Isolate control GND from power GND.

- All control components must be grounded to SGND.

- A single thick trace must be connected from SGND to GND and then extended to the flyback current

sense resistor R21 with a short run.

- The connection between the boost output capacitor C4 and resistor R21 must be short.

• Decouple the capacitor directly at the VDD pin of the CS1610/11 to SGND.

• Run sense traces, especially current sense, away from power-carrying traces characterized by high dv/ dt

(fast rise/fall times) traces, such as collectors and drains of transistors Q2, Q3, and Q4, or the auxiliary

windings or the SOURCE pin.

• Further details are available in application note AN346 CS150x and CS160x PCB Layout Guidelines.

AN364REV3 19

Page 20

AN364

V

BST max

405V= 1.1 V 445V=

[Eq. 27]

V

Breakdown

V

BST maxVCLAMPVMinarg

++ 445V 315V 40V++ 800V===

[Eq. 28]

N

V

Reflected

V

OUT

--------------------------

220V

15V 0.4V+

----------------------------- -

14.3== =

[Eq. 29]

T1 T2+

1

F

sw

-----------

T3–

1

85kHz

----------------- -

1s– 11.76s== =

[Eq. 30]

4 Design Example

The Cirrus Logic CRD1611-8W reference design is used for the design example. The required operating parameters

for the analytical process are outlined in the table below.

Parameters Symbol Value

Output Power

AC Line Input Voltage

Output Voltage

Load Current

Maximum Switching Frequency*

* Increasing Fsw reduces the size of the magnetics but increases switching losses in the FET.

4.1 Flyback Design Steps

Step 1) Select a Value for Boost Output Voltage

The CRD1611-8W is a 230V reference design. Boost output voltage V

Step 2) Select an Appropriate FET

Use Equation 3

voltage to +10%. V

to calculate maximum boost output voltage V

BST(max)

is calculated using Equation 27:

BST(max)

BST

. The CS1611 limits the boost output

P

OUT

V

IN

V

OUT

I

OUT

F

sw(max)

is 405V nominal.

6.6W

230V

15V

440mA

85kHz

Using a 300V zener as a clamp device sets the maximum clamp voltage V

leaving 40V of V

(V

Reflected

- V

CLAMP

It is recommended to choose V

to an 800V FET. Using an analytical approach to partition V

Margin

) requires assumptions on the switching details.

Reflected

to equal 70% of V

CLAMP

. Voltage V

Reflected

to 315V (+5% tolerance),

CLAMP

CLAMP

into V

is set to 220V, leaving 80V

Reflected

and

of overshoot to dissipate as leakage inductance energy. The actual overshoot range is from 65V to 95 V,

depending on the clamp zener tolerance. See Equation 28:

Step 3) Determine the Flyback Transformer Turns Ratio

Select a turns ratio for the flyback transformer T1 based on the desired output voltage, V

Output voltage V

voltage V

. Using Equation 4, calculate turns ratio N:

F

is the maximum LED string forward voltage at full current, plus rectifying diode forward

OUT

OUT

, and V

Reflected

Step 4) Select the Full Brightness Switching Frequency

At full power, the flyback stage operates in valley-switching mode. The addition of a small transition time T3

results in extending time TT and slightly reducing the design frequency. The frequency reduction has a

negligible effect on the design, but requires that time T1, T2 and TT be correctly calculated at full brightness.

An optimal compromise between transformer size and efficiency is reached at a switching frequency of

~85kHz.

To accommodate valley switching, T3 is set to approximately one-half of the resonant period of the flyback

inductor resonance, taking into account all capacitances associated with the FET drain node. Setting T3 to 1

s

is an acceptable starting value. Once a system is built and validated, the design can be refined. Using

Equation 5, solve for (T1 + T2):

.

20 AN364REV3

Page 21

Step 5) Determine the Flyback Nominal Timing T1 and T2

T1

1

F

sw

--------- T 3–

V

Reflected

V

ReflectedVBST

+

----------------------------------------------------

=

1

85k Hz

----------------- -

1s–

220V

220V 405V+

---------------------------------- -

4.14s==

[Eq. 31]

T2

1

F

sw

--------- T 3–

V

BST

V

ReflectedVBST

+

----------------------------------------------------

=

1

85k Hz

----------------- -

1s–

405V

220V 405V+

---------------------------------- -

7.62s==

[Eq. 32]

I

PK FB

2P

OUT max

TT

fb

V

BST

T1fb

----------------------------------------------

= 26.6W

12.5s

0.85 365V 4.05 s

-------------------------------------------------------- -

0.131A==

[Eq. 33]

R

Sense

1.4V

I

PK FB

------------------

1.4V

0.131A

------------------ -

10.7===

[Eq. 34]

L

P

V

BST

T1

I

PK FB

--------------------------------

365V 4.05s

0.131A

------------------------------------------- -

11.3mH== =

[Eq. 35]

R

FBGAIN

4M

TT

fb

T2

fb

----------- -

128

64–

----------------------------------------------

=

4M

12.5s

7.65s

------------------

128

64–

------------------------------------------------------- -

=26.5k=

[Eq. 36]

I

RMSIPK FB

T

current

3TT

--------------------=0.131A

4.05s

3 12.5s

--------------------------- - 43 mA==

[Eq. 37]

Use Equation 7 to solve for T1:

Use Equation 8 to solve for T2:

Step 6) Calculate Peak Current on the Flyback Primary-side

To deliver constant power, I

I

:

PK(FB)

is at its maximum when V

PK(FB)

BST

AN364

is at its minimum. Use Equation 9 solve for

Although I

is calculated to equal 0.131A, the flyback transformer is specified at I

PK(FB)

PK(FB)

= 0.15A to

guarantee margin against saturation.

Step 7) Calculate R

The CS1611 current sense threshold is set to 1.4V. The voltage drop across the sense resistor R

equal 1.4V when a maximum current of 0.15 A flows through resistor R

R

(R23).

Sense

Sense

(R23)

. Use Equation 10 to solve for

Sense

Sense

must

Choosing a 10Ω standard value will assure margin against resistor tolerance. To prevent false triggering by

the comparator, pin FBSENSE has an internal blanking time of 550ns. To reduce switching spikes, it is

recommended to add an additional RC filter circuit using a 1k resistor followed by a 100 pF capacitor.

Step 8) Calculate the Flyback Primary-side Inductance

Use Equation 11

Step 9) Calculate R

Using Equation 12, solve for R

and the minimum I

FBGAIN

(R17)

FBGAIN

from Equation 33 to calculate the primary inductance:

PK(FB)

(R17):

Step 10) Determine the RMS Current in the Winding

Using Equation 13

AN364REV3 21

, calculate transformer T1 primary RMS current:

Page 22

AN364

I

RMSIPK FB

N

T

current

3TT

--------------------

=0.131A14.3

7.45s

312.5s

--------------------------- -

850m A==

[Eq. 38]

I

Ripple RMS

0.85A20.44A

2

– 0.73A==

[Eq. 39]

I

PK BST

3.64 PIN

V

RMS

-------------------------- -

3.64 7.3W

230V

------------------------------- -

116mA== =

[Eq. 40]

Using Equation 13, calculate the transformer T1 secondary RMS current:

Step 11) Determine Output Capacitor

Output capacitor C5 ripple current I

Ripple(RMS)

current and the DC load current. See Equation 39.

Output capacitor C5 is selected as a 100F, 25V capacitor.

Step 12) Flyback Transformer Specification

Specifications for the flyback transformer T1 can now be compiled to enable suppliers to design within size

and cost constraints.

Parameter Value

Output DC Power 6.6W

Converter Topology

Switching Frequency 85kHz

Primary Inductance

Peak Primary Current

Primary RMS Current 43mA

Turns Ratio N

P/NS

Secondary Voltage 15.4V

is the vectorial difference between transformer T1 secondary

CRM flyback

11.3 mH

10%

0.15A

14.3

Secondary RMS Current 0.85A

Primary Leakage Inductance <100H

Primary Voltage

Electrostatic Shield

Auxiliary Winding Turns Ratio (N

Auxiliary Wire

Rigidity Sec

Core/Primary/Aux/Shield

P/NAUX

Between primary and secondary winding

)

Any convenient gauge

405V

20

>2,500V

Step 13) Circuit Adjustments

Now that the transformer has been defined and built, it may need to be adjusted. For more information, see

Circuit Adjustments on page 11.

Step 14) Recalculate R

Sense

Validate that the system meets the operating criteria. This may require adjusting components like R

R

. For more information, see Recalculate R

FBGAIN

on page 11.

Sense

4.2 Boost Stage Design Steps

Step 15) Determine I

PK(BST)

Using Equation 19, calculate I

, I

SAT, and RIPK

PK(BST)

:

(R13)

Sense

and

22 AN364REV3

Page 23

AN364

R

IPK

15.625 103V

I

PK BST

------------------------------------------ -

15.625 103V

116m A

------------------------------------------ -

134k ===

[Eq. 41]

L

BST

50 W mH

7.3W

-------------------------------- -

6.8m H==

[Eq. 42]

I

RMS

P

IN

PF

-------- -

1.25

V

IN

-----------

7.3W

0.9

------------- -

1.25

230V

------------- -

= 44mA==

[Eq. 43]

N

P

N

AUX

--------------

405

22

--------- -

18.4==

[Eq. 44]

P

BST

P

OUT

0.9

--------------

6.6W

0.9

------------- -

7.3 W===

[Eq. 45]

Using Equation 20, calculate R

IPK

:

Step 16) Boost Inductor Specifications

See Figure 8 in the Boost Inductor Specifications section on page 11. Choosing a maximum switching

frequency of 110kHz, find the intersection with the 230V maximum switching curve, and get the corresponding

power. This is 50Watt mH, the constant P

IN

L

, for this frequency and voltage. Dividing by the input

BST

power, obtain the inductor value.

Boost inductor RMS current I

depends on the AC line RMS current, the triangular shape and the stepped

RMS

envelope. As a first approximation consider the inductor RMS current to be equal to 1.25 times the AC line

RMS current.

Calculate the auxiliary winding turns ratio by means of Equation 44.

In summary, the inductor specifications are:

• Primary inductance = 10.4mH

• Saturation Current = 0.6A @ 3000Gauss

• RMS Current = 44mA

• Turns Ratio 18.4:1

After procuring an inductor sample meeting specifications, perform the tests described in the Boost Inductor

Specifications section on page 16.

Step 17) Determine Boost Output Capacitor

Using a flyback transformer with a 90% efficiency, boost stage output power P

can be determined using

BST

Equation 45.

For a 230V design, boost output capacitor C4 must be greater than 0.5 7.3 = 3.7F. Taking into account the

tolerance and life degradation, choosing a 4.7F capacitor will satisfy the requirements. This capacitor must

be rated at 450V.

Step 18) Determine Boost Input Capacitor

To accommodate a variety of dimmers, capacitor C3 is proportional to input power: ~4nF/W for 230V designs

and ~12nF/ W for 120 V designs.

AN364REV3 23

Page 24

4.3 Final Design Steps

N

P

N

AUX

--------------

V

BST

22

--------------=

[Eq. 46]

Step 19) Choose Power Components

The drain current through transistor Q4 is limited to 165mA. The smallest 800V MOSFET in a package

capable of handling the power is 1A. The flyback stage output diode D3 has a peak current of 14.3 0.131 =

1.87A, an average DC current of 0.44A, and a maximum reverse voltage of 445/14.3 + 15 = 46V. A 1A 60V

Schottky diode meet the requirements. The boost diode D1 has a peak current of 0.6A and an average DC

current of 7.3W/ 405 V = 18mA. The maximum boost drain current in transistor Q2 is 600mA due to the attach

current. A 600V 1A MOSFET is adequate.

Step 20) Bias Circuit

It is recommended to build a bias circuit that contains the following components: C2, C8, D7, D4, Z1, R9, Q1,

R12, D8, C6, D5, C9, and R11 (for more information about these values, see the Bill of Materials on page 27.)

The bias circuit is optimized to work with the CS1610/11 across a range of applications.

Step 21) Zero-current Detection

The auxiliary winding on inductor L3 must have sufficient voltage to produce 16V across capacitor C6 and be

current limited. Capacitor C9 limits the available current by reducing the charge transfer for each cycle. The

auxiliary secondary peak-to-peak voltage is V

charge transfer will occur. Choosing V

= 22V allows sufficient charge transfer across capacitor C9 without

AUX

unnecessarily wasting power.

BST

(N

AUX/NP

) and must be greater than 16V, otherwise no

AN364

The current through pin BSTAUX must be limited to less than 1mA. A series resistor of at least 22 k needs

to be used to limit the current. Resistor R3 completes a resistor divider with resistor R11 to limit the voltage on

the BSTAUX pin to less than 5V.

Step 22) Overvoltage Protection

Transformer T1 auxiliary winding has the same number of turns as the power secondary. The voltage available

on transformer T1 SOURCE pin is between +15V and -31V. Resistor R22 limits the current to less than 0.5mA.

The voltage at pin FBAUX reaches the OVP threshold of +1.25V when the transformer T1 SOURCE pin

reaches +16.8V. Transformer T1 auxiliary terminal A reaches +16.8V at the same time (the turns ratio is 1:1).

Deducting the 0.4V drop across diode D3 sets the OVP threshold at 16.4V, or approximately +10% of the

nominal output voltage.

Step 23) External Overtemperature Protection

The external negative temperature coefficient (NTC) thermistor reference is a Murata NCP18WF104J03RB.

This NTC is 100k with a Beta of 4275. If the temperature exceeds 95°C, R

is approximately 6.3 k and

NTC

R18 is 14k, so the eOTP pin has a total resistance of 20.3k. The eOTP pin initiates protective dimming

action. At 125°C the thermistor has 2.5k plus R18 = 14k present a resistance of 16.5k at the eOTP pin

reaching the point where a thermal shutdown fault intervenes.

Step 24) Clamp Circuit

Clamp load resistors R6 and R16 must each be 2k2W resistors for 230 V systems. This value has been

validated for optimal dimming performance.

24 AN364REV3

Page 25

AN364REV3 25

Figure 11. Schematic

600-00543-Z1_Rev_A3

JWJW

SHEET

OFSHEET

ENGINEER

DATE

DRAWN BY

PART #

SHEET

4/30/2012

SCH.,CRD1611-8W-Z

11

TITLE

SIZE

B

INITIAL RELEASEA.0

DATEDESCRIPTIONREV

11/18/11

NOTES: UNLESS OT HERWISE SPECI FI ED:

1. ALL RESISTO R VALUES ARE IN OHMS.

CHANGED R21 TO A 10_5 OHM RES. ADDED C12 FOR ASSEMBLY CHANGE

A1

ECO

915

ONLY. NOT REFLECT ED IN CURRENT PCB AS A C12 FOOTPRINT.

12/22/11

917

CHANGED C5 TO EL LO ESR

A2

1/6/12

A3959

CHANGED U1 PIN 6 & 7 PINNAMES TO NC

04/30/12

F1 1A

1

+

3

2

-

4

BR1

HD04-T

C1

4700pF

C2

0.1UF

C3

0.033UF

L1

4.7mH

L2

4.7mH

R1 4.7K

R2 4.7K

4

3

2

1

7A

8

B

T1

RM06-CL01

2

1

5

4

L3

RM05-CL01

D1

STTH1R06

C4

4.7uF

ELEC

1

BSTAU X

2

IAC

3

CLAMP

4

SGND

5

SOURCE

6

NC

7

NC

8

IPK

9

FBGAIN

10

EOTP

11

FBSENSE

12

GND

13

GD

14

VDD

15

FBAUX

16

BSTOUT

PAD

THERM

U1

CS1611-FSZ

12

D2

STTH1L06A

1

2

CY

2200pF

12

D3

SS26-TP

R5

27K

1%

D7

S1G-13-F

D4

1N4148W

Z1

SMAZ16-TP

16V

C8

2.2uF

X7R

R15

1.50M

R14

1.50M

R7

1.50M

R8

1.50M

R11 22.1K

R17

22.1K

R13

120K

D5

BAV23S-7-F

R10

22 OHM

C9

0.33uF

X7R

C6

22uF

ELEC

R12

51 OHM

Q1

ZVN4106FTA

Q2

STD1NK60T4

R9 47 OHM

R24

47 OHM

C10

1.0UF

X7R

R3

4.7K

Q3

FQN1N50CTA

R19 47 OHM

R18

14.0K

-t

NTC

100K

C7

100pF

COG

R20 1K

R21

10.5

R23

5.6K

R22

69.8K

S

D

G

Q4

STD1NK80ZT4

C11

47pF

C0G

PCB DWG-

240-00543-Z1

ASSY DWG-

603-00543-Z1

SCHEMATIC DWG

600-00543-Z1

LBL SUBASSY PROD ID AND REV

E1

LINE

E2

NEUTRAL

E3

LED+

E4

LED-

C5

100uF

ELEC

R4

2K

2W

Z2

P6KE350A

300V

D6

SBR130S3-7

30V

D8

SBR130S3-7

30V

R6

2K

2W

R16

2K

2W

C12

0.01UF

X7R

5 Summary

AN364

Page 26

26 AN364REV3

1 2

1 2

1

2

1 2

123

1

2

1

2

1

2

4

5

1 2

3

4

7

8

1

2

1

2

1

2

1

2

1

2

1

2

Figure 12. PCB Dimensions

6 BOARD LAYOUT

AN364

Page 27

AN364REV3 27

CIRRUS LOGIC

CRD1611-8W_Rev_A.bom

BILL OF MATERIAL

16 070-00212-Z1 A

7 Bill of Materials

Item Cirrus P/N Rev Description Qty Reference Designator MFG MFG P/N

1 070-00211-Z1 A DIODE RECT 400V 0.8A NPB MINIDIP 1 BR1 DIODES INC HD04-T

2 001-10275-Z1 A CAP 4700PF ±10% 1000V X7R NPb 1206 1 C1 MURATA GRM31BR73A472KW01L

3 010-00004-Z1 A CAP 0.1UF ±5% 400V MTL FLM RAD 1 C2 Panasonic ECQE4104JF

4 010-00005-Z1 A CAP 0.033uF ±10% 400V MTL NPb RAD 1 C3 PANASONIC ECQE4333KF

5 012-00197-Z1 A CAP 4.7uF 450V ±20% NPb RAD 10x20 1 C4 PANASONIC-ECG ECA2WHG4R7

6 012-00206-Z1 A CAP 100uF ±20% 25V EL LO ESR NPb RD 1 C5 PANASONIC EEUFM1E101

7 012-00203-Z1 A CAP 22uF ±20% 35V ELEC NPb RAD 1 C6 PANASONIC EEA-GA1V220H

8 001-10084-Z1 A CAP 100pF ±5% 50V C0G NPb 0603 1 C7 KEMET C0603C101J5GAC

9 001-10279-Z1 A CAP 2.2uF ±10% 25V X7R NPb 0805 1 C8 MURATA GRM21BR71E225KA73L

10 001-10276-Z1 A CAP 0.33UF ±10% 50V X7R NPb 0603 1 C9 TDK C1608X7R1H334K

11 001-10283-Z1 A CAP 1.0uF 10% 25V X7R NPb 0603 1 C10 MURATA GRM188R71E105KA12D

12 001-10278-Z1 A CAP 47pF ±5% 1000V C0G NPb 1206 1 C11 JOHANSON DIELECTRICS 102R18N470JV4E

12a 001-10285-Z1 A CAP 0.01uF ±10% 630V X7R NPb 1206 1 C12 MURATA

13 011-00069-Z1 A CAP 2200PF +80/-20% 2KV CER NPb RAD 1 CY MURATA DEBE33D222ZA2B

14 070-00142-Z2 A DIODE FAST 600V 1A NPb DO-41 1 D1 ST STTH1R06

15 070-00156-Z1 A DIODE ULT FAST 600V 1A NPb SMA 1 D2 ST MICROELECTRONICS STTH1L06A

17 070-00007-Z1 A DIODE FAST SW 75V 350mW NPb SOD123 1 D4 DIODES INC 1N4148W-7-F

18 070-00214-Z1 A DIODE SWT 250V 0.4A NPb SOT-23 1 D5 DIODES INC BAV23S-7-F

19 070-00213-Z1 A DIODE RECT 30V 1A NPb SOD-323 2 D6 D8 DIODES INC SBR130S3-7

20 070-00218-Z1 A DIODE RECT 400V 1A NPb SMA 1 D7 DIODES INC S1G-13-F

21 180-00029-Z1 A FUSE 1A 250V TLAG NPb RAD 1 F1 LITTLE FUSE 39211000440

22 040-00154-Z1 A IND 4.7mH ±10% 17.6 OHM 350 DIA TH 2 L1 L2 COILCRAFT RFB0807-472L

23 050-00053-Z1 A XFMR 6.8mH ±10% 10KHz NPb TH 1 L3 KUNSHAN EAGERNESS RM05-CL01

24 036-00019-Z1 A THERM 100K OHM ±5% 0.10mA NPb 0603 1 NTC MURATA NCP18WF104J03RB

25 071-00118-Z1 A TRAN MOSFET nCH 60V.2A NPb SOT23-3 1 Q1 DIODES INC ZVN4106FTA

26 071-00120-Z1 A TRAN MOSFET nCH 1.0A 600V NPb DPAK 1 Q2 ST MICROELECTRONICS STD1NK60T4

27 071-00121-Z1 A TRAN MOSFET nCH 0.38A 500V NPb TO92 1 Q3 FAIRCHILD FQN1N50CTA

28 071-00122-Z1 A TRAN MOSFET nCH 1A 800V NPb DPAK 1 Q4 ST MICROELECTRONICS STD1NK80ZT4

29 021-00596-01 A RES 4.7k OHM 1/4W ±5% 1206 FILM 2 R1 R2 DALE CRCW1206472J

30 020-06499-Z1 A RES 4.70K OHM 1/10W ±1% NPb 0603 1 R3 PANASONIC ERJ3EKF4701V

31 034-00005-Z1 A RES PWR 2.0K OHM 2W ±5% NPb AXL 3 R4 R6 R16 VISHAY PR02000202001JR500

32 020-06501-Z1 A RES 27K OHM 1/8W ±1% NPb 0805 1 R5 PANASONIC ERJ6ENF2702V

33 020-06502-Z1 A RES 1.50M OHM 1/4W ±1% NPb 1206 4 R7 R8 R14 R15 PANASONIC ERJ8ENF1504V

34 020-06500-Z1 A RES 47 OHM 1/10W ±1% NPb 0603 3 R9 R19 R24 PANASONIC ERJ3EKF47R0V

35 020-06496-Z1 A RES 22.0 OHM 1/10W ±1% NPb 0603 1 R10 PANASONIC ERJ3EKF22R0V

36 020-01167-Z1 A RES 22.1k OHM 1/10W ±1% NPb 0603 2 R11 R17 DALE CRCW060322K1FKEA

37 020-06497-Z1 A RES 51.0 OHM 1/10W ±1% NPb 0603 1 R12 PANASONIC ERJ3EKF51R0V

38 020-06498-Z1 A RES 120K OHM 1/10W ±1% NPb 0603 1 R13 PANASONIC ERJ3EKF1203V

39 020-01145-Z1 A RES 14k OHM 1/10W ±1% NPB 0603 FILM 1 R18 DALE CRCW060314K0FKEA

40 020-01016-Z1 A RES 1k OHM 1/10W ±1% NPb 0603 FILM 1 R20 DALE CRCW06031K00FKEA

41 020-06515-Z1 A RES 10.5 OHM 1/4W ±1% NPb 1206 1 R21 DALE CRCW120610R5FKEA

42 020-01227-Z1 A RES 69.8k OHM 1/10W ±1% NPb 0603 1 R22 DALE CRCW060369K8FKEA

43 021-00260-Z1 A RES 5.6k OHM 1/10W ±5% NPb 0603 FLM 1 R23 DALE CRCW06035K60JNEA

44 050-00054-Z1 A XFMR 14.5mH ±10% 10KHz NPb TH 1 T1 KUNSHAN EAGERNESS RM06-CL01

45 065-00354-Z1 B1 IC CRUS DIMMER LED DRVR NPb SOIC16 1 U1 CIRRUS LOGIC CS1611-FSZ/B1

46 070-00215-Z1 A DIODE ZENER 16V 1W NPb DO-214AC 1 Z1 MICRO COMMERCIAL SMAZ16-TP

47 070-00216-Z1 A DIODE TVS 300V 600W NPb DO-204AC 1 Z2 LITTELFUSE P6KE350A

GRM31BR72J103KW01L

DIODE SKY RECT 60V 2A NPb DO-214AC 1 D3 MICRO COMMERCIAL(MCC) SS26-TP

AN364

Figure 13. Bill of Materials

Page 28

Revision History

Revision Date Changes

REV1 MAR 2012 Initial release

REV2 JUNE 2012 Corrected typographical errors.

REV3 AUG 2012 Context change and corrected typographical errors.

AN364

28 AN364REV3

Loading...

Loading...