Cameron DV-550, DV-560 Service manual

Cameron DV-550/DV-560

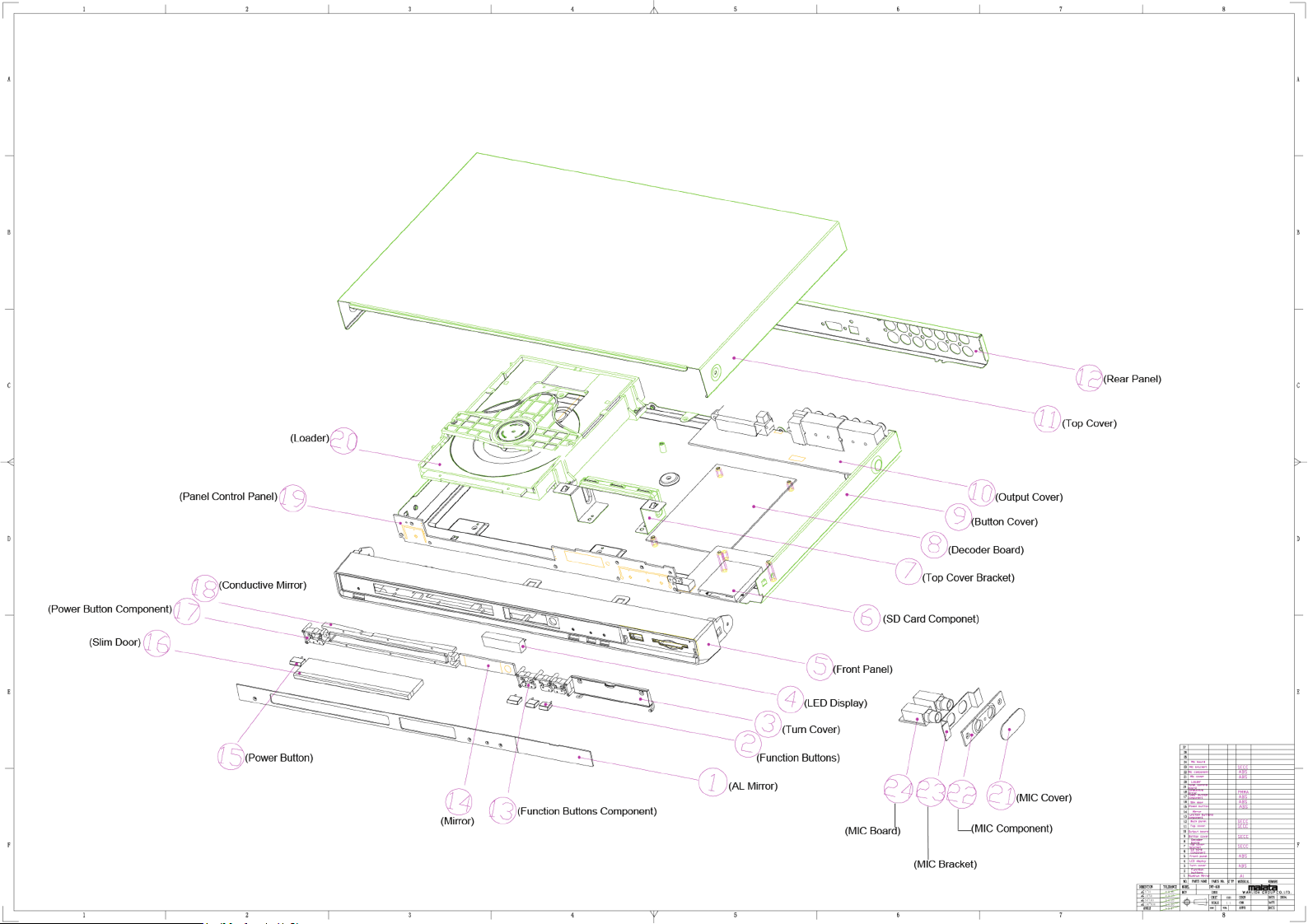

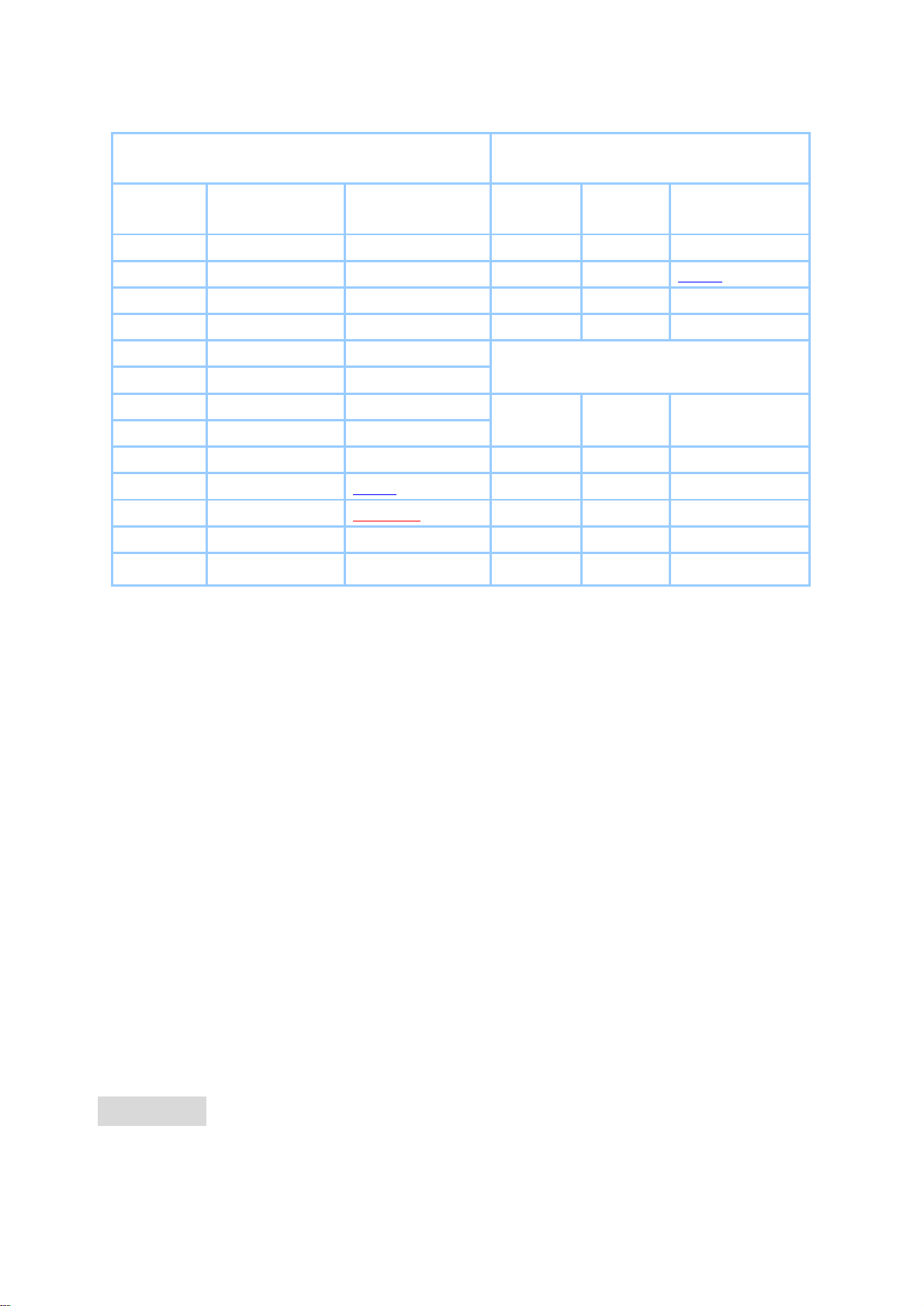

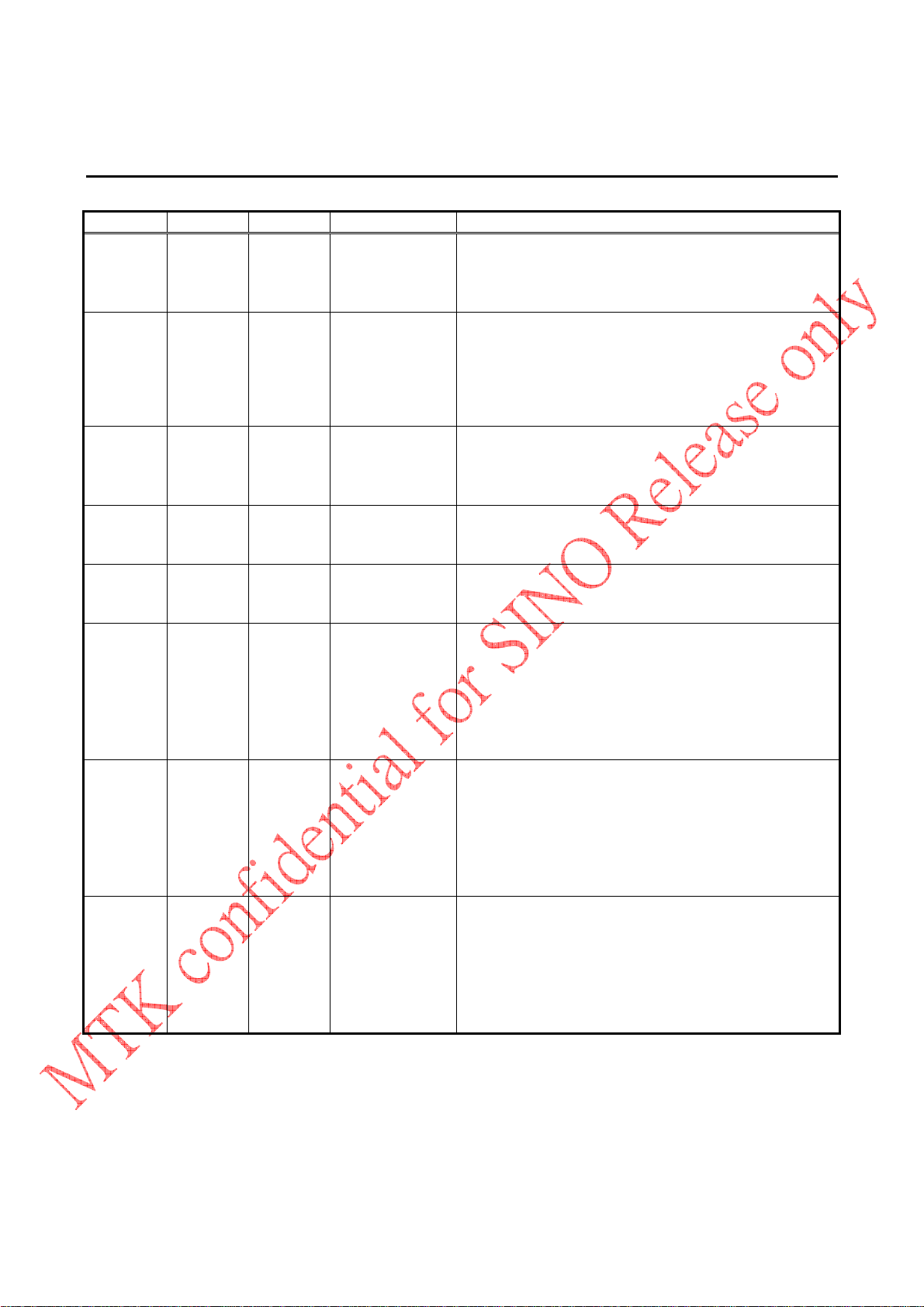

Spare Parts List (DV-550)

DescriptionItem QTY

1 AL Mirror

2 Function Buttons

3 Turn Cover

4 LED Display

5 Front Panel

6 SD Card Componet

7 Top Cover Bracket

8 Decoder Board (MAINBOARD)

9 Button Cover

10 Output Cover (OUTPUT BOARD)

11 Top Cover

12 Rear Panel

13 Function Buttons Component

14 Mirror

Part №

(Код ЗЧД=Номер ЗЧД)

1 DV-550-1

1 DV-550-2

1 DV-550-3

1 DV-550-4

1 DV-550-5

1 DV-550-6

1 DV-550-7

1 DV-550-8

1 DV-550-9

1 DV-550-10

1 DV-550-11

1 DV-550-12

1 DV-550-13

1 DV-550-14

15 Power Button

16 Slim Door

17 Power Button Component

18 Conductive Mirror

19 Panel Control Panel

20 Loader

21 MIC Cover

22 MIC Component

23 MIC Bracket

24 MIC Board (KARAOKE BOARD)

Remote Control

POWER BOARD

FRONT BOARD

1 DV-550-15

1 DV-550-16

1 DV-550-17

1 DV-550-18

1 DV-550-19

1 KHM-313AAA

1 DV-550-21

1 DV-550-22

1 DV-550-23

1 DV-550-24

1 DV-550-25

1 DV-550-26

1 DV-550-27

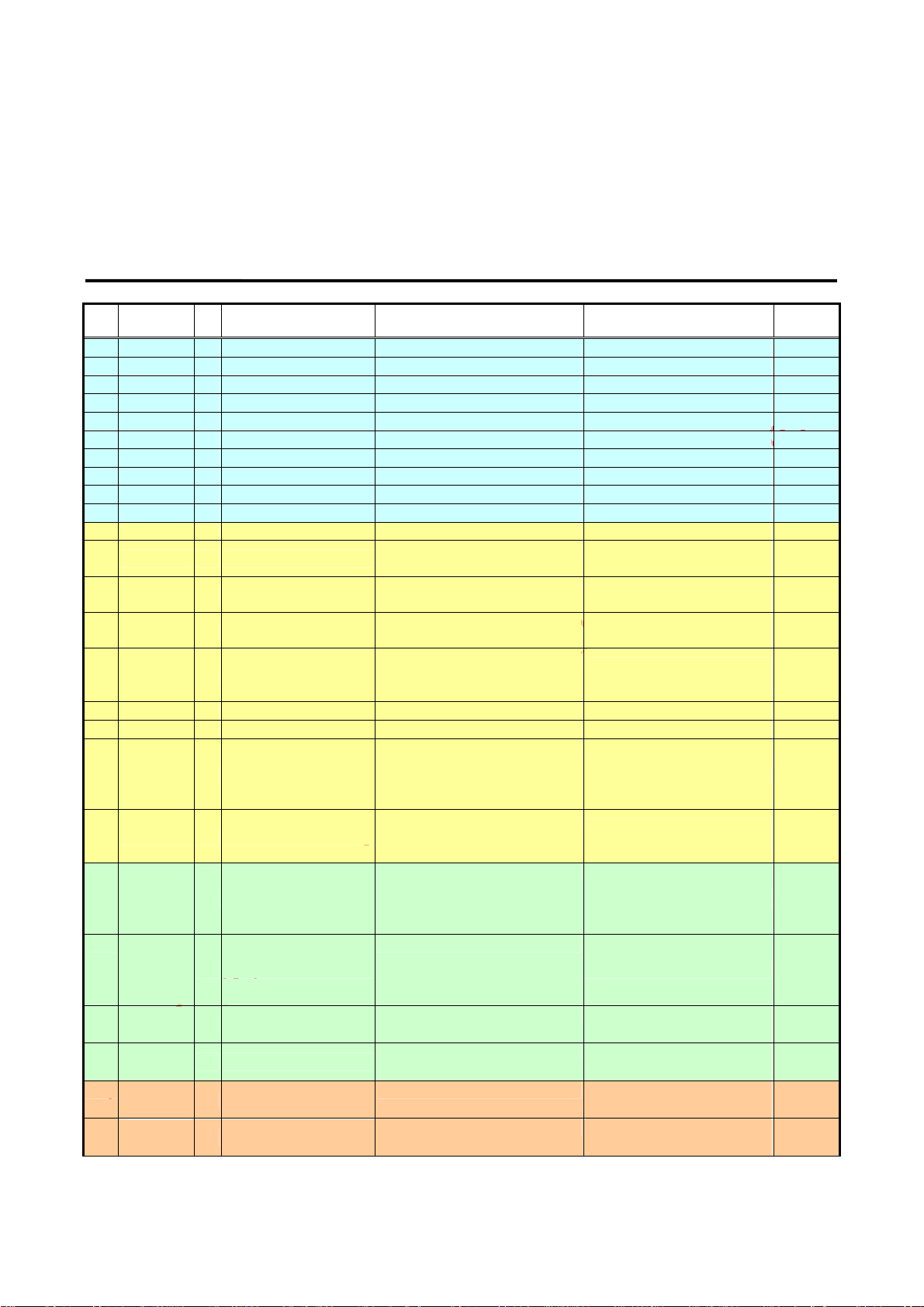

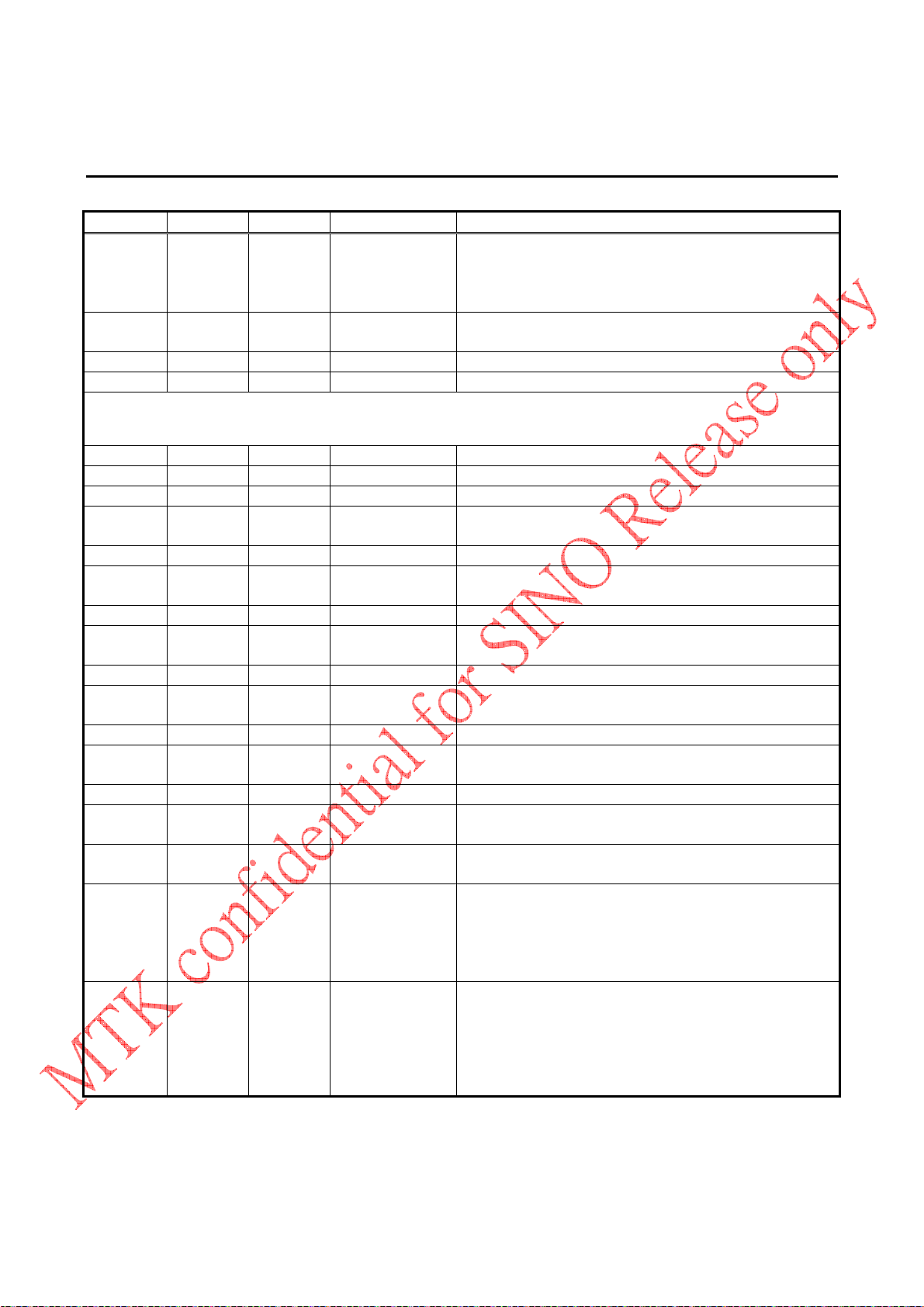

Spare Parts List (DV-560)

DescriptionItem QTY

1 AL Mirror

2 Function Buttons

3 Turn Cover

4 LED Display

5 Front Panel

6 SD Card Componet (CARDREAD BOARD)

7 Top Cover Bracket

8 Decoder Board (MAINBOARD)

9 Button Cover

10 Output Cover (OUTPUT BOARD)

11 Top Cover

12 Rear Panel

13 Function Buttons Component

14 Mirror

Part №

(Код ЗЧД=Номер ЗЧД)

1 DV-560-1

1 DV-560-2

1 DV-560-3

1 DV-560-4

1 DV-560-5

1 DV-560-6

1 DV-560-7

1 DV-560-8

1 DV-560-9

1 DV-560-10

1 DV-560-11

1 DV-560-12

1 DV-560-13

1 DV-560-14

15 Power Button

16 Slim Door

17 Power Button Component

18 Conductive Mirror

19 Panel Control Panel

20 Loader

21 MIC Cover

22 MIC Component

23 MIC Bracket

24 MIC Board (KARAOKE BOARD)

Remote Control

POWER BOARD

FRONT BOARD

1 DV-560-15

1 DV-560-16

1 DV-560-17

1 DV-560-18

1 DV-560-19

1 KHM-313AAA

1 DV-560-21

1 DV-560-22

1 DV-560-23

1 DV-560-24

1 DV-560-25

1 DV-560-26

1 DV-560-27

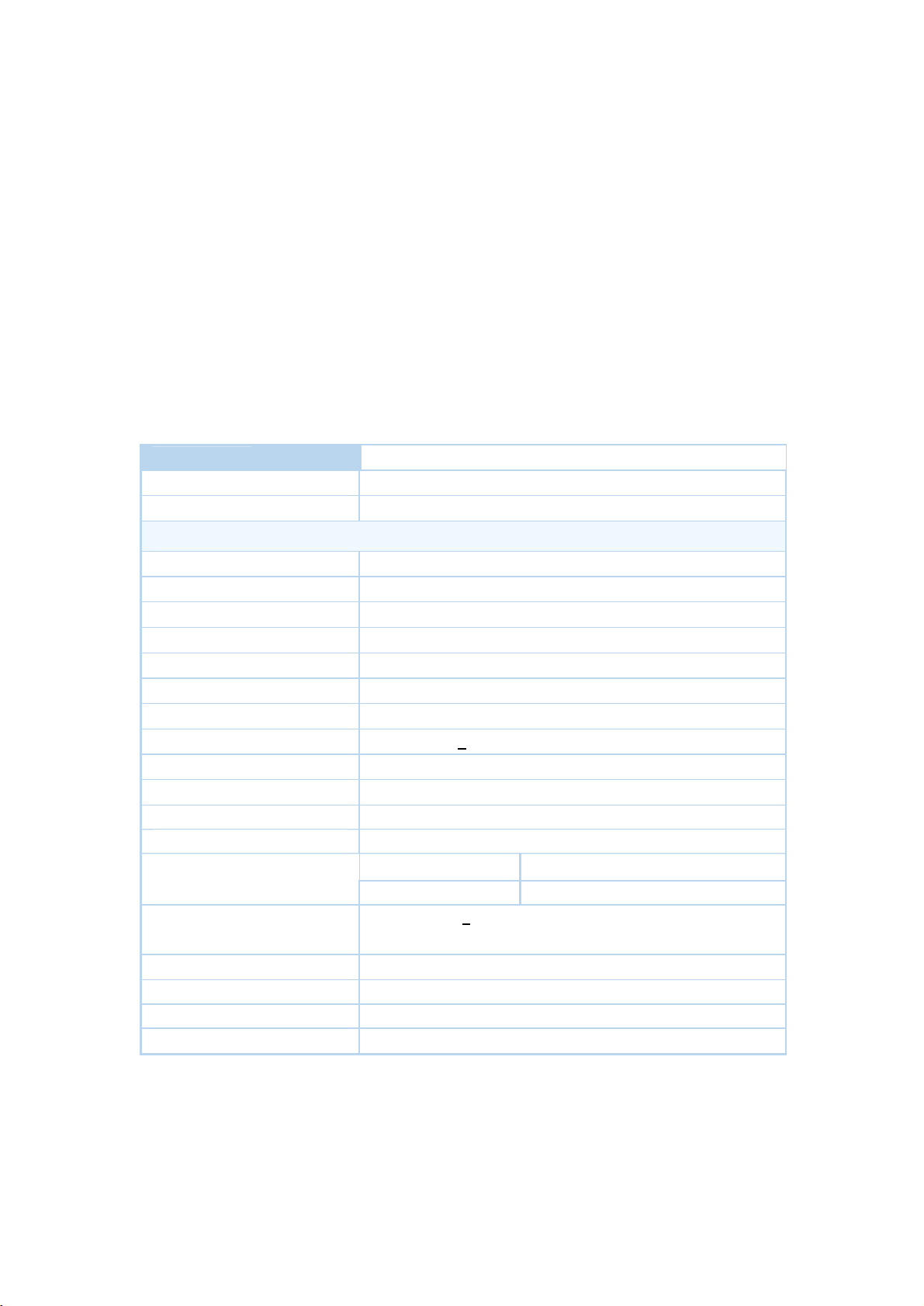

SERVICE MANUAL

MODEL:DV550/DV560

CONTENT

PART 1: Brief Introduction

◆ Speciation

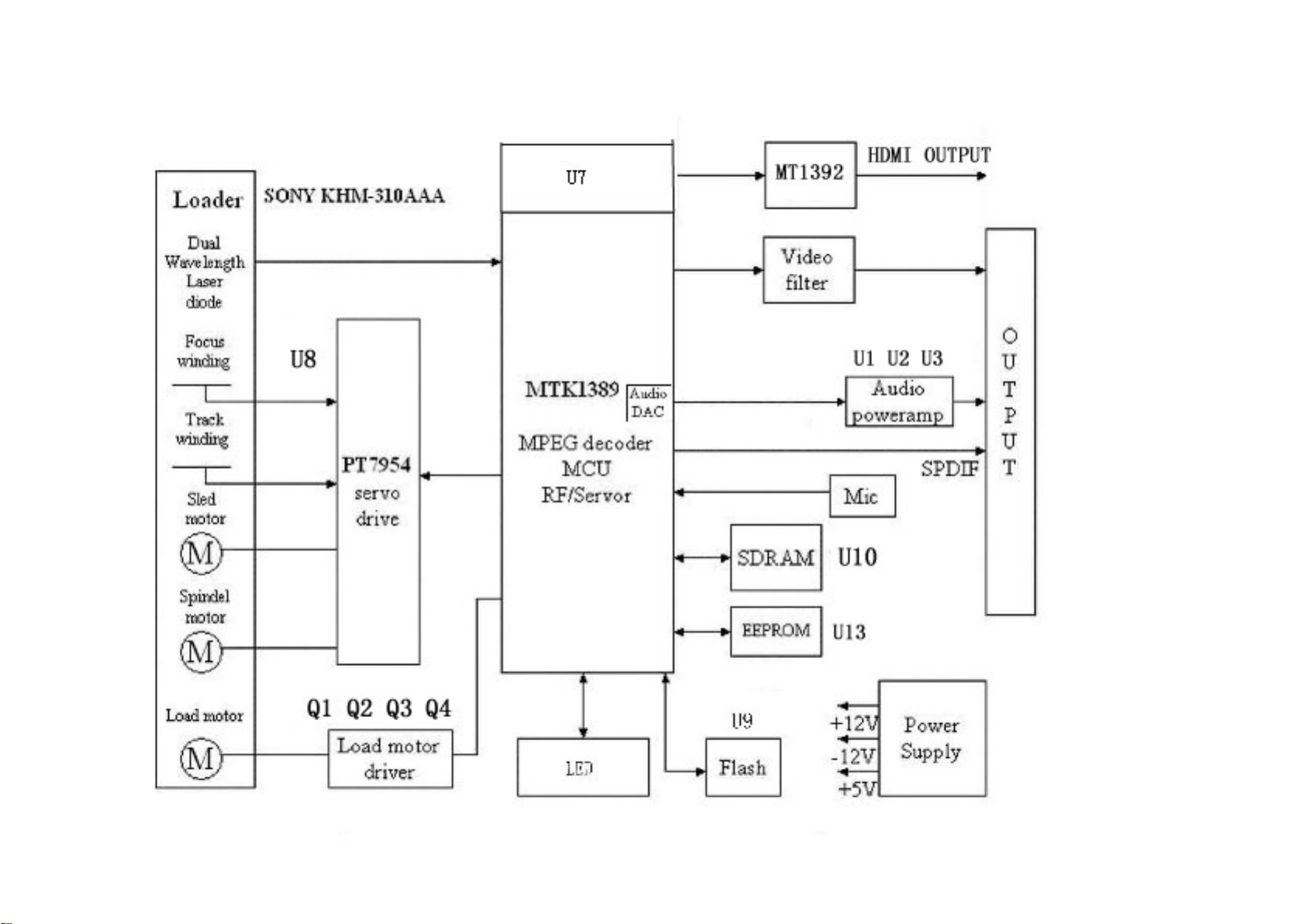

◆ Schematic Diagram

PART 2: Key Ics And Assemblies

PART 3: Detailed Circuit

Panel Board(attached drawing)

◆

Power Board(attached drawing)

◆

Main Board(attached drawing)

◆

ist

L

s

t

r

a

P

:

4

T

R

A

P

PART 5: Debug Procedure

Part 1 Brief Introduction

AUTO/NTSC/PAL

Analog audio out

T

hank you for buying

player,

The DVD offers the high quality of DVD playback from a

ELENBERG DVD Product. As a high-resolution DVD

sleek, portable chassis. It plays almost all kinds of discs such as DVD-video, video

CD, CD-R, CD-RW, MP3,WMA,PICTURE-CD JPEG, audio CD, and Super Video

CD and MP4 discs compatible with the horizontal resolution more than 500 lines. It

features an optical Dolby Digital output for ready connection with receivers equipped

with Dolby decoders,The DAC audio converter and virtual surround sound capability

deliver great sound whether you're listening through six speakers or two, while video

features like A-B repeat and multiple-viewing-angle are displayed on the high-quality

TV screen. The DVD SERIES comes with a wireless remote control, USER`S

MANUAL.

Speciations

Brand

DVD Type DV550/DV560

General

Exterior Color Silver&black

Number of Discs

Playable Audio Formats CD, CD-R, CD-RW, MP3

Playable Video Formats DVD, SVCD, JPEG,MP4

Video Outputs Composite,S-VEDIO,VGA,SCART

Laser wavelength 780/650 nm

Video system

Frequency Response 20Hz-20KHz + 2.5dB

Audio signal-to noise rate ≥85 dB

Audio distortion + noise ≤-70dB (1KHz)

Dynamic range ≥80Db (1KHz)

Channel separation ≥70Db (1KHz)

Audio Out

Video Out

Power Supply

Power Consumation

Dimension

Weight

ELENBERG

Digital audio out:

Out level: 1V

Unbalanced negative

AC 100-240V 50/60 Hz

≤14W

370mm×245mm×44mm

About 2kg

+0.2 load:75Ω

P-P

Out Level: 2V±

Out Level: 0.5V

0.2

, Load: 10kΩ

1.0

, Load: 75Ω

P-P

PART 2 KEY Ics And Assemblies

U4

PCM1606

AT24C16AN

U11

MT1392E

U12

IC800

IC801

IC803

On Main Board On power board

Serial

No

1 U

2 U

3

4 U

5 U

6

7

8 U10 HY57V641620HGT

9 U

10 U1

11

12 U1

Position Type

5 U14

6 U15

7

8

9 KH29LV160BT

3

U2 U3

AMS1117 1

CX1117-3.3 2 PC817/EL817

1389DE/H

MT

PT7954

24C04

NJM4558

Serial

no

3 KA431

position type

On Panel board

Serial

no

1 U1 PT1628

position position

2A0565/FSDH321

ICS ON MAIN BOARD

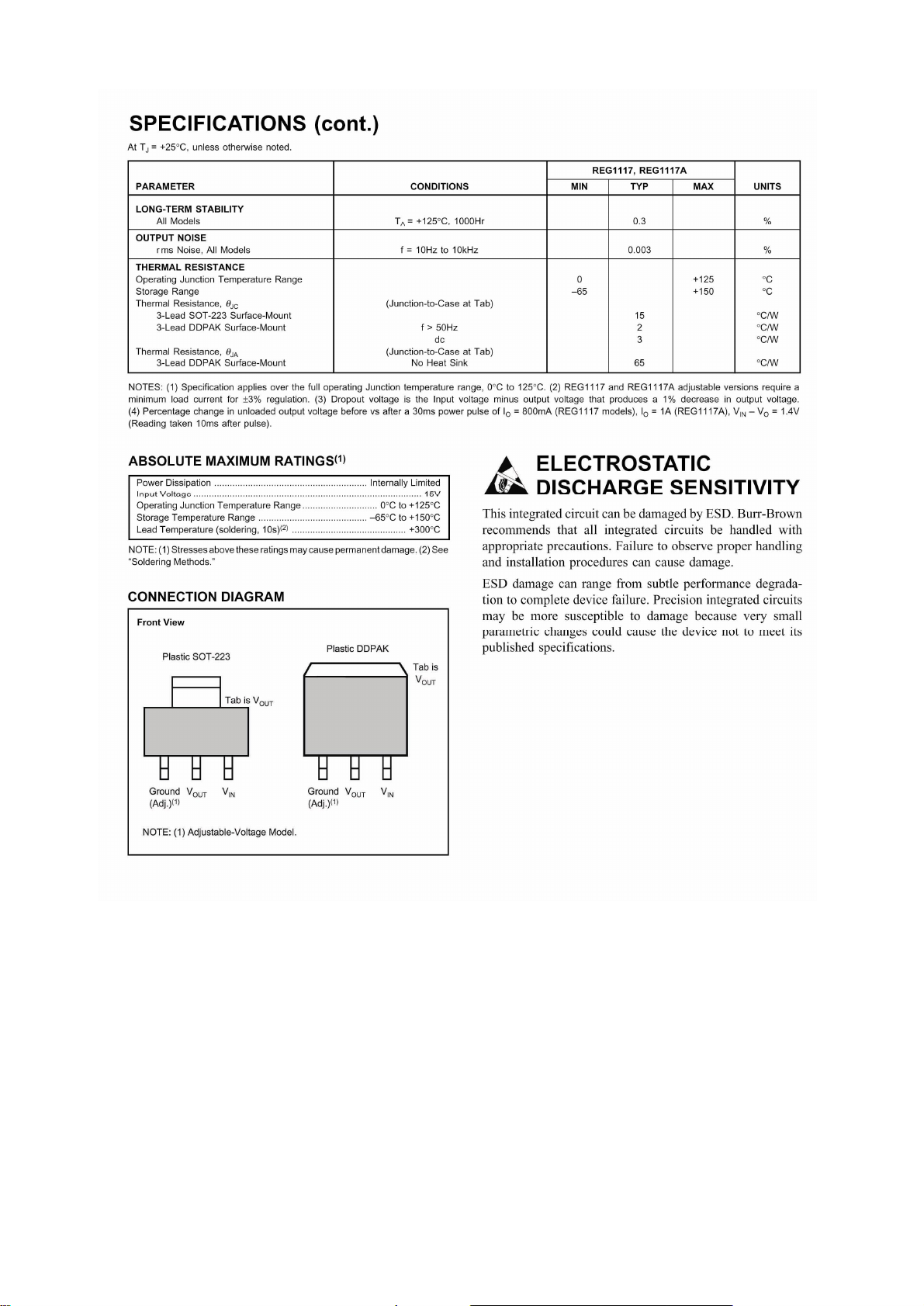

REG1117:800mA and 1A Low Dropout Positive Regulator1.8V, 2.5V, 2.85V,

3.3V, 5V, and Adjustable

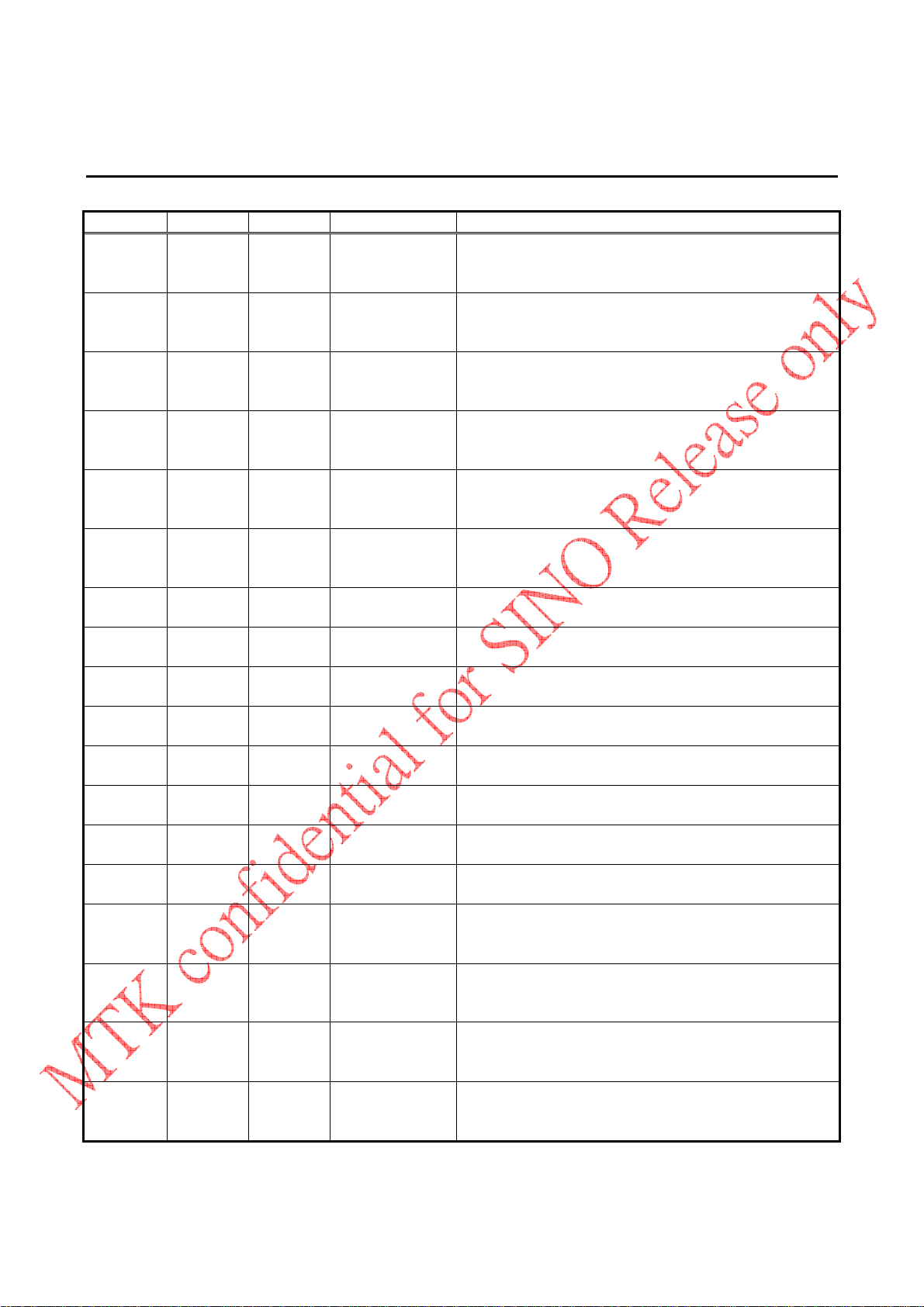

Version 1.6 MT1389HD

Specifications are subject to change without notice Control I/O Pin Assignment

Item

Name

1 UP1_2 97 Inout, 4MA, SR, PU, SMT Micro Controller Port 1-2 (>4 Bank)

2 UP1_3 98 Inout, 4MA, SR, PU, SMT Micro Controller Port 1-3 VSCK

3 UP1_4 99 Inout, 4MA, SR, PU, SMT Micro Controller Port 1-4 VSTB

4 UP1_5 100 Inout, 4MA, SR, PU, SMT Micro Controller Port 1-5 VSDA

5 UP1_6 101 Inout, 4MA, SR, PU, SMT Micro Controller Port 1-6 I2C SCK

6 UP1_7 102 Inout, 4MA, SR, PU, SMT Micro Controller Port 1-7 I2C SDA

7 UP3_0 103 Inout, 4MA, SR, PU, SMT Micro Controller Po rt 3-0 ASTB

8 UP3_1 104 Inout, 4MA, SR, PU, SMT Micro Controller Port 3-1 Microphone Detection

9 IOA20 75 Inout, 2~16MA, SR, SMT Flash Address 20 / IO (> 1M)

10 IOA21 87 Input, Pull-Down Flash Address 21 / IO (> 2M) Peripheral Reset

11 SPMCLK 204 Input, Non-pull Master Clock of SPDIF Input 1. MS card detect

12

SPDATA 205 Input, Non-pull

13

SPLRCK 206 Input, Non-pull

14

SPBCK 207 Input, Non-pull

15

ASDATA3 212 Output, Pull-Down

16 ASDATA4 214 Output, Pull-Down Audio Serial Data 4 (Downmix L/R)

17 MC_DATA 215 Input, Pull-Down Microphone Serial Input

18

VSYN 181 Input, Non-pull

19

YUV7 180 Input, Non-pull

20

HSYN 179 Input, Non-pull

21

IO_17

(DQM2)

22

C_0/IO_0

(RD16)

23

C_1/IO_1

(RD17)

24

C_2/IO_2

(RD18)

25

C_3/IO_3

(RD19)

Pin

Power-on & IO Status

#

177 Input, Pull-Up

176 Input, Non-pull

175 Input, Non-pull

173 Input, Non-pull

172 Input, Non-pull

Original Purpose

Audio Data of SPDIF Input 1. SD card detect

Left/Right Channel Clock of SPDIF In 1. SM card detect

Bit Clock of SPDIF Input 1. CF card detect

Audio Serial Data 3 (Cb or Rb/Lb)

Vertical Sync. Input/Output

Video Data Output Bit 7

Horizontal Sync. Input/Output

1.SM CE- (O)

1.CF –RESET (O)

1.CF INTRQ (I)/SM CLE (O)

1.CF –IOWR (O)/SM –WE (O)

GPIO Purpose

2. SCART TV Selection

2. SCART RGB Selection

2. SCART Aspect Ratio Selection

1. CF D10(IO)/SD CMD (IO)

2. Audio Mute

1. CF D01 (IO)/SD DATA0(IO)

1. CF D09 (IO)/SD DATA1(IO)

2. Audio Line In

1. CF D02 (IO)/SD DATA2(IO)

1.CF IORDY (I)/SD DATA3(IO)

2. Digital Video output C bit 0

2. Digital Video output C bit 1

2. Digital Video output C bit 2

2. Digital Video output C bit 3

Note

Note #4

Note #6

Note #7

Note #1

Note #4

Note #6

Note #7

Note #4

Note #6

Note #7

Note #1

Note #4

Note #6

Note #7

Note #2

Note #4

Note #6

Note #7

Note #7

Note #7

Note #3

Note #7

Note #7

2005/11/15

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389HD

Item

Name

26

C_4/IO_4

(RD20)

27

C_5/IO_5

(RD21)

28

C_6/IO_6

(RD22)

29

C_7/IO_7

(RD23)

30 YUVCLK

/IO_8

(DQM3)

31

Y_0/IO_9

(RD24)

32

Y_1/IO_10

(RD25)

33

Y_2/IO_11

(RD26)

34

Y_3/IO_12

(RD27)

35

Y_4/IO_13

(RD28)

36

Y_5/IO_14

(RD29)

37

Y_6/IO_15

(RD30)

38

Y_7/IO_16

(RD31)

39 IO_18

(DQS1)

40 IO_19

(DQS0)

41 TDI 51 Input, Non-pull JTAG Data In SERVO TROUT Note #1

42 TMS 52 Input, Non-pull Test Mode Select SERVO TRIN Note #1

43 TCK 53 Input, Non-pull JTAG Clock SERVO STBY Note #1

44 TDO 54 Input, Non-pull JTAG Data Out SERVO TRCLOSE (Only GPO) Note #1

45

ASDATA2/

GPO_0

46

ASDATA1

/ GPO_1

47

ASDATA0

/ GPO_2

48

GPIO_3 201 Input, Pull-Down

49 GPIO_4 200 Input, Pull-Down

Pin

Power-on & IO Status

#

171 Input, Non-pull

169 Input, Non-pull

168 Input, Non-pull

167 Input, Non-pull

166 Input, Pull-Up

165 Input, Non-pull

164 Input, Non-pull

163 Input, Non-pull

162 Input, Non-pull

161 Input, Non-pull

159 Input, Non-pull

158 Input, Non-pull

157 Input, Non-pull

130 Input, Non-pull

112 Input, Non-pull

203 Input, Pull-Down Audio Serial Data 2 (C/Sub) 1.MS CLK (O)

202 Input, Pull-Down Audio Serial Data 1 (Ls/Rs)

197 Input, Pull-Down Audio Serial Data 0 (L/R) 1. SD CLK(O)

Original Purpose

1.CF –IORD (O)/SM –RE (O)

1.CF –CS1 (O)

1.CF –CS0 (O)

1.CF D15 (IO)/SM –R_B(IO)

1.CF D14 (IO)/SM D4 (IO)

1.CF D06 (IO)/SM D3 (IO)

1.CF D13 (IO)/SM D5 (IO)

1.CF D05 (IO)/SM D2 (IO)

1.CF D12 (IO)/SM D6 (IO)

1.CF D04 (IO)/SM D1 (IO)

1.CF D11 (IO)/SM D7 (IO)

1.CF D03 (IO)/SM D0 (IO)

GPIO Purpose

2. Digital Video output C bit 4

2. Digital Video output C bit 5

2. Digital Video output C bit 6

2. Digital Video output C bit 7

1.CF D07 (IO)

2.Digital Video Clock output

2. Digital Video output Y bit 0

2. Digital Video output Y bit 1

2. Digital Video output Y bit 2

2. Digital Video output Y bit 3

2. Digital Video output Y bit 4

2. Digital Video output Y bit 5

2. Digital Video output Y bit 6

2. Digital Video output Y bit 7

Sled fglimit

SERVO IOA Laser Switch

1.CF A00 (O)/MS BS(O)/SM –WP

(O)

1. CF D08 (IO)/MS DATA0 (IO)

1. CF D00 (IO)/MS DATA1 (IO)

Note

Note #7

Note #7

Note #7

Note #5

Note #7

Note #7

Note #7

Note #7

Note #7

Note #7

Note #7

Note #7

Note #7

Note #7

GPO only

Note #6

Note #7

GPO only

Note #6

Note #7

GPO only

Note #6

Note #7

Note #6

Note #7

Note #6

Note #7

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389HD

Item

Name

50 RCLKB

(GPIO_5)

51 RVREF

(GPIO_6)

52 ARF/

AGPIO_0

53 ARS/

ASDATA3

54 AR/

ASDATA1

55 AL/

ASDATA2

56 ALS/

ASDATA0

57 ALF/

AGPIO_1

Pin

Power-on & IO Status

#

199 Input, Pull-Up

198 Input, Pull-Up

222 Input, Non-pull

223 Input, Non-pull

224 Input, Non-pull

226 Input, Non-pull

227 Input, Non-pull

228 Input, Non-pull

Original Purpose

AUDIO DAC Subwoofer channel

output

AUDIO DAC right s urround channel

output

AUDIO DAC right channel output

AUDIO DAC left channel output

AUDIO DAC left surround channel

output

AUDIO DAC Center chann e l ou tput

GPIO Purpose

1. CF A01 (O)/MS DATA2 (IO)

1. CF A02 (O)/MS DATA3 (IO)/SM

ALE (O)

Note

Note #6

Note #7

Note #6

Note #7

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

History: 1.3 Finalized the 6-in-1 pins assignment

1.4 The same with 1.3.

1.5 Renaming the RD16~RD31 and define the HDMI and card reader pins.

Notice :

Note #1 :

These pins should not Pull-high to 5V.

3.3V is ok for that.

Item Name Pin# Max. Input voltage

1

2

3

4

5

6

7

FG

TDI

TMS

TCK

TDO

VSYN

HSYN

Note #2:

Pull-high to 3.3V by > 10K Ohms on the board when CF is applied.

Note #3:

50 3.3

51 3.3

52 3.3

53 3.3

54 3.3

181 3.3

179 3.3

Pull-low to ground by > 10K Ohms on the board when CF is applied.

Note #4:

Pull-high to 3.3V by 10K Ohms on the board when SD is applied.

Note #5:

Pull-high to 3.3V by 10K?? Ohms on the board when SMC is applied.

Note #6:

4-in-1 related pins.(MS/MS Pro/SD/MMC)

Note #7:

6-in-1 related pins.(MS/MS Pro/SD/MMC/CF/SM)

Abbr. :

SR : Slew Rate

PU : Pull Up

PD : Pull Down

SMT : Schmitt Trigger

2MA~16MA : Output buffer driving strength.

Pin Main Alt. Type Description

RF Interface ( 26 )

231 RFGND18 Ground Analog ground

232 RFVDD18 Power Analog power 1.8V

252 OSP Analog output RF Offset cancellation capacitor connecting

253 OSN Analog output RF Offset cancellation capacitor connecting

254 RFGC Analog output RF AGC loop capacitor connecting for DVD-ROM

Current reference input. It generates reference current for

255 IREF Analog Input

256 AVDD3 Power Analog power 3.3V

1 AGND Ground Analog ground

2 DVDA Analog Input AC coupled input path A

3 DVDB Analog Input AC coupled input path B

4 DVDC A nalog I nput AC coupled input path C

5 DVDD Analog Input AC coupled input path D

6 DVDRFIP Analog Input AC coupled DVD RF signal input RFIP

7 DVDRFIN Analog I nput AC coupled DVD RF signal input RFIN

8 MA Analog Input DC coupled main-beam RF signal input A

9 MB Analog Input DC coupled main-beam RF signal input B

10 MC Analog Input DC coupled main-beam RF signal input C

11 MD Analog Input DC coupled main-beam RF signal input D

12 SA Analog Input DC coupled sub-beam RF signal input A

13 SB Analog Input DC coupled sub-beam RF signal input B

14 SC Analog Input DC coupled sub-beam RF signal input C

15 SD Analog Input DC coupled sub-beam RF signal input D

16 CDFON Analog Input CD focusing error negative input

17 CDFOP Analog Input CD focusing error positive input

18 TNI Analog Input 3 beam satellite PD signal nega tive input

19 TPI Analog Input 3 beam satellite PD signal positive input

RF path. Connect an external 15K resistor to this pin and

AVSS.

ALPC ( 4 )

MTK Confidential A

Pin Main Alt. Type Description

20 MDI1 Analog Input Laser power monitor input

21 MDI2 Analog Input Laser power monitor input

22 LDO2 Analog Output Laser driver output

23 LDO1 Analog Output Laser driver output

ADC Power ( 2 )

244 ADCVDD3 Power Analog 3.3V Power for ADC

245 ADCVSS Ground Analog ground for ADC

VPLL (3)

43 VPLLVSS Ground Analog ground for VPLL

44 CAPPAD Analog Inout VPLL External Capacitance connection

45 VPLLVDD3 Power Analog 3.3V Power for VPLL

Reference Voltage ( 3 )

28 V2REFO Analog output Reference voltage 2.8V

29 V20 Analog output Reference voltage 2.0V

30 VREFO Analog output Reference voltage 1.4V

Analog Monitor Output ( 7 )

24 SVDD3 Power Analog power 3.3V

25 CSO RFOP Analog output

26 RFLVL RFON Analog output

27 SGND Ground Analog ground

31 FEO Analog output Focus error monitor output

32 TEO Analog output Tracking error monitor output

33 TEZISLV Analog output TE Slicing Level

Analog Servo Interface ( 6 )

246 RFVDD3 Power Analog Power

247 RFRPDC Analog output RF ripple detect output

248 RFRPAC Analog Input RF ripple detect input(through AC-coupling)

249 HRFZC Analog Input High frequency RF ripple zero crossing

250 CRTPLP Analog output Defect level filter capacitor connecting

251 RFGND Ground Analog Power

1) Central servo

2) Positive main beam summing output

1) RFRP low pass, or

2) Negative main beam summing output

RF Data PLL Interface ( 9 )

235 JITFO Analog output The output terminal of RF jitter meter.

236 JITFN Analog Input The input terminal of RF jitter meter.

237 PLLVSS Ground Ground pin for data PLL and related analog circuitry.

MTK Confidential A

Pin Main Alt. Type Description

238 IDACEXLP Analog output Data PLL DAC Low-pass filter

239 PLLVDD3 Power Power pin for data PLL and related analog circuitry.

240 LPFON Analog Output The negative output of loop filter amplifier

241 LPFIP Analog Input The positive input terminal of loop filter amplifier.

242 LPFIN Analog Input The negative input terminal of loop filter amplifier.

243 LPFOP Analog Output The positive output of loop filter amplifier

Motor and Actuator Driver Interface ( 10 )

34 OP_OUT Analog output Op amp output.

35 OP_INN Analog input Op amp negative input

36 OP_INP Analog input Op amp positive input

37 DMO Analog Output Disk motor control output. PWM output.

38 FMO Analog Output Feed motor control. PWM output.

39

40 PWMOUT1 V_ADIN9 Analog Output

41 TRO Analog Output

42 FOO Analog Output Focus servo output. PDM output of focus servo compensator

50

TROPENPW

M

FG

(Diogital pin)

Analog Output Tray PWM output / Tray open output.

st

1) 1

General PWM output, or

2) Version AD input 9

Tracking servo output. PDM output of tracking servo

compensator.

LVTTL 3.3V Input,

V_ADIN8

Schmitt Input, pull

up , with analog

input path for

1) Motor Hall sensor input, or

2) Version AD input 8

V_ADIN8

General Power/Ground ( 18 )

55,93,

142,160,

DVDD18 Power 1.8V power pin for internal digital circuitry

174, 213

81,178 DVSS Ground 1.8V Ground pin for internal digital circuitry

65,96,118,

131,145,156,

DVDD3 Power 3.3V power pin for internal digital circuitry

170, 208

90, 148 DVSS Ground 3.3V Ground pin for internal digital circuitry

Micro Controller and Flash Interface ( 48 )

Inout

62 HIGHA0

2~16MA, SR

Microcontroller address 8

PU

Inout

74 HIGHA1

2~16MA, SR

Microcontroller address 9

PU

MTK Confidential A

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389HD

Pin Main Alt. Type Description

Inout

73 HIGHA2

72 HIGHA3

71 HIGHA4

70 HIGHA5

69 HIGHA6

68 HIGHA7

89 AD7

86 AD6

85 AD5

84 AD4

83 AD3

82 AD2

80 AD1

79 AD0

92 IOA0

77 IOA1

56

57 IOA3

IOA2

2~16MA, SR

PU

Inout

2~16MA, SR

PU

Inout

2~16MA, SR

PU

Inout

2~16MA, SR

PU

Inout

2~16MA, SR

PU

Inout

2~16MA, SR

PU

Inout

2~16MA, SR

Inout

2~16MA, SR

Inout

2~16MA, SR

Inout

2~16MA, SR

Inout

2~16MA, SR

Inout

2~16MA, SR

Inout

2~16MA, SR

Inout

2~16MA, SR

Inout

2~16MA, SR

PU

Inout

2~16MA, SR

PU

Inout

2~16MA, SR

PU

Inout

2~16MA, SR

PU

Microcontroller address 10

Microcontroller address 11

Microcontroller address 12

Microcontroller address 13

Microcontroller address 14

Microcontroller address 15

Microcontroller address/data 7

Microcontroller address/data 6

Microcontroller address/data 5

Microcontroller address/data 4

Microcontroller address/data 3

Microcontroller address/data 2

Microcontroller address/data 1

Microcontroller address/data 0

Microcontroller address 0 / IO

Microcontroller address 1 / IO

Microcontroller address 2 / IO

Microcontroller address 3 / IO

4

MTK Confidential A

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389HD

Pin Main Alt. Type Description

Inout

58 IOA4

59 IOA5

60 IOA6

61 IOA7

67 A16

91 A17

63 IOA18

64 IOA19

75 IOA20

87 IOA21

88 ALE

78 IOOE#

66 IOWR#

76 IOCS#

94 UWR#

95 URD#

2~16MA, SR

PU

Inout

2~16MA, SR

PU

Inout

2~16MA, SR

PU

Inout

2~16MA, SR

PU

Output

2~16MA, SR

Output

2~16MA, SR

Inout

2~16MA, SR

SMT

Inout

2~16MA, SR

SMT

Inout

2~16MA, SR

SMT

Inout

2~16MA, SR

SMT

Inout

2~16MA, SR

PU, SMT

Inout

2~16MA, SR

SMT

Inout

2~16MA, SR

SMT

Inout

2~16MA, SR

PU, SMT

Inout

2~16MA, SR

PU, SMT

Inout

2~16MA, SR

PU, SMT

Microcontroller address 4 / IO

Microcontroller address 5 / IO

Microcontroller address 6 / IO

Microcontroller address 7 / IO

Flash address 16

Flash address 17

Flash address 18 / IO

Flash address 19 / IO

Flash address 20 / IO

1) Flash address 21 / IO

2) While External FLASH size <= 2MB:

I) GPIO

Microcontroller address latch enable

Flash output enable, active low / IO

Flash write enable, active low / IO

Flash chip select, active low / IO

Microcontroller write strobe, active low

Microcontroller read strobe, active low

5

MTK Confidential A

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389HD

Pin Main Alt. Type Description

Inout

97 UP1_2

98 UP1_3

99 UP1_4

100 UP1_5

101 UP1_6 SCL

102 UP1_7 SDA

103 UP3_0 RXD

104 UP3_1 TXD

105 UP3_4

106 UP3_5

RXD

SCL

TXD

SDA

109 IR

110 INT0#

4MA, SR

PU, SMT

Inout

4MA, SR

PU, SMT

Inout

4MA, SR

PU, SMT

Inout

4MA, SR

PU, SMT

Inout

4MA, SR

PU, SMT

Inout

4MA, SR

PU, SMT

Inout

4MA, SR

PU, SMT

Inout

4MA, SR

PU, SMT

Inout

4MA, SR

PU, SMT

Inout

4MA, SR

PU, SMT

Input

SMT

Inout

2~16MA, SR

PU, SMT

Microcontroller port 1-2

Microcontroller port 1-3

Microcontroller port 1-4

Microcontroller port 1-5

1) Microcontroller port 1-6

2

2) I

C clock pin

1) Microcontroller port 1-7

2

2) I

C data pin

1) Microcontroller port 3-0

2) 8032 RS232 RXD

1) Microcontroller port 3-1

2) 8032 RS232 TXD

1) Microcontroller port 3-4

2) Hardwired RD232 RXD

2

3) I

C clock pin

1) Microcontroller port 3-5

2) Hardwired RD232 TXD

2

C data pin

3) I

IR control signal input

Microcontroller external interrupt 0, active low

204 SPMCLK SCLK0

205 SPDATA SDIN0

Audio interface ( 28 )

1) Audio DAC master clock of SPDIF input

Inout

2) While SPDIF input is not used:

Non-pull

1) Audio data of SPDIF input

Inout

2) While SPDIF input is not used:

Non-pull

6

I) Serial interface port 0 clock pin

II) GPIO

I) Serial interface port 0 data-in

II) GPIO

MTK Confidential A

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389HD

Pin Main Alt. Type Description

1) Audio left/right channel clock of SPDIF input

206 SPLRCK SDO0

207 SPBCK

209 ALRCK

210 ABCK Fs64

211 ACLK

197 ASDATA0

202 ASDATA1

203 ASDATA2

SDCS0

ASDATA5

Inout

Non-pull

Inout

Non-pull

Inout

4MA,

PD, SMT

Output

4MA

Non-pull

Inout

4MA

Non-pull

Inout

4MA

PD SMT

Inout

4MA

PD SMT

Inout

4MA

PD SMT

2) While SPDIF input is not used:

I) Serial interface port 0 data-out

II) GPIO

1) Audio bit clock of SPDIF input

2) While SPDIF input is not used:

I) Serial interface port 0 chip select

II) Audio serial data 5 part I : DSD data sub-woofer

channel or Microphone output

III) GPIO

1) Audio left/right channel clock

2) Trap value in power-on reset:

I) 1 : use external 373

II) 0: use internal 373

1) Audio bit clock

2) Phase de-modulation

Audio DAC master clock

1) Audio serial data 0 (Front-Left/Front-Right)

2) DSD data left channel

3) Trap value in power-on reset :

I) 1 : manufactory test mode

II) 0 : normal operation

4) While using external channels:

I) GPO_2

1) Audio serial data 1 (Left-Surround/Right-Surround)

2) DSD data right channel

3) Trap value in power-on reset :

I) 1 : manufactory test mode

II) 0 : normal operation

4) While using external channels:

I) GPO_1

1) Audio serial data 2 (Center/LFE)

2) DSD data left surround channel

3) Trap value in power-on reset :

I) 1 : manufactory test mode

II) 0 : normal operation

4) While using external channels:

I) GPO_0

7

MTK Confidential A

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389HD

Pin Main Alt. Type Description

1) Audio serial data 3 (Center-back/

Center-left-back/Center-right-back, in 6.1 or 7.1 mode)

Inout

212 ASDATA3

214 ASDATA4 INT1#

215 MC_DATA INT2#

216 SPDIF

217 APLLVDD3 Power 3.3V Power pin for audio clock circuitry

218 APLLCAP Analog Inout APLL External Capacitance connection

219 APLLVSS Ground Ground pin for audio clock circuitry

220 ADACVSS2 Ground Ground pin for AUDIO DAC circuitry

221 ADACVSS1 Ground Ground pin for AUDIO DAC circuitry

222 ARF GPIO Output

223 ARS GPIO Output

224 AR GPIO Output

225 AVCM Analog AUDIO DAC reference voltage

226 AL GPIO Output

4MA

PD SMT

Inout

4MA

PD SMT

Inout

PD SMT

Output

2~16MA,

SR : ON/OFF

Non-pull

2) DSD data right surround channel

3) Trap value in power-on reset :

I) 1 : manufactory test mode

II) 0 : normal operation

4) While only 2 channels output:

I) GPIO

1) Audio serial data 4 (Down-mixed Left/Right)

2) DSD data center channel

3) Trap value in power-on reset :

I) 1 : manufactory test mode

II) 0 : normal operation

4) While only 2 channels output:

I) Microcontroller exte rnal interrupt 1

II) GPIO

1) Microphone serial input

2) While not support Microphone:

I) Microcontroller exte rnal interrupt 2

II) GPIO

SPDIF output

1) AUDIO DAC Sub-woofer channel output

2) While internal AUDIO DAC not used: GPIO

1) AUDIO DAC Right Surround channel output

2) While internal AUDIO DAC not used:

a. SDATA3

b. GPIO

1) AUDIO DAC Right channel output

2) While internal AUDIO DAC not used:

a. SDATA1

b. GPIO

1) AUDIO DAC Left Surround channel output

2) While internal AUDIO DAC not used:

a. SDATA2

b. GPIO

8

MTK Confidential A

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389HD

Pin Main Alt. Type Description

1) AUDIO DAC Left Surround channel output

227 ALS GPIO Output

228 ALF GPIO Output

229 ADACVDD1 Power 3.3V power pin for AUDIO DAC circuitry

230 ADACVDD2 Power 3.3V power pin for AUDIO DAC circuitry

Video Interface ( 18 )

196 DACVDDC Power 3.3V power pin for VIDEO DAC circuitry

195 VREF Analog Bandgap reference voltage

194 FS Analog Full scale adjustment

193 YUV0 CIN

192 DACVSSC Ground Ground pin for VIDEO DAC circuitry

191 YUV1 Y

190 DACVDDB Power 3.3V power pin for VIDEO DAC circuitry

189 YUV2 C

188 DACVSSB Ground Ground pin for VIDEO DAC circuitry

187 YUV3 CVBS

186 DACVDDA Power 3.3V power pin for VIDEO DAC circuitry

185 YUV4 Y/G

184 DACVSSA Ground Ground pin for VIDEO DAC circuitry

183 YUV5 B/Cb/Pb

182 YUV6 R/Cr/Pr

181 VSYN V_ADIN1

180 YUV7

INT3#

ASDATA5

Output

4MA, SR

Output

4MA, SR

Output

4MA, SR

Output

4MA, SR

Output

4MA, SR

Output

4MA, SR

Output

4MA, SR

Inout

4MA, SR

SMT

Non-pull

Inout

4MA, SR

SMT

Non-pull

2) While internal AUDIO DAC not used:

a. SDATA0

b. GPIO

1) AUDIO DAC Center channel output

2) While internal AUDIO DAC not used: GPIO

1) Video data output bit 0

2) Compensation capacitor

1) Video data output bit 1

2) Analog Y output

1) Video data output bit 2

2) Analog chroma output

1) Video data output bit 3

2) Analog composite output

1) Video data output bit 4

2) Green or Y

1) Video data output bit 5

2) Blue or CB

1) Video data output bit 6

2) Red or CR

1) Vertical sync input/output

2) While no External TV-encoder:

I) Vertical sync for video-input

II) Version AD input port 1

III) GPIO

1) Video data output bit 7

2) While no External TV-encoder:

I) Microcontroller exte rnal interrupt 3

II) Audio serial data 5 part II : DSD data sub-woofer

channel or Microphone output

III) GPIO

9

MTK Confidential A

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389HD

Pin Main Alt. Type Description

1) Horizontal sync input/output

Inout

179 HSYN

46 USB_VSS USB Ground USB ground pin

47 USBP Analog Inout USB port DPLUS analog pin

48 USBM Analog Inout USB port DMINUS analog pin

49 USB_VDD3 USB Power USB Power pin 3.3V

108 PRST#

107 ICE

233 XTALO Output 27M crystal out

234 XTALI Input

201 GPIO_3

200 GPIO_4

199 RCLKB GPIO_5

198

RVREF GPIO_6

INT4#

V_ADIN2

4MA, SR

SMT

Non-pull

MISC ( 12 )

Input

PU, SMT

Input

PD, SMT

Inout

Pull-Down

Inout

Pull-Down

Inout

Pull-Up

Inout

Pull-Up

2) While no External TV-encoder:

I) Horizontal sync for video-input

II) Microcontroller external interrupt 4

III) Version AD input port 2

IV) GPIO

Power on reset input, active low

Microcontroller ICE mode enable

27M crystal in

GPIO

GPIO

GPIO

GPIO

176 C_0

175 C_1

173 C_2

172 C_3

171 C_4

169 C_5

168 C_6

167 C_7

IO_0

(RD16)

IO_1

(RD17)

IO_2

(RD18)

IO_3

(RD19)

IO_4

(RD20)

IO_5

(RD21)

IO_6

(RD22)

IO_7

(RD23)

Dram Interface ( 58 ) ( Sorted by position )

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

1) Digital Video output C bit 0

2) GPIO

1) Digital Video output C bit 1

2) GPIO

1) Digital Video output C bit 2

2) GPIO

1) Digital Video output C bit 3

2) GPIO

1) Digital Video output C bit 4

2) GPIO

1) Digital Video output C bit 5

2) GPIO

1) Digital Video output C bit 6

2) GPIO

1) Digital Video output C bit 7

2) GPIO

10

MTK Confidential A

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389HD

Pin Main Alt. Type Description

177 IO_17 (DQM2)

166 YUVCLK

165

164

163

162

161

159

158

157

155 RA4

154 RA5

153 RA6

152 RA7

151 RA8

150 RA9

149 RA11

147 CKE output DRAM clock enable

146 RCLK Inout Dram clock

144 RA3

143 RA2

141 RA1

140 RA0

139 RA10

138 BA1

137 BA0

136 RCS#

135 RAS#

134 CAS#

133 RWE#

132 DQM1

130 IO_18 (DQS1)

129 RD8

128 RD9

Y_0

Y_1

Y_2

Y_3

Y_4

Y_5

Y_6

Y_7

IO_8

(DQM3)

IO_9

(RD24)

IO_10

(RD25)

IO_11

(RD26)

IO_12

(RD27)

IO_13

(RD28)

IO_14

(RD29)

IO_15

(RD30)

IO_16

(RD31)

Inout

Pull-Up

Inout

Pull-Up

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

Inout

Inout

Inout

Inout

Inout

Inout

Inout

Pull-Down

Inout

Inout

Inout

Inout

Inout

Inout

Inout

output

output

output

output

Inout

Inout

Non-pull

Inout

Inout

GPIO

1) Digital Video output Clock

2) GPIO

1) Digital Video output Y bit 0

2) GPIO

1) Digital Video output Y bit 1

2) GPIO

1) Digital Video output Y bit 2

2) GPIO

1) Digital Video output Y bit 3

2) GPIO

1) Digital Video output Y bit 4

2) GPIO

1) Digital Video output Y bit 5

2) GPIO

1) Digital Video output Y bit 6

2) GPIO

1) Digital Video output Y bit 7

2) GPIO

DRAM address 4

DRAM address 5

DRAM address 6

DRAM address 7

DRAM address 8

DRAM address 9

DRAM address bit 11

DRAM address 3

DRAM address 2

DRAM address 1

DRAM address 0

DRAM address 10

DRAM bank address 1

DRAM bank address 0

DRAM chip select, active low

DRAM row address strobe, active low

DRAM column address strobe, active low

DRAM Write enable, active low

Data mask 1

GPIO

DRAM data 8

DRAM data 9

11

MTK Confidential A

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389HD

Pin Main Alt. Type Description

127 RD10

126 RD11

125 RD12

124 RD13

123 RD14

122 RD15

121 RD0

120 RD1

119 RD2

117 RD3

116 RD4

115 RD5

114 RD6

113 RD7

112 IO_19 (DQS0)

111 DQM0

Inout

Inout

Inout

Inout

Inout

Inout

Inout

Inout

Inout

Inout

Inout

Inout

Inout

Inout

Inout

Non-pull

Inout

JTAG Interface( 4 )

DRAM data 10

DRAM data 11

DRAM data 12

DRAM data 13

DRAM data 14

DRAM data 15

DRAM data 0

DRAM data 1

DRAM data 2

DRAM data 3

DRAM data 4

DRAM data 5

DRAM data 6

DRAM data 7

GPIO

Data mask 0

1) Serial interface port 3 data-out

2) Version AD input port 4

3) GPIO

1) Serial interface port 3 data-in

2) Version AD input port 5

3) GPIO

1) Serial interface port 3 clock pin

2) Version AD input port 6

3) GPIO

1) Serial interface port 3 chip-select

2) Version AD input port 7

3) GPO

51 TDI

52 TMS

53 TCK

54 TDO

V_ADIN4

V_ADIN5

V_ADIN6

V_ADIN7

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

Inout

Non-pull

Note:

1. The Main column is the main function, Alt. Means alternative function.

2. The multi-function GPIO pins are set to green characters.

3. The video input por t a nd external TV en c oder mode can not bo th use CCIR-601 mode, at least one of them

should be in C CIR-65 6 mode.

4. Following is a summary of modified pins.

(a) Pin 48, 49, 50, 51 are no longer for JTAG functions.

(b) V_ADIN0 and V_ADIN3 is not available.

Revision History:

Date Version Content

2004-09-14 1.0 z Document Initial

2004-09-17 1.1 z Reorder all pins based on pinV1.1

12

MTK Confidential A

2004-09-30 1.2 z Reorder all pins ba sed on pinV1.2 for better Placement

2004-10-04 1.3 z Update the pull status of IO

z Change the 5.1CH ADAC p ins positions fo r L-group and R-gro up

2004-11-08 1.4

2004-11-15 1.5

z

being together.(pin 223~pi n228)

z pin43, pin45 change order to pin43(VPLLVSS),

pin45(VPLLVDD)

z Add ASDAT A3 function on pin223(PAD_ARS)

z Renaming the RD16~RD31, DQM[3:2], DQS[1:0] as IO_[19:0]

z Pin229 was changed as ADACVDD1

z Pin230 was changed as ADACVDD2

Loading...

Loading...