Burr Brown Corporation ADS7806UB-1K, ADS7806UB, ADS7806U-1K, ADS7806U, ADS7806PB Datasheet

...

Low-Power 12-Bit Sampling CMOS

ANALOG-to-DIGITAL CONVERTER

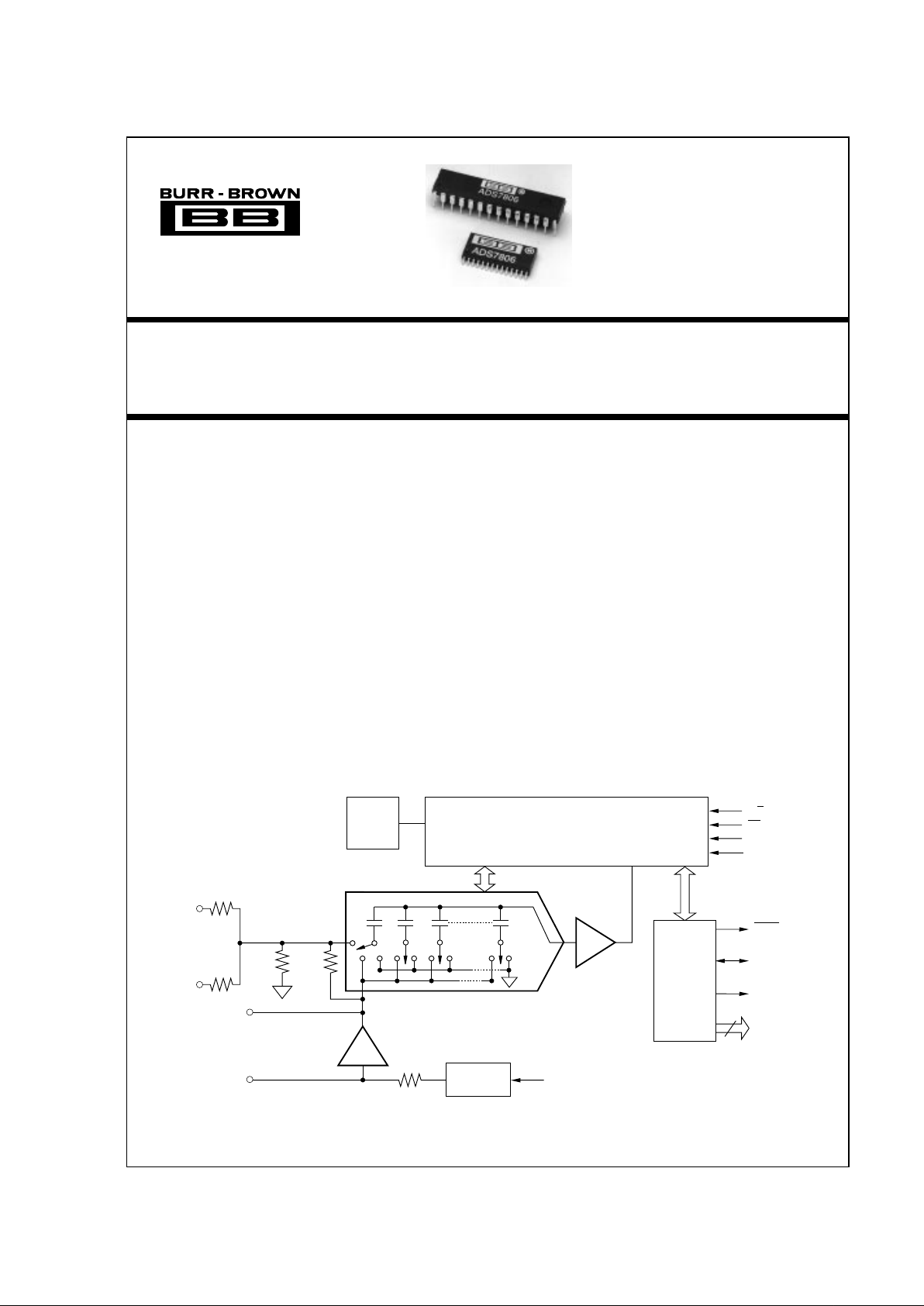

DESCRIPTION

The ADS7806 is a low-power 12-bit sampling analogto-digital using state-of-the-art CMOS structures. It

contains a complete 12-bit, capacitor-based, SAR A/D

with S/H, clock, reference, and microprocessor interface with parallel and serial output drivers.

The ADS7806 can acquire and convert to full 12-bit

accuracy in 25µs max while consuming only 35mW

max. Laser-trimmed scaling resistors provide standard

industrial input ranges of ±10V and 0V to +5V. In

addition, a 0V to +4V range allows development of

complete single supply systems.

The 28-pin ADS7806 is available in a plastic 0.3" DIP

and in an SOIC, both fully specified for operation over

the industrial –40°C to +85°C temperature range.

CDAC

6kΩ

40kΩ

10kΩ

BUSY

Parallel

and

Serial

Data

Out

Comparator

Buffer

20kΩ

R1

IN

R2

IN

REF

Successive Approximation Register and Control Logic

Clock

Power

Down

BYTE

CS

R/C

40kΩ

Internal

+2.5V Ref

Reference

Power

Down

Serial Data

Clock

Parallel Data

CAP

Serial Data

8

FEATURES

● 35mW max POWER DISSIPATION

● 50

µW POWER DOWN MODE

● 25

µs max ACQUISITION AND

CONVERSION

●

±1/2LSB max INL AND DNL

● 72dB min SINAD WITH 1kHz INPUT

●

±10V, 0V TO +5V, AND 0V TO +4V INPUT

RANGES

● SINGLE +5V SUPPLY OPERATION

● PARALLEL AND SERIAL DATA OUTPUT

● PIN-COMPATIBLE WITH 16-BIT ADS7807

● USES INTERNAL OR EXTERNAL

REFERENCE

● 28-PIN 0.3" PLASTIC DIP AND SOIC

ADS7806

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706

Tel: (520) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

®

©

1992 Burr-Brown Corporation PDS-1158C Printed in U.S.A. November, 1994

2

®

ADS7806

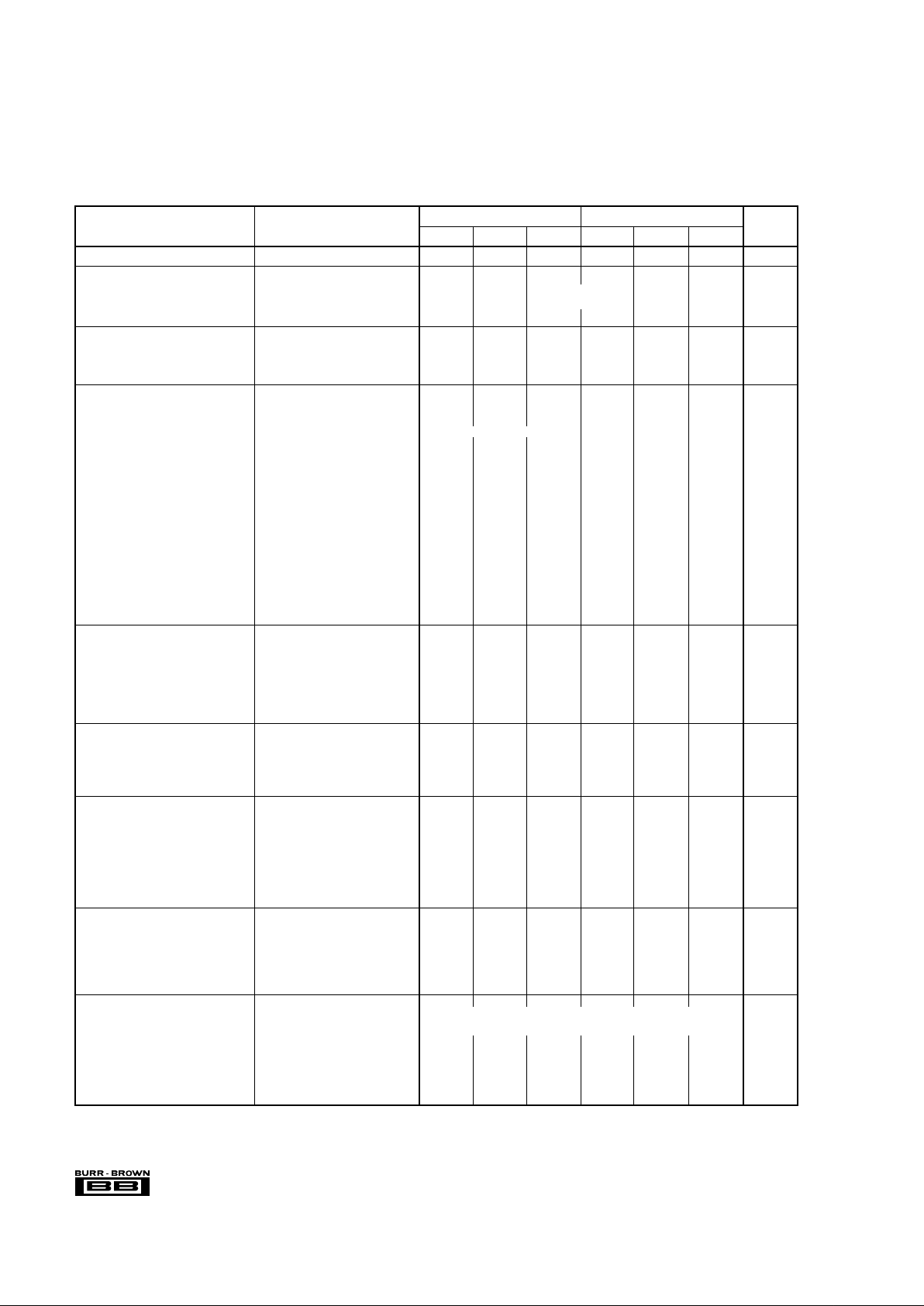

SPECIFICATIONS

ELECTRICAL

At TA = –40°C to +85°C, fS = 40kHz, V

DIG

= V

ANA

= +5V, using internal reference and fixed resistors shown in Figure 7b, unless otherwise specified.

ADS7806P, U ADS7806PB, UB

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

Parallel 12-bits in 2-bytes; Serial

Binary Two’s Complement or Straight Binary

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN

assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject

to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not

authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

RESOLUTION 12 * Bits

ANALOG INPUT

Voltage Ranges ±10, 0 to +5, 0 to +4 V

Impedance (See Table II)

Capacitance 35 * pF

THROUGHPUT SPEED

Conversion Time 20 * µs

Complete Cycle Acquire and Convert 25 * µs

Throughput Rate 40 * kHz

DC ACCURACY

Integral Linearity Error ±0.15 ±0.9 * ±0.45 LSB

(1)

Differential Linearity Error ±0.15 ±0.9 * ±0.45 LSB

No Missing Codes

Guaranteed

* Bits

Transition Noise

(2)

0.1 * LSB

Gain Error ±0.2 ±0.1 %

Full Scale Error

(3,4)

±0.5 ±0.25 %

Full Scale Error Drift ±7 ±5 ppm/°C

Full Scale Error

(3,4)

Ext. 2.5000V Ref ±0.5 ±0.25 %

Full Scale Error Drift Ext. 2.5000V Ref ±0.5 * ppm/°C

Bipolar Zero Error

(3)

±10V Range ±10 * mV

Bipolar Zero Error Drift ±10V Range ±0.5 * ppm/°C

Unipolar Zero Error

(3)

0V to 5V, 0V to 4V Ranges ±3*mV

Unipolar Zero Error Drift 0V to 5V, 0V to 4V Ranges ±0.5 * ppm/°C

Recovery Time to Rated Accuracy 2.2µF Capacitor to CAP 1 * ms

from Power Down

(5)

Power Supply Sensitivity +4.75V < VS < +5.25V ±0.5 * LSB

(V

DIG

= V

ANA

= VS)

AC ACCURACY

Spurious-Free Dynamic Range f

IN

= 1kHz, ±10V 80 90 * * dB

(6)

Total Harmonic Distortion f

IN

= 1kHz, ±10V –90 –80 * * dB

Signal-to-(Noise+Distortion) f

IN

= 1kHz, ±10V 70 73 72 * dB

Signal-to-Noise f

IN

= 1kHz, ±10V 70 73 72 * dB

Usable Bandwidth

(7)

130 * kHz

Full Power Bandwidth (-3dB) 600 * kHz

SAMPLING DYNAMICS

Aperture Delay 40 * ns

Aperture Jitter 20 * ps

Transient Response FS Step 5 * µs

Overvoltage Recovery

(8)

750 * ns

REFERENCE

Internal Reference Voltage No Load 2.48 2.5 2.52 * * * V

Internal Reference Source Current 1 * µA

(Must use external buffer.)

Internal Reference Drift 8 * ppm/°C

External Reference Voltage Range 2.3 2.5 2.7 * * * V

for Specified Linearity

External Reference Current Drain Ext. 2.5000V Ref 100 * µA

DIGITAL INPUTS

Logic Levels

V

IL

–0.3 +0.8 * * V

V

IH

+2.0 VD +0.3V * * V

I

IL

VIL = 0V ±10 * µA

I

IH

VIH = 5V ±10 * µA

DIGITAL OUTPUTS

Data Format

Data Coding

V

OL

I

SINK

= 1.6mA +0.4 * V

V

OH

I

SOURCE

= 500µA+4 * V

Leakage Current High-Z State, ±5*µA

V

OUT

= 0V to V

DIG

Output Capacitance High-Z State 15 * pF

3

®

ADS7806

ELECTROSTATIC

DISCHARGE SENSITIVITY

Electrostatic discharge can cause damage ranging from

performance degradation to complete device failure. BurrBrown Corporation recommends that this integrated circuit

be handled and stored using appropriate ESD protection

methods.

DIGITAL TIMING

Bus Access Time R

L

= 3.3kΩ, CL = 50pF 83 * ns

Bus Relinquish Time R

L

= 3.3kΩ, CL = 10pF 83 * ns

POWER SUPPLIES

Specified Performance

V

DIG

Must be ≤ V

ANA

+4.75 +5 +5.25 * * * V

V

ANA

+4.75 +5 +5.25 * * * V

I

DIG

0.6 * mA

I

ANA

5.0 * mA

Power Dissipation V

ANA

= V

DIG

= 5V, fS = 40kHz 28 35 * * mW

REFD HIGH 23 * mW

PWRD and REFD HIGH 50 * µW

TEMPERATURE RANGE

Specified Performance –40 +85 * * °C

Derated Performance –55 +125 * * °C

Storage –65 +150 * * °C

Thermal Resistance (

θ

JA

)

Plastic DIP 75 * °C/W

SOIC 75 * °C/W

NOTES: (1) LSB means Least Significant Bit. One LSB for the ±10V input range is 4.88mV. (2) Typical rms noise at worst case transition. (3) As measured with

fixed resistors shown in Figure 7b. Adjustable to zero with external potentiometer. (4) Full scale error is the worst case of –Full Scale or +Full Scale untrimmed

deviation from ideal first and last code transitions, divided by the transition voltage (not divided by the full-scale range) and includes the effect of offset error. (5)

This is the time delay after the ADS7806 is brought out of Power Down Mode until all internal settling occurs and the analog input is acquired to rated accuracy.

A Convert Command after this delay will yield accurate results. (6) All specifications in dB are referred to a full-scale input. (7) Usable Bandwidth defined as FullScale input frequency at which Signal-to-(Noise + Distortion) degrades to 60dB. (8) Recovers to specified performance after 2 x FS input overvoltage.

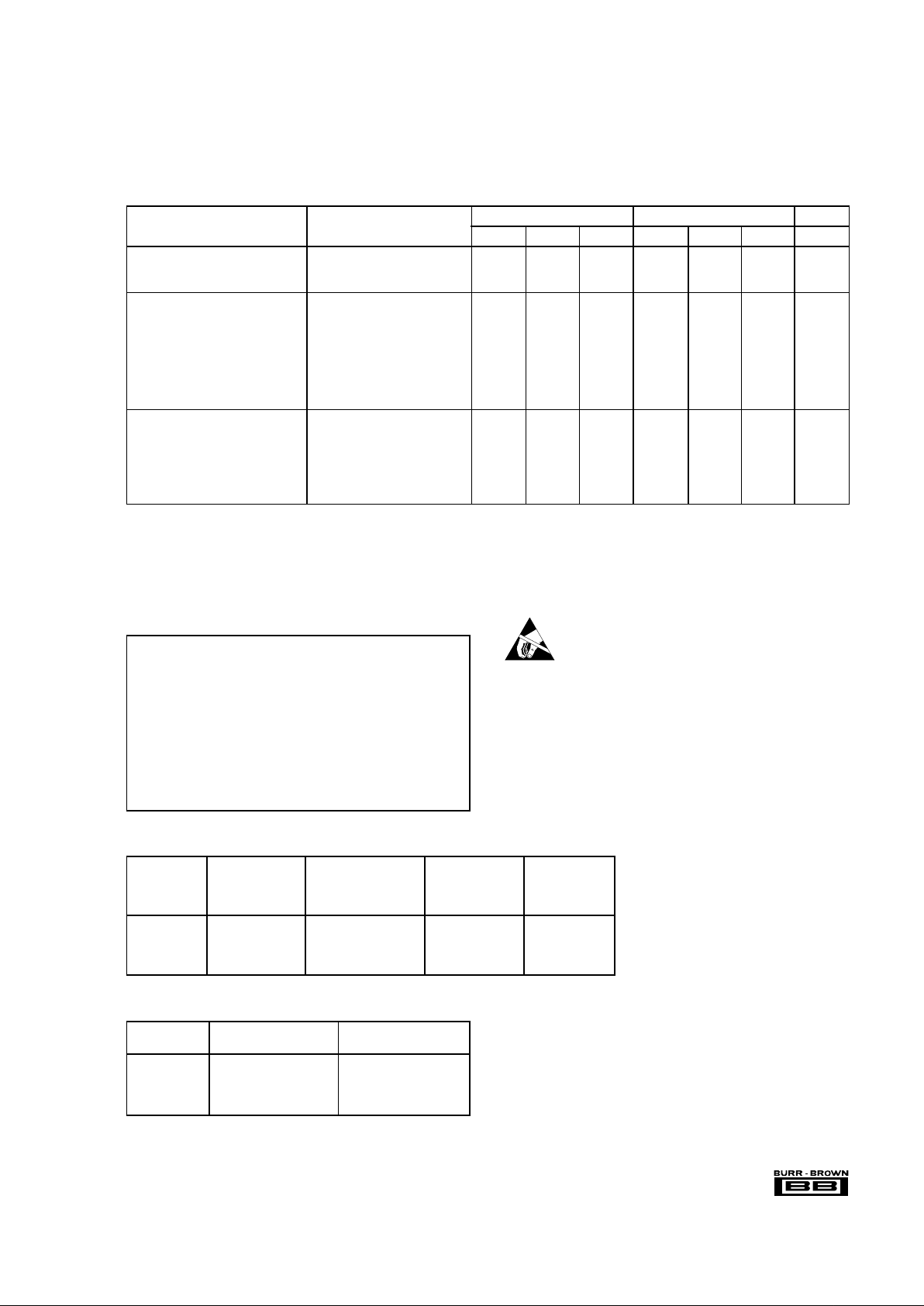

SPECIFICATIONS (CONT)

ELECTRICAL

At TA = –40°C to +85°C, fS = 40kHz, V

DIG

= V

ANA

= +5V, using internal reference and fixed resistors shown in Figure 7b, unless otherwise specified.

ADS7806P, U ADS7806PB, UB

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

Analog Inputs: R1IN........................................................................... ±25V

R2

IN

........................................................................... ±25V

CAP .................................... V

ANA

+0.3V to AGND2 –0.3V

REF .........................................Indefinite Short to AGND2,

Momentary Short to V

ANA

Ground Voltage Differences: DGND, AGND1, and AGND2 .............±0.3V

V

ANA

....................................................................................................... 7V

V

DIG

to V

ANA

......................................................................................+0.3V

V

DIG

........................................................................................................ 7V

Digital Inputs .............................................................. –0.3V to V

DIG

+0.3V

Maximum Junction Temperature ................................................... +165°C

Internal Power Dissipation ............................................................. 825mW

Lead Temperature (soldering, 10s)................................................ +300°C

ABSOLUTE MAXIMUM RATINGS

MAXIMUM MINIMUM

INTEGRAL SIGNAL-TO- SPECIFICATION

LINEARITY (NOISE + DISTORTION) TEMPERATURE

MODEL ERROR (LSB) RATIO (dB) RANGE PACKAGE

ADS7806P ±0.9 70 –40°C to +85°C Plastic DIP

ADS7806PB ±0.45 72 –40°C to +85°C Plastic DIP

ADS7806U ±0.9 70 –40°C to +85°C SOIC

ADS7806UB ±0.45 72 –40°C to +85°C SOIC

ORDERING INFORMATION

PACKAGE INFORMATION

PACKAGE DRAWING

MODEL PACKAGE NUMBER

(1)

ADS7806P Plastic DIP 246

ADS7806PB Plastic DIP 246

ADS7806U SOIC 217

ADS7806UB SOIC 217

NOTE: (1) For detailed drawing and dimension table, please see end of data

sheet, or Appendix D of Burr-Brown IC Data Book.

4

®

ADS7806

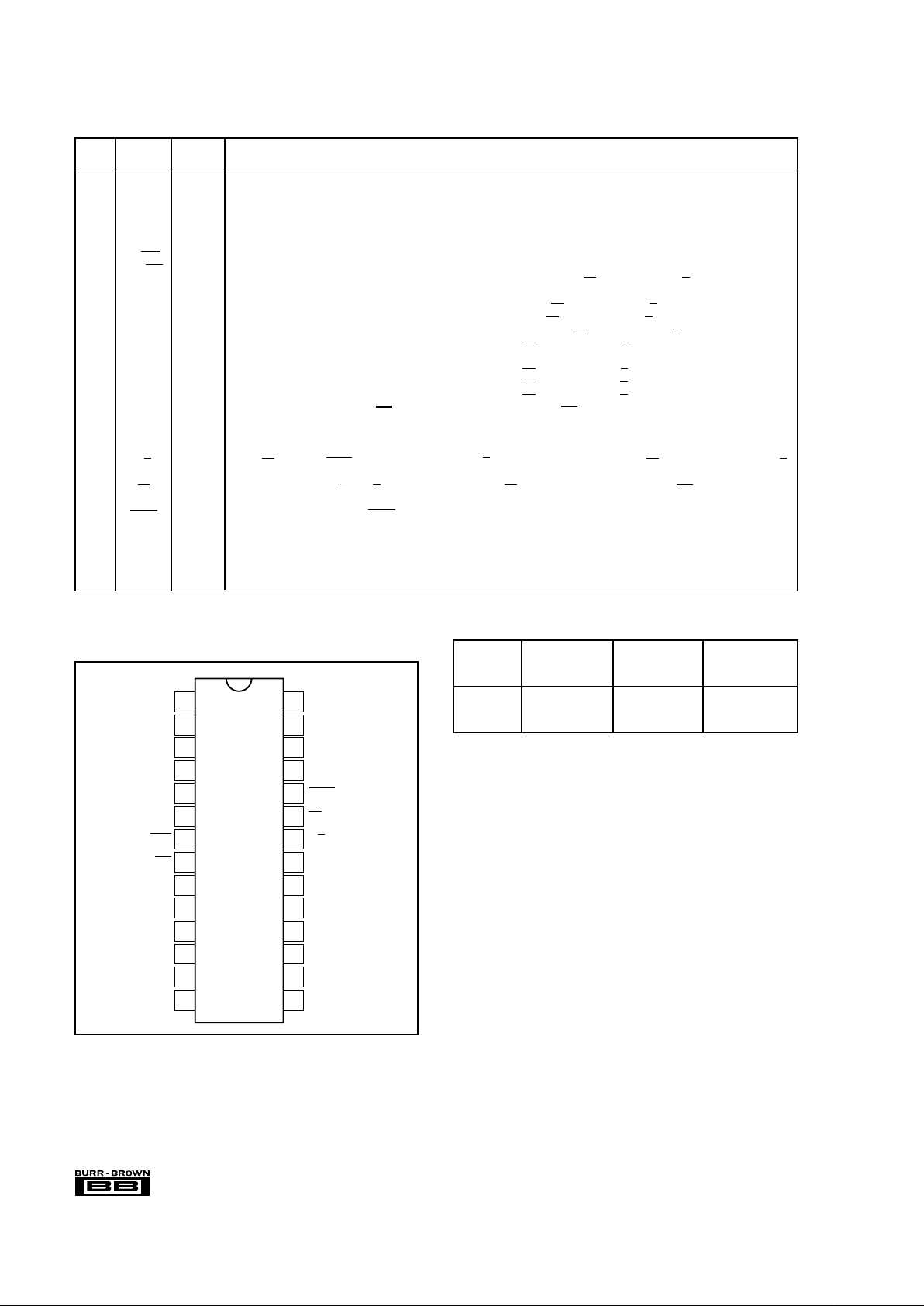

DIGITAL

PIN # NAME I/O DESCRIPTION

TABLE I. Pin Assignments.

ANALOG CONNECT R1INCONNECT R2

IN

INPUT VIA 200Ω VIA 100Ω

RANGE TO TO IMPEDANCE

±10V V

IN

CAP 45.7kΩ

0V to 5V AGND V

IN

20.0kΩ

0V to 4V V

IN

V

IN

21.4kΩ

TABLE II. Input Range Connections. See also Figure 7.

PIN CONFIGURATION

V

DIG

V

ANA

REFD

PWRD

BUSY

CS

R/C

BYTE

TAG

SDATA

DATACLK

D0

D1

D2

R1

IN

AGND1

R2

IN

CAP

REF

AGND2

SB/BTC

EXT/INT

D7

D6

D5

D4

D3

DGND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

ADS7806

1R1

IN

Analog Input. See Figure 7.

2 AGND1 Analog Sense Ground.

3R2

IN

Analog Input. See Figure 7.

4 CAP Reference Buffer Output. 2.2µF tantalum capacitor to ground.

5 REF Reference Input/Output. 2.2µF tantalum capacitor to ground.

6 AGND2 Analog Ground.

7 SB/BTC I Selects Straight Binary or Binary Two’s Complement for Output Data Format.

8 EXT/INT I External/Internal data clock select.

9 D7 O Data Bit 3 if BYTE is HIGH. Data bit 11 (MSB) if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW. Leave

unconnected when using serial output.

10 D6 O Data Bit 2 if BYTE is HIGH. Data bit 10 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.

11 D5 O Data Bit 1 if BYTE is HIGH. Data bit 9 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.

12 D4 O Data Bit 0 (LSB) if BYTE is HIGH. Data bit 8 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.

13 D3 O LOW if BYTE is HIGH. Data bit 7 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.

14 DGND Digital Ground.

15 D2 O LOW if BYTE is HIGH. Data bit 6 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.

16 D1 O LOW if BYTE is HIGH. Data bit 5 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.

17 D0 O LOW if BYTE is HIGH. Data bit 4 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.

18 DATACLK I/O Data Clock Output when EXT/INT is LOW. Data clock input when EXT/INT is HIGH.

19 SDATA O Serial Output Synchronized to DATACLK.

20 TAG I Serial Input When Using an External Data Clock.

21 BYTE I Selects 8 most significant bits (LOW) or 4 least significant bits (HIGH) on parallel output pins.

22 R/C I With CS LOW and BUSY HIGH, a Falling Edge on R/C Initiates a New Conversion. With CS LOW, a rising edge on R/C

enables the parallel output.

23 CS I Internally OR’d with R/C. If R/C is LOW, a falling edge on CS initiates a new conversion. If EXT/INT is LOW, this same

falling edge will start the transmission of serial data results from the previous conversion.

24 BUSY O At the start of a conversion, BUSY goes LOW and stays LOW until the conversion is completed and the digital outputs

have been updated.

25 PWRD I PWRD HIGH shuts down all analog circuitry except the reference. Digital circuitry remains active.

26 REFD I REFD HIGH shuts down the internal reference. External reference will be required for conversions.

27 V

ANA

Analog Supply. Nominally +5V. Decouple with 0.1µF ceramic and 10µF tantalum capacitors.

28 V

DIG

Digital Supply. Nominally +5V. Connect directly to pin 27. Must be ≤ V

ANA

.

5

®

ADS7806

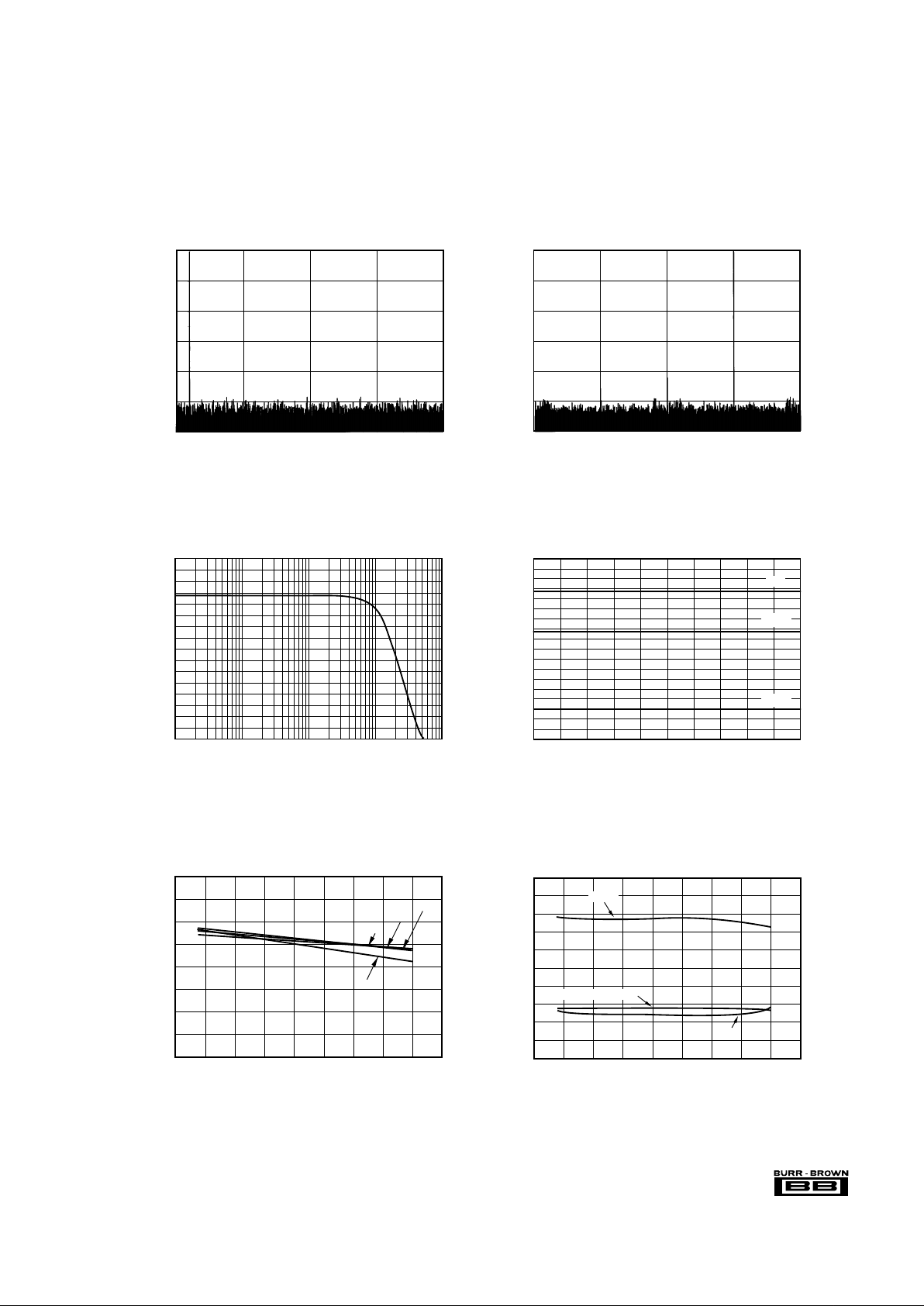

TYPICAL PERFORMANCE CURVES

TA = +25°C, fS = 40kHz, V

DIG

= V

ANA

= +5V, using internal reference and fixed resistors shown in Figure 7b, unless otherwise specified.

FREQUENCY SPECTRUM

(8192 Point FFT; f

IN

= 1kHz, 0dB)

Frequency (kHz)

Amplitude (dB)

0

–20

–40

–60

–80

–100

–120

0 5 10 15 20

SIGNAL-TO-(NOISE + DISTORTION)

vs INPUT FREQUENCY (f

IN

= 0dB)

90

80

70

60

50

40

30

20

10

SINAD (dB)

100 1k 10k 100k 1M

Input Signal Frequency (Hz)

10kHz

20kHz

30kHz

40kHz

SIGNAL-TO-(NOISE + DISTORTION) vs TEMPERATURE

(f

IN

= 1kHz, 0dB; fS = 10kHz to 40kHz)

74.0

73.9

73.8

73.7

73.6

–75 –50 –25 0 25 50 75 100 125 150

Temperature (°C)

SINAD (dB)

A.C. PARAMETERS vs TEMPERATURE

(f

IN

= 1kHz, 0dB)

110

105

100

95

90

85

80

75

70

65

60

–60

–65

–70

–75

–80

–85

–90

–95

–100

–105

–110

SFDR, SNR, and SINAD (dB)

THD (dB)

–75 –50 –25 0 25 50 75 100 125 150

Temperature (°C)

SFDR

SNR and SINAD

THD

FREQUENCY SPECTRUM

(8192 Point FFT; f

IN

= 15kHz, 0dB)

Frequency (kHz)

Amplitude (dB)

0

–20

–40

–60

–80

–100

–120

0 5 10 15 20

SIGNAL-TO-(NOISE + DISTORTION)

vs INPUT FREQUENCY AND INPUT AMPLITUDE

90

80

70

60

50

40

30

20

10

0

SINAD (dB)

02468101214161820

Input Signal Frequency (kHz)

0dB

–20dB

–60dB

6

®

ADS7806

3

2

1

0

–1

–2

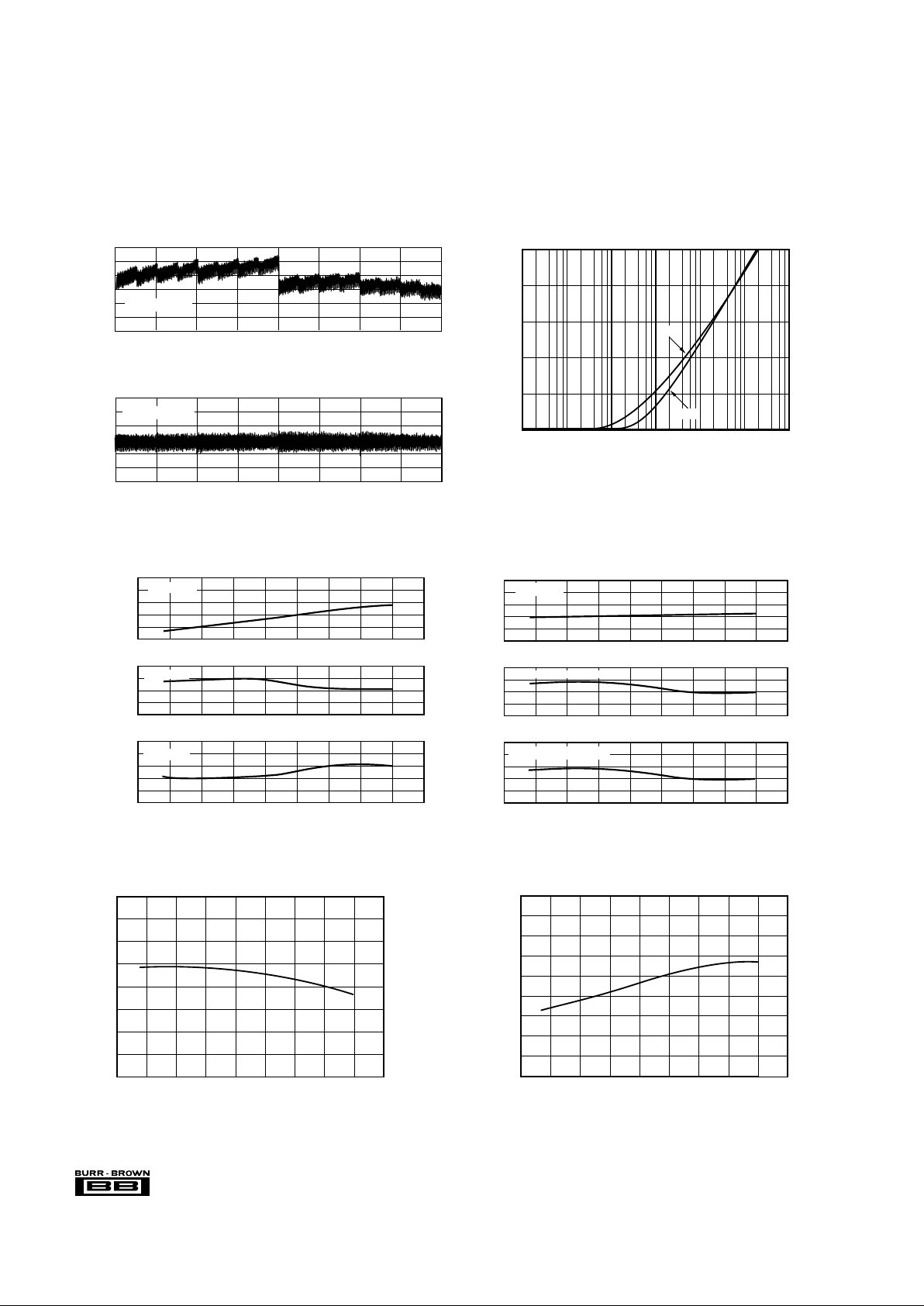

TYPICAL PERFORMANCE CURVES (CONT)

TA = +25°C, fS = 40kHz, V

DIG

= V

ANA

= +5V, using internal reference and fixed resistors shown in Figure 7b, unless otherwise specified.

0.10

0

–0.10

12-Bit LSBs

0

40953584

30722560

204815361024512

Decimal Code

0.10

0

–0.10

12-Bit LSBs

0 4095358430722560

204815361024512

Decimal Code

All Codes DNL

3

2

1

0

–1

–2

0.20

0

–0.20

Percent

From Ideal

mV From Ideal

ENDPOINT ERRORS (20V BIPOLAR RANGE)

Temperature (°C)

–50 –25 0 25

50 75 100 125

150

–75

Percent

From Ideal

0.20

0

–0.20

0.40

0.20

0

0.40

0.20

0

Percent

From Ideal

mV From Ideal

ENDPOINT ERRORS (UNIPOLAR RANGES)

Temperature (°C)

–75

–50 –25 0 25

50 75 100 125

150

Percent

From Ideal

All Codes INL

UPO Error

+FS Error (4V Range)

+FS Error (5V Range)

–FS Error

+FS Error

BPZ Error

POWER SUPPLY RIPPLE SENSITIVITY

INL/DNL DEGRADATION PER LSB OF P-P RIPPLE

Power Supply Ripple Frequency (Hz)

10

1

10

2

10

3

10

4

10

5

10

6

10

7

1

10–1

10–2

10–3

10–4

10

–5

Linearity Degradation (LSB/LSB)

INL

DNL

INTERNAL REFERENCE VOLTAGE vs TEMPERATURE

–75 –50 –25 0 25 50 75 100 125 150

2.520

2.515

2.510

2.505

2.500

2.495

2.490

2.485

2.480

Internal Reference (V)

Temperature (°C)

CONVERSION TIME vs TEMPERATURE

15.10

15.00

14.90

14.80

14.70

14.60

14.50

14.40

14.30

14.20

–75 –50 –25 0 25 50 75 100 125 150

Temperature (°C)

Conversion Time (µs)

Loading...

Loading...