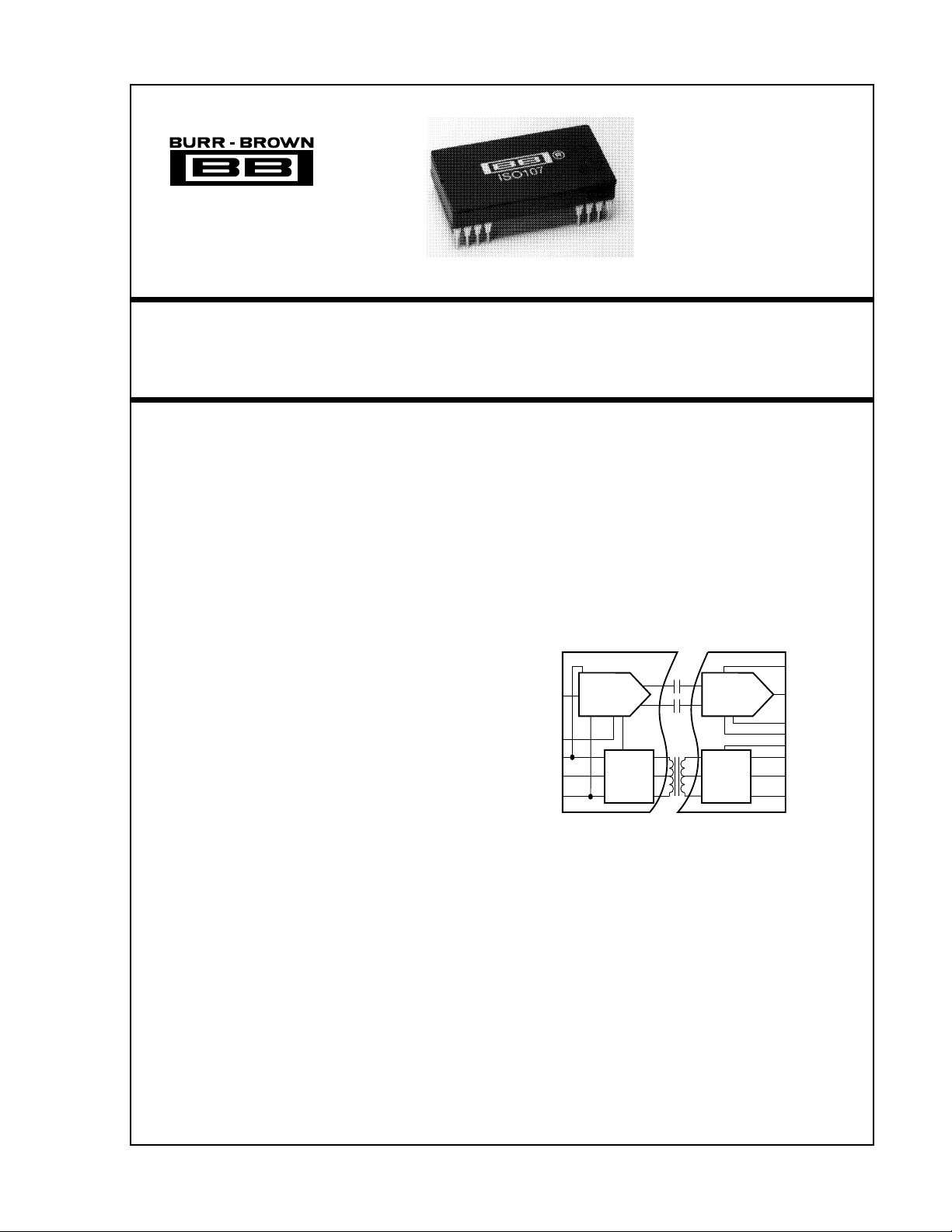

Burr Brown ISO107 Datasheet

Duty Cycle

Modulator

Oscillator

Driver

V

OUT

+V

CC1

Enable

–V

CC2

–V

CC1

Gnd 1

Com 1

V

IN

Sense

+V

CC2

Sync

Gnd 2

Rectifiers

Filters

Com 2

Sync

Duty Cycle

Demodulator

ISO107 BLOCK DIAGRAM

®

High-Voltage, Internally Powered

ISOLATION AMPLIFIER

ISO107

FEATURES

● SIGNAL AND POWER IN ONE

TRIPLE-WIDE PACKAGE

● 8000Vpk TEST VOLTAGE

● 2500Vrms CONTINUOUS AC BARRIER

RATING

APPLICATIONS

● MULTICHANNEL ISOLATED DATA

ACQUISITION

● BIOMEDICAL INSTRUMENTATION

● POWER SUPPLY AND MOTOR CONTROL

● GROUND LOOP ELIMINATION

● WIDE INPUT SIGNAL RANGE:

–10V to +10V

● WIDE BANDWIDTH: 20kHz Small Signal,

20kHz Full Power

● BUILT-IN ISOLATED POWER:

±10V to ±18V Input, ±50mA Output

● MULTICHANNEL SYNCHRONIZATION

CAPABILITY (TTL)

DESCRIPTION

The ISO107 isolation amplifier provides both signal

and power across an isolation barrier. The ceramic

side-brazed hybrid package contains a transformercoupled DC/DC converter and a capacitor-coupled

signal channel.

Extra power is available on the isolated input side for

external input conditioning circuitry. The converter is

protected from shorts to ground with an internal current limit, and the soft-start feature limits the initial

currents from the power source. Multiple-channel synchronization can be accomplished by applying a TTL

clock signal to paralleled Sync pins. The Enable con-

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706

Tel: (520) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

© 1989 Burr-Brown Corporation PDS-898C Printed in U.S.A. October, 1993

trol is used to turn off transformer drive while keeping

the signal channel demodulator active. This feature

provides a convenient way to reduce quiescent current

for low power applications.

The wide barrier pin spacing and internal insulation

allow for the generous 2500Vrms continuous rating.

Reliability is assured by 100% barrier breakdown

testing that conforms to UL544 test methods. Low

barrier capacitance minimizes AC leakage currents.

These specifications and built-in features make the

ISO107 easy to use, as well as providing for compact

PC board layouts.

SPECIFICATIONS

ELECTRICAL

TA = +25°C and V

PARAMETERS CONDITIONS MIN TYP MAX UNITS

ISOLATION

Rated Continuous Voltage

AC, 60Hz T

DC T

Test Breakdown, AC, 60Hz 10s 8000 Vpk

Isolation-Mode Rejection 2500Vrms, 60Hz 100 dB

Barrier Impedance 10

Leakage Current 240Vrms, 60Hz 1.2 2 µA

GAIN

Nominal 1 V/V

Initial Error ±0.1 ±0.25 % FSR

Gain vs Temperature ±50 ±120 ppm/°C

Nonlinearity ±0.01 ±0.025 % FSR

INPUT OFFSET VOLTAGE

Initial Offset ±20 ±50 mV

vs Temperature ±150 ±400 µV/°C

vs Power Supplies V

INPUT

Voltage Range Output Voltage in Range ±10 ±15 V

Resistance 200 kΩ

SIGNAL OUTPUT

Voltage Range ±10 ±12.5 V

Current Drive ±5 ±15 mA

Ripple Voltage, 800kHz Carrier (See Figure 4) 20 mVp-p

Capacitive Load Drive 1000 pF

Voltage Noise 4 µV/√Hz

FREQUENCY RESPONSE

Small Signal Bandwidth 20 kHz

Slew Rate 1.5 V/µs

Settling Time 0.1%, –10/10V 75 µs

POWER SUPPLIES

Rated Voltage, V

Voltage Range ±10 ±18 V

Input Current I

Ripple Current No Filter 10 mAp-p

Rated Output Voltage ±14.25 ±15 ±15.75 V

Output Current Balanced Load ±15 ±50 mA

Load Regulation Balanced Load 0.5 %/mA

Line Regulation 1.18 V/V

Output Voltage vs Temperature 10 mV/°C

Voltage Balance Error, ±V

Voltage Ripple No External Capacitors 10 mVp-p

Output Capacitive Load (See Figure 1) 1 µF

Sync Frequency Sync-Pin Grounded

TEMPERATURE RANGE

Specification –25 +85 °C

Operating –25 +85 °C

Storage –25 +125 °C

NOTES: (1) Conforms to UL544 test methods. 100% tested at 2500Vrms for 1 minute. (2) For other conditions, see Performance Curve, Input Current (+V

Current. Input Current (–V

1.2MHz and 2MHz with a duty-cycle greater than 25%.

= ±15V, ±15mA output current unless otherwise noted.

CC2

(1)

to T

MIN

to T

MIN

2121VDC 160 dB

= ±10V to ±18V ±2 mV/V

CC2

CC2

= ±15mA

O

C

= 1µF 3 mAp-p

IN

Single 30 100 mA

CC1

) is constant at –4.5mA (typ) for all output currents. (3) If using external synchronization with a TTL-level clock, frequency should be between

CC2

MAX

MAX

2500 Vrms

3500 VDC

12

|| 13 Ω || pF

±15 V

(2)

+75/–4.5 mA

0.05 %

(3)

1.6 MHz

CC2

) vs Output

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes

no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change

without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant

any BURR-BROWN product for use in life support devices and/or systems.

®

ISO107

2

®

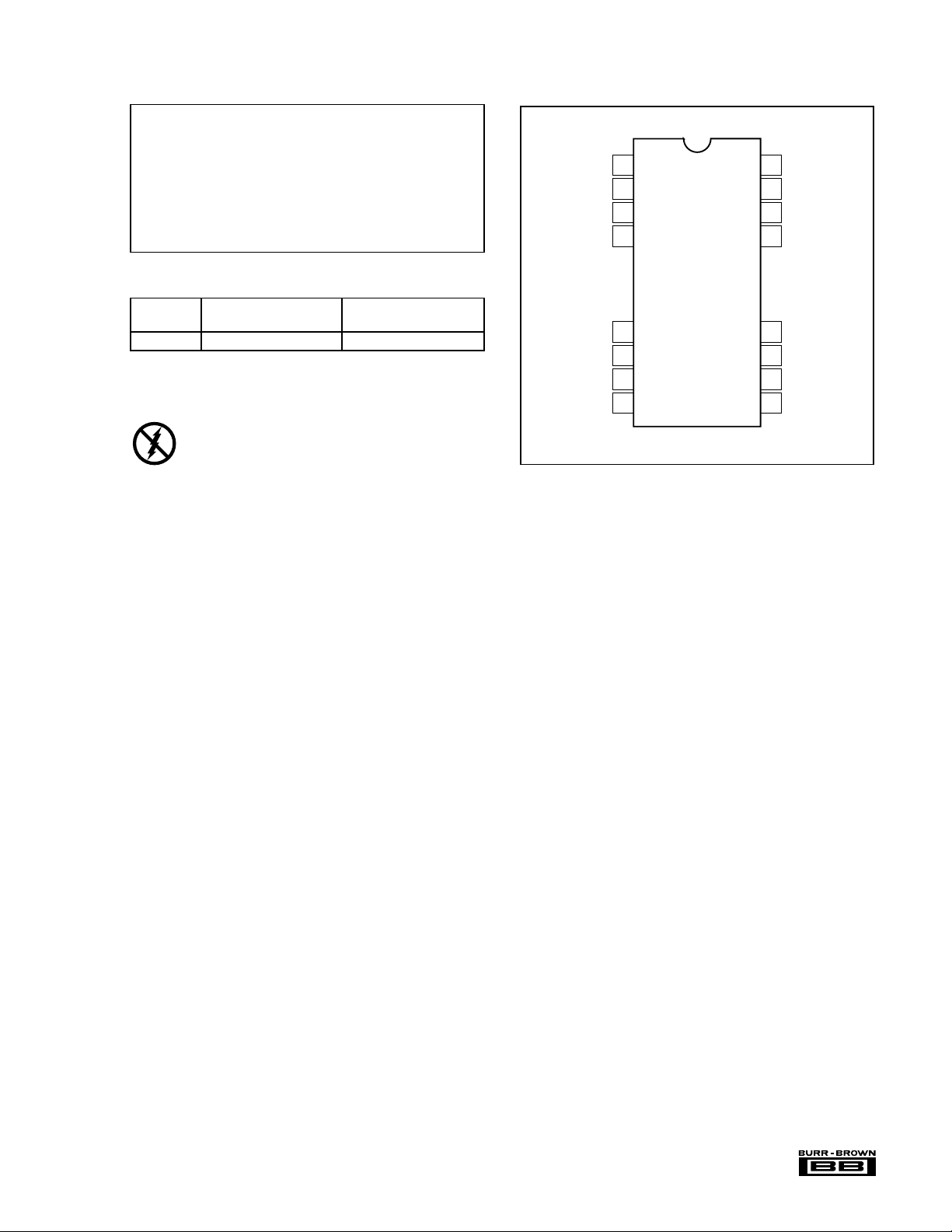

ABSOLUTE MAXIMUM RATINGS

1

2

3

4

32

31

30

29

20

19

18

17

13

14

15

16

NC

+V

NC

–V

CC1

CC1

Com 2

V

Sense

Gnd 2

OUT

NC

Gnd 1

V

Com 1

IN

–V

Sync*

+V

Enable

CC2

CC2

*Operation requires that this pin be grounded or driven with TTL levels.

Supply Without Damage .................................................................... ±18V

, Sense Voltage ............................................................................ ±50V

V

IN

Com 1 to Gnd 1 or Com 2 to Gnd 2 ........................................... ±200mV

Enable, Sync ...........................................................................0V to +V

Continuous Isolation Voltage ..................................................... 2500Vrms

, dv/dt ...................................................................................... 20kV/µs

V

ISO

Junction Temperature ...................................................................... 150°C

Storage Temperature ..................................................... –25°C to +125°C

Lead Temperature, (soldering, 10s)................................................ 300°C

Output Short to Gnd 2 Duration.............................................. Continuous

±V

to Gnd 1 Duration .......................................................... Continuous

CC1

PIN CONFIGURATION

Top View DIP

CC2

PACKAGE INFORMATION

MODEL PACKAGE NUMBER

ISO107 32-Pin Side-Braze Ceramic 210

NOTE: (1) For detailed drawing and dimension table, please see end of data

sheet, or Appendix D of Burr-Brown IC Data Book.

(1)

PACKAGE DRAWING

ELECTROSTATIC

DISCHARGE SENSITIVITY

Any integrated circuit can be damaged by ESD. Burr-Brown

recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and

installation procedures can cause damage.

ESD damage can range from subtle performance degradation

to complete device failure. Precision integrated circuits may

be more susceptible to damage because very small parametric

changes could cause the device not to meet published specifications.

3

ISO107

Loading...

Loading...