5

www.teknisi-indonesia.com

4

IH618-MHS

3

H61MGP

REV 6.1

2

1

PAGE

1

2

D D

3

4

5

6

7

8

9

10

11

12

13

14

15

16

C C

17

18

19

20

21

22

23

24

25

26

27

28

29

30

B B

31

32

33

34

35

36

37

38

39

40

CONTENTS

INDEX

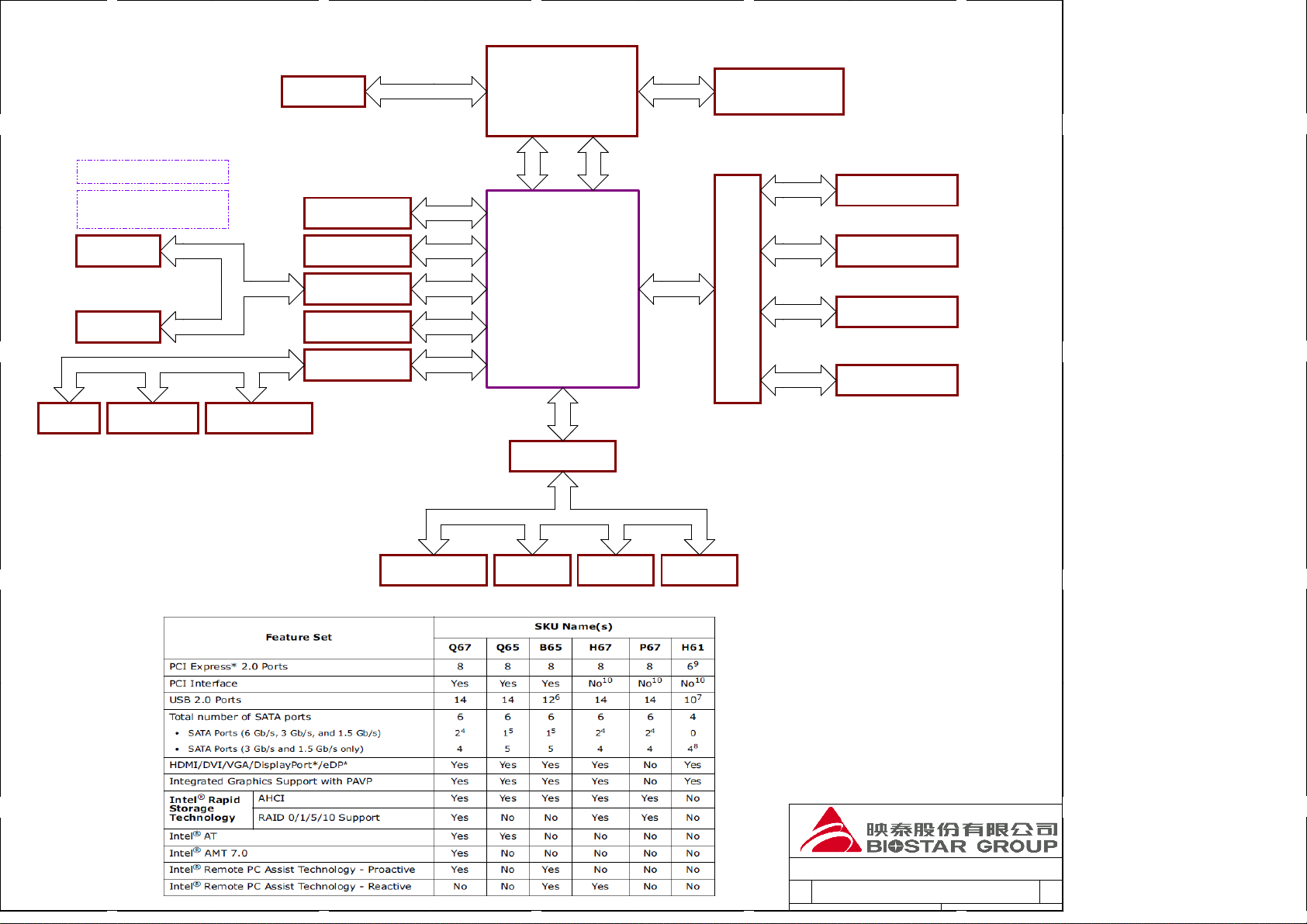

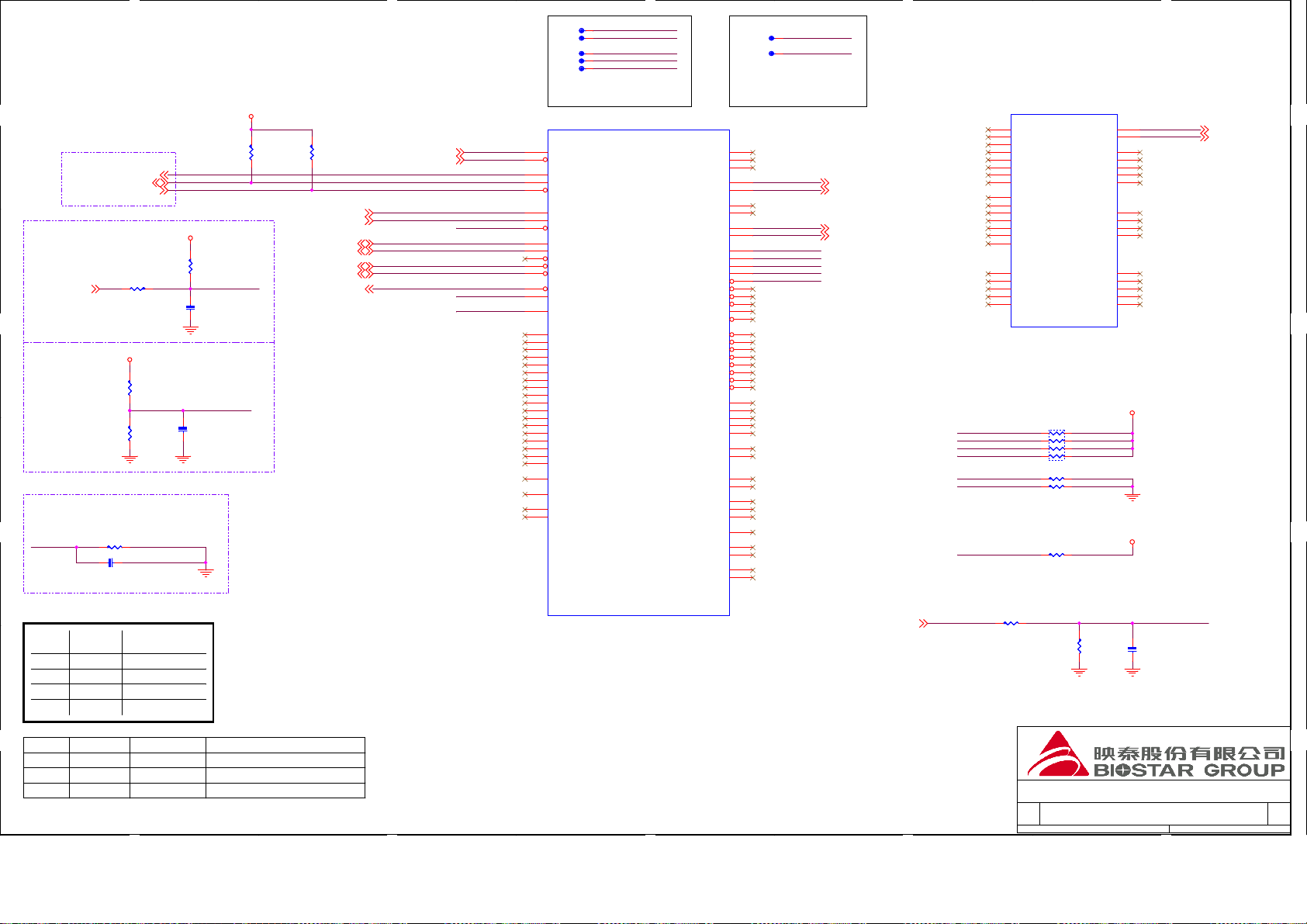

BLOCK DIAGRAM

POW ER DELIV ERY

CPU PCIEX1 6/DMI/FDI

CPU DDR CHANNEL A

CPU DDR CHANNEL B

CPU MISC

CPU POWER & GND

DDR3 DIMMA1/A2

DDR3 DIMMB1/B2

PCH PCI

PCH DMI/PCIE/USB

PCH CL INK/S ATA/CPU HOST

PCH LPC/HDA/SPI/MISC

PCH NVRAM & FDILINK

PCH VGA/DISPLA Y PORT

PCH CL OCK BUFFER

PCH POWER

PCH GND

SPI ROM/BA T

PCIEX 16 S LOT

PCIEX 1 SL OT

VGA/DVI CO NNECTOR

AUDIO CODEC VT170 8B

AUDIO CONNECTOR

LAN RTL8111E/8105E

SUPERIO ITE8728

SUPERIO PS2/CO M/LPT

SUPERIO FA N CONTROL

USB P ORT

24PIN POW ER CONN&FP

RESUME RESET LOG IC

ACPI POW ER CONTROL

LINEA R POWE R

MEMORY DC-DC Conver

VTT DC-DC Conver

VCORE VREG1

VCORE VREG2

OVER VOLTAGE

BOM

CPU:

Intel Sandy/Ivy Bridge processors in LGA1155 Package 95W

System Chipset:

Cugar Point H61

Main Memory:

Dual Channel/DDR-III*2(Max 16GB) 1066/1333

DDR3-1333 /1066 /800

Onboard Device:

Super I/O:IT8728

LAN:Realtek 8111G

HD Codec:ALC662

Power solution:

CPU Voltage Regulators:2phase by ISL6363

AXG voltage Regulators:1phase by ISL6363

VTT voltage Regulators:1Phase by uP1514

DDR voltage Regulators:1Phase by uP1514

Expansion Slots:

PCI EXPRESS 16X SLOT*1

PCI EXPRESS 1X SLOT*2

REAR IO:

PS/2 KB/MS

HDMI Port

VGA

2 layer USB2.0 Ports

2 layer USB2.0 + Gb RJ-45 Ports

Audio Jackets

LPT1

COM1

HW Engineer

HW Leader1

HW Leader2

Date

Date

Date

A A

5

Front I/O:

SATA2 * 4

USB Header * 2

CPU /System1

Front Audio Header

4

『

BIOSTAR'S PROPRIETARY INFORMATION

『Any unauthorized use, reproduction,

duplication, or disclosure of this

document will be subject to the

applicable civil and/or criminal

penalties.

3

』

2

』

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

INDEX

INDEX

INDEX

IH618-MHS

IH618-MHS

IH618-MHS

1 42Wednesday, December 18, 2013

1 42Wednesday, December 18, 2013

1 42Wednesday, December 18, 2013

6.0

6.0

6.0

1

5

www.teknisi-indonesia.com

4

3

2

1

Sandy Bridge

PEG X16 PCIE GEN2/3 X16

Ivy Bridge

LGA 1155 SOCKET

1066/1333

Channel A DIMM X1

Channel B DIMM X1

D D

Ports 0 & 1 6 Gb/s Support

Cost Reduced HDMI Level

Shifter When Trace length

less than 9.25'

DVI/HDMI

PORTS

VGA PORT

PORT B/D PEG X1 CONN

C C

3 JACKS

SPDIF OUT PORT Front Audio Header

B B

USB 2.0 PORTS

X8

SATA2.0 PORTS X4

Dual Independent

Dispaly

SPI FLASH 32M

HDC CODEC

VT1708B

CPU SMART FAN X1

SYSTEM FAN X1

DMI FDI

Cougar Point

PCH

LPC

ITE8728

PS2 KB/MS COM Port CIR Header

5GT/s

8 PCIE2.0 PORTS

GIGA LAN RTL8111EL

X16 SLOT X1

IT8893E

PCI SLOTSX2

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

IH618-MHS

IH618-MHS

IH618-MHS

2 42Wednesday, December 18, 2013

2 42Wednesday, December 18, 2013

2 42Wednesday, December 18, 2013

6.0

6.0

6.0

5

www.teknisi-indonesia.com

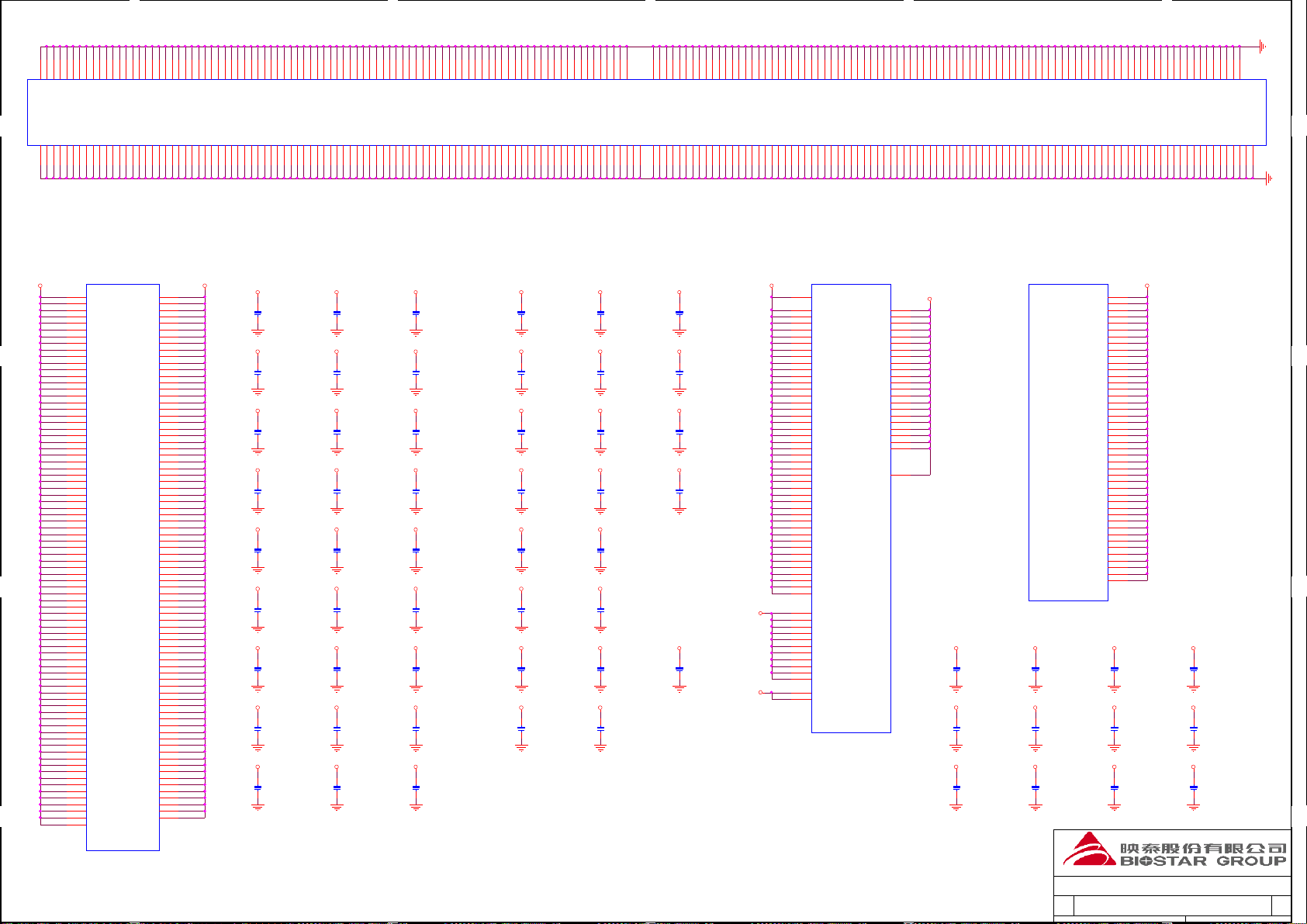

Change from V6.2

1, Page 21,22,26,32 : del +3V3_AUX regulator, change net_name +3v3_DUAL

2, Page 23 : del VSYNC & HSYNC LEVEL SHIFT 74HC08

3, Page 24 : co-lay VT1708B/ALC662/ALC662VD

D D

4, Page 26 : Add Switching regulator disabled cricuit

5, Page 31 : FP_RST circuit modify

4

3

2

1

C C

B B

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

5

4

3

2

CHANGE LIST

CHANGE LIST

CHANGE LIST

IH618-MHS

IH618-MHS

IH618-MHS

1

6.0

6.0

6.0

3 42Wednesday, December 18, 2013

3 42Wednesday, December 18, 2013

3 42Wednesday, December 18, 2013

5

www.teknisi-indonesia.com

www.teknisi-indonesia.com

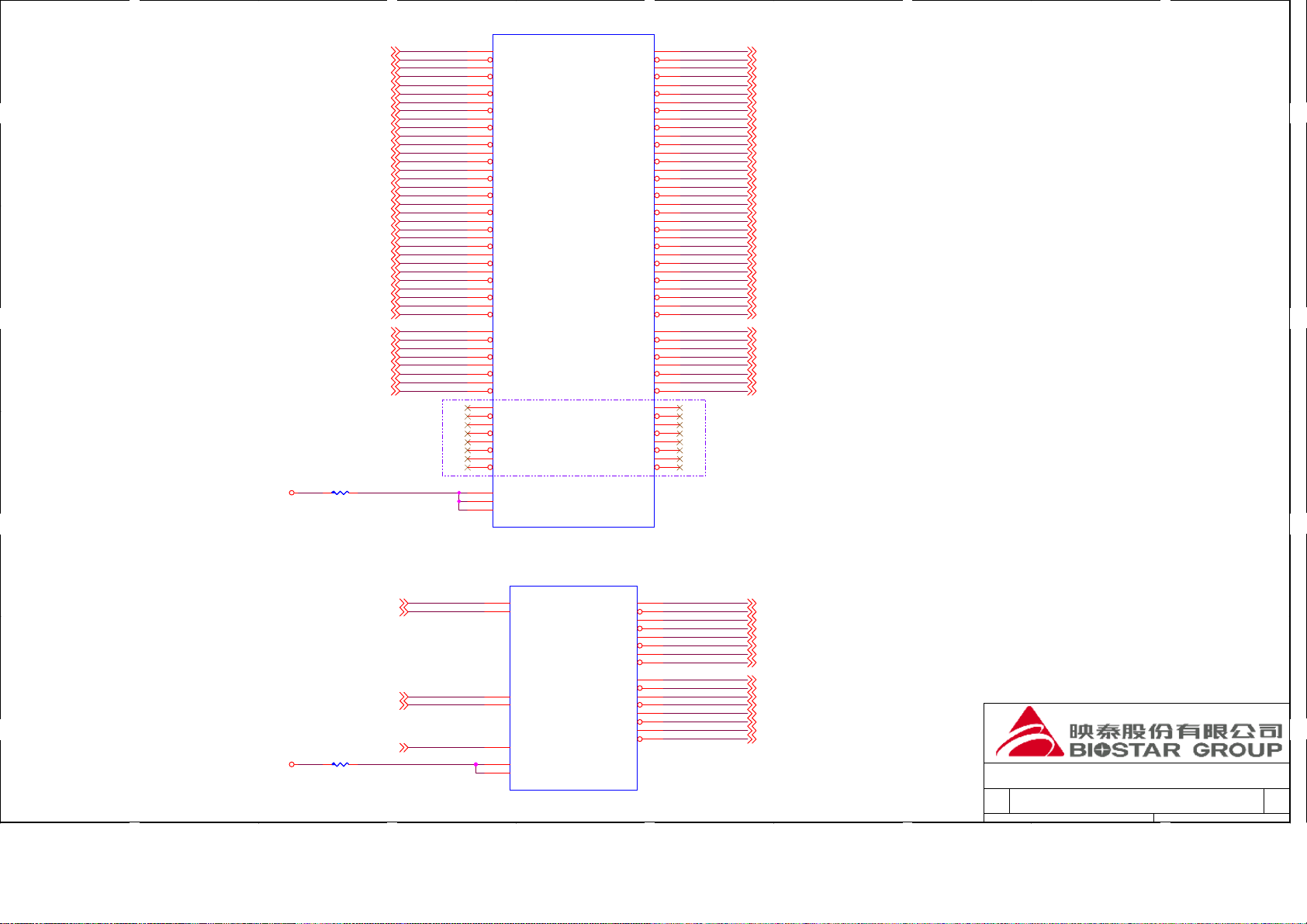

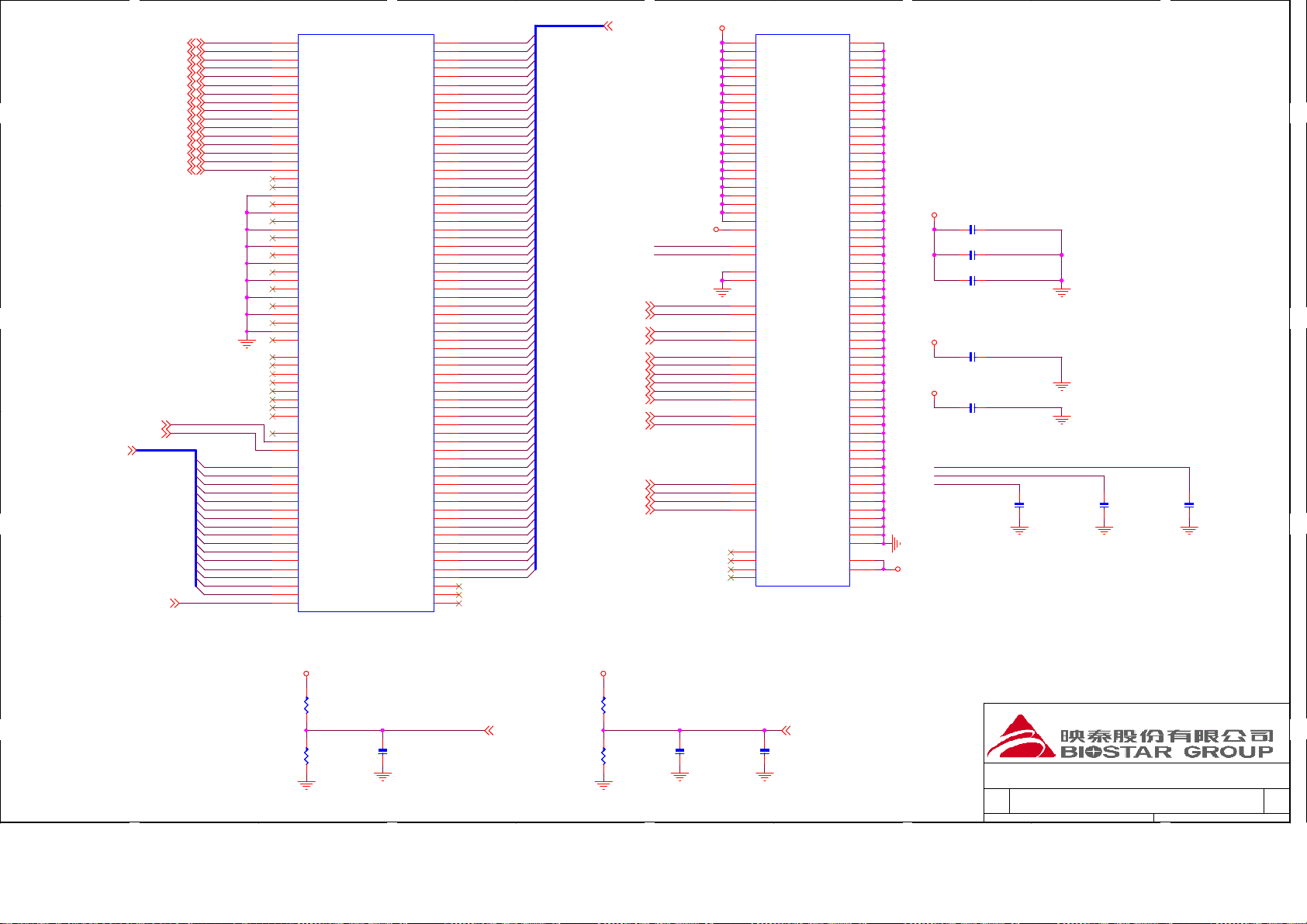

EXP_A_RX_0_DP21

EXP_A_RX_0_DN21

EXP_A_RX_1_DP21

EXP_A_RX_1_DN21

EXP_A_RX_2_DP21

EXP_A_RX_2_DN21

EXP_A_RX_3_DP21

D D

C C

V_CPU_VCCIO

B B

PEG_ICOMPI & PEG_RCOMPO: 4m il /15mil;

PEG_ICOMPO : 12m il /15m il

LESS THAN 500mil

SHORT B4 & C4 TOGETHER, ROUTE AS A SINGLE 4 MIL TR ACE TO R 1

ROUTE B5 TO R1 AS A SEPERATE 10 MIL TRACE

EXP_A_RX_3_DN21

EXP_A_RX_4_DP21

EXP_A_RX_4_DN21

EXP_A_RX_5_DP21

EXP_A_RX_5_DN21

EXP_A_RX_6_DP21

EXP_A_RX_6_DN21

EXP_A_RX_7_DP21

EXP_A_RX_7_DN21

EXP_A_RX_8_DP21

EXP_A_RX_8_DN21

EXP_A_RX_9_DP21

EXP_A_RX_9_DN21

EXP_A_RX_10_DP21

EXP_A_RX_10_DN21

EXP_A_RX_11_DP21

EXP_A_RX_11_DN21

EXP_A_RX_12_DP21

EXP_A_RX_12_DN21

EXP_A_RX_13_DP21

EXP_A_RX_13_DN21

EXP_A_RX_14_DP21

EXP_A_RX_14_DN21

EXP_A_RX_15_DP21

EXP_A_RX_15_DN21

DMI_IT_MR_0_DP12

DMI_IT_MR_0_DN12

DMI_IT_MR_1_DP12

DMI_IT_MR_1_DN12

DMI_IT_MR_2_DP12

DMI_IT_MR_2_DN12

DMI_IT_MR_3_DP12

DMI_IT_MR_3_DN12

CR1 24.9 1% 0402CR1 24.9 1% 0402

FDI_FSYNC_015

FDI_LSYNC_015

FDI_FSYNC_115

FDI_LSYNC_115

A A

V_CPU_VCCIO

CR2 24.9 1% 0402CR2 24.9 1% 0402

5

4

CPU1C

CPU1C

BIOSTAR_D V1_4

B11

B12

D12

D11

C10

C9

E10

E9

B8

B7

C6

C5

A5

A6

E2

E1

F4

F3

G2

G1

H3

H4

J1

J2

K3

K4

L1

L2

M3

M4

N1

N2

W5

W4

V3

V4

Y3

Y4

AA4

AA5

P3

P4

R2

R1

T4

T3

U2

U1

PEG_RCOMP

FDI_INT15

FDI_RCOMP

B5

C4

B4

BIOSTAR_D V1_4

PEG_RX_ 0

PEG_RX# _0

PEG_RX_ 1

PEG_RX# _1

PEG_RX_ 2

PEG_RX# _2

PEG_RX_ 3

PEG_RX# _3

PEG_RX_ 4

PEG_RX# _4

PEG_RX_ 5

PEG_RX# _5

PEG_RX_ 6

PEG_RX# _6

PEG_RX_ 7

PEG_RX# _7

PEG_RX_ 8

PEG_RX# _8

PEG_RX_ 9

PEG_RX# _9

PEG_RX_ 10

PEG_RX# _10

PEG_RX_ 11

PEG_RX# _11

PEG_RX_ 12

PEG_RX# _12

PEG_RX_ 13

PEG_RX# _13

PEG_RX_ 14

PEG_RX# _14

PEG_RX_ 15

PEG_RX# _15

DMI_RX_0

DMI_RX#_ 0

DMI_RX_1

DMI_RX#_ 1

DMI_RX_2

DMI_RX#_ 2

DMI_RX_3

DMI_RX#_ 3

PE_RX_ 0

PE_RX# _0

PE_RX_ 1

PE_RX# _1

PE_RX_ 2

PE_RX# _2

PE_RX_ 3

PE_RX# _3

PEG_ICOMPO

PEG_RCOMPO

PEG_COMPI

LGA 1155 SOCKET

LGA 1155 SOCKET

CPU1D

CPU1D

AC5

FDI_FSY NC_0

AC4

FDI_LS YNC_0

AE5

FDI_FSY NC_1

AE4

FDI_LS YNC_1

AG3

FDI_INT

AE2

FDI_COMPI O

AE1

FDI_ICOMP O

LGA 1155 SOCKET

LGA 1155 SOCKET

PEGDMI

PEGDMI

GEN

GEN

BIOSTAR_D V1_4

BIOSTAR_D V1_4

FDI_TX#_ 0

FDI_TX#_ 1

FDI_TX#_ 2

FDI_TX#_ 3

FDI_TX#_ 4

FDI_TX#_ 5

FDI_TX#_ 6

FDI_TX#_ 7

FDI

FDI

LINK

LINK

4/10

4/10

FDI_TX_0

FDI_TX_1

FDI_TX_2

FDI_TX_3

FDI_TX_4

FDI_TX_5

FDI_TX_6

FDI_TX_7

4

PEG_TX_0

PEG_TX#_ 0

PEG_TX_1

PEG_TX#_ 1

PEG_TX_2

PEG_TX#_ 2

PEG_TX_3

PEG_TX#_ 3

PEG_TX_4

PEG_TX#_ 4

PEG_TX_5

PEG_TX#_ 5

PEG_TX_6

PEG_TX#_ 6

PEG_TX_7

PEG_TX#_ 7

PEG_TX_8

PEG_TX#_ 8

PEG_TX_9

PEG_TX#_ 9

PEG_TX_1 0

PEG_TX#_ 10

PEG_TX_1 1

PEG_TX#_ 11

PEG_TX_1 2

PEG_TX#_ 12

PEG_TX_1 3

PEG_TX#_ 13

PEG_TX_1 4

PEG_TX#_ 14

PEG_TX_1 5

PEG_TX#_ 15

DMI_TX_0

DMI_TX#_0

DMI_TX_1

DMI_TX#_1

DMI_TX_2

DMI_TX#_2

DMI_TX_3

DMI_TX#_3

PE_TX_0

PE_TX#_0

PE_TX_1

PE_TX#_1

PE_TX_2

PE_TX#_2

PE_TX_3

PE_TX#_3

3/10

3/10

3

C13

C14

E14

E13

G14

G13

F12

F11

J14

J13

D8

D7

D3

C3

E6

E5

F8

F7

G10

G9

G5

G6

K7

K8

J5

J6

M8

M7

L6

L5

N5

N6

V7

V6

W7

W8

Y6

Y7

AA7

AA8

P8

P7

T7

T8

R6

R5

U5

U6

AC8

AC7

AC2

AC3

AD2

AD1

AD4

AD3

AD7

AD6

AE7

AE8

AF3

AF2

AG2

AG1

For P67,all the FDI signals FDI_T X, FDI_F SYNC, FD I_LSYNC and

FDI_INT signals on the CPU and the PCH can be left as No

connect for solutions not using integ rated grap hics./DG98

PEG : (18)16/5/5/5/16(18) 80ohm

EXP_A_TX_0_DP 21

EXP_A_TX_0_DN 21

EXP_A_TX_1_DP 21

EXP_A_TX_1_DN 21

EXP_A_TX_2_DP 21

EXP_A_TX_2_DN 21

EXP_A_TX_3_DP 21

EXP_A_TX_3_DN 21

EXP_A_TX_4_DP 21

EXP_A_TX_4_DN 21

EXP_A_TX_5_DP 21

EXP_A_TX_5_DN 21

EXP_A_TX_6_DP 21

EXP_A_TX_6_DN 21

EXP_A_TX_7_DP 21

EXP_A_TX_7_DN 21

EXP_A_TX_8_DP 21

EXP_A_TX_8_DN 21

EXP_A_TX_9_DP 21

EXP_A_TX_9_DN 21

EXP_A_TX_10_DP 21

EXP_A_TX_10_DN 21

EXP_A_TX_11_DP 21

EXP_A_TX_11_DN 21

EXP_A_TX_12_DP 21

EXP_A_TX_12_DN 21

EXP_A_TX_13_DP 21

EXP_A_TX_13_DN 21

EXP_A_TX_14_DP 21

EXP_A_TX_14_DN 21

EXP_A_TX_15_DP 21

EXP_A_TX_15_DN 21

DMI_MT_IR_0_DP 12

DMI_MT_IR_0_DN 12

DMI_MT_IR_1_DP 12

DMI_MT_IR_1_DN 12

DMI_MT_IR_2_DP 12

DMI_MT_IR_2_DN 12

DMI_MT_IR_3_DP 12

DMI_MT_IR_3_DN 12

DMI : (15)12/4/5/4/12(15) 85ohm

PCIE X4 LANES ARE NOT SUPPORTED ON DT CPU SKUS

FDI_TX_0_DP 15

FDI_TX_0_DN 15

FDI_TX_1_DP 15

FDI_TX_1_DN 15

FDI_TX_2_DP 15

FDI_TX_2_DN 15

FDI_TX_3_DP 15

FDI_TX_3_DN 15

FDI_TX_4_DP 15

FDI_TX_4_DN 15

FDI_TX_5_DP 15

FDI_TX_5_DN 15

FDI_TX_6_DP 15

FDI_TX_6_DN 15

FDI_TX_7_DP 15

FDI_TX_7_DN 15

3

2

2

1

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU PCIEX16/DMI/FDI

CPU PCIEX16/DMI/FDI

CPU PCIEX16/DMI/FDI

IH618-MHS

IH618-MHS

IH618-MHS

4 42Wednesday, December 18, 2013

4 42Wednesday, December 18, 2013

4 42Wednesday, December 18, 2013

1

6.0

6.0

6.0

5

www.teknisi-indonesia.com

4

3

2

1

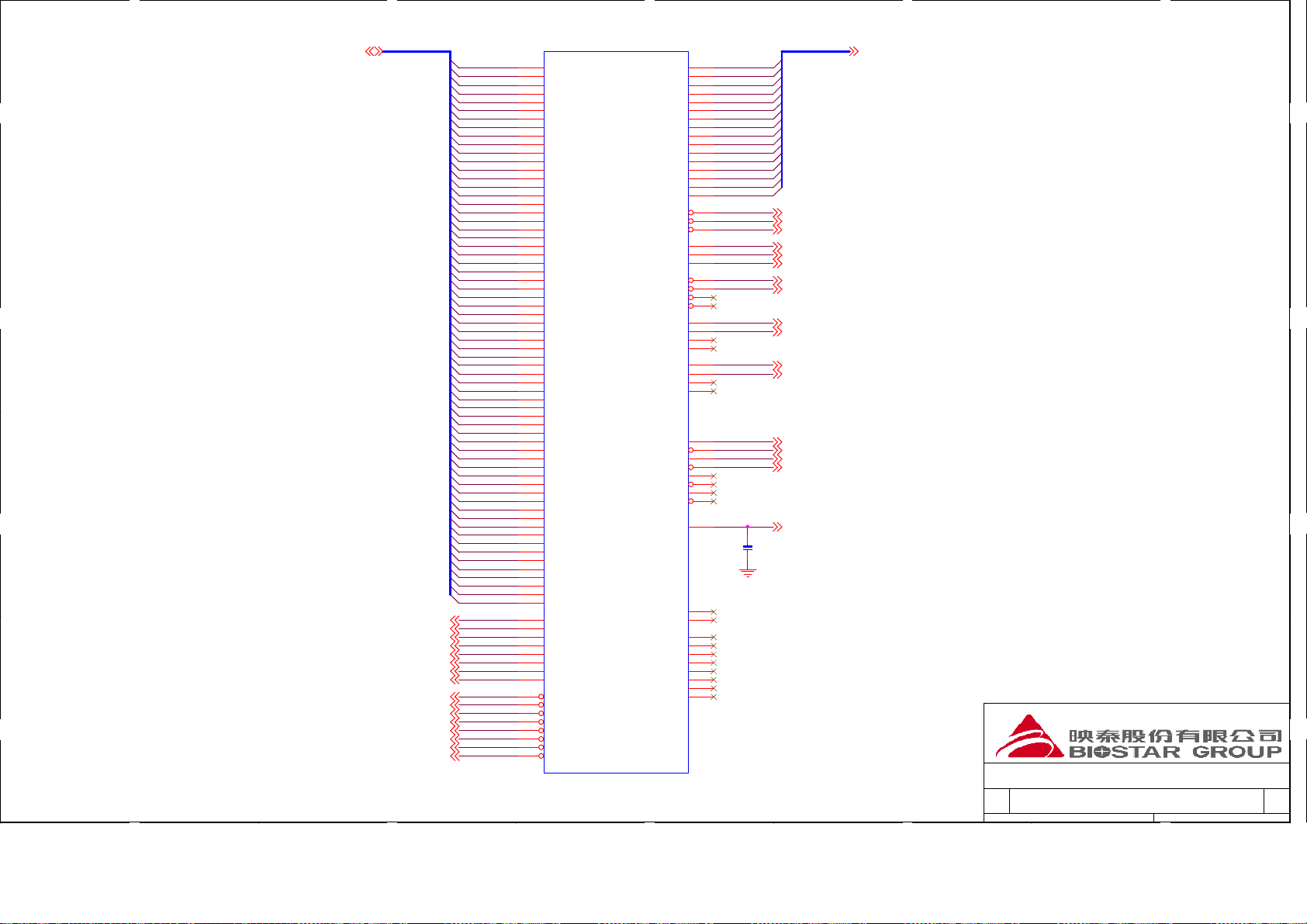

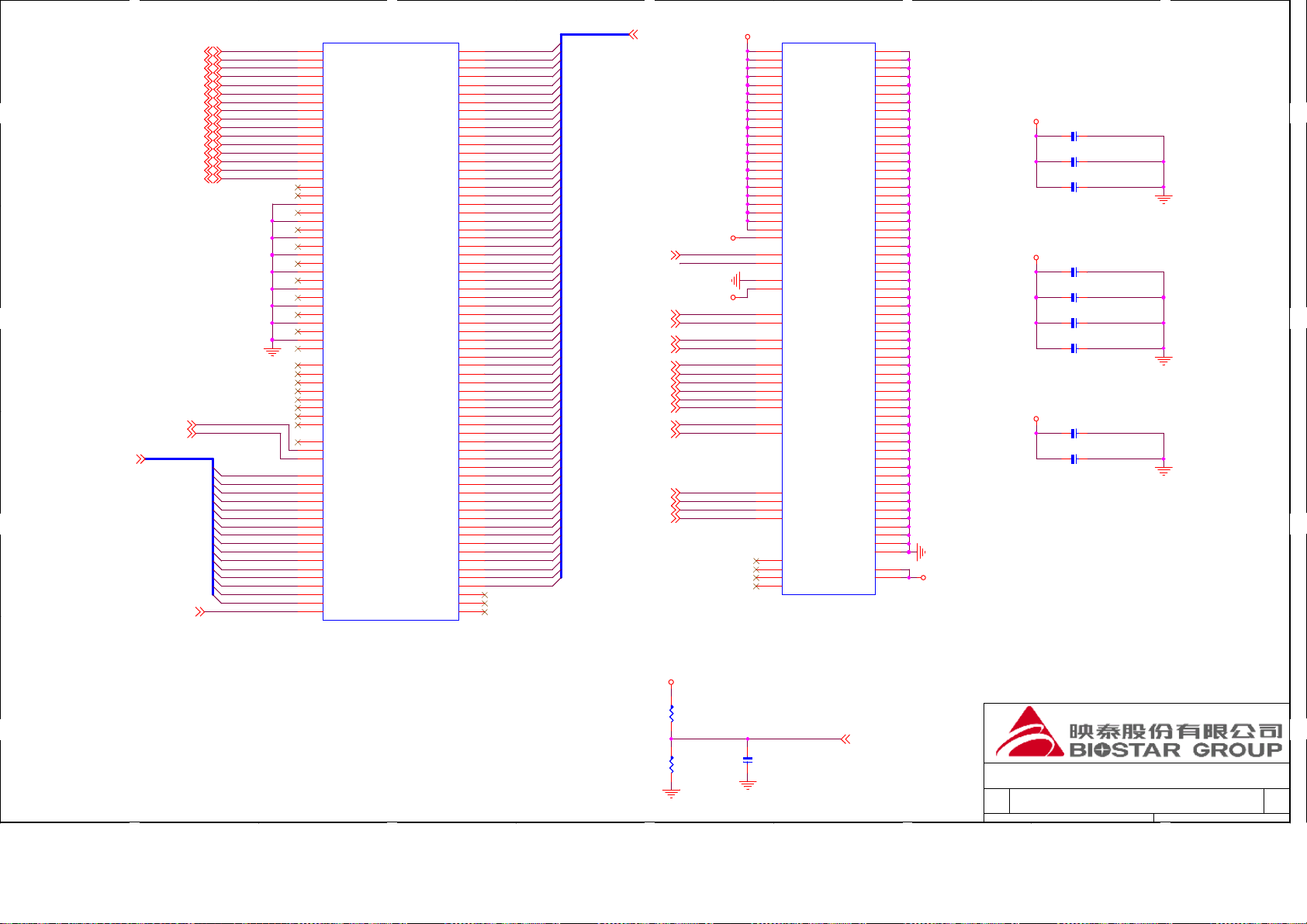

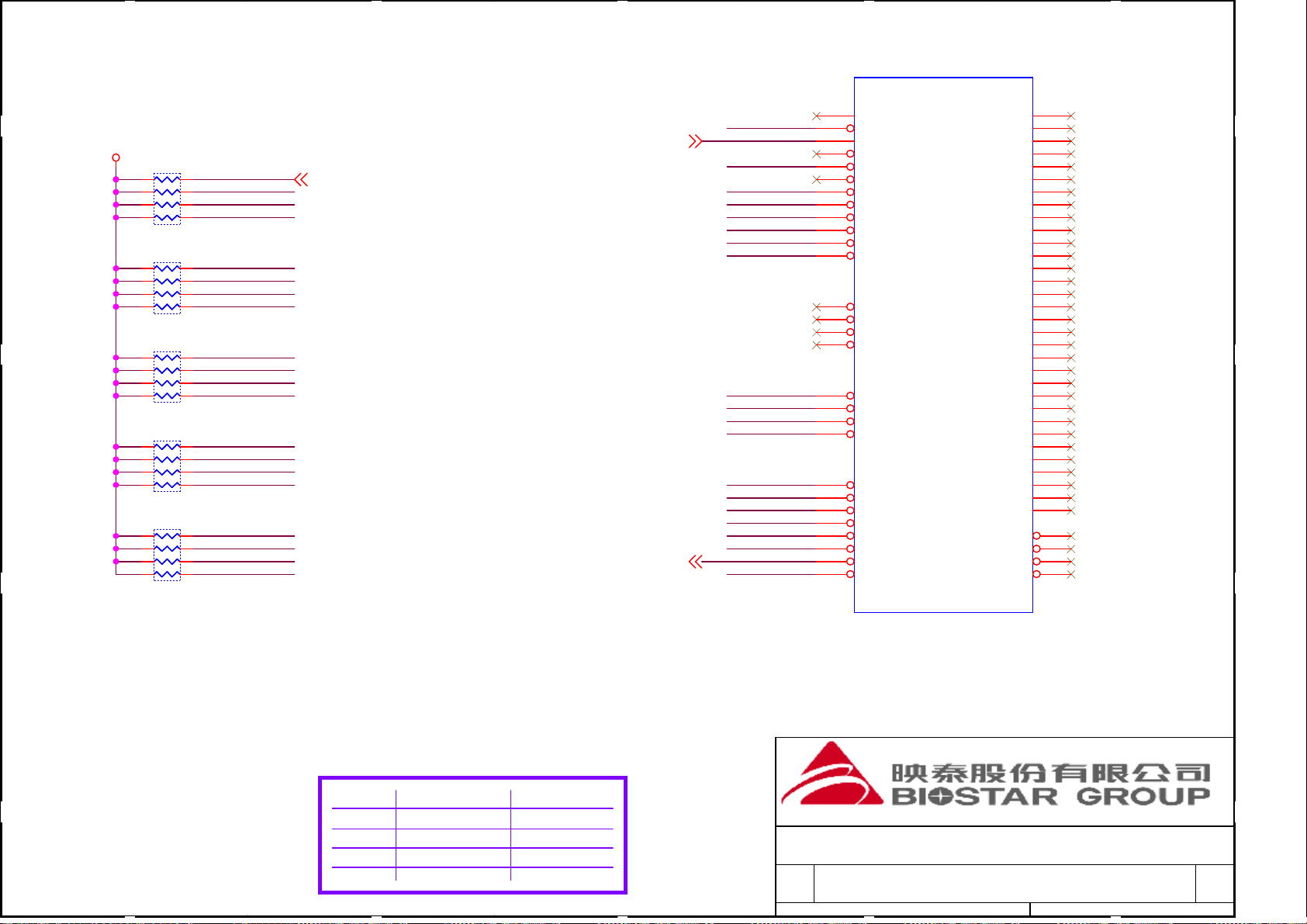

M_DATA_A[0..63]9

D D

C C

B B

A A

5

M_DATA_A[0..63]

M_DQS_A_DP09

M_DQS_A_DP19

M_DQS_A_DP29

M_DQS_A_DP39

M_DQS_A_DP49

M_DQS_A_DP59

M_DQS_A_DP69

M_DQS_A_DP79

M_DQS_A_DN09

M_DQS_A_DN19

M_DQS_A_DN29

M_DQS_A_DN39

M_DQS_A_DN49

M_DQS_A_DN59

M_DQS_A_DN69

M_DQS_A_DN79

4

M_DATA_A0

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DATA_A8

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

M_DATA_A16

M_DATA_A17

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

M_DATA_A22

M_DATA_A23

M_DATA_A24

M_DATA_A25

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

M_DATA_A30

M_DATA_A31

M_DATA_A32

M_DATA_A33

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A37

M_DATA_A38

M_DATA_A39

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

M_DATA_A44

M_DATA_A45

M_DATA_A46

M_DATA_A47

M_DATA_A48

M_DATA_A49

M_DATA_A50

M_DATA_A51

M_DATA_A52

M_DATA_A53

M_DATA_A54

M_DATA_A55

M_DATA_A56

M_DATA_A57

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A61

M_DATA_A62

M_DATA_A63

AJ3

AJ4

AL3

AL4

AJ2

AJ1

AL2

AL1

AN1

AN4

AR3

AR4

AN2

AN3

AR2

AR1

AV2

AW3

AV5

AW5

AU2

AU3

AU5

AY5

AY7

AU7

AV9

AU9

AV7

AW7

AW9

AY9

AU35

AW37

AU39

AU36

AW35

AY36

AU38

AU37

AR40

AR37

AN38

AN37

AR39

AR38

AN39

AN40

AL40

AL37

AJ38

AJ37

AL39

AL38

AJ39

AJ40

AG40

AG37

AE38

AE37

AG39

AG38

AE39

AE40

AK3

AP3

AW4

AV8

AV37

AP38

AK38

AF38

AK2

AP2

AV4

AW8

AV36

AP39

AK39

AF39

CPU1A

CPU1A

BIOSTAR_D V1_4

BIOSTAR_D V1_4

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

LGA 1155 SOCKET

LGA 1155 SOCKET

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_WE#

SA_CAS#

SA_RAS#

SA_BS_0

SA_BS_1

SA_BS_2

SA_CS#_0

SA_CS#_1

SA_CS#_2

SA_CS#_3

SA_CKE_0

SA_CKE_1

SA_CKE_2

SA_CKE_3

SA_ODT_0

SA_ODT_1

SA_ODT_2

SA_ODT_3

SA_CK_0

SA_CK#_0

SA_CK_1

SA_CK#_1

SA_CK_2

SA_CK#_2

SA_CK_3

SA_CK#_3

SM_DRAMRST#

SA_DQS_8

SA_DQS#_8

SA_ECC_CB_ 0

SA_ECC_CB_ 1

SA_ECC_CB_ 2

SA_ECC_CB_ 3

SA_ECC_CB_ 4

SA_ECC_CB_ 5

SA_ECC_CB_ 6

SA_ECC_CB_ 7

DDR_0

DDR_0

1/10

1/10

3

AV27

AY24

AW24

AW23

AV23

AT24

AT23

AU22

AV22

AT22

AV28

AU21

AT21

AW32

AU20

AT20

AW29

AV30

AU28

AY29

AW28

AV20

AU29

AV32

AW30

AU33

AV19

AT19

AU18

AV18

AV31

AU32

AU30

AW33

AY25

AW25

AU24

AU25

AW27

AY27

AV26

AW26

AW18

AV13

AV12

AU12

AU14

AW13

AY13

AU13

AU11

AY12

AW12

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_MAA_A14

M_MAA_A15

M_MAA_A[0..15]

M_WE_A_N 9

M_CAS_A_N 9

M_RAS_A_N 9

M_SBS_A0 9

M_SBS_A1 9

M_SBS_A2 9

M_SCS_A_N0 9

M_SCS_A_N1 9

M_SCKE_A0 9

M_SCKE_A1 9

M_ODT_A0 9

M_ODT_A1 9

CK_M_DDR0_A_DP 9

CK_M_DDR0_A_DN 9

CK_M_DDR1_A_DP 9

CK_M_DDR1_A_DN 9

DDR3_DRAMRST_N 9,10

CC1

CC1

0.1UF 16V X7R 0402 /NI

0.1UF 16V X7R 0402 /NI

M_MAA_A[0..15] 9

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU DDR CHANNEL A

CPU DDR CHANNEL A

CPU DDR CHANNEL A

IH618-MHS

IH618-MHS

IH618-MHS

5 42Wednesday, December 18, 2013

5 42Wednesday, December 18, 2013

5 42Wednesday, December 18, 2013

1

6.0

6.0

6.0

5

www.teknisi-indonesia.com

www.teknisi-indonesia.com

4

3

2

1

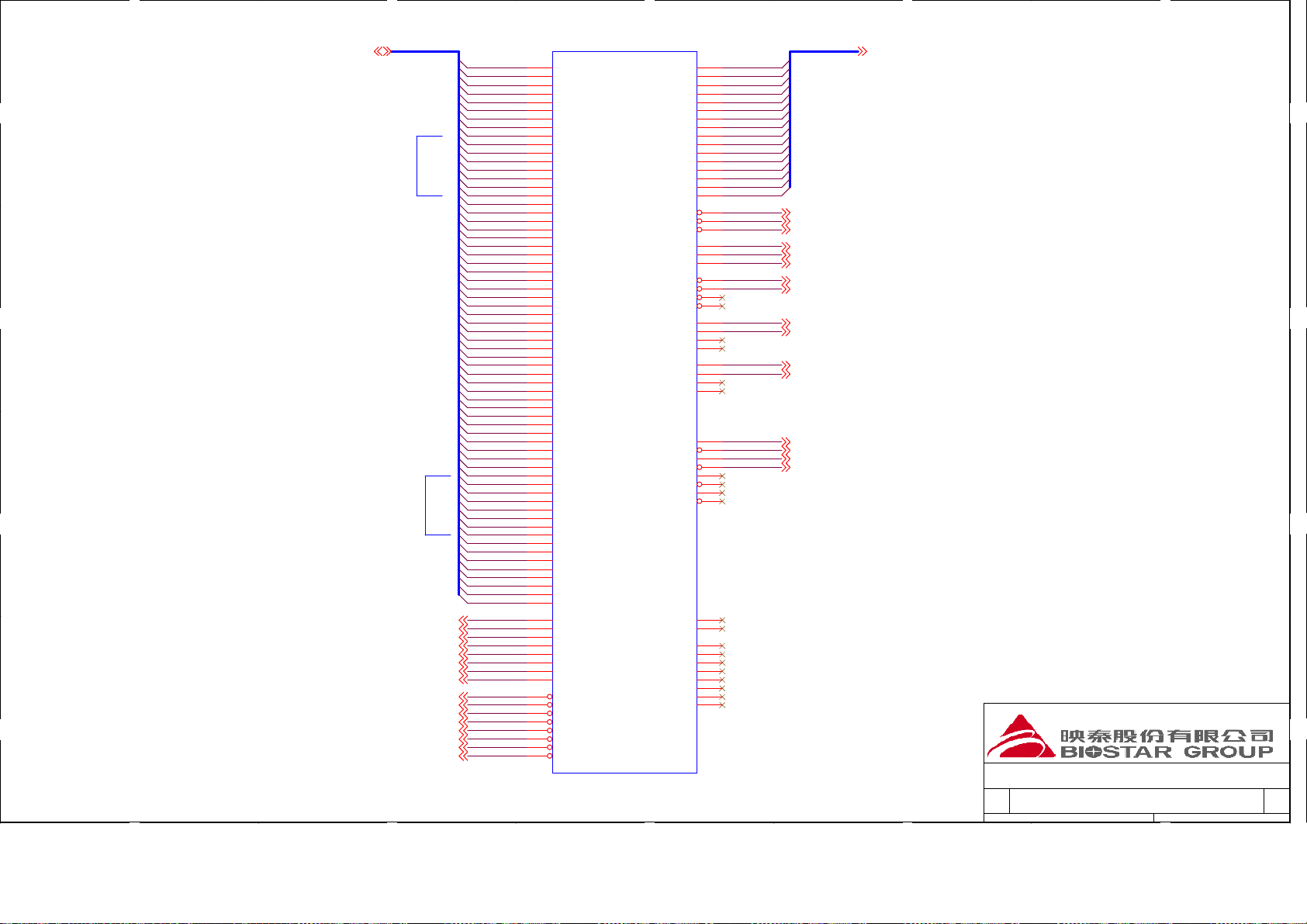

M_DATA_B[0..63]10

D D

DQ REMAPPING IMPLEMENTED

TO IMPROVE BREAKOUT AND

MINIMIZE CH-2-CH COUPLING

C C

DQ REMAPPING IMPLEMENTED

TO IMPROVE BREAKOUT AND

B B

MINIMIZE CH-2-CH COUPLING

A A

5

M_DATA_B[0..63]

M_DQS_B_DP010

M_DQS_B_DP110

M_DQS_B_DP210

M_DQS_B_DP310

M_DQS_B_DP410

M_DQS_B_DP510

M_DQS_B_DP610

M_DQS_B_DP710

M_DQS_B_DN010

M_DQS_B_DN110

M_DQS_B_DN210

M_DQS_B_DN310

M_DQS_B_DN410

M_DQS_B_DN510

M_DQS_B_DN610

M_DQS_B_DN710

4

M_DATA_B0

M_DATA_B1

M_DATA_B2

M_DATA_B3

M_DATA_B4

M_DATA_B5

M_DATA_B6

M_DATA_B7

M_DATA_B13

M_DATA_B9

M_DATA_B11

M_DATA_B15

M_DATA_B12

M_DATA_B8

M_DATA_B14

M_DATA_B10

M_DATA_B16

M_DATA_B17

M_DATA_B18

M_DATA_B19

M_DATA_B20

M_DATA_B21

M_DATA_B22

M_DATA_B23

M_DATA_B24

M_DATA_B25

M_DATA_B26

M_DATA_B27

M_DATA_B28

M_DATA_B29

M_DATA_B30

M_DATA_B31

M_DATA_B32

M_DATA_B33

M_DATA_B34

M_DATA_B35

M_DATA_B36

M_DATA_B37

M_DATA_B38

M_DATA_B39

M_DATA_B40

M_DATA_B41

M_DATA_B42

M_DATA_B43

M_DATA_B44

M_DATA_B45

M_DATA_B46

M_DATA_B47

M_DATA_B48

M_DATA_B52

M_DATA_B55

M_DATA_B51

M_DATA_B54

M_DATA_B49

M_DATA_B53

M_DATA_B50

M_DATA_B56

M_DATA_B57

M_DATA_B58

M_DATA_B59

M_DATA_B60

M_DATA_B61

M_DATA_B62

M_DATA_B63

CPU1B

CPU1B

AG7

AG8

AJ9

AJ8

AG5

AG6

AJ6

AJ7

AL7

AM7

AM10

AL10

AL6

AM6

AL9

AM9

AP7

AR7

AP10

AR10

AP6

AR6

AP9

AR9

AM12

AM13

AR13

AP13

AL12

AL13

AR12

AP12

AR28

AR29

AL28

AL29

AP28

AP29

AM28

AM29

AP32

AP31

AP35

AP34

AR32

AR31

AR35

AR34

AM32

AM31

AL35

AL32

AM34

AL31

AM35

AL34

AH35

AH34

AE34

AE35

AJ35

AJ34

AF33

AF35

AH7

AM8

AR8

AN13

AN29

AP33

AL33

AG35

AH6

AL8

AP8

AN12

AN28

AR33

AM33

AG34

LGA 1155 SOCKET

LGA 1155 SOCKET

BIOSTAR_D V1_4

BIOSTAR_D V1_4

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_1 0

SB_DQ_1 1

SB_DQ_1 2

SB_DQ_1 3

SB_DQ_1 4

SB_DQ_1 5

SB_DQ_1 6

SB_DQ_1 7

SB_DQ_1 8

SB_DQ_1 9

SB_DQ_2 0

SB_DQ_2 1

SB_DQ_2 2

SB_DQ_2 3

SB_DQ_2 4

SB_DQ_2 5

SB_DQ_2 6

SB_DQ_2 7

SB_DQ_2 8

SB_DQ_2 9

SB_DQ_3 0

SB_DQ_3 1

SB_DQ_3 2

SB_DQ_3 3

SB_DQ_3 4

SB_DQ_3 5

SB_DQ_3 6

SB_DQ_3 7

SB_DQ_3 8

SB_DQ_3 9

SB_DQ_4 0

SB_DQ_4 1

SB_DQ_4 2

SB_DQ_4 3

SB_DQ_4 4

SB_DQ_4 5

SB_DQ_4 6

SB_DQ_4 7

SB_DQ_4 8

SB_DQ_4 9

SB_DQ_5 0

SB_DQ_5 1

SB_DQ_5 2

SB_DQ_5 3

SB_DQ_5 4

SB_DQ_5 5

SB_DQ_5 6

SB_DQ_5 7

SB_DQ_5 8

SB_DQ_5 9

SB_DQ_6 0

SB_DQ_6 1

SB_DQ_6 2

SB_DQ_6 3

SB_DQS_ 0

SB_DQS_ 1

SB_DQS_ 2

SB_DQS_ 3

SB_DQS_ 4

SB_DQS_ 5

SB_DQS_ 6

SB_DQS_ 7

SB_DQS# _0

SB_DQS# _1

SB_DQS# _2

SB_DQS# _3

SB_DQS# _4

SB_DQS# _5

SB_DQS# _6

SB_DQS# _7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SA_CK(2)

SA_CK(1)

SA_ODT(2)

SB_BS_ 0

SB_BS_ 1

SB_BS_ 2

SB_CS# _0

SB_CS# _1

SB_CS# _2

SB_CS# _3

SB_CKE_ 0

SB_CKE_ 1

SB_CKE_ 2

SB_CKE_ 3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_CK_ 0

SB_CK# _0

SB_CK_ 1

SB_CK# _1

SB_CK_ 2

SB_CK# _2

SB_CK_ 3

SB_CK# _3

SB_DQS_ 8

SB_DQS# _8

SB_ECC_ CB_0

SB_ECC_ CB_1

SB_ECC_ CB_2

SB_ECC_ CB_3

SB_ECC_ CB_4

SB_ECC_ CB_5

SB_ECC_ CB_6

SB_ECC_ CB_7

DDR_1

DDR_1

2/10

2/10

3

AK24

AM20

AM19

AK18

AP19

AP18

AM18

AL18

AN18

AY17

AN23

AU17

AT18

AR26

AY16

AV16

AR25

AK25

AP24

AP23

AM24

AW17

AN25

AN26

AL25

AT26

AU16

AY15

AW15

AV15

AL26

AP26

AM26

AK26

AL21

AL22

AL20

AK20

AL23

AM22

AP21

AN21

AN16

AN15

AL16

AM16

AP16

AR16

AL15

AM15

AR15

AP15

M_MAA_B0

M_MAA_B1

M_MAA_B2

M_MAA_B3

M_MAA_B4

M_MAA_B5

M_MAA_B6

M_MAA_B7

M_MAA_B8

M_MAA_B9

M_MAA_B10

M_MAA_B11

M_MAA_B12

M_MAA_B13

M_MAA_B14

M_MAA_B15

M_MAA_B[0..15]

M_WE_B_N 10

M_CAS_B_N 10

M_RAS_B_N 10

M_SBS_B0 10

M_SBS_B1 10

M_SBS_B2 10

M_SCS_B_N0 10

M_SCS_B_N1 10

M_SCKE_B0 10

M_SCKE_B1 10

M_ODT_B0 10

M_ODT_B1 10

CK_M_DDR0_B_DP 10

CK_M_DDR0_B_DN 10

CK_M_DDR1_B_DP 10

CK_M_DDR1_B_DN 10

M_MAA_B[0..15] 10

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU DDR CHANNEL A

CPU DDR CHANNEL A

CPU DDR CHANNEL A

IH618-MHS

IH618-MHS

IH618-MHS

6 42Wednesday, December 18, 2013

6 42Wednesday, December 18, 2013

6 42Wednesday, December 18, 2013

1

6.0

6.0

6.0

5

www.teknisi-indonesia.com

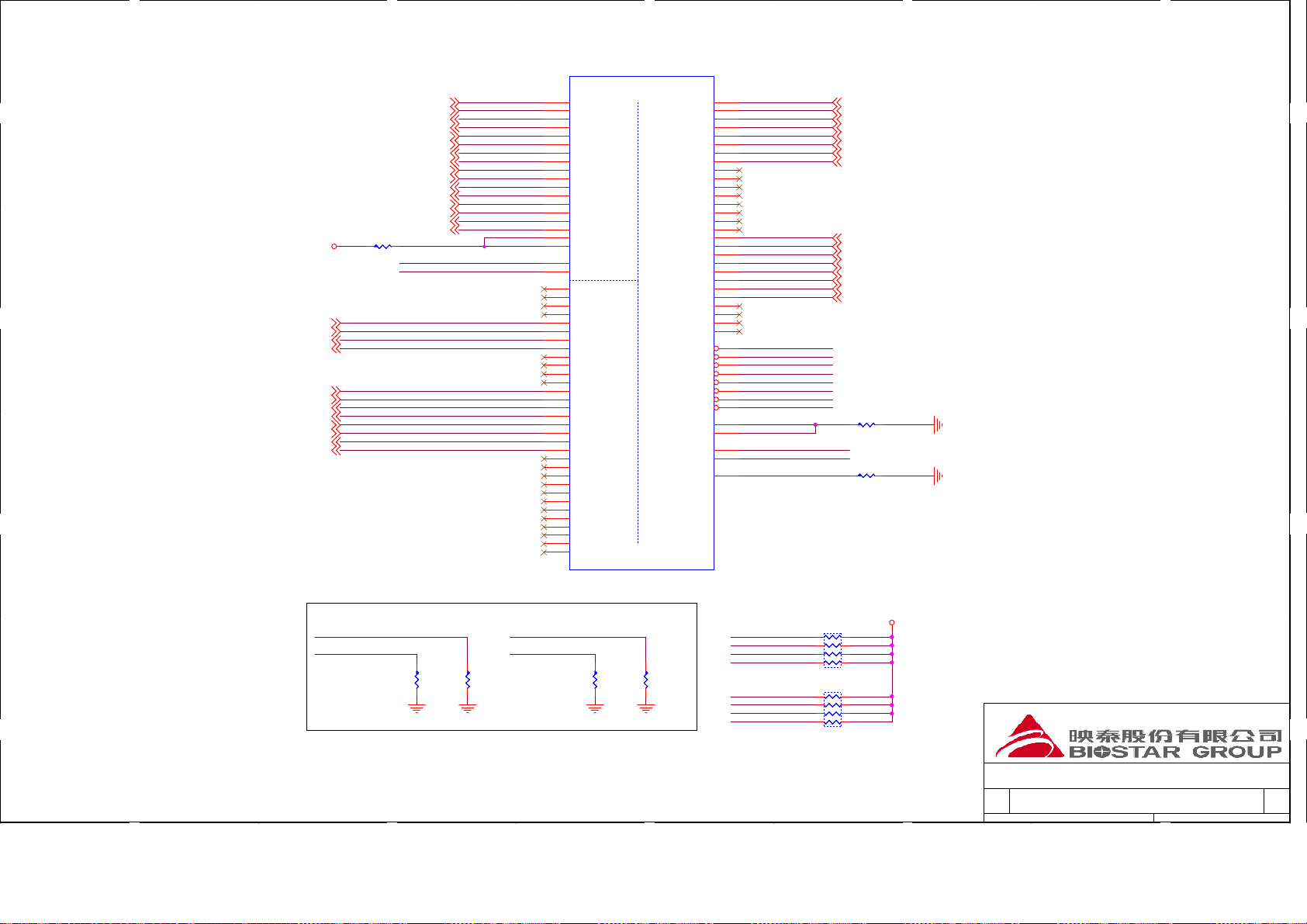

FROM CLK GEN.

FROM PCH

D D

VRD12 INTERFACE

H_VIDSCK39

H_VIDSOUT39

H_VIDALERT_N39

TBD

NEAR PCH

CR15 4.7K 0402CR15 4.7K 0402

NV_CLE15

update for Ivy bridge

C C

DMI/FDI Termination Select

PUT INSIDE THE

CPU SOCKET

V_SM

NEAR CPU

B B

H_PWRGD

CR32 1K 0402CR32 1K 0402

CC55 0.1UF 16V Y5V 0402 /NICC55 0.1UF 16V Y5V 0402 /NI

PCH NO PECI SUPPORTED

CFG5CFG6

1 1

1 0

0 1

0 0

V_1P8_SFR

CR18

CR18

1K 1% 0402

1K 1% 0402

CR24

CR24

1K 1% 0402

1K 1% 0402

PCI E CONFIG

1 X 16

2 X 8

RESERVED

X8,X4,X4

V_CPU_VCCIO

CR14

CR14

2.2K 0402

2.2K 0402

H_SNB_N

CC2

CC2

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

SNB_DDR_VREF

CC3

CC3

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

CR8

CR8

110 1% 0402

110 1% 0402

CR9

CR9

75 1% 0402

75 1% 0402

H_PWRGD14,35

H_DRAMPWRGD14

H_PM_SYNC_013

H_PECI29

H_PROCHOT_N29,39

H_THERMTRIP_N13

H_SKTOCC_N35,39

4

CK_PE_100M_MCP_DP17

CK_PE_100M_MCP_DN17

VIDSCLK

VIDSOUT

VIDALERT#

H_PWRGD

H_DRAMPWRGD

PLTRST_CPU_N

H_PECI

H_SNB_N

SNB_DDR_VREF

CPU1E

CPU1E

W2

BCLK_0

W1

BCLK#_0

C37

VIDSCLK

B37

VIDSOUT

A37

VIDALERT#

J40

UNCOREPWRGOOD

AJ19

SM_DRAMPWROK

F36

RESET#

E38

PM_SYNC

J35

PECI

E37

CATERR#

H34

PROCHOT#

G35

THERMTRIP#

AJ33

SKTOCC#

K32

PROC_SEL

AJ22

SM_VREF

H36

CFG_0

J36

CFG_1

J37

CFG_2

K36

CFG_3

L36

CFG_4

N35

CFG_5

L37

CFG_6

M36

CFG_7

J38

CFG_8

L35

CFG_9

M38

CFG_10

N36

CFG_11

N38

CFG_12

N39

CFG_13

N37

CFG_14

N40

CFG_15

G37

CFG_16

G36

CFG_17

AT14

RSVD_016

AY3

RSVD_023

H7

RSVD_028

H8

RSVD_029

LGA 1155 SOCKET

LGA 1155 SOCKET

MTP1MTP1

MTP2MTP2

MTP3MTP3

MTP4MTP4

MTP5MTP5

1

1

1

1

1

3

CK_PE_100M_MCP_DP

CK_PE_100M_MCP_DN

H_PWRGD

H_DRAMPWRGD

PLTRST_CPU_N

NEAR CPU

BIOSTAR_D V1_4

BIOSTAR_D V1_4

MISC

MISC

VCCP_SELECT

VCCSA_VID

VCCSA_SENSE

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSSIO_SENSE

VCCAXG_SENSE

VSSAXG_SENSE

TDO

TCK

TMS

TRST#

PRDY#

PREQ#

DBR#

RSVD_001

RSVD_002

BPM#_0

BPM#_1

BPM#_2

BPM#_3

BPM#_4

BPM#_5

BPM#_6

BPM#_7

RSVD_024

RSVD_030

RSVD_037

RSVD_036

RSVD_033

RSVD_040

RSVD_039

RSVD_018

RSVD_020

RSVD_038

RSVD_032

RSVD_034

RSVD_035

RSVD_050

RSVD_053

RSVD_051

RSVD_052

5/10

5/10

MTP80MTP80

MTP81MTP81

VCCIO_SENSE

1

VSSIO_SENSE

1

2

1

NEAR CPU

CPU1J

CPU1J

BIOSTAR_D V1_4

BIOSTAR_D V1_4

AB7

RSVD_04

AD37

RSVD_05

AG4

RSVD_08

P33

P34

T2

VCCIO_SENSE

A36

VSSIO_SENSE

B36

AB4

AB3

L32

M32

H_TDO

L39

H_TDI

L40

TDI

M40

L38

J39

K38

K40

E39

C40

D40

H40

H38

G38

G40

G39

F38

E40

F40

B39

J33

L34

L33

K34

N33

M34

AV1

AW2

L9

J9

K9

L31

J31

K31

AD34

AD35

H_TCK

H_TMS

H_TRST_N

VCC_SENSE 39

VSS_SENSE 39

VCCAXG_SENSE 39

VSSAXG_SENSE 39

AJ29

AJ30

AJ31

AV34

AW34

P35

P37

P39

R34

R36

R38

R40

A38

AU40

AW38

C2

D1

H_TDI

H_TDO

H_TMS

H_PROCHOT_N

H_TRST_N

H_TCK

H_DRAMPWRGD

RSVD_10

RSVD_11

RSVD_12

RSVD_19

RSVD_21

RSVD_43

RSVD_44

RSVD_45

RSVD_46

RSVD_47

RSVD_48

RSVD_49

NCTF_01

NCTF_02

NCTF_03

NCTF_04

NCTF_05

SPARES

SPARES

LGA 1155 SOCKET

LGA 1155 SOCKET

CRN1

CRN1

51 8P4R 0402

51 8P4R 0402

CR31 51 0402CR31 51 0402

CR25 51 0402CR25 51 0402

CR34 1K 0402CR34 1K 0402

12

34

56

78

for Ivy bridge processor support

AH1

FC_AH1

AH4

FC_AH2

AT11

RSVD_15

AP20

RSVD_14

AN20

RSVD_13

AU10

RSVD_17

AY10

RSVD_22

AF4

RSVD_07

AB6

RSVD_03

AE6

RSVD_06

AJ11

RSVD_09

D38

RSVD_27

C39

RSVD_26

C38

RSVD_25

J34

RSVD_31

N34

RSVD_41

10/10

10/10

V_CPU_VCCIO

V_SM

DIMM_DQ_VREF_B 10

DIMM_DQ_VREF_A 9

CPU RESET LOGIC

PLTRST_N PLTRST_CPU_N

PLTRST_N14,29

CR30 200 1% 0402CR30 200 1% 0402

CR28

CR28

110 1% 0402

110 1% 0402

CC4

CC4

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

*

*

DESCR IPT ION

PEGLANE REVERSAL[0],X16NORM

SEL0

SEL1

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

4

3

2

CPU MISC

CPU MISC

CPU MISC

IH618-MHS

IH618-MHS

IH618-MHS

1

6.0

6.0

7 42Wednesday, December 18, 2013

7 42Wednesday, December 18, 2013

7 42Wednesday, December 18, 2013

6.0

A A

CFG H L

2

5

6

RESERVED

*

*

5

CPU1I

www.teknisi-indonesia.com

www.teknisi-indonesia.com

5

CPU1I

LGA 1155 SOCKET

LGA 1155 SOCKET

AM27

AM3

AM30

AM36

AM37

AM38

AM39

AM4

AM40

AM5

AN10

AN11

AN14

AN17

AN19

AN22

AN24

AN27

AN30

AN31

AN32

AN33

AN34

AN35

AN36

AN5

AN6

AN7

AN8

AN9

AP1

AP11

AP14

AP17

AP22

AP25

AP27

AP30

AP36

AP37

AP4

AP40

AP5

AR11

AR14

AR17

VSS_091

VSS_092

VSS_093

VSS_094

VSS_095

VSS_096

VSS_097

VSS_098

VSS_099

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

D D

BIOSTAR_D V1_4

BIOSTAR_D V1_4

VSS_001

VSS_002

VSS_003

VSS_004

VSS_005

VSS_006

VSS_007

VSS_008

VSS_009

VSS_010

VSS_011

VSS_012

VSS_013

VSS_014

VSS_015

VSS_016

VSS_017

VSS_018

VSS_019

VSS_020

VSS_021

VSS_022

VSS_023

VSS_024

VSS_025

VSS_026

VSS_027

VSS_028

VSS_029

VSS_030

VSS_031

VSS_032

VSS_033

VSS_034

VSS_035

VSS_036

VSS_037

VSS_038

VSS_039

VSS_040

VSS_041

VSS_042

VSS_043

VSS_044

VSS_045

VSS_046

A17

A23

A26

A29

A35

AA6

AB5

AC1

AA33

AA34

AC6

AA35

AA36

AA37

AA38

AD33

AD36

AD38

AF1

AF5

AF6

AD5

AD8

AE3

AD39

AD40

AE33

AE36

AF7

AH2

AH3

AH5

AH8

AJ12

AF34

AF36

AF37

AF40

AH33

AH36

AG36

AJ15

AH37

AH38

AH39

AH40

4

AR18

AR19

AR27

AR30

AR36

AR5

AT1

AT10

AT12

AT13

AT15

AT16

AT17

AT2

AT25

AT27

AT28

AT29

AT3

AT30

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AT39

AT4

AT40

AT5

AT6

AT7

AT8

AT9

AU1

AU15

AU26

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_047

VSS_048

VSS_049

VSS_050

VSS_051

VSS_052

VSS_053

VSS_054

VSS_055

VSS_056

VSS_057

VSS_058

VSS_059

VSS_060

VSS_061

VSS_062

VSS_063

VSS_064

VSS_065

VSS_066

VSS_067

VSS_068

VSS_069

VSS_070

VSS_071

VSS_072

VSS_073

VSS_074

VSS_075

VSS_076

VSS_077

VSS_078

VSS_079

VSS_080

VSS_081

VSS_082

VSS_083

VSS_084

VSS_085

AJ5

AK1

AJ18

AJ21

AJ25

AJ27

AJ36

AK10

AK13

AK14

AK16

AK22

AK28

AK4

AK5

AK6

AK7

AK8

AK9

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AL11

AK40

AL5

AL14

AM1

AL17

AL19

AL24

AL27

AL30

AL36

AM11

AM14

3

AU34

AU4

AU6

AU8

AV10

H17

H20

H23

H26

H29

H33

H35

H37

H39

J11

J17

J20

J23

J26

J29

J32

K12

K13

K14

K17

K20

K23

K26

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_271G8VSS_272H1VSS_273

VSS_274H2VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283H5VSS_284H6VSS_285H9VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293K1VSS_294

VSS_295

VSS_296

VSS_297

VSS_298K2VSS_299

VSS_300

VSS_301

VSS_086

VSS_087

VSS_088

VSS_089

VSS_090

VSS_NCTF_01A4VSS_NCTF_02

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211B6VSS_212

B10

B13

B14

B17

B23

B26

B29

B32

B35

AV3

AM2

AV39

AM17

AM21

AM23

AM25

AV6

AV11

AV14

AV17

AV35

AV38

AW10

AW11

AW14

AY4

AY6

AY8

AW6

AY11

AY14

AY18

AY35

AW16

AW36

B38

2

K29

K33

K35

K37

K39

L10

L17

L20

L23

L26

L29

M17

M20

M23

M26

M29

M33

M35

M37

M39

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307K5VSS_308K6VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315L8VSS_316M1VSS_317

VSS_318M2VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221C7VSS_222C8VSS_223

VSS_224D2VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232D4VSS_233D5VSS_234D9VSS_235

C11

C12

C17

C20

C23

C26

C29

C32

C35

D17

D20

D23

D26

D29

D32

D37

D39

E11

E12

VSS_326

VSS_327M5VSS_328M6VSS_329M9VSS_330N8VSS_331P1VSS_332P2VSS_333

VSS_236

VSS_237

VSS_238

VSS_239

E17

E20

E23

E26

P36

P38

P40

R33

R35

R37

R39

VSS_334

VSS_335

VSS_336P5VSS_337P6VSS_338

VSS_339

VSS_340

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244E7VSS_245E8VSS_246F1VSS_247

VSS_248

VSS_249

VSS_250

F10

F13

F14

E29

E32

F17

E36

VSS_341

VSS_342R8VSS_343T1VSS_344T5VSS_345T6VSS_346U8VSS_347V1VSS_348V2VSS_349

VSS_251F2VSS_252

VSS_253

VSS_254

VSS_255

F20

F23

F26

F29

F35

1

V33

V34

V35

V36

V37

V38

V39

V40

Y8

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_355

VSS_356

VSS_357V5VSS_358W6VSS_359Y5VSS_360

9/10

9/10

VSS_256

VSS_257

VSS_258

VSS_259F5VSS_260F6VSS_261F9VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270G7VSS_NCTF_03

VSS_NCTF_04

F37

F39

G11

G12

G17

B3

G20

G23

G26

G29

G34

AY37

V_CPU_CORE V_CPU_CORE V_AXGV_CPU_VCCIO

C C

B B

A A

CPU1F

CPU1F

A12

VCC_001

A13

VCC_002

A14

VCC_003

A15

VCC_004

A16

VCC_005

A18

VCC_006

A24

VCC_007

A25

VCC_008

A27

VCC_009

A28

VCC_010

B15

VCC_011

B16

VCC_012

B18

VCC_013

B24

VCC_014

B25

VCC_015

B27

VCC_016

B28

VCC_017

B30

VCC_018

B31

VCC_019

B33

VCC_020

B34

VCC_021

C15

VCC_022

C16

VCC_023

C18

VCC_024

C19

VCC_025

C21

VCC_026

C22

VCC_027

C24

VCC_028

C25

VCC_029

C27

VCC_030

C28

VCC_031

C30

VCC_032

C31

VCC_033

C33

VCC_034

C34

VCC_035

C36

VCC_036

D13

VCC_037

D14

VCC_038

D15

VCC_039

D16

VCC_040

D18

VCC_041

D19

VCC_042

D21

VCC_043

D22

VCC_044

D24

VCC_045

D25

VCC_046

D27

VCC_047

D28

VCC_048

D30

VCC_049

D31

VCC_050

D33

VCC_051

D34

VCC_052

D35

VCC_053

D36

VCC_054

E15

VCC_055

E16

VCC_056

E18

VCC_057

E19

VCC_058

E21

VCC_059

E22

VCC_060

E24

VCC_061

E25

VCC_062

E27

VCC_063

E28

VCC_064

E30

VCC_065

E31

VCC_066

E33

VCC_067

E34

VCC_068

E35

VCC_069

F15

VCC_070

F16

VCC_071

F18

VCC_072

F19

VCC_073

F21

VCC_074

F22

VCC_075

F24

VCC_076

F25

VCC_077

F27

VCC_078

F28

VCC_079

F30

VCC_080

F31

VCC_081

LGA 1155 SOCKET

LGA 1155 SOCKET

BIOSTAR_D V1_4

BIOSTAR_D V1_4

VCC_082

VCC_083

VCC_084

VCC_085

VCC_086

VCC_087

VCC_088

VCC_089

VCC_090

VCC_091

VCC_092

VCC_093

VCC_094

VCC_095

VCC_096

VCC_097

VCC_098

VCC_099

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

VCC_123

CPU POWER

CPU POWER

VCC_124

VCC_125

VCC_126

VCC_127

VCC_128

VCC_129

VCC_130

VCC_131

VCC_132

VCC_133

VCC_134

VCC_135

VCC_136

VCC_137

VCC_138

VCC_139

VCC_140

VCC_141

VCC_142

VCC_143

VCC_144

VCC_145

VCC_146

VCC_147

VCC_148

VCC_149

VCC_150

VCC_151

VCC_152

VCC_153

VCC_154

VCC_155

VCC_156

VCC_157

VCC_158

VCC_159

VCC_160

VCC_161

6/10

6/10

CPU1H

AG33

AJ16

AJ17

AJ26

AJ28

AJ32

AK15

AK17

AK19

AK21

AK23

AK27

AK29

AK30

AK11

AK12

M13

A11

A7

AA3

AB8

AF8

B9

D10

D6

E3

E4

G3

G4

J3

J4

J7

J8

L3

L4

L7

N3

N4

N7

R3

R4

R7

U3

U4

U7

V8

W3

H10

H11

H12

J10

K10

K11

L11

L12

M10

M11

M12

CPU1H

BIOSTAR_D V1_4

BIOSTAR_D V1_4

VCCIO_34

VCCIO_01

VCCIO_02

VCCIO_03

VCCIO_04

VCCIO_05

VCCIO_06

VCCIO_07

VCCIO_08

VCCIO_09

VCCIO_10

VCCIO_11

VCCIO_12

VCCIO_13

VCCIO_14

VCCIO_15

VCCIO_16

VCCIO_17

VCCIO_18

VCCIO_19

VCCIO_20

VCCIO_21

VCCIO_22

VCCIO_23

VCCIO_24

VCCIO_25

VCCIO_26

VCCIO_27

VCCIO_28

VCCIO_29

VCCIO_30

VCCIO_31

VCCIO_32

VCCIO_33

VCCIO_35

VCCIO_36

VCCIO_37

VCCIO_38

VCCIO_39

VCCIO_40

VCCIO_41

VCCIO_42

VCCIO_43

VCCIO_44

VCCIO_45

VCCSA_01

VCCSA_02

VCCSA_03

VCCSA_04

VCCSA_05

VCCSA_06

VCCSA_07

VCCSA_08

VCCSA_09

VCCSA_10

VCCSA_11

VCCPLL_01

VCCPLL_02

LGA 1155 SOCKET

LGA 1155 SOCKET

VDDQ_01

VDDQ_02

VDDQ_04

VDDQ_05

VDDQ_06

VDDQ_07

VDDQ_08

VDDQ_09

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

VDDQ_20

VDDQ_21

VDDQ_22

VDDQ_23

VDDQ_03

POWER

POWER

8/10

8/10

AJ13

AJ14

AJ23

AJ24

AR20

AR21

AR22

AR23

AR24

AU19

AU23

AU27

AU31

AV21

AV24

AV25

AV29

AV33

AW31

AY23

AY26

AY28

AJ20

V_SM

CC7

CC7

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_AXG

CC42

CC42

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC67

CC67

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

F32

F33

F34

G15

G16

G18

G19

G21

G22

G24

G25

G27

G28

G30

G31

G32

G33

H13

H14

H15

H16

H18

H19

H21

H22

H24

H25

H27

H28

H30

H31

H32

J12

J15

J16

J18

J19

J21

J22

J24

J25

J27

J28

J30

K15

K16

K18

K19

K21

K22

K24

K25

K27

K28

K30

L13

L14

L15

L16

L18

L19

L21

L22

L24

L25

L27

L28

L30

M14

M15

M16

M18

M19

M21

M22

M24

M25

M27

M28

M30

V_CPU_CORE

V_CPU_CORE

V_CPU_CORE

V_CPU_CORE

V_CPU_CORE

CC18

CC18

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC13

CC13

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC21

CC21

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC20

CC20

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC24

CC24

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC32

CC32

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC28

CC28

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC38

CC38

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC37

CC37

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC8

CC8

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC14

CC14

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC54

CC54

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC22

CC22

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC23

CC23

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC26

CC26

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC27

CC27

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC35

CC35

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC36

CC36

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_CPU_COREV_CPU_CORE

V_CPU_COREV_CPU_CORE

V_CPU_COREV_CPU_CORE

V_CPU_COREV_CPU_COREV_CPU_CORE

V_CPU_COREV_CPU_CORE

V_CPU_COREV_CPU_COREV_CPU_CORE

V_CPU_COREV_CPU_CORE

V_CPU_COREV_CPU_COREV_CPU_CORE

CC9

CC9

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC15

CC15

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC61

CC61

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC56

CC56

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC57

CC57

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC58

CC58

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC62

CC62

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC59

CC59

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC60

CC60

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_CPU_VCCIO V_CPU_VCCIO

CC10

CC10

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_CPU_VCCIOV_CPU_COREV_CPU_COREV_CPU_CORE

CC29

CC29

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_CPU_VCCIO V_CPU_VCCIO V_CPU_VCCIO

CC43

CC43

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_CPU_VCCIO

CC65

CC65

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_1P8_SFR

CC25

CC25

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_SM

CC5

CC5

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC12

CC12

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_SM

CC17

CC17

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC11

CC11

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_CPU_VCCIO

CC30

CC30

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC44

CC44

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_CPU_VCCIO

CC34

CC34

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_1P8_SFR

CC47

CC47

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_SM

CC6

CC6

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_SMV_SM V_AXG

CC45

CC45

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_SM

CC19

CC19

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_CPU_VCCIO

V_CPU_VCCIO

V_CPU_VCCIO

V_SM

CC16

CC16

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC48

CC48

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC46

CC46

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC66

CC66

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_CPU_VCCIO

CC64

CC64

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_1P8_SFR

CPU1G

CPU1G

BIOSTAR_D V1_4

BIOSTAR_D V1_4

7/10

7/10

LGA 1155 SOCKET

LGA 1155 SOCKET

V_AXG

CC39

CC39

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_AXG V_AXGV_AXG

CC49

CC49

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

V_AXG V_AXGV_AXGV_AXG

CC52

CC52

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

VCCAXG_01

VCCAXG_02

VCCAXG_03

VCCAXG_04

VCCAXG_05

VCCAXG_06

VCCAXG_07

VCCAXG_08

VCCAXG_09

VCCAXG_10

VCCAXG_11

VCCAXG_12

VCCAXG_13

VCCAXG_14

VCCAXG_15

VCCAXG_16

VCCAXG_17

VCCAXG_18

VCCAXG_19

VCCAXG_20

VCCAXG_21

VCCAXG_22

VCCAXG_23

VCCAXG_24

VCCAXG_25

VCCAXG_26

VCCAXG_27

VCCAXG_28

VCCAXG_29

VCCAXG_30

VCCAXG_31

VCCAXG_32

VCCAXG_33

VCCAXG_34

VCCAXG_35

VCCAXG_36

VCCAXG_37

VCCAXG_38

VCCAXG_39

VCCAXG_40

VCCAXG_41

VCCAXG_42

VCCAXG_43

VCCAXG_44

AB33

AB34

AB35

AB36

AB37

AB38

AB39

AB40

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

T33

T34

T35

T36

T37

T38

T39

T40

U33

U34

U35

U36

U37

U38

U39

U40

W33

W34

W35

W36

W37

W38

Y33

Y34

Y35

Y36

Y37

Y38

CC40

CC40

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC51

CC51

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC63

CC63

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CPU POWER

CPU POWER

CPU POWER

IH618-MHS

IH618-MHS

IH618-MHS

V_AXGV_AXG

CC41

CC41

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC50

CC50

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

CC53

CC53

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

6.0

6.0

8 42Wednesday, December 18, 2013

8 42Wednesday, December 18, 2013

8 42Wednesday, December 18, 2013

6.0

5

www.teknisi-indonesia.com

DDR3_A1A

M_DQS_A_DN05

M_DQS_A_DP05

M_DQS_A_DN15

M_DQS_A_DP15

M_DQS_A_DN25

M_DQS_A_DP25

M_DQS_A_DN35

M_DQS_A_DP35

D D

M_DQS_A_DN45

M_DQS_A_DP45

M_DQS_A_DN55

M_DQS_A_DP55

M_DQS_A_DN65

M_DQS_A_DP65

M_DQS_A_DN75

M_DQS_A_DP75

M_DQS_A_DN0

M_DQS_A_DP0

M_DQS_A_DN1

M_DQS_A_DP1

M_DQS_A_DN2

M_DQS_A_DP2

M_DQS_A_DN3

M_DQS_A_DP3

M_DQS_A_DN4

M_DQS_A_DP4

M_DQS_A_DN5

M_DQS_A_DP5

M_DQS_A_DN6

M_DQS_A_DP6

M_DQS_A_DN7

M_DQS_A_DP7

C C

SMB_DATA_RESUME10,14,21,22,24

SMB_CLK_RESUME10,14,21,22,24

M_MAA_A[0..15]5

B B

M_SBS_A25

SMB_DATA_RESUME

SMB_CLK_RESUME

M_MAA_A[0..15]

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_MAA_A14

M_MAA_A15

M_SBS_A2

DDR3_A1A

6

DQS0-

7

DQS0

15

DQS1-

16

DQS1

24

DQS2-

25

DQS2

33

DQS3-

34

DQS3

84

DQS4-

85

DQS4

93

DQS5-

94

DQS5

102

DQS6-

103

DQS6

111

DQS7-

112

DQS7

42

DQS8-

43

DQS8

125

DQS9

126

DQS9-

134

DQS10

135

DQS10-

143

DQS11

144

DQS11-

152

DQS12

153

DQS12-

203

DQS13

204

DQS13-

212

DQS14

213

DQS14-

221

DQS15

222

DQS15-

230

DQS16

231

DQS16-

161

DQS17

162

DQS17-

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

79

RSVD

238

SDA

118

SCL

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10

55

A11

174

A12

196

A13

172

A14

171

A15

52

A16/BA2

DDR3-240 PIN-R

DDR3-240 PIN-R

BLACK

BLACK

4

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

234

233

228

227

115

114

109

108

225

224

219

218

106

105

100

99

216

215

210

209

97

96

91

90

207

206

201

200

88

87

82

81

156

155

150

149

37

36

31

30

147

146

141

140

28

27

22

21

138

137

132

131

19

18

13

12

129

128

123

122

10

9

4

3

68

53

167

M_DATA_A63

M_DATA_A62

M_DATA_A61

M_DATA_A60

M_DATA_A59

M_DATA_A58

M_DATA_A57

M_DATA_A56

M_DATA_A55

M_DATA_A54

M_DATA_A53

M_DATA_A52

M_DATA_A51

M_DATA_A50

M_DATA_A49

M_DATA_A48

M_DATA_A47

M_DATA_A46

M_DATA_A45

M_DATA_A44

M_DATA_A43

M_DATA_A42

M_DATA_A41

M_DATA_A40

M_DATA_A39

M_DATA_A38

M_DATA_A37

M_DATA_A36

M_DATA_A35

M_DATA_A34

M_DATA_A33

M_DATA_A32

M_DATA_A31

M_DATA_A30

M_DATA_A29

M_DATA_A28

M_DATA_A27

M_DATA_A26

M_DATA_A25

M_DATA_A24

M_DATA_A23

M_DATA_A22

M_DATA_A21

M_DATA_A20

M_DATA_A19

M_DATA_A18

M_DATA_A17

M_DATA_A16

M_DATA_A15

M_DATA_A14

M_DATA_A13

M_DATA_A12

M_DATA_A11

M_DATA_A10

M_DATA_A9

M_DATA_A8

M_DATA_A7

M_DATA_A6

M_DATA_A5

M_DATA_A4

M_DATA_A3

M_DATA_A2

M_DATA_A1

M_DATA_A0

M_DATA_A[0..63]

DDR3_DRAMRST_N5,10

M_SCS_A_N05

M_SCS_A_N15

CK_M_DDR1_A_DN5

CK_M_DDR1_A_DP5

CK_M_DDR0_A_DN5

CK_M_DDR0_A_DP5

M_DATA_A[0..63] 5

M_SCKE_A05

M_SCKE_A15

M_SBS_A05

M_SBS_A15

M_WE_A_N5

M_RAS_A_N5

M_CAS_A_N5

M_ODT_A05

M_ODT_A15

3

DIMM_CA_VREF

DIMM_DQ_VREF_A

M_SBS_A0

M_SBS_A1

DDR3_DRAMRST_N

M_WE_A_N

M_RAS_A_N

M_CAS_A_N

VCC3_3

V_SM

DDR3_A1B

DDR3_A1B

51

VDDQ1 (P)

54

VDDQ2 (P)

57

VDDQ3 (P)

60

VDDQ4 (P)

62

VDDQ5 (P)

65

VDDQ6 (P)

66

VDDQ7 (P)

69

VDDQ8 (P)

72

VDDQ9 (P)

75

VDDQ10 (P)

78

VDDQ11 (P)

170

VDD1 (P)

173

VDD2 (P)

176

VDD3 (P)

179

VDD4 (P)

182

VDD5 (P)

183

VDD6 (P)

186

VDD7(P)

189

VDD8(P)

191

VDD9(P)

194

VDD10(P)

197

VDD11(P)

236

VDDSPD(P)

67

VREFCA

1

VREFDQ

117

SA0

237

SA1

50

CKE0

169

CKE1

71

BA0

190

BA1

168

RESET

73

WE-

192

RAS-

74

CAS-

193

S-0

76

S-1

195

ODT0

77

ODT1

64

CK-1

63

CK1

185

CK-0

184

CK0

48

FREE1

49

FREE2

187

FREE3

198

FREE4

DDR3-240 PIN-R

DDR3-240 PIN-R

VSS1(P)

VSS2(P)

VSS3(P)

VSS4(P)

VSS5(P)

VSS6(P)

VSS7(P)

VSS8(P)

VSS9(P)

VSS10(P)

VSS11(P)

VSS12(P)

VSS13(P)

VSS60(P)

VSS14(P)

VSS15(P)

VSS16(P)

VSS17(P)

VSS18(P)

VSS19(P)

VSS20(P)

VSS21(P)

VSS22(P)

VSS23(P)

VSS24(P)

VSS25(P)

VSS26(P)

VSS27(P)

VSS28(P)

VSS29(P)

VSS30(P)

VSS31(P)

VSS32(P)

VSS33(P)

VSS34(P)

VSS35(P)

VSS36(P)

VSS37(P)

VSS38(P)

VSS39(P)

VSS40(P)

VSS41(P)

VSS42(P)

VSS43(P)

VSS44(P)

VSS45(P)

VSS46(P)

VSS47(P)

VSS48(P)

VSS49(P)

VSS50(P)

VSS51(P)

VSS52(P)

VSS53(P)

VSS54(P)

VSS55(P)

VSS56(P)

VSS57(P)

VSS58(P)

VSS59(P)

VTT

VTT

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

80

83

86

92

95

98

101

104

107

110

113

116

119

121

124

127

130

133

136

139

142

145

148

151

154

157

160

163

166

199

202

205

208

211

214

217

220

223

226

229

232

235

239

89

120

240

2

V_SM

MC2 1UF 6.3V X5R 0402MC2 1UF 6.3V X5R 0402

MC7 1UF 6.3V X5R 0402MC7 1UF 6.3V X5R 0402

MC6 0.1UF 16V Y5V 0402MC6 0.1UF 16V Y5V 0402

V_SM_VTT

MC14 1UF 16V 0805 Y5V /NIMC14 1UF 16V 0805 Y5V /NI

VCC3_3

MC15 0.1UF 16V Y5V 0402MC15 0.1UF 16V Y5V 0402

DDR3_DRAMRST_N

SMB_DATA_RESUME

SMB_CLK_RESUME

V_SM_VTT

Near DDR3_A1

MC3

MC3

100P 50V NPO 0402

100P 50V NPO 0402

1

MC4

MC4

100P 50V NPO 0402

100P 50V NPO 0402

MC5

MC5

100P 50V NPO 0402

100P 50V NPO 0402

V_SMV_SM

MR1

MR1

1K 1% 0402

1K 1% 0402

A A

MR4

MR4

1K 1% 0402

1K 1% 0402

5

for Ivy bridge processor support

DIMM_DQ_VREF_A

MC11

MC11

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

DIMM_DQ_VREF_A 7 DIMM_CA_VREF 10

4

MR5

MR5

1K 1% 0402

1K 1% 0402

MR6

MR6

1K 1% 0402

1K 1% 0402

3

Near DIMM Slot

DIMM_CA_VREF

MC16

MC16

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402

MC17

MC17

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

Title

Title

Title

DDR2 DIMMA1

DDR2 DIMMA1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

DDR2 DIMMA1

IH618-MHS

IH618-MHS

IH618-MHS

1

6.0

6.0

6.0

9 42Wednesday, December 18, 2013

9 42Wednesday, December 18, 2013

9 42Wednesday, December 18, 2013

5

www.teknisi-indonesia.com

DDR3_B1A

M_DQS_B_DN06

M_DQS_B_DP06

M_DQS_B_DN16

M_DQS_B_DP16

M_DQS_B_DN26

M_DQS_B_DP26

M_DQS_B_DN36

D D

M_DQS_B_DP36

M_DQS_B_DN46

M_DQS_B_DP46

M_DQS_B_DN56

M_DQS_B_DP56

M_DQS_B_DN66

M_DQS_B_DP66

M_DQS_B_DN76

M_DQS_B_DP76

M_DQS_B_DN0

M_DQS_B_DP0

M_DQS_B_DN1

M_DQS_B_DP1

M_DQS_B_DN2

M_DQS_B_DP2

M_DQS_B_DN3

M_DQS_B_DP3

M_DQS_B_DN4

M_DQS_B_DP4

M_DQS_B_DN5

M_DQS_B_DP5

M_DQS_B_DN6

M_DQS_B_DP6

M_DQS_B_DN7

M_DQS_B_DP7

C C

SMB_DATA_RESUME9,14,21,22,24

SMB_CLK_RESUME9,14,21,22,24

M_MAA_B[0..15]6

M_MAA_B[0..15]

B B

M_SBS_B26

SMB_DATA_RESUME

SMB_CLK_RESUME

M_MAA_B0

M_MAA_B1

M_MAA_B2

M_MAA_B3

M_MAA_B4

M_MAA_B5

M_MAA_B6

M_MAA_B7

M_MAA_B8

M_MAA_B9

M_MAA_B10

M_MAA_B11

M_MAA_B12

M_MAA_B13

M_MAA_B14

M_MAA_B15

M_SBS_B2

DDR3_B1A

6

DQS0-

7

DQS0

15

DQS1-

16

DQS1

24

DQS2-

25

DQS2

33

DQS3-

34

DQS3

84

DQS4-

85

DQS4

93

DQS5-

94

DQS5

102

DQS6-

103

DQS6

111

DQS7-

112

DQS7

42

DQS8-

43

DQS8

125

DQS9

126

DQS9-

134

DQS10

135

DQS10-

143

DQS11

144

DQS11-

152

DQS12

153

DQS12-

203

DQS13

204

DQS13-

212

DQS14

213

DQS14-

221

DQS15

222

DQS15-

230

DQS16

231

DQS16-

161

DQS17

162

DQS17-

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

79

RSVD

238

SDA

118

SCL

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10

55

A11

174

A12

196

A13

172

A14

171

A15

52

A16/BA2

DDR3-240 PIN-R

DDR3-240 PIN-R

4

BLACK

BLACK

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

234

233

228

227

115

114

109

108

225

224

219

218

106

105

100

99

216

215

210

209

97

96

91

90

207

206

201

200

88

87

82

81

156

155

150

149

37

36

31

30

147

146

141

140

28

27

22

21

138

137

132

131

19

18

13

12

129

128

123

122

10

9

4

3

68

53

167

M_DATA_B63

M_DATA_B62

M_DATA_B61

M_DATA_B60

M_DATA_B59

M_DATA_B58

M_DATA_B57

M_DATA_B56

M_DATA_B55

M_DATA_B54

M_DATA_B53

M_DATA_B52

M_DATA_B51

M_DATA_B50

M_DATA_B49

M_DATA_B48

M_DATA_B47

M_DATA_B46

M_DATA_B45

M_DATA_B44

M_DATA_B43

M_DATA_B42

M_DATA_B41

M_DATA_B40

M_DATA_B39

M_DATA_B38

M_DATA_B37

M_DATA_B36

M_DATA_B35

M_DATA_B34

M_DATA_B33

M_DATA_B32

M_DATA_B31

M_DATA_B30

M_DATA_B29

M_DATA_B28

M_DATA_B27

M_DATA_B26

M_DATA_B25

M_DATA_B24

M_DATA_B23

M_DATA_B22

M_DATA_B21

M_DATA_B20

M_DATA_B19

M_DATA_B18

M_DATA_B17

M_DATA_B16

M_DATA_B15

M_DATA_B14

M_DATA_B13

M_DATA_B12

M_DATA_B11

M_DATA_B10

M_DATA_B9

M_DATA_B8

M_DATA_B7

M_DATA_B6

M_DATA_B5

M_DATA_B4

M_DATA_B3

M_DATA_B2

M_DATA_B1

M_DATA_B0

M_DATA_B[0..63]

DIMM_CA_VREF9

DDR3_DRAMRST_N5,9

CK_M_DDR1_B_DN6

CK_M_DDR1_B_DP6

CK_M_DDR0_B_DN6

CK_M_DDR0_B_DP6

3

M_DATA_B[0..63] 6

M_SCKE_B06

M_SCKE_B16

M_SBS_B06

M_SBS_B16

M_WE_B_N6

M_RAS_B_N6

M_CAS_B_N6

M_SCS_B_N06

M_SCS_B_N16

M_ODT_B06

M_ODT_B16

V_SM

VCC3_3

DIMM_CA_VREF

DIMM_DQ_VREF_B

VCC3_3

M_SBS_B0

M_SBS_B1

DDR3_DRAMRST_N

M_WE_B_N

M_RAS_B_N

M_CAS_B_N

DDR3_B1B

DDR3_B1B

51

VDDQ1 (P)

54

VDDQ2 (P)

57

VDDQ3 (P)

60

VDDQ4 (P)

62

VDDQ5 (P)

65

VDDQ6 (P)

66

VDDQ7 (P)

69

VDDQ8 (P)

72

VDDQ9 (P)

75

VDDQ10 (P)

78

VDDQ11 (P)

170

VDD1 (P)

173

VDD2 (P)

176

VDD3 (P)

179

VDD4 (P)

182

VDD5 (P)

183

VDD6 (P)

186

VDD7(P)

189

VDD8(P)

191

VDD9(P)

194

VDD10(P)

197

VDD11(P)

236

VDDSPD(P)

67

VREFCA

1

VREFDQ

117

SA0

237

SA1

50

CKE0

169

CKE1

71

BA0

190

BA1

168

RESET

73

WE-

192

RAS-

74

CAS-

193

S-0

76

S-1

195

ODT0

77

ODT1

64

CK-1

63

CK1

185

CK-0

184

CK0

48

FREE1

49

FREE2

187

FREE3

198

FREE4

DDR3-240 PIN-R

DDR3-240 PIN-R

VSS1(P)

VSS2(P)

VSS3(P)

VSS4(P)

VSS5(P)

VSS6(P)

VSS7(P)

VSS8(P)

VSS9(P)

VSS10(P)

VSS11(P)

VSS12(P)

VSS13(P)

VSS60(P)

VSS14(P)

VSS15(P)

VSS16(P)

VSS17(P)

VSS18(P)

VSS19(P)

VSS20(P)

VSS21(P)

VSS22(P)

VSS23(P)

VSS24(P)

VSS25(P)

VSS26(P)

VSS27(P)

VSS28(P)

VSS29(P)

VSS30(P)

VSS31(P)

VSS32(P)

VSS33(P)

VSS34(P)

VSS35(P)

VSS36(P)

VSS37(P)

VSS38(P)

VSS39(P)

VSS40(P)

VSS41(P)

VSS42(P)

VSS43(P)

VSS44(P)

VSS45(P)

VSS46(P)

VSS47(P)

VSS48(P)

VSS49(P)

VSS50(P)

VSS51(P)

VSS52(P)

VSS53(P)

VSS54(P)

VSS55(P)

VSS56(P)

VSS57(P)

VSS58(P)

VSS59(P)

VTT

VTT

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

80

83

86

92

95

98

101

104

107

110

113

116

119

121

124

127

130

133

136

139

142

145

148

151

154

157

160

163

166

199

202

205

208

211

214

217

220

223

226

229

232

235

239

89

120

240

2

V_SM_VTT

Near DDR3_B1

V_SM

MC8 0.1UF 16V Y5V 0402MC8 0.1UF 16V Y5V 0402

MC23 1UF 6.3V X5R 0402MC23 1UF 6.3V X5R 0402

MC26 0.1UF 16V Y5V 0402MC26 0.1UF 16V Y5V 0402

Near CPU

V_SM

MC19 10UF 10V 0805 Y5VMC19 10UF 10V 0805 Y5V

MC21 10UF 10V 0805 Y5VMC21 10UF 10V 0805 Y5V

MC9 0.1UF 16V Y5V 0402MC9 0.1UF 16V Y5V 0402

MC12 0.1UF 16V Y5V 0402MC12 0.1UF 16V Y5V 0402

V_SM_VTT

MC28 0.1UF 16V Y5V 0402MC28 0.1UF 16V Y5V 0402

MC29 0.1UF 16V Y5V 0402MC29 0.1UF 16V Y5V 0402

1

V_SM

MR7

MR7

1K 1% 0402

1K 1% 0402

A A

5

4

3

DIMM_DQ_VREF_B

MR10

MR10

1K 1% 0402

1K 1% 0402

for Ivy bridge processor support

DIMM_DQ_VREF_B 7

MC25

MC25

0.1UF 16V Y5V 0402

0.1UF 16V Y5V 0402

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

DDR2 DIMMB1

DDR2 DIMMB1

DDR2 DIMMB1

IH618-MHS

IH618-MHS

IH618-MHS

10 42Wednesday, December 18, 2013

10 42Wednesday, December 18, 2013

10 42Wednesday, December 18, 2013

1

6.0

6.0

6.0

5

www.teknisi-indonesia.com

www.teknisi-indonesia.com

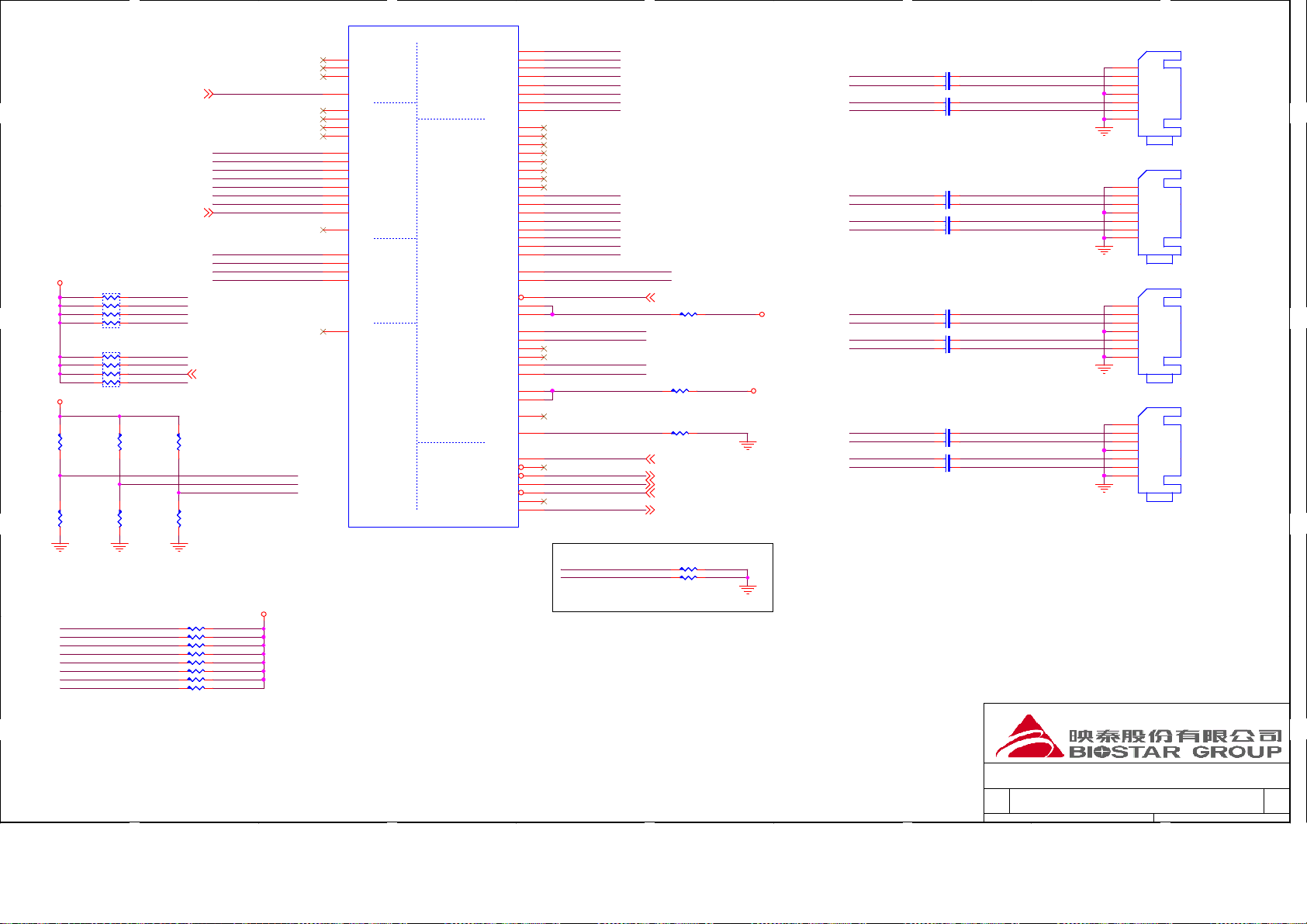

D D

VCC3_3

C C

YRN1

YRN1

8.2K 8P4R 0402

8.2K 8P4R 0402

YRN2

YRN2

8.2K 8P4R 0402

8.2K 8P4R 0402

YRN3

YRN3

8.2K 8P4R 0402

8.2K 8P4R 0402

YRN4

YRN4

8.2K 8P4R 0402

8.2K 8P4R 0402

YRN5

YRN5

8.2K 8P4R 0402

8.2K 8P4R 0402

GPIO71

12

PCH_INTC_N

34

PCH_INTE_N

56

PCH_REQ_N2

78

PCH_FRAME_N

12

PCH_TRDY_N

34

PCH_REQ_N3

56

PCH_INTF_N

78

PCH_IRDY_N

12

PCH_DEVSEL_N

34

PCH_STOP_N

56

PCH_REQ_N0

78

PCH_INTD_N

12

PCH_PERR_N

34

PCH_PLOCK_N

56

PCH_INTB_N

78

PCH_SERR_N

12

PCH_REQ_N1

34

PCH_INTH_N

56

PCH_INTA_N

78

GPIO71 13

B B

4

3

PCH_DEVSEL_N

CK_PCH_33M_FB17

PCH_INTG_N13

CK_PCH_33M_FB

PCH_IRDY_N

PCH_SERR_N

PCH_STOP_N

PCH_PLOCK_N

PCH_TRDY_N

PCH_PERR_N

PCH_FRAME_N

PCH_REQ_N0

PCH_REQ_N1

PCH_REQ_N2

PCH_REQ_N3

PCH_INTA_N

PCH_INTB_N

PCH_INTC_N

PCH_INTD_N

PCH_INTE_N

PCH_INTF_N

PCH_INTG_N

PCH_INTH_N

BM15

2

PCH1-1

PCH1-1

+Panther Point VER:0.5

+Panther Point VER:0.5

BH8

PAR

BH9

DEVSEL#

BD15

CLKIN_PCILOOPBACK

AV14

PCIRST#

BF11

IRDY#

AV15

PME#

BR6

SERR#

BC12

STOP#

BA17

PLOCK#

BC8

TRDY#

BM3

PERR#

BC11

FRAME#

BA15

GNT0#

AV8

GNT1#_GPIO51

BU12

GNT2#_GPIO53

BE2

GNT3#_GPIO55

BG5

REQ0#

BT5

REQ1#_GPIO50

BK8

REQ2#_GPIO52

AV11

REQ3#_GPIO54

BK10

PIRQA#

BJ5

PIRQB#

PIRQC#

BP5

PIRQD#

BN9

PIRQE#_GPIO2

AV9

PIRQF#_GPIO3

BT15

PIRQG#_GPIO4

BR4

PIRQH#_GPIO5

BIOSTAR-D VER:1.2

BIOSTAR-D VER:1.2

PCI

PCI

C_BE0#

C_BE1#

C_BE2#

C_BE3#

1/10

1/10

COUGARPOINT-H61 B3

COUGARPOINT-H61 B3

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

1

BF15

BF17

BT7

BT13

BG12

BN11

BJ12

BU9

BR12

BJ3

BR9

BJ10

BM8

BF3

BN2

BE4

BE6

BG15

BC6

BT11

BA14

BL2

BC4

BL4

BC2

BM13

BA9

BF9

BA8