BBK DW9953S Service Manual

R

SERVICE MANUAL

DW9953S

Ver 0.0

PREFACE

INDEX

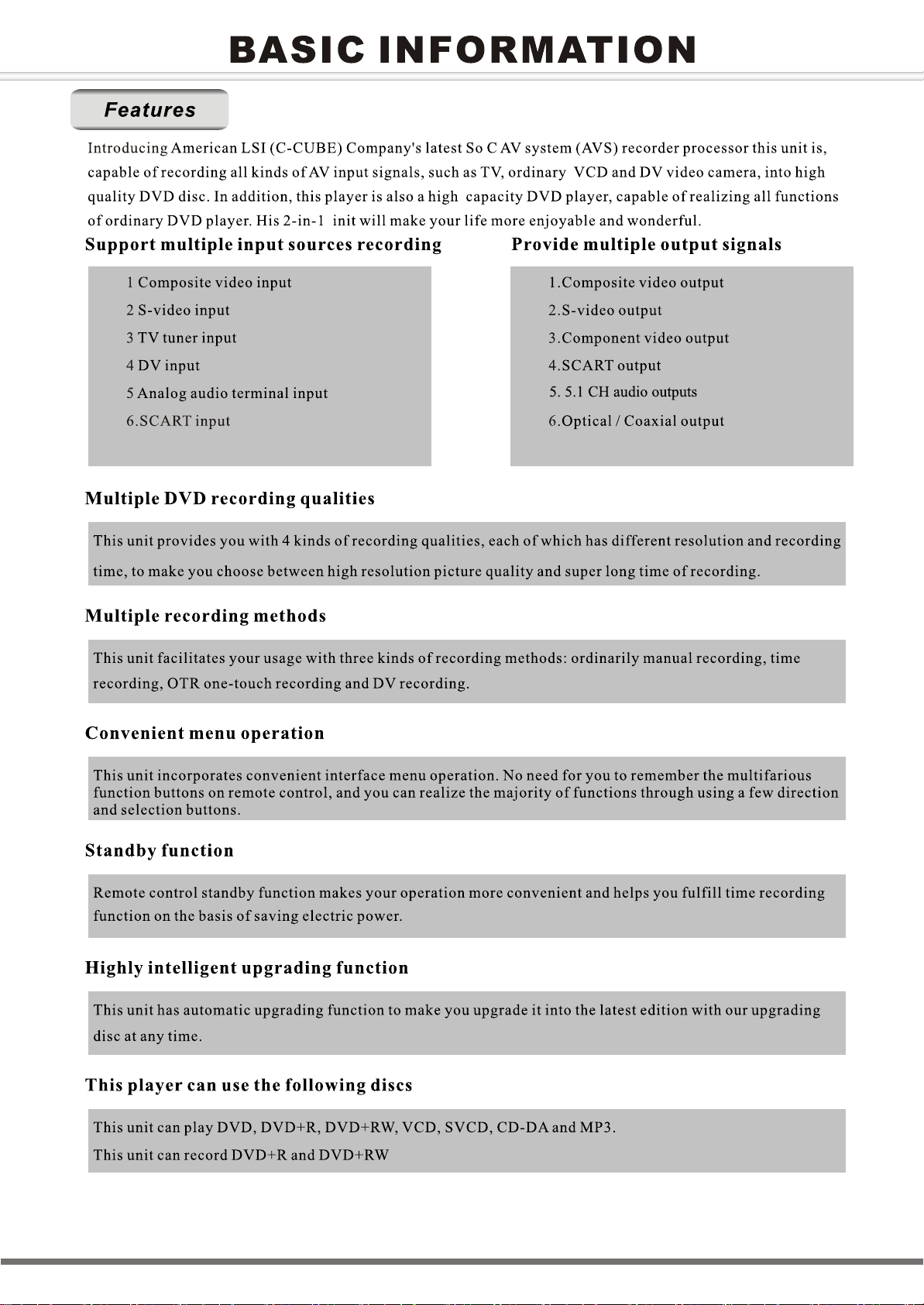

FEATURES

FRONT PANEL&REAR PANEL

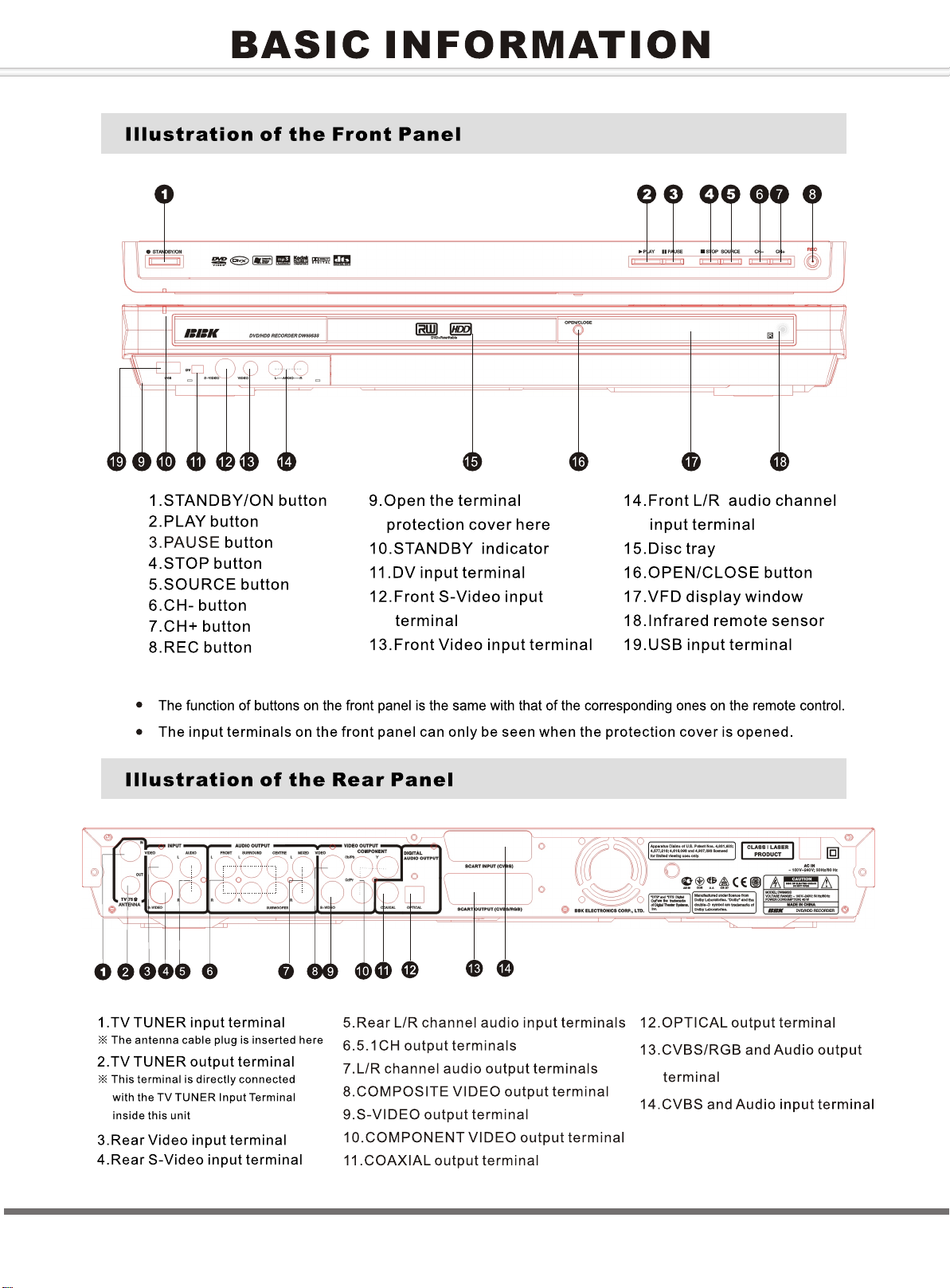

REMOTE CONTROL

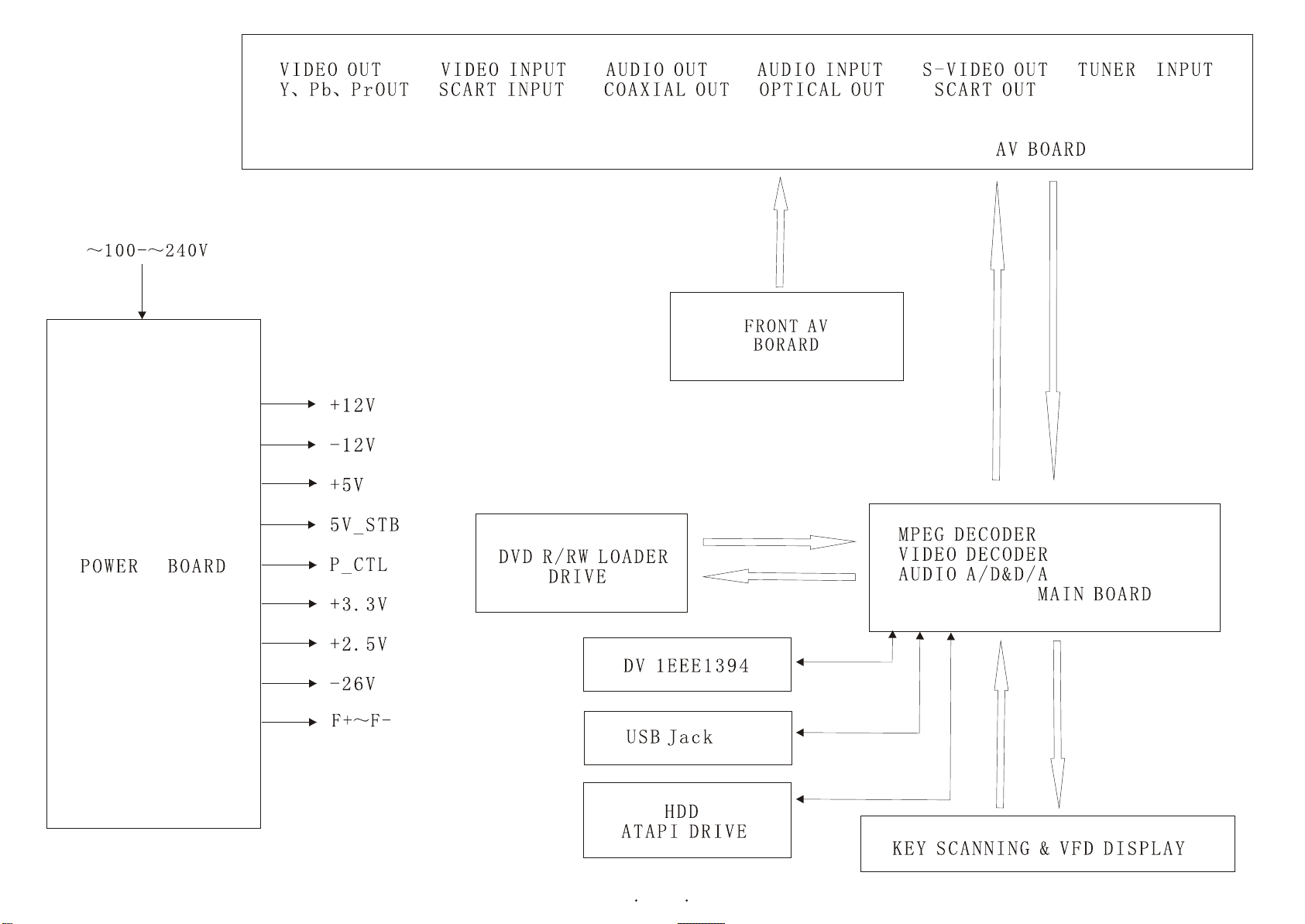

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

...................................................................................................................................

........................................................................................................................

...................................................................................................................

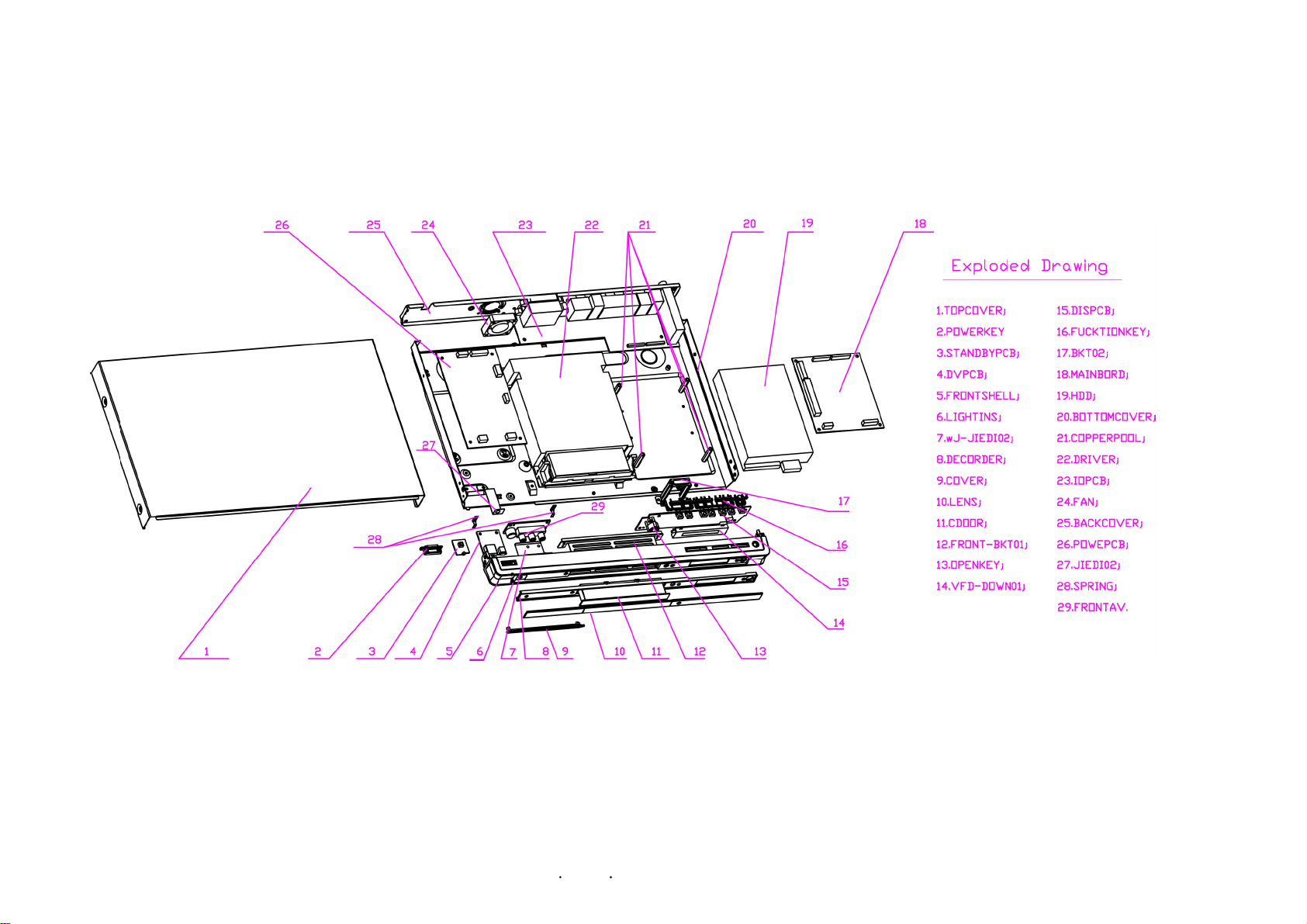

EXPLODED VIEW

EXPLODED VIEW

..............................................................................................................................

PARTS SPECIFICATIONS

SST39VF3201 ..................................................................................................................................

HY5DU561622CT .............................................................................................................................

TSB41AB1

TVP5146

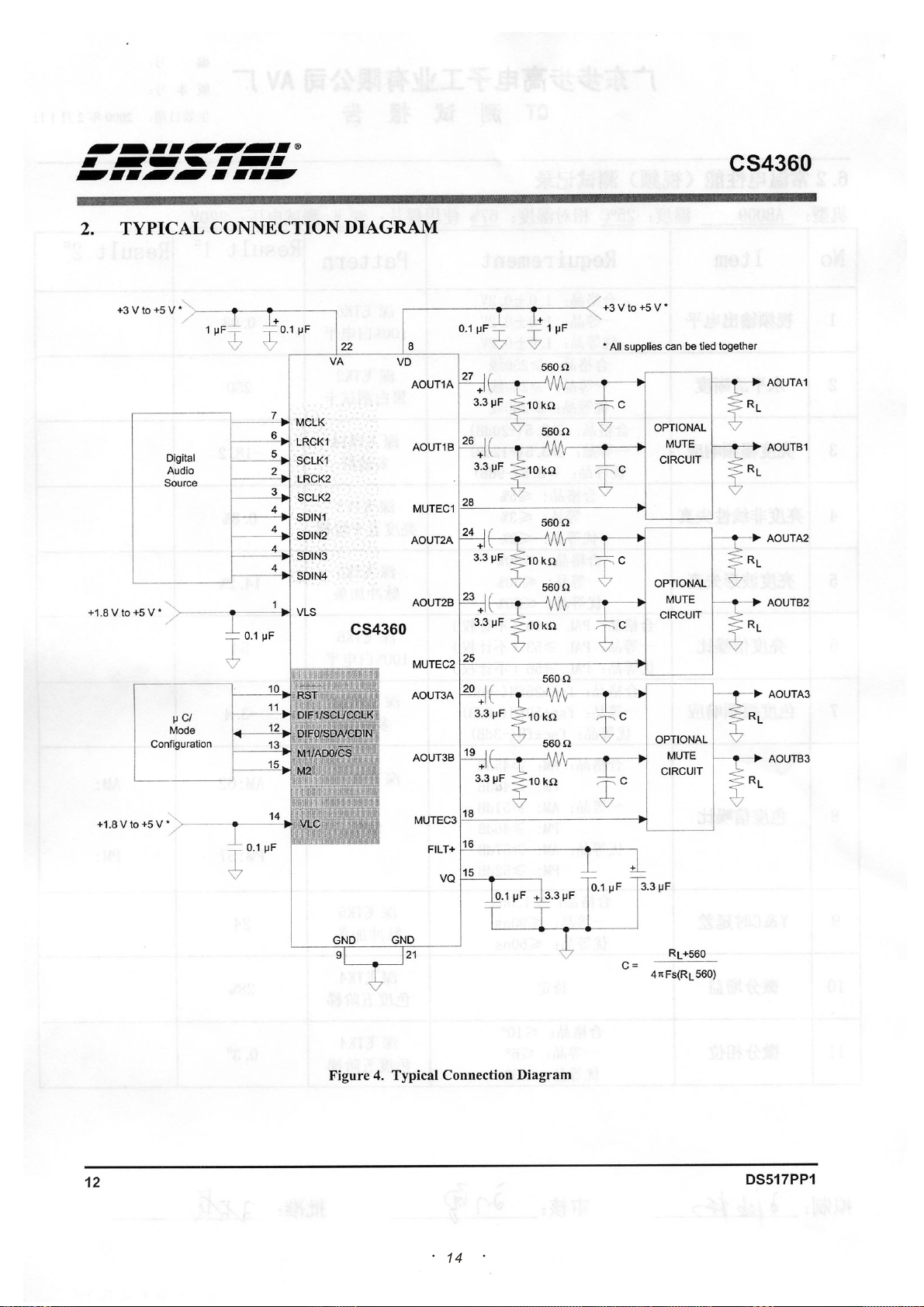

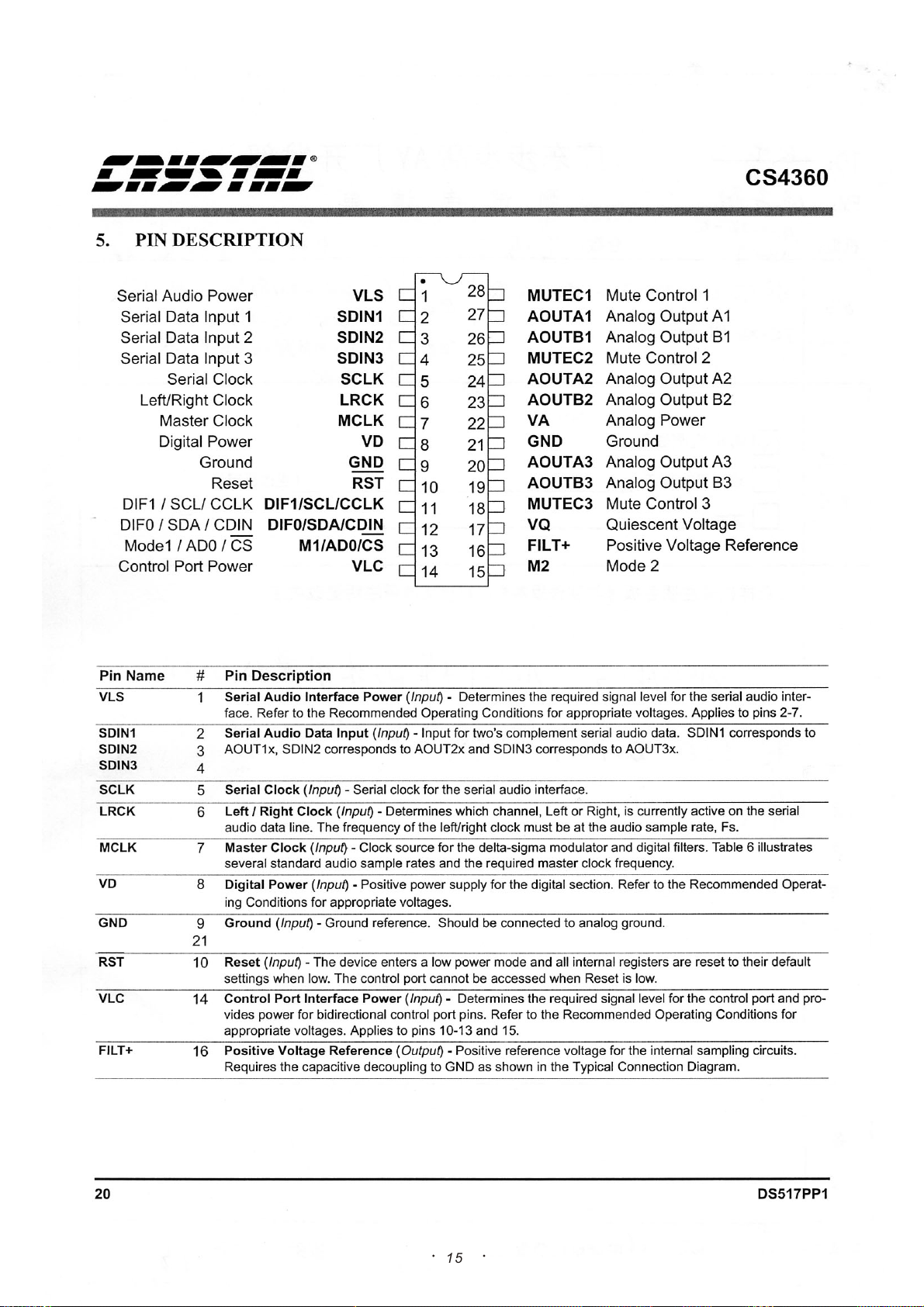

CS4360

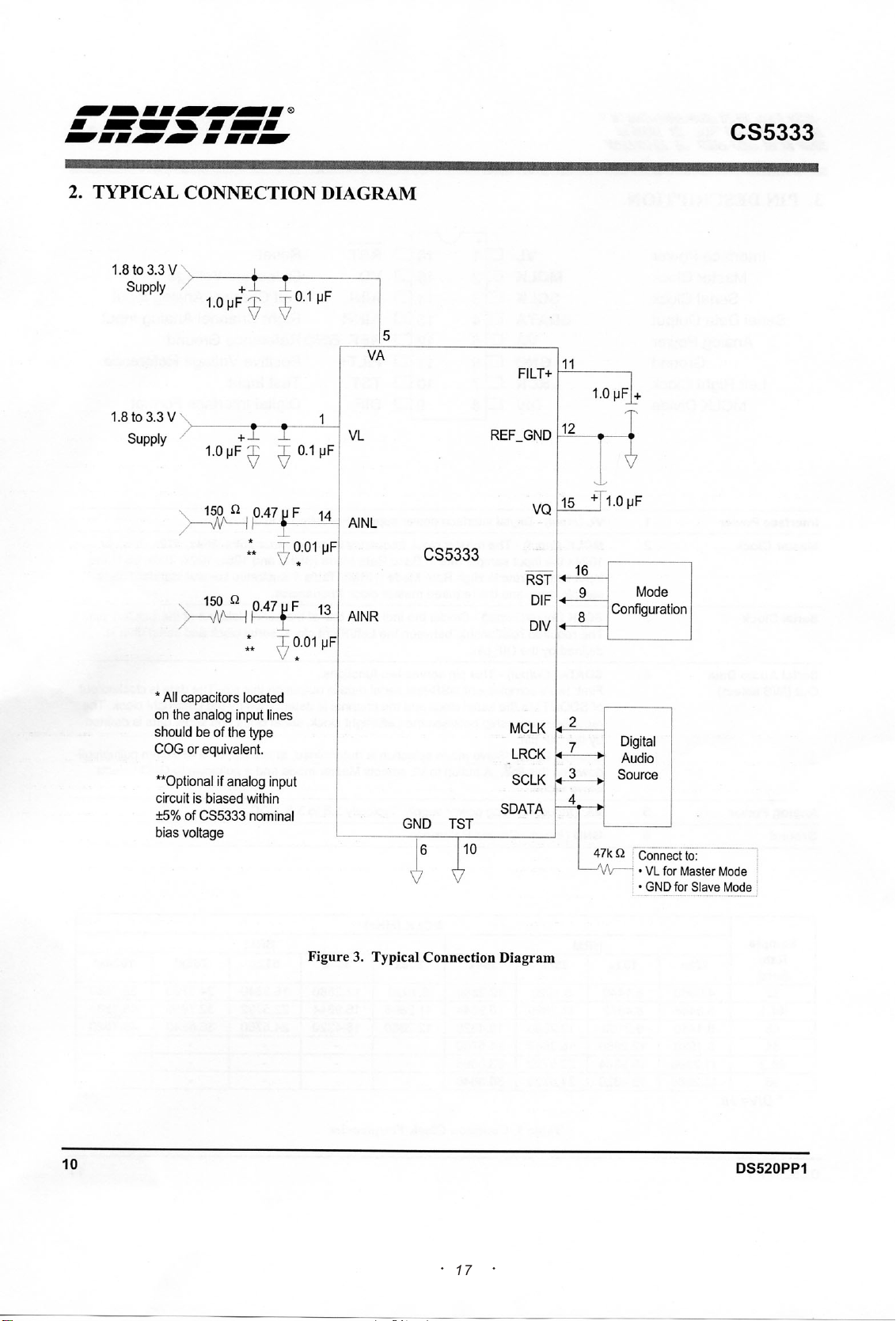

CS5333 .............................................................................................................................................

74HC/HCT14 ..................................................................................................................................

74ALVT16373 ...........................................................................................................................

MM1221~MM1228 .................................................................................................................................

LP2995

PQXXXEZ02Z ..................................................................................................................................

MSP 34x5G

TUNER ...................................................................................................................

..........................................................................................................

...........................................................................................................................

...................................................................................................................

.......................................................................................................................

................................................................................................................

..................................................................................................

1

2

3

4

5

6

7

8

9-12

13-14

15-16

17

18

19-20

21

22

23

24

SCHEMATIC DIAGRAM&PCB SILKSCREEN

MAIN BOARD SCHEMATIC AND PCB LAYOUT 25-39

AV BOARD SCHEMATIC AND PCB LAYOUT 40-51

KEY BOARD SCHEMATIC AND PCB LAYOUT

POWER BOARD SCHEMATIC AND PCB LAYOUT

...............................................................

.................................................................

...............................................................

...........................................................

PARTSLIST

MAIN BOARD ..................................................................................................................................

MAIN KEY BOARD

POWER BOARD

AV BOARD ............................................................................................................................................ 66-67

POWER SWITCH BOARD 68

DV BOARD 69

FRONT AV BOARD 70

.......................................................................................................................................

......................................................................................................................................

................................................................................................................

..............................................................................................................

.........................................................................................................................

52-56

57-59

60-62

63

64-65

7.USB input

1

2

3

BLOCK DIAGRAM

4

EXPLODED VIEW

5

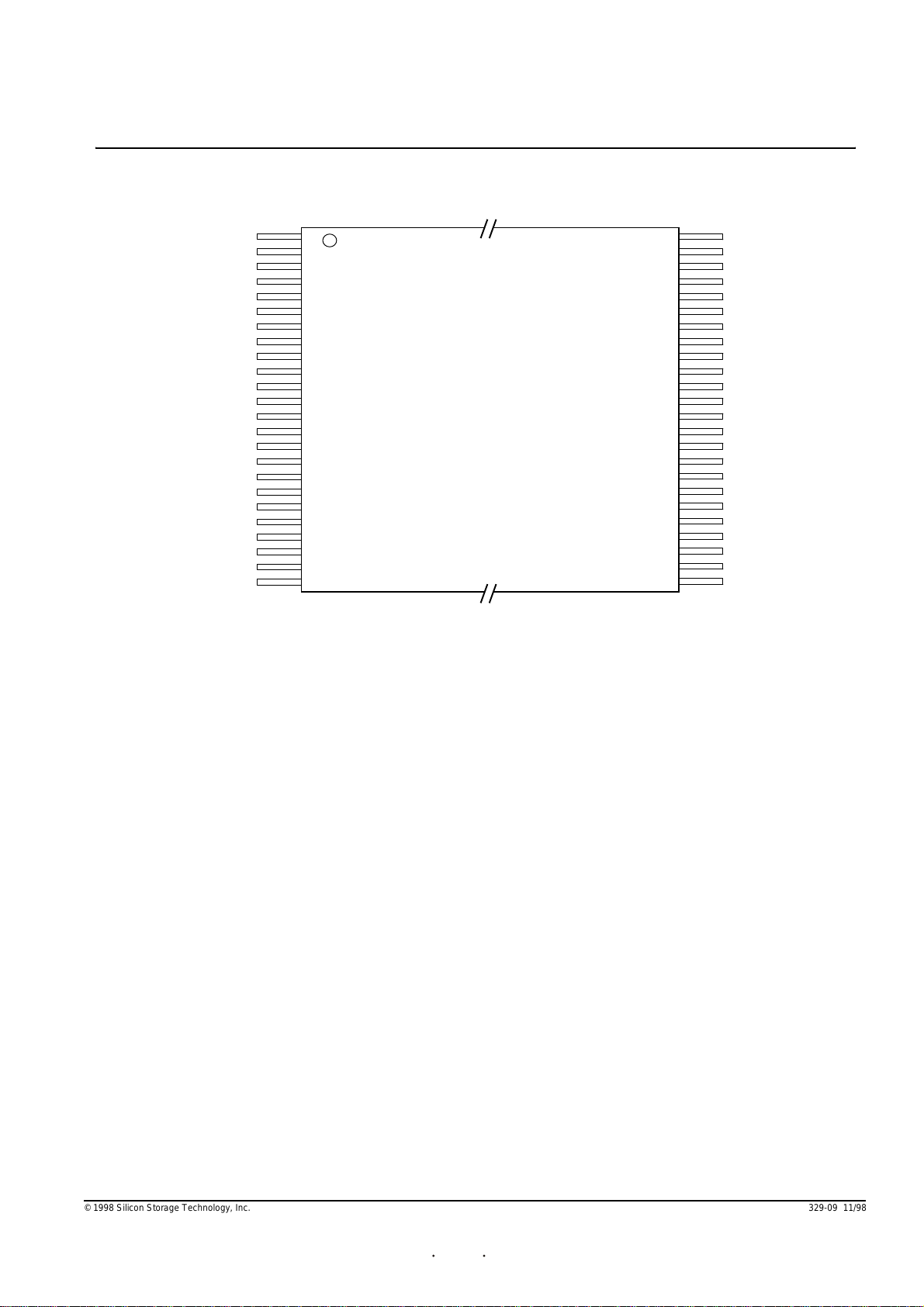

CONNECTION DIAGRAMS

A15

A14

A13

A12

A11

A10

A9

A8

A19

A20

WE#

RESET#

NC

WP#/ACC

RY/BY#

A18

A17

A7

A6

A5

A4

A3

A2

A1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48-Pin Standard TSOP

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

A16

BYTE#

V

SS

DQ15/A-1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

CC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE#

V

SS

CE#

A0

© 1998 Silicon Storage Technology, Inc.329-09 11/98

6

PIN CONFIGURATION(TSOP)

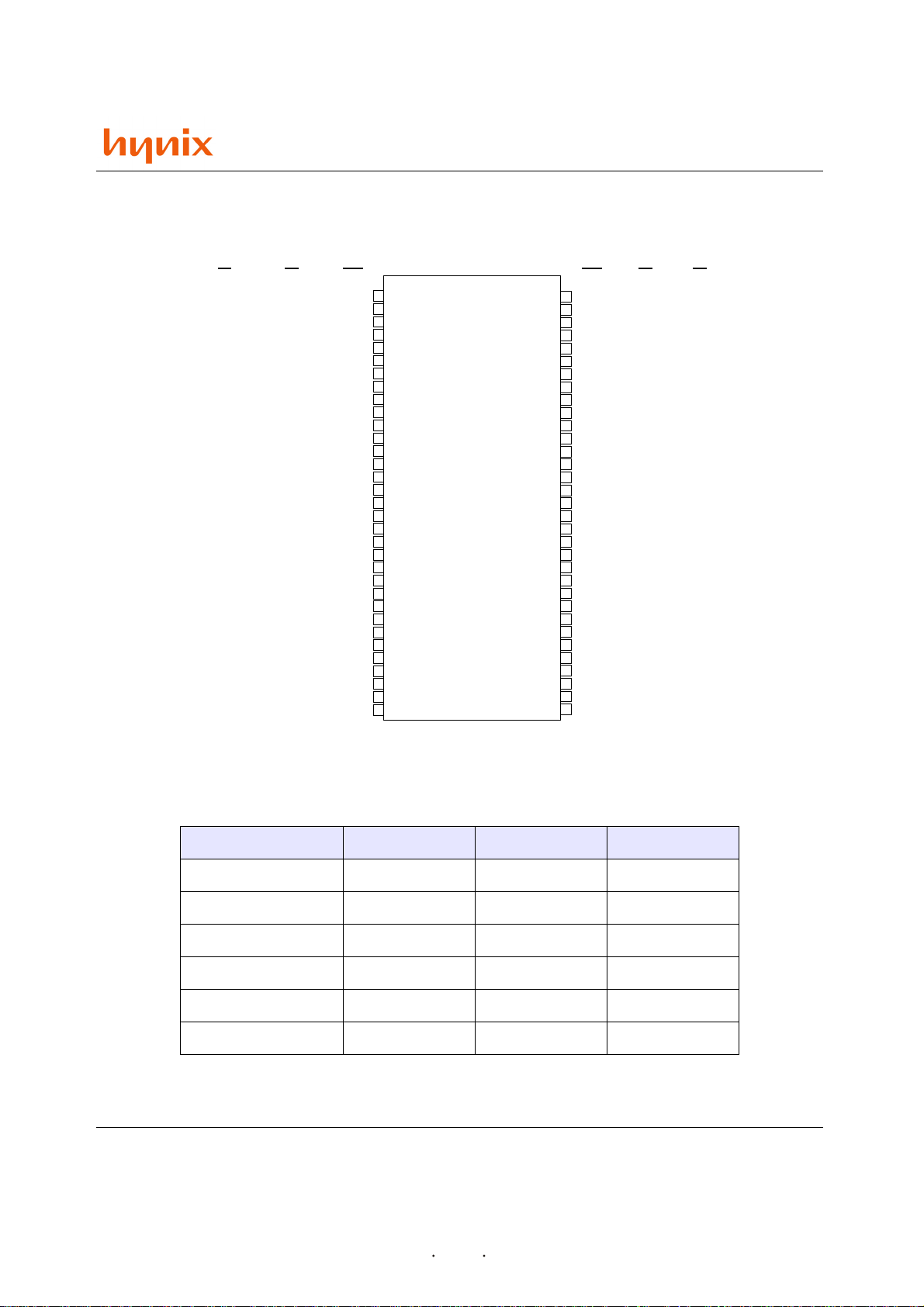

HY5DU561622CT

HY5DU28822ET

HY5DU281622ET

x16 x8 x4x4 x8 x16

VDD

NC

VDDQ

NC

DQ0

VSSQ

NC

NC

VDDQ

NC

DQ1

VSSQ

NC

NC

VDDQ

NC

NC

VDD

NC

NC

/WE

/CAS

/RAS

/CS

NC

BA0

BA1

A10/AP

A0

A1

A2

A3

VDD

VDD

DQ0

VDDQ

NC

DQ1

VSSQ

NC

DQ2

VDDQ

NC

DQ3

VSSQ

NC

NC

VDDQ

NC

NC

VDD

NC

NC

/WE

/CAS

/RAS

/CS

NC

BA0

BA1

A10/AP

A0

A1

A2

A3

VDD

VDD

DQ0

VDDQ

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

DQ7

NC

VDDQ

LDQS

NC

VDD

NC

LDM

/WE

/CAS

/RAS

/CS

NC

BA0

BA1

A10/AP

A0

A1

A2

A3

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

400mil X 875mil

15

16

66pin TSOP -II

17

18

0.65mm pin pitch

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

VSS

66

DQ15

65

VSSQ

64

DQ14

63

DQ13

62

VDDQ

61

DQ12

60

DQ11

59

VSSQ

58

DQ10

57

DQ9

56

VDDQ

55

DQ8

54

NC

53

VSSQ

52

UDQS

51

NC

50

VREF

49

VSS

48

UDM

47

/CK

46

CK

45

CKE

44

NC

43

NC

42

A11

41

A9

40

A8

39

A7

38

A6

37

A5

36

A4

35

VSS

34

VSS

DQ7

VSSQ

NC

DQ6

VDDQ

NC

DQ5

VSSQ

NC

DQ4

VDDQ

NC

NC

VSSQ

DQS

NC

VREF

VSS

DM

/CK

CK

CKE

NC

NC

A11

A9

A8

A7

A6

A5

A4

VSS

VSS

NC

VSSQ

NC

DQ3

VDDQ

NC

NC

VSSQ

NC

DQ2

VDDQ

NC

NC

VSSQ

DQS

NC

VREF

VSS

DM

/CK

CK

CKE

NC

NC

A11

A9

A8

A7

A6

A5

A4

VSS

ROW AND COLUMN ADDRESS TABLE

ITEMS 32Mx4 16Mx8 8Mx16

Organization 8M x 4 x 4banks 4M x 8 x 4banks 2M x 16 x 4banks

Row Address A0 - A11 A0 - A11 A0 - A11

Column Address A0-A9, A11 A0-A9 A0-A8

Bank Address BA0, BA1 BA0, BA1 BA0, BA1

Auto Precharge Flag A10 A10 A10

Refresh 4K 4K 4K

Rev. 0.4 /Aug. 2004

7

SLLS423D – JUNE 2000 – REVISED SEPTEMBER 2002

description (continued)

required for normal network operation regardless of the state of the PHY-LLC interface. When the interface is

in the reset or disabled state and LPS is again observed active, the PHY initializes the interface and returns it

to normal operation.

When the PHY-LLC interface is in the low-power disabled state, the TSB41AB1 automatically enters a

low-power mode if the port is inactive (disconnected, disabled, or suspended). In this low-power mode, the

TSB41AB1 disables its internal clock generators and also disables various voltage and current reference

circuits depending on the state of the port (some reference circuitry must remain active in order to detect new

cable connections, disconnections, or incoming TPBIAS, for example). The lowest power consumption (the

ultralow-power sleep mode) is attained when the port is either disconnected, or disabled with the port interrupt

enable bit cleared. The TSB41AB1 exits the low-power mode when the LPS input is asserted high or when a

port event occurs which requires that the TSB41AB1 become active in order to respond to the event or to notify

the LLC of the event (for example, incoming bias is detected on a suspended port, a disconnection is detected

on a suspended port, a new connection is detected on a nondisabled port, etc.). The SYSCLK output becomes

active (and the PHY-LLC interface is initialized and becomes operative) within 7.3 ms after LPS is asserted high

when the TSB41AB1 is in the low-power mode.

The PHY uses the C/LKON terminal to notify the LLC to power up and become active. When activated, the

C/LKON signal is a square wave of approximately 163-ns period. The PHY activates the C/LKON output when

the LLC is inactive and a wake-up event occurs. The LLC is considered inactive when either the LPS input is

inactive, as described above, or the LCtrl bit is cleared to 0. A wake-up event occurs when a link-on PHY packet

addressed to this node is received, or when a PHY interrupt occurs. The PHY deasserts the C/LKON output

when the LLC becomes active (both LPS active and the LCtrl bit set to 1). The PHY also deasserts the C/LKON

output when a bus reset occurs unless a PHY interrupt condition exists which would otherwise cause C/LKON

to be active.

PHP package terminal diagram

SYSCLK

CTL0

CTL1

D0

D1

D2

D3

D4

D5

D6

D7

PD

LREQ

DGND

DGND

47 46 45 44 4348 42 40 39 3841

1

2

3

4

5

6

7

8

9

10

11

12

14 15

DGND

C/LKON

16

13

LPS

PHP PACKAGE

(TOP VIEW)

DDDVDD

DV

XO

XI

TSB41AB1

17 18 19 20

ISO

PC1

PC2

PC0

DD

PLLGND

PLLV

FILTER1

22 23 24

21

DD

CPS

DV

TESTM

FILTER0

RESET

37

SE

SM

36

35

34

33

32

31

30

29

28

27

26

25

AGND

AV

DD

R1

R0

AGND

TPBIAS

TPA+

TPA–

TPB+

TPB–

AGND

AV

DD

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

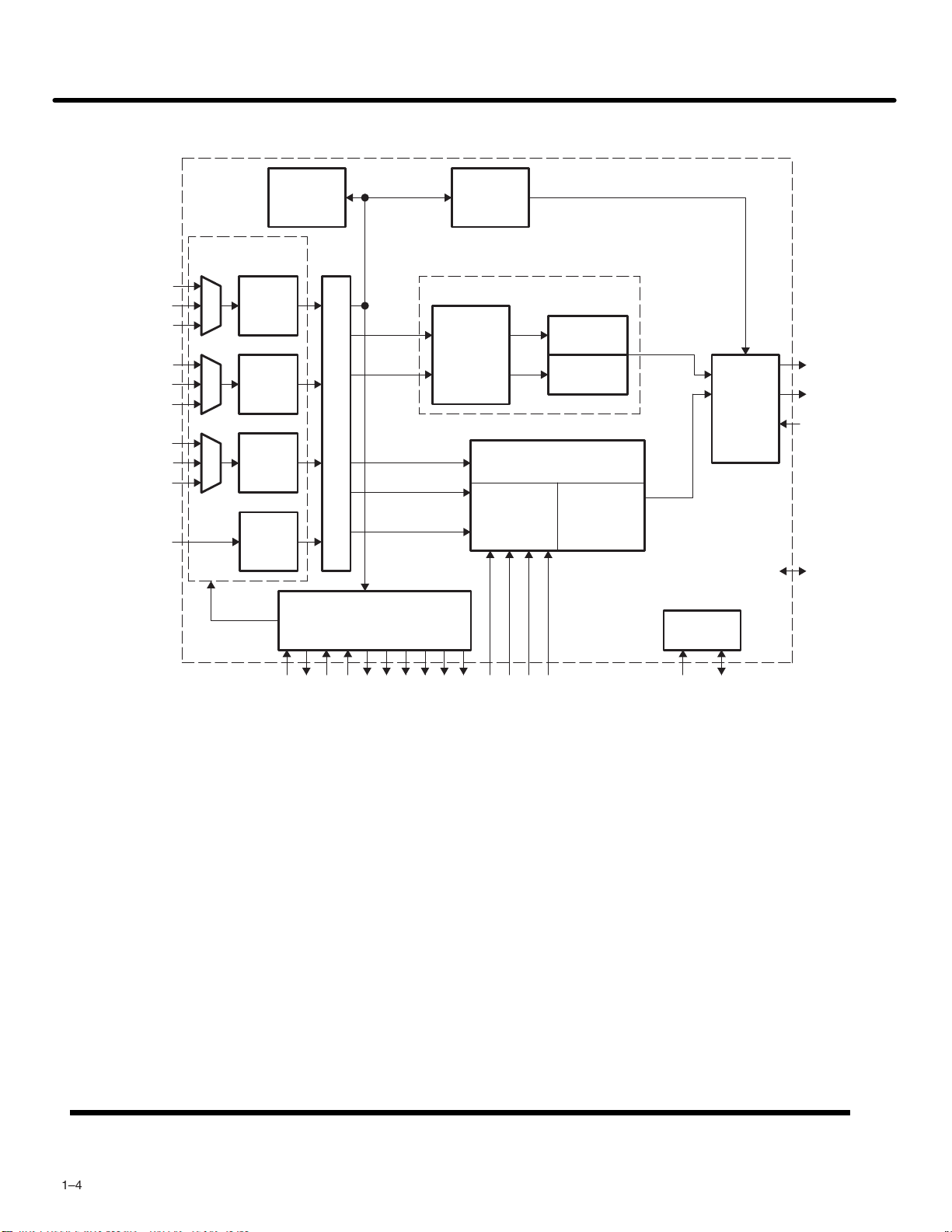

1.5 Functional Block Diagram

TVP5146

CVBS/

Pb/B/C

CVBS/

Y/G

CVBS/

Pr/R/C

CVBS/Y

VI_1_A

VI_1_B

VI_1_C

VI_2_A

VI_2_B

VI_2_C

VI_3_A

VI_3_B

VI_3_C

VI_4_A

Protection

Detector

Analog Front End

ADC1

ADC2

ADC3

ADC4

Sampling

Clock

Copy

M

U

X

Timing Processor

with Sync Detector

CVBS/Y/G

CVBS/Y

C

Y/G

Pb/B

Pr/R

VBI

Data

Slicer

Composite and S-Video Processor

Y/C

Separation

5-line

Adaptive

Comb

Gain/Offset

Y

C

Component

Luma

Processing

Chroma

Processing

Processor

Color

Space

Conversion

YCbCr

YCbCr

Host

Interface

Output

Formatter

Y[9:0]

C[9:0]

FSS

GPIO

XTAL1

XTAL2

PWDN

RESETB

AVID

DATACLK

FID

VS/VBLK

GLCO

HS/CS

DRDGDB

Figure 1–1. Functional Block Diagram

FSO

SCL

SDA

1–4

9

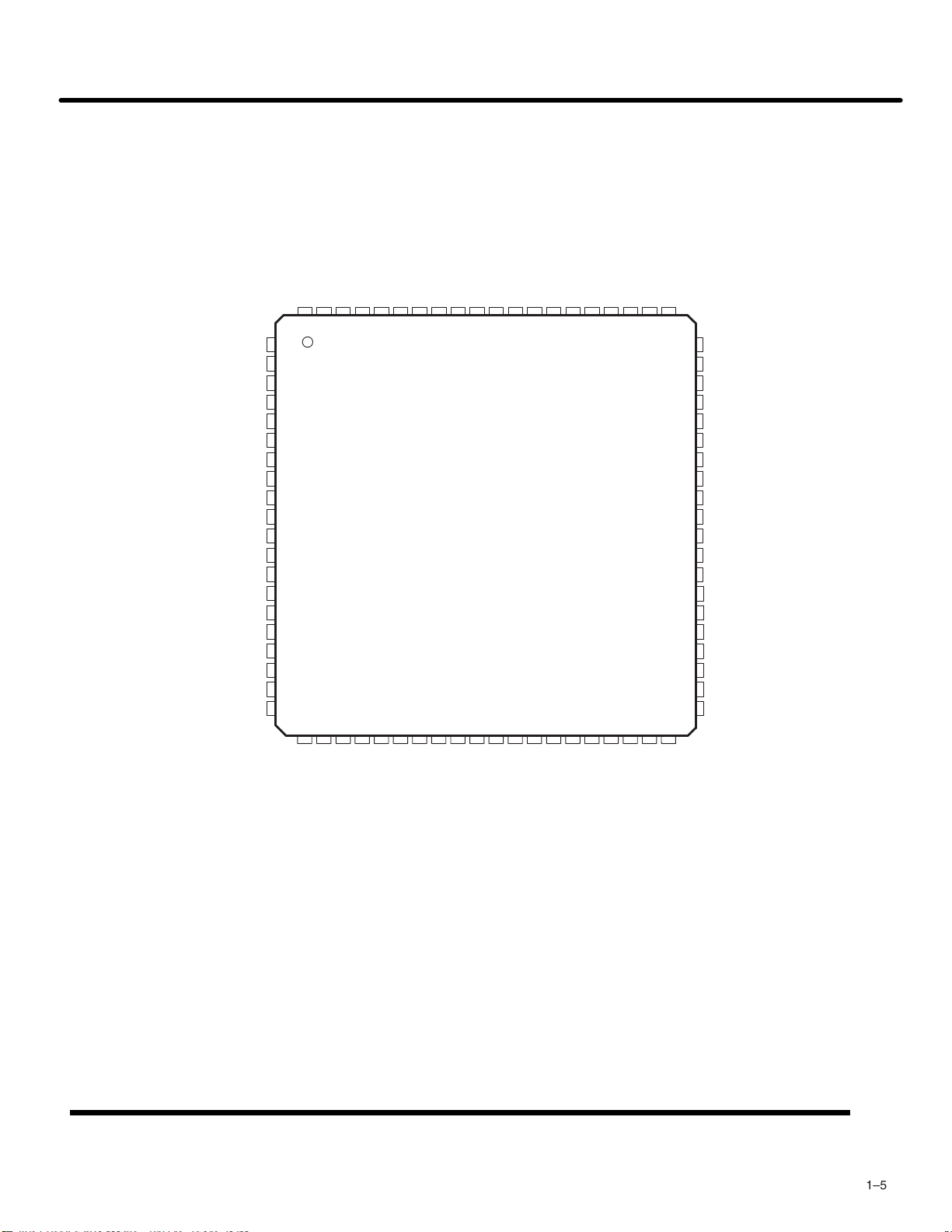

1.6 Terminal Assignments

VI_1_A

CH1_A18GND

CH1_A18VDD

PLL_A18GND

PLL_A18VDD

XTAL2

XTAL1

PFP PACKAGE

(TOP VIEW)

VS/VBLK/GPIO

HS/CS/GPIO

FID/GPIO

C_0/GPIO

C_1/GPIO

DGND

DVDD

C_2/GPIO

C_3/GPIO

C_4/GPIO

C_5/GPIO

IOGND

IOVDD

TVP5146

VI_1_B

VI_1_C

CH1_A33GND

CH1_A33VDD

CH2_A33VDD

CH2_A33GND

VI_2_A

VI_2_B

VI_2_C

CH2_A18GND

CH2_A18VDD

A18VDD_REF

A18GND_REF

CH3_A18VDD

CH3_A18GND

VI_3_A

VI_3_B

VI_3_C

CH3_A33GND

CH3_A33VDD

79 78 77 76 7580 74 72 71 7073

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

22 23

24

VI_4_A

CH4_A33VDD

CH4_A33GND

25 26 27 28

SCL

AGND

DGND

CH4_A18VDD

CH4_A18GND

29

30 31 32 33

SDA

INTREQ

69 682167 66 65 64

34 35 36 37 38 39 40

DVDD

DGND

PWDN

RESETB

FSS/GPIO

63 62 61

IOVDD

AVID/GPIO

GLCO/I2CA

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

IOGND

DATACLK

C_6/GPIO/RED

C_7/GPIO/GREEN

C_8/GPIO/BLUE

C_9/GPIO/FSO

DGND

DVDD

Y_0

Y_1

Y_2

Y_3

Y_4

IOGND

IOVDD

Y_5

Y_6

Y_7

Y_8

Y_9

DGND

DVDD

Figure 1–2. Terminal Assignments Diagram

10

1–5

TVP5146

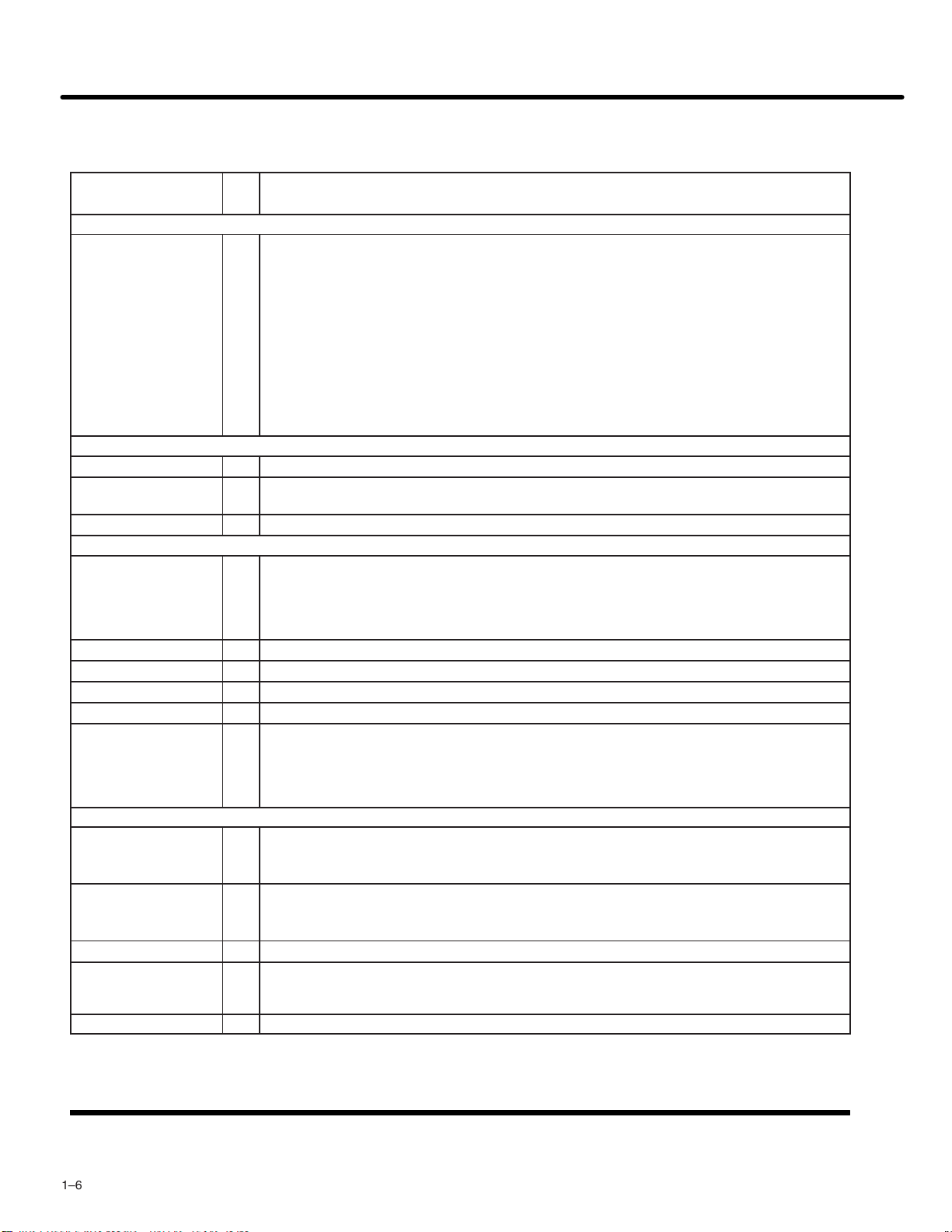

1.7 Terminal Functions

Table 1–1. Terminal Functions

TERMINAL

NAME NUMBER

Analog Video

VI_1_A

VI_1_B

VI_1_C

VI_2_A

VI_2_B

VI_2_C

VI_3_A

VI_3_B

VI_3_C

VI_4_A

Clock Signals

DATACLK 40 O Line-locked data output clock.

XTAL1 74 I

XTAL2 75 O External clock reference output. Not connected if XTAL1 is driven by an external single-ended oscillator.

Digital Video

C[9:0]/

GPIO[9:0]

D_BLUE 58 I Digital BLUE input from overlay device

D_GREEN 59 I Digital GREEN input from overlay device

D_RED 60 I Digital RED input from overlay device

FSO 57 I Fast-switch overlay between digital RGB and any video

Y[9:0]

Miscellaneous Signals

FSS/GPIO 35 I/O

GLCO/I2CA 37 I/O

INTREQ 30 O Interrupt request

PWDN 33 I

RESETB 34 I Reset input, active low

80

1

2

7

8

9

16

17

18

23

57, 58,

59, 60,

63, 64,

65, 66,

69, 70

43, 44,

45, 46,

47, 50,

51, 52,

53, 54

I/O

VI_1_x: Analog video input for CVBS/Pb/B/C

VI_2_x: Analog video input for CVBS/Y/G

VI_3_x: Analog video input for CVBS/Pr/R/C

VI_4_A: Analog video input for CVBS/Y

I

Up to 10 composite, 4 S-video, and 2 composite or 3 component video inputs (or a combination thereof)

can be supported.

The inputs must be ac-coupled. The recommended coupling capacitor is 0.1 µF.

The possible input configurations are listed in the input select register at I2C subaddress 00h (see

Section 2.11.1).

External clock reference input. It may be connected to an external oscillator with a 1.8-V compatible clock

signal or a 14.31818-MHz crystal oscillator.

Digital video output of CbCr, C[9] is MSB and C[0] is LSB. Unused outputs can be left unconnected. Also,

these terminals can be programmable general-purpose I/O.

O

For the 8-bit mode, the two LSBs are ignored.

Digital video output of Y/YCbCr, Y[9] is MSB and Y[0] is LSB.

O

For the 8-bit mode, the two LSBs are ignored. Unused outputs can be left unconnected.

Fast-switch (blanking) input. Switching signal between the synchronous component video (YPbPr/RGB)

and the composite video input.

Programmable general-purpose I/O

Genlock control output (GLCO). Two Genlock data formats are available: TI format and real time control

(RTC) format.

During reset, this terminal is an input used to program the I2C address LSB.

Power down input:

1 = Power down

0 = Normal mode

DESCRIPTION

1–6

11

Table 1–1. Terminal Functions (Continued)

TVP5146

TERMINAL

NAME NUMBER

Host Interface

SCL 28 I I2C clock input

SDA 29 I/O I2C data bus

Power Supplies

AGND 26 I Analog ground. Connect to analog ground.

A18GND_REF 13 I Analog 1.8-V return

A18VDD_REF 12 I Analog power for reference 1.8 V

CH1_A18GND

CH2_A18GND

CH3_A18GND

CH4_A18GND

CH1_A18VDD

CH2_A18VDD

CH3_A18VDD

CH4_A18VDD

CH1_A33GND

CH2_A33GND

CH3_A33GND

CH4_A33GND

CH1_A33VDD

CH2_A33VDD

CH3_A33VDD

CH4_A33VDD

DGND

DVDD

IOGND 39, 49, 62 I Digital power return

IOVDD 38, 48, 61 I Digital power. Connect to 3.3 V or less for reduced noise.

PLL_A18GND 77 I Analog power return

PLL_A18VDD 76 I Analog power. Connect to 1.8 V.

Sync Signals

HS/CS/GPIO 72 I/O

VS/VBLK/GPIO 73 I/O

FID/GPIO 71 I/O

AVID/GPIO 36 I/O

79

10

15

24

78

11

14

25

3

6

19

22

4

5

20

21

27, 32, 42,

56, 68

31, 41, 55,

67

I/O

I Analog 1.8-V return

I Analog power. Connect to 1.8 V.

I Analog 3.3-V return

I Analog power. Connect to 3.3 V.

I Digital return

I Digital power. Connect to 1.8 V.

Horizontal sync output or digital composite sync output

Programmable general-purpose I/O

Vertical sync output (for modes with dedicated VSYNC) or VBLK output

Programmable general-purpose I/O

Odd/even field indicator output. This terminal needs a pulldown resistor.

Programmable general-purpose I/O

Active video indicator output

Programmable general-purpose I/O

DESCRIPTION

121413151416151716

1–7

Philips SemiconductorsProduct specification

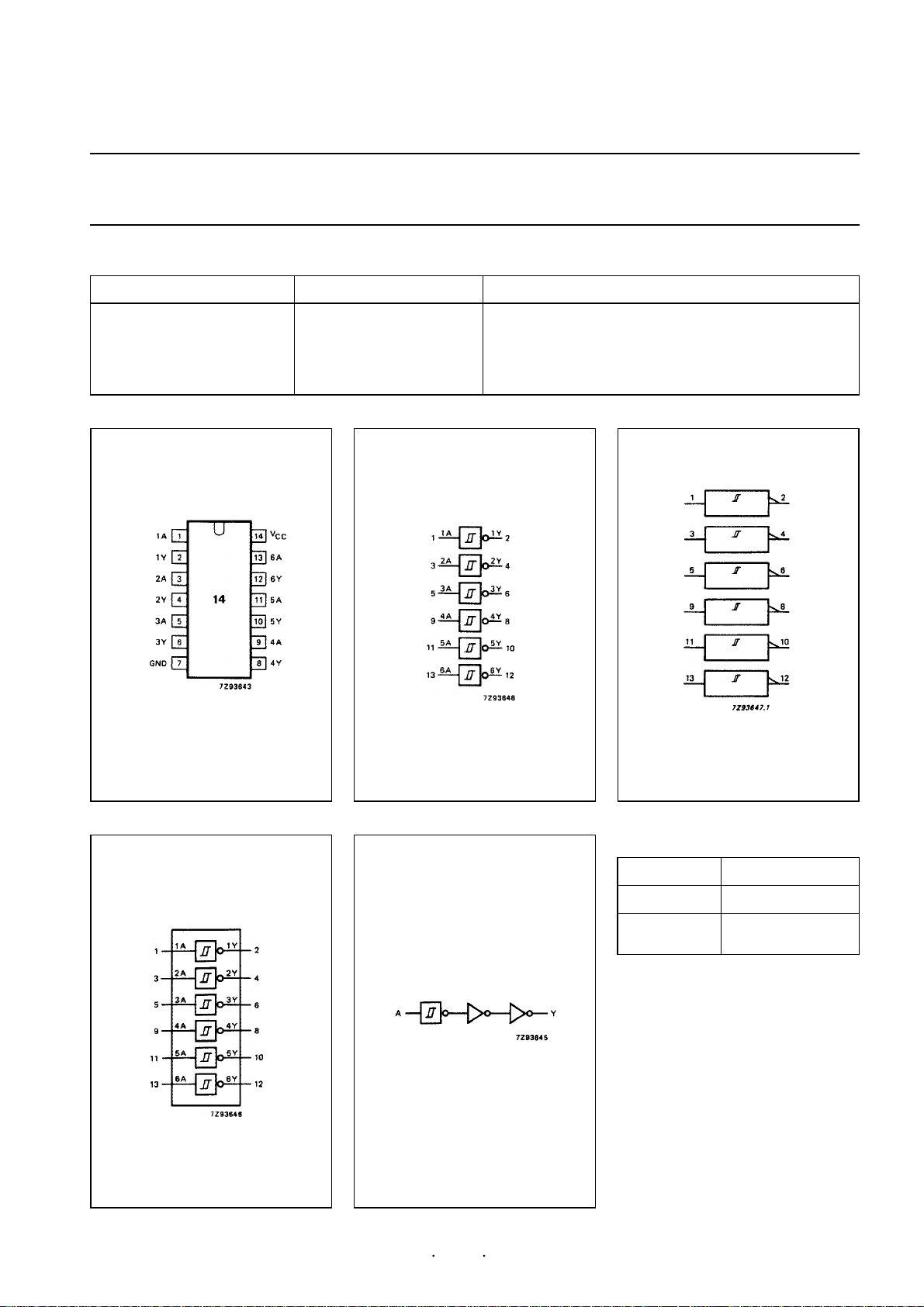

Hex inverting Schmitt trigger 74HC/HCT14

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1, 3, 5, 9, 11, 13 1A to 6A data inputs

2, 4, 6, 8, 10, 12 1Y to 6Y data outputs

7 GND ground (0 V)

14 V

CC

positive supply voltage

Fig.1 Pin configuration. Fig.2 Logic symbol. Fig.3 IEC logic symbol.

FUNCTION TABLE

INPUT OUTPUT

nA nY

L

H

Notes

1. H = HIGH voltage level

L = LOW voltage level

APPLICATIONS

• Wave and pulse shapers

• Astable multivibrators

• Monostable multivibrators

Fig.4 Functional diagram. Fig.5 Logic diagram

(one Schmitt trigger).

H

L

17

Philips Semiconductors Product specification

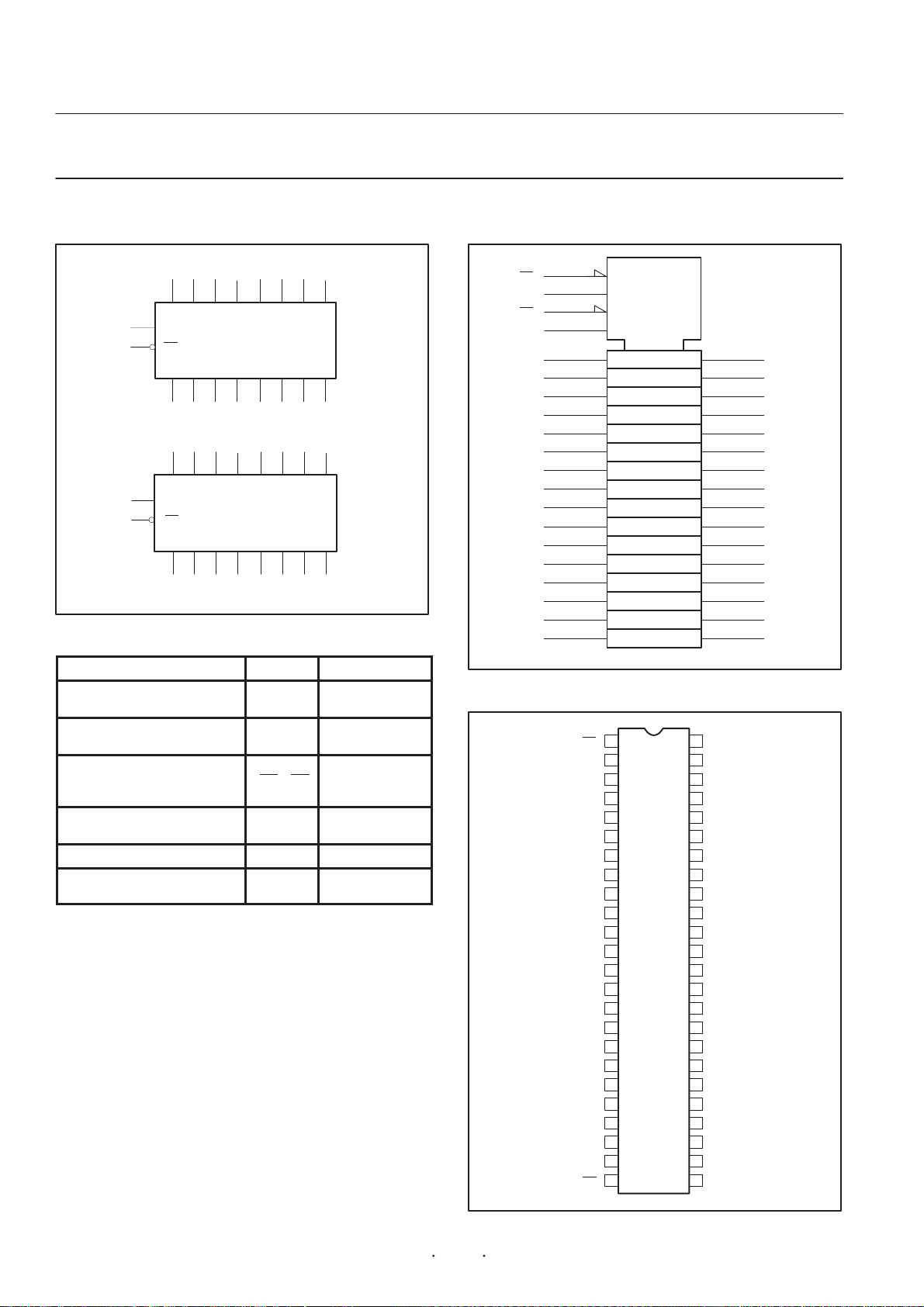

74ALVT163732.5V/3.3V 16-bit transparent D-type latch (3-State)

LOGIC SYMBOL

47 46 44 43

1

1D0 1D1 1D2 1D3

1LE

1OE

1Q0 1Q1 1Q2651Q3

32

36 35 33 32

2D02D21 2D2 2D3

2LE

2OE

2Q0 2Q1 2Q2 2Q3

1413 1716

48

25

24

41 40 38 37

1D4 1D5 1D6 1D7

1Q4 1Q5 1Q6

30 29 27 26

2D4 2D5 2D6 2D7

2Q4 2Q5 2Q6 2Q7

1Q7

98

2019 2322

SA00044

1211

PIN DESCRIPTION

PIN NUMBER SYMBOL FUNCTION

47, 46, 44, 43, 41, 40, 38, 37,

36, 35, 33, 32, 30, 29, 27, 26

2, 3, 5, 6, 8, 9, 11, 12, 13,

14, 16, 17, 19, 20, 22, 23

1, 24 1OE, 2OE

48, 25 1LE, 2LE

4, 10, 15, 21, 28, 34, 39, 45 GND Ground (0V)

7, 18, 31, 42 V

1D0 – 1D7

2D0 – 2D7

1Q0 – 1Q7

2Q0 – 2Q7

CC

Data inputs

Data outputs

Output enable

inputs

(active-Low)

Enable inputs

(active-High)

Positive

supply voltage

LOGIC SYMBOL (IEEE/IEC)

1OE

1LE

2OE

2LE

1D1

1D2

1D3

1D4

1D5

1D6

1D7

1D8

2D1

2D2

2D3

2D4

2D5

2D6

2D7

2D8

1

48

24

25

47

46

44

43

41

40

38

37

36

35

33

32

30

29

27

26

1EN

C3

2EN

C4

3D

4D

PIN CONFIGURATION

1

1OE

2

1Q0

1Q1

3

GND

4

1Q2

5

6

1Q3

7

V

CC

8

1Q4

1Q5

9

GND

10

1Q6

11

1Q7

12

2Q0

13

2Q1

14

GND

15

16

2Q2

2Q3

17

18

V

CC

2Q4

19

20

2Q5

21

GND

22

2Q6

23

2Q7

24

2OE

1 ∇

2 ∇

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

SA00043

1LE

1D0

1D1

GND

1D2

1D3

V

CC

1D4

1D5

GND

1D6

1D7

2D0

2D1

GND

2D2

2D3

V

CC

2D4

2D5

GND

2D6

2D7

2LE

2

1Q1

3

1Q2

5

1Q3

6

1Q4

8

1Q5

9

1Q6

11

1Q7

12

1Q8

13

2Q1

14

2Q2

16

2Q3

17

2Q4

19

2Q5

20

2Q6

22

2Q7

23

2Q8

SW00010

18

MITSUMI

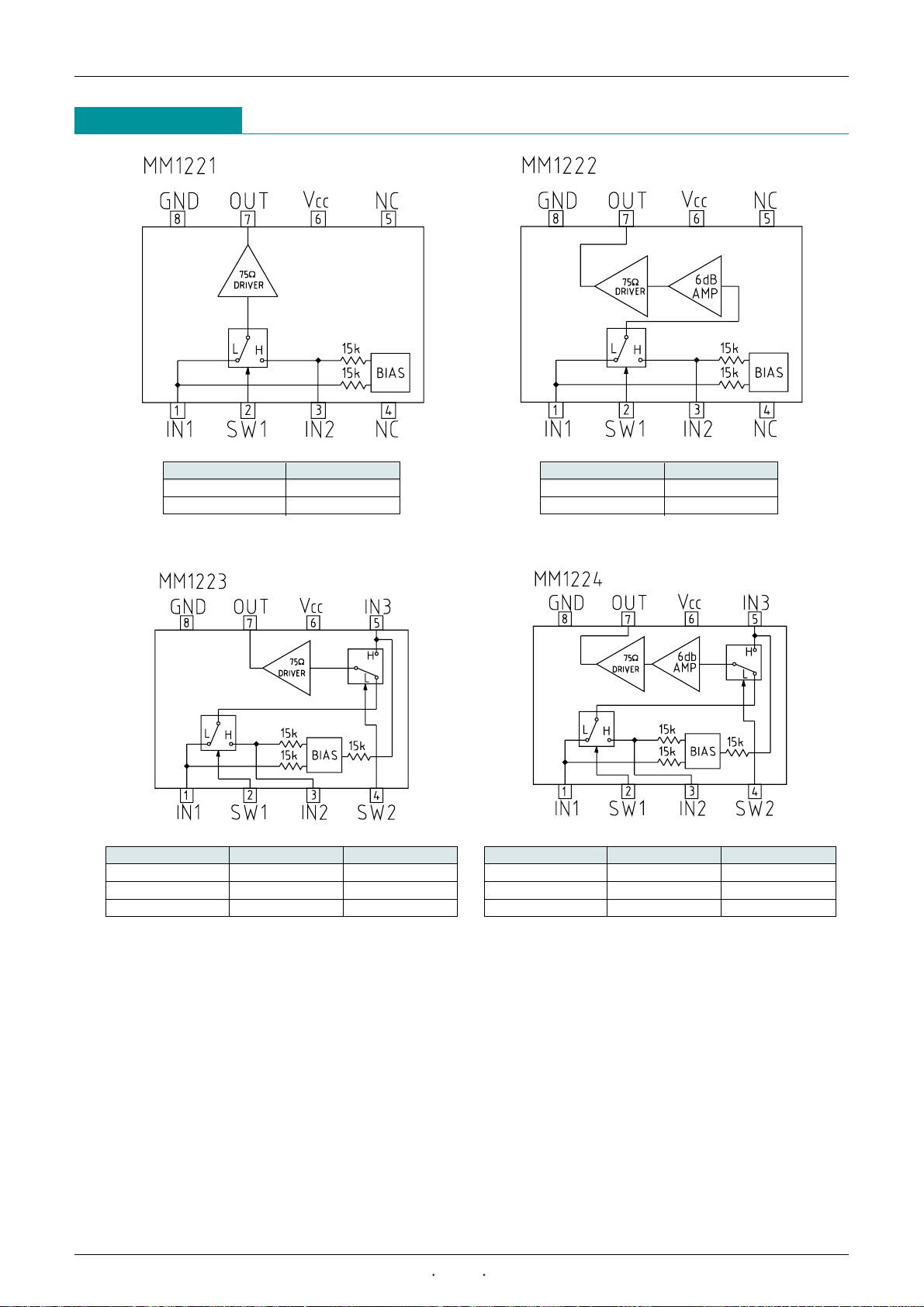

2-Input 1-Output Video Switch (75Ω driver)/3-Input 1-Output Video Switch (75Ω driver) MM1221~1228

2-Input 1-Output Video Switch (75Ω driver)/3-Input 1-Output Video Switch (75Ω driver)

Monolithic IC MM1221~MM1228

Outline

These ICs are high grade video switches with 2-input 1-output or 3-input 1-output and built-in 75Ω driver.

The series includes those with and without built-in clamp and 6dB amp circuits.

Circuit configuration tables and block diagrams are as follows.

MM1228 is used as the representative model in this description.

MM1221~MM1228 Series Circuit Configuration Table

Model name # of Inputs # of Outputs 6dB amp circuit Clamp circuit

MM1221 2 1 No No 8~13V

MM1222 2 1 Yes No 8~13V

MM1223 3 1 No No 8~13V

MM1224 3 1 Yes No 8~13V

MM1225 2 1 No Yes 4.7~13V

MM1226 2 1 Yes Yes 4.7~13V

MM1227 3 1 No Yes 4.7~13V

MM1228 3 1 Yes Yes 4.7~13V

Power supply voltage range

MM1221~MM1228 Input/Output Voltage Measurement Values (typ.)

Model name

MM1221

MM1222

Power supply

5V 9V 12V Unit

voltage

Input voltage 4.53 6.05 V

Output voltage 4.5 6.1 V

Input voltage 4.05 5.4 V

Output voltage 5.34 7.12 V

MM1223

MM1224

MM1225

MM1226

MM1227

MM1228

Input voltage 4.53 6.05 V

Output voltage 4.5 6.1 V

Input voltage 4.05 5.4 V

Output voltage 5.34 7.12 V

Input voltage 1.27 2.17 2.86 V

Output voltage 1.31 2.25 2.96 V

Input voltage 1.3 2.2 2.9 V

Output voltage 1.4 2.23 2.88 V

Input voltage 1.27 2.17 2.86 V

Output voltage 1.31 2.25 2.96 V

Input voltage 1.3 2.2 2.9 V

Output voltage 1.4 2.23 2.88 V

19

MITSUMI

2-Input 1-Output Video Switch (75Ω driver)/3-Input 1-Output Video Switch (75Ω driver) MM1221~1228

Block Diagram

Control input truth table

SW OUT

(MM1221~MM1228)

LIN1

HIN2

Control input truth table

SW OUT

LIN1

HIN2

Control input truth table Control input truth table

SW1 SW2 OUT

LLIN1

HLIN2

L/H H IN3

22

SW1 SW2 OUT

LLIN1

HLIN2

L/H H IN3

20

Loading...

Loading...