Page 1

A

4 4

B

C

D

E

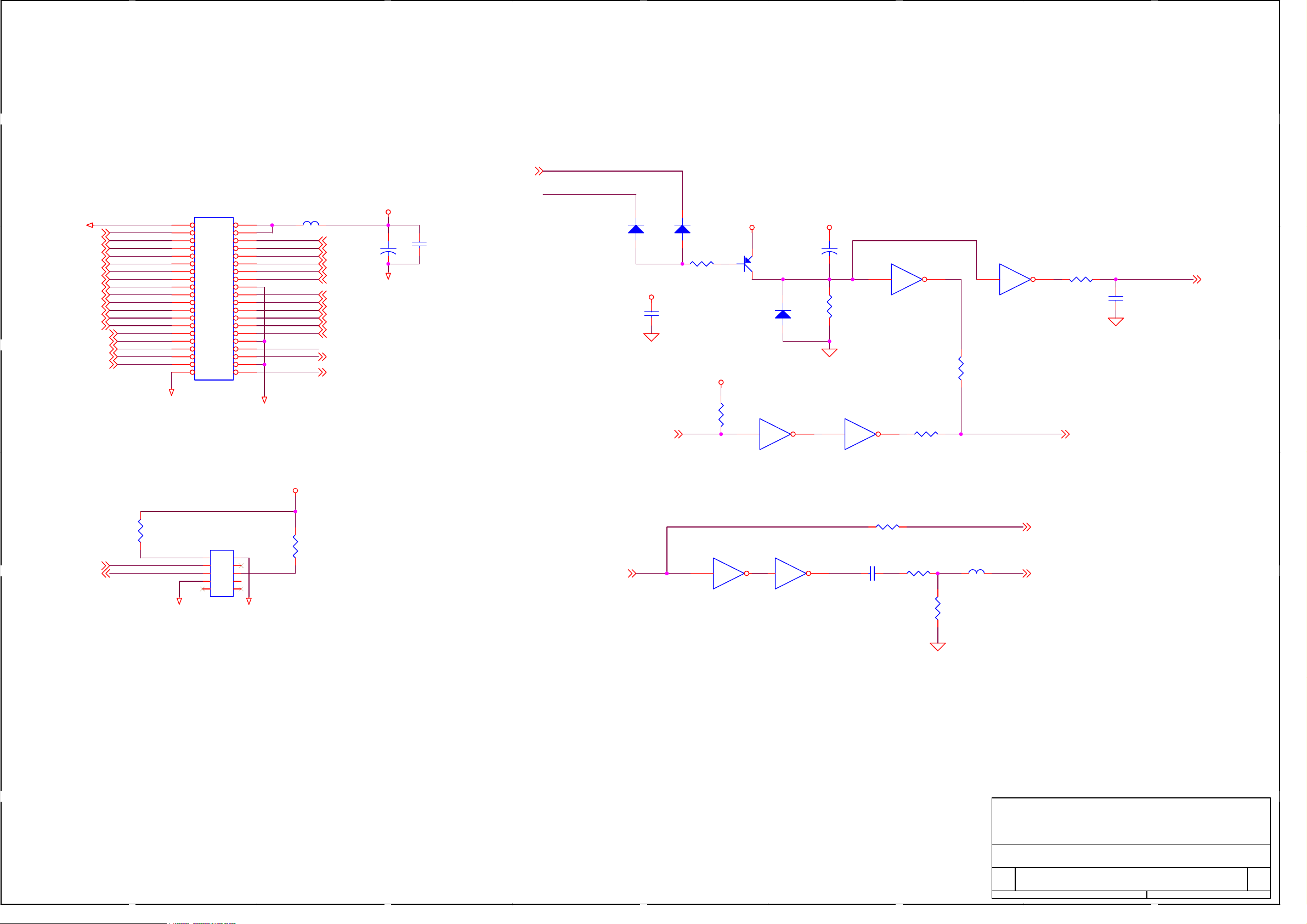

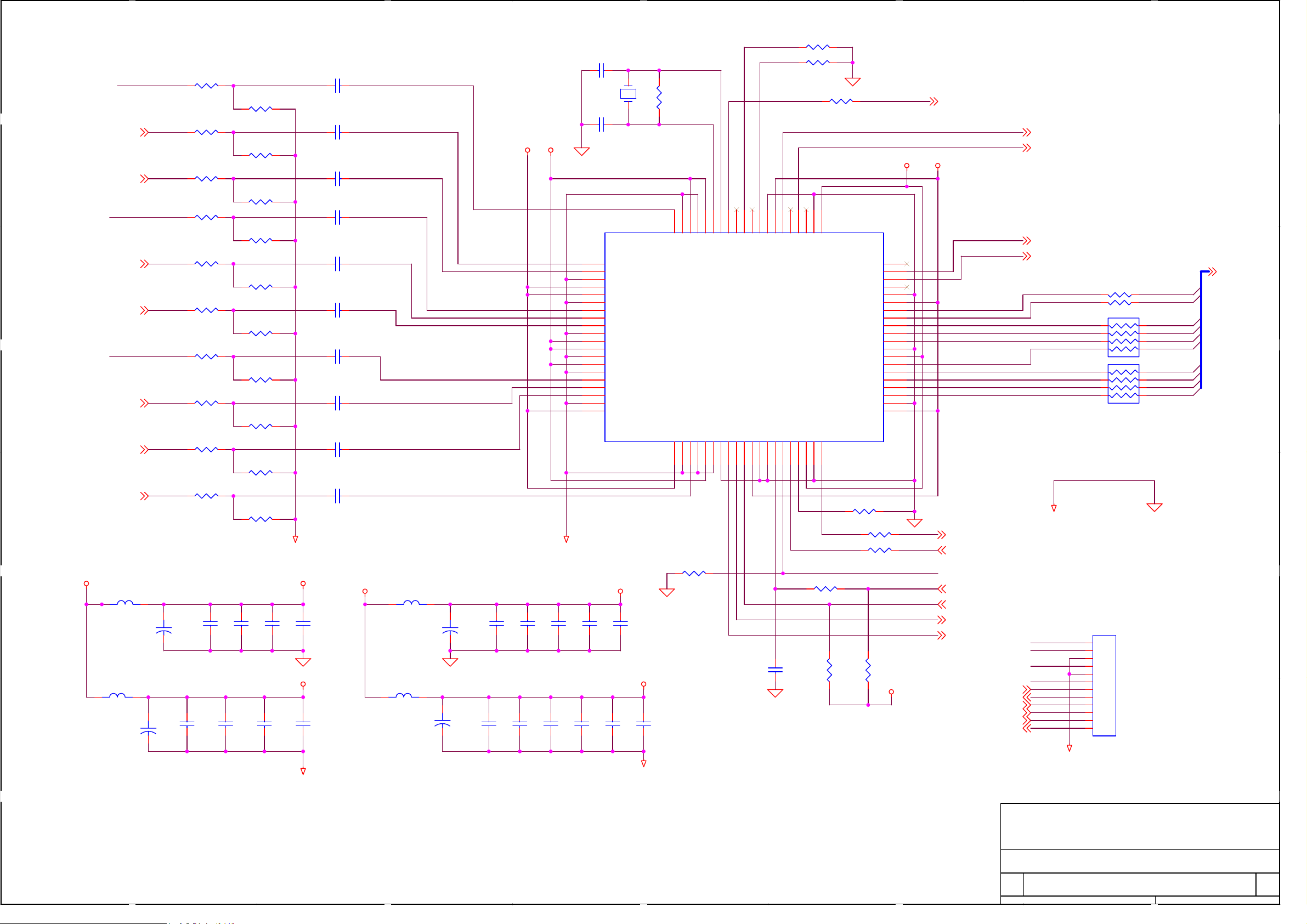

FIGARO - 2

DMN8602MK Main Codec Board (DDR SDRAM)

BBK AV ELECTRONICS CORP.,LTD.

REVISION HISTORY

VER REV DATE DESCRIPTION

Initial Draft08/20/2003A0

1: Correct net name E5_SDRAM_DQ0(U27_M18) and E5_SDRAM_DQ1(U27_M19).09/27/2003A1

2: Change net I2C_SCL to IDC_SCL.

3 3

10/26/20031A BBK MODIFY BY FENGHONGJUN

SCHEMATICS CONTENTS

TITLE

FIGARO-2 COVER PAGE

E5.1

TERM AT E5 & DDR & VREF/VTT

2 (8M x 16) DDR SDRAM

RST, IR, AV IO/ELink-3 Connector, UART

FLASH, ATA, EEPROM, IR

1394 PHY & USB

2 2

POWER CONN

VIDEO IN

VIDEO OUT DRIVER

PAGE DESCRIPTION

1

2

3

4

5

6

7

8

9

10

1 1

LSI Logic Corporation

560 Cottonwood Drive

Milpitas, CA 95035

U.S.A.

Title

FIGARO-2 COVER PAGE

Size Document Number Rev

<Doc> A1

C

112Thursday, September 15, 2005

Date: Sheet

A

B

C

D

E

of

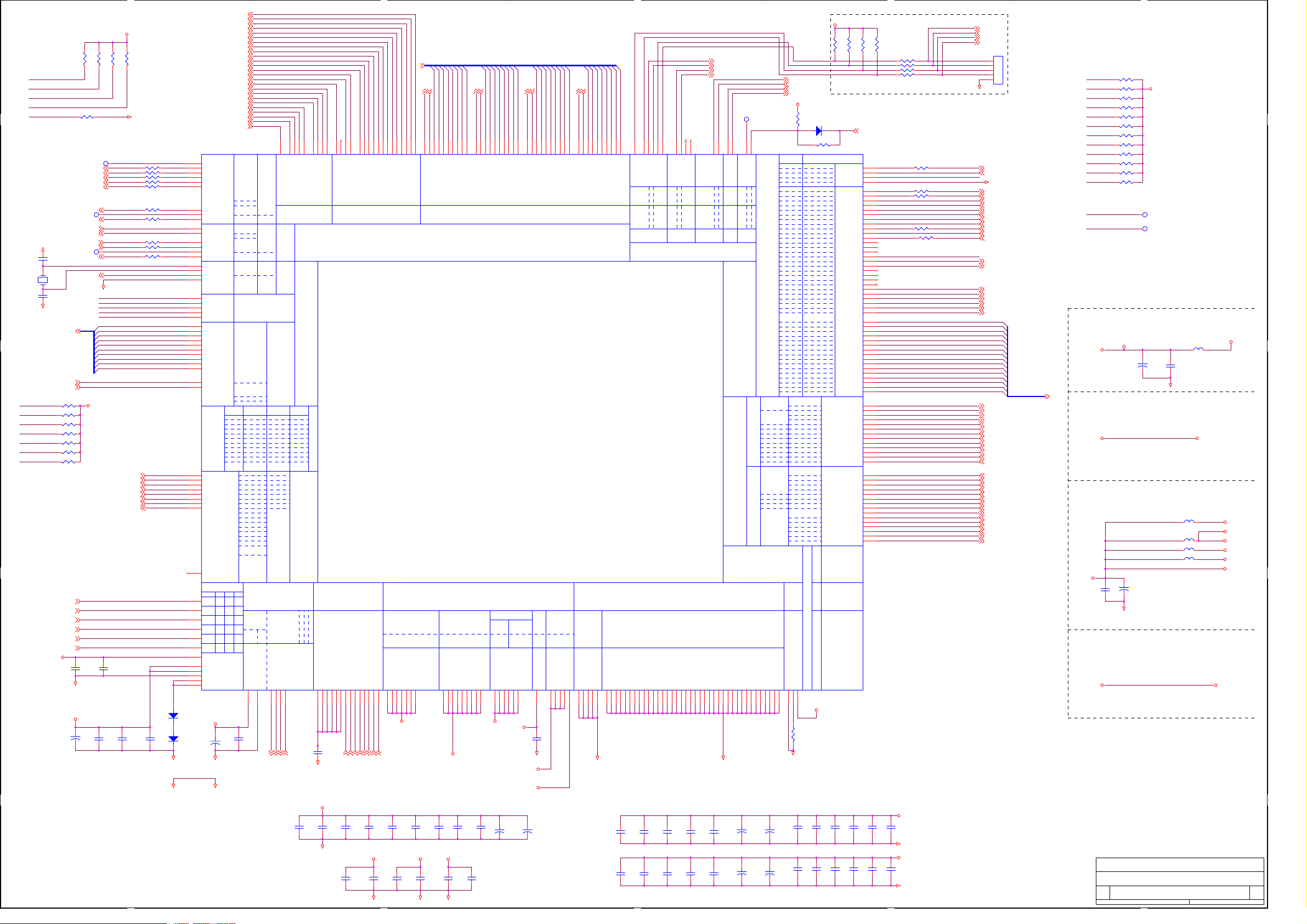

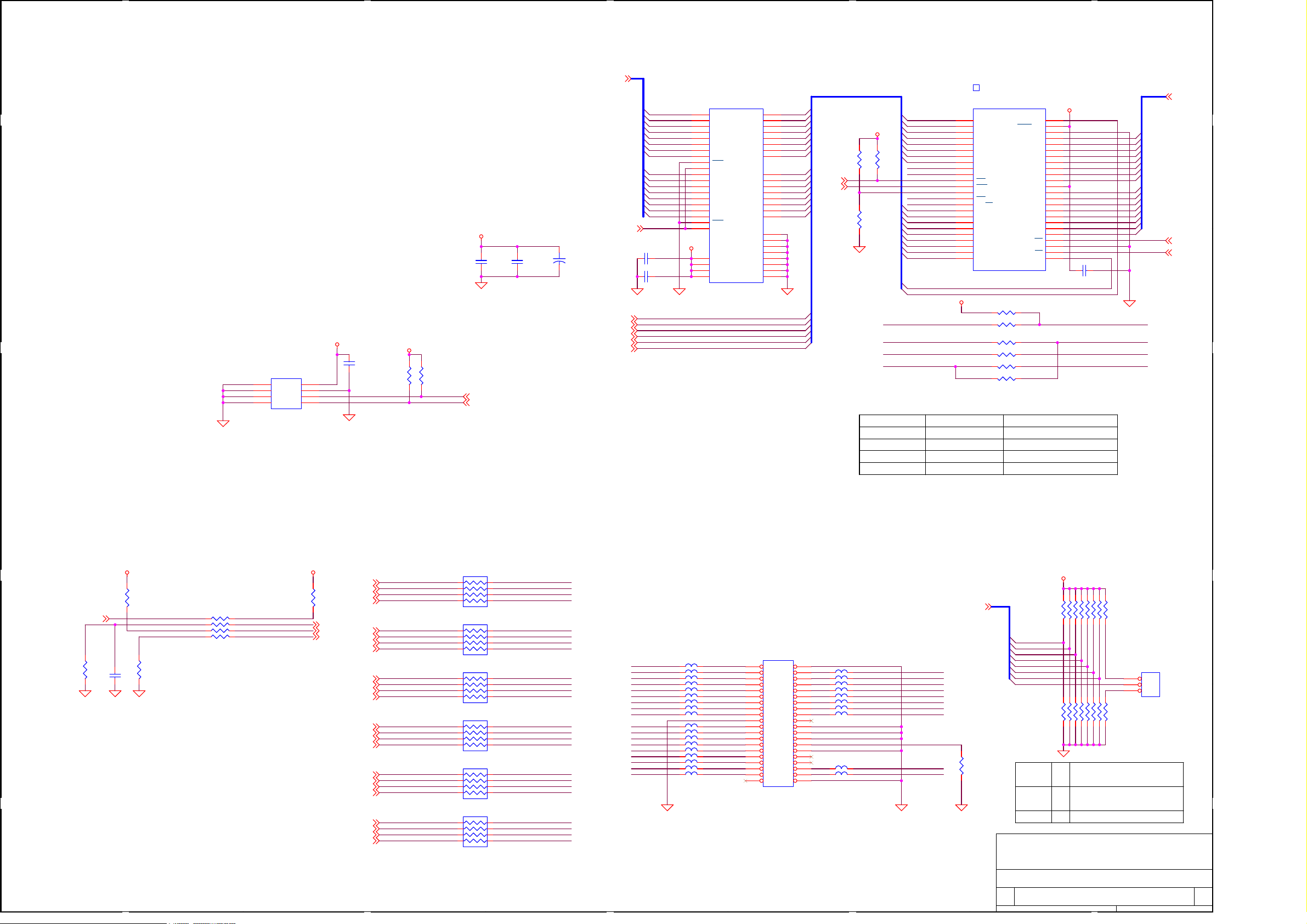

Page 2

A

V33

R1

R11 10K

AO_SCLK11

AO_FSYNC11

AO_IEC9585

AO_MCLKO11

RDS_DATA7

AI_SCLK11

AI_FSYNC11

AI_MCLKO11

E5_GPIOx355,9

10K

AO_D111

AO_D211

AO_D311

AI_D011

TMS

TDI

TDO

TCK

C1

27P

13.5MHZ

C2

27P

TRST_L

GND

Y1

GND

VI_D[9..0]9

4 4

3 3

VI_VSYNC9

VI_CLK09

E5_GPIOx2

E5_GPIOx1

E5_GPIOx3

E5_GPIOx4

E5_GPIOx5

E5_GPIOx6

E5_GPIOx7

R36 10K

R37 10K

R38 10K

R39 10K

R40 10K

R41 10K

R42 10K

V33

(BIO_PHY_PD)

(VI_AVID)

(MIC_DET)

(MUTE)

(INT_VI)

(/RST_VI)

R2

10K

TP1

1

TP2

1

(Reset_Audio)

GND

VI_VSYNC

VI_CLK0

R4

R3

10K

10K

AO_D0

1

E5_GPIOx33

(Input Only)

E5_GPIOx32

CLKI

CLKX

TCK

TDI

TDO

TMS

TRST_L

VI_D0

VI_D1

VI_D2

VI_D3

VI_D4

VI_D5

VI_D6

VI_D7

VI_D8

VI_D9

E5_GPIOx07

E5_GPIOx112

E5_GPIOx212

E5_GPIOx39

E5_GPIOx412

E5_GPIOx511

E5_GPIOx69

E5_GPIOx79

GND

R19 22

R21 22

R23 22

R24 22

R26 22

R29 22

R30 22

R33 22

R34 22

R35 22

E5_GPIOx35

(SCART_GPIO)

(SCART_GPIO)

(SCART_GPIO)

E5_GPIO6

E5_GPIOx0

E5_GPIOx1

E5_GPIOx2

E5_GPIOx3

E5_GPIOx4

E5_GPIOx5

E5_GPIOx6

E5_GPIOx7

AO_1

AO_2

AO_3

AOSCLK

AOFSYNC

AOIEC

AOMCLKO

AISCLK

AIFSYNC

AIMCLKO

2 2

CVBS10

Y10

C10

Y/G10

Pb/B10

Pr/R10

V18_E5_DAC_DVDD

GND

V33_E5_DAC_AVDD

+

CA2

T47u/16

C6

C7

104

103

12

D2

IN4148

12

D3

C10

C9

C8

104

104

IN4148

103

VO_GND

VO_GND GND

1 1

A17

B15

B16

B17

B14

A14

B13

A13

A15

C14

D14

A12

D13

C13

A16

E1

F1

H1

G1

B7

A7

C6

B6

D6

B10

C10

B11

C11

D11

D10

B12

C12

D12

A11

A10

A9

D7

C7

D8

C8

B8

D9

C9

B9

A8

A1

A2

A3

A4

A5

A6

D5

B2

B3

C5

B4

B5

E5_SDRAM_A03

E5_SDRAM_A13

E5_SDRAM_A23

E5_SDRAM_A33

E5_SDRAM_A43

E5_SDRAM_A53

E5_SDRAM_A63

E5_SDRAM_A73

E5_SDRAM_A83

E5_SDRAM_A93

E5_SDRAM_A103

E5_SDRAM_A113

E5_SDRAM_A123

E5_SDRAM_A143

E5_SDRAM_A153

E5_SDRAM_CS03

E5_SDRAM_CAS#3

E5_SDRAM_RAS#3

E5_SDRAM_CLKE3

E5_SDRAM_WE#3

E5_SDRAM_CLK03

E5_SDRAM_CLK#03

E5_SDRAM_CLK13

E5_SDRAM_CLK#13

AO_D0

AO_D1

AO_D2

AO_D3

AO_SCLK

AO_FSYNC

AO_IEC958

AO_MCLKI

AO_MCLKO

AI_D0

AI_D1

AI_SCLK

AI_FSYNC

AI_MCLKI

AI_MCLKO

3.3v only

CLKI

CLKX

CLKO

BYPASS_PLL

TCK

TDI

TDO

TMS

TRST_L

VI_D0

VI_D1

VI_D2

VI_D3

VI_D4

VI_D5

VI_D6

VI_D7

VI_D8

VI_D9

VI_VSYNC0

VI_CLK0

VO_D0

VO_D1

VO_D2

VO_D3

VO_D4

VO_D5

VO_D6

VO_D7

VO_CLK

VDENC

012

SEL

DAC1

CPST Y -

DAC2

Y CPST -

DAC3

C CPST -

DAC4

G/Y Y -

DAC5

B/Pb C CPST

DAC6

R/Pr C CPST

DAC_Dvdd (1.8v)

DAC_Vdd0(3.3v)

DAC_Vdd1(3.3v)

DAC_Dvss

DAC1bar

DAC0bar

V33_E5_USB

+

C11

GND

10UF/1206

VREF3,4

GPIO[6]

GPIO[7]

AOUT

CS[9]-

CS[8]-

DACO

GPIOx[31]

GPIOx[34]

GPIOx[33]

GPIOx[32]

GPIOx[35]

JTAG

PEC

GPIOx[45]

GPIOx[29]

2nd 24-bit

VI_D0

VI_D1

VI_D2

VI_D3

VI_D4

VI_D5

VI_D6

VI_D7

VI_D8

VI_D9

voutvin

VO_D16

VO_D17

VO_D18

VO_D19

VO_D20

VO_D21

VO_D22

VO_D23

GPIOx[0]

GPIOx[1]

GPIOx[2]

GPIOx[3]

GPIOx[4]

GPIOx[5]

GPIOx[6]

GPIOx[7]

GPIOx[8]

GPIOx[9]

GPIOx[10]

GPIOx[11]

GPIOx[12]

GPIOx[13]

GPIOx[14]

GPIOx[15]

GPIOx[30]

20-bit

vin

VI_D10

VI_D11

VI_D12

VI_D13

VI_D14

VI_D15

VI_D16

VI_D17

VI_D18

VI_D19

3.3V ONLY

USB 1394

POWER

3.3V

GND

Dplus_0

USB_Avdd0(3.3v)

USB_VSS0

G3G4H2

F3

F4

C12

104

USB_D0-

USB_D0+

VREF

D16

SDRAM_VREF

Dminus_0

Host_PO_0

USB_PO0

VIN

H3

USB_OC0

L20

K20

E20

D20

SDRAM_CLK1

SDRAM_CLK_L0

SDRAM_CLK_L1

AIN

SYSTEM

2nd

vout

VO_D0

VO_D1

VO_D2

VO_D3

VO_D4

VO_D5

VO_D6

VO_D7

VOUT

GPIOx[43]

GPIOx[44]

Host_OC_0

7

7

7

C14

102

N18

N19

SDRAM_CLK0

SDRAM_WE_L

VIO

GPIOx[36]

7

GND

SSTL2_VDD

GND

SDRAM_CKE

BIO_PHY_DATA7

N17

C?

101

P20

SDRAM_CAS_L

SDRAM_RAS_L

BIO_PHY_DATA5

BIO_PHY_DATA6

C15

102

E5_SDRAM_CS1

E5_SDRAM_A15

R20

P19

P18

SDRAM__A17

SDRAM__A16

SDRAM__A15

BIO_PHY_DATA1

BIO_PHY_DATA2

BIO_PHY_DATA3

BIO_PHY_DATA4

L2L4L3J1K4K3K2

BIO_PHY_DATA1

A

B

E5_SDRAM_A9

E5_SDRAM_A7

E5_SDRAM_A6

E5_SDRAM_A5

E5_SDRAM_A4

E5_SDRAM_A2

E5_SDRAM_A14

Y20

SDRAM__A14

E5_SDRAM_A12

U20

*SDRAM__A13

E5_SDRAM_A11

V19

SDRAM__A12

E5_SDRAM_A10

U18

SDRAM__A11

W20

SDRAM__A10

E5_SDRAM_A8

U19

SDRAM__A8

SDRAM__A9

E5_SDRAM_A0

E5_SDRAM_A3

E5_SDRAM_A1

R17

T19

P17

R19

R18

T18

T20

V20

SDRAM__A0

SDRAM__A1

SDRAM__A2

SDRAM__A3

SDRAM__A4

SDRAM__A5

SDRAM__A6

SDRAM__A7

SDRAM I/F

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

PADS CORE

3.3V 1.8V 3.3V

BIO_PHY_DATA0

BIO_PHY_CTL0

BIO_PHY_CTL1

BIO_LREQ

BIO_LPS

BIO_LINK_ON

BIO_PHY_CLK

VDD_PAD1

VDD_PAD2

VDD_PAD3

VDD_PAD4

VDD_PAD5

VDD_PAD6

7

J5K5E11

E5_VPAD

7

7

7

7

7

C18

104

C53

103

E12

T12

7

E5_AVDD

VDD_PAD7

T11

7

C19

104

J2

J3K1N1M1J4L1H4

BIO_LPS

BIO_LREQ

BIO_PHY_CLK

BIO_LINK_ON

BIO_PHY_CTL1

BIO_PHY_CTL0

BIO_PHY_DATA0

C16

C17

102

104

E5_VDDREF E5_VDDX

C51

C52

103

104

GND GND GND

B

E5_SDRAM_DQ[31..0] 3

3

3

E5_SDRAM_DQS3

E5_SDRAM_DQ29

E5_SDRAM_DQ31

E5_SDRAM_DQ30

E5_SDRAM_DQM3

C19

B19

C20

C18

D18

SDRAM_DQ29

SDRAM_DQ30

SDRAM_DQ31

SDRAM_DQS3

SDRAM_DQM3

E5_SDRAM_DQS2

E5_SDRAM_DQ25

E5_SDRAM_DQ26

E5_SDRAM_DQ23

E5_SDRAM_DQ27

E5_SDRAM_DQ28

E5_SDRAM_DQ24

E5_SDRAM_DQM2

E17

A18

B18

A20

A19

B20

F19

F20

SDRAM_DQ24

SDRAM_DQ25

SDRAM_DQ27

SDRAM_DQ26

SDRAM_DQ28

SDRAM_DQS2

SDRAM_DQM2

3

3

E5_SDRAM_DQS1

E5_SDRAM_DQ20

E5_SDRAM_DQ21

E5_SDRAM_DQ22

F17

E19

E18

SDRAM_DQ20

SDRAM_DQ21

SDRAM_DQ22

SDRAM_DQ23

E5_SDRAM_DQ15

E5_SDRAM_DQ18

E5_SDRAM_DQ19

E5_SDRAM_DQ17

E5_SDRAM_DQ16

E5_SDRAM_DQM1

G20

G19

G18

G17

F18

J20

H20

SDRAM_DQ16

SDRAM_DQ17

SDRAM_DQ18

SDRAM_DQ19

SDRAM_DQS1

SDRAM_DQM1

3

3

E5_SDRAM_DQ8

E5_SDRAM_DQ9

E5_SDRAM_DQS0

E5_SDRAM_DQ12

E5_SDRAM_DQ14

E5_SDRAM_DQ11

E5_SDRAM_DQ10

E5_SDRAM_DQ13

E5_SDRAM_DQM0

J19

J18

H17

H19

H18

J17

K17

M20

K19

SDRAM_DQ9

SDRAM_DQ8

SDRAM_DQ15

SDRAM_DQ12

SDRAM_DQ14

SDRAM_DQ10

SDRAM_DQ13

SDRAM_DQ11

SDRAM_DQM0

3

E5_SDRAM_DQ0

E5_SDRAM_DQ3

E5_SDRAM_DQ6

E5_SDRAM_DQ2

E5_SDRAM_DQ7

E5_SDRAM_DQ1

E5_SDRAM_DQ4

E5_SDRAM_DQ5

N20

M19

M18

M17

L19

L18

L17

K18

SDRAM_DQ2

SDRAM_DQ1

SDRAM_DQ3

SDRAM_DQ4

SDRAM_DQ5

SDRAM_DQ6

SDRAM_DQ7

SDRAM_DQS0

DATAADDRCONTROL

E5.1-BGA-308-A

U1

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

TOP VIEW

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

POWER GND

SDRAM

SDR

3.3V

DDR

2.5V 5V

VDD_CORE8

VDD_CORE2

VDD_CORE3

C55

104

VDD_CORE4

VDD_CORE5

T10E9E10

C21

104

VDD_CORE6

D19

VDD_CORE7

T17

V17

SSTL2_VDD

C56

102

VDD_CORE9

VDD_25V1

VDD_25V2

VDD_25V3

VDD_25V4

VDD_25V5

C16

D17

J16

K16

L16

E5_V5BIAS

E5_AVDD

E5_VDDX

C22

C23

+

104

T47u/16

VDD_CORE1

L5M5T9

E5_VCORE

C20

104

C54

103

M16

104

C13

VDD_25V6

5V_BIAS0

D15

GND

+

C24

10UF/1206

BIAS

PLL PLL

AVDD1

AVDD2

AVDD0

AVDD3

VDDX

AGND1

C4E4D3D2E2C3D4E3D1

AGND2

AGND0

AGND3

GNDX

VSS_PC2_CTR1

VSS_PC2_CTR2

VSS_PC2_CTR3

C15

C17H8H9

F2

3

SDRAM_DQ0

VSS_PC2_CTR4

VSS_PC2_CTR5

H10

C33

102

C46

102

C

Y15

SPI_CLK

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

VSS_PC2_CTR6

VSS_PC2_CTR7

VSS_PC2_CTR8

H11

H12

H13J8J9

C

E5_GPIOx25

E5_GPIOx24

W17

W18

W16

V16

Y16

SPI_CS0

SPI_CS1

SPI_CS2

SPI_MOSI

SPI_MISO

CS10-

CS11-GPIOx[25]

GPIOx[24]

DIGITAL

VSS_PC2_CTR9

VSS_PC2_CTR10

VSS_PC2_CTR11

VSS_PC2_CTR12

VSS_PC2_CTR13

VSS_PC2_CTR14

J10

J11

J12

J13K8K9

C35

C34

102

102

C47

C48

102

102

E5_GPIOx42

E5_GPIOx41

U17

U15

W19

UART1_CTS

UART1_RTS

GPIOx[42]

GPIOx[41]

SIO

VSS_PC2_CTR15

VSS_PC2_CTR16

VSS_PC2_CTR17

K10

K11

D

R235

10K

OPEN FOR DW9916

DI 9

DO 9

CL 9

R236

10K

R237 22

R238 22

R239 22

R240 22

/DTACK

R20 22

MCONFIG

R27 22

R28 22

E5_GPIO0

E5_GPIO1

E5_GPIO2

E5_GPIO3

E5_GPIO4

E5_GPIO5

R31 22

R32 22

/WAIT

/E5_CS2

Y8

W15

G2

Y11

Y9

V14

V6

V12

W9

V8

W8

U10

Y7

U8

U9

W3

Y2

Y6

Y4

Y5

Y3

V4

V5

W4

U5

W5

U6

W7

W6

U7

V7

V10

W11

Y10

V9

V11

Y12

W10

W12

Y13

U11

V13

W13

Y14

U12

U13

W14

V3

T4

V1

U2

U4

W2

U1

R4

R1

P3

P1

N2

M2

M3

M4

N3

N4

P2

P4

R3

T1

Y1

T2

W1

T3

V2

U3

R2

CE 9

CN8

5P1.0

DI

1

DO

2

CL

3

CE

4

5

GND

E5_ALE 5,6

/SYS_RST 5,6

GND

/E5_OE 5,6

/E5_UDS 5

E5_GPIO0 12

E5_GPIO1 7

E5_GPIO2 5

E5_GPIO3 11

E5_GPIO4 12

E5_GPIO5 12

/E5_WEL 5,6

/WAIT 5

E5_/DTACK 5

/E5_CS1 5

/E5_CS0 6

E5_MA22 6

E5_MA5 5,6

E5_MA4 5,6

E5_MA3 5,6

E5_MA2 5,6

E5_MA1 5,6

HD15

HD14

HD13

HD12

HD11

HD10

HD9

HD8

HD7

HD6

HD5

HD4

HD3

HD2

HD1

HD0

AtapiAddr0 6

AtapiAddr1 6

AtapiAddr2 6

AtapiAddr3 6

AtapiAddr4 6

ATAPI_DATA15 6

ATAPI_DATA14 6

ATAPI_DATA13 6

ATAPI_DATA12 6

ATAPI_DATA11 6

ATAPI_DATA10 6

ATAPI_DATA9 6

ATAPI_DATA8 6

ATAPI_DATA7 6

ATAPI_DATA6 6

ATAPI_DATA5 6

ATAPI_DATA4 6

ATAPI_DATA3 6

ATAPI_DATA2 6

ATAPI_DATA1 6

ATAPI_DATA0 6

ATAPI_RESET 6

ATAPI_DMAACK_L 6

ATAPI_DMARQ 6

ATAPI_IORDY 6

ATAPI_INTRQ 6

ATAPI_DIOR_L 6

ATAPI_DIOW_L 6

(FP D_HOST)

(/RST_PHY)

(/ETHER_IRQ)

(RST_CS4360)

(AUDIO_SEL0)

(AUDIO_SEL1)

HD[15..0]5,6

/DTACK

MCONFIG

/E5_CS0

/E5_CS1

/E5_CS2

E5_GPIO0

E5_GPIO1

E5_GPIO2

E5_GPIO3

E5_GPIO4

E5_GPIO5

/WAIT

E5_UART2_TX

E5_UART2_RX

1.8V

V18

2.5V

V25

3.3V

V33

5V

VCC

VCC

R234

R233

10K

10K

E5_GPIOx25 12

E5_GPIOx24 12

E5_GPIOx41 12

E5_GPIOx42 12

U16

V18

Y19

UART2_TX

UART1_TX

UART2_RX

UART1_RX

GPIOx[38]

GPIOx[37]

(RDY_FM)

(ATN_FM)

(FP SCLK)

(FP D_FM)

IRTX1

1

V15

Y18

Y17

U14

IRRX

IRTX1

IDC_CLK

IDC_DAT

CS7-

CS6-

GPIOx[39]

GPIOx[40]

IDCUART1 UART2SPI IR

GPIOx[23]

GPIOx[22]

GPIOx[21]

GPIOx[20]

GPIOx[19]

GPIOx[18]

GPIOx[17]

GPIOx[16]

CD_C2PO

CD_BCK

CD_LRCK

ATAPI I/F

CD_DATA

SD/CD SBP

SPI_MOSI

SPI_MISO

SPI_SCK

SPI_CS2

E5_UART2_TX 5

E5_UART2_RX 5

SDA 6,7,9,11,12

SCL 6,7,9,11,12

E5_VDDX

R6

D1

*10K

*1N6263

1 2

R10 *0

RSTMCONFIG

CS-

RD-

LDS-

DMAREQ

UDSHINTA0

A1

A2

PCMCIA_IOW-

PCMCIA_IORRD

WRWAITDTACKD31

D30

D29

D28

D27

D26

D25

D24

D23

D22

D21

D20

D19

D18

HOST I/F

D17

D16

D15

MA[21]

D14

MA[20]

D13

MA[19]

D12

MA[18]

D11

MA[17]

D10

MA[16]

D9

MA[15]

D8

MA[14]

D7

MA[13]

D6

MA[12]

D5

MA[11]

D4

MA[10]

D3

MA[9]

D2

MA[8]

D1

MA[7]

D0

MA[6]

SBP_FRAME

SBP_ACK

SBP_RD

SBP_REQ

SBP_CLK

SBP_D[7]

SBP_D[6]

SBP_D[5]

SBP_D[4]

SBP_D[3]

SBP_D[2]

SBP_D[1]

SBP_D[0]

SD_D[7]

SD_D[6]

SD_D[5]

SD_D[4]

SD_D[3]

SD_D[2]

SD_D[1]

SD_D[0]

SD_SECSTART

SD_ERROR

SD_CLK

SD_ACK

SD_RDREQ

SD_WRREQ

MASTERSLAVE

MCONFIG

CS0_8BIT

AtapiAddr0

AtapiAddr1

AtapiAddr2

AtapiAddr3

AtapiAddr4

ATAPI_DATA15

ATAPI_DATA14

ATAPI_DATA13

ATAPI_DATA12

ATAPI_DATA11

ATAPI_DATA10

ATAPI_DATA9

ATAPI_DATA8

ATAPI_DATA7

ATAPI_DATA6

ATAPI_DATA5

ATAPI_DATA4

ATAPI_DATA3

ATAPI_DATA2

ATAPI_DATA1

ATAPI_DATA0

ATAPI_RESET_L

ATAPI_DMAACK_L

ATAPI_DMARQ

ATAPI_IORDY

ATAPI_INTRQ

ATAPI_DIOR_L

ATAPI_DIOW_L

RST-

UWEGPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

LWE-

WAIT-

DTACK-

CS5CS4CS3CS2CS1-

CS0MA[26]

MS[25]

MA[24]

MA[23]

MA[22]

MA[5]

MA[4]

MA[3]

MA[2]

MA[1]

ALE

OE-

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

IR_FMUTE 11,12

CONTROL

VREF

ADDRDATA

ATAPI2 I/F

VDD_REF

R_REF

VSS_REF

VSS_PC2_CTR37

VSS_PC2_CTR18

VSS_PC2_CTR19

VSS_PC2_CTR20

VSS_PC2_CTR21

VSS_PC2_CTR22

VSS_PC2_CTR23

VSS_PC2_CTR24

VSS_PC2_CTR25

VSS_PC2_CTR26

VSS_PC2_CTR27

VSS_PC2_CTR28

VSS_PC2_CTR29

K12

K13L8L9

L10

VSS_PC2_CTR30

L11

L12

L13M8M9

M10

M11

M12

GNDGND

VSS_PC2_CTR31

VSS_PC2_CTR32

M13N8N9

VSS_PC2_CTR38

VSS_PC2_CTR33

VSS_PC2_CTR34

VSS_PC2_CTR35

VSS_PC2_CTR36

N12

N13

N10

N11

C2C1B1

E5_VDDREF

R43

1.18K 1%

GND

R5 10K

R7 10K

R8 10K

R9 10K

R12 10K

R13 10K

R14 10K

R15 10K

R16 *10K

R18 10K

R22 10K

R25 10K

E5_VCORE

C5

104

GND

+

T47u/16

E

V33

TX1

1

RX1

1

V18_E5_DAC_DVDD

FB1

C3

104

GND

L1 601

L2 601

L3 601

L4 601

601

SSTL2_VDD

V33_E5_USB

E5_VDDX

E5_AVDD

E5_VDDREF

V33_E5_DAC_AVDD

E5_VPAD

E5_V5BIAS

CA1

+

T47u/16

C4

General decoupling cap placement:

Caps with smaller capacitance values to be

closer to respective power pins compared to

those of larger values. All should be as

close as possible.

C28

C29

C26

C25

+

C37

C36

103

103

C49

103

10UF/1206

C38

+

C50

104

10UF/1206

+

10UF/1206

C39

+

10UF/1206

C27

104

104

C40

C41

104

104

C30

104

104

C42

C43

104

104

E5_VPAD

C31

C32

104

104

GND

E5_VCORE

C44

C45

104

104

GND

D

BBK AV ELECTRONICS CORP.,LTD.

Title

E5.1

Size Document Number Rev

Date: Sheet of

HDW-10-310000-1 A1

2

12Thursday, September 15, 2005

E

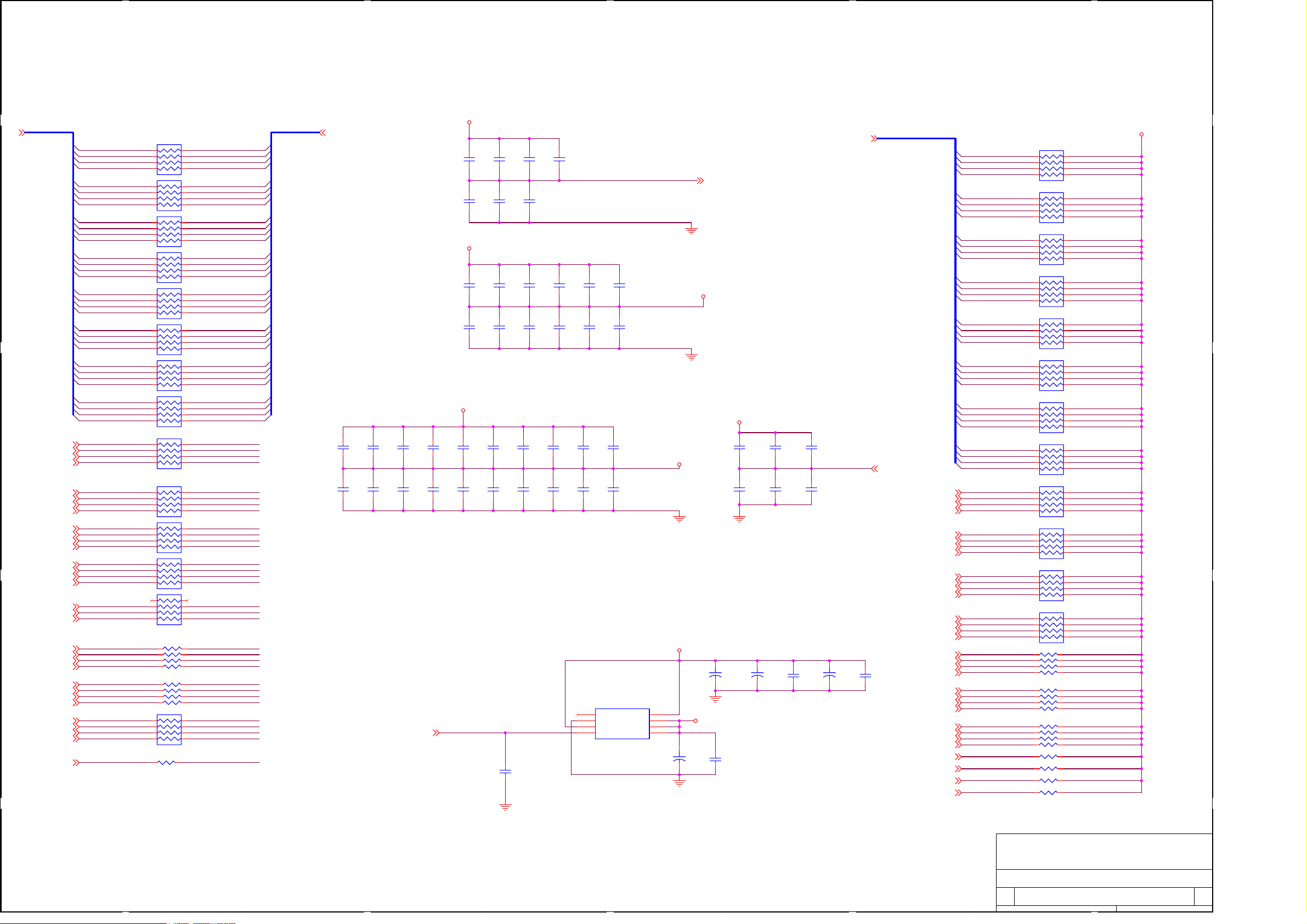

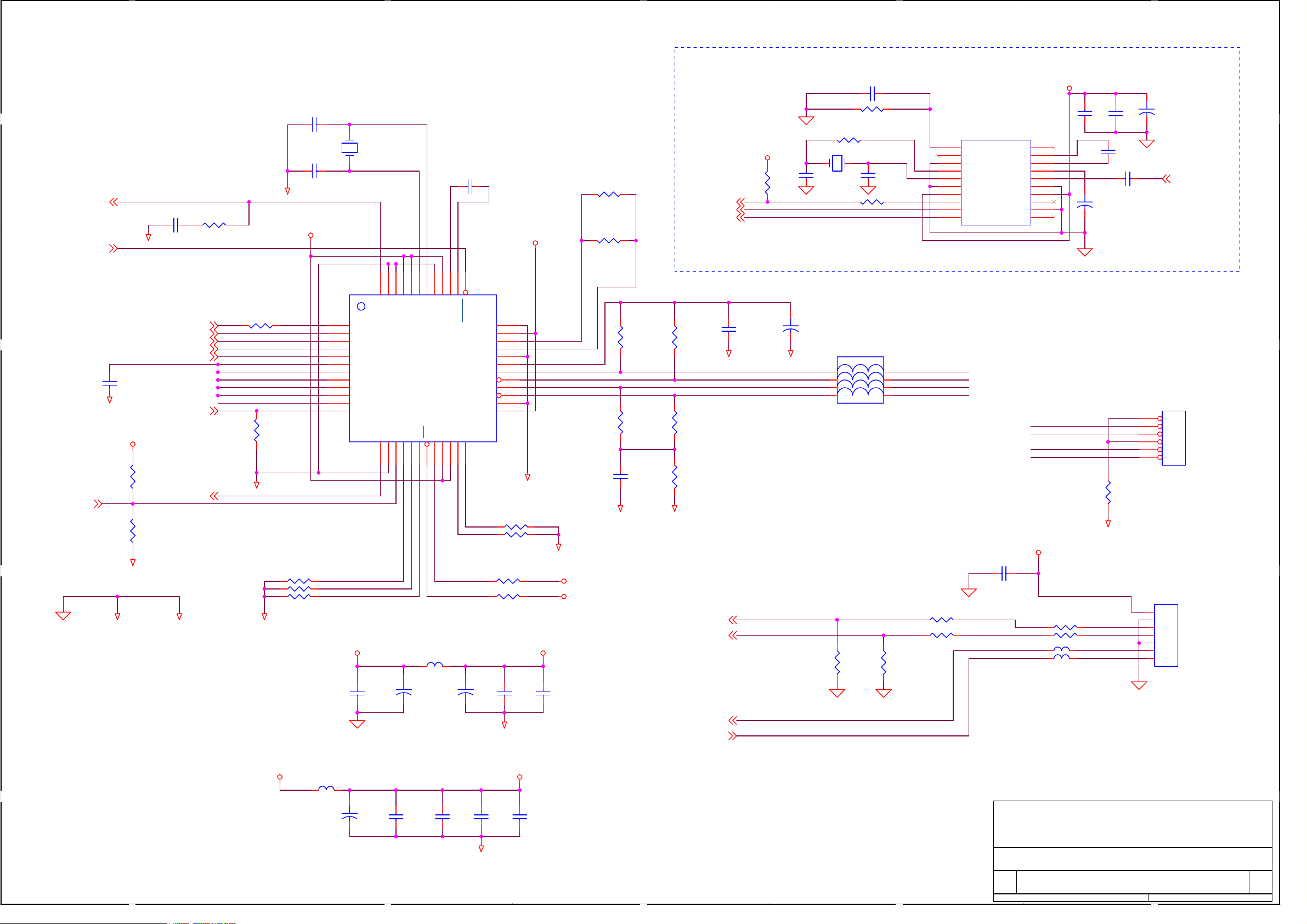

Page 3

A

B

C

D

E

TERMINATION

AT E5.1

C79

103

C92

103

SSTL2_VDD

C57

104

C61

104

SSTL2_VDD

C64

104

C70

104

SSTL2_VDD

C80

104

C93

104

VREF

4 4

E5_SDRAM_DQ0

E5_SDRAM_DQ1

E5_SDRAM_DQ2

E5_SDRAM_DQ3

E5_SDRAM_DQ4

E5_SDRAM_DQ5

E5_SDRAM_DQ6

E5_SDRAM_DQ7

E5_SDRAM_DQ8

E5_SDRAM_DQ9

E5_SDRAM_DQ10

E5_SDRAM_DQ11

E5_SDRAM_DQ12

E5_SDRAM_DQ13

E5_SDRAM_DQ14

E5_SDRAM_DQ15

E5_SDRAM_DQ16

E5_SDRAM_DQ17

E5_SDRAM_DQ18

E5_SDRAM_DQ19

E5_SDRAM_DQ20

E5_SDRAM_DQ21

E5_SDRAM_DQ22

3 3

2 2

E5_SDRAM_DQ23

E5_SDRAM_DQ24

E5_SDRAM_DQ25

E5_SDRAM_DQ26

E5_SDRAM_DQ27

E5_SDRAM_DQ31

E5_SDRAM_DQ28

E5_SDRAM_DQ30

E5_SDRAM_DQ29

E5_SDRAM_DQM0 2

E5_SDRAM_DQM1 2

E5_SDRAM_DQM2 2

E5_SDRAM_DQM3 2

E5_SDRAM_A1 2

E5_SDRAM_A6 2

E5_SDRAM_A3 2

E5_SDRAM_A15 2

E5_SDRAM_A8 2

E5_SDRAM_A0 2

E5_SDRAM_A4 2

E5_SDRAM_A2 2

E5_SDRAM_A7 2

E5_SDRAM_A14 2

E5_SDRAM_A9 2

E5_SDRAM_A12 2

E5_SDRAM_A11 2

E5_SDRAM_A10 2

E5_SDRAM_A5 2

E5_SDRAM_DQS0 2

E5_SDRAM_DQS1 2

E5_SDRAM_DQS2 2

E5_SDRAM_DQS3 2

E5_SDRAM_CLK0 2

E5_SDRAM_CLK1 2

E5_SDRAM_CLK#0 2

E5_SDRAM_CLK#1 2

E5_SDRAM_RAS# 2

E5_SDRAM_CLKE 2

E5_SDRAM_CAS# 2

E5_SDRAM_WE# 2

E5_SDRAM_CS0 2

RP1 51/RP

RP3 51/RP

1 8

2 7

3 6

4 5

RP5 51/RP

RP7 51/RP

RP9 51/RP

RP11 51/RP

1 8

2 7

3 6

4 5

RP12 51/RP

RP14 51/RP

1 8

2 7

3 6

4 5

RP16 22/RP

1 8

2 7

3 6

4 5

RP18 22/RP

RP20 22/RP

1 8

2 7

3 6

4 5

RP22 22/RP

RP24 22/RP

1 8

2 7

3 6

4 5

R44 51

R45 51

R47 51

R49 51

R52 22

R53 22

R55 22

R57 22

RP26 22/RP

1 8

2 7

3 6

4 5

R65 22

SDRAM_DQ0

18

SDRAM_DQ1 SDRAM_DQ0

27

SDRAM_DQ2

36

SDRAM_DQ3

45

SDRAM_DQ4

SDRAM_DQ5

SDRAM_DQ6

SDRAM_DQ7

SDRAM_DQ8

18

SDRAM_DQ9

27

SDRAM_DQ10

36

SDRAM_DQ11

45

SDRAM_DQ12

18

SDRAM_DQ13

27

SDRAM_DQ14

36

SDRAM_DQ15

45

SDRAM_DQ16

18

SDRAM_DQ17

27

SDRAM_DQ18

36

SDRAM_DQ19

45

SDRAM_DQ20

SDRAM_DQ21

SDRAM_DQ22

SDRAM_DQ23

SDRAM_DQ24

45

SDRAM_DQ25

36

SDRAM_DQ26

27

SDRAM_DQ27

18

SDRAM_DQ31

SDRAM_DQ28

SDRAM_DQ30

SDRAM_DQ29

SDRAM_DQM0

SDRAM_DQM1

SDRAM_DQM2

SDRAM_DQM3

SDRAM_A1

18

SDRAM_A6

27

SDRAM_A3

36

SDRAM_A15

45

SDRAM_A8

SDRAM_A0

SDRAM_A4

SDRAM_A2

SDRAM_A7

18

SDRAM_A14

27

SDRAM_A9

36

SDRAM_A12

45

SDRAM_A11

SDRAM_A10

SDRAM_A5

SDRAM_DQS0

SDRAM_DQS1

SDRAM_DQS2

SDRAM_DQS3

SDRAM_CLK0

SDRAM_CLK1

SDRAM_CLK#0

SDRAM_CLK#1

SDRAM_RAS#

SDRAM_CLKE

SDRAM_CAS#

SDRAM_WE#

SDRAM_CS0

SDRAM_DQ[31..0]4E5_SDRAM_DQ[31..0] 2

C78

C77

C76

103

104

104

C91

C90

C89

103

104

104

DDR TERMINATION VOLTAGE REGULATOR

VREF needs to be decoupled

to both SSTL2_VDD and SSTL2_GND with balanced

decoupling capacitors.

VREF should be routed over a

reference plane and isolated, and possibly

shielded with both SSTL2_VDD and SSTL2_GND

VREF2,4

The VTT side of the terminaton resistors should be placed

on a wide VTT island on the surface layer. The island is

located at each end of the bus, so it does not interfere

with the signal routing.

C59

103

C63

103

C66

103

C72

103

C60

103

C67

103

C73

103

C84

C83

102

102

C97

C96

102

102

1

2

3

4 5

C68

C69

104

104

C74

C75

104

104

C85

104

C98

104

U2

NC

GND

VSENSE

VREF VDDQ

LP2995

GND_SSTL2

PVIN

AVIN

C81

104

C94

104

C58

104

C62

104

C65

104

C71

104

C82

102

C95

102

C107

104

VTT

GND_SSTL2

VTT

VREF

GND_SSTL2

VTT

GND_SSTL2

VTT

VTT

8

7

6

+

CA4

220u/16

VREF 2,4

VTT

+

SSTL2_VDD

TERMINATION

AT DDR

SDRAM_DQ[31..0]4

SSTL2_VDD

CA3

220u/16

C106

104

C86

104

C99

104

GND_SSTL2

+

C87

102

C100

102

C102

10u/16

C88

102

C101

102

C104

104

+

T47u/16

C103

VREF

VREF 2,4

C105

104

SDRAM_DQ1

SDRAM_DQ2

SDRAM_DQ3

SDRAM_DQ4

SDRAM_DQ5

SDRAM_DQ6

SDRAM_DQ7

SDRAM_DQ8

SDRAM_DQ9

SDRAM_DQ10

SDRAM_DQ11

SDRAM_DQ12

SDRAM_DQ13

SDRAM_DQ14

SDRAM_DQ15

SDRAM_DQ16

SDRAM_DQ17

SDRAM_DQ18

SDRAM_DQ19

SDRAM_DQ20

SDRAM_DQ21

SDRAM_DQ22

SDRAM_DQ23

SDRAM_DQ24

SDRAM_DQ25

SDRAM_DQ26

SDRAM_DQ27

SDRAM_DQ28

SDRAM_DQ29

SDRAM_DQ30

SDRAM_DQ31

SDRAM_A0 4

SDRAM_A1 4

SDRAM_A2 4

SDRAM_A3 4

SDRAM_A7 4

SDRAM_A6 4

SDRAM_A5 4

SDRAM_A4 4

SDRAM_A12 4

SDRAM_A11 4

SDRAM_A9 4

SDRAM_A8 4

SDRAM_RAS# 4

SDRAM_A14 4

SDRAM_A15 4

SDRAM_A10 4

SDRAM_DQS0 4

SDRAM_DQS1 4

SDRAM_DQS2 4

SDRAM_DQS3 4

SDRAM_DQM0 4

SDRAM_DQM1 4

SDRAM_DQM2 4

SDRAM_DQM3 4

SDRAM_CLK#0 4

SDRAM_CLK#1 4

SDRAM_CLK0 4

SDRAM_CLK1 4

SDRAM_CLKE 4

SDRAM_WE# 4

SDRAM_CAS# 4

SDRAM_CS0 4

RP2 51/RP

RP4 51/RP

RP6 51/RP

4 5

3 6

2 7

1 8

RP8 51/RP

4 5

3 6

2 7

1 8

RP10 51/RP

RP13 51/RP

RP15 51/RP

RP17 51/RP

RP19 51/RP

RP21 51/RP

1 8

2 7

3 6

4 5

RP23 51/RP

1 8

2 7

3 6

4 5

RP25 51/RP

R46 51

R48 51

R50 51

R51 51

R54 51

R56 51

R58 51

R59 51

R60 51

R61 51

R62 51

R63 51

R64 51

R66 51

R67 51

R68 51

VTT

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

1 1

BBK AV ELECTRONICS CORP.,LTD.

Title

TERM AT E5

Size Document Number Rev

C

A

B

C

D

Date: Sheet

E

312Thursday, September 15, 2005

of

D0

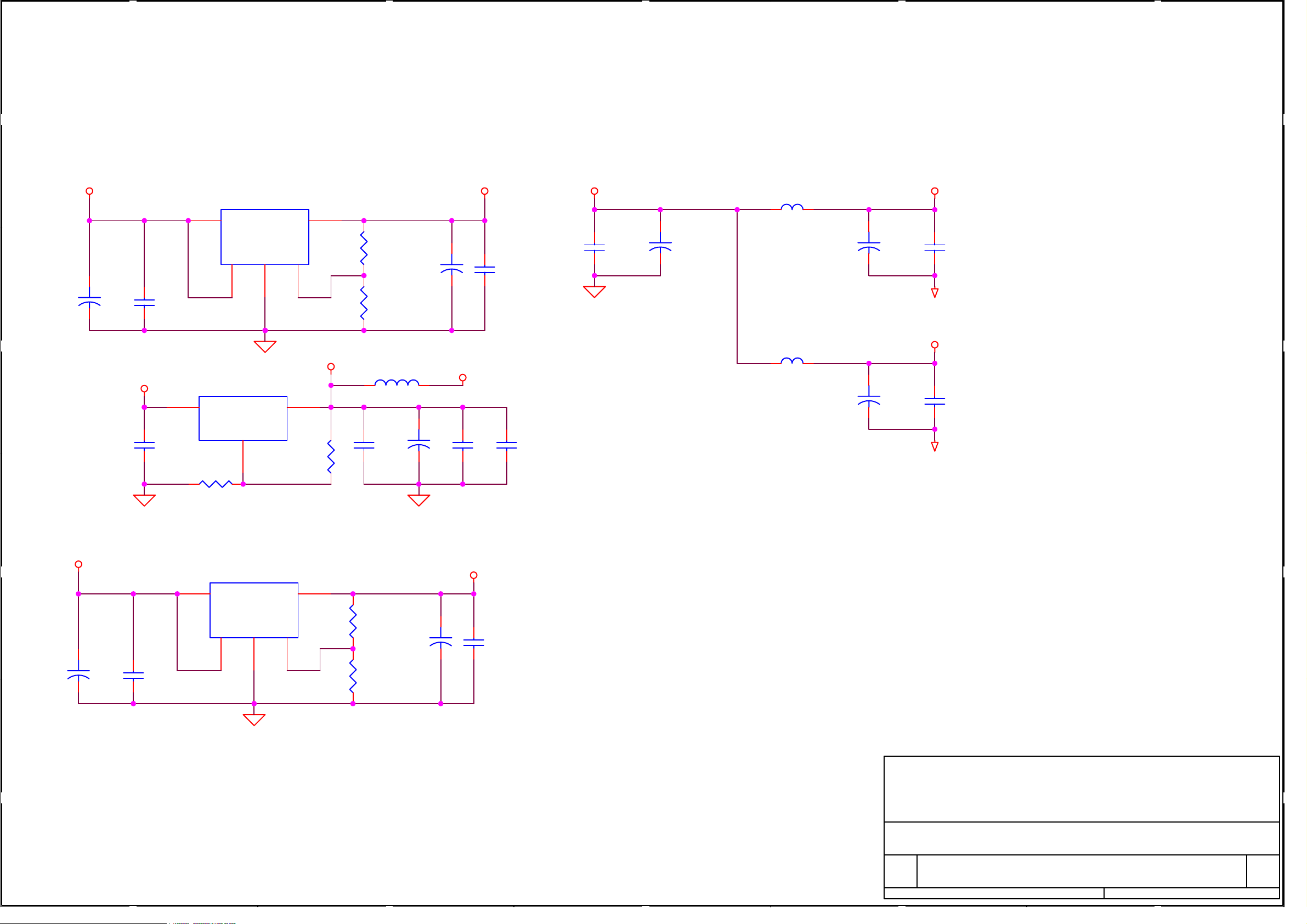

Page 4

A

B

C

D

E

C119

104

LAYOUT

NOTE:

PLACEMENT

E5

C110

104

C120

102

C111

102

C121

102

SDRAM_CS0

SDRAM_CLK1

SDRAM_CLK0

C112

102

C122

102

M2

U25

M1

U22

C113

102

C123

102

C114

+

10UF/1206

SDRAM_DQ[31..0]3

SDRAM_A03

SDRAM_A13

SDRAM_A23

SDRAM_A33

4 4

SDRAM_A43

SDRAM_A53

SDRAM_A63

SDRAM_A73

SDRAM_A83

SDRAM_A93

SDRAM_A103

SDRAM_A113

SDRAM_A123

SDRAM_A143

SDRAM_A153

SDRAM_CS03

SDRAM_CLKE3

SDRAM_RAS#3

SDRAM_CAS#3

SDRAM_WE#3

SDRAM_DQM03

SDRAM_DQM13

SDRAM_DQS03

SDRAM_DQS13

SDRAM_CLK03

SDRAM_CLK#03

VREF2,3

SDRAM_A0

SDRAM_A1

SDRAM_A2

SDRAM_A3

SDRAM_A4

SDRAM_A5

SDRAM_A6

SDRAM_A7

SDRAM_A8

SDRAM_A9

SDRAM_A10

SDRAM_A11

SDRAM_A12

SDRAM_A14

SDRAM_A15

DDR_VDD

3 3

29

30

31

32

35

36

37

38

39

40

28

41

42

26

27

24

44

23

22

21

20

47

16

51

45

46

49

18

33

15

55

61

U3

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

BA0

BA1

CS#

CKE

RAS#

CAS#

WE#

LDM

UDM

LDQS

UDQS

CLK

CLK#

VREF

1

VCC

VCC

VCC

3

VCCQ

9

VCCQ

VCCQ

VCCQ

VCCQ

8MX16 DDR

+

C124 10UF/1206

D10

D11

D12

D13

D14

D15

NC

NC

NC

NC

NC

NC

NC

GND

GND

GND

GNDQ

GNDQ

GNDQ

GNDQ

GNDQ

2

D0

4

D1

5

D2

7

D3

8

D4

10

D5

11

D6

13

D7

54

D8

56

D9

57

59

60

62

63

65

14

17

19

25

43

50

53

34

48

66

6

12

52

58

64

GND

SDRAM_DQ0

SDRAM_DQ1

SDRAM_DQ2

SDRAM_DQ3

SDRAM_DQ4

SDRAM_DQ5

SDRAM_DQ6

SDRAM_DQ7

SDRAM_DQ8

SDRAM_DQ9

SDRAM_DQ10

SDRAM_DQ11

SDRAM_DQ12

SDRAM_DQ13

SDRAM_DQ14

SDRAM_DQ15

SSTL2_VDD

FB2

B601

V33

Option for DDR with 3.3V VDD

FB3

*B601

CA5

+

T47u/16

SSTL2_VDD

C115

104

C116

104

DDR_VDD

C108

104

GND

C117

104

C109

104

C118

104

GND

SDRAM_A03

SDRAM_A13

SDRAM_A23

SDRAM_A33

SDRAM_A43

SDRAM_A53

SDRAM_A63

SDRAM_A73

SDRAM_A83

SDRAM_A93

SDRAM_A103

SDRAM_A113

SDRAM_A123

2 2

SDRAM_DQM23

SDRAM_DQM33

SDRAM_DQS23

SDRAM_DQS33

SDRAM_CLK13

SDRAM_CLK#13

SDRAM_A143

SDRAM_A153

SDRAM_CS03

SDRAM_A0

SDRAM_A1

SDRAM_A2

SDRAM_A3

SDRAM_A4

SDRAM_A5

SDRAM_A6

SDRAM_A7

SDRAM_A8

SDRAM_A9

SDRAM_A10

SDRAM_A11

SDRAM_A12

SDRAM_A14

SDRAM_A15

DDR_VDD

SSTL2_VDD

29

30

31

32

35

36

37

38

39

40

28

41

42

26

27

24

44

23

22

21

20

47

16

51

45

46

49

18

33

15

55

61

U4

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

BA0

BA1

CS#

CKE

RAS#

CAS#

WE#

LDM

UDM

LDQS

UDQS

CLK

CLK#

VREF

1

VCC

VCC

VCC

3

VCCQ

9

VCCQ

VCCQ

VCCQ

VCCQ

8MX16 DDR

+

C141 10UF/1206

D10

D11

D12

D13

D14

D15

NC

NC

NC

NC

NC

NC

NC

GND

GND

GND

GNDQ

GNDQ

GNDQ

GNDQ

GNDQ

GND

SDRAM_DQ16

SDRAM_DQ17

SDRAM_DQ18

SDRAM_DQ19

SDRAM_DQ20

SDRAM_DQ21

SDRAM_DQ22

SDRAM_DQ23

SDRAM_DQ24

SDRAM_DQ25

SDRAM_DQ26

SDRAM_DQ27

SDRAM_DQ28

SDRAM_DQ29

SDRAM_DQ30

SDRAM_DQ31

2

D0

4

D1

5

D2

7

D3

8

D4

10

D5

11

D6

13

D7

54

D8

56

D9

57

59

60

62

63

65

14

17

19

25

43

50

53

34

48

66

6

12

52

58

64

DDR_VDD

C125

104

GND

SSTL2_VDD

C132

104

GND

C126

104

C133

104

C127

104

C134

104

C128

102

C135

104

C129

102

C136

104

C130

102

C137

102

+

C131

T47u/16

C138

102

C139

102

C140

102

GND_SSTL2

GND

1 1

BBK AV ELECTRONICS CORP.,LTD.

Title

2 (8M x 16) DDR SDRAM

Size Document Number Rev

Custom

A

B

C

D

Date: Sheet

E

of

412Thursday, September 15, 2005

A1

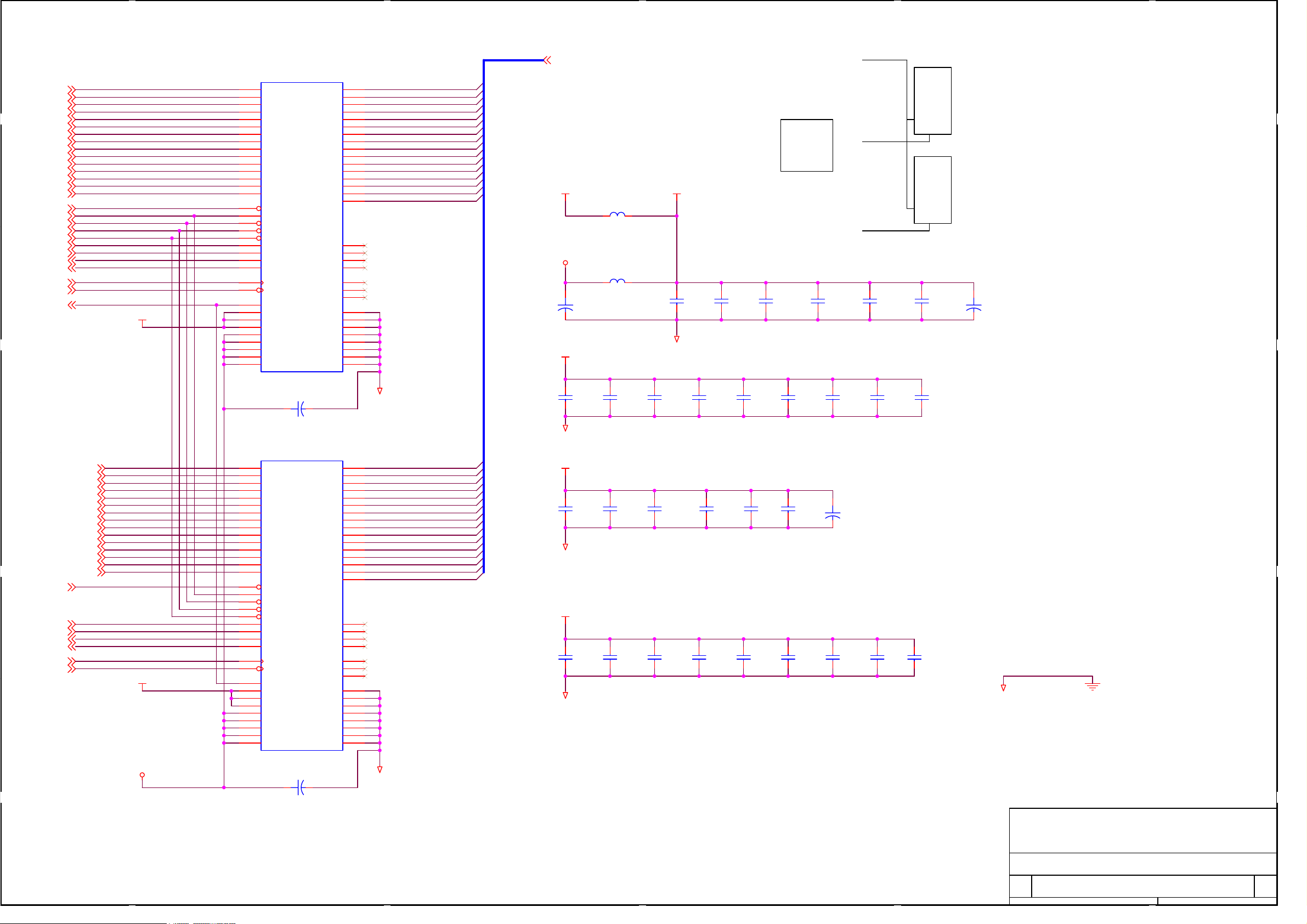

Page 5

A

B

C

D

E

4 4

E-Link III

Connector

C142

*47u/16

V33

GND

+

C143

*104

GND

/ETHER_IRQ

3 3

/E5_CS1 2

E5_ALE 2,6

E5_MA2 2,6

HD15 2,6

HD13 2,6 HD142,6

HD11 2,6

HD9 2,6

HD8 2,6

HD6 2,6

HD2 2,6

E5_GPIO2 2

/E5_OE 2,6

/E5_WEL 2,6

E5_MA5 2,6

E5_MA4 2,6

E5_UART2_TX 2

GND

J1

12

34

56

78

910

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

*HEADER 20X2

E5_UART2_RX2

GND

FB4 *601

/SYS_RST2,6

E5_MA32,6

E5_MA12,6

HD122,6

HD102,6

HD72,6

HD52,6HD4 2,6

HD32,6

HD12,6HD0 2,6

E5_/DTACK2

/E5_UDS2

/RST_SW

/WAIT2

/RST_HOST12

/RST_HOST

/RST_SW

D5

C146

104

IN4148

1 2

R69

10K

2

V33

R73

10K

D4

*IN4148

1 2

VCC

E5_GPIOx352,9 /RST_AUDIO 11,12

RESET CIRCUITRY

V33

13

Q1

3906

D6

IN4148

U5C

74AHCT14

5 6

1 2

C144

10u/16

VCC

+

R71

10K

U5D

74AHCT14

9 8

U5A

74AHCT14

1 2

R74

*0

3 4

R72

0

/RST_AUDIO

U5B

74AHCT14

R70

0

C145

102

/SYS_RST2,6

UART

R75

*0

2 2

E5_UART2_TX2

E5_UART2_RX2

J2

1

+

+

3

+

+

5

+

+

7

+

+

9

+

+

DNS CON5X2

2

4

6

8

10

GNDGND

V33

R77

*10K

U5E

74AHCT14

11 10

U5F

74AHCT14

13 12

R76

33

C147

104

R78

330

GND

R79

120

OPTICAL 12

L5

SPDIF_OUT 12AO_IEC9582

0

1 1

BBK AV ELECTRONICS CORP.,LTD.

Title

FP, RST, IR, AV IO/ELink-3 CON, UART

Size Document Number Rev

A3

Date: Sheet

A

B

C

D

E

512Thursday, September 15, 2005

of

A1

Page 6

A

B

C

D

E

FLASH MEMORY(2 or 4 or 8 Mb)

HD[15..0]2,5

BA[22..1]

V33

U7

47

1A1

46

1A2

44

1A3

43

1A4

41

1A5

40

1A6

38

1A7

37

1A8

1

1OE

48

1LE

36

2A1

35

2A2

33

2A3

32

2A4

30

2A5

29

2A6

27

2A7

26

2A8

24

2OE

25

2LE

7

VCC

18

VCC

31

VCC

42

VCC

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

GND

GND

GND

GND

GND

GND

GND

GND

74LVC16373

HD0

4 4

V33

C152

C154

104

V33

3 3

U9

1

A0

VCC

2

A1

WP

3

A2

SCL

4 5

GND SDA

*AT24C16

8

7

6

C158

*104

R88

2.2K

VCC

R89

2.2K

SCL

SDA

SCL 2,7,9,11,12

SDA 2,7,9,11,12

C155

102

+

10u/16

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

E5_ALE 2,5

C153

104

C157

104

E5_MA1 2,5

E5_MA2 2,5

E5_MA3 2,5

E5_MA4 2,5

E5_MA5 2,5

E5_MA22 2

BA6

2

BA7

3

BA8

5

BA9

6

8

BA11

9

BA12

11

BA13

12

BA14

13

BA15

BA16

BA17

BA18

BA19

BA20

BA21

BA1

BA2

BA3

BA4

BA5

BA22

/E5_WEL2,5

/SYS_RST2,5

14

16

17

19

20

22

23

4

10

15

21

28

34

39

45

R80

*4.7k

V33

R82

10K

R83

0

BA22

BA21

BA20

BA16

BA15

BA14

BA13BA10

BA12

BA11

BA10

BA9

A19/A19/A21

NC/A20/A20

ACC

WP#/ACC

RY/BY/A19

BA19

BA18

BA8

BA7

BA6

BA5

BA4

BA3

BA2

BA1

BA17

Size Stuff Not Stuff

V33

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

SKT-U2

SKT-TSOP48

U8

A15

A14

A13

A12

A11

A10

A9

A8

A19/A19/A21

NC/A20/A20

WE

RST

ACC

WP/ACC

RY/BY/A19

A18

A17

A7

A6

A5

A4

A3

A2

A1

MX29LV160

R81 *4.7k

R84 0

R85 DNS-0

R86 DNS-0

R87 DNS-0

R90 0

A16

BYTE/VIO

VSS

D15

D14

D13

D12

VCC

D11

D10

VSS

V33

BA17

48

47

46

HD15

45

HD7

44

D7

D6

D5

D4

D3

D2

D9

D1

D8

D0

OE

CE

A0

HD14

43

HD6

42

HD13

41

HD5

40

HD12

39

HD4

38

37

HD11

36

HD3

35

HD10

34

HD2

33

HD9

32

HD1

31

HD8

30

HD0

29

28

27

26

BA1

25

C156

104

WP#/ACC/SYS_RST

A19/A19/A21

NC/A20/A20

RY/BY/A19

HD[15..0] 2,5

/E5_OE 2,5

/E5_CS0 2

1MB R85,R86,R87,R90

2MB(Default)

4MB

8MB

R90

R86,R90

R85,R86,R87

R85,R87

R85,R86,R87 R90

DEDICATED ATAPI INTERFACE

2 2

VCC

R91

C159

22PF

4.7K

INT_ATA

IORDY

DMARQ

R106

4.7K

ATAPI_RESET2

R105

680

R101 0

R102 82

R103 82

R104 82

RSTATA

ATAPI_INTRQ2

ATAPI_IORDY2

ATAPI_DMARQ2

1 1

VCC

R92

10K

ATAPI_DATA8 2

ATAPI_DATA7 2

ATAPI_DATA9 2

ATAPI_DATA6 2

ATAPI_DATA10 2

ATAPI_DATA5 2

ATAPI_DATA11 2

ATAPI_DATA4 2

ATAPI_DATA12 2

ATAPI_DATA3 2

ATAPI_DATA13 2

ATAPI_DATA2 2

ATAPI_DATA14 2

ATAPI_DATA1 2

ATAPI_DATA15 2

ATAPI_DATA0 2

ATAPI_DIOW_L 2

ATAPI_DIOR_L 2

ATAPI_DMAACK_L 2

AtapiAddr1 2

AtapiAddr0 2

AtapiAddr2 2

AtapiAddr3 2

AtapiAddr4 2

RP27 33/RP

RP28 33/RP

RP29 33/RP

RP30 33/RP

RP31 33/RP

RP32 33/RP

HOST Read

45

36

27

18

45

36

27

18

45

36

27

18

45

36

27

18

45

36

27

18

45

36

27

18

HD_AT8

HD_AT7

HD_AT9

HD_AT6

HD_AT10

HD_AT5

HD_AT11

HD_AT4

HD_AT12

HD_AT3

HD_AT13

HD_AT2

HD_AT14

HD_AT1

HD_AT15

HD_AT0

DIOW

DIOR

DMACK

ATA_A1

ATA_A0

ATA_A2

CS1FX

CS3FX

RSTATA

HD_AT7

HD_AT6

HD_AT5

HD_AT4

HD_AT3

HD_AT2

HD_AT1

HD_AT0

DMARQ

DIOW

DIOR

IORDY

DMACK

INT_ATA

ATA_A1

ATA_A0

CS1FX

FB5 B601

FB6 B601

FB8 B601

FB10 B601

FB12 B601

FB14 B601

FB16 B601

FB18 B601

FB20 B601

FB22 B601

FB23 B601

FB24 B601

FB25 B601

FB26 B601

FB27 B601

FB28 B601

FB29 B601

FB31 B601

J3

12

34

56

78

910

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

HEADER 20X2

FB7 B601

FB9 B601

FB11 B601

FB13 B601

FB15 B601

FB17 B601

FB19 B601

FB21 B601

FB30 B601

FB32 B601

HD_AT8

HD_AT9

HD_AT10

HD_AT11

HD_AT12

HD_AT13

HD_AT14

HD_AT15

KEYWAY (NO PIN)

CAB_SEL

ATA_A2

CS3FX

HD[15..0]2,5

R115

0

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD[1:0]

HD[3:2]

HD[7]

V33

R94 DNS-4.7K

R96 DNS-4.7K

R98 DNS-4.7K

R95 DNS-4.7K

R93 DNS-4.7K

R97 DNS-4.7K

R99 DNS-4.7K

R100 DNS-4.7K

JP1

1

2

3

DNS HEADER 3X1

R111 DNS-4.7K

R113 DNS-4.7K

R108 DNS-4.7K

R107 DNS-4.7K

00

01

10

11

00

01

0 Normal Mode (Jumper 1-2)

1

BBK AV ELECTRONICS CORP.,LTD.

R114 DNS-4.7K

R110 DNS-4.7K

R112 DNS-4.7K

R109 DNS-4.7K

Samsung - K4H281638D-TCB3

Micron - MT46V8M16-55

ESMT - M13S128168A-6T

Nanya

64Mb DDR SDRAM10

128Mb DDR SDRAM

256Mb DDR SDRAM

Reserve11

Debuge Mode (Jumper 2-3)

Title

FLASH, ATA, EEPROM

Size Document Number Rev

C

A

B

C

D

Date: Sheet

E

612Thursday, September 15, 2005

of

A1

Page 7

A

B

C

D

E

RDS /RBDS PRE-PROCESSOR

1394 FIREWIRE PHY

CR3

104

RR4

1K

YR1

RR2 22

RR3

470K

CR2

47PF

1

2

3

4

5

6

7

8

9

10

UR1

SAA6588

MRO

MPTH

TCON

OSCO

OSCI

VSSD

VDDD

DAVN

SDA

SCL

LVIN

CIN

SCOUT

VREF

MPXIN

VSSA

VDDA

AFIN

MAD

PSWN

4 4

GND_PHY_D

BIO_LREQ2

GND_PHY_D

E5_GPIO12

C163

56PF

R117 51

C160

27PF

C161

27PF

V33_PHY_D

BIO_LREQ

PHY_XI

Y2

24.576MHz

PHY_XO

C162 104

PHY_FILT0

PHY_FILT1

V33_PHY_A

R116 6.34K/1%

R118 1M/1%

VCC

RR1

10K

RDS_DATA2

SDA2,6,9,11,12

SCL2,6,9,11,12

CR1

82PF

4.332MHz

VCC

CR5

104

CR7

331

+

CR8

47u/16

RDS_MPX 9

CR4

104

20

19

18

17

16

15

14

13

12

11

CR6

151

+

CR9

2.2u/50

PHY_R0

R120

56.2/1%

R126

56.2/1%

C166

221

TPBIAS

R121

56.2/1%

R127

56.2/1%

R130

5.11K/1%

GND_PHY_A

GND_PHY_A

USB_D0-2

USB_D0+2

C165

224

C164

+

1u/50

GND_PHY_A

T1

1

2

3

4

L

USB

R143

15K

5

6

7

8

R144

15K

TPA+

TPATPB+

TPB-

R134 22

R139 22

C167

104

USB_BDM0

USB_BDP0

TPBTPB+

TPATPA+

VCC

R137 0

R140 0

FB34

FB35

GND_PHY_A

B601

B601

R17

FB221

CN1

6P2.0

1

2

3

4

5

6

J4

7

6

5

4

3

2

1

*7P2.0

PHY_R1

PHY_R0

TPBIAS

PA+

PAPB+

PB-

V33_PHY_D

V33_PHY_D

C177

104

PHY_R1

GND_PHY_A

U10

R119 22

BIO_PHY_CLK2

BIO_PHY_CTL02

3 3

C148

101

GND_PHY_D

V33_PHY_D

BIO_LINK_ON2

2 2

GND_PHY_D

GND_PHY_D

BIO_PHY_CTL12

BIO_PHY_DATA02

BIO_PHY_DATA12

R129

DNS-10K

R131

10K

GND_PHY_A

E5_GPIOx02

R128

2.2K

GND_PHY_D

BIO_LPS2

R135 680

R138 680

R141 680

GND_PHY_D

1

2

3

4

5

6

7

8

9

10

11

12

SYSCLK

CTL0

CTL1

D0

D1

D2

D3

D4

D5

D6

D7

PD

PHY_PC0

PHY_PC1

PHY_PC2

E5_VPAD

C175

104

LPS LREQ

13 48

45

46

47

DVDD

DGND

DGND

TSB41AB1

S-PQFP-48-TI

DGND

C/LKON

PC0

14

15

161718

PHY_PC0

+

43

42

41

40

44

XI

XO

DVDD

PLLVDD

PLLGND

CPS

ISO

DVDD

PC1

PC2

20

19

21

PHY_ISO

PHY_PC1

PHY_PC2

PHY_CPS

PHY_ISO

L6 B601

C169

47u/16

37

38

39

RESET

FILTER0

FILTER1

AGND

AVDD

R1

R0

AGND

TPBIAS

TPA+

TPA-

TPB+

TPB-

AGND

AVDD

TESTM

SE

SM

22

23

24

R132 1K

PHY_SM

PHY_SE

R133 1K

R136 10K

R142 10K

+

C170

T47u/16

36

35

34

33

32

31

30

29

28

27

26

25

GND_PHY_A

V33_PHY_A

C176

104

GND_PHY_D

USB_OC02

GND_PHY_A

E5_VPAD

L23 B601

1 1

A

C168

+

10u/16

C171

103

C172

103

GND_PHY_D

B

V33_PHY_D

C173

103

C174

104

C

USB_PO02

BBK AV ELECTRONICS CORP.,LTD.

Title

1394 PHY &USB

Size Document Number Rev

A3

of

Date: Sheet

D

E

712Thursday, September 15, 2005

A1

Page 8

A

B

C

D

E

MAIN POWER REG

4 4

C179

+

100u/16

C186

+

220u/16

VCC_VOUT_A

C181

104

GND_VOUT

VCC_AOUT_A

C187

104

GND_AOUT

2_5V

U11

PQ018EZ02/PQ070XZ02

1

VIN

VC

2

+

C184

220u/16

3 3

VCC

C185

104

C189

104

U12

LT1117-3.3

3

VIN

VOUT

GND

5

VOUT

ADJ

1

ADJ

4

2

R147

*1K

3

DV33

R145

*1K

R146

*2.2K

L9

*FB

C190

104

C182

330u/16

+

C188

47u/16

V18

C191

103

C183

104

C192

104

+

V33

VCC

C180

104

L7 B601

C178

+

100u/16

L8 B601

R148

0

V33

2 2

+

C196

220u/16

1 1

C197

104

U13

PQ025EZ01

1

VIN

VC

2

GND

5

VOUT

4

ADJ

3

R149

*1K

C194

330u/16

R150

*1K

+

V25

C195

104

BBK AV ELECTRONICS CORP.,LTD.

Title

Size Document Number Rev

A4

Date: Sheet

A

B

C

POWER CONN

D

A1

812Thursday, September 15, 2005

E

of

Page 9

A

B

C

D

E

DGND

C_1/GPIO

R231 2.2K

R232 2.2K

DVDD

C_2/GPIO

C_3/GPIO

C_4/GPIO

C_5/GPIO

R152 *33

61

IOVDD

IOGND

C_6/GPIO/RED

C_7/GPIO/GREEN

C_8/GPIO/BLUE

C_9/GPIO/FSO

IOGND

IOVDD

DGND

DVDD

Y_0

Y_1

Y_2

Y_3

Y_4

Y_5

Y_6

Y_7

Y_8

Y_9

DGND

DVDD

V33_VID

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

VI_VSYNC 2

V18_VID

C2 11

C4 11

GPO1 12

GPO2 12

VI_0

R162 33

VI_1

R163 33

VI_2

VI_3

VI_4

VI_5

VI_6

VI_7

VI_8

VI_9 VI_D9

RP33 33/RP

4 5

3 6

2 7

1 8

RP34 33/RP

4 5

3 6

2 7

1 8

VI_D0

VI_D1

VI_D2

VI_D3

VI_D4

VI_D5

VI_D6

VI_D7

VI_D8

VI_D[9..0] 2

C198

33PF

Pb/B_IN

4 4

F_C_IN12

F_CVBS_IN12

Y/G_IN

F_Y_IN12

R_Y_IN12

3 3

Pr/R_IN

TV_CVBS_IN12

R151 18

R153 56

R154 18

R155 56

R156 18

R157 56

R158 18

R159 56

R160 18

R161 56

R164 18

R165 56

R166 18

R167 56

R168 18

R169 56

C199 104

C201 104

C202 104

C203 104

C204 104

C205 104

C206 104

C207 104

V33_VIA

V18_VIA

Y3

14.31818MHz

C200

33PF

1

VI_1_B

2

VI_1_C

3

CH1_A33GND

4

CH1_A33VDD

5

CH2_A33VDD

6

CH2_A33GND

7

VI_2_A

8

VI_2_B

9

VI_2_C

10

CH2_A18GND

11

CH2_A18VDD

12

A18VDD_REF

13

A18GND_REF

14

CH3_A18VDD

15

CH3_A18GND

16

VI_3_A

17

VI_3_B

18

VI_3_C

19

CH3_A33GND

20

CH3_A33VDD

R226

100K

80797877767574737271706968676665646362

XTAL2

VI_1_A

CH1_A18GND

XTAL1

PLL_A18VDD

PLL_A18GND

CH1_A18VDD

U14

TVP5146

FID/GPIO

C_0/GPIO

HS/CS/GPIO

VS/VBLK/GPIO

CH4_A33VDD

CH4_A33GND

VI_4_A

CH4_A18GND

CH4_A18VDD

NSUB

TMS

SCL

SDA

INTREQ

DVDD

DGND

PWDN

RESETB

FSS/GPIO

AVID/GPIO

GLCO/I2CA

IOVDD

IOGND

DATACLK

40

R228 2.2K

R176 100

R177

10K

R174 33

R175 33

(/RST_VI)

(INT_VI)

R178

10K

V33_VID

(VI_AVID)

VI_FSS

VI_CLK0 2

E5_GPIOx3 2

(Fast switch input source between RGB and CVBS/YC)

E5_GPIOx7 2

E5_GPIOx6 2

SDA 2,6,7,11,12

SCL 2,6,7,11,12

E5_GPIOx352,5

DO2

CL2

DI2

CE2

RDS_MPX7

C223

+

100u/16

R170 18

R172 18

C210

+

10u/16

C224

104

C211

104

R171 56

R173 *56

C212

104

C225

104

GND_VIN

V33_VID

C213

104

C226

104

R_C_IN12

R_SC2_SC1_CVBS_IN12

2 2

DV33

L13

L11

B601

21

B601

21

C214

104

V33_VIA

C208 104

C209 104

C227

104

GND_VIN

V18 V18_VID

L14

L12

B601

B601

21

C218

104

C230

C219

104

C231

104

104

C215

+

10u/16

21

C222

+

100u/16

104

C216

104

C228

C217

104

C229

104

104

C220

104

V18_VIA

C232

21222324252627282930313233343536373839

R229 *2.2K

C233

104

C221

104

IDC Slave Addr:

0xB8/B9

GND_VIN

CN2

VI_FSS

Pb/B_IN

Y/G_IN

Pr/R_IN

DO

CL

DI

CE

12P1.0

1

2

3

4

5

6

7

8

9

10

11

12

7P1.0 for

DW9916,

12P1.0 for

rw+amplifier

and VCR

GND_VIN

GND_VIN

GND_VIN

1 1

BBK AV ELECTRONICS CORP.,LTD.

Title

VIDEO IN

Size Document Number Rev

A3

of

A

B

C

D

Date: Sheet

E

912Thursday, September 15, 2005

A1

Page 10

A

B

C

D

E

C234

*22PF

C235

*22PF

4 4

R179

*220

C236

*331

L15

1.8uH

C237

101

Y_O 12 C2Y2

R180

*220

C238

*331

L16

1.8uH

C239

101

C_O 12

C240

C241

*22PF

*22PF

Pr/R2

Y/G2

R182

*220

3 3

C244

*331

L18

1.8uH

C245

101

Y/G_O 12

R181

*220

C242

*331

L17

1.8uH

C243

101

Pr/R_O 12

C246

*22PF

Pb/B2

R183

*220

C247

*331

L19

1.8uH

C248

101

Pb/B_O 12

VCC_VOUT_A

R185

C249

*22PF

C250

6.8K

220u/10

2 2

CVBS2

R188

180

C251

*331

L20

1.8uH

C252

101

+

R189

6.8K

1 1

Q2

3904

CVBS_O 12

R184

470

BBK AV ELECTRONICS CORP.,LTD.

Title

<Title>

Size Document Number Rev

A

Date: Sheet

A

B

C

<Doc> A1

10 12Thursday, September 15, 2005

D

of

E

Page 11

A

e

B

C

D

E

Audio Out (2 & 6 ch)

DV33

4 4

AO_MCLKO 2

AO_SCLK 2

AO_FSYNC 2

AO_D3 2

AO_D2 2

AO_D1 2

SCL 2,6,7,9,12

SDA 2,6,7,9,12

E5_GPIO3 2

R230

2.2K

VCC_AOUT_A

3 3

C271

104

C270

1u/50

GND_AOUT

+

IDC Slave Addr: 0x22/23

U15

7

5

6

2

3

4

15

13

11

12

10

1

14

8

22

MCLK

BCLK

LRCK

SDATA1

SDATA2

SDATA3

M2

AD0/CS

SCL

SDA

RST

VLS

VLC

VD

VA

C272

104

C273

104

AOUTL1

AOUTR1

MUTEC1

AOUTL2

AOUTR2

MUTEC2

AOUTL3

AOUTR3

MUTEC3

FILT+

VQ

GND1

GND2

CS4360

C269

103

27

26

28

24

23

25

20

19

18

16

17

9

21

GND_AOUT

MUTECS

MUTELRS

MUTELR

+

C265

3.3u/16

C267

104

GND_AOUTGND_AIN

+

C266

3.3u/16

C253 10u/16

C254 10u/16

C255 10u/16

C256 10u/16

C257 10u/16

C258 10u/16

C268

104

IR_FMUTE2,12

E5_GPIOx52

+

+

+

+

+

+

IR_FMUTE

MUTECS

C29

R190 5.6K

R191 5.6K

R192 5.6K

R193 5.6K

R194 5.6K

R195 5.6K

GND_AOUT

D8 IN4148

1 2

D9 *IN4148

1 2

1

3

2

C259

122

D10 *MMBD4148CC

C260

122

C261

122

C262

122

MUTE 12

C263

122

CENTER 12

SUBWOOFER 12

REAR_L 12

REAR_R 12

A_L_OUT 12

A_R_OUT 12

C264

122

MUTELR

MUTELRS

MUTEC

MUTES

CN7

*6P2.0

1

2

3

4

5

6

Audio In

C49

R122

10K

R214 22

R215 *10K

C285

104

+

C283

1u/50

R186

6.8K

R125

6.8K

V33_AIN_A

R124

6.8K

B601

R123

6.8K

V33_AIN_A

DV33

C287

L10

10u/16

C193

+

10u/16

GND_AIN

R210 *0

R211 *0

/RST_AUDIO 5,12

+

C289

104

ADC_DIF

ADC_DIV

U17

10

AINL

12

AINR

9

16

13

RST

1

M0

M1

6

VD

3

VL

VA

R216 10K

R217 10K

C288

104

GND_AIN GND_AIN

MCLK

SCLK

LRCK

SDOUT

FILT+

VQ

REF_GND

GND

CS5340

2

7

8

4

15

11

14

5

DV33

AIN_D

V33_AIN_A

2 2

R212

A_L_IN 12

A_R_IN 12

1 1

0

R213

0

C281

102

GND_AIN

C282

102

1

2

GND_AIN

C286

104

Title

Size Document Number Rev

A4

D7 *MMBD4148CC

3

AI_MCLKO 2

AI_SCLK 2

AI_FSYNC 2

AI_D0 2

+

C284

1u/50

BBK AV ELECTRONICS CORP.,LTD.

<Title>

<Doc> <RevCod

Date: Sheet

A

B

C

D

11 12Thursday, September 15, 2005

of

E

Page 12

A

4 4

E5_GPIOx422

E5_GPIOx412

E5_GPIOx252

IR_FMUTE2,11

/RST_HOST5

E5_GPIO02

E5_GPIOx242

3 3

FRONT PANEL INTERFACE

D_FM

FP_SCLK

RDY_FM

/FP_RST

D_HOST

ATN_FM

C290

C291

C292

47PF

47PF

47PF

B

C293

47PF

C294

47PF

5V_STB

R218 2.2K

R219 33

R220 33

R221 33

R222 2.2K

+

C295

10u/16

C

GND

VFD_DIO

VFD_CLK

VFD_STB

IR_FMUTE

5V_STB

/RST_HOST

P_CTL

10

1

2

3

4

5

6

7

8

9

CN4

10P2.0

CN3

24P1.0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

D

OPTICAL 5

SPDIF_OUT 5

SUBWOOFER 11

MUTE 11

CENTER 11

/RST_AUDIO 5,11

REAR_R 11

REAR_L 11

A_R_OUT 11

SCART1

SCART2

A_L_OUT 11

GPO1 9

GPO2 9

E5_GPIOx2 2

E5_GPIOx4 2

E5_GPIO4 2

E5_GPIO5 2

SDA 2,6,7,9,11

SCL 2,6,7,9,11

AUDIO_SEL0

AUDIO_SEL1

E

5V_STB

GND_AOUT

CN5

26P1.0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

S_Y_OUT

S_C_OUT

V_OUT+3.3V

R_V_OUT

G_Y_OUT

B_U_OUT

R_C_IN

R_Y_IN

V3_IN

V4_IN

V1_IN

A_L_IN

A_R_IN

E5_GPIOx1 2

Y_O 10

C_O 10

CVBS_O 10

Pr/R_O 10

Y/G_O 10

Pb/B_O 10

R_C_IN 9

R_Y_IN 9

F_Y_IN 9

F_CVBS_IN 9

R_SC2_SC1_CVBS_IN 9

F_C_IN 9

TV_CVBS_IN 9

A_L_IN 11

A_R_IN 11

CN6

10P2.5

1

2

3

4

5

6

7

8

9

10

P_CTL

5VSTB

VCC

GND

GND

GND

+2.5V

+2.5V

5V_STB

L21 FB

2_5V

L22

FB

VCCV33

R223

1K

2 2

C297

104

+

C298

330u/16

C301

104

+

C299

330u/16

C300

104

+

C296

330u/16

A/V I/O Connector

GND_AIN

1 1

BBK AV ELECTRONICS CORP.,LTD.

Title

Size Document Number Rev

Date: Sheet

A

B

C

D

<Title>

<Doc> 0.0

Custom

of

12 12Thursday, September 15, 2005

E

Page 13

VDD

1

2

CN3

2P2.0

CN4

4P2.0

4

3

2

1

STB_LED

R11 1K

R9

1K

Q3

9015

K13 SW

K1

K3 SW

K9 SW

R4

10K

VDD

R21

4.7K

CN1

5P2.0

Q4

2

9014

3

1

K12

K14 SW

K2

K4 SW

K7 SW

K10 SW

R5

10K

5

4

3

2

1

R2 1K

R1 2.2 1/4W

C1

VCC

22u/50

K15 SW

K5 SW

K6 SW

K8 SW

K11 SW

R6

10K

1 1

LD1

STBY

VCC

R20

4.7K

LD3

VTR

LD2

DVDR

R14

10K

Q1

8050C

R8 220

R7 220

C15

102

U2

HS0038B3V

OUT

VCC

GND

CN5

4P2.0

4

3

2

1

K16 SW

9DW9919-1

D7

1N4148

VDD

12

+

C11

4.7u/16

R16

10K

F+

F-

-24V

+

Q2

9015

C2

104

C6

30PFC730PF

3

2

1

R15

4.7K

D8

1N4148

D5

1N4148

D1

1N4148

D2

1N4148

D3

1N4148

D4

1N4148

Y1

5MHZ/20pF

C14

10u/16

+

C13

103

STB_LED

P_CTL_PSW

C3

103

G7

G6

G5

G8

37

38

39

FIP21

FIP22

KEYC

KEYB

KEYA

R13

10

12

40

41

42

43

44

45

46

47

48

49

50

51

52

VDD

Y2

32.768KHZ/20pF

C9

20PF

D6

1N4148

C8

103

FIP23

FIP24

P00

P01

P02

P03

P04

P05

P06

P07

IC

X2

X1

VSS0

VDD0

XT1

XT2

12345678910111213

R12

100

C10

20PF

5V_STB

12

+

G2

G3

G4

33

34

35

36

FIP18

FIP19

FIP20

U1

UPD16316

RESET

P10

P11

R17

2.7K

VDD

C12

47u/16

A

P16

G1

32

FIP16

FIP17

P12

SCKSOSI

P15

31

FIP15

G[1:6]

P14

30

FIP14

R18

2.7K

29

FIP13

INTP0

27

28

VDD1

VLOAD

INTP1

TI

R19

2.7K

FIP12

FIP11

FIP10

FIP9

FIP8

FIP7

FIP6

FIP5

FIP4

FIP3

FIP2

FIP1

FIP0

R10

470

26

25

24

23

22

21

20

19

18

17

16

15

14

VDD

P13

P12

P11

P10

P9

P8

P7

P6

P5

P4

P3

P2

P1

更改

设 计

P[1:16]

-24V

R3

270K

C5

103

K1 CH+

K2 CH-

C4

*103

VDD

K7 VCR

K8 OPEN/CLOSE

K3 EJECT K9 PLAY

K4 DVD

K10 STOP

K5 SOURCE K11 PAUSE

K6 FWD

5V_STB

更改单号

标准化审 核

日期数量 签名

批 准

K12 REC

D_FM

FP_SCLK

RDY_FM

/FP_RST

D_HOST

ATN_FM

DW9919面板原理图

VFD

4DW9919-2

F-

P1

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

P16

G1

G2

G3

G4

G5

G6

F+

K13 REV

K14 PREV

K15 NEXT

GND

VFD_DIO

VFD_CLK

VFD_STB

MUTE

5V_STB

/RST_HOST_LED

P_CTL_PSW

D_HOST

ATN_FM

BBK

第 1 张

VFD1

20-0607F(1200229)

35

F2

34

F2

32

P16

31

P15

30

P14

29

P13

28

P12

27

P11

26

P10

25

P9

24

P8

23

P7

22

P6

21

P5

20

P4

19

P3

18

P2

17

P1

16

NX

15

NX

14

NX

13

NX

12

NX

11

NX

10

NX

9

1G

8

2G

7

3G

6

4G

5

5G

4

6G

2

F1

1

F1

CN2

10P2.0

1

2

3

4

5

6

7

8

9

10

共 1 张

版次:1.0

广东步步高电子工业有限公司

A

Page 14

A

4 4

D10

1N4007

D11

1N4007

D9

1N4007

D12

1N4007

3 3

C13

104/~275

RV1

680K/1/2W

2 2

C3

*221 AC400V

F1

250V/T2AL

BCN1

2P7.92

1 1

LF1

40mHX2

LF2

40mHX2

C14

*221 AC400V

1

2

RT1

10/4A(104MS)

t

D17

*22V 1/2W

+

CE11

47u/50

CE5

100uF/400V

6

5

4

3

C6

102 AC400V

C1

102 AC400V

+

R5

75 1/4W

IC1

FSDM0565R

Vstr

N.C

Vfb

Vcc

Drain

GND

1

2

D16

*PK6E200

R1

36K 1/2W

R6

36K 1/2W

C26

*333

B

L4

FB

D7

HER105

R33

*470

P_CTL

T1

BCK-28-0605

1

C4

102/1KV

R2

39K 2W

D4

FR207

3

5

6

IC2

PC817

C27

*473

C9

473

D21

*5.1V/7.5mm

B+12V V_CTL

R32 1k

R29

2.2k

43

R28 10k

12

Q7 3906/9015

R31

2.2k

Q8

3904/9014

R15 470

15

14

13

12

11

10

R30

1.5K

9

8

7

C

HER105

C5

101

D6

D1

HER105

D16

HER105

C19

101/500V

C18 101/500V

C17

101/500V

CE13

47u/50

HER105

R14

1.2K

IC3

TL431

D8

C7

104

+

+

CE12

100u/25

+

220U/63V

D2

SR3A0

D3

SR10100

CE6

GZ2200u/10

D5

SR10100

C15

104

C10

102

C12

104

R17

10

R25

1.2K

L1 FB

CE1

+

100u/25

L6 30uH

CE18

CE21

10u/50

+

F-

FF+

R16

12K 1%

R11

8.2K 1%

Q6 9015

3

R21

3.3K

2

Q5

9014

+

+

+

1

D20

CE2

+

100u/25

Q3

2SD669A

D18

27V 1W

L2

10uH

CE3

1000u/25

L3

10uH

L5

10uH

CE9

GZ2200u/10

D13 5.1V 1/2W

R9

47K

*C25

104

-25VB-25V

25V 1/2W

CE4

470u/25

CE8

GZ1000u/10

GZ1000u/10

B-25V

+15V

+

+

CE10

+

-25V

R8

9.1K 1/6W

CE14

47u/16

D

CE19

100u/50

B+12V

+

-12V

C2

104

Q1

1PP15N03L

+

L7

20uH

C20

104

C22

104

1PP15N03L

10K 1/6W 1%

Q4

9014/3904

CE23

+

100u/25

IC4

PQ12RD21

1 2

Vin Vo

C11

104

+6V

Q2

R19

IC5

TL431

10K 1%

+

R20

D19

5.6V 1/2W

GND

3

CE17

220u/16

+

CE22

10u/25

+

C23

104

Vc

47u/25

CE20

100u/16

+26V

GND

+15V

+6V

GND

GND

GND

3.3V

4

CE24

+

R12

75 1/4W

IC6

TL431

5VSTB

C21

104

R34

330

CN6

6P2.0

1

2

3

4

5

6

J6

*5MM

J7

CE16

100u/25

+

R4 3.3K

R22

1.8K 1/6W 1%

+

R24

5.1K 1/6W 1%

9014/3904

for +6V

for +15V

for +26V

5MM

C8

104

V_CTL

+3.3V

D14

1N5401

D15

1N5401

CE15

+

220u/16

R23

3.3K 1/4W

R3 3.3K

CE7

10u/25

Q9

8050

Q10

E

+12V

-12V

GND

+12V

GND/3.3

+5V

+2.5V/5

+2.5V/G

J8

J9 *7.5MM

V_CTL

F+

F-

-25V

GND

+5V

P_CTL

5VSTB

+3.3V

+3.3V

+5V

GND

GND

5MM

+12V

+5V

F+FF+

R7

430

R10

100

CN3

10P2.5

F-

CN1

2P2.5

1

2

CN2

5P2.5

1

2

3

4

5

1

2

3

4

5

6

7

8

9

10

GND

+12V

C16

104

CN4

4P3.96

1

2

3

4

CN5

5P2.0

1

2

3

4

5

TO fan

+5V

BBK

开关电源原理图

更改

设 计

数量

审 核

更改单号

标准化

签名

日期

批 准

SWITCH POWER SUPPLY

板号:5DW9919-2

第 1 张

共 1 张

版次:1.0

广东步步高电子工业有限公司

A

B

C

D

E

Page 15

A

B

C

D

E

Modify Notes:

2005.01.08

P1 U1 Supply voltage from +6.2V to +5V

4 4

P8 Del Net E5_C

P8 Add C166,C167,C168 when in mtk scart and out scart(rgb) ,exist interference.

P7. add gcode ic

P9. add r210,r211,r213,r214 amend the sound distortion when playing vcd,stero out,connect KONGJA tv

P8 add c169,c176 amend log picture distortion

2005.01.12

P8 add Q39,Q40,r218,r219,r220 etc. switch RGB/CVBS select votage level,when SCART in

2005.01.28

3 3

change c136,c145 to 220u

2 2

1 1

Title

<Title>

Size Document Number Rev

A

Date: Sheet

A

B

C

<Doc> <RevCode>

110Friday, September 16, 2005

D

of

E

Page 16

A

B

C

D

E

+12V

ADC_SEL1

N/A

R_AUDIO

F_AUDIO

TUNER

+5V

C17

103

TV_MONO 7,8

CN1

24P1.0

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

CN2

26P1.0

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

1

2

3

4

5

6

7

8

9

OPTICAL 6

SPDIF_OUT 6

SUBWOOFER 5

MUTE 3

CENTER 5

/RST_BTSC 7

REAR_R 4

REAR_L 4

A_R_OUT 3

SCART1

SCART2

ADC_SEL0

ADC_SEL1

A_L_OUT 3

TVP5146_C7 8

TVP5146_C8 8

E5_GPIOx2 8

E5_GPIOx4 8

E5_GPIO4

E5_GPIO5

SAA7115Pin35

SAA7115Pin34

CPUMUTE(for DMN8600)

E5_GPIO3(for DMN8600)

SAA7115Pin49

SAA7115Pin48

IIC_SDA 2,7,9

IIC_SCL 2,7,9

5V_STB

E5_GPIO1(for DMN8600)

1

2

3

4

5

6

7

8

9

E5_GPIOx1_RTC_INT 2,8

S_Y_OUT 2

S_C_OUT 2

V_OUT 9

R_V_OUT

G_Y_OUT

B_U_OUT

R_V_OUT 6

G_Y_OUT 6

B_U_OUT 6

R_C_IN

R_Y_IN

F_Y_IN

V3_IN

V4_IN

V1_IN

R_SC2_SC1_CVBS_IN 8,9

A_L_IN

A_R_IN

BBK AV ELECTRONICS CORP.,LTD.

C1

47u/16

R11

10K

+6.2V

R1 220

D1

6.2V 1/2W

A_L_IN

A_R_IN

-12V