Page 1

SERVICE MANUAL

DW9937S

Ver 0.0

Page 2

PREFACE

INDEX

FEATURES

FRONT PANEL&REAR PANEL

REMOTE CONTROL

........................................................................................................................

.................................................................................................................

BLOCK DIAGRAM

BLOCK DIAGRAM

.............................................................................................................

EXPLODED VIEW

EXPLODED VIEW

......................................................................................................................

PARTS SPECIFICATIONS

SST39VF16 0 ............................................................................................................................... 6

M13S128168A ............................................................................................................................

TSB41AB1

TVP5146

CS4360

CS5333 ......................................................................................................................................... 15

74HC/HCT14 ............................................................................................................................. 17

74ALVT16373 ...................................................................................................................... 18

MM1313 ............................................................................................................................................ 19-30

MAX4051 .......................................................................................................................................... 31-50

FSDM07652RB ................................................................................................................................ 51-70

LP2995

PQXXXEZ02Z .......................................................................................................................... 72

TUNER .............................................................................................................. 73

..................................................................................................................................

...................................................................................................................... 9

........................................................................................................................................ 13

................................................................................................................

........................................................................................................................

1

2

3

4

5

7

8

71

SCHEMA

TIC DIAGRAM&PCB SILKSCREEN

MAIN BOARD SCHEMATIC AND PCB LAYOUT

AV BOARD SCHEMATIC ..................................................................................................... 85-95

KEY BOARD SCHEMATIC .......................................................................................................

POWER BOARD SCHEMATIC ........................................................................................... 97

VCR MODLE 98-100

PARTSLIST

MAIN BOARD .............................................................................................................................. 101-102

MAIN PANEL BOARDKEY

POWER BOARD .............................................................................................................. 105-107

AV BOARD 108-110

............................................................................

.........................................................................................................................

......................................................................................................................

....................................................................................................................................

74-84

96

103-104

Page 3

1

Page 4

2

Page 5

3

Page 6

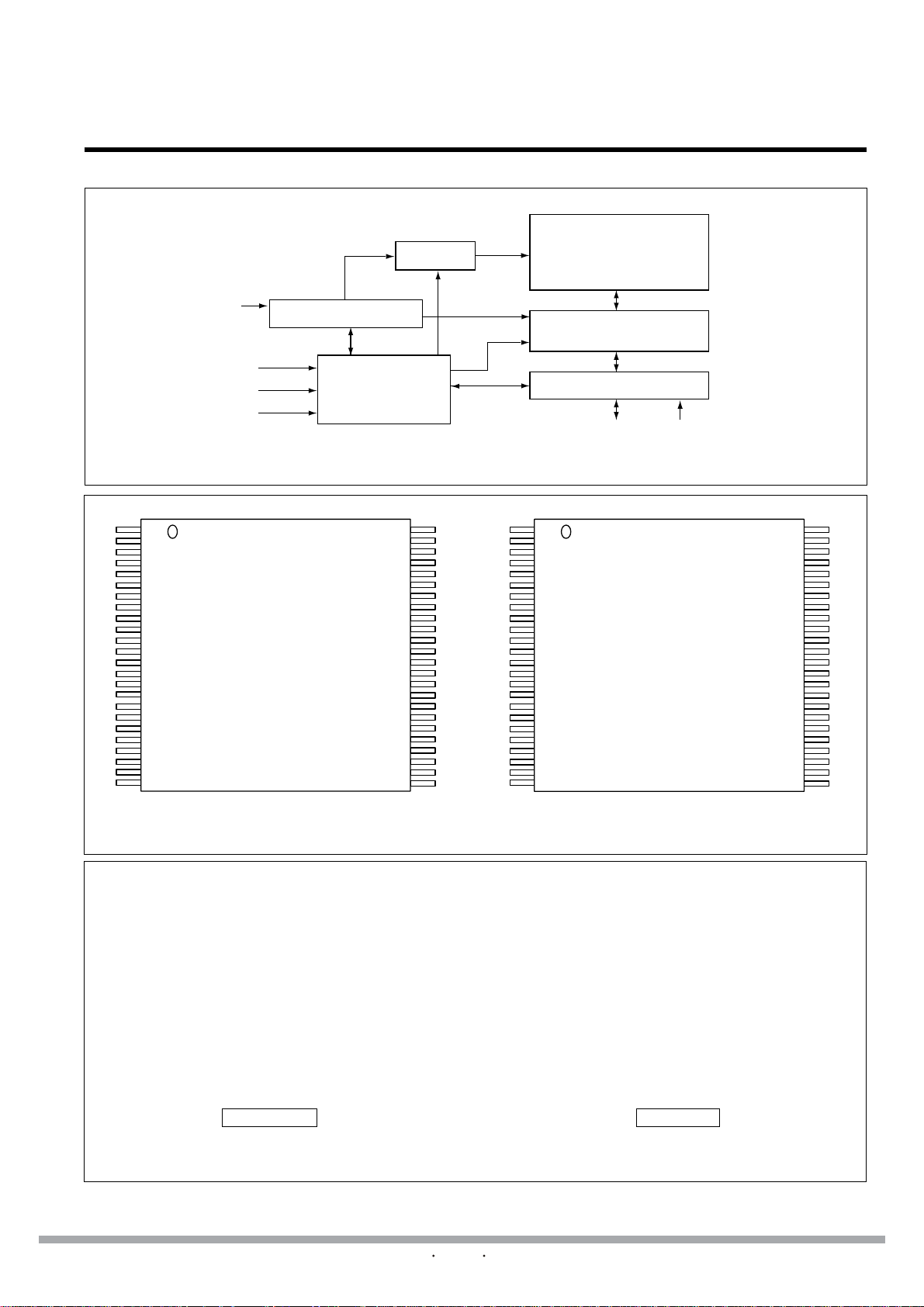

BLOCK DIAGRAM

POWER SUPPLY

Power board Video signal(s) Main pannel board

Audio signal(s)

Control signal(s)

wake up signal

Power on/off signal

VCR

VCR CVBS signal

HC4052

VCR L&R audio signals

MSP3415

CD4052

AV Channel

VMM1313

Switch

audio Signals outputs (except mixed L/R Audio) (except CVBS )

CVBS &mixed Audio inputs Video inputs Audio outputs Video outputs

key matrix

µPD16316

VFD-DISP

Video ADC

5146

DNM8602

Audio ADC

CS5333

CS4360

Audio

DVD L&R audio signals

DVD CVBS signal

Main board

4

AV board

Page 7

EXPLODED VIEW

55

Page 8

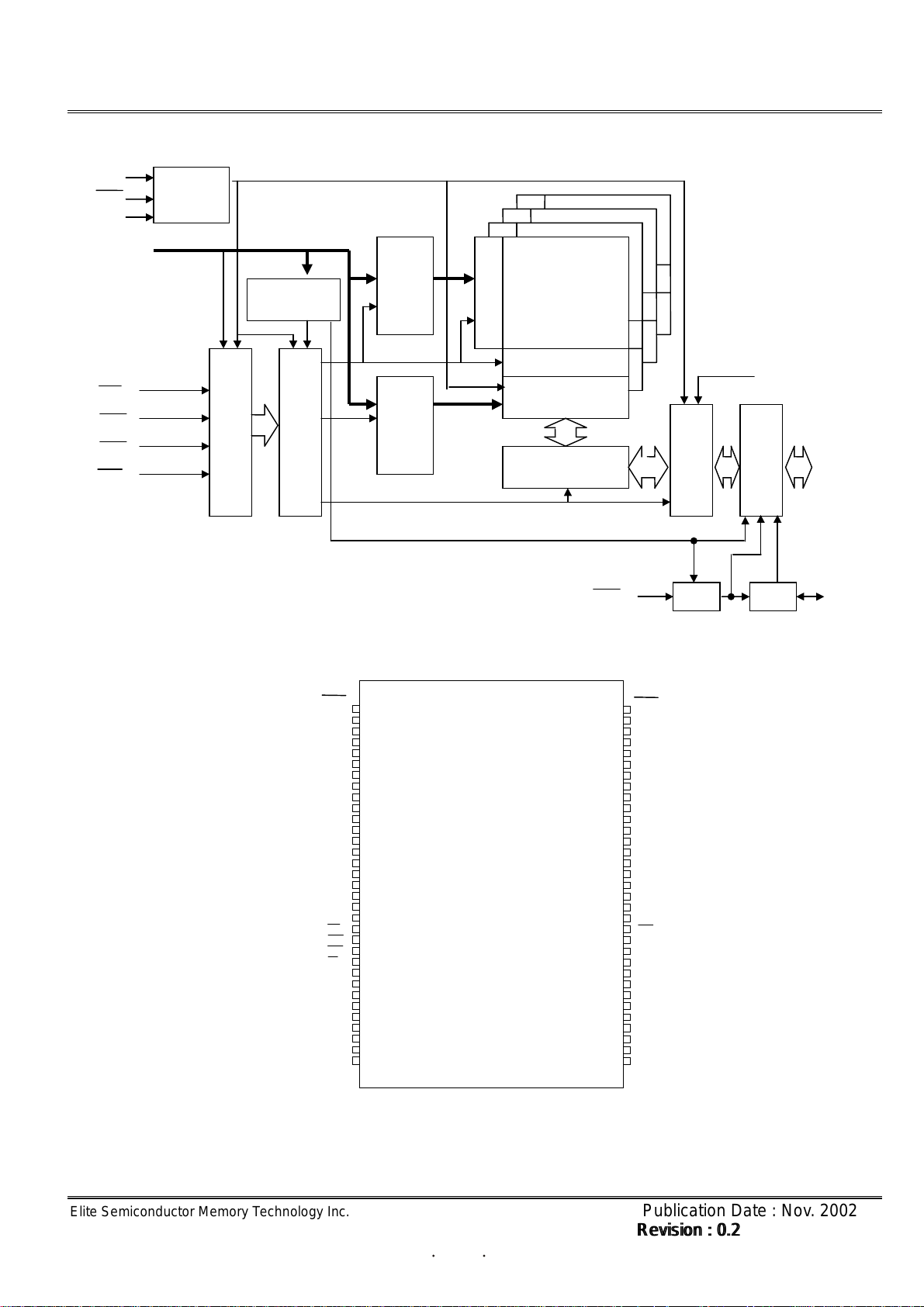

FUNCTIONAL BLOCK DIAGRAM

A19 - A

0

CE#

OE#

WE#

X-Decoder

Address Buffer & Latches

Control Logic

16 Megabit Multi-Purpose Flash

SST39VF160Q / SST39VF160

Advance Information

16,777,216 bit

EEPROM

Cell Array

Y-Decoder

I/O Buffers and Data Latches

DQ15 - DQ

V

0

DDQ

329 ILL B1.2

A15

A14

A13

A12

A11

A10

A19

WE#

A18

A17

1

2

3

4

5

6

A9

7

A8

8

9

NC

10

11

NC

12

NC

13

NC

14

NC

15

16

17

A7

18

A6

19

A5

20

A4

21

A3

22

A2

23

A1

24

Standard Pinout

T op Vie w

Die Up

SST39VF160Q

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

329 ILL F01.2

A16

V

V

DQ15

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE#

V

CE#

A0

FIGURE 1: PIN ASSIGNMENTS FOR 48-PIN TSOP PACKAGES

123456

A

A3 A7 NC WE# A9 A13

B

A4 A17 NC NC A8 A12

C

A2 A6 A18 NC A10 A14

D

A1 A5 NC A19 A11 A15

E

A0 DQ0 DQ2 DQ5 DQ7 A16

F

CE# DQ8 DQ10 DQ12 DQ14 V

G

OE# DQ9 DQ11 V

H

V

DQ1 DQ3 DQ4 DQ6 V

SS

SST39VF160Q

DD

DQ13 DQ15

DDQ

SS

329 ILL F02.4

DDQ

SS

DD

SS

A15

A14

A13

A12

A11

A10

A19

WE#

A18

A17

NC

NC

NC

NC

NC

A9

A8

A7

A6

A5

A4

A3

A2

A1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Standard Pinout

T op Vie w

Die Up

SST39VF160

123456

A

A3 A7 NC WE# A9 A13

B

A4 A17 NC NC A8 A12

C

A2 A6 A18 NC A10 A14

D

A1 A5 NC A19 A11 A15

E

A0 DQ0 DQ2 DQ5 DQ7 A16

F

CE# DQ8 DQ10 DQ12 DQ14 NC

G

OE# DQ9 DQ11 V

H

V

DQ1 DQ3 DQ4 DQ6 V

SS

SST39VF160

DD

DQ13 DQ15

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

329 ILL F01a.0

SS

329 ILL F02a.0

A16

NC

V

SS

DQ15

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

DD

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE#

V

SS

CE#

A0

FIGURE 2: PIN ASSIGNMENTS FOR 48-PIN TFBGA

6

Page 9

ESMT

M13S128168A

45

45

;(

45-45

2

2

66 PIN TSOP(II)

(400mil x 875mil)

(0.65 mm PIN PITCH)

Elite Semiconductor Memory Technology Inc.

7

Publication Date : Nov. 2002

Revision : 0.2

Revision : 0.2

Page 10

SLLS423D – JUNE 2000 – REVISED SEPTEMBER 2002

description (continued)

required for normal network operation regardless of the state of the PHY-LLC interface. When the interface is

in the reset or disabled state and LPS is again observed active, the PHY initializes the interface and returns it

to normal operation.

When the PHY-LLC interface is in the low-power disabled state, the TSB41AB1 automatically enters a

low-power mode if the port is inactive (disconnected, disabled, or suspended). In this low-power mode, the

TSB41AB1 disables its internal clock generators and also disables various voltage and current reference

circuits depending on the state of the port (some reference circuitry must remain active in order to detect new

cable connections, disconnections, or incoming TPBIAS, for example). The lowest power consumption (the

ultralow-power sleep mode) is attained when the port is either disconnected, or disabled with the port interrupt

enable bit cleared. The TSB41AB1 exits the low-power mode when the LPS input is asserted high or when a

port event occurs which requires that the TSB41AB1 become active in order to respond to the event or to notify

the LLC of the event (for example, incoming bias is detected on a suspended port, a disconnection is detected

on a suspended port, a new connection is detected on a nondisabled port, etc.). The SYSCLK output becomes

active (and the PHY-LLC interface is initialized and becomes operative) within 7.3 ms after LPS is asserted high

when the TSB41AB1 is in the low-power mode.

The PHY uses the C/LKON terminal to notify the LLC to power up and become active. When activated, the

C/LKON signal is a square wave of approximately 163-ns period. The PHY activates the C/LKON output when

the LLC is inactive and a wake-up event occurs. The LLC is considered inactive when either the LPS input is

inactive, as described above, or the LCtrl bit is cleared to 0. A wake-up event occurs when a link-on PHY packet

addressed to this node is received, or when a PHY interrupt occurs. The PHY deasserts the C/LKON output

when the LLC becomes active (both LPS active and the LCtrl bit set to 1). The PHY also deasserts the C/LKON

output when a bus reset occurs unless a PHY interrupt condition exists which would otherwise cause C/LKON

to be active.

PHP package terminal diagram

SYSCLK

CTL0

CTL1

D0

D1

D2

D3

D4

D5

D6

D7

PD

LREQ

DGND

DGND

47 46 45 44 4348 42 40 39 3841

1

2

3

4

5

6

7

8

9

10

11

12

14 15

LPS

DGND

C/LKON

16

13

PHP PACKAGE

(TOP VIEW)

DDDVDD

DV

XO

XI

TSB41AB1

17 18 19 20

ISO

PC1

PC2

PC0

DD

PLLGND

PLLV

FILTER1

22 23 24

21

DD

CPS

DV

TESTM

FILTER0

RESET

37

SE

SM

36

35

34

33

32

31

30

29

28

27

26

25

AGND

AV

DD

R1

R0

AGND

TPBIAS

TPA+

TPA–

TPB+

TPB–

AGND

AV

DD

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 11

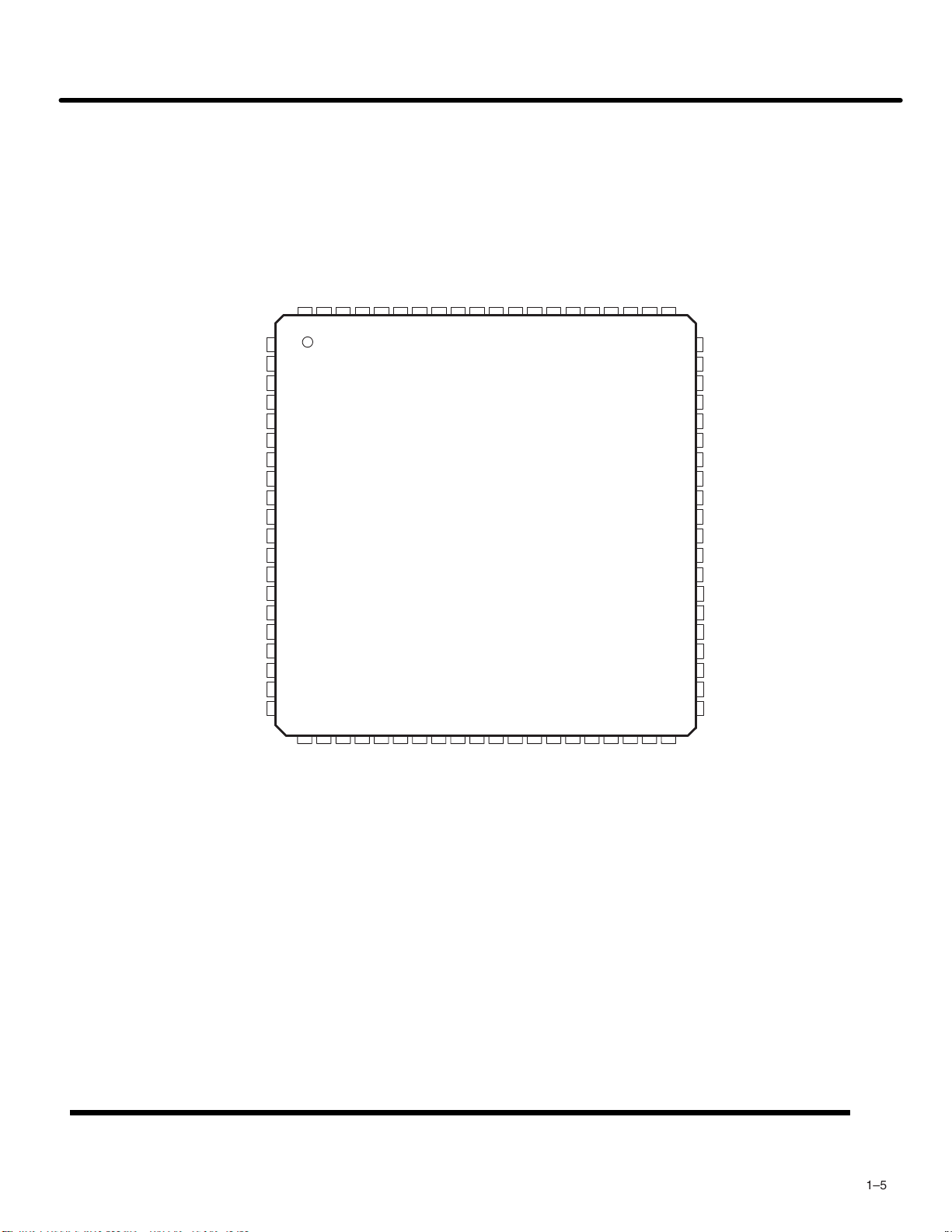

1.5 Functional Block Diagram

TVP5146

CVBS/

Pb/B/C

CVBS/

Y/G

CVBS/

Pr/R/C

CVBS/Y

VI_1_A

VI_1_B

VI_1_C

VI_2_A

VI_2_B

VI_2_C

VI_3_A

VI_3_B

VI_3_C

VI_4_A

Protection

Detector

Analog Front End

ADC1

ADC2

ADC3

ADC4

Sampling

Clock

Copy

M

U

X

Timing Processor

with Sync Detector

CVBS/Y/G

CVBS/Y

C

Y/G

Pb/B

Pr/R

VBI

Data

Slicer

Composite and S-Video Processor

Y/C

Separation

5-line

Adaptive

Comb

Gain/Offset

Y

C

Component

Luma

Processing

Chroma

Processing

Processor

Color

Space

Conversion

YCbCr

YCbCr

Host

Interface

Output

Formatter

Y[9:0]

C[9:0]

FSS

GPIO

XTAL1

XTAL2

PWDN

RESETB

AVID

DATACLK

FID

VS/VBLK

GLCO

HS/CS

DRDGDB

Figure 1–1. Functional Block Diagram

FSO

SCL

SDA

1–4

9

Page 12

1.6 Terminal Assignments

VI_1_A

CH1_A18GND

CH1_A18VDD

PLL_A18GND

PLL_A18VDD

XTAL2

XTAL1

PFP PACKAGE

(TOP VIEW)

VS/VBLK/GPIO

HS/CS/GPIO

FID/GPIO

C_0/GPIO

C_1/GPIO

DGND

DVDD

C_2/GPIO

C_3/GPIO

C_4/GPIO

C_5/GPIO

IOGND

IOVDD

TVP5146

VI_1_B

VI_1_C

CH1_A33GND

CH1_A33VDD

CH2_A33VDD

CH2_A33GND

VI_2_A

VI_2_B

VI_2_C

CH2_A18GND

CH2_A18VDD

A18VDD_REF

A18GND_REF

CH3_A18VDD

CH3_A18GND

VI_3_A

VI_3_B

VI_3_C

CH3_A33GND

CH3_A33VDD

79 78 77 76 7580 74 72 71 7073

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

22 23

24

VI_4_A

CH4_A33VDD

CH4_A33GND

25 26 27 28

SCL

AGND

DGND

CH4_A18VDD

CH4_A18GND

29

30 31 32 33

SDA

INTREQ

69 682167 66 65 64

34 35 36 37 38 39 40

DVDD

DGND

PWDN

RESETB

FSS/GPIO

63 62 61

IOVDD

AVID/GPIO

GLCO/I2CA

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

IOGND

DATACLK

C_6/GPIO/RED

C_7/GPIO/GREEN

C_8/GPIO/BLUE

C_9/GPIO/FSO

DGND

DVDD

Y_0

Y_1

Y_2

Y_3

Y_4

IOGND

IOVDD

Y_5

Y_6

Y_7

Y_8

Y_9

DGND

DVDD

Figure 1–2. Terminal Assignments Diagram

10

1–5

Page 13

TVP5146

1.7 Terminal Functions

Table 1–1. Terminal Functions

TERMINAL

NAME NUMBER

Analog Video

VI_1_A

VI_1_B

VI_1_C

VI_2_A

VI_2_B

VI_2_C

VI_3_A

VI_3_B

VI_3_C

VI_4_A

Clock Signals

DATACLK 40 O Line-locked data output clock.

XTAL1 74 I

XTAL2 75 O External clock reference output. Not connected if XTAL1 is driven by an external single-ended oscillator.

Digital Video

C[9:0]/

GPIO[9:0]

D_BLUE 58 I Digital BLUE input from overlay device

D_GREEN 59 I Digital GREEN input from overlay device

D_RED 60 I Digital RED input from overlay device

FSO 57 I Fast-switch overlay between digital RGB and any video

Y[9:0]

Miscellaneous Signals

FSS/GPIO 35 I/O

GLCO/I2CA 37 I/O

INTREQ 30 O Interrupt request

PWDN 33 I

RESETB 34 I Reset input, active low

80

1

2

7

8

9

16

17

18

23

57, 58,

59, 60,

63, 64,

65, 66,

69, 70

43, 44,

45, 46,

47, 50,

51, 52,

53, 54

I/O

VI_1_x: Analog video input for CVBS/Pb/B/C

VI_2_x: Analog video input for CVBS/Y/G

VI_3_x: Analog video input for CVBS/Pr/R/C

VI_4_A: Analog video input for CVBS/Y

I

Up to 10 composite, 4 S-video, and 2 composite or 3 component video inputs (or a combination thereof)

can be supported.

The inputs must be ac-coupled. The recommended coupling capacitor is 0.1 µF.

The possible input configurations are listed in the input select register at I2C subaddress 00h (see

Section 2.11.1).

External clock reference input. It may be connected to an external oscillator with a 1.8-V compatible clock

signal or a 14.31818-MHz crystal oscillator.

Digital video output of CbCr, C[9] is MSB and C[0] is LSB. Unused outputs can be left unconnected. Also,

these terminals can be programmable general-purpose I/O.

O

For the 8-bit mode, the two LSBs are ignored.

Digital video output of Y/YCbCr, Y[9] is MSB and Y[0] is LSB.

O

For the 8-bit mode, the two LSBs are ignored. Unused outputs can be left unconnected.

Fast-switch (blanking) input. Switching signal between the synchronous component video (YPbPr/RGB)

and the composite video input.

Programmable general-purpose I/O

Genlock control output (GLCO). Two Genlock data formats are available: TI format and real time control

(RTC) format.

During reset, this terminal is an input used to program the I2C address LSB.

Power down input:

1 = Power down

0 = Normal mode

DESCRIPTION

1–6

11

Page 14

Table 1–1. Terminal Functions (Continued)

TVP5146

TERMINAL

NAME NUMBER

Host Interface

SCL 28 I I2C clock input

SDA 29 I/O I2C data bus

Power Supplies

AGND 26 I Analog ground. Connect to analog ground.

A18GND_REF 13 I Analog 1.8-V return

A18VDD_REF 12 I Analog power for reference 1.8 V

CH1_A18GND

CH2_A18GND

CH3_A18GND

CH4_A18GND

CH1_A18VDD

CH2_A18VDD

CH3_A18VDD

CH4_A18VDD

CH1_A33GND

CH2_A33GND

CH3_A33GND

CH4_A33GND

CH1_A33VDD

CH2_A33VDD

CH3_A33VDD

CH4_A33VDD

DGND

DVDD

IOGND 39, 49, 62 I Digital power return

IOVDD 38, 48, 61 I Digital power. Connect to 3.3 V or less for reduced noise.

PLL_A18GND 77 I Analog power return

PLL_A18VDD 76 I Analog power. Connect to 1.8 V.

Sync Signals

HS/CS/GPIO 72 I/O

VS/VBLK/GPIO 73 I/O

FID/GPIO 71 I/O

AVID/GPIO 36 I/O

79

10

15

24

78

11

14

25

3

6

19

22

4

5

20

21

27, 32, 42,

56, 68

31, 41, 55,

67

I/O

I Analog 1.8-V return

I Analog power. Connect to 1.8 V.

I Analog 3.3-V return

I Analog power. Connect to 3.3 V.

I Digital return

I Digital power. Connect to 1.8 V.

Horizontal sync output or digital composite sync output

Programmable general-purpose I/O

Vertical sync output (for modes with dedicated VSYNC) or VBLK output

Programmable general-purpose I/O

Odd/even field indicator output. This terminal needs a pulldown resistor.

Programmable general-purpose I/O

Active video indicator output

Programmable general-purpose I/O

DESCRIPTION

121413151416151716

1–7

Page 15

Page 16

Page 17

Page 18

Page 19

Philips SemiconductorsProduct specification

Hex inverting Schmitt trigger 74HC/HCT14

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1, 3, 5, 9, 11, 13 1A to 6A data inputs

2, 4, 6, 8, 10, 12 1Y to 6Y data outputs

7 GND ground (0 V)

14 V

CC

positive supply voltage

Fig.1 Pin configuration. Fig.2 Logic symbol. Fig.3 IEC logic symbol.

FUNCTION TABLE

INPUT OUTPUT

nA nY

L

H

Notes

1. H = HIGH voltage level

L = LOW voltage level

APPLICATIONS

• Wave and pulse shapers

• Astable multivibrators

• Monostable multivibrators

Fig.4 Functional diagram. Fig.5 Logic diagram

(one Schmitt trigger).

H

L

17

Page 20

Philips Semiconductors Product specification

74ALVT163732.5V/3.3V 16-bit transparent D-type latch (3-State)

LOGIC SYMBOL

47 46 44 43

1

1D0 1D1 1D2 1D3

1LE

1OE

1Q0 1Q1 1Q2651Q3

32

36 35 33 32

2D02D21 2D2 2D3

2LE

2OE

2Q0 2Q1 2Q2 2Q3

1413 1716

48

25

24

41 40 38 37

1D4 1D5 1D6 1D7

1Q4 1Q5 1Q6

30 29 27 26

2D4 2D5 2D6 2D7

2Q4 2Q5 2Q6 2Q7

98

2019 2322

1Q7

1211

SA00044

PIN DESCRIPTION

PIN NUMBER SYMBOL FUNCTION

47, 46, 44, 43, 41, 40, 38, 37,

36, 35, 33, 32, 30, 29, 27, 26

2, 3, 5, 6, 8, 9, 11, 12, 13,

14, 16, 17, 19, 20, 22, 23

1, 24 1OE, 2OE

48, 25 1LE, 2LE

4, 10, 15, 21, 28, 34, 39, 45 GND Ground (0V)

7, 18, 31, 42 V

1D0 – 1D7

2D0 – 2D7

1Q0 – 1Q7

2Q0 – 2Q7

CC

Data inputs

Data outputs

Output enable

inputs

(active-Low)

Enable inputs

(active-High)

Positive

supply voltage

LOGIC SYMBOL (IEEE/IEC)

1OE

1LE

2OE

2LE

1D1

1D2

1D3

1D4

1D5

1D6

1D7

1D8

2D1

2D2

2D3

2D4

2D5

2D6

2D7

2D8

1

48

24

25

47

46

44

43

41

40

38

37

36

35

33

32

30

29

27

26

1EN

C3

2EN

C4

3D

4D

PIN CONFIGURATION

1

1OE

2

1Q0

1Q1

3

GND

4

1Q2

5

6

1Q3

7

V

CC

8

1Q4

1Q5

9

GND

10

1Q6

11

1Q7

12

2Q0

13

2Q1

14

GND

15

16

2Q2

2Q3

17

18

V

CC

2Q4

19

20

2Q5

21

GND

22

2Q6

23

2Q7

24

2OE

1 ∇

2 ∇

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

SA00043

1LE

1D0

1D1

GND

1D2

1D3

V

CC

1D4

1D5

GND

1D6

1D7

2D0

2D1

GND

2D2

2D3

V

CC

2D4

2D5

GND

2D6

2D7

2LE

2

1Q1

3

1Q2

5

1Q3

6

1Q4

8

1Q5

9

1Q6

11

1Q7

12

1Q8

13

2Q1

14

2Q2

16

2Q3

17

2Q4

19

2Q5

20

2Q6

22

2Q7

23

2Q8

SW00010

18

Page 21

2

C BUS Control 5-Input 2-Output AV Switch MM1313

MITSUMI

I

I2C BUS Control 5-Input 2-Output AV Switch

Monolithic IC MM1313

Outline

This IC is a 5-input 2-output AV switch with I2C control, developed for use in televisions. Two outputs enable

it to support two screens or "picture-in-picture".

Features

1. Serial control by I2C bus.

2. 5-inputs, 2-outputs.

3. Video and audio system switches can be controlled independently.

4. 6dB amplifier built in to video system.

5. Built-in Y/C MIX circuit.

6. Slave address can be changed : 90H or 92H.

7. Audio muting possible by external pin.

8. Maintains high impedance even when I

9. Built-in 3 value discrimination function.

10.On-chip power ON reset function.

11.Two types of audio input impedance : 60kΩ and 30kΩ.

MM1313AD : 60kΩ MM1313BD : 30kΩ

12.Supports 2-screen or P-IN-P TV.

2

C BUS line (SDA, SCL) power supply is off.

Package

SDIP-42A (MM1313AD, MM1313BD)

Applications

1. Televisions

2. Other video equipment

19

Page 22

MITSUMI

Equivalent Block Diagram

2

C BUS Control 5-Input 2-Output AV Switch MM1313

I

20

Page 23

MITSUMI

Pin Function

2

C BUS Control 5-Input 2-Output AV Switch MM1313

I

Pin No.

Name

41 MTV-V

1 V1

7 V2

13 V3

27 STV

3 V1

9 V2

31 Y

5 V1-C

11 V2

29 C

42 MTV-L

2 V1

8 V2

14 V3

25 STV

40 MTV

4 V1

10 V2

16 V3

26 STV

-

-

-

-

-

IN1

-

IN1

-

-

-

-

-

-

Internal equivalent circuit diagram

Pin No.

Name

Internal equivalent circuit diagram

33 LOUT1

V

V

V

-

V

22 L

32 R

24 R

OUT2

OUT1

OUT2

Y

Y

36 BIAS

C

19 SCL

L

L

L

-

L

-

R

R

R

R

-

R

34 VOUT1

23 V

OUT2

37 YOUT1

39 C

OUT1

20 SDA

6 S1

12 S2

21 ADR

28 Mute

21

Page 24

MITSUMI

2

C BUS Control 5-Input 2-Output AV Switch MM1313

I

Absolute Maximum Ratings

Item Symbol Ratings Units

Storage temperature T

Operating temperature T

Power supply voltage V

Allowable power dissipation Pd 850 mW

Electrical Characteristics

Item Symbol

Operating power supply voltage

Current consumption I

V

OUT1 output

Voltage gain G

Frequency characteristics F

Differential gain DG

Differential phase DP

Input dynamic range D

V

OUT2 output

Voltage gain G

Frequency characteristics F

Differential gain DG

Differential phase DP

Input dynamic range D

YOUT1 output

Voltage gain

Frequency characteristics

Differential gain DGY TP2

Differential phase DPY TP2

(Ta=25°C, VCC=9V)

VCC 8910V

CC 38 VCC=9V, no signal, no load 40 52 mA

V1 TP1 Sine wave 1.0VP-P, 100kHz 5.5 6.0 6.5 dB

V1 TP1

V1 TP1

V1 TP1

V1 SG1~3 Maximum input for total higher 1.6 1.9 VP-P

V2 TP6 Sine wave 1.0VP-P, 100kHz 5.5 6.0 6.5 dB

V2 TP6

V2 TP6

V2 TP6

V2 SG1~3 Maximum input for total higher 1.6 1.9 VP-P

G

Y1 TP2

G

Y2 TP2

Y1 TP2

F

F

Y2 TP2

(Ta=25°C)

Measure

ment pin

STG

OPR

CC 12 V

-

40~+125

-

20~+75

Conditions (unless otherwise indicated,

Measurement Circuit Figure 1)

Sine wave 1.0V

Vn-V : Staircase 1V

P-P

, 10MHz/100kHz-1.0 0 1.0 dB

P-P

°

C

°

C

Min. Typ. Max. Units

APL=10~90%

Vn-Y : Staircase (luminance signal) 1V

Vn-C : Chroma signal 0.3V

P-P

P-P

-

30 3 %

APL=10~90%

Vn-V : Staircase 1V

P-P

APL=10~90%

Vn-Y : Staircase (luminance signal) 1V

Vn-C : Chroma signal 0.3V

P-P

P-P

-

3 0 3 deg

APL=10~90%

Sine wave 100kHz

harmonic distortion factor < 1.0%

Sine wave 1.0V

10MHz/100kHz

Vn-V : Staircase 1V

P-P

P-P

-

1.0 0 1.0 dB

APL=10~90%

Vn-Y : Staircase (luminance signal) 1V

Vn-C : Chroma signal 0.3V

P-P

P-P

-

30 3 %

APL=10~90%

Vn-V : Staircase 1V

P-P

APL=10~90%

Vn-Y : Staircase (luminance signal) 1V

Vn-C : Chroma signal 0.3V

P-P

P-P

-

3 0 3 deg

APL=10~90%

Sine wave 100kHz

harmonic distortion factor < 1.0%

Vn-Y : Sine wave 1.0V

YIN1 : Sine wave 2.0V

-

Y : Sine wave 1.0VP

Vn

10MHz/100kHz

Y

IN1 : Staircase 2.0VP-P

10MHz/100kHz

Vn-Y : Staircase 1V

APL=10~90%

Y

IN1: Staircase 2VP-P

P-P

, 100kHz

P-P

, 100kHz-0.5 0 0.5

-

P

P-P

5.5 6.0 6.5

-

1.0 0 1.0

-

1.0 0 1.0

-

30 3 %

APL=10~90%

Vn-Y : Staircase 1V

APL=10~90%

IN1 : Staircase 2VP-P

Y

P-P

-

3 0 3 deg

APL=10~90%

dB

dB

22

Page 25

MITSUMI

2

C BUS Control 5-Input 2-Output AV Switch MM1313

I

Item Symbol

D

Measure

ment pin

Y1 SG2 Maximum input for total higher 1.6 1.9

Input dynamic range

DY2 SG4 Maximum input for total higher 3.2 3.8

Output impedance Z

C

OUT1 output

Voltage gain

OYC150Ω

C1 TP3

G

G

C2 TP3

F

C1 TP3

Frequency characteristics

C2 TP3

F

Differential gain DG

Differential phase DP

C TP3

C TP3

D

C1 SG3 Maximum input for total higher 2.75 3.25

Input dynamic range

C2 SG5 Maximum input for total higher 5.5 6.5

D

Input impedance Z

Output impedance Z

OUT1 output

L

Voltage gain

Frequency characteristics F

Total higher harmonic distortion

Input dynamic range D

IC Vn

OC150Ω

G

L11 TP4 b7=0, Sine wave 2.5VP-P, 1kHz

G

L12 TP4 b7=1, Sine wave 2.5VP-P, 1kHz

L1 TP4 Sine wave 2.5VP-P, 1MHz/1kHz

1 TP4 Sine wave 2.5VP

THDL

L1 SG6 Maximum input for total higher 2.6 2.8 Vrms

Output offset voltage VOFFL133

Input impedance Z

Output impedance Z

L

OUT2 output

Voltage gain G

Frequency characteristics F

Total higher harmonic distortion

Input dynamic range D

IL1 426078kΩ

OL1 120 Ω

L2 TP7 Sine wave 2.5VP-P, 1kHz

L2 TP7 Sine wave 2.5VP-P, 1MHz/1kHz

THDL2 TP7 Sine wave 2.5VP

L2 SG6 Maximum input for total higher 2.6 2.8 Vrms

Output offset voltage VOFFL222

Output impedance Z

R

OUT1 output

Voltage gain

Frequency characteristics F

Total higher harmonic distortion

Input dynamic range D

OL2 120 Ω

R11 TP5 b7=0, Sine wave 2.5VP-P, 1kHz

G

G

R12 TP5 b7=1, Sine wave 2.5VP-P, 1kHz

R1 TP5 Sine wave 2.5VP-P, 1MHz/1kHz

R1 TP5 Sine wave 2.5VP-P, 1kHz 0.03 0.1 %

THD

R1 SG7 Maximum input for total higher 2.6 2.8 Vrms

Output offset voltage VOFFR132

Input impedance Z

Output impedance Z

IR1 426078kΩ

OR1 120 Ω

Conditions (unless otherwise indicated,

Measurement Circuit Figure 1)

Min. Typ. Max. Units

Vn-Y : Sine wave 100kHz

harmonic distortion factor < 1.0%

V

IN1 : Sine wave 100kHz

harmonic distortion factor < 1.0%

Vn-C : Sine wave 1.0V

CIN1 : Sine wave 2.0V

-

C : Sine wave 1.0VP

Vn

10MHz/100kHz

C

IN1 : Sine wave 2.0VP-P

10MHz/100kHz

IN1 : Staircase 2VP-P

C

APL=10~90%

C

IN1 : Staircase 2VP-P

APL=10~90%

P-P

, 100kHz

P-P

, 100kHz-0.5 0 0.5

-

P

5.5 6.0 6.5

-

1.0 0 1.0

-

1.0 0 1.0

-

30 3 %

-

3 0 3 deg

Vn-C : Sine wave 100kHz

harmonic distortion factor < 1.0%

CIN1: Sine wave 100kHz

harmonic distortion factor < 1.0%

-

C, CIN1 101520kΩ

-

6.5-6.0-5.5

-

0.5 0.0 0.5

-

3.0 0 1.0 dB

-

P, 1kHz 0.03 0.1 %

Sine wave 1kHz

harmonic distortion factor < 0.5%

L

OUT1 pin DC difference during

SW switching

-

0.5 0.0 0.5 dB

-

3.0 0 1.0 dB

-

P, 1kHz 0.03 0.1 %

Sine wave 1kHz

harmonic distortion factor < 0.5%

OUT2 pin DC difference during

L

SW switching

-

6.5-6.0-5.5

-

0.5 0.0 0.5

-

3.0 0 1.0 dB

Sine wave 1kHz

harmonic distortion factor < 0.5%

R

OUT1 pin DC difference during

SW switching

P-P

V

dB

dB

V

P-P

dB

0 ±15 mV

0 ±15 mV

dB

0 ±15 mV

23

Page 26

MITSUMI

SDA

SCL

t

BUF

P PS

tHD:STA tHD:DAT tHIGH tSU:DAT tSU:STA tSU:STD

tLOW

Sr

t

R tF

2

C BUS Control 5-Input 2-Output AV Switch MM1313

I

Item Symbol

Measure

ment pin

ROUT2 output

Voltage gain G

Frequency characteristics F

Total higher harmonic distortion

Input dynamic range D

R2 TP8 Sine wave 2.5VP-P, 1kHz

R2 TP8 Sine wave 2.5VP-P, 1MHz/1kHz

THDR2 TP8 Sine wave 2.5VP

R2 SG7 Maximum input for total higher 2.6 2.8 Vrms

Output offset voltage VOFFR224

Output impedance Z

OR2 120 Ω

Crosswalk

V

OUT 1 CTV1 TP1

OUT 2 CTV2 TP2

V

Y

OUT 1 CTY1 TP3

OUT 1 CTC1 TP6

C

L

OUT 1 CTL1 TP4

OUT 2 CTL2 TP5 Measurement Circuit Figure 2

L

R

OUT 1 CTR1 TP7 1kHz, 2.5VP-P

R

OUT 2 CTR2 TP8

Video I/O Pin Voltage

Input pin voltage V

VIP No signal, no load 4.6 4.9 5.2 V

VOP

V

Output pin voltage

V

SOP

Audio I/O Pin Voltage

Input pin voltage V

Output pin voltage V

AIP No signal, no load 4.0 4.3 4.6 V

AOP No signal, no load 3.9 4.2 4.5 V

Logic section (Refer to figure below)

Input voltage L V

Input voltage H V

Low level output voltage (SDA)

High level input current I

Low level input current I

Clock frequency f

Data transmission waiting time

SCL start hold time t

SCL low level hold time t

SCL high level hold time t

SCL start set-up time t

SDA data hold time t

SDA data set-up time t

SCL rise time t

SCL fall time t

SCL stop set-up time t

IL I

IH

VOL SDA for 3mA inflow 0.0 0.4 V

IH when SDA, SCL=4.5V impressed

IL when SDA, SCL=0.4V impressed

SCL 100 kHz

BUF 4.7 µS

t

HD;STA 4.0 µS

LOW 4.7 µS

HIGH 4.0 µS

SU;STA 4.7 µS

HD;DAT 200 nS

SD;DAT 250 nS

R 1000 nS

F 300 nS

SU;STO 4.0 µS

Conditions (unless otherwise indicated,

Measurement Circuit Figure 1)

-

P, 1kHz 0.03 0.1 %

Min. Typ. Max. Units

-

0.5 0.0 0.5 dB

-

3.0 0 1.0 dB

Sine wave 1kHz

harmonic distortion factor < 0.5%

R

OUT2 pin DC difference during

switching

Measurement Circuit Figure 2

for SG1 input : 4.43MHz, 1V

for SG2 input : 4.43MHz, 0.5V

VOUT1 pin, VOUT2 pin

No signal, no load

YOUT1 pin, COUT1 pin

No signal, no load

2

C logic low level discrimination value 0.0 1.5 V

2

I

Clogic high level discrimination value 3.0 5.0 V

P-P

P-P

4.1 4.4 4.7 V

3.3 3.6 3.9 V

-

-

0 ±15 mV

-

60-53 dB

-

60-53 dB

-

60-53 dB

-

60-53 dB

-

90-80 dB

-

90-80 dB

-

90-80 dB

-

90-80 dB

10 +10 µA

10 +10 µA

I2C BUS BUS Control Signal

24

Page 27

MITSUMI

Measurement Circuit

Measurement Circuit 1

2

C BUS Control 5-Input 2-Output AV Switch MM1313

I

25

Page 28

MITSUMI

Measurement Circuit 2 (Crosstalk measurement)

2

C BUS Control 5-Input 2-Output AV Switch MM1313

I

26

Page 29

2

SDA

SCL

S

123456 78A123 8A P

S:Start Condition

P:Stop Condition

A:Acknowledge

C BUS Control 5-Input 2-Output AV Switch MM1313

MITSUMI

I

I2C BUS

The I2C BUS is a BUS system developed by Philips for internal use in equipment. Data transmission is carried

out by the two SDA and SCL lines, in byte units, with the MSB first from start condition.

[Control Register]

The control register contains data sent from the master in order to determine the status of each switch.

S

Slave address

1001000/10

R/W

A

Control register 1

b7 b6 b5 b4 b3 b2 b1 b0

A

Control register 2

b7 b6 b5 b4 b3 b2 b1 b0

AP

Address byte Control data

The data format is set as shown in the figure above. The first 7 bits in the address byte are allocated to the

slave address, and the remaining 1 bit is allocated to the read/write bit. The read/write bit is set at 0 when

using as a control register.

The MM1313 slave address can be selected as 90H/92H depending on the status of the ADR pin. When ADR

pin is low it is 90H.

The relationship between the control register bits and switch control is as shown below.

b7 b6 b5 b4 b3 b2 b1 b0

Audio

S/Comp

Video-Select Audio-Select

Gain Select

The control register bits are reset to 0 when power is applied.

MM1313 control is carried out by the 3-byte structure of the 1 address byte and 2 control data bytes. The first

byte in the control data is control data for output 1, and the remaining 1 byte is control data for output 2.

All of the remaining data (fourth byte and after) are ignored.

Refer to the separate tables for details on switch control.

27

Page 30

2

Reset released

Reset status

Undefined

0.6V 4.3V 5.4V V

CC

C BUS Control 5-Input 2-Output AV Switch MM1313

MITSUMI

I

[Status Register]

The status register contains data for sending device status to the master.

S

A

Slave address R/W

Status register

NA P

1001000/11 b7b6b5b4b3b2b1b0

Address byte Status data

The data format is set as shown in the figure above. The first 7 bits in the address byte are allocated to the

slave address, and the remaining 1 bit is allocated to the read/write bit. The read/write bit is set at 1 when

using as a status register.

The MM1313 slave address can be selected as 91H/93H depending on the status of the ADR pin. When the

ADR pin is low it is 91H. However, the confirmation response after completion of the status register should be

non-acknowledge.

The status register output data as shown below.

b7 b6 b5 b4 b3 b2 b1 b0

P-ON S1 S1 S2 S2

RESET

OPEN SEL OPEN SEL

P-ON RESET : Returns 1 for power on reset. However once data read begins, 0 is returned next.

S1/S2 OPEN : Returns 0 when the S1/S2 pin is not open, and returns 1 when the S1/S2 pin is open

S1/S2 SEL : Returns 0 when the S1/S2 pin is not grounded, and returns 1 when the S1/S2 pin is grounded.

S1/S2 OPEN, SEL have 3-value discrimination, and the combinations are as shown below.

S1/S2 pin DC voltage S1/S2 OPEN S1/S2 SEL

0.8V or less 01

1.3V or more, 3.5V or less

00

4.5V or more 10

[Power On Reset]

Power on reset is built in to reset each control register to 0 when power is turned on.

Power on reset threshold has hysteresis as shown in the figure below. The IC power on reset status can be

discriminated by reading the status register P-ON RESET.

28

Page 31

MITSUMI

Switch Control Table

2

C BUS Control 5-Input 2-Output AV Switch MM1313

I

1. Video Output 1

b6 b5 b4 b3 VOUT1YOUT1COUT1

0000 Mute Mute Mute

0001MTV

0010 V1

0011 V2

0100 V3

0101 STV

10

01

11

1000 Mute Mute Mute

1001MTV

1010V1

1011V2

1100 V3

1101 STV

10

11

11

-

VYIN1CIN1

-

VYIN1CIN1

-

VYIN1CIN1

-

VYIN1CIN1

-

VYIN1CIN1

Mute Mute Mute

-

VYIN1CIN1

-

Y+C V1-YV1

-

Y+C V2-YV2

-

VYIN1CIN1

-

VYIN1CIN1

Mute Mute Mute

2. Video Output 2

b6 b5 b4 b3 VOUT2

0000 Mute

0001MTV

0010 V1

0011 V2

0100 V3

0101 STV

01

1000 Mute

1001MTV

-

C

-

C

1010V1

1011V2

1100 V3

1101 STV

11

10

11

10

11

-

-

-

Mute

-

Y+C

-

Y+C

-

Mute

-

V

V

V

V

-

V

-

V

V

-

V

3. Audio Output 1

Mute pin b2 b1 b0 LOUT1ROUT1

0 0 0 Mute Mute

001MTV

010 V1

1.5V or less 011 V2

(OPEN) 100 V3

101 STV

10

1

11

3.0V or more

---

-

L MTV-R

-

LV1

-

LV2

-

LV3

-

L STV-R

Mute Mute

Mute Mute

5. Audio Output 2

Mute pin b2 b1 b0 LOUT2ROUT2

0 0 0 Mute Mute

001MTV

010 V1

1.5V or less 011 V2

-

L MTV-R

-

LV1

-

LV2

4. Audio Output 1 Gain

Switching

b7 Output gain

0

-

R

-

R

-

R

-

R

-

R

1 0dB output

-

6dB output

(OPEN) 100 V3

101 STV

10

3.0V or more

1

11

---

Mute Mute

Mute Mute

-

LV3

-

L STV-R

29

-

R

Page 32

MITSUMI

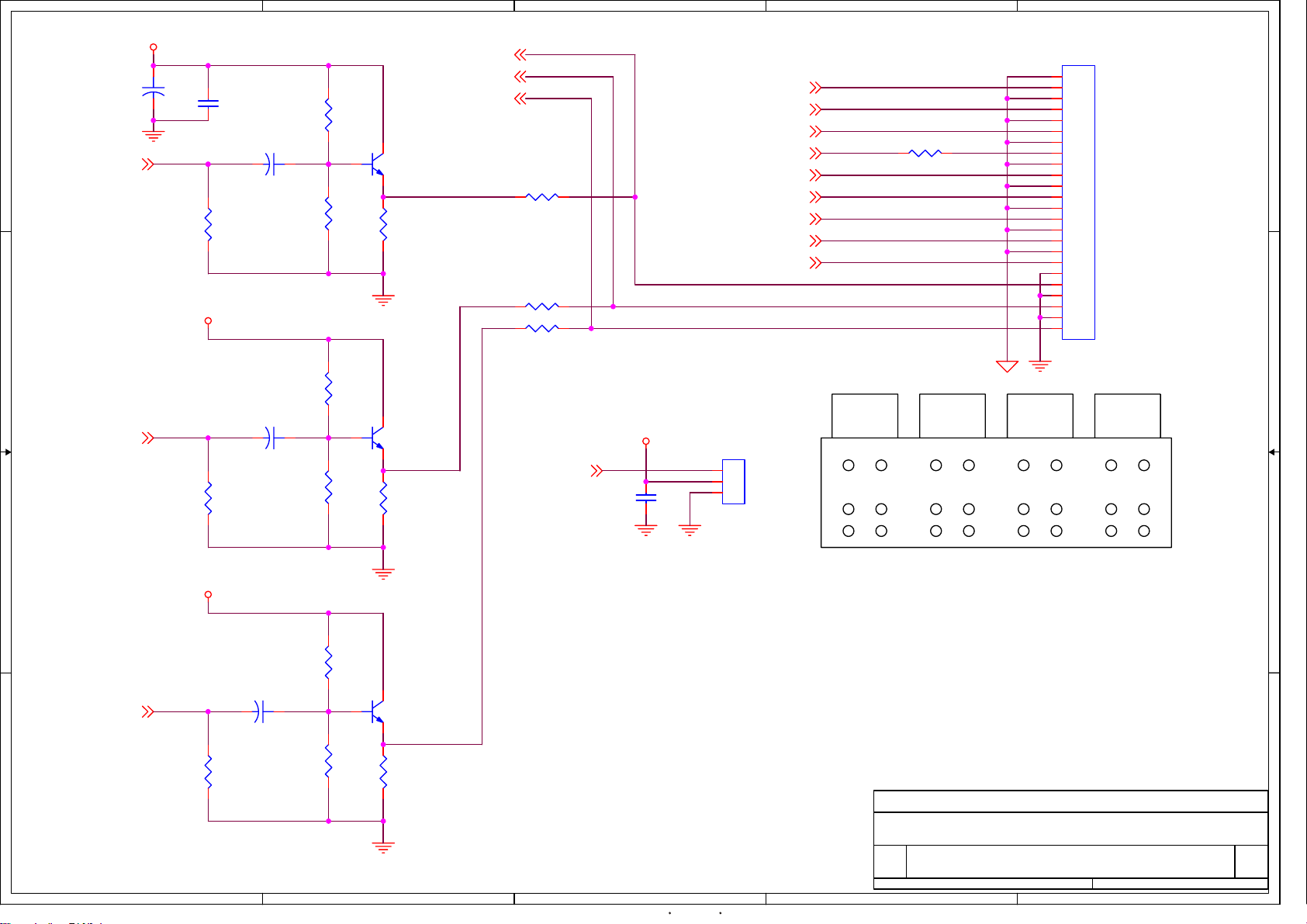

Application Circuit

2

C BUS Control 5-Input 2-Output AV Switch MM1313

I

Notes

OUT is set at 4.4V and CIN at 4.9V

1. V

Please note that capacitance polarity may vary depending on comb filter bias.

2. Each audio output can be muted by making pin 19 high. Mute is off when it is open or low.

30

Page 33

19-0463; Rev 0; 1/96

Low-Voltage, CMOS Analog

Multiplexers/Switches

_______________General Description

The MAX4051/MAX4052/MAX4053 and MAX4051A/

MAX4052A/MAX4053A are low-voltage, CMOS analog

ICs configured as an 8-channel multiplexer (MAX4051/A),

two 4-channel multiplexers (MAX4052/A), and three single-pole/double-throw (SPDT) switches (MAX4053/A).

The A-suffix parts are fully characterized for on-resistance

match, on-resistance flatness, and low leakage.

These CMOS devices can operate continuously with

dual power supplies ranging from ±2.7V to ±8V or a

single supply between +2.7V and +16V. Each switch

can handle rail-to-rail analog signals. The off leakage

current is only 0.1nA at +25°C or 5nA at +85°C

(MAX4051A/MAX4052A/4053A).

All digital inputs have 0.8V to 2.4V logic thresholds,

ensuring TTL/CMOS-logic compatibility when using

±5V or a single +5V supply.

________________________Applications

Battery-Operated Equipment

Audio and Video Signal Routing

Low-Voltage Data-Acquisition Systems

Communications Circuits

____________________________Features

♦ Pin Compatible with Industry-Standard

74HC4051/74HC4052/74HC4053

♦ Guaranteed On-Resistance:

100Ω with ±5V Supplies

♦ Guaranteed Match Between Channels:

6Ω (MAX4051A–MAX4053A)

12Ω (MAX4051–MAX4053)

♦ Guaranteed Low Off Leakage Currents:

0.1nA at +25°C (MAX4051A–MAX4053A)

1nA at +25°C (MAX4051–MAX4053)

♦ Guaranteed Low On Leakage Currents:

0.1nA at +25°C (MAX4051A–MAX4053A)

1nA at +25°C (MAX4051–MAX4053)

♦ Single-Supply Operation from +2.0V to +16V

Dual-Supply Operation from ±2.7V to ±8V

♦ TTL/CMOS-Logic Compatible

♦ Low Distortion: < 0.04% (600Ω)

♦ Low Crosstalk: < -90dB (50Ω)

♦ High Off Isolation: < -90dB (50Ω)

______________Ordering Information

PART

MAX4051ACPE

MAX4051ACSE

MAX4051ACEE 0°C to +70°C

Ordering Information continued at end of data sheet.

TEMP. RANGE PIN-PACKAGE

0°C to +70°C

0°C to +70°C

16 Plastic DIP

16 Narrow SO

16 QSOP

MAX4051/A, MAX4052/A, MAX4053/A

___________________________________Pin Configurations/Functional Diagrams

TOP VIEW

MAX4053

1

2

3

4

5

6

7

8

DIP/SO/QSOP

V+

16

COMB

15

COMC

14

NOC

13

NCC

12

11

ADDC

10

ADDB

9

ADDA

NO1

NO3

COM

NO7

NO5

INH

V-

GND

MAX4051

1

2

3

4

5

6

7

LOGIC

8

DIP/SO/QSOP

MAX4052

NO0B

NO1B

COMB

NO3B

NO2B

INH

GND

1

2

3

4

5

6

V-

7

LOGIC

8

V+

16

NO2

15

NO4

14

NO0

13

NO6

12

11

ADDC

10

ADDB

9

ADDA

V+

16

NO1A

15

NO2A

14

COMA

13

NO0A

12

11

NO3A

10

ADDB

9

ADDA

NOB

NCB

NOA

COMA

NCA

INH

V-

GND

DIP/SO/QSOP

31

Page 34

Low-Voltage, CMOS Analog

Multiplexers/Switches

ABSOLUTE MAXIMUM RATINGS

Voltages Referenced to GND

V+ ........................................................................-0.3V to +17V

V-..........................................................................+0.3V to -17V

V+ to V-................................................................-0.3V to +17V

Voltage into Any Terminal (Note 1)..........(V- - 2V) to (V+ + 2V)

Continuous Current into Any Terminal..............................±30mA

Peak Current, NO or COM

(pulsed at 1ms, 10% duty cycle).................................±100mA

Note 1: Signals on any terminal exceeding V+ or V- are clamped by internal diodes. Limit forward-diode current to maximum

current rating.

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

or 30mA (whichever occurs first)

Continuous Power Dissipation (T

Plastic DIP (derate 10.53mW/°C above +70°C)............842mW

Narrow SO (derate 8.70mW/°C above +70°C)..............696mW

QSOP (derate 8.00mW/°C above +70°C).....................640mW

CERDIP (derate 10.00mW/°C above +70°C)................800mW

Operating Temperature Ranges

MAX405_C_ E/MAX405_AC_E.............................0°C to +70°C

MAX405_E_ E/MAX405_AE_E...........................-40°C to +85°C

MAX405_MJE/MAX405_AMJE........................-55°C to +125°C

Storage Temperature Range.............................-65°C to +150°C

Lead Temperature (soldering, 10sec).............................+300°C

ELECTRICAL CHARACTERISTICS—Dual Supplies

(V+ = +4.5V to +5.5V, V- = -4.5V to -5.5V, TA= T

PARAMETER

ANALOG SWITCH

Analog Signal Range

COM–NO On-Resistance

COM–NO On-Resistance

Match Between Channels

(Note 3)

SYMBOL

, V

COM

R

ON

∆R

ON

NO

MAX4051/A, MAX4052/A, MAX4053/A

COM–NO On-Resistance

Flatness (Note 4)

NO Off Leakage Current

(Note 5)

R

FLAT(ON)

I

NO(OFF)

to T

MIN

V+ = 5V, V- = -5V, INO= 1mA,

V

= ±3V

COM

V+ = 5V, V- = -5V,

INO= 1mA,

V

= ±3V

COM

V+ = 5V, V- = -5V,

INO= 1mA,

V

= -3V, 0V, 3V

COM

V+ = 5.5V, V- = -5.5V,

VNO= 4.5V,

V

= -4.5V

COM

V+ = 5.5V, V- = -5.5V,

VNO= -4.5V,

V

= 4.5V

COM

, unless otherwise noted. Typical values are at TA= +25°C.)

MAX

CONDITIONS

MAX4051A,

MAX4052A,

MAX4053A

MAX4051,

MAX4052,

MAX4053

MAX4051A,

MAX4052A,

MAX4053A

MAX4051,

MAX4052,

MAX4053

MAX4051A,

MAX4052A,

MAX4053A

C, E, M

TA= +25°C

C, E, M

TA= +25°C 6

C, E, M 12

TA= +25°C

C, E, M 18

TA= +25°C

C, E, M 15

TA= +25°C

C, E -10 10

M

TA= +25°C -0.1 0.002 0.1

C, E

M

= +70°C)

A

MIN TYP MAX

(Note 2)

60 100

125

12

10

-1 0.002 1

-100 100

-5 5

-100 100

UNITS

VV- V+V

Ω

Ω

Ω

nA

32

Page 35

Low-Voltage, CMOS Analog

Multiplexers/Switches

ELECTRICAL CHARACTERISTICS—Dual Supplies (continued)

(V+ = +4.5V to +5.5V, V- = -4.5V to -5.5V, TA= T

SYMBOLPARAMETER

COM Off Leakage

Current (Note 5)

COM On Leakage

Current (Note 5)

I

COM(OFF)

I

COM(ON)

to T

MIN

V+ = 5.5V, V- = -5.5V,

VNO= 4.5V,

V

COM

V+ = 5.5V, V- = -5.5V,

VNO= -4.5V,

V

COM

V+ = 5.5V, V- = -5.5V,

V

COM

, unless otherwise noted. Typical values are at TA= +25°C.)

MAX

CONDITIONS

= -4.5V

= 4.5V

= VNO= ±4.5V

MAX4051A

MAX4051

MAX4052A,

MAX4053A

MAX4052,

MAX4053

MAX4051A

MAX4051

MAX4052A,

MAX4053A

MAX4052,

MAX4053

MAX4051A

MAX4051

MAX4052A,

MAX4053A

MAX4052,

MAX4053

TA= +25°C -0.1 0.002 0.1

C, E

M -100 100

TA= +25°C

C, E -10 10

M

TA= +25°C

C, E

M

TA= +25°C

C, E -5 5

M

TA= +25°C -0.1 0.002 0.1

C, E

M -100 100

TA= +25°C

C, E -10 10

M

TA= +25°C -0.1 0.002 0.1

C, E

M

TA= +25°C

C, E

M

TA= +25°C -0.1 0.002 0.1

C, E

M -100 100

TA= +25°C

C, E -10 10

M

TA= +25°C -0.1 0.002 0.1

C, E

M

TA= +25°C

C, E

M

MIN TYP MAX

(Note 2)

-5 5

-1 0.002 1

-100 100

-0.1 0.002 0.1

-2.5 2.5

-100 100

-1 0.002 1

-50 50

-5 5

-1 0.002 1

-100 100

-2.5 2.5

-50 50

-1 0.002 1

-5 5

-50 50

-5 5

-1 0.002 1

-100 100

-2.5 2.5

-50 50

-1 0.002 1

-5 5

-50 50

MAX4051/A, MAX4052/A, MAX4053/A

UNITS

nA

nA

33

Page 36

Low-Voltage, CMOS Analog

Multiplexers/Switches

ELECTRICAL CHARACTERISTICS—Dual Supplies (continued)

(V+ = +4.5V to +5.5V, V- = -4.5V to -5.5V, TA= T

SYMBOLPARAMETER

DIGITAL I/O

ADD, INH Input Logic

Threshold High

ADD, INH Input Logic

Threshold Low

ADD, INH Input Current

Logic High or Low

SWITCH DYNAMIC CHARACTERISTICS

Turn-On Time (Note 6) Figure 3

Turn-Off Time (Note 6) Figure 3

Transition Time Figure 2

Break-Before-Make Delay Figure 4

NO Off Capacitance VNO= GND, f = 1MHz, Figure 7

COM Off Capacitance

Switch On Capacitance

Off Isolation

Channel-to-Channel

Crosstalk

POWER SUPPLY

IH

IL

IL

t

ON

t

OFF

TRANS

OPEN

NO(OFF)

COM(OFF)

(ON)

ISO

CT

MAX4051/A, MAX4052/A, MAX4053/A

I+V+ Supply Current INH = ADD = 0V or V+

I-V- Supply Current INH = ADD = 0V or V+

Note 2: The algebraic convention is used in this data sheet; the most negative value is shown in the minimum column.

Note 3: ∆R

Note 4: Flatness is defined as the difference between the maximum and minimum value of on-resistance as measured over the

Note 5: Leakage parameters are 100% tested at maximum-rated hot operating temperature, and guaranteed by correlation at

Note 6: Guaranteed by design, not production tested.

= R

ON

specified analog signal ranges; i.e., V

= +25°C.

T

A

ON(MAX)

- R

ON(MIN)

.

to T

MIN

V

, V

ADD

CL= 1nF, RS= 0Ω, VNO= 0V,

Figure 5

V

= GND, f = 1MHz, Figure 7

COM

V

= V

COM

Figure 7

CL= 15pF, RL= 50Ω, f = 100kHz,

VNO= 1V

CL= 15pF, RL= 50Ω, f = 100kHz,

VNO= 1V

= 3V to 0V and 0V to -3V.

NO

, unless otherwise noted. Typical values are at TA= +25°C.)

MAX

CONDITIONS

= V+, 0V

INH

= GND, f = 1MHz,

NO

, Figure 6

RMS

, Figure 6

RMS

MIN TYP MAX

(Note 2)

C, E, M V2.4V

C, E, M V0.8V

C, E, M µA-1 0.03 1IIH, I

TA= +25°C

C, E, M

TA= +25°C

C, E, M

TA= +25°C

TA= +25°C

TA= +25°C

TA= +25°C pF2C

TA= +25°C pF2C

TA= +25°C pF8C

TA= +25°C dB<-90V

TA= +25°C dB<-90V

C, E, M V±2.7 ±8V+, V-Power-Supply Range

TA= +25°C

C, E, M

TA= +25°C -1 0.1 1

C, E, M

50 175

40 150

210t

-1 0.1 1

-10

225

200

10

UNITS

ns

ns

ns75 250t

ns

pC210QCharge Injection (Note 6)

µA

µA

34

Page 37

Low-Voltage, CMOS Analog

Multiplexers/Switches

ELECTRICAL CHARACTERISTICS—Single +5V Supply

(V+ = +4.5V to +5.5V, V- = 0V, TA= T

SYMBOLPARAMETER

ANALOG SWITCH

Analog Signal Range

COM–NO On-Resistance

NO Off Leakage Current

(Note 5)

COM Off Leakage

Current (Note 5)

COM On Leakage

Current (Note 5)

DIGITAL I/O

ADD, INH Input Logic

Threshold High

ADD, INH Input Logic

Threshold Low

ADD, INH Input Current

Logic High or Low

POWER SUPPLY

COM

I

NO(OFF)

I

COM(OFF)

I

COM(ON)

, V

R

ON

V

IH

V

IL

IH, IIL

to T

MIN

NO

, unless otherwise noted. Typical values are at TA= +25°C.)

MAX

V+ = 5V, INO= 1mA,

V

= 3.5V

COM

V+ = 5.5V, VNO= 4.5V,

V

= 0V

COM

V+ = 5.5V, VNO= 0V,

V

= 4.5V

COM

V+ = 5.5V, VNO= 4.5V,

V

= 0V

COM

V+ = 5.5V, VNO= 0V,

V

= 4.5V or 0V

COM

V+ = 5.5V,

V

= VNO= 4.5V

COM

ADD, VINH

INH = ADD = 0V or V+ µAI+V+ Supply Current

CONDITIONS

MAX4051/A

MAX4052/A,

MAX4053/A

MAX4051/A

MAX4052/A,

MAX4053/A

MAX4051/A

MAX4052/A,

MAX4053/A

= V+, 0V µAI

MIN TYP MAX

(Note 2)

C, E, M

TA= +25°C

C, E, M

TA= +25°C -1 0.002 1

C, E

M

TA= +25°C

C, E

M

TA= +25°C -1 0.002 1

C, E

M -100 100

TA= +25°C

C, E -5 5

M

TA= +25°C -1 0.002 1

C, E

M -100 100

TA= +25°C

C, E -5 5

M

TA= +25°C

C, E -10 10

M

TA= +25°C -1 0.002 1

C, E

M

C, E, M 2.4

C, E, M 0.8

C, E, M -1 0.03 1V

TA= +25°C -1 1

C, E, M 10

V- V+V

125 225

280

-10 10

-100 100

-1 0.002 1

-10 10

-100 100

-10 10

-1 0.002 1

-50 50

-10 10

-1 0.002 1

-50 50

-1 0.002 1

-100 100

-10 10

-100 100

MAX4051/A, MAX4052/A, MAX4053/A

UNITS

V

Ω

nA

nA

nA

V

V

35

Page 38

Low-Voltage, CMOS Analog

Multiplexers/Switches

ELECTRICAL CHARACTERISTICS—Single +5V Supply (continued)

(V+ = +4.5V to +5.5V, V- = 0V, TA= T

SYMBOLPARAMETER

DIGITAL I/OSWITCH DYNAMIC CHARACTERISTICS

Turn-On Time (Note 6) Figure 3

Turn-Off Time (Note 6)

Break-Before-Make Delay Figure 4

Off Isolation

Channel-to-Channel

Crosstalk

Note 2: The algebraic convention is used in this data sheet; the most negative value is shown in the minimum column.

Note 3: ∆R

Note 4: Flatness is defined as the difference between the maximum and minimum value of on-resistance as measured over the

Note 5: Leakage parameters are 100% tested at maximum-rated hot operating temperature, and guaranteed by correlation at

Note 6: Guaranteed by design, not production tested.

= R

ON

specified analog signal ranges; i.e., V

= +25°C.

T

A

ON(MAX)

- R

ON(MIN)

t

ON

t

OFF

OPEN

ISO

CT

to T

MIN

.

, unless otherwise noted. Typical values are at TA= +25°C.)

MAX

Figure 3

CL= 1nF, RS= 0Ω, VNO= 0V,

Figure 5

CL= 15pF, RL= 50Ω, f = 100kHz,

VNO= 1V

CL= 15pF, RL= 50Ω, f = 100kHz,

VNO= 1V

NO

, Figure 6

RMS

, Figure 6

RMS

= 3V to 0V and 0V to -3V.

CONDITIONS

TA= +25°C

C, E, M

TA= +25°C

C, E, M

TA= +25°C

TA= +25°C

TA= +25°C dB<-90V

TA= +25°C dB<-90V

MIN TYP MAX

(Note 2)

90 200

275

60 125

175

UNITS

ns

ns

ns30t

pC210QCharge Injection (Note 6)

MAX4051/A, MAX4052/A, MAX4053/A

36

Page 39

Low-Voltage, CMOS Analog

Multiplexers/Switches

ELECTRICAL CHARACTERISTICS—Single +3V Supply

(V+ = +3.0V to +3.6V, V- = 0V, TA= T

SYMBOLPARAMETER

ANALOG SWITCH

Analog Signal Range

COM–NO On-Resistance

NO Off Leakage Current

(Note 5)

COM Off Leakage

Current (Note 5)

COM On Leakage

Current (Note 5)

DIGITAL I/O

ADD, INH Input Logic

Threshold High

ADD, INH Input Logic

Threshold Low

ADD, INH Input Current

Logic High or Low

POWER SUPPLY

COM

I

NO(OFF)

I

COM(OFF)

I

COM(ON)

to T

MIN

, V

NO

R

ON

V

IH

V

IL

IH, IIL

I+ INH = ADD = 0V or V+V+ Supply Current µA

, unless otherwise noted. Typical values are at TA= +25°C.)

MAX

CONDITIONS

INO= 1mA, V+ = 3V,

V

= 1.5V

COM

V+ = 3.6V, VNO= 3V,

V

= 0V

COM

V+ = 3.6V, VNO= 0V,

V

= 3V

COM

MAX4051/A

V+ = 3.6V, VNO= 3V,

V

= 0V

COM

V+ = 3.6V, VNO= 0V,

V

= 3V

COM

V+ = 3.6V,

V

= VNO= 3V

COM

V

ADD, VINH

= V+, 0V

MAX4052/A,

MAX4053/A

MAX4051/A

MAX4052/A,

MAX4053/A

MAX4051/A

MAX4052/A,

MAX4053/A

MIN TYP MAX

(Note 2)

C, E, M

TA= +25°C

C, E, M

TA= +25°C

C, E

M

TA= +25°C

C, E

M

TA= +25°C -1 0.002 1

C, E

M -100 100

TA= +25°C

C, E -5 5

M

TA= +25°C -1 0.002 1

C, E

M -100 100

TA= +25°C

C, E -5 5

M

TA= +25°C

C, E -10 10

M

TA= +25°C

C, E

M

C, E, M 2.4

C, E, M 0.8

C, E, M -1 0.03 1I

TA= +25°C -1 1

C, E, M 10

V- V+V

250 525

700

-1 0.002 1

-10 10

-100 100

-1 0.002 1

-10 10

-100 100

-10 10

-1 0.002 1

-50 50

-10 10

-1 0.002 1

-50 50

-1 0.002 1

-100 100

-1 0.002 1

-10 10

-100 100

MAX4051/A, MAX4052/A, MAX4053/A

UNITS

V

Ω

nA

nA

nA

nA

V

V

µA

nA

37

Page 40

Low-Voltage, CMOS Analog

Multiplexers/Switches

ELECTRICAL CHARACTERISTICS—Single +3V Supply (continued)

(V+ = +3.0V to +3.6V, V- = 0V, TA= T

SYMBOLPARAMETER

DIGITAL I/OSWITCH DYNAMIC CHARACTERISTICS

Turn-On Time (Note 6) Figure 3

Turn-Off Time (Note 6)

Break-Before-Make Delay Figure 4

Off Isolation

Channel-to-Channel

Crosstalk

Note 2: The algebraic convention is used in this data sheet; the most negative value is shown in the minimum column.

Note 3: ∆R

Note 4: Flatness is defined as the difference between the maximum and minimum value of on-resistance as measured over the

Note 5: Leakage parameters are 100% tested at maximum-rated hot operating temperature, and guaranteed by correlation at

Note 6: Guaranteed by design, not production tested.

= R

ON

specified analog signal ranges; i.e., V

= +25°C.

T

A

ON(MAX)

- R

ON(MIN)

t

ON

t

OFF

OPEN

ISO

CT

to T

MIN

.

, unless otherwise noted. Typical values are at TA= +25°C.)

MAX

Figure 3

CL= 1nF, RS= 0Ω, VNO= 0V,

Figure 5

CL= 15pF, RL= 50Ω, f = 100kHz,

VNO= 1V

CL= 15pF, RL= 50Ω, f = 100kHz,

VNO= 1V

NO

, Figure 6

RMS

, Figure 6

RMS

= 3V to 0V and 0V to -3V.

CONDITIONS

TA= +25°C

C, E, M

TA= +25°C

C, E, M

TA= +25°C

TA= +25°C

TA= +25°C dB<-90V

TA= +25°C dB<-90V

MIN TYP MAX

(Note 2)

180 600

700

100 300

400

UNITS

ns

ns

ns90t

pC110QCharge Injection (Note 6)

MAX4051/A, MAX4052/A, MAX4053/A

38

Page 41

Low-Voltage, CMOS Analog

Multiplexers/Switches

__________________________________________Typical Operating Characteristics

(V+ = +5V, V- = -5V, GND = 0V, TA= +25°C, unless otherwise noted.)

ON-RESISTANCE vs. V

(DUAL SUPPLIES)

110

100

90

80

(Ω)

70

ON

R

60

50

40

30

-5 -3 1

ON-RESISTANCE vs. V

AND TEMPERATURE

180

160

140

120

(Ω)

ON

100

R

80

60

40

02

(SINGLE SUPPLY)

V+ = 5V

V- = 0V

153

5

Qj (pC)

COM

V± = ±3V

V± = ±5V

-1 3

V

(V)

COM

TA = +125°C

T

= +25°C

A

V

(V)

COM

COM

TA = +85°C

TA = -55°C

4

5-4 0-2 2 4

CHARGE INJECTION vs. V

V+ = 5V

V- = 0V

110

100

MAX4051/2/3-TOC1

90

80

(Ω)

70

ON

R

60

50

40

30

1000

MAX4051/2/3-TOC4

100

OFF-LEAKAGE (pA)

0.1

COM

ON-RESISTANCE vs. V

AND TEMPERATURE

(DUAL SUPPLIES)

V+ = 5V

V- = -5V

TA = +125°C

TA = +85°C

TA = +25°C

TA = -55°C

-5 -3 1

V+ = 5.5V

V- = -5.5V

10

1

-50 12525-25 0 7550 100

OFF-LEAKAGE vs.

TEMPERATURE (°C)

MAX4051/2/3-TOC7

-1 3

V

TEMPERATURE

COM

(V)

COM

10

1

I+, I- (nA)

MAX4051/2/3-TOC2

5-4 0-2 2 4

10,000

MAX4051/2/3-TOC5

SUPPLY CURRENT vs.

TEMPERATURE

V+ = 5V

V- = -5V

= VA = 0V, 5V

V

EN

ON-RESISTANCE vs. V

300

275

250

225

200

(Ω)

175

ON

R

150

125

100

75

50

02

1000

100

10

ON-LEAKAGE (pA)

1

0.1

-50 12525-25 0 7550 100

(SINGLE SUPPLY)

V- = 0V

153

V

COM

ON-LEAKAGE vs.

TEMPERATURE

V+ = 5.5V

V- = -5.5V

TEMPERATURE (°C)

I+

I-

V+ = 3V

(V)

MAX4051/2/3-TOC8

V+ = 5V

COM

4

MAX4051/A, MAX4052/A, MAX4053/A

MAX4051/2/3-TOC3

MAX4051/2/3-TOC6

V+ = 5V

V- = -5V

-5

-5 -3 1

-1 305-4 0-2 2 4

V

(V)

COM

39

0.1

-50 12525-25 0 7550 100

TEMPERATURE (°C)

Page 42

Low-Voltage, CMOS Analog

Multiplexers/Switches

____________________________Typical Operating Characteristics (continued)

(V+ = +5V, V- = -5V, GND = 0V, TA= +25°C, unless otherwise noted.)

FREQUENCY RESPONSE

0

-10

-20

INSERTION LOSS

-30

-40

-50

LOSS (dB)

-60

-70

-80

-90

0.01 0.1 1 10 100 300

OFF ISOLATION

ON PHASE

50Ω IN/OUT

FREQUENCY (MHz)

5

0

MAX4051/2/3-09

-5

-10

-15

-20

-25

-30

-35

-40

PHASE (DEGREES)

_____________________________________________________________Pin Descriptions

PIN

NO0B–NO3B—

NO0A–NO3A—

NAME

NO0–NO7—

COMB15

ADDA9

ADDB10

ADDC11

COMA4

COMC14

COM—

NOB1

NCB2

NOA3

NCA5

INH

GND8

NCC12

NOC13

Analog Switch Inputs 0–7—

Analog Switch Common—3

Analog Switch “B” Inputs 0–31, 2, 5, 4—

Analog Switch “B” Common3—

Analog Switch “B” Normally Open Input——

Analog Switch “B” Normally Closed Input——

Analog Switch “A” Normally Open Input——

Analog Switch “A” Normally Closed Input——

Digital Inhibit Input. Normally connect to GND. Can be driven

to logic high to set all switches off.

V-7

Negative Analog Supply Voltage Input. Connect to GND for

single-supply operation.

Ground. Connect to digital ground. (Analog signals have no

ground reference; they are limited to V+ and V-.)

Digital Address “A” Input99

Digital Address “B” Input1010

Digital Address “C” Input—11

Analog Switch “A” Inputs 0–312, 15, 14, 11—

Analog Switch “A” Common13—

Analog Switch “C” Normally Closed Input——

Analog Switch “C” Normally Open Input——

Analog Switch “C” Common——

Positive Analog and Digital Supply Voltage Input1616 V+16

MAX4051/

MAX4051A

MAX4052/

MAX4052A

MAX4053/

MAX4053A

13, 1, 15, 2,

14, 5, 12, 4

MAX4051/A, MAX4052/A, MAX4053/A

66

6

77

88

Note: NO, NC, and COM pins are identical and interchangeable. Any may be considered an input or output; signals pass equally

well in both directions.

TOTAL HARMONIC DISTORTION

100

V± = ±5V

600Ω IN AND OUT

10

1

THD (%)

0.1

0.01

10 100 1k 10k

vs. FREQUENCY

FREQUENCY (Hz)

FUNCTION

MAX4051/2/3-10

40

Page 43

Low-Voltage, CMOS Analog

Multiplexers/Switches

Table 1. Truth Table/Switch Programming

ON SWITCHESADDRESS BITS

INH

X = Don’t care * ADDC not present on MAX4052.

Note: NO and COM pins are identical and interchangeable. Either may be considered an input or output; signals pass equally well

in either direction.

ADDC*

X1

00

00

00

00

10

10

10

10

ADDB ADDA

X X All switches open All switches open All switches open

0 0 COM–NO0

0 1 COM–NO1

1 0 COM–NO2

1 1 COM–NO3

0 0 COM–NO4

0 1 COM–NO5

1 0 COM–NO6

1 1 COM–NO7

MAX4051/

MAX4051A

MAX4052/

MAX4052A

COMB–NO0B,

COMC–NO0C

COMB–NO1B,

COMC–NO1C

COMB–NO2B,

COMC–NO2C

COMB–NO3B,

COMC–NO3C

COMB–NO0B,

COMC–NO0C

COMB–NO1B,

COMC–NO1C

COMB–NO2B,

COMC–NO2C

COMB–NO3B,

COMC–NO3C

MAX4053/

MAX4053A

COMA–NCA,

COMB–NCB,

COMC–NCC

COMA–NOA,

COMB–NCB,

COMC–NCC

COMA–NCA,

COMB–NOB,

COMC–NCC

COMA–NOA,

COMB–NOB,

COMC–NCC

COMA–NCA,

COMB–NCB,

COMC–NOC

COMA–NOA,

COMB–NCB,

COMC–NOC

COMA–NCA,

COMB–NOB,

COMC–NOC

COMA–NOA,

COMB–NOB,

COMC–NOC

MAX4051/A, MAX4052/A, MAX4053/A

__________Applications Information

Power-Supply Considerations

Overview

The MAX4051/MAX4052/MAX4053 and MAX4051A/

MAX4052A/MAX4053A construction is typical of most

CMOS analog switches. They have three supply pins:

V+, V-, and GND. V+ and V- are used to drive the internal CMOS switches and set the limits of the analog voltage on any switch. Reverse ESD-protection diodes are

internally connected between each analog signal pin

and both V+ and V-. If any analog signal exceeds V+ or

V-, one of these diodes will conduct. During normal

operation, these (and other) reverse-biased ESD diodes

leak, forming the only current drawn from V+ or V-.

41

Virtually all the analog leakage current comes from the

ESD diodes. Although the ESD diodes on a given signal

pin are identical, and therefore fairly well balanced,

they are reverse biased differently. Each is biased by

either V+ or V- and the analog signal. This means their

leakages will vary as the signal varies. The

difference

the two diode leakages to the V+ and V- pins constitutes the analog signal path leakage current. All analog

leakage current flows between each pin and one of the

supply terminals, not to the other switch terminal. This is

why both sides of a given switch can show leakage currents of either the same or opposite polarity.

There is no connection between the analog signal

paths and GND.

in

Page 44

Low-Voltage, CMOS Analog

Multiplexers/Switches

V+ and GND power the internal logic and logic-level

translators, and set both the input and output logic limits. The logic-level translators convert the logic levels

into switched V+ and V- signals to drive the gates of

the analog signals. This drive signal is the only connection between the logic supplies (and signals) and the

analog supplies. V+ and V- have ESD-protection

diodes to GND.

The logic-level thresholds are TTL/CMOS compatible

when V+ is +5V. As V+ rises, the threshold increases

slightly, so when V+ reaches +12V, the threshold is

about 3.1V; above the TTL-guaranteed high-level minimum of 2.8V, but still compatible with CMOS outputs.

COM NO

Bipolar Supplies

These devices operate with bipolar supplies between

±3.0V and ±8V. The V+ and V- supplies need not be

symmetrical, but their sum cannot exceed the absolute

maximum rating of +17V.

EXTERNAL BLOCKING DIODE

Single Supply

These devices operate from a single supply between

+3V and +16V when V- is connected to GND. All of the

bipolar precautions must be observed. At room temperature, they actually “work” with a single supply at near

or below +1.7V, although as supply voltage decreases,

switch on-resistance and switching times become very

high.

Figure 1. Overvoltage Protection Using External Blocking

Diodes

Overvoltage Protection

Proper power-supply sequencing is recommended for

all CMOS devices. Do not exceed the absolute maximum ratings, because stresses beyond the listed ratings can cause permanent damage to the devices.

Always sequence V+ on first, then V-, followed by the

logic inputs (NO) and by COM. If power-supply

MAX4051/A, MAX4052/A, MAX4053/A

sequencing is not possible, add two small signal diodes

(D1, D2) in series with the supply pins for overvoltage

protection (Figure 1).

Adding diodes reduces the analog signal range to one

diode drop below V+ and one diode drop above V-, but

does not affect the devices’ low switch resistance and

low leakage characteristics. Device operation is

unchanged, and the difference between V+ and Vshould not exceed 17V. These protection diodes are

not recommended when using a single supply if signal

levels must extend to ground.

In 50Ω systems, signal response is reasonably flat up

to 50MHz (see

Above 20MHz, the on response has several minor

peaks which are highly layout dependent. The problem

is not turning the switch on, but turning it off. The offstate switch acts like a capacitor, and passes higher

frequencies with less attenuation. At 10MHz, off isolation is about -45dB in 50Ω systems, becoming worse

(approximately 20dB per decade) as frequency

increases. Higher circuit impedances also make off isolation worse. Adjacent channel attenuation is about 3dB

above that of a bare IC socket, and is entirely due to

capacitive coupling.

V+

*

*

V-

High-Frequency Performance

Typical Operating Characteristics

V+

D1EXTERNAL BLOCKING DIODE

MAX4051/A

MAX4052/A

MAX4053/A

*

*

D2

V-

* INTERNAL PROTECTION DIODES

).

42

Page 45

Low-Voltage, CMOS Analog

Multiplexers/Switches

______________________________________________Test Circuits/Timing Diagrams

V

50Ω

V

50Ω

ADD

ADD

ADDC

ADDB

ADDA

INH

ADDC

ADDB

INH

V+

V+

MAX4051/A

GND

V+

V+

MAX4052/A

GND

NO0

NO1–NO6

NO7

COM

V-

V-

NO0

NO1–NO2

NO3

COM

V-

V-

300Ω

300Ω

V+

V-

V

OUT

35pF

V+

V-

V

OUT

35pF

V+

V

ADD

0V

V

NO0

0V

V

OUT

V

NO7

t

TRANS

V+

V

ADD

0V

V

NO0

0V

V

OUT

V

NO3

t

TRANS

50%

50%

90%

90%

90%

90%

t

TRANS

t

TRANS

MAX4051/A, MAX4052/A, MAX4053/A

V+

V

ADD

50Ω

V- = 0V FOR SINGLE-SUPPLY OPERATION.

REPEAT TEST FOR EACH SECTION.

ADD

INH

V+

MAX4053/A

GND

Figure 2. Address Transition Time

V+

V

NO

V-

NC

V+

COM

V-

300Ω

V-

35pF

V

OUT

ADD

0V

V

NC

0V

V

OUT

V

NO

t

TRANS

50%

90%

90%

t

TRANS

43

Page 46

Low-Voltage, CMOS Analog

Multiplexers/Switches

V+

V+

GND

GND

GND

V+

V+

V+

V+

NO0

NO1–NO7

COM

V-

V-

NO0

NO1–NO3

COM

V-

V-

COM

V-

V-

V+

V

OUT

300Ω

300Ω

NO

NC

300Ω

35pF

V+

V

OUT

35pF

V+

V-

V

OUT

35pF

ADDC

ADDB

ADDA

V

INH

50Ω

V

INH

50Ω

MAX4051/A, MAX4052/A, MAX4053/A

V

INH

50Ω

MAX4051/A

INH

ADDC

ADDB

MAX4052/A

INH

ADD

MAX4053/A

INH

V+

V

INH

0V

V

NO0

V

OUT

0V

V+

V

INH

0V

V

NO0

V

OUT

0V

V+

V

INH

0V

V

NO_

V

OUT

0V

50%

t

ON

50%

t

ON

50%

t

ON

90%

90%

90%

90%

90%

90%

t

OFF

t

OFF

t

OFF

V- = 0V FOR SINGLE-SUPPLY OPERATION.