Page 1

R

SERVICE MANUAL

DW9916S

Ver 0.0

Page 2

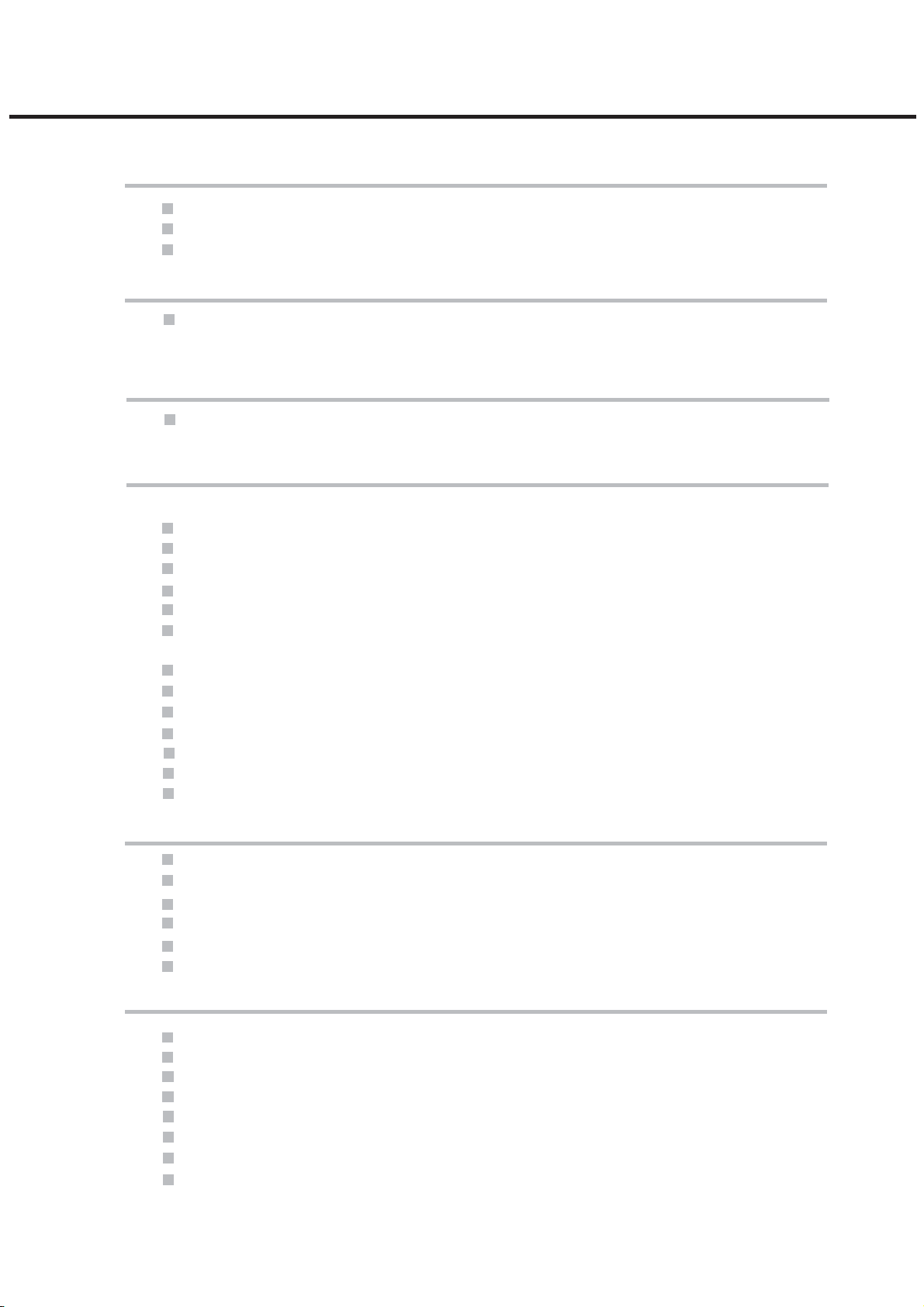

PREFACE

INDEX

FEATURES ...........................................................................................................................................

FRONT PA

REMOTE CONTROL

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

NEL&REAR PANEL

................................................................................................................................

.........................................................................................................................

.........................................................................................................................

EXPLODED VIEW

EXPLODED VIEW

........................................................................................................................................5

PARTS SPECIFICATIONS

SST39VF160............................................................................................................................................ 6

M13S128168A .......................................................................................................................................7

TSB41AB1

TVP5146

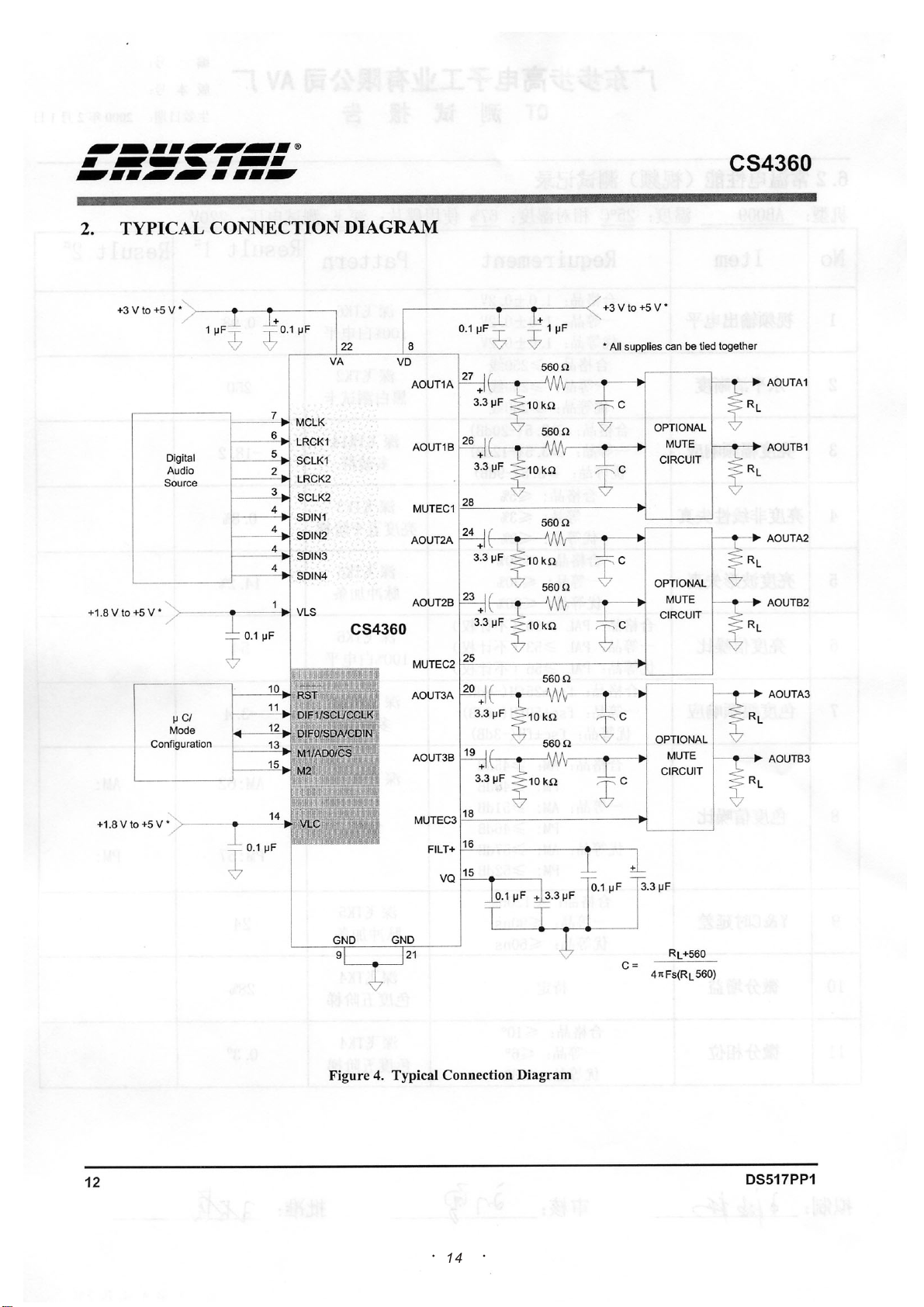

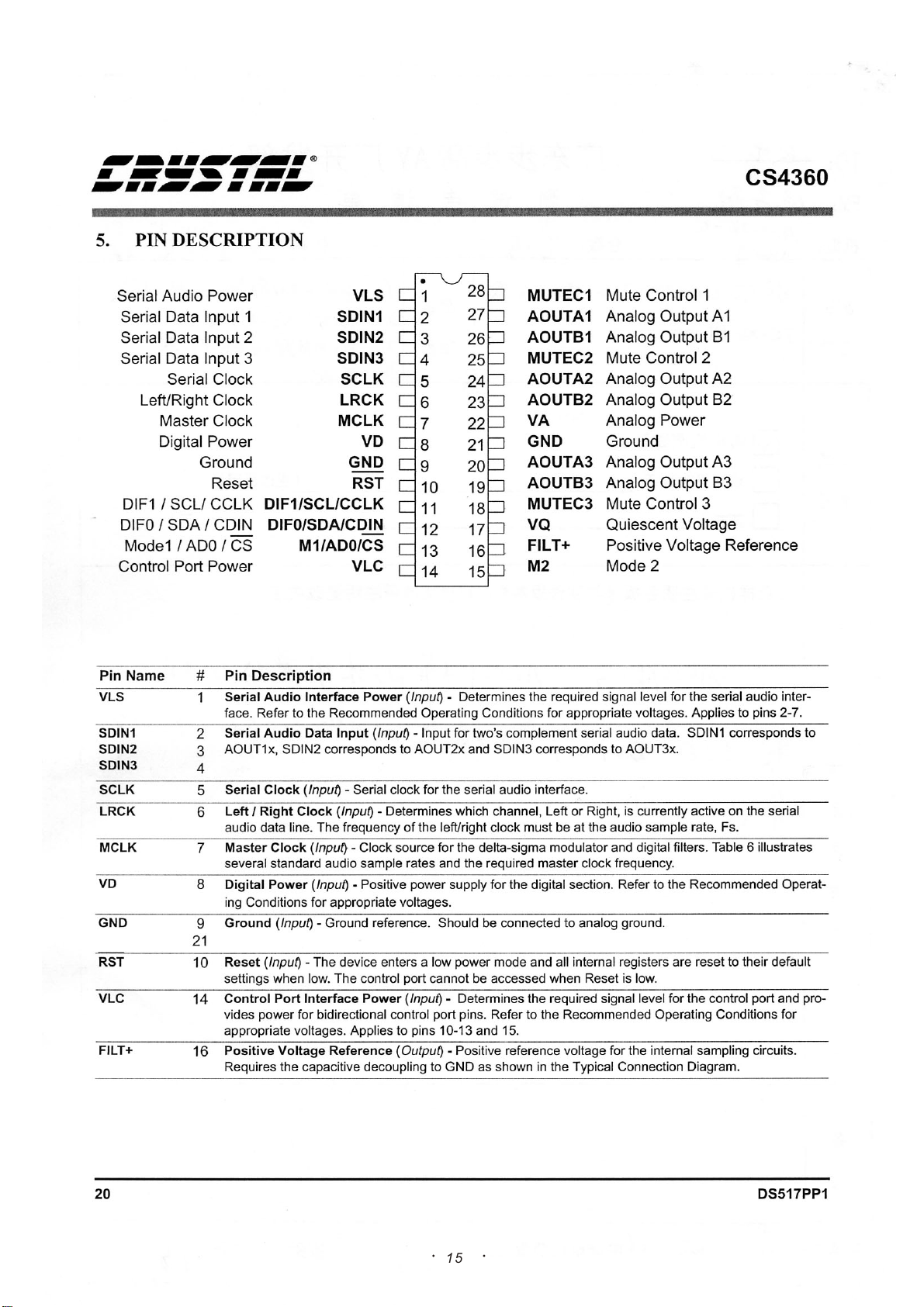

CS4360

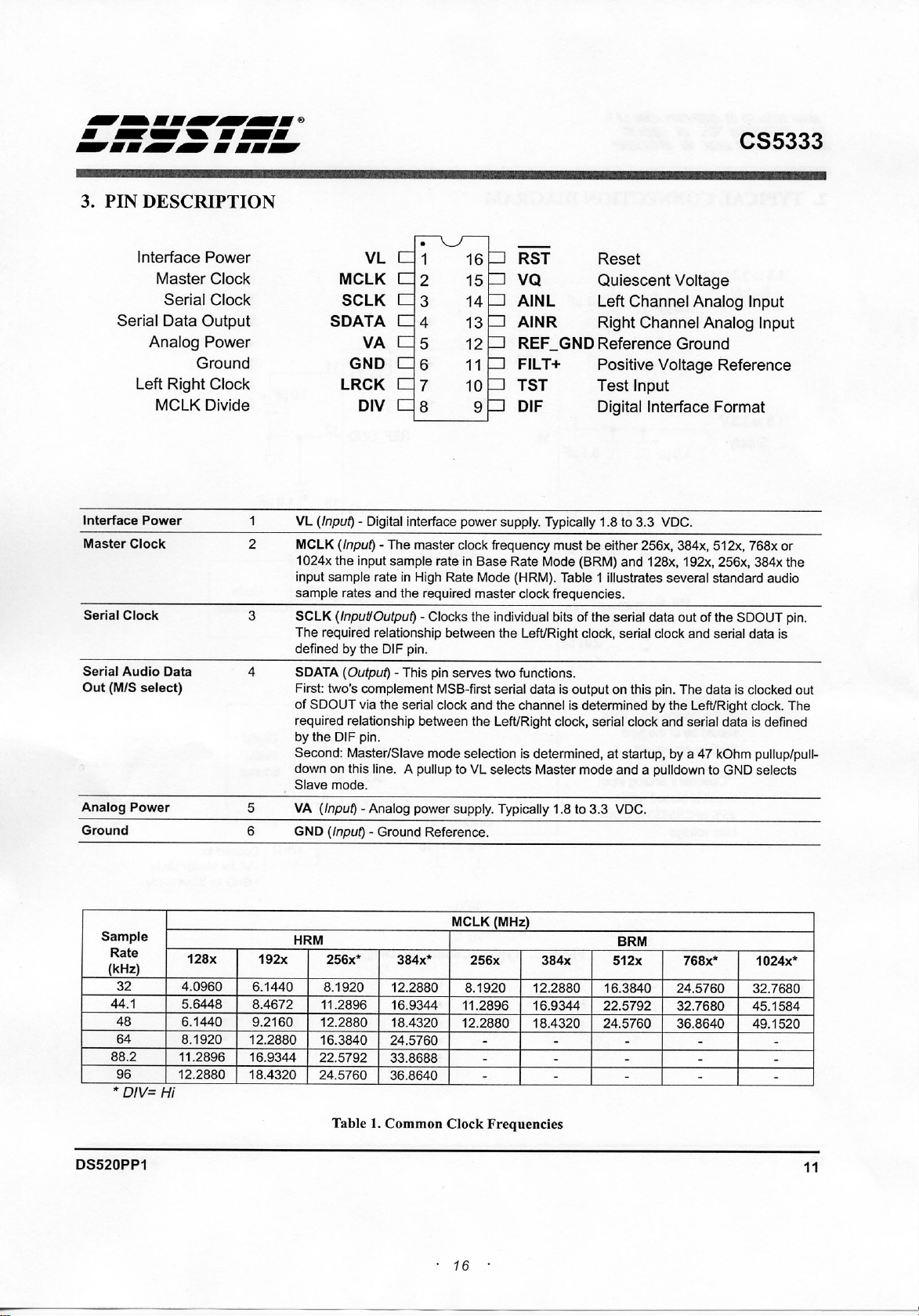

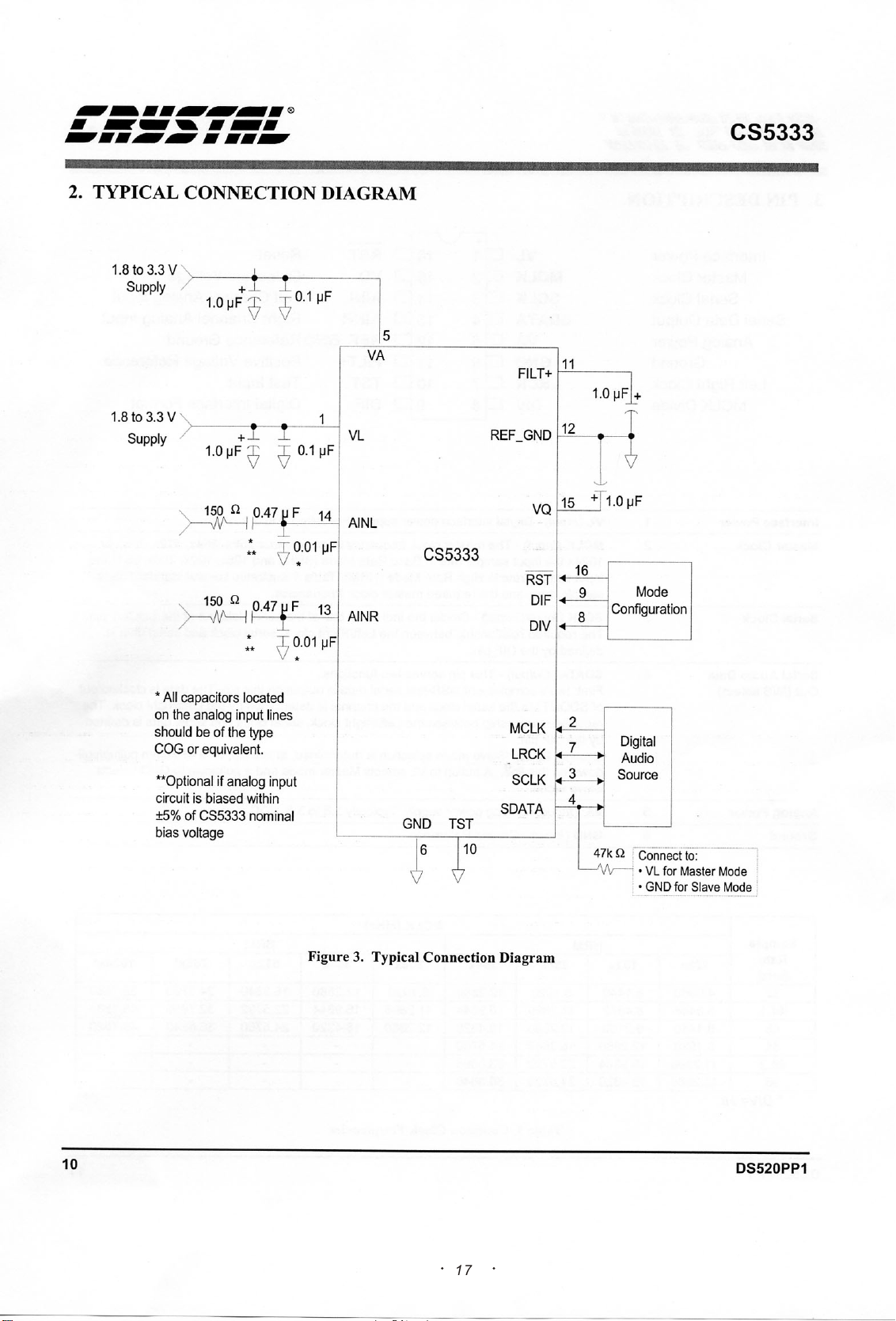

CS5333 .............................................................................................................................................. 15

................................................................................................................

................................................................................................................................9

...................................................................................................................... 13

.......................................................................................................................................

1

2

3

4

8

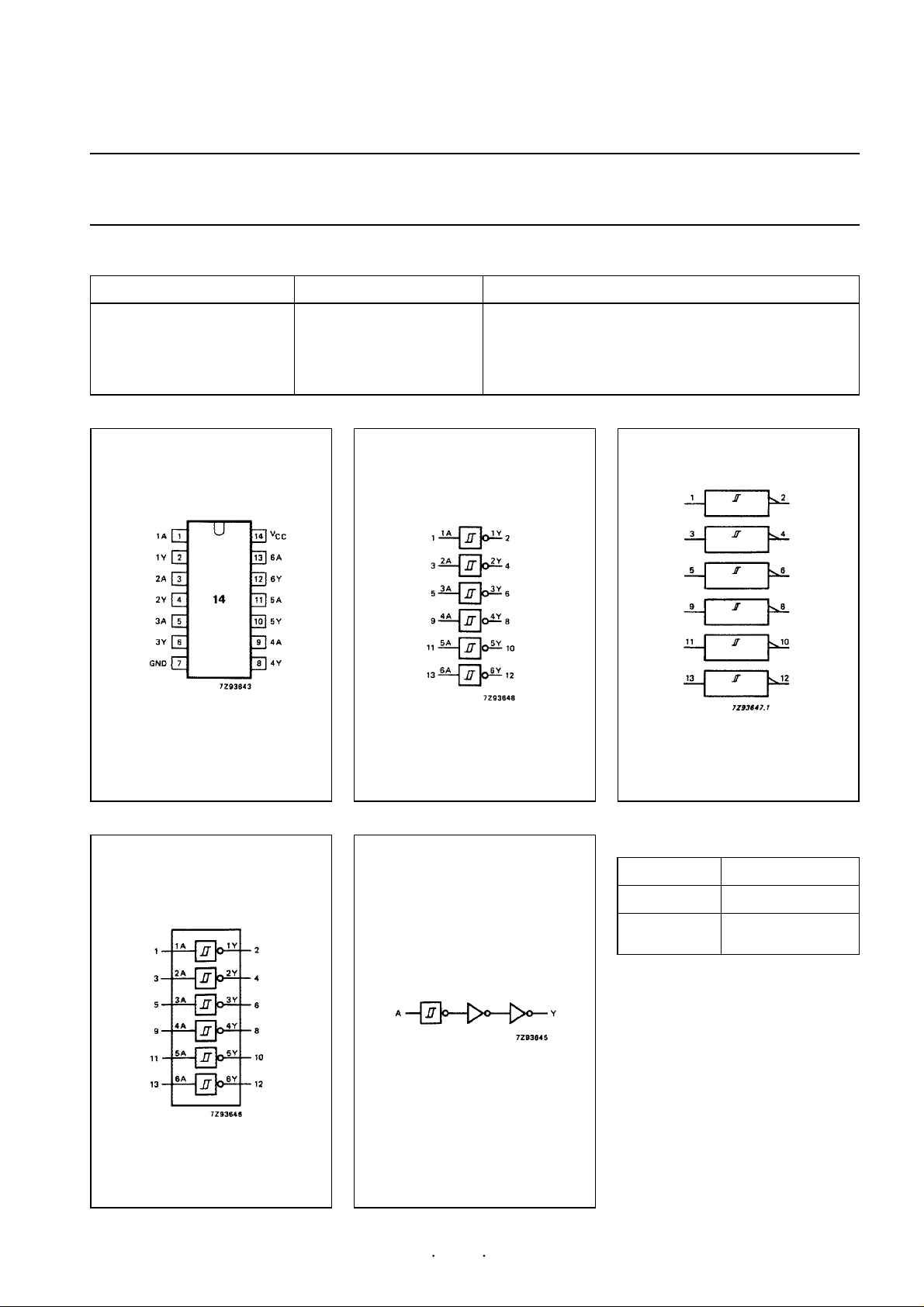

74HC/HCT14 ........................................................................................................................................ 17

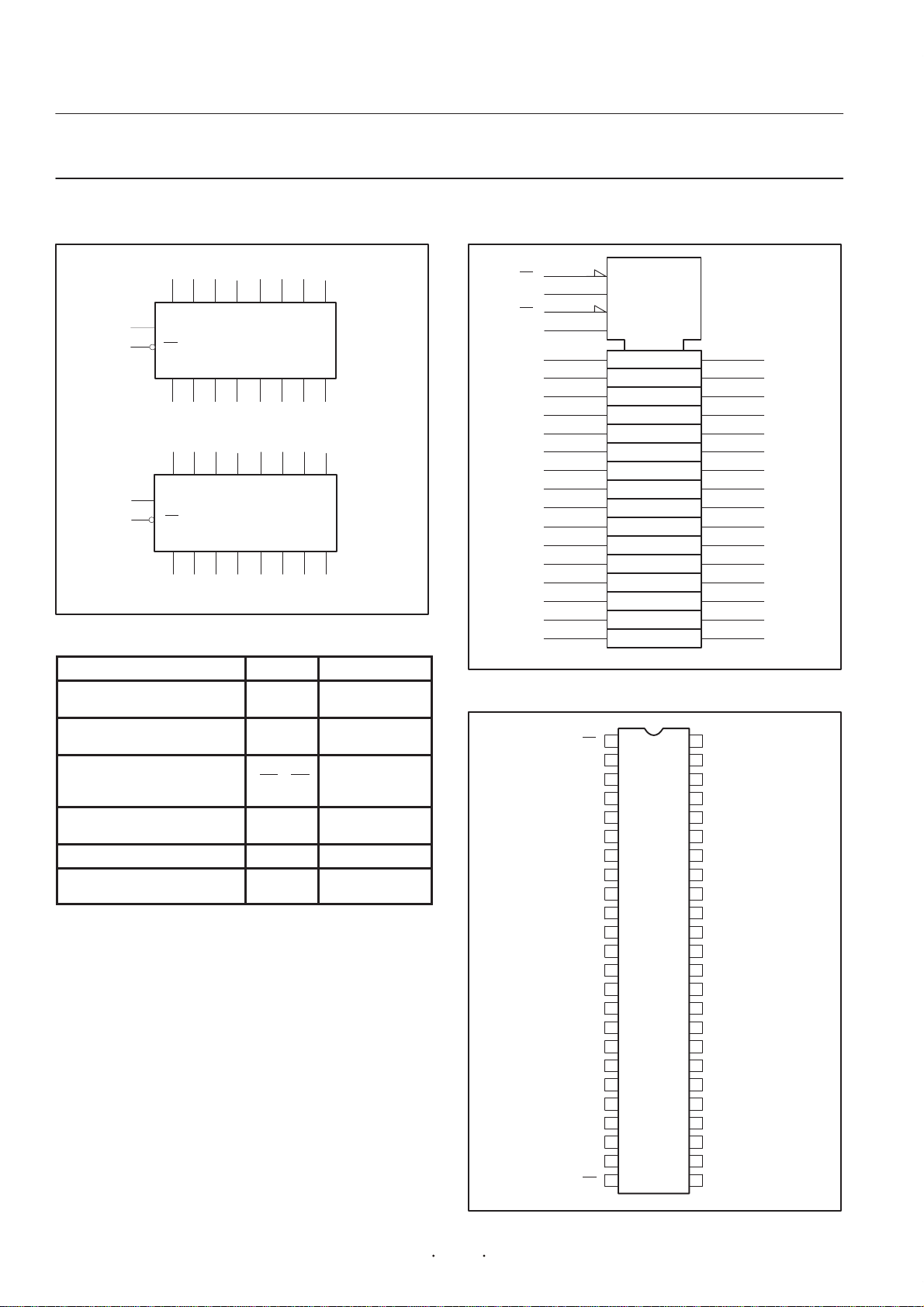

74ALVT16373

MM1225

LP2995

PQXXXEZ02Z .................................................................................................................................. 22

MS3415

TUNER ..................................................................................................................... 24

............................................................................................................................... 18

...................................................................................................................................................... 19

.......................................................................................................................

.........................................................................................................................

SCHEMATIC DIAGRAM&PCB SILKSCREEN

MAIN BOARD SCHEMATIC AND PCB LAYOUT

AV BOARD SCHEMATIC AND PCB LAYOUT

KEY BOARD SCHEMATIC AND PCB LAYOUT

POWER BOARD SCHEMATIC AND PCB LAYOUT

DV+FRONT AV BOARD SCHEMATIC AND PCB LAYOUT..............................................................56-58

CARD READER BOARD SCHEMATIC AND PCB LAYOUT..............................................................59-61

..................................................................................

..............................................................................................................

.................................................................................

............................................................

PARTS LIST

MAIN BOARD................................................................................................................................. 62-63

MAIN KEY BOARD

AUXILIARY KEY BOARD

DV+FRONT AV BOARD

CARD READER BOARD

POWER BOARD .................................................................................................................. 68-69

CONTROLLER....................................................................................................................................70

REAR AV BOARD...............................................................................................................................71-72

........................................................................................................................................

......................................................................................................

...........................................................................................................................66

....................................................................................................67

21

23

25-37

38-47

48-52

53-55

64

65

Page 3

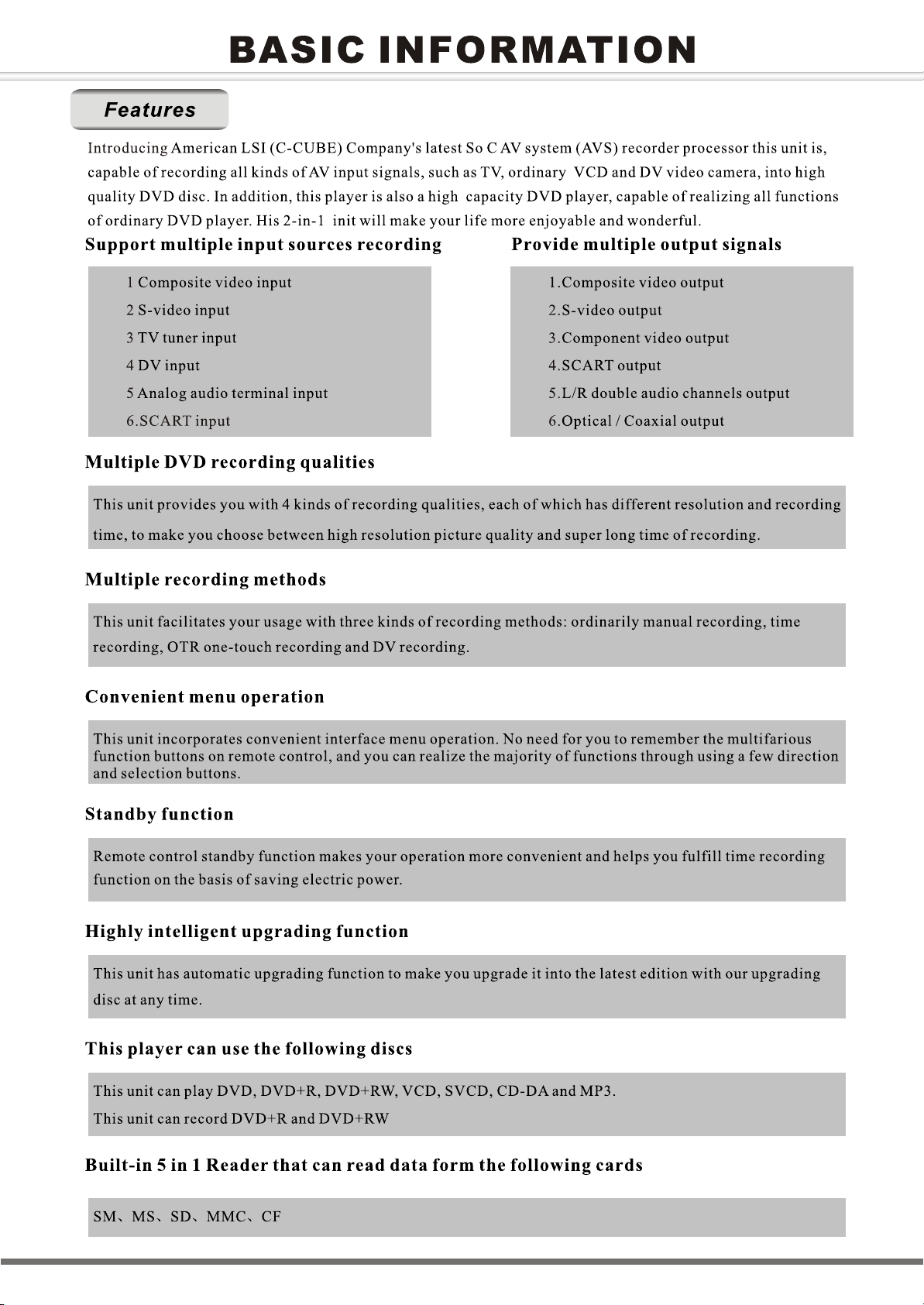

1

Page 4

2

Page 5

3

Page 6

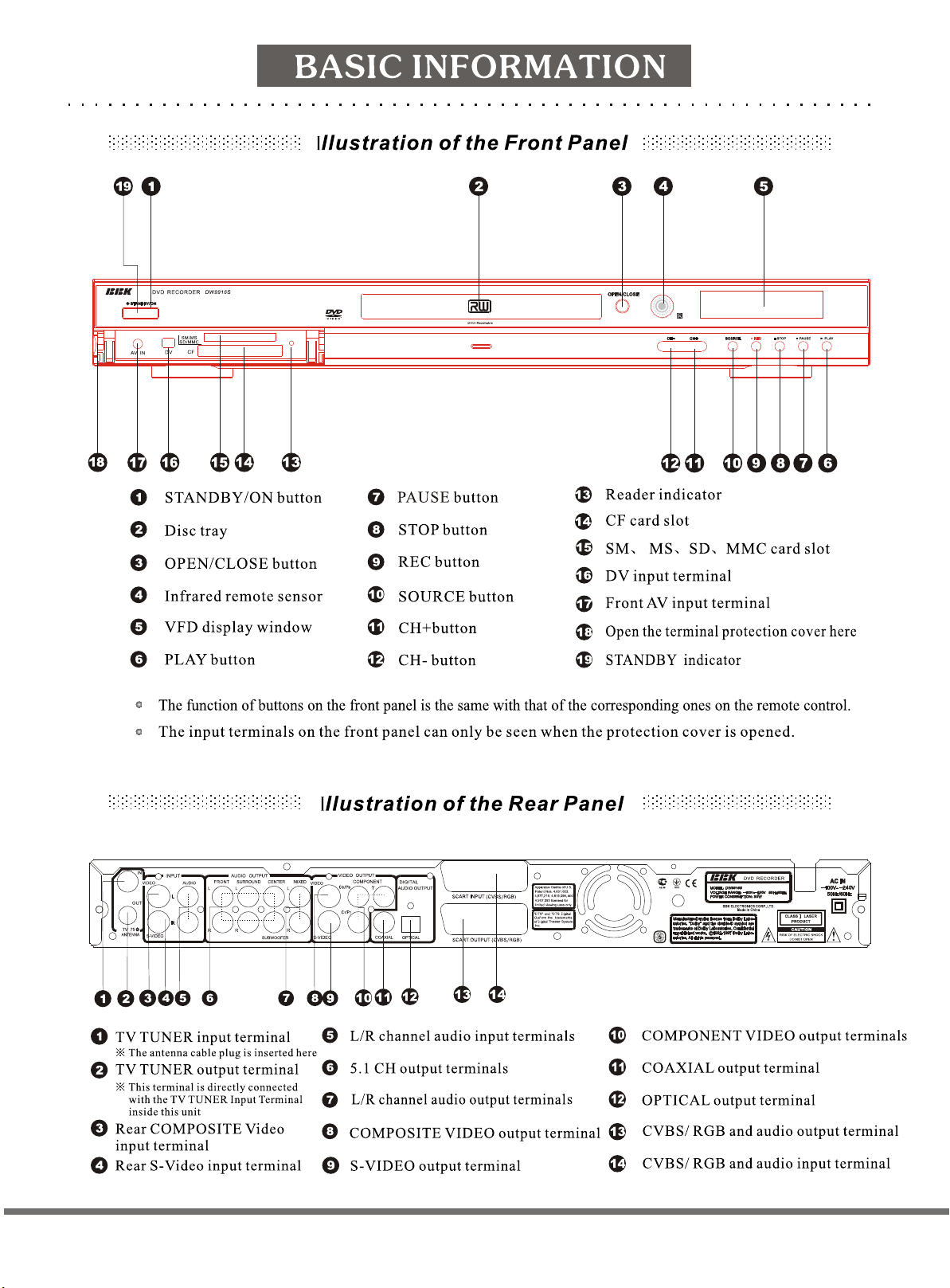

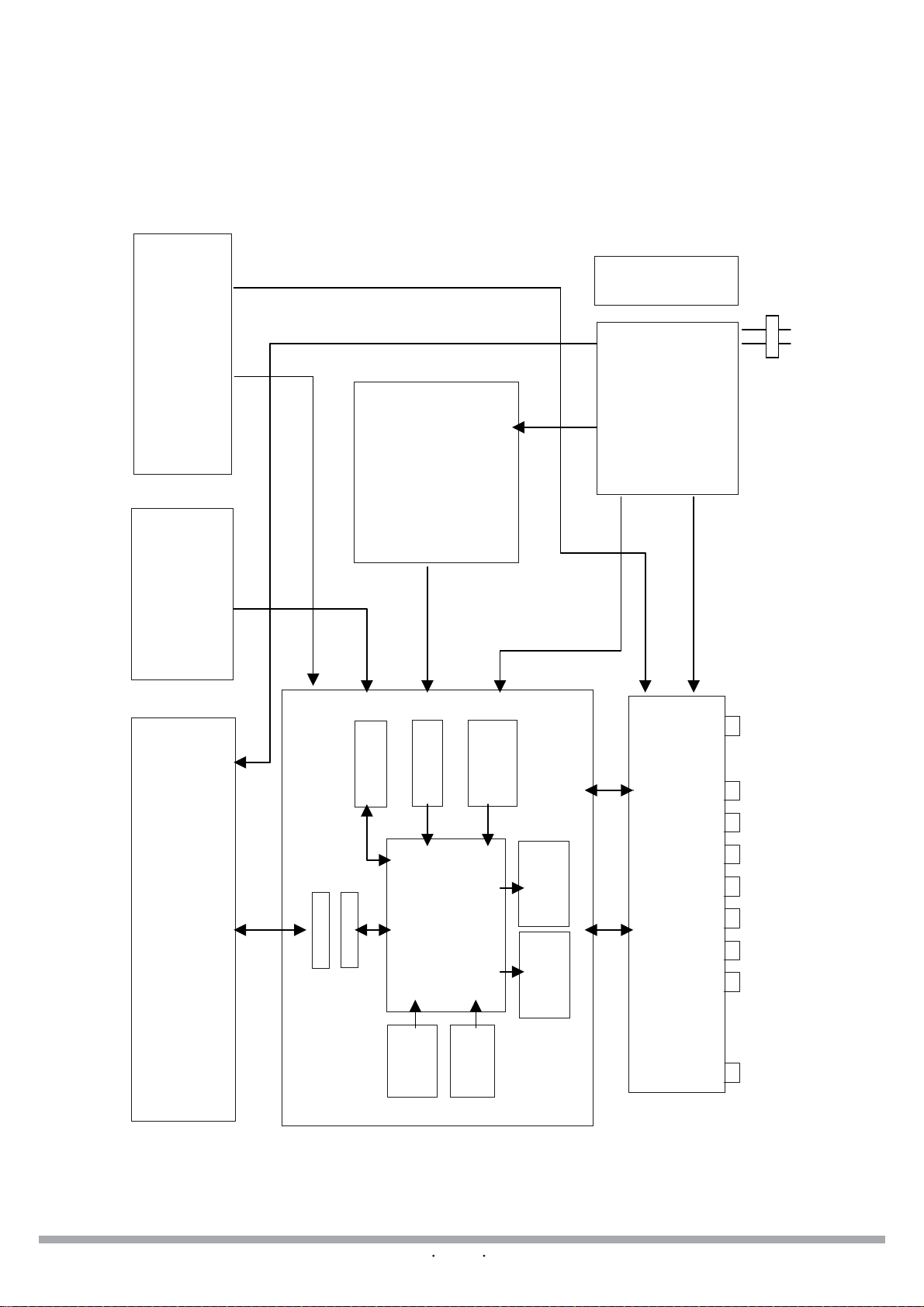

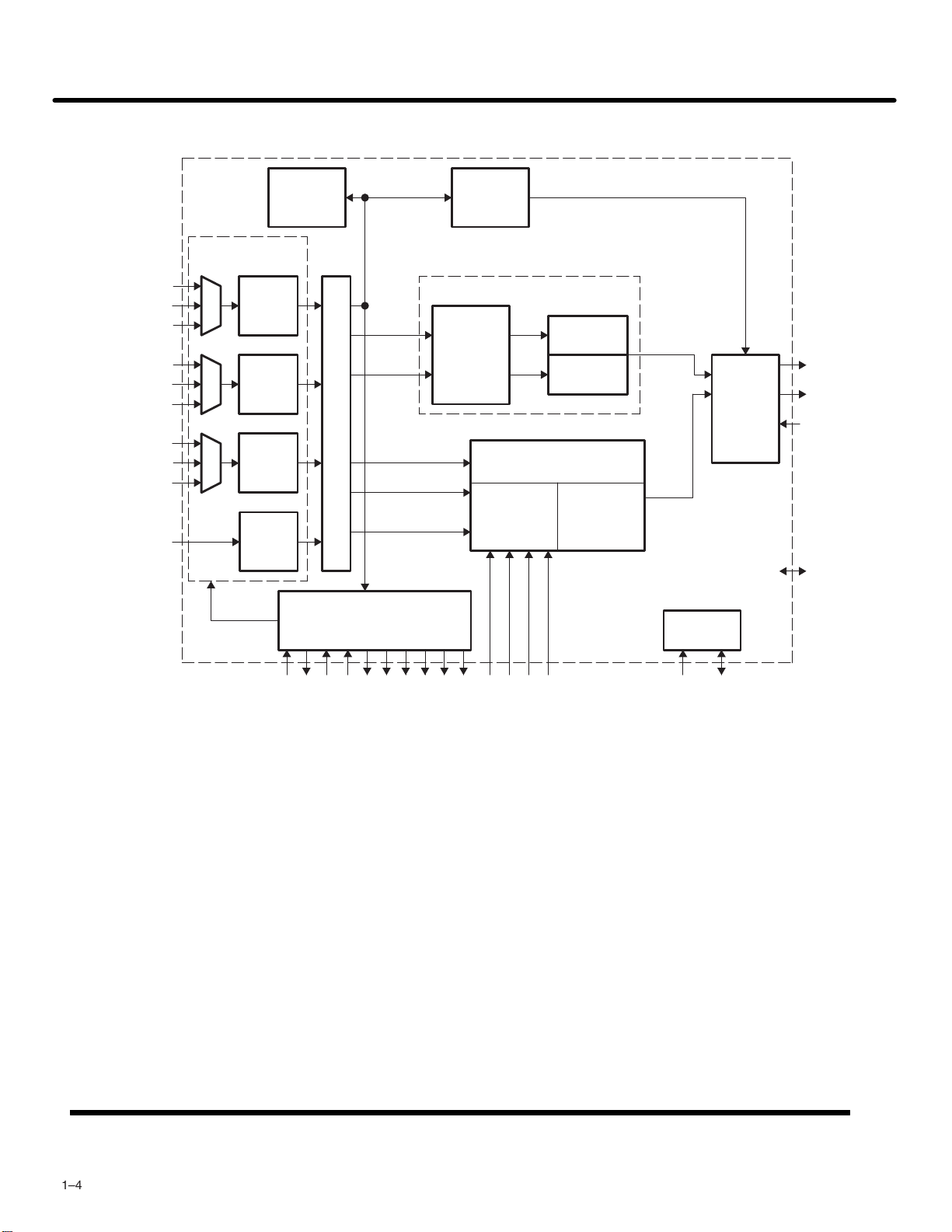

BLOCK DIAGRAM

FRONT AV+DV INPUT

CDW9916-4

CARD READER

DDW916-2

5VSTB

+3.3V

+5V

+2.5V

+12V

-12V

-22V

POWER BOARD

5AB9915-3

DVD+RW

DVD Re co rd a ble

AC 100V-240V INPUT

Scart input/output

MAIN BOARD

DV(1394) Phy

NTSC/PAL

Decoder

tvp5146

Audio

5.1CH Audio

output

AV INPUT/OUTPUT BOARD

7DW9916-5

FRONT PANEL

4DW9916-2,9DW9916-1

DIS PL AY &KEY

Video output

(component)

FP Control

Front Panel

DMN-8602

Audio DAC

5.1CH

Cs4

A/V input

360

2DW9916-3

1M 16bit

×

FLASH

39VF160

SDR/DDR

SDRAM

TV Tuner

4

Page 7

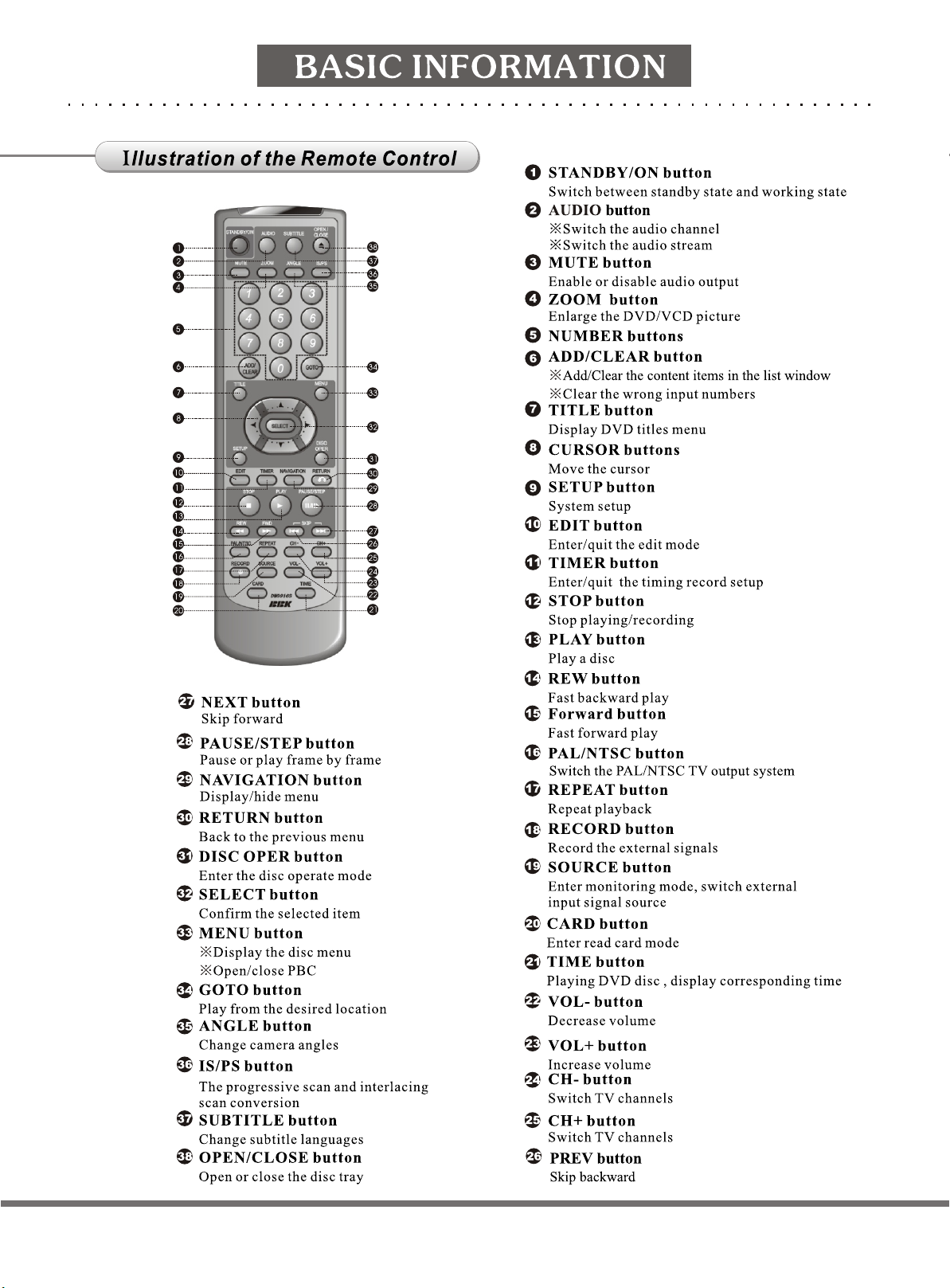

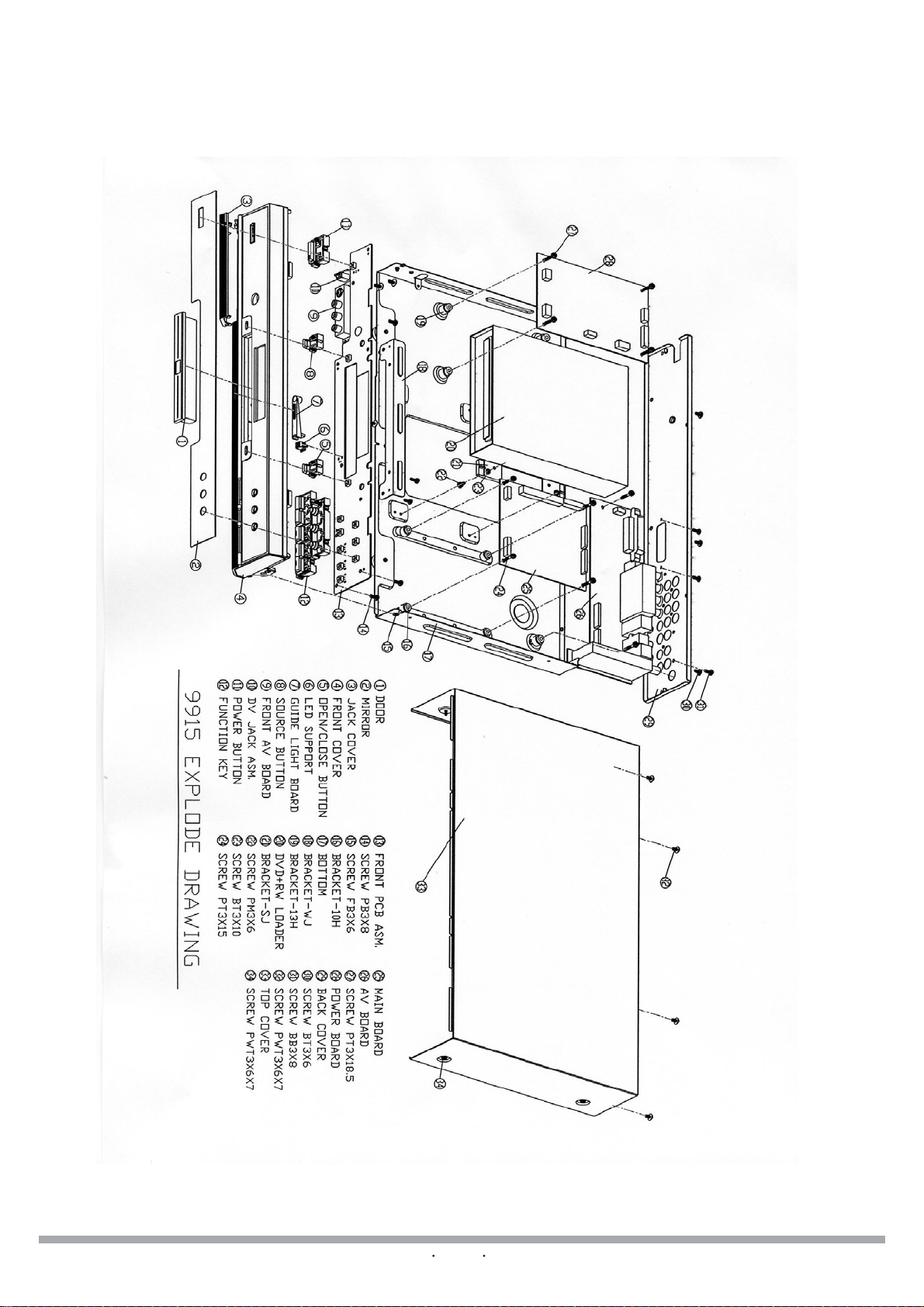

EXPLODED VIEW

55

Page 8

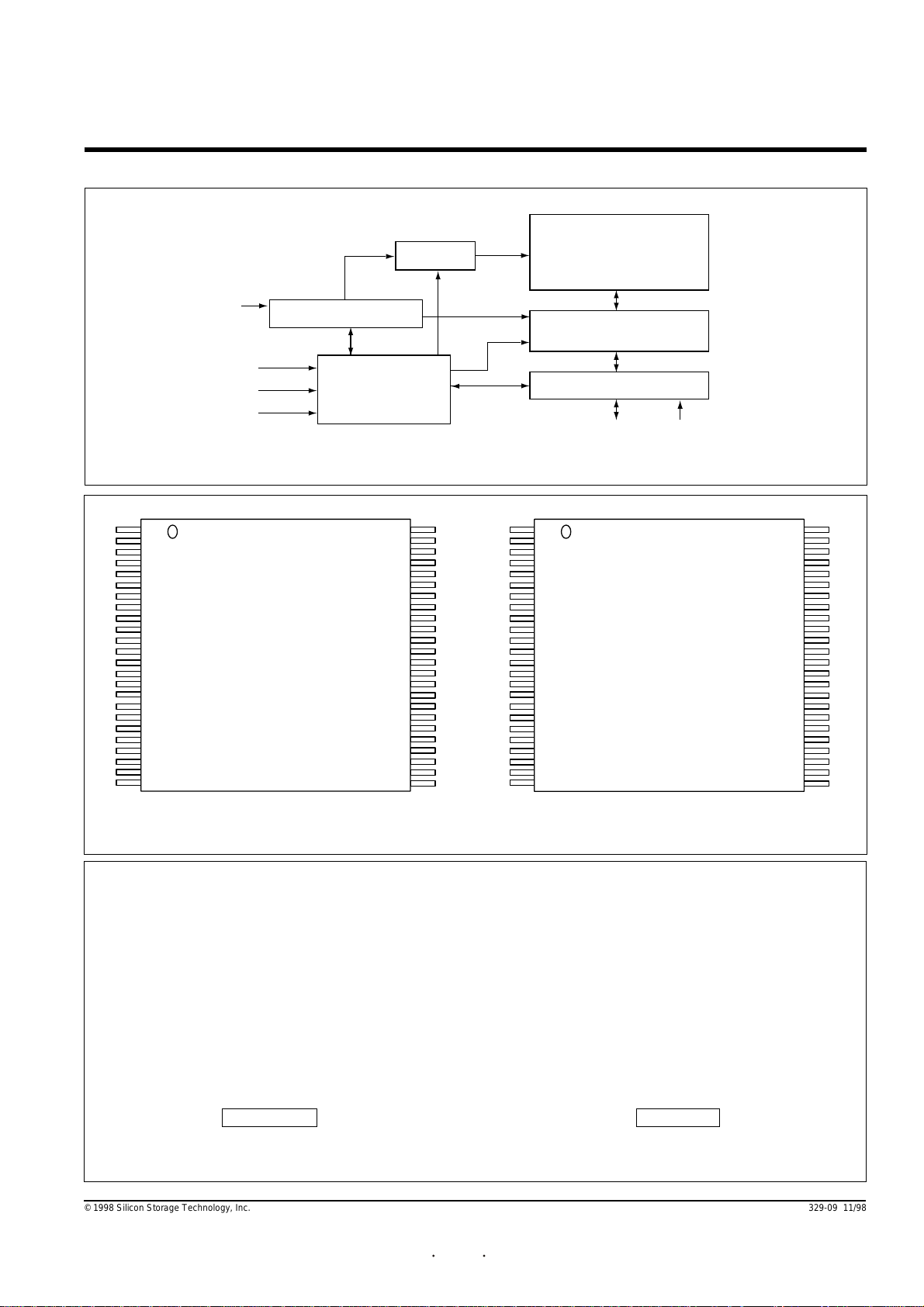

FUNCTIONAL BLOCK DIAGRAM

A19 - A

0

CE#

OE#

WE#

X-Decoder

Address Buffer & Latches

Control Logic

16 Megabit Multi-Purpose Flash

SST39VF160Q / SST39VF160

Advance Information

16,777,216 bit

EEPROM

Cell Array

Y-Decoder

I/O Buffers and Data Latches

DQ15 - DQ

V

0

DDQ

329 ILL B1.2

A15

A14

A13

A12

A11

A10

A19

WE#

A18

A17

1

2

3

4

5

6

A9

7

A8

8

9

NC

10

11

NC

12

NC

13

NC

14

NC

15

16

17

A7

18

A6

19

A5

20

A4

21

A3

22

A2

23

A1

24

Standard Pinout

T op Vie w

Die Up

SST39VF160Q

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

329 ILL F01.2

A16

V

V

DQ15

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE#

V

CE#

A0

FIGURE 1: PIN ASSIGNMENTS FOR 48-PIN TSOP PACKAGES

123456

A

A3 A7 NC WE# A9 A13

B

A4 A17 NC NC A8 A12

C

A2 A6 A18 NC A10 A14

D

A1 A5 NC A19 A11 A15

E

A0 DQ0 DQ2 DQ5 DQ7 A16

F

CE# DQ8 DQ10 DQ12 DQ14 V

G

OE# DQ9 DQ11 V

H

V

DQ1 DQ3 DQ4 DQ6 V

SS

SST39VF160Q

DD

DQ13 DQ15

DDQ

SS

329 ILL F02.4

DDQ

SS

DD

SS

A15

A14

A13

A12

A11

A10

A19

WE#

A18

A17

NC

NC

NC

NC

NC

A9

A8

A7

A6

A5

A4

A3

A2

A1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Standard Pinout

T op Vie w

Die Up

SST39VF160

123456

A

A3 A7 NC WE# A9 A13

B

A4 A17 NC NC A8 A12

C

A2 A6 A18 NC A10 A14

D

A1 A5 NC A19 A11 A15

E

A0 DQ0 DQ2 DQ5 DQ7 A16

F

CE# DQ8 DQ10 DQ12 DQ14 NC

G

OE# DQ9 DQ11 V

H

V

DQ1 DQ3 DQ4 DQ6 V

SS

SST39VF160

DD

DQ13 DQ15

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

329 ILL F01a.0

SS

329 ILL F02a.0

A16

NC

V

SS

DQ15

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

DD

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE#

V

SS

CE#

A0

FIGURE 2: PIN ASSIGNMENTS FOR 48-PIN TFBGA

© 1998 Silicon Storage Technology, Inc.329-09 11/98

6

Page 9

ESMT

M13S128168A

45

45

;(

45-45

2

2

66 PIN TSOP(II)

(400mil x 875mil)

(0.65 mm PIN PITCH)

Elite Semiconductor Memory Technology Inc.

7

Publication Date : Nov. 2002

Revision : 0.2

Revision : 0.2

Page 10

SLLS423D – JUNE 2000 – REVISED SEPTEMBER 2002

description (continued)

required for normal network operation regardless of the state of the PHY-LLC interface. When the interface is

in the reset or disabled state and LPS is again observed active, the PHY initializes the interface and returns it

to normal operation.

When the PHY-LLC interface is in the low-power disabled state, the TSB41AB1 automatically enters a

low-power mode if the port is inactive (disconnected, disabled, or suspended). In this low-power mode, the

TSB41AB1 disables its internal clock generators and also disables various voltage and current reference

circuits depending on the state of the port (some reference circuitry must remain active in order to detect new

cable connections, disconnections, or incoming TPBIAS, for example). The lowest power consumption (the

ultralow-power sleep mode) is attained when the port is either disconnected, or disabled with the port interrupt

enable bit cleared. The TSB41AB1 exits the low-power mode when the LPS input is asserted high or when a

port event occurs which requires that the TSB41AB1 become active in order to respond to the event or to notify

the LLC of the event (for example, incoming bias is detected on a suspended port, a disconnection is detected

on a suspended port, a new connection is detected on a nondisabled port, etc.). The SYSCLK output becomes

active (and the PHY-LLC interface is initialized and becomes operative) within 7.3 ms after LPS is asserted high

when the TSB41AB1 is in the low-power mode.

The PHY uses the C/LKON terminal to notify the LLC to power up and become active. When activated, the

C/LKON signal is a square wave of approximately 163-ns period. The PHY activates the C/LKON output when

the LLC is inactive and a wake-up event occurs. The LLC is considered inactive when either the LPS input is

inactive, as described above, or the LCtrl bit is cleared to 0. A wake-up event occurs when a link-on PHY packet

addressed to this node is received, or when a PHY interrupt occurs. The PHY deasserts the C/LKON output

when the LLC becomes active (both LPS active and the LCtrl bit set to 1). The PHY also deasserts the C/LKON

output when a bus reset occurs unless a PHY interrupt condition exists which would otherwise cause C/LKON

to be active.

PHP package terminal diagram

SYSCLK

CTL0

CTL1

D0

D1

D2

D3

D4

D5

D6

D7

PD

LREQ

DGND

DGND

47 46 45 44 4348 42 40 39 3841

1

2

3

4

5

6

7

8

9

10

11

12

14 15

DGND

C/LKON

16

13

LPS

PHP PACKAGE

(TOP VIEW)

DDDVDD

DV

XO

XI

TSB41AB1

17 18 19 20

ISO

PC1

PC2

PC0

DD

PLLGND

PLLV

FILTER1

22 23 24

21

DD

CPS

DV

TESTM

FILTER0

RESET

37

SE

SM

36

35

34

33

32

31

30

29

28

27

26

25

AGND

AV

DD

R1

R0

AGND

TPBIAS

TPA+

TPA–

TPB+

TPB–

AGND

AV

DD

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 11

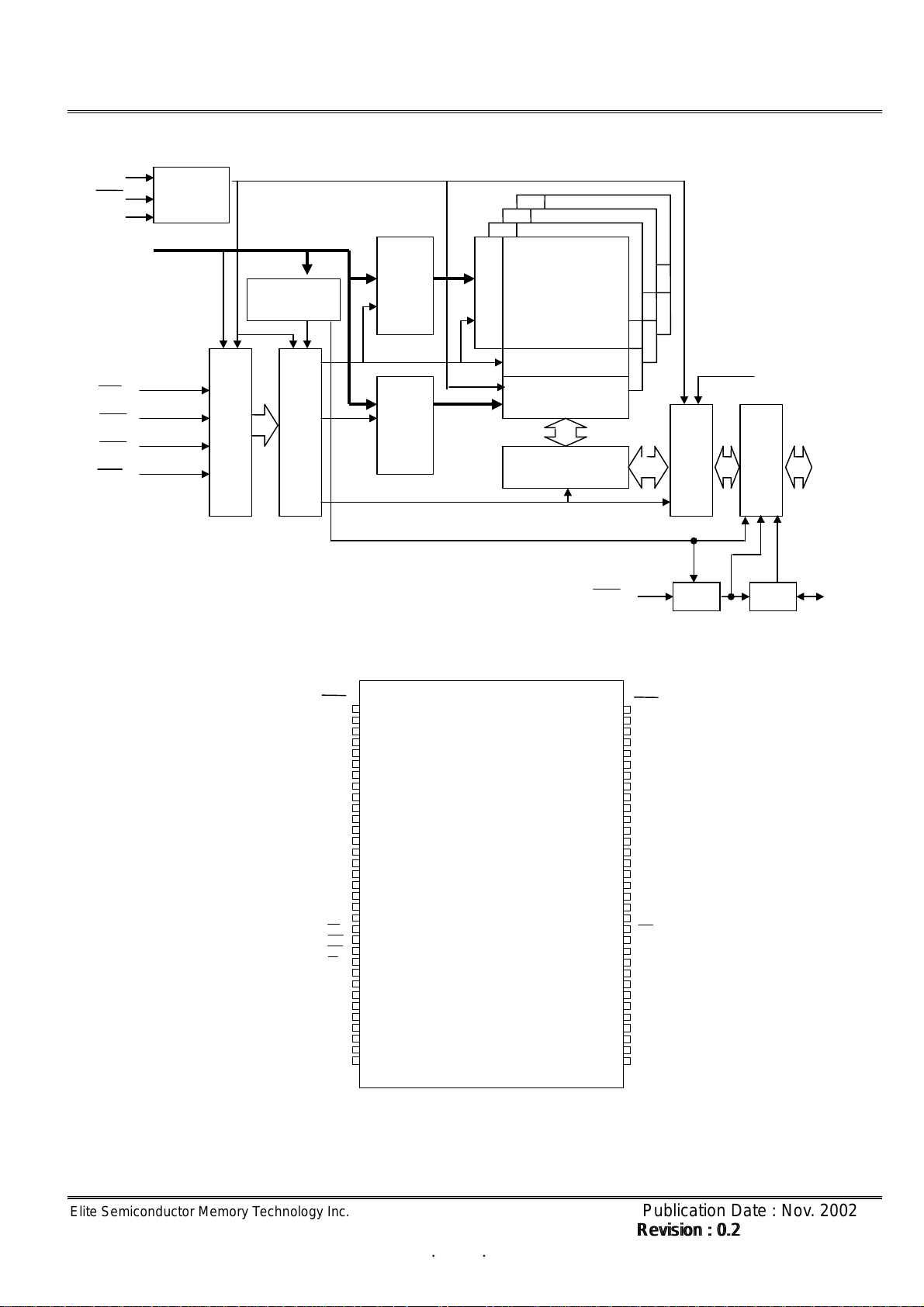

1.5 Functional Block Diagram

TVP5146

CVBS/

Pb/B/C

CVBS/

Y/G

CVBS/

Pr/R/C

CVBS/Y

VI_1_A

VI_1_B

VI_1_C

VI_2_A

VI_2_B

VI_2_C

VI_3_A

VI_3_B

VI_3_C

VI_4_A

Protection

Detector

Analog Front End

ADC1

ADC2

ADC3

ADC4

Sampling

Clock

Copy

M

U

X

Timing Processor

with Sync Detector

CVBS/Y/G

CVBS/Y

C

Y/G

Pb/B

Pr/R

VBI

Data

Slicer

Composite and S-Video Processor

Y/C

Separation

5-line

Adaptive

Comb

Component

Gain/Offset

Y

Processing

Chroma

C

Processing

Processor

Conversion

Luma

Color

Space

YCbCr

YCbCr

Host

Interface

Output

Formatter

Y[9:0]

C[9:0]

FSS

GPIO

XTAL1

XTAL2

PWDN

RESETB

AVID

DATACLK

FID

VS/VBLK

GLCO

HS/CS

DRDGDB

Figure 1–1. Functional Block Diagram

FSO

SCL

SDA

1–4

9

Page 12

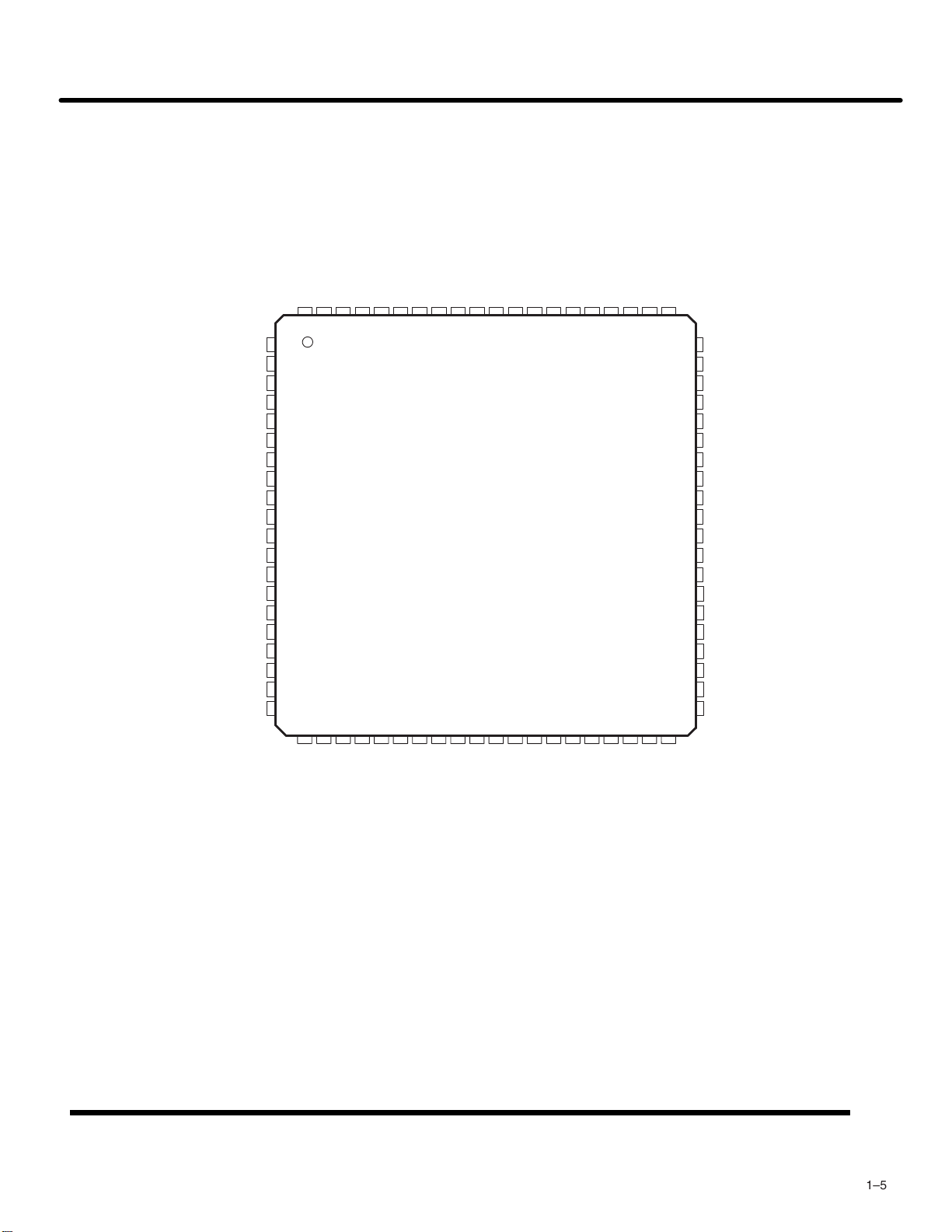

1.6 Terminal Assignments

VI_1_A

CH1_A18GND

CH1_A18VDD

PLL_A18GND

PLL_A18VDD

XTAL2

XTAL1

PFP PACKAGE

(TOP VIEW)

VS/VBLK/GPIO

HS/CS/GPIO

FID/GPIO

C_0/GPIO

C_1/GPIO

DGND

DVDD

C_2/GPIO

C_3/GPIO

C_4/GPIO

C_5/GPIO

IOGND

IOVDD

TVP5146

VI_1_B

VI_1_C

CH1_A33GND

CH1_A33VDD

CH2_A33VDD

CH2_A33GND

VI_2_A

VI_2_B

VI_2_C

CH2_A18GND

CH2_A18VDD

A18VDD_REF

A18GND_REF

CH3_A18VDD

CH3_A18GND

VI_3_A

VI_3_B

VI_3_C

CH3_A33GND

CH3_A33VDD

79 78 77 76 7580 74 72 71 7073

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

22 23

24

VI_4_A

CH4_A33VDD

CH4_A33GND

25 26 27 28

SCL

AGND

DGND

CH4_A18VDD

CH4_A18GND

29

30 31 32 33

SDA

INTREQ

69 682167 66 65 64

34 35 36 37 38 39 40

DVDD

DGND

PWDN

RESETB

FSS/GPIO

63 62 61

IOVDD

AVID/GPIO

GLCO/I2CA

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

IOGND

DATACLK

C_6/GPIO/RED

C_7/GPIO/GREEN

C_8/GPIO/BLUE

C_9/GPIO/FSO

DGND

DVDD

Y_0

Y_1

Y_2

Y_3

Y_4

IOGND

IOVDD

Y_5

Y_6

Y_7

Y_8

Y_9

DGND

DVDD

Figure 1–2. Terminal Assignments Diagram

10

1–5

Page 13

TVP5146

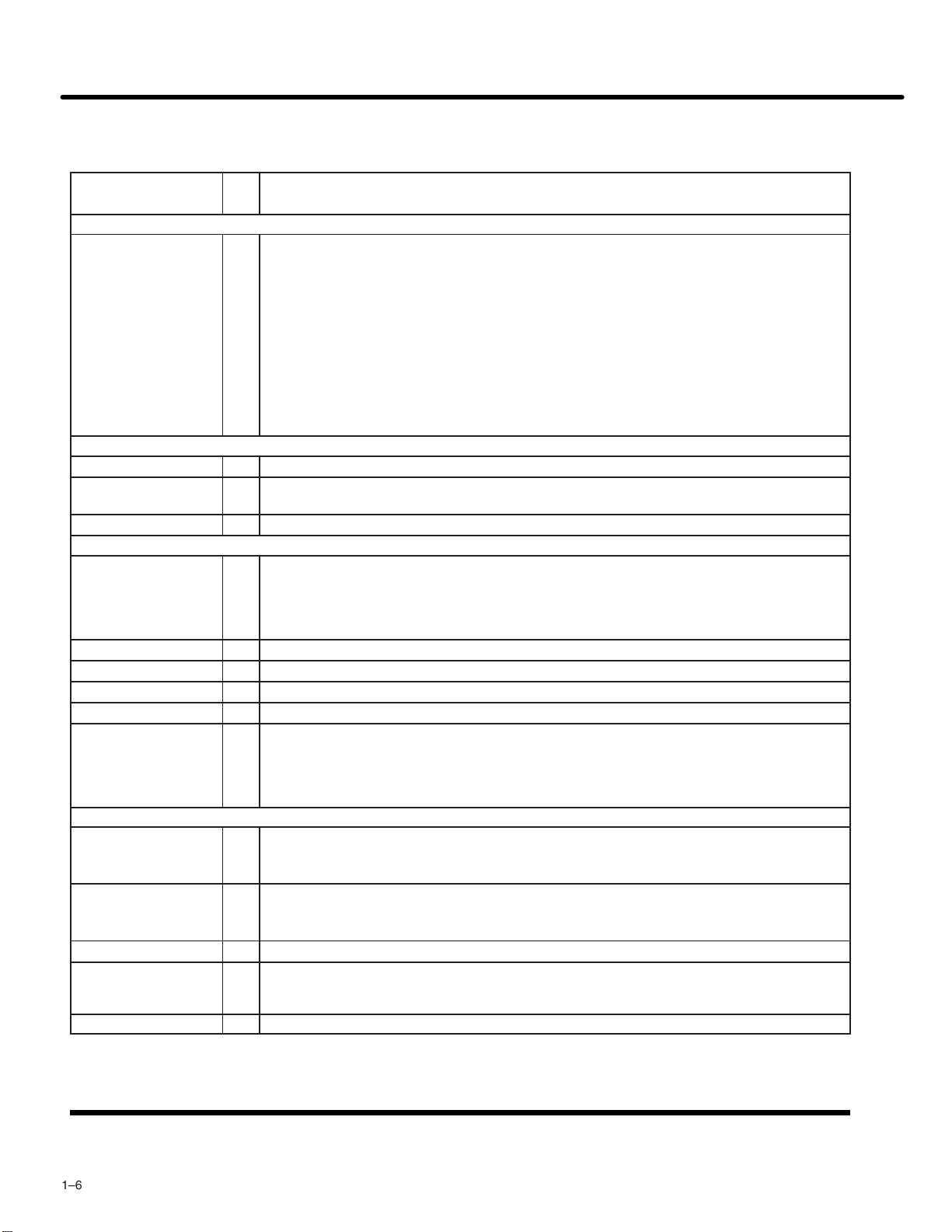

1.7 Terminal Functions

Table 1–1. Terminal Functions

TERMINAL

NAME NUMBER

Analog Video

VI_1_A

VI_1_B

VI_1_C

VI_2_A

VI_2_B

VI_2_C

VI_3_A

VI_3_B

VI_3_C

VI_4_A

Clock Signals

DATACLK 40 O Line-locked data output clock.

XTAL1 74 I

XTAL2 75 O External clock reference output. Not connected if XTAL1 is driven by an external single-ended oscillator.

Digital Video

C[9:0]/

GPIO[9:0]

D_BLUE 58 I Digital BLUE input from overlay device

D_GREEN 59 I Digital GREEN input from overlay device

D_RED 60 I Digital RED input from overlay device

FSO 57 I Fast-switch overlay between digital RGB and any video

Y[9:0]

Miscellaneous Signals

FSS/GPIO 35 I/O

GLCO/I2CA 37 I/O

INTREQ 30 O Interrupt request

PWDN 33 I

RESETB 34 I Reset input, active low

80

1

2

7

8

9

16

17

18

23

57, 58,

59, 60,

63, 64,

65, 66,

69, 70

43, 44,

45, 46,

47, 50,

51, 52,

53, 54

I/O

VI_1_x: Analog video input for CVBS/Pb/B/C

VI_2_x: Analog video input for CVBS/Y/G

VI_3_x: Analog video input for CVBS/Pr/R/C

VI_4_A: Analog video input for CVBS/Y

I

Up to 10 composite, 4 S-video, and 2 composite or 3 component video inputs (or a combination thereof)

can be supported.

The inputs must be ac-coupled. The recommended coupling capacitor is 0.1 µF.

The possible input configurations are listed in the input select register at I2C subaddress 00h (see

Section 2.11.1).

External clock reference input. It may be connected to an external oscillator with a 1.8-V compatible clock

signal or a 14.31818-MHz crystal oscillator.

Digital video output of CbCr, C[9] is MSB and C[0] is LSB. Unused outputs can be left unconnected. Also,

these terminals can be programmable general-purpose I/O.

O

For the 8-bit mode, the two LSBs are ignored.

Digital video output of Y/YCbCr, Y[9] is MSB and Y[0] is LSB.

O

For the 8-bit mode, the two LSBs are ignored. Unused outputs can be left unconnected.

Fast-switch (blanking) input. Switching signal between the synchronous component video (YPbPr/RGB)

and the composite video input.

Programmable general-purpose I/O

Genlock control output (GLCO). Two Genlock data formats are available: TI format and real time control

(RTC) format.

During reset, this terminal is an input used to program the I2C address LSB.

Power down input:

1 = Power down

0 = Normal mode

DESCRIPTION

1–6

11

Page 14

Table 1–1. Terminal Functions (Continued)

TVP5146

TERMINAL

NAME NUMBER

Host Interface

SCL 28 I I2C clock input

SDA 29 I/O I2C data bus

Power Supplies

AGND 26 I Analog ground. Connect to analog ground.

A18GND_REF 13 I Analog 1.8-V return

A18VDD_REF 12 I Analog power for reference 1.8 V

CH1_A18GND

CH2_A18GND

CH3_A18GND

CH4_A18GND

CH1_A18VDD

CH2_A18VDD

CH3_A18VDD

CH4_A18VDD

CH1_A33GND

CH2_A33GND

CH3_A33GND

CH4_A33GND

CH1_A33VDD

CH2_A33VDD

CH3_A33VDD

CH4_A33VDD

DGND

DVDD

IOGND 39, 49, 62 I Digital power return

IOVDD 38, 48, 61 I Digital power. Connect to 3.3 V or less for reduced noise.

PLL_A18GND 77 I Analog power return

PLL_A18VDD 76 I Analog power. Connect to 1.8 V.

Sync Signals

HS/CS/GPIO 72 I/O

VS/VBLK/GPIO 73 I/O

FID/GPIO 71 I/O

AVID/GPIO 36 I/O

79

10

15

24

78

11

14

25

3

6

19

22

4

5

20

21

27, 32, 42,

56, 68

31, 41, 55,

67

I/O

I Analog 1.8-V return

I Analog power. Connect to 1.8 V.

I Analog 3.3-V return

I Analog power. Connect to 3.3 V.

I Digital return

I Digital power. Connect to 1.8 V.

Horizontal sync output or digital composite sync output

Programmable general-purpose I/O

Vertical sync output (for modes with dedicated VSYNC) or VBLK output

Programmable general-purpose I/O

Odd/even field indicator output. This terminal needs a pulldown resistor.

Programmable general-purpose I/O

Active video indicator output

Programmable general-purpose I/O

DESCRIPTION

121413151416151716

1–7

Page 15

Page 16

Page 17

Page 18

Page 19

Philips SemiconductorsProduct specification

Hex inverting Schmitt trigger 74HC/HCT14

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1, 3, 5, 9, 11, 13 1A to 6A data inputs

2, 4, 6, 8, 10, 12 1Y to 6Y data outputs

7 GND ground (0 V)

14 V

CC

positive supply voltage

Fig.1 Pin configuration. Fig.2 Logic symbol. Fig.3 IEC logic symbol.

FUNCTION TABLE

INPUT OUTPUT

nA nY

L

H

Notes

1. H = HIGH voltage level

L = LOW voltage level

APPLICATIONS

• Wave and pulse shapers

• Astable multivibrators

• Monostable multivibrators

Fig.4 Functional diagram. Fig.5 Logic diagram

(one Schmitt trigger).

H

L

17

Page 20

Philips Semiconductors Product specification

74ALVT163732.5V/3.3V 16-bit transparent D-type latch (3-State)

LOGIC SYMBOL

47 46 44 43

1

1D0 1D1 1D2 1D3

1LE

1OE

1Q0 1Q1 1Q2651Q3

32

36 35 33 32

2D02D21 2D2 2D3

2LE

2OE

2Q0 2Q1 2Q2 2Q3

1413 1716

48

25

24

41 40 38 37

1D4 1D5 1D6 1D7

1Q4 1Q5 1Q6

30 29 27 26

2D4 2D5 2D6 2D7

2Q4 2Q5 2Q6 2Q7

98

2019 2322

1Q7

1211

SA00044

PIN DESCRIPTION

PIN NUMBER SYMBOL FUNCTION

47, 46, 44, 43, 41, 40, 38, 37,

36, 35, 33, 32, 30, 29, 27, 26

2, 3, 5, 6, 8, 9, 11, 12, 13,

14, 16, 17, 19, 20, 22, 23

1, 24 1OE, 2OE

48, 25 1LE, 2LE

4, 10, 15, 21, 28, 34, 39, 45 GND Ground (0V)

7, 18, 31, 42 V

1D0 – 1D7

2D0 – 2D7

1Q0 – 1Q7

2Q0 – 2Q7

CC

Data inputs

Data outputs

Output enable

inputs

(active-Low)

Enable inputs

(active-High)

Positive

supply voltage

LOGIC SYMBOL (IEEE/IEC)

1OE

1LE

2OE

2LE

1D1

1D2

1D3

1D4

1D5

1D6

1D7

1D8

2D1

2D2

2D3

2D4

2D5

2D6

2D7

2D8

1

48

24

25

47

46

44

43

41

40

38

37

36

35

33

32

30

29

27

26

1EN

C3

2EN

C4

3D

4D

PIN CONFIGURATION

1

1OE

2

1Q0

1Q1

3

GND

4

1Q2

5

6

1Q3

7

V

CC

8

1Q4

1Q5

9

GND

10

1Q6

11

1Q7

12

2Q0

13

2Q1

14

GND

15

16

2Q2

2Q3

17

18

V

CC

2Q4

19

20

2Q5

21

GND

22

2Q6

23

2Q7

24

2OE

1 ∇

2 ∇

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

SA00043

1LE

1D0

1D1

GND

1D2

1D3

V

CC

1D4

1D5

GND

1D6

1D7

2D0

2D1

GND

2D2

2D3

V

CC

2D4

2D5

GND

2D6

2D7

2LE

2

1Q1

3

1Q2

5

1Q3

6

1Q4

8

1Q5

9

1Q6

11

1Q7

12

1Q8

13

2Q1

14

2Q2

16

2Q3

17

2Q4

19

2Q5

20

2Q6

22

2Q7

23

2Q8

SW00010

18

Page 21

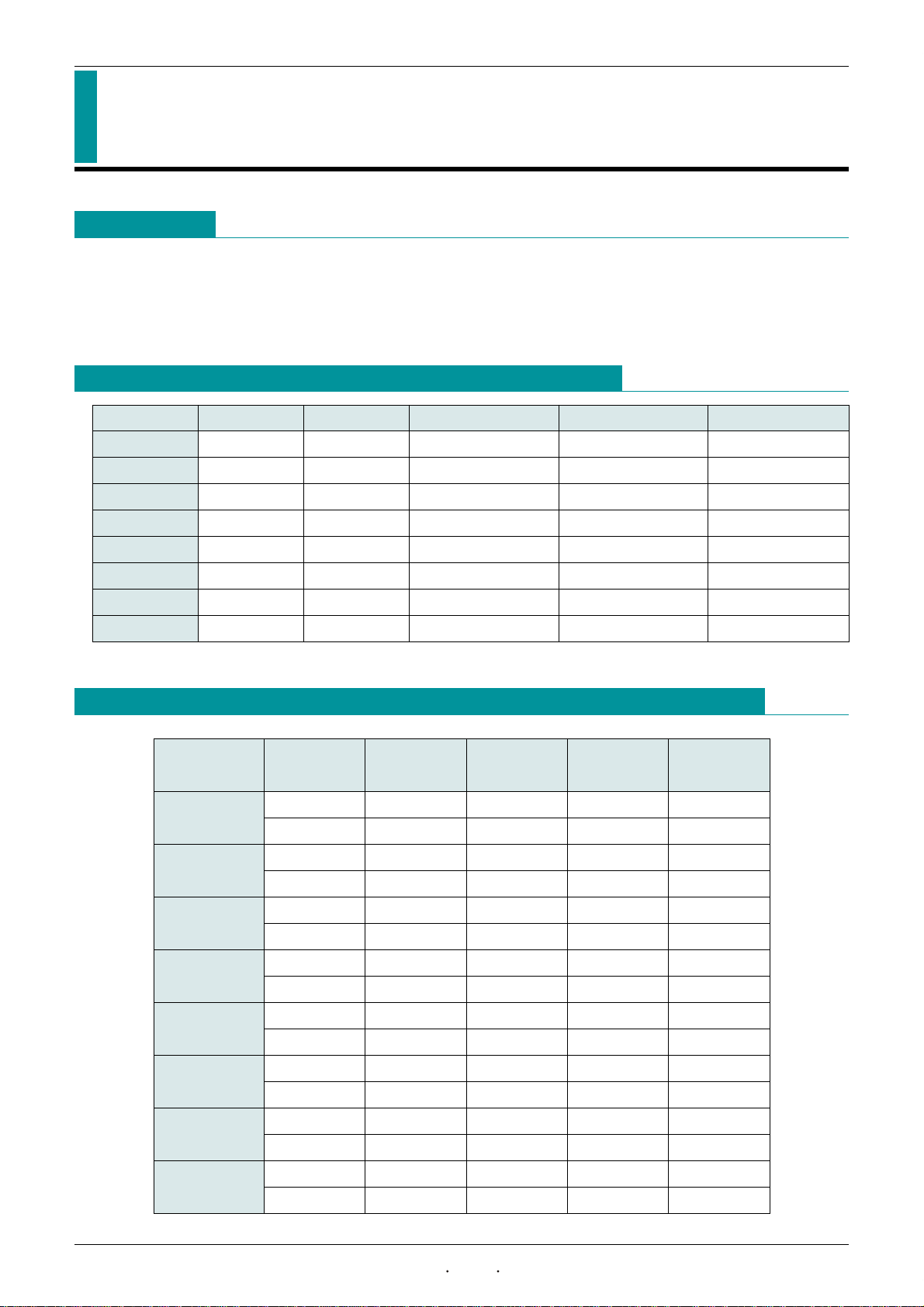

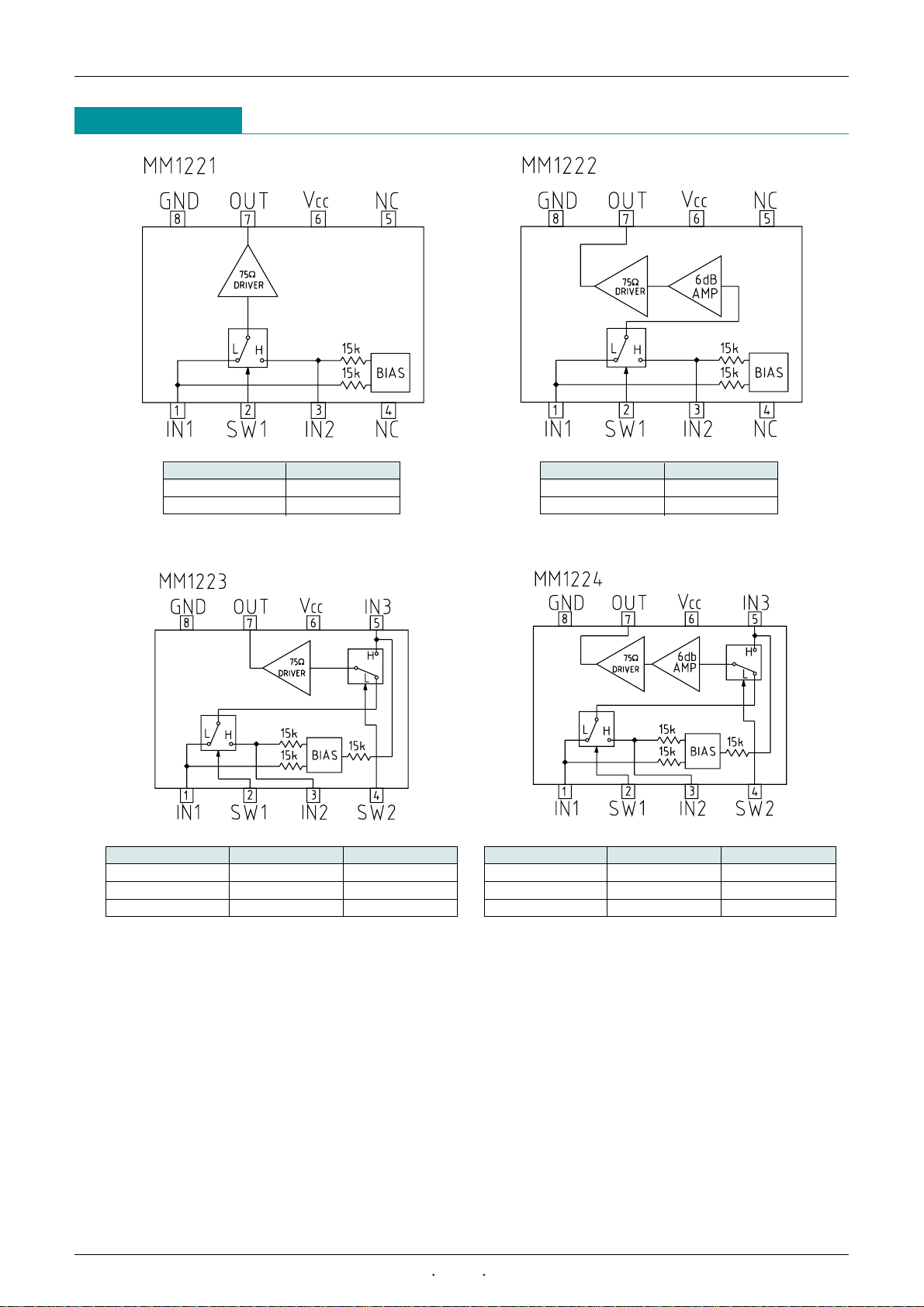

MITSUMI

2-Input 1-Output Video Switch (75Ω driver)/3-Input 1-Output Video Switch (75Ω driver) MM1221~1228

2-Input 1-Output Video Switch (75Ω driver)/3-Input 1-Output Video Switch (75Ω driver)

Monolithic IC MM1221~MM1228

Outline

These ICs are high grade video switches with 2-input 1-output or 3-input 1-output and built-in 75Ω driver.

The series includes those with and without built-in clamp and 6dB amp circuits.

Circuit configuration tables and block diagrams are as follows.

MM1228 is used as the representative model in this description.

MM1221~MM1228 Series Circuit Configuration Table

Model name # of Inputs # of Outputs 6dB amp circuit Clamp circuit

MM1221 2 1 No No 8~13V

MM1222 2 1 Yes No 8~13V

MM1223 3 1 No No 8~13V

MM1224 3 1 Yes No 8~13V

MM1225 2 1 No Yes 4.7~13V

MM1226 2 1 Yes Yes 4.7~13V

MM1227 3 1 No Yes 4.7~13V

MM1228 3 1 Yes Yes 4.7~13V

Power supply voltage range

MM1221~MM1228 Input/Output Voltage Measurement Values (typ.)

Model name

MM1221

MM1222

Power supply

5V 9V 12V Unit

voltage

Input voltage 4.53 6.05 V

Output voltage 4.5 6.1 V

Input voltage 4.05 5.4 V

Output voltage 5.34 7.12 V

MM1223

MM1224

MM1225

MM1226

MM1227

MM1228

Input voltage 4.53 6.05 V

Output voltage 4.5 6.1 V

Input voltage 4.05 5.4 V

Output voltage 5.34 7.12 V

Input voltage 1.27 2.17 2.86 V

Output voltage 1.31 2.25 2.96 V

Input voltage 1.3 2.2 2.9 V

Output voltage 1.4 2.23 2.88 V

Input voltage 1.27 2.17 2.86 V

Output voltage 1.31 2.25 2.96 V

Input voltage 1.3 2.2 2.9 V

Output voltage 1.4 2.23 2.88 V

19

Page 22

MITSUMI

2-Input 1-Output Video Switch (75Ω driver)/3-Input 1-Output Video Switch (75Ω driver) MM1221~1228

Block Diagram

Control input truth table

SW OUT

(MM1221~MM1228)

LIN1

HIN2

Control input truth table

SW OUT

LIN1

HIN2

Control input truth table Control input truth table

SW1 SW2 OUT

LLIN1

HLIN2

L/H H IN3

22

SW1 SW2 OUT

LLIN1

HLIN2

L/H H IN3

20

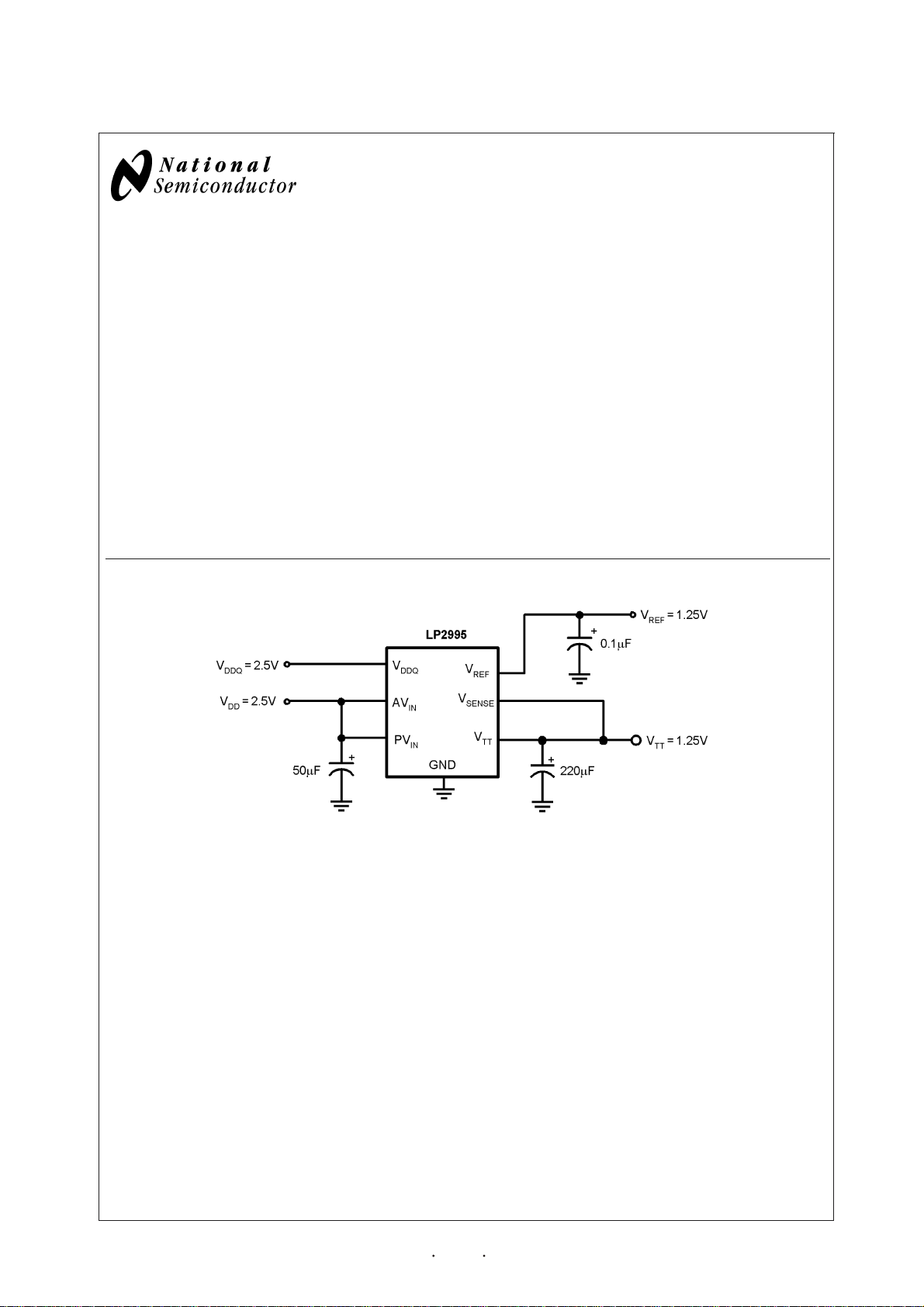

Page 23

LP2995

DDR Termination Regulator

LP2995 DDR Termination Regulator

July 2003

General Description

The LP2995 linear regulator is designed to meet the JEDEC

SSTL-2 and SSTL-3 specifications for termination of DDRSDRAM. The device contains a high-speed operational amplifier to provide excellent response to load transients. The

output stage prevents shoot through while delivering 1.5A

continuous current and transient peaks up to 3A in the

application as required for DDR-SDRAM termination. The

LP2995 also incorporates a V

load regulation and a V

chipset and DDR DIMMS.

Patents Pending

REF

pin to provide superior

SENSE

output as a reference for the

Typical Application Circuit

Features

n Low output voltage offset

n Works with +5v, +3.3v and 2.5v rails

n Source and sink current

n Low external component count

n No external resistors required

n Linear topology

n Available in SO-8, PSOP-8 or LLP-16 packages

n Low cost and easy to use

Applications

n DDR Termination Voltage

n SSTL-2

n SSTL-3

20039302

© 2003 National Semiconductor Corporation DS200393 www.national.com

21

Page 24

22

Page 25

MSP 34x5G PRELIMINARY DATA SHEET

CAPL_M

AHVSS

AGNDC

SC2_IN_L

SC2_IN_R

ASG

SC1_IN_L

SC1_IN_R

VREFTOP

MONO_IN

AVSS

RESETQ

I2S_DA_IN2

DVSS

DVSUP

ADR_CL

I2S_DA_IN1

I2S_DA_OUT

I2S_WS

I2S_CL

I2C_DA

I2C_CL

NC

SC1_OUT_L

SC1_OUT_R

VREF1

NC

AHVSUP

DACM_L

DACM_R

VREF2

NC

NC

ANA_IN1+

ANA_IN−

TESTEN

XTAL_IN

XTAL_OUT

AVSUP

TP

D_CTR_I/O1

D_CTR_I/O0

ADR_SEL

STANDBYQ

MSP 34x5G

34

35

36

37

38

39

40

41

42

43

44

22

21

20

19

18

17

16

15

14

13

12

1234567891011

33 32 31 30 29 28 27 26 25 24 23

Fig. 4–10: 44-pin PMQFP package

23

Page 26

11.Terminal for External Connection & Outline Drawing

24

Page 27

A

V33

R1

R4

R2

R3

10K

10K

10K

R11 10K

AO_FSYNC11

AO_IEC9585

AO_MCLKO11

RDS_DATA7

AI_FSYNC11

AI_MCLKO11

E5_GPIOx355,9

(BIO_PHY_PD)

AO_D111

AO_D211

AO_D311

AO_SCLK11

AI_D011

AI_SCLK11

(VI_AVID)

(MIC_DET)

(MUTE)

(INT_VI)

(/RST_VI)

V33

VI_VSYNC

VI_CLK0

1

TP1

1

TP2

1

(Reset_Audio)

GND

10K

AO_D0

E5_GPIOx33

(Input Only)

E5_GPIOx32

CLKI

CLKX

TCK

TDI

TDO

TMS

TRST_L

VI_D0

VI_D1

VI_D2

VI_D3

VI_D4

VI_D5

VI_D6

VI_D7

VI_D8

VI_D9

E5_GPIOx07

E5_GPIOx112

E5_GPIOx212

E5_GPIOx39

E5_GPIOx412

E5_GPIOx511

E5_GPIOx69

E5_GPIOx79

GND

R19 22

R21 22

R23 22

R24 22

R26 22

R29 22

R30 22

R33 22

R34 22

R35 22

E5_GPIOx35

(SCART_GPIO)

(SCART_GPIO)

(SCART_GPIO)

E5_GPIO6

E5_GPIOx0

E5_GPIOx1

E5_GPIOx2

E5_GPIOx3

E5_GPIOx4

E5_GPIOx5

E5_GPIOx6

E5_GPIOx7

TMS

TDI

TDO

TCK

TRST_L

4 4

GND

C1

27P

Y1

13.5MHZ

C2

27P

GND

VI_D[9..0]9

3 3

VI_VSYNC9

VI_CLK09

E5_GPIOx2

R36 10K

E5_GPIOx1

R37 10K

E5_GPIOx3

R38 10K

E5_GPIOx4

R39 10K

E5_GPIOx5

R40 10K

E5_GPIOx6

R41 10K

E5_GPIOx7

R42 10K

2 2

CVBS10

Y10

C10

Y/G10

Pb/B10

Pr/R10

V18_E5_DAC_DVDD

GND

V33_E5_DAC_AVDD

+

CA2

T47u/16

C6

C7

104

103

C10

C9

C8

104

103

104

1 1

E5_SDRAM_CLK#03

E5_SDRAM_CLK#13

A17

AO_D0

AO_1

B15

AO_D1

AO_2

B16

AO_D2

AO_3

B17

AO_D3

AOSCLK

B14

AO_SCLK

AOFSYNC

A14

AO_FSYNC

AOIEC

B13

AO_IEC958

A13

AO_MCLKI

AOMCLKO

A15

AO_MCLKO

C14

AI_D0

D14

AI_D1

AISCLK

A12

AI_SCLK

AIFSYNC

D13

AI_FSYNC

C13

AI_MCLKI

AIMCLKO

A16

AI_MCLKO

E1

CLKI

F1

CLKX

H1

CLKO

G1

BYPASS_PLL

B7

TCK

A7

TDI

C6

TDO

B6

TMS

D6

TRST_L

B10

VI_D0

C10

VI_D1

B11

VI_D2

C11

VI_D3

D11

VI_D4

D10

VI_D5

B12

VI_D6

C12

VI_D7

D12

VI_D8

A11

VI_D9

A10

VI_VSYNC0

A9

VI_CLK0

D7

VO_D0

C7

VO_D1

D8

VO_D2

C8

VO_D3

B8

VO_D4

D9

VO_D5

C9

VO_D6

B9

VO_D7

A8

VO_CLK

VDENC

SEL

A1

DAC1

A2

DAC2

A3

DAC3

A4

DAC4

A5

DAC5

A6

DAC6

D5

DAC_Dvdd (1.8v)

B2

DAC_Vdd0(3.3v)

B3

DAC_Vdd1(3.3v)

C5

DAC_Dvss

B4

DAC1bar

B5

DAC0bar

12

D2

IN4148

V33_E5_USB

12

D3

IN4148

VO_GND

VO_GND GND

E5_SDRAM_A03

E5_SDRAM_A13

E5_SDRAM_A23

E5_SDRAM_A33

E5_SDRAM_A43

E5_SDRAM_A53

E5_SDRAM_A63

E5_SDRAM_A73

E5_SDRAM_A83

E5_SDRAM_A93

E5_SDRAM_A103

E5_SDRAM_A113

E5_SDRAM_A123

E5_SDRAM_A143

E5_SDRAM_A153

E5_SDRAM_CS03

E5_SDRAM_CAS#3

E5_SDRAM_RAS#3

E5_SDRAM_CLKE3

E5_SDRAM_WE#3

E5_SDRAM_CLK03

E5_SDRAM_CLK13

3.3v only

012

CPST Y -

Y CPST -

C CPST -

G/Y Y -

B/Pb C CPST

R/Pr C CPST

+

GND

VREF3,4

GPIOx[31]

GPIOx[34]

CS[9]-

GPIOx[33]

GPIO[6]

GPIO[7]

CS[8]-

GPIOx[32]

GPIOx[35]

DACO

JTAG

PEC

GPIOx[45]

GPIOx[29]

2nd 24-bit

voutvin

VI_D0

VI_D1

VO_D16

VI_D2

VO_D17

VI_D3

VO_D18

VI_D4

VO_D19

VI_D5

VO_D20

VI_D6

VO_D21

VI_D7

VO_D22

VI_D8

VO_D23

VI_D9

GPIOx[0]

GPIOx[1]

GPIOx[2]

GPIOx[3]

GPIOx[4]

GPIOx[5]

GPIOx[6]

GPIOx[7]

GPIOx[8]

GPIOx[9]

GPIOx[10]

GPIOx[11]

GPIOx[12]

GPIOx[13]

GPIOx[14]

GPIOx[15]

GPIOx[30]

USB 1394

POWER

3.3V

GND

USB_Avdd0(3.3v)

USB_VSS0

F3

F4

C12

104

C11

10UF/1206

VREF

D16

SDRAM_VREF

AOUT

20-bit

vin

VI_D10

VI_D11

VI_D12

VI_D13

VI_D14

VI_D15

VI_D16

VI_D17

VI_D18

VI_D19

3.3V ONLY

Dplus_0

Dminus_0

Host_PO_0

G3G4H2

USB_D0-

USB_D0+

USB_PO0

E20

D20

SDRAM_CLK1

SDRAM_CLK_L1

AIN

SYSTEM

VIN

2nd

vout

VO_D0

VO_D1

VO_D2

VO_D3

VO_D4

VO_D5

VO_D6

VO_D7

Host_OC_0

H3

7

USB_OC0

L20

K20

SDRAM_CLK_L0

VOUT

GPIOx[43]

GPIOx[44]

7

7

C14

102

SDRAM_CLK0

GPIOx[36]

7

N17

N18

N19

SDRAM_CKE

SDRAM_WE_L

SDRAM_RAS_L

VIO

BIO_PHY_DATA6

BIO_PHY_DATA7

BIO_PHY_DATA6

BIO_PHY_DATA7

SSTL2_VDD

GND

P20

SDRAM_CAS_L

BIO_PHY_DATA4

BIO_PHY_DATA5

BIO_PHY_DATA4

BIO_PHY_DATA5

C15

102

A

B

E5_SDRAM_A9

E5_SDRAM_A7

E5_SDRAM_A6

E5_SDRAM_A8

E5_SDRAM_CS1

E5_SDRAM_A14

E5_SDRAM_A12

E5_SDRAM_A15

E5_SDRAM_A11

E5_SDRAM_A10

T20

V20

U19

W20

U18

V19

U20

Y20

R20

P19

P18

SDRAM__A6

SDRAM__A7

SDRAM__A8

SDRAM__A9

SDRAM__A17

SDRAM__A16

SDRAM__A10

SDRAM__A11

SDRAM__A12

SDRAM__A14

SDRAM__A15

*SDRAM__A13

BIO_PHY_DATA0

BIO_PHY_DATA1

BIO_PHY_DATA2

BIO_PHY_DATA3

BIO_PHY_CTL0

BIO_PHY_CTL1

BIO_LREQ

BIO_LPS

BIO_LINK_ON

BIO_PHY_CLK

VDD_PAD1

J2

L2L4L3J1K4K3K2J3K1N1M1J4L1

H4

7

7

7

7

7

7

7

7

BIO_LPS

BIO_LREQ

BIO_PHY_CLK

BIO_LINK_ON

BIO_PHY_CTL1

BIO_PHY_CTL0

BIO_PHY_DATA1

BIO_PHY_DATA2

BIO_PHY_DATA3

BIO_PHY_DATA0

C16

C17

102

104

E5_VDDREF E5_VDDX

C51

C52

103

104

GND GND GND

B

E5_SDRAM_DQ[31..0] 3

3

3

E5_SDRAM_DQS3

E5_SDRAM_DQ29

E5_SDRAM_DQ31

E5_SDRAM_DQ25

E5_SDRAM_DQ26

E5_SDRAM_DQ27

E5_SDRAM_DQ28

E5_SDRAM_DQ30

E5_SDRAM_DQ24

E5_SDRAM_DQM3

E5_SDRAM_A5

E5_SDRAM_A4

E5_SDRAM_A2

E5_SDRAM_A0

E5_SDRAM_A3

E5_SDRAM_A1

R17

T19

P17

R19

R18

T18

SDRAM__A0

SDRAM__A1

SDRAM__A2

SDRAM__A3

SDRAM__A4

SDRAM__A5

A18

B18

A20

A19

B20

C19

B19

C20

C18

D18

SDRAM_DQ24

SDRAM_DQ25

SDRAM_DQ27

SDRAM_DQ26

SDRAM_DQ28

SDRAM_DQ29

SDRAM_DQ30

SDRAM_DQ31

SDRAM_DQS3

SDRAM_DQM3

3

3

E5_SDRAM_DQS2

E5_SDRAM_DQM2

F19

F20

SDRAM_DQS2

SDRAM_DQM2

E5_SDRAM_DQS1

E5_SDRAM_DQ12

E5_SDRAM_DQ15

E5_SDRAM_DQ20

E5_SDRAM_DQ18

E5_SDRAM_DQ19

E5_SDRAM_DQ17

E5_SDRAM_DQ21

E5_SDRAM_DQ16

E5_SDRAM_DQ14

E5_SDRAM_DQ11

E5_SDRAM_DQ10

E5_SDRAM_DQ23

E5_SDRAM_DQ22

E19

E18

E17

SDRAM_DQ22

SDRAM_DQ23

E5_SDRAM_DQ13

E5_SDRAM_DQM1

G20

J18

H17

H19

H18

J17

G19

G18

G17

F18

F17

J20

H20

SDRAM_DQ15

SDRAM_DQ12

SDRAM_DQ14

SDRAM_DQ13

SDRAM_DQ11

SDRAM_DQ16

SDRAM_DQ17

SDRAM_DQ18

SDRAM_DQ19

SDRAM_DQ20

SDRAM_DQ21

SDRAM_DQS1

SDRAM_DQM1

DATAADDRCONTROL

SDRAM I/F

E5.1-BGA-308-A

U1

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

TOP VIEW

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

POWER GND

PADS CORE

3.3V 1.8V 3.3V

VDD_PAD2

VDD_PAD3

VDD_PAD4

VDD_PAD5

VDD_PAD6

VDD_PAD7

E12

T12

T11L5M5T9T10E9E10

7

7

C19

104

E5_AVDD

C54

C53

103

103

VDD_CORE1

E5_VCORE

C20

104

J5K5E11

E5_VPAD

7

7

7

7

C18

104

SDRAM

SDR

DDR

VDD_CORE8

VDD_CORE9

VDD_CORE2

VDD_CORE3

VDD_CORE4

VDD_CORE5

VDD_CORE6

VDD_CORE7

VDD_25V1

VDD_25V2

D19

C16

D17

T17

V17

SSTL2_VDD

C22

C21

+

104

104

C56

C55

102

104

J16

C23

T47u/16

VDD_25V3

VDD_25V4

K16

3.3V

2.5V 5V

VDD_25V5

VDD_25V6

L16

M16

E5_V5BIAS

104

C13

E5_AVDD

E5_VDDX

+

5V_BIAS0

D15

GND

C24

10UF/1206

BIAS

PLL PLL

AVDD1

AVDD2

C4E4D3D2E2C3D4E3D1

C

(RDY_FM)

E5_GPIOx25 12

(ATN_FM)

E5_GPIOx24 12

(FP SCLK)

E5_GPIOx41 12

(FP D_FM)

E5_GPIOx42 12

3

3

E5_SDRAM_DQ8

E5_SDRAM_DQ9

J19

K17

SDRAM_DQ9

SDRAM_DQ8

SDRAM_DQ10

3

3

E5_GPIOx24

E5_GPIOx25

E5_GPIOx42

E5_SDRAM_DQ0

E5_SDRAM_DQ3

E5_SDRAM_DQ6

E5_SDRAM_DQ2

E5_SDRAM_DQ7

E5_SDRAM_DQ1

E5_SDRAM_DQ4

E5_SDRAM_DQ5

E5_SDRAM_DQS0

E5_SDRAM_DQM0

N20

M19

M18

M17

L19

L18

L17

K18

M20

K19

SDRAM_DQ2

SDRAM_DQ1

SDRAM_DQ0

SDRAM_DQ3

SDRAM_DQ4

SDRAM_DQ5

SDRAM_DQ6

SDRAM_DQ7

SDRAM_DQS0

SDRAM_DQM0

E5_GPIOx41

Y19

U17

U15

W19

W17

W18

W16

V16

Y16

Y15

SPI_CS0

SPI_CS1

SPI_CS2

SPI_CLK

SPI_MOSI

SPI_MISO

UART1_TX

UART1_RX

UART1_CTS

UART1_RTS

CS10-

CS11-GPIOx[25]

GPIOx[42]

GPIOx[41]

GPIOx[24]

U16

V18

UART2_TX

UART2_RX

GPIOx[38]

GPIOx[37]

Y18

Y17

IDC_CLK

IDC_DAT

IDCUART1 UART2SPI IR

IRTX1

1

V15

U14

IRRX

IRTX1

CS6-

CS7-

GPIOx[39]

GPIOx[40]

SIO

HOST I/F

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

GPIOx[23]

GPIOx[22]

GPIOx[21]

GPIOx[20]

GPIOx[19]

GPIOx[18]

GPIOx[17]

GPIOx[16]

CD_C2PO

CD_BCK

CD_LRCK

ATAPI I/F

CD_DATA

SD/CD SBP

SPI_MOSI

SPI_MISO

SPI_SCK

SPI_CS2

E5_UART2_TX 5

E5_UART2_RX 5

SDA 6,7,9,11,12

SCL 6,7,9,11,12

E5_VDDX

R6

*10K

RSTMCONFIG

CS-

RDDMAREQ

HINTA0

A1

A2

RD

WAITDTACKD31

D30

D29

D28

D27

D26

D25

D24

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

SBP_FRAME

SBP_ACK

SBP_RD

SBP_REQ

SBP_CLK

SBP_D[7]

SBP_D[6]

SBP_D[5]

SBP_D[4]

SBP_D[3]

SBP_D[2]

SBP_D[1]

SBP_D[0]

SD_D[7]

SD_D[6]

SD_D[5]

SD_D[4]

SD_D[3]

SD_D[2]

SD_D[1]

SD_D[0]

SD_SECSTART

SD_ERROR

SD_CLK

SD_ACK

SD_RDREQ

SD_WRREQ

D1

*1N6263

1 2

R10 *0

LDSUDS-

PCMCIA_IOWPCMCIA_IORWR-

MA[21]

MA[20]

MA[19]

MA[18]

MA[17]

MA[16]

MA[15]

MA[14]

MA[13]

MA[12]

MA[11]

MA[10]

MA[9]

MA[8]

MA[7]

MA[6]

VCC

R233

10K

MASTERSLAVE

ATAPI_DATA15

ATAPI_DATA14

ATAPI_DATA13

ATAPI_DATA12

ATAPI_DATA11

ATAPI_DATA10

ATAPI_DATA9

ATAPI_DATA8

ATAPI_DATA7

ATAPI_DATA6

ATAPI_DATA5

ATAPI_DATA4

ATAPI_DATA3

ATAPI_DATA2

ATAPI_DATA1

ATAPI_DATA0

ATAPI_RESET_L

ATAPI_DMAACK_L

ATAPI_DMARQ

ATAPI_IORDY

ATAPI_INTRQ

ATAPI_DIOR_L

ATAPI_DIOW_L

CONTROL

VREF

ADDRDATA

MCONFIG

CS0_8BIT

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

DTACK-

MA[26]

MS[25]

MA[24]

MA[23]

MA[22]

AtapiAddr0

AtapiAddr1

AtapiAddr2

AtapiAddr3

AtapiAddr4

R234

10K

IR_FMUTE 11,12

ALE

RST-

OE-

UWE-

LWE-

WAIT-

CS5CS4CS3CS2CS1CS0-

MA[5]

MA[4]

MA[3]

MA[2]

MA[1]

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

D

OPEN FOR DW9916

R235

R236

10K

10K

R237 22

R238 22

R239 22

R240 22

R20 22

Y8

W15

MCONFIG

G2

Y11

R27 22

Y9

R28 22

V14

E5_GPIO0

V6

E5_GPIO1

V12

E5_GPIO2

W9

E5_GPIO3

V8

E5_GPIO4

W8

E5_GPIO5

U10

R31 22

Y7

U8

/DTACK

R32 22

U9

W3

Y2

Y6

Y4

Y5

Y3

V4

V5

W4

U5

W5

U6

W7

W6

U7

V7

V10

W11

Y10

V9

V11

Y12

W10

W12

Y13

U11

V13

W13

Y14

U12

U13

W14

V3

T4

V1

U2

U4

W2

U1

R4

R1

P3

P1

N2

M2

M3

M4

N3

N4

P2

P4

R3

T1

Y1

T2

W1

T3

V2

U3

R2

/WAIT

/E5_CS2

DI 9

DO 9

CL 9

CE 9

CN8

5P1.0

DI

DO

CL

CE

GND

E5_ALE 5,6

/SYS_RST 5,6

GND

/E5_OE 5,6

/E5_UDS 5

E5_GPIO0 12

E5_GPIO1 7

E5_GPIO2 5

E5_GPIO3 11

E5_GPIO4 12

E5_GPIO5 12

/E5_WEL 5,6

/WAIT 5

E5_/DTACK 5

/E5_CS1 5

/E5_CS0 6

E5_MA22 6

E5_MA5 5,6

E5_MA4 5,6

E5_MA3 5,6

E5_MA2 5,6

E5_MA1 5,6

HD15

HD14

HD13

HD12

HD11

HD10

HD9

HD8

HD7

HD6

HD5

HD4

HD3

HD2

HD1

HD0

AtapiAddr0 6

AtapiAddr1 6

AtapiAddr2 6

AtapiAddr3 6

AtapiAddr4 6

ATAPI_DATA15 6

ATAPI_DATA14 6

ATAPI_DATA13 6

ATAPI_DATA12 6

ATAPI_DATA11 6

ATAPI_DATA10 6

ATAPI_DATA9 6

ATAPI_DATA8 6

ATAPI_DATA7 6

ATAPI_DATA6 6

ATAPI_DATA5 6

ATAPI_DATA4 6

ATAPI_DATA3 6

ATAPI_DATA2 6

ATAPI_DATA1 6

ATAPI_DATA0 6

ATAPI_RESET 6

ATAPI_DMAACK_L 6

ATAPI_DMARQ 6

ATAPI_IORDY 6

ATAPI_INTRQ 6

ATAPI_DIOR_L 6

ATAPI_DIOW_L 6

1

2

3

4

5

(FP D_HOST)

(/RST_PHY)

(/ETHER_IRQ)

(RST_CS4360)

(AUDIO_SEL0)

(AUDIO_SEL1)

/DTACK

MCONFIG

/E5_CS0

/E5_CS1

/E5_CS2

E5_GPIO0

E5_GPIO1

E5_GPIO2

E5_GPIO3

E5_GPIO4

E5_GPIO5

/WAIT

E5_UART2_TX

E5_UART2_RX

1.8V

V18

HD[15..0]5,6

2.5V

V25

3.3V

V33

E5_VCORE

C5

104

R5 10K

R7 10K

R8 10K

R9 10K

R12 10K

R13 10K

R14 10K

R15 10K

R16 *10K

R18 10K

R22 10K

R25 10K

GND

E

V33

TX1

1

RX1

1

V18_E5_DAC_DVDD

FB1

601

CA1

C3

+

T47u/16

104

GND

SSTL2_VDD

L1 601

L2 601

L3 601

L4 601

C4

+

T47u/16

V33_E5_USB

E5_VDDX

E5_AVDD

E5_VDDREF

V33_E5_DAC_AVDD

E5_VPAD

DIGITAL

ATAPI2 I/F

AVDD0

AVDD3

VDDX

AGND1

AGND2

AGND0

AGND3

GNDX

VSS_PC2_CTR1

VSS_PC2_CTR2

VSS_PC2_CTR3

VSS_PC2_CTR4

VSS_PC2_CTR5

VSS_PC2_CTR6

VSS_PC2_CTR7

VSS_PC2_CTR8

VSS_PC2_CTR9

VSS_PC2_CTR10

VSS_PC2_CTR11

VSS_PC2_CTR12

VSS_PC2_CTR13

VSS_PC2_CTR14

VSS_PC2_CTR15

VSS_PC2_CTR16

VSS_PC2_CTR17

VSS_PC2_CTR18

VSS_PC2_CTR19

VSS_PC2_CTR20

VSS_PC2_CTR21

VSS_PC2_CTR22

VSS_PC2_CTR23

VSS_PC2_CTR24

VSS_PC2_CTR25

VSS_PC2_CTR26

VSS_PC2_CTR27

VSS_PC2_CTR28

VSS_PC2_CTR29

VSS_PC2_CTR30

C15

C17H8H9

H10

H11

H12

H13J8J9

J10

J11

J12

J13K8K9

K10

K11

K12

C35

102

C48

102

25

K13L8L9

C36

103

C49

103

F2

C34

C33

102

102

C47

C46

102

102

C

VSS_PC2_CTR31

L10

L11

L12

L13M8M9

M10

M11

M12

M13N8N9

GNDGND

General decoupling cap placement:

Caps with smaller capacitance values to be

closer to respective power pins compared to

those of larger values. All should be as

close as possible.

C25

+

C37

103

10UF/1206

C38

+

C50

10UF/1206

104

VDD_REF

R_REF

VSS_REF

VSS_PC2_CTR37

VSS_PC2_CTR38

VSS_PC2_CTR32

VSS_PC2_CTR33

VSS_PC2_CTR34

VSS_PC2_CTR35

VSS_PC2_CTR36

N12

N13

N10

N11

C2C1B1

E5_VDDREF

R43

1.18K 1%

GND

C26

+

10UF/1206

C39

+

10UF/1206

C28

C29

C27

104

104

104

C40

C41

C42

104

104

104

E5_VPAD

C30

C31

C32

104

104

104

GND

E5_VCORE

C43

C44

C45

104

104

104

GND

D

5V

VCC

LSI Logic Corp

Title

E5.1

Size Document Number Rev

Date: Sheet

HDW-10-310000-1 A1

2

E

E5_V5BIAS

of

12Monday, June 07, 2004

Page 28

A

B

C

D

E

TERMINATION

AT E5.1

4 4

E5_SDRAM_DQ0

E5_SDRAM_DQ1

E5_SDRAM_DQ2

E5_SDRAM_DQ3

E5_SDRAM_DQ4

E5_SDRAM_DQ5

E5_SDRAM_DQ6

E5_SDRAM_DQ7

E5_SDRAM_DQ8

E5_SDRAM_DQ9

E5_SDRAM_DQ10

E5_SDRAM_DQ11

E5_SDRAM_DQ12

E5_SDRAM_DQ13

E5_SDRAM_DQ14

E5_SDRAM_DQ15

E5_SDRAM_DQ16

E5_SDRAM_DQ17

E5_SDRAM_DQ18

E5_SDRAM_DQ19

E5_SDRAM_DQ20

E5_SDRAM_DQ21

E5_SDRAM_DQ22

3 3

2 2

E5_SDRAM_DQ23

E5_SDRAM_DQ24

E5_SDRAM_DQ25

E5_SDRAM_DQ26

E5_SDRAM_DQ27

E5_SDRAM_DQ31

E5_SDRAM_DQ28

E5_SDRAM_DQ30

E5_SDRAM_DQ29

E5_SDRAM_DQM0 2

E5_SDRAM_DQM1 2

E5_SDRAM_DQM2 2

E5_SDRAM_DQM3 2

E5_SDRAM_A1 2

E5_SDRAM_A6 2

E5_SDRAM_A3 2

E5_SDRAM_A15 2

E5_SDRAM_A8 2

E5_SDRAM_A0 2

E5_SDRAM_A4 2

E5_SDRAM_A2 2

E5_SDRAM_A7 2

E5_SDRAM_A14 2

E5_SDRAM_A9 2

E5_SDRAM_A12 2

E5_SDRAM_A11 2

E5_SDRAM_A10 2

E5_SDRAM_A5 2

E5_SDRAM_DQS0 2

E5_SDRAM_DQS1 2

E5_SDRAM_DQS2 2

E5_SDRAM_DQS3 2

E5_SDRAM_CLK0 2

E5_SDRAM_CLK1 2

E5_SDRAM_CLK#0 2

E5_SDRAM_CLK#1 2

E5_SDRAM_RAS# 2

E5_SDRAM_CLKE 2

E5_SDRAM_CAS# 2

E5_SDRAM_WE# 2

E5_SDRAM_CS0 2

RP1 51/RP

RP3 51/RP

1 8

2 7

3 6

4 5

RP5 51/RP

RP7 51/RP

RP9 51/RP

RP11 51/RP

1 8

2 7

3 6

4 5

RP12 51/RP

RP14 51/RP

1 8

2 7

3 6

4 5

RP16 22/RP

1 8

2 7

3 6

4 5

RP18 22/RP

RP20 22/RP

1 8

2 7

3 6

4 5

RP22 22/RP

RP24 22/RP

1 8

2 7

3 6

4 5

R44 51

R45 51

R47 51

R49 51

R52 22

R53 22

R55 22

R57 22

RP26 22/RP

1 8

2 7

3 6

4 5

R65 22

SDRAM_DQ0

18

SDRAM_DQ1 SDRAM_DQ0

27

SDRAM_DQ2

36

SDRAM_DQ3

45

SDRAM_DQ4

SDRAM_DQ5

SDRAM_DQ6

SDRAM_DQ7

SDRAM_DQ8

18

SDRAM_DQ9

27

SDRAM_DQ10

36

SDRAM_DQ11

45

SDRAM_DQ12

18

SDRAM_DQ13

27

SDRAM_DQ14

36

SDRAM_DQ15

45

SDRAM_DQ16

18

SDRAM_DQ17

27

SDRAM_DQ18

36

SDRAM_DQ19

45

SDRAM_DQ20

SDRAM_DQ21

SDRAM_DQ22

SDRAM_DQ23

SDRAM_DQ24

45

SDRAM_DQ25

36

SDRAM_DQ26

27

SDRAM_DQ27

18

SDRAM_DQ31

SDRAM_DQ28

SDRAM_DQ30

SDRAM_DQ29

SDRAM_DQM0

SDRAM_DQM1

SDRAM_DQM2

SDRAM_DQM3

SDRAM_A1

18

SDRAM_A6

27

SDRAM_A3

36

SDRAM_A15

45

SDRAM_A8

SDRAM_A0

SDRAM_A4

SDRAM_A2

SDRAM_A7

18

SDRAM_A14

27

SDRAM_A9

36

SDRAM_A12

45

SDRAM_A11

SDRAM_A10

SDRAM_A5

SDRAM_DQS0

SDRAM_DQS1

SDRAM_DQS2

SDRAM_DQS3

SDRAM_CLK0

SDRAM_CLK1

SDRAM_CLK#0

SDRAM_CLK#1

SDRAM_RAS#

SDRAM_CLKE

SDRAM_CAS#

SDRAM_WE#

SDRAM_CS0

SDRAM_DQ[31..0]4E5_SDRAM_DQ[31..0] 2

C78

C77

C76

104

C89

104

103

104

C91

C90

103

104

DDR TERMINATION VOLTAGE REGULATOR

VREF needs to be decoupled

to both SSTL2_VDD and SSTL2_GND with balanced

decoupling capacitors.

VREF should be routed over a

reference plane and isolated, and possibly

shielded with both SSTL2_VDD and SSTL2_GND

SSTL2_VDD

C57

104

C61

104

SSTL2_VDD

C64

104

C70

104

SSTL2_VDD

C80

C79

104

103

C92

C93

103

104

VREF

VREF2,4

The VTT side of the terminaton resistors should be placed

on a wide VTT island on the surface layer. The island is

located at each end of the bus, so it does not interfere

with the signal routing.

C59

C58

104

C62

104

C65

104

C71

104

C81

104

C94

104

C107

104

C60

103

103

C63

103

C66

C67

C68

103

103

C72

C73

103

103

C82

C83

102

102

C95

C96

102

102

C69

104

104

C74

C75

104

104

C85

C84

104

102

C98

C97

104

102

U2

1

NC

2

GND

3

VSENSE

4 5

VREF VDDQ

LP2995

GND_SSTL2

VTT

PVIN

AVIN

GND_SSTL2

VTT

GND_SSTL2

8

7

6

VREF

VTT

GND_SSTL2

VTT

VTT

+

CA4

220u/16

VTT

SSTL2_VDD

TERMINATION

AT DDR

VREF 2,4

SSTL2_VDD

C86

C87

104

102

C100

C99

102

104

GND_SSTL2

CA3

+

10u/16

C102

+

220u/16

C106

104

C104

104

C88

102

C101

102

SDRAM_DQ[31..0]4

SDRAM_DQ1

SDRAM_DQ2

SDRAM_DQ3

SDRAM_DQ4

SDRAM_DQ5

SDRAM_DQ6

SDRAM_DQ7

SDRAM_DQ8

SDRAM_DQ9

SDRAM_DQ10

SDRAM_DQ11

SDRAM_DQ12

SDRAM_DQ13

SDRAM_DQ14

SDRAM_DQ15

SDRAM_DQ16

SDRAM_DQ17

SDRAM_DQ18

SDRAM_DQ19

SDRAM_DQ20

SDRAM_DQ21

SDRAM_DQ22

SDRAM_DQ23

SDRAM_DQ24

SDRAM_DQ25

SDRAM_DQ26

SDRAM_DQ27

SDRAM_DQ28

SDRAM_DQ29

SDRAM_DQ30

SDRAM_DQ31

SDRAM_A0 4

SDRAM_A1 4

SDRAM_A2 4

SDRAM_A3 4

SDRAM_A7 4

SDRAM_A6 4

SDRAM_A5 4

SDRAM_A4 4

SDRAM_A12 4

SDRAM_A11 4

SDRAM_A9 4

SDRAM_A8 4

SDRAM_RAS# 4

SDRAM_A14 4

SDRAM_A15 4

SDRAM_A10 4

SDRAM_DQS0 4

SDRAM_DQS1 4

SDRAM_DQS2 4

SDRAM_DQS3 4

SDRAM_DQM0 4

SDRAM_DQM1 4

SDRAM_DQM2 4

SDRAM_DQM3 4

SDRAM_CLK#0 4

SDRAM_CLK#1 4

SDRAM_CLK0 4

SDRAM_CLK1 4

SDRAM_CLKE 4

SDRAM_WE# 4

SDRAM_CAS# 4

SDRAM_CS0 4

+

C103

T47u/16

VREF

VREF 2,4

C105

104

RP2 51/RP

RP4 51/RP

RP6 51/RP

4 5

3 6

2 7

1 8

RP8 51/RP

4 5

3 6

2 7

1 8

RP10 51/RP

RP13 51/RP

RP15 51/RP

RP17 51/RP

RP19 51/RP

RP21 51/RP

1 8

2 7

3 6

4 5

RP23 51/RP

1 8

2 7

3 6

4 5

RP25 51/RP

R46 51

R48 51

R50 51

R51 51

R54 51

R56 51

R58 51

R59 51

R60 51

R61 51

R62 51

R63 51

R64 51

R66 51

R67 51

R68 51

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

VTT

1 1

LSI LOGIC

560 COTTONWOOD DR.

MILPITAS, CA 95035

U. S. A.

Title

TERM AT E5

Size Document Number Rev

C

A

B

C

26

D

Date: Sheet

E

312Monday, June 07, 2004

D0

of

Page 29

A

B

C

D

E

C119

104

C129

102

C136

104

LAYOUT

NOTE:

PLACEMENT

E5

C110

104

C120

102

C130

102

C137

102

C111

102

+

SDRAM_CS0

SDRAM_CLK1

SDRAM_CLK0

C121

102

C131

T47u/16

C138

102

C112

102

C122

102

C139

102

M2

U25

M1

U22

C113

102

C123

102

C140

102

D

C114

+

10UF/1206

GND_SSTL2

GND

LSI LOGIC

560 COTTONWOOD DR.

MILPITAS, CA 95035

U. S. A.

Title

2 (8M x 16) DDR SDRAM

Size Document Number Rev

Custom

Date: Sheet

E

412Monday, June 07, 2004

A1

of

SDRAM_DQ[31..0]3

SDRAM_A03

SDRAM_A13

SDRAM_A23

SDRAM_A33

SDRAM_A43

4 4

SDRAM_A53

SDRAM_A63

SDRAM_A73

SDRAM_A83

SDRAM_A93

SDRAM_A103

SDRAM_A113

SDRAM_A123

SDRAM_A143

SDRAM_A153

SDRAM_CS03

SDRAM_CLKE3

SDRAM_RAS#3

SDRAM_CAS#3

SDRAM_WE#3

SDRAM_DQM03

SDRAM_DQM13

SDRAM_DQS03

SDRAM_DQS13

SDRAM_CLK03

SDRAM_CLK#03

SDRAM_A0

SDRAM_A1

SDRAM_A2

SDRAM_A3

SDRAM_A4

SDRAM_A5

SDRAM_A6

SDRAM_A7

SDRAM_A8

SDRAM_A9

SDRAM_A10

SDRAM_A11

SDRAM_A12

SDRAM_A14

SDRAM_A15

VREF2,3

DDR_VDD

3 3

SDRAM_A03

SDRAM_A13

SDRAM_A23

SDRAM_A33

SDRAM_A43

SDRAM_A53

SDRAM_A63

SDRAM_A73

SDRAM_A83

SDRAM_A93

SDRAM_A103

SDRAM_A113

SDRAM_A123

SDRAM_A143

2 2

SDRAM_A153

SDRAM_CS03

SDRAM_DQM23

SDRAM_DQM33

SDRAM_DQS23

SDRAM_DQS33

SDRAM_CLK13

SDRAM_CLK#13

SDRAM_A0

SDRAM_A1

SDRAM_A2

SDRAM_A3

SDRAM_A4

SDRAM_A5

SDRAM_A6

SDRAM_A7

SDRAM_A8

SDRAM_A9

SDRAM_A10

SDRAM_A11

SDRAM_A12

SDRAM_A14

SDRAM_A15

DDR_VDD

SSTL2_VDD

U3

29

A0

30

A1

31

A2

32

A3

35

A4

36

A5

37

A6

38

A7

39

A8

40

A9

28

A10/AP

41

A11

42

A12

26

BA0

27

BA1

24

CS#

44

CKE

23

RAS#

22

CAS#

21

WE#

20

LDM

47

UDM

16

LDQS

51

UDQS

45

CLK

46

CLK#

49

VREF

1

VCC

18

VCC

33

VCC

3

VCCQ

9

VCCQ

15

VCCQ

55

VCCQ

61

VCCQ

8MX16 DDR

C124 10UF/1206

U4

29

A0

30

A1

31

A2

32

A3

35

A4

36

A5

37

A6

38

A7

39

A8

40

A9

28

A10/AP

41

A11

42

A12

26

BA0

27

BA1

24

CS#

44

CKE

23

RAS#

22

CAS#

21

WE#

20

LDM

47

UDM

16

LDQS

51

UDQS

45

CLK

46

CLK#

49

VREF

1

VCC

18

VCC

33

VCC

3

VCCQ

9

VCCQ

15

VCCQ

55

VCCQ

61

VCCQ

8MX16 DDR

C141 10UF/1206

2

D0

4

D1

5

D2

7

D3

8

D4

10

D5

11

D6

13

D7

54

D8

56

D9

57

D10

59

D11

60

D12

62

D13

63

D14

65

D15

14

NC

17

NC

19

NC

25

NC

43

NC

50

NC

53

NC

34

GND

48

GND

66

GND

6

GNDQ

12

GNDQ

52

GNDQ

58

GNDQ

64

GNDQ

+

2

D0

4

D1

5

D2

7

D3

8

D4

10

D5

11

D6

13

D7

54

D8

56

D9

57

D10

59

D11

60

D12

62

D13

63

D14

65

D15

14

NC

17

NC

19

NC

25

NC

43

NC

50

NC

53

NC

34

GND

48

GND

66

GND

6

GNDQ

12

GNDQ

52

GNDQ

58

GNDQ

64

GNDQ

+

GND

GND

SDRAM_DQ0

SDRAM_DQ1

SDRAM_DQ2

SDRAM_DQ3

SDRAM_DQ4

SDRAM_DQ5

SDRAM_DQ6

SDRAM_DQ7

SDRAM_DQ8

SDRAM_DQ9

SDRAM_DQ10

SDRAM_DQ11

SDRAM_DQ12

SDRAM_DQ13

SDRAM_DQ14

SDRAM_DQ15

SDRAM_DQ16

SDRAM_DQ17

SDRAM_DQ18

SDRAM_DQ19

SDRAM_DQ20

SDRAM_DQ21

SDRAM_DQ22

SDRAM_DQ23

SDRAM_DQ24

SDRAM_DQ25

SDRAM_DQ26

SDRAM_DQ27

SDRAM_DQ28

SDRAM_DQ29

SDRAM_DQ30

SDRAM_DQ31

SSTL2_VDD

FB2

B601

V33

Option for DDR with 3.3V VDD

FB3

*B601

CA5

+

T47u/16

SSTL2_VDD

C116

C115

104

104

GND

DDR_VDD

C126

C125

104

104

GND

SSTL2_VDD

C133

C132

104

104

GND

DDR_VDD

GND

C117

104

C127

104

C134

104

C108

104

C109

104

C118

104

C128

102

C135

104

1 1

A

B

27

C

Page 30

A

B

C

D

E

4 4

E-Link III

Connector

C142

*47u/16

V33

GND

C143

+

*104

GND

J1

12

34

56

78

910

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

*HEADER 20X2

GND

/ETHER_IRQ

3 3

/E5_CS1 2

E5_ALE 2,6

E5_MA2 2, 6

HD15 2,6

HD13 2,6 HD142,6

HD11 2,6

HD9 2,6

HD8 2,6

HD6 2,6

HD2 2,6

E5_GPIO2 2

/E5_OE 2,6

/E5_WEL 2,6

E5_MA5 2, 6

E5_MA4 2, 6

E5_UART2_TX 2

UART

R75

*0

E5_UART2_TX2

2 2

E5_UART2_RX2

J2

1

+

+

3

+

+

5

+

+

7

+

+

9

+

+

DNS CON5X2

2

4

6

8

10

GNDGND

E5_UART2_RX2

GND

FB4 *601

/SYS_RST2,6

E5_MA32,6

E5_MA12,6

HD122,6

HD102,6

HD72,6

HD52,6HD4 2,6

HD32,6

HD12,6HD0 2,6

E5_/DTACK2

/E5_UDS2

/RST_SW

/WAIT2

V33

R77

*10K

/RST_HOST12

/RST_HOST

/RST_SW

D5

C146

104

IN4148

1 2

R69

10K

R73

10K

11 10

V33

2

U5E

74AHCT14

D4

*IN4148

1 2

VCC

E5_GPIOx352,9 /RST_AUDIO 11,12

RESET CIRCUITRY

V33

13

Q1

3906

D6

IN4148

5 6

13 12

1 2

U5C

74AHCT14

U5F

74AHCT14

C144

10u/16

VCC

+

R71

10K

9 8

U5D

74AHCT14

1 2

R76

33

C147

104

U5A

74AHCT14

R74

*0

R78

330

R79

120

3 4

R72

0

/RST_AUDIO

L5

0

U5B

74AHCT14

SPDIF_OUT 12AO_IEC9582

R70

OPTICAL 12

C145

102

/SYS_RST2,6

0

GND

1 1

A

B

C

28

D

LSI LOGIC

560 COTTONWOOD DR.

MILPITAS, CA 95035

U. S. A.

Title

FP, RST, IR, AV IO/ELink-3 CON, UART

Size Document Number Rev

A3

Date: Sheet

512Monday, June 07, 2004

of

E

A1

Page 31

A

B

C

D

E

FLASH MEMORY(2 or 4 or 8 Mb)

HD[15..0]2,5

HD0

HD1

4 4

V33

C152

C155

102

+

10u/16

C154

104

V33

3 3

U9

1

A0

VCC

2

A1

WP

3

A2

SCL

4 5

GND SDA

*AT24C16

8

7

6

*104

C158

VCC

R88

R89

2.2K

2.2K

SCL

SCL 2,7,9,11,12

SDA

SDA 2,7,9,11,12

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

E5_ALE 2,5

C153

104

C157

104

E5_MA1 2,5

E5_MA2 2,5

E5_MA3 2,5

E5_MA4 2,5

E5_MA5 2,5

E5_MA22 2

U7

47

1A1

46

1A2

44

1A3

43

1A4

41

1A5

40

1A6

38

1A7

37

1A8

1

1OE

48

1LE

36

2A1

35

2A2

33

2A3

32

2A4

30

2A5

29

2A6

27

2A7

26

2A8

24

2OE

25

2LE

V33

7

VCC

18

VCC

31

VCC

42

VCC

74LVC16373

2

1B1

3

1B2

5

1B3

6

1B4

8

1B5

9

1B6

11

1B7

12

1B8

13

2B1

14

2B2

16

2B3

17

2B4

19

2B5

20

2B6

22

2B7

23

2B8

4

GND

10

GND

15

GND

21

GND

28

GND

34

GND

39

GND

45

GND

BA6

BA7

BA8

BA9

BA11

BA12

BA13

BA14

BA15

BA16

BA17

BA18

BA19

BA20

BA21

BA1

BA2

BA3

BA4

BA5

BA22

BA[22..1]

BA16

BA15

BA14

V33

BA13BA10

BA12

BA11

R82

R80

*4.7k

/E5_WEL2,5

/SYS_RST2,5

R83

0

2MB(Default)

BA10

BA9

A19/A19/A21

NC/A20/A20

10K

ACC

WP#/ACC

RY/BY/A19

BA19

BA18

BA8

BA7

BA6

BA5

BA4

BA3

BA2

BA1

BA17

BA22

BA21

BA20

Size Stuff Not Stuff

1MB R85,R86,R87,R90

4MB

8MB

SKT-U2

SKT-TSOP48

U8

1

A15

2

A14

3

A13

4

A12

5

A11

6

A10

7

A9

8

A8

9

A19/A19/A21

10

NC/A20/A20

11

WE

12

RST

13

ACC

14

WP/ACC

15

RY/BY/A19

16

A18

17

A17

18

A7

19

A6

20

A5

21

A4

22

A3

23

A2

24

A1

MX29LV160

V33

R81 *4.7k

R84 0

R85 DNS-0

R86 DNS-0

R87 DNS-0

R90 0

R90

R86,R90

R85,R86,R87 R90

R85,R86,R87

R85,R87

BYTE/VIO

V33

BA17

48

A16

47

46

VSS

D15

D14

D13

D12

VCC

D11

D10

VSS

HD15

45

HD7

44

D7

HD14

43

HD6

42

D6

HD13

41

HD5

40

D5

HD12

39

HD4

38

D4

37

HD11

36

HD3

35

D3

HD10

34

HD2

33

D2

HD9

32

D9

HD1

31

D1

HD8

30

D8

HD0

29

D0

28

OE

27

26

CE

BA1

25

A0

C156

104

WP#/ACC/SYS_RST

A19/A19/A21

NC/A20/A20

RY/BY/A19

HD[15..0] 2,5

/E5_OE 2,5

/E5_CS0 2

DEDICATED ATAPI INTERFACE

R105

680

VCC

C159

22PF

R91

4.7K

INT_ATA

IORDY

DMARQ

R106

4.7K

R101 0

R102 82

R103 82

R104 82

2 2

ATAPI_RESET2

1 1

A

RSTATA

ATAPI_INTRQ2

ATAPI_IORDY2

ATAPI_DMARQ2

VCC

R92

10K

ATAPI_DATA8 2

ATAPI_DATA7 2

ATAPI_DATA9 2

ATAPI_DATA6 2

ATAPI_DATA10 2

ATAPI_DATA5 2

ATAPI_DATA11 2

ATAPI_DATA4 2

ATAPI_DATA12 2

ATAPI_DATA3 2

ATAPI_DATA13 2

ATAPI_DATA2 2

ATAPI_DATA14 2

ATAPI_DATA1 2

ATAPI_DATA15 2

ATAPI_DATA0 2

ATAPI_DIOW_L 2

ATAPI_DIOR_L 2

ATAPI_DMAACK_L 2

AtapiAddr1 2

AtapiAddr0 2

AtapiAddr2 2

AtapiAddr3 2

AtapiAddr4 2

B

RP27 33/RP

RP28 33/RP

RP29 33/RP

RP30 33/RP

RP31 33/RP

RP32 33/RP

45

36

27

18

45

36

27

18

45

36

27

18

45

36

27

18

45

36

27

18

45

36

27

18

HD_AT8

HD_AT7

HD_AT9

HD_AT6

HD_AT10

HD_AT5

HD_AT11

HD_AT4

HD_AT12

HD_AT3

HD_AT13

HD_AT2

HD_AT14

HD_AT1

HD_AT15

HD_AT0

DIOW

DIOR

DMACK

ATA_A1

ATA_A0

ATA_A2

CS1FX

CS3FX

RSTATA

FB5 B601

HD_AT7

FB6 B601

HD_AT6

FB8 B601

HD_AT5

FB10 B601

HD_AT4

FB12 B601

HD_AT3

FB14 B601

HD_AT2

FB16 B601

HD_AT1

FB18 B601

HD_AT0

FB20 B601

DMARQ

FB22 B601

DIOW

FB23 B601

DIOR

FB24 B601

IORDY

FB25 B601

DMACK

FB26 B601

INT_ATA

FB27 B601

ATA_A1

FB28 B601

ATA_A0

FB29 B601

CS1FX

FB31 B601

C

29

J3

12

34

56

78

910

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

HEADER 20X2

FB7 B601

FB9 B601

FB11 B601

FB13 B601

FB15 B601

FB17 B601

FB19 B601

FB21 B601

FB30 B601

FB32 B601

D

HD_AT8

HD_AT9

HD_AT10

HD_AT11

HD_AT12

HD_AT13

HD_AT14

HD_AT15

KEYWAY (NO PIN)

CAB_SEL

ATA_A2

CS3FX

HOST Read

HD[15..0]2,5

R115

0

LSI LOGIC

560 COTTONWOOD DR.

MILPITAS, CA 95035

U. S. A.

Title

Size Document Number Rev

C

Date: Sheet

V33

R94 DNS-4.7K

R96 DNS-4.7K

R95 DNS-4.7K

R93 DNS-4.7K

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

R108 DNS-4.7K

R110 DNS-4.7K

R109 DNS-4.7K

R107 DNS-4.7K

HD[1:0]

HD[3:2]

HD[7]

FLASH, ATA, EEPROM

Samsung - K4H281638D-TCB3

00

01

Micron - MT46V8M16-55

ESMT - M13S128168A-6T

10

Nanya

11

64Mb DDR SDRAM10

00

128Mb DDR SDRAM

01

256Mb DDR SDRAM

Reserve11

0 Normal Mode (Jumper 1-2)

1

Debuge Mode (Jumper 2-3)

R98 DNS-4.7K

R97 DNS-4.7K

R99 DNS-4.7K

R100 DNS-4.7K

R111 DNS-4.7K

R113 DNS-4.7K

R114 DNS-4.7K

R112 DNS-4.7K

E

JP1

1

2

3

DNS HEADER 3X1

of

612Monday, June 07, 2004

A1

Page 32

A

B

C

D

E

RDS /RBDS PRE-PROCESSOR

1394 FIREWIRE PHY

4 4

GND_PHY_D

BIO_LREQ2

GND_PHY_D

E5_GPIO12

C163

56PF

R117 51

C160

27PF

C161

27PF

V33_PHY_D

BIO_LREQ

PHY_XI

Y2

24.576MHz

PHY_XO

C162 104

PHY_FILT0

PHY_FILT1

V33_PHY_A

R116 6.34K/1%

R118 1M/1%

VCC

RR1

10K

RDS_DATA2

SDA2,6,9,11,12

SCL2,6,9,11,12

CR1

82PF

YR1

4.332MHz

RR3

470K

RR4

1K

RR2 22

CR2

CR3

104

47PF

10

1

2

3

4

5

6

7

8

9

UR1

SAA6588

MRO

MPTH

TCON

OSCO

OSCI

VSSD

VDDD

DAVN

SDA

SCL

LVIN

SCOUT

VREF

MPXIN

VSSA

VDDA

AFIN

MAD

PSWN

VCC

CR5

104

CR7

331

+

CR8

47u/16

RDS_MPX 9

CR4

104

20

19

CIN

18

17

16

15

14

13

12

11

CR6

151

CR9

+

2.2u/50

GND_PHY_A

C177

104

PHY_R0

R120

56.2/1%

R126

56.2/1%

C166

221

C

TPBIAS

R121

56.2/1%

R127

56.2/1%

R130

5.11K/1%

GND_PHY_A

30

GND_PHY_A

USB_D0-2

USB_D0+2

USB_OC02

USB_PO02

C165

224

+

GND_PHY_A

C164

1u/50

R122 22

R123 22

R124 22

R125 22

USB

R143

15K

TPA+

TPATPB+

TPB-

R144

15K

D

R134 22

R139 22

CN1

6P2.0

B601

B601

FB33

B601

1

2

3

4

5

6

J4

7

6

5

4

3

2

1

*7P2.0

712Monday, June 07, 2004

TPBTPB+

TPATPA+

GND_PHY_A

VCC

C167

104

USB_BDM0

USB_BDP0

R137 0

R140 0

FB34

FB35

LSI LOGIC

560 COTTONWOOD DR.

MILPITAS, CA 95035

U. S. A.

Title

1394 PHY &USB

Size Document Number Rev

A3

Date: Sheet

E

A1

of

PHY_R1

PHY_R0

TPBIAS

PA+

PAPB+

PB-

GND_PHY_D

V33_PHY_A

C176

104

PHY_R1

V33_PHY_D

V33_PHY_D

U10

GND_PHY_D

C172

103

R119 22

R128

2.2K

GND_PHY_D

R135 680

R138 680

R141 680

V33_PHY_D

C173