Page 1

TECHNICAL

MANUAL

LSI53C876/876E

PCI to Dual Channel

SCSI Multifunction

Controller

Version 2.1

March 2001

®

S14066

Page 2

This document contains proprietary information of LSI Logic Corporation. The

information contained herein is not to be used by or disclosed to third parties

without the express written permission of an officer of LSI Logic Corporation.

LSI Logic products are not intended for use in life-support appliances, devices,

or systems. Use of any LSI Logic product in such applications without written

consent of the appropriate LSI Logic officer is prohibited.

Document DB14-000167-00, First Edition (March 2001)

This document describes the LSI Logic LSI53C876/876E PCI to Dual Channel

SCSI Multifunction Controller and will remain the official reference source for all

revisions/releases of this product until rescinded by an update.

To receive product literature, visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein

at any time without notice. LSI Logic does not assume any responsibility or

liability arising out of the application or use of any product described herein,

except as expressly agreed to in writing by LSI Logic; nor does the purchase or

use of a product from LSI Logic convey a license under any patent rights,

copyrights, trademark rights, or any other of the intellectual property rights of

LSI Logic or third parties.

Copyright © 1996–2001 by LSI Logic Corporation. All rights reserved.

TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design, TolerANT, SDMS, SYMplicity, and SCRIPTS are

registered trademarks or trademarks of LSI Logic Corporation. All other brand

and product names may be trademarks of their respective companies.

ii

Page 3

Audience

Preface

This book is the primary reference and technical manual for the LSI Logic

LSI53C876/876E PCI to Dual Channel SCSI Multifunction Controller. It

contains a complete functional description for the product and includes

complete physical and electrical specifications.

This technical manual assumes the user is familiar with the current and

proposed standards for SCSI and PCI. For additional background

information on these topics, please refer to the list of reference materials

provided in the Related Publications list.

This manual assumes some prior knowledge of current and proposed

SCSI and PCI standards.

Organization

This document has the following chapters and appendixes:

• Chapter 1, General Description, includes general information about

the LSI53C876/876E.

• Chapter 2, Functional Description, describes the main functional

areas of the chip in more detail, including the interfaces to the SCSI

bus and external memory.

• Chapter 3, Signal Descriptions, contains pin diagrams and signal

descriptions.

• Chapter 4, Registers, describes each bit in the operating registers,

and is organized by register address.

• Chapter 5, SCSI SCRIPTS Instruction Set, defines the SCSI

SCRIPTS instructions supported by the LSI53C876/876E.

Preface iii

Page 4

• Chapter 6, Electrical Characteristics, contains the electrical

• Appendix A, Register Summary, is a register summary.

• Appendix B, External Memory Interface Diagram Examples,

Related Publications

For background please contact:

ANSI

11 West 42nd Street

New York, NY 10036

(212) 642-4900

Ask for document number X3.131-199X (SCSI-2)

Global Engineering Documents

15 Inverness Way East

Englewood, CO 80112

(800) 854-7179 or (303) 397-7956 (outside U.S.) FAX (303) 397-2740

Ask for document number X3.131-1994 (SCSI-2) or X3.253

(SCSI-3 Parallel Interface)

characteristics and AC timing diagrams.

contains serveral example interface drawings for connecting the

LSI53C876 to external ROMs.

ENDL Publications

14426 Black Walnut Court

Saratoga, CA 95070

(408) 867-6642

Document names:

SCSI Tutor

Prentice Hall

113 Sylvan Avenue

Englewood Cliffs, NJ 07632

(800) 947-7700

Ask for document number ISBN 0-13-796855-8,

the Small Computer System Interface

LSI Logic World Wide Web Home Page

www.lsil.com

iv Preface

SCSI Bench Reference, SCSI Encyclopedia,

SCSI: Understanding

Page 5

PCI Special Interest Group

2575 N. E. Katherine

Hillsboro, OR 97214

(800) 433-5177; (503) 693-6232 (International); FAX (503) 693-8344

SCSI SCRIPTS™ Processors Programming Guide,

S14044.A

Conventions Used in This Manual

The word

deassert

assert

means to drive a signal true or active. The word

means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix “0x” —for example,

0x32CF. Binary numbers are indicated by the prefix “0b” —for example,

0b0011.0010.1100.1111.

Revision Record

Revision Date Remarks

1.0 9/96 Prelimiary technical manual.

2.0 11/97 Revised technical manual.

2.1 3/01 All product names changed from SYM to LSI.

Order Number

Preface v

Page 6

vi Preface

Page 7

Contents

Chapter 1 General Description

1.1 Wide Ultra SCSI Benefits 1-4

1.2 TolerANT®Technology 1-4

1.3 LSI53C876 Benefits 1-5

1.3.1 PCI Performance 1-5

1.3.2 SCSI Performance 1-5

1.3.3 Testability 1-6

1.3.4 Integration 1-7

1.3.5 Reliability 1-7

Chapter 2 Functional Description

2.1 PCI Functional Description 2-3

2.1.1 PCI Addressing 2-3

2.1.2 PCI Bus Commands and Functions Supported 2-4

2.1.3 Internal Arbiter 2-10

2.1.4 PCI Cache Mode 2-11

2.2 SCSI Functional Description 2-13

2.2.1 Two SCSI Controllers 2-13

2.2.2 SCRIPTS Processor 2-13

2.2.3 JTAG Boundary Scan Testing 2-16

2.2.4 SCSI Loopback Mode 2-17

2.2.5 Parity Options 2-17

2.2.6 DMA FIFO 2-20

2.2.7 SCSI Bus Interface 2-24

2.2.8 Synchronous Operation 2-30

2.2.9 Designing a Wide Ultra SCSI System 2-32

2.2.10 Interrupt Handling 2-33

2.2.11 Chained Block Moves 2-40

2.3 Parallel ROM Interface 2-43

Contents vii

Page 8

2.4 Serial EEPROM Interface 2-45

2.4.1 Mode A Operation 2-45

2.4.2 Mode B Operation 2-46

2.4.3 Mode C Operation 2-46

2.4.4 Mode D Operation 2-48

2.5 Power Management 2-48

2.5.1 Power State D0 2-49

2.5.2 Power State D1 2-49

2.5.3 Power State D2 2-49

2.5.4 Power State D3 2-50

Chapter 3 Signal Descriptions

3.1 PCI Interface Signals 3-6

3.1.1 System Signals 3-6

3.1.2 Address and Data Signals 3-7

3.1.3 Interface Control Signals 3-8

3.1.4 Arbitration Signals 3-9

3.1.5 Error Reporting Signals 3-9

3.1.6 PCI Interrupt Signals 3-10

3.1.7 GPIO Interface Signals 3-11

3.2 SCSI Bus Interface Signals 3-13

3.2.1 SCSI Bus Interface Signal 3-13

3.2.2 SCSI Bus Interface 3-14

3.3 ROM/Flash Interface Signals 3-18

3.4 Test Interface Signals 3-19

3.5 Power and Ground Signals 3-20

3.5.1 Isolated Power Supplies 3-21

3.6 MAD Bus Programming 3-21

Chapter 4 Registers

4.1 PCI Configuration Registers 4-1

4.2 SCSI Registers 4-20

Chapter 5 SCSI SCRIPTS Instruction Set

5.1 Low Level Register Interface Mode 5-1

5.2 High Level SCSI SCRIPTS Mode 5-2

5.2.1 Sample Operation 5-3

viii Contents

Page 9

5.3 Block Move Instruction 5-6

5.3.1 First Dword 5-6

5.3.2 Second Dword 5-13

5.4 I/O Instruction 5-13

5.4.1 First Dword 5-13

5.4.2 Second Dword 5-22

5.5 Read/Write Instructions 5-22

5.5.1 First Dword 5-22

5.5.2 Second Dword 5-24

5.5.3 Read-Modify-Write Cycles 5-24

5.5.4 Move To/From SFBR Cycles 5-25

5.6 Transfer Control Instructions 5-27

5.6.1 First Dword 5-27

5.6.2 Second Dword 5-34

5.7 Memory Move Instructions 5-34

5.7.1 Read/Write System Memory from SCRIPTS 5-36

5.7.2 Second Dword 5-36

5.7.3 Third Dword 5-36

5.8 Load and Store Instructions 5-38

5.8.1 First Dword 5-39

5.8.2 Second Dword 5-40

Chapter 6 Electrical Characteristics

6.1 DC Characteristics 6-1

6.2 3.3 V PCI DC Characteristics 6-7

6.3 TolerANT Technology Electrical Characteristics 6-8

6.4 AC Characteristics 6-12

6.4.1 PCI and External Memory Interface Timings 6-15

6.4.2 PCI and External Memory Interface Timing 6-54

6.4.3 SCSI Interface Timing 6-55

6.5 Package Diagrams 6-60

Appendix A Register Summary

Appendix B External Memory Interface Diagram Examples

Contents ix

Page 10

Figures

Index

Customer Feedback

1.1 Typical LSI53C876 System Application 1-2

1.2 Typical LSI53C876 Board Application 1-3

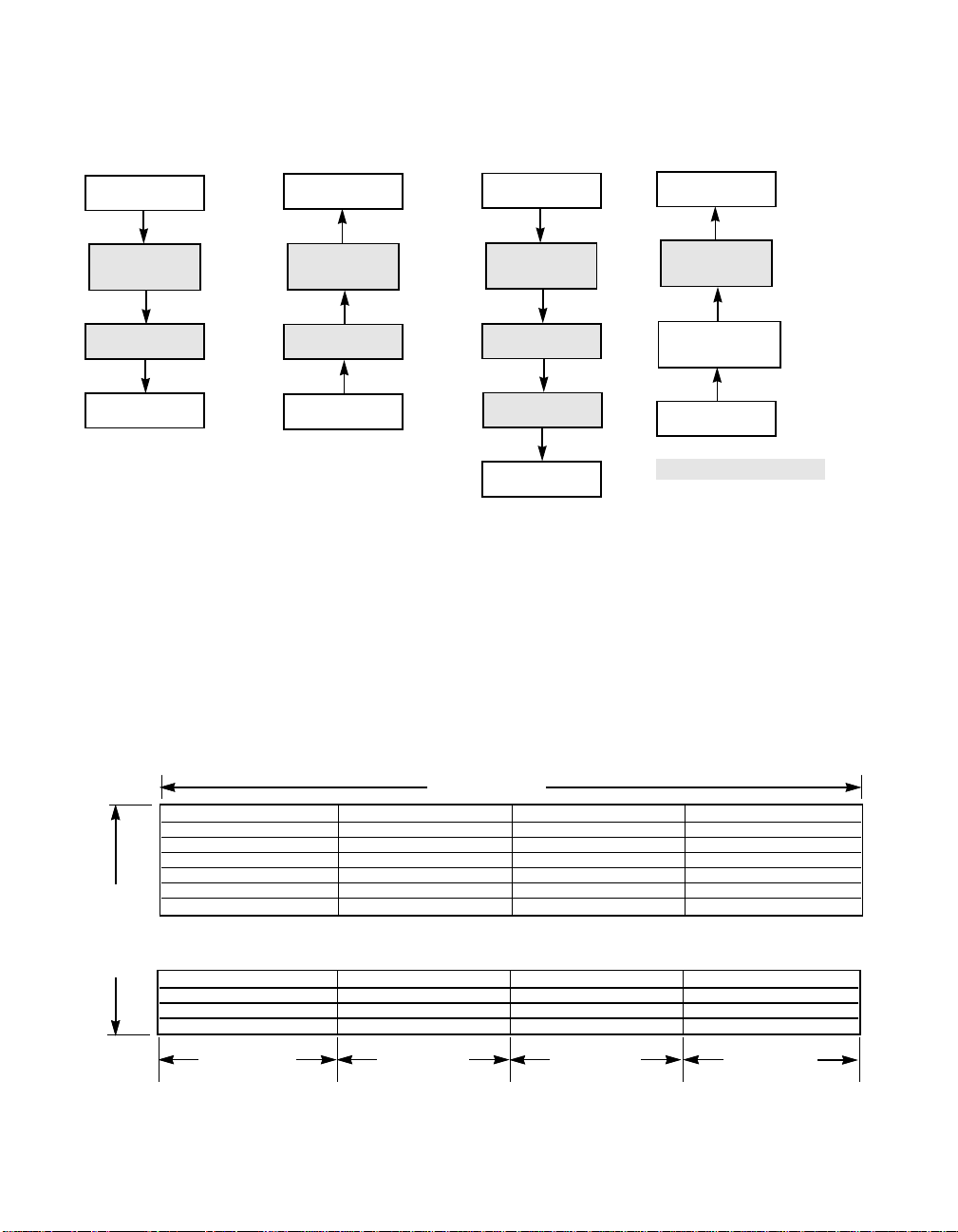

2.1 LSI53C876 Block Diagram 2-2

2.2 Parity Checking/Generation 2-20

2.3 DMA FIFO Sections 2-20

2.4 LSI53C876 Host Interface SCSI Data Paths 2-24

2.5 LSI53C876 Differential Wiring Diagram 2-27

2.6 Regulated Termination 2-29

2.7 Determining the Synchronous Transfer Rate 2-32

2.8 Block Move and Chained Block Move Instructions 2-40

3.1 LSI53C876 208-Pin PQFP Diagram 3-2

3.2 LSI53C876 256-Ball BGA Diagram (Top View) 3-3

3.3 LSI53C876 Functional Signal Grouping 3-4

5.1 SCRIPTS Overview 5-5

5.2 Block Move Instruction Register 5-8

5.3 I/O Instruction Register 5-16

5.4 Read/Write Instruction Register 5-23

5.5 Transfer Control Instruction 5-29

5.6 Memory Move Instruction 5-37

5.7 Load and Store Instruction Format 5-41

6.1 Rise and Fall Time Test Conditions 6-10

6.2 SCSI Input Filtering 6-10

6.3 Hysteresis of SCSI Receivers 6-10

6.4 Input Current as a Function of Input Voltage 6-11

6.5 Output Current as a Function of Output Voltage 6-11

6.6 Clock Timing 6-12

6.7 Reset Input 6-13

6.8 Interrupt Output 6-14

6.9 Configuration Register Read 6-17

6.10 Configuration Register Write 6-18

6.11 Target Read (Not From External Memory) 6-19

x Contents

Page 11

6.12 Target Write (Not From External Memory) 6-20

6.13 Target Read, from External Memory 6-22

6.14 Target Write, from External Memory 6-26

6.15 Opcode Fetch, Nonburst 6-29

6.16 Opcode Fetch, Burst 6-31

6.17 Back-to-Back Read 6-33

6.18 Back-to-Back Write 6-35

6.19 Burst Read 6-38

6.20 Burst Write 6-42

6.21 Read Cycle, Normal/Fast Memory (≥ 128 Kbytes),

Single Byte Access 6-44

6.22 Write Cycle, Normal/Fast Memory (≥ 128 Kbytes),

Single Byte Access 6-45

6.23 Read Cycle, Normal/Fast Memory (≥ 128 Kbyte),

Multiple Byte Access 6-46

6.24 Write Cycle, Normal/Fast Memory (≥ 128 Kbyte),

Multiple Byte Access 6-48

6.25 Read Cycle, Slow Memory (≥ 128 Kbytes) 6-50

6.26 Write Cycle, Slow Memory (≥ 128 Kbytes) 6-51

6.28 Read Cycle, 16 Kbytes ROM 6-52

6.27 Read Cycle, 16 Kbytes ROM 6-52

6.29 Write Cycle, 16 Kbytes ROM 6-53

6.30 Initiator Asynchronous Send 6-55

6.31 Initiator Asynchronous Receive 6-56

6.32 Target Asynchronous Send 6-57

6.33 Target Asynchronous Receive 6-57

6.34 Initiator and Target Synchronous Transfers 6-58

6.35 256-pin PBGA (GU) Mechanical Drawing 6-61

6.36 208-pin PQFP (P9) Mechanical Drawing (Sheet 1 of 2) 6-62

B.1 64 Kbyte Interface with 200 ns Memory B-1

B.2 64 Kbyte Interface with 150 ns Memory B-2

B.3 256 Kbyte Interface with 150 ns Memory B-3

B.4 512 Kbyte Interface with 150 ns Memory B-4

Tables

2.1 PCI Bus Commands and Encoding Types 2-4

2.2 Bits Used for Parity Control and Generation 2-18

2.3 SCSI Parity Control 2-19

Contents xi

Page 12

2.4 SCSI Parity Errors and Interrupts 2-19

2.5 Differential Mode 2-25

2.6 Parallel ROM Support 2-44

2.7 Mode A Serial EEPROM Data Format 2-46

2.8 Mode C Serial EEPROM Data Format 2-47

2.9 Power States 2-48

3.1 System Signals 3-6

3.2 Address and Data Signals 3-7

3.3 Interface Control Signals 3-8

3.4 Arbitration Signals 3-9

3.5 Error Reporting Signals 3-9

3.6 PCI Interrupt Signals 3-10

3.7 SCSI GPIO Function A Signals 3-11

3.8 SCSI GPIO Function B Signals 3-12

3.9 SCSI Bus Interface Signal 3-13

3.10 SCSI Function A Interface Signals 3-14

3.11 SCSI Function B Interface Signals 3-15

3.12 SCSI Function A Differential Control Signals 3-16

3.13 SCSI Function B Differential Control Signals 3-17

3.14 ROM/Flash Interface Signals 3-18

3.15 Test Interface Signals 3-19

3.16 Power and Ground Signals 3-20

3.17 Decode of MAD Pins 3-22

4.1 PCI to SCSI Configuration Register Map 4-2

4.2 LSI53C876 SCSI Register Address Map 4-21

4.3 Examples of Synchronous Transfer Periods for SCSI-1

Transfer Rates 4-35

4.4 Example Transfer Periods for Fast SCSI and Wide Ultra

SCSI Transfer Rates 4-35

4.5 Maximum Synchronous Offset 4-36

4.6 SCSI Synchronous Data FIFO Word Count 4-46

5.1 SCRIPTS Instructions 5-3

5.2 Read/Write Instructions 5-25

6.1 Absolute Maximum Stress Ratings 6-2

6.2 Operating Conditions 6-2

6.3 SCSI Signals—SD[15:0]/, SDP[1:0]/, SREQ/, SACK/ 6-3

6.4 SCSI Signals—SMSG, SI_O/, SC_D/, SATN/, SBSY/,

SSEL/, SRST/ 6-3

xii Contents

Page 13

6.5 Input Signals—CLK, SCLK, GNT/, IDSEL, RST/,

TESTIN, DIFFSENS 6-3

6.6 Capacitance 6-4

6.7 Output Signals—INTA/, INTB/ 6-4

6.8 Output Signals—SDIR[15:0], SDIRP0, SDIRP1, BSYDIR,

SELDIR, RSTDIR, TGS, IGS, MAS/[1:0], MCE/,

MOE/_TESTOUT, MWE/ 6-4

6.9 Output Signal—REQ/ 6-5

6.10 Output Signal—SERR/ 6-5

6.11 Bidirectional Signals—AD[31:0], C_BE/[3:0], FRAME/,

IRDY/, TRDY/, DEVSEL/, STOP/, PERR/, PAR 6-5

6.12 Bidirectional Signals—GPIO0_FETCH/,

GPIO1_MASTER/, GPIO2, GPIO3, GPIO4 6-6

6.13 Bidirectional Signals—MAD[7:0] 6-6

6.14 Input Signals—TDI, TMS, TCK 6-6

6.15 Output Signal—TDO 6-7

6.16 Bidirectional Signals—AD[31:0], C_BE[3:0]/, FRAME/,

IRDY/, TRDY/, DEVSEL/, STOP/, PERR/, PAR 6-7

6.17 Input Signals—CLK, GNT/, IDSEL, RST/, 6-7

6.18 Output Signals—INTA/, INTB, REQ/ 6-8

6.19 Output Signal—SERR/ 6-8

6.20 TolerANT Technology Electrical Characteristics 6-9

6.21 Clock Timing 6-12

6.22 Reset Input 6-13

6.23 Interrupt Output 6-14

6.24 3.3 V PCI Timing 6-16

6.25 Configuration Register Read 6-17

6.26 Configuration Register Write 6-18

6.27 Target Read (Not From External Memory) 6-19

6.28 Target Write (Not From External Memory) 6-20

6.29 Target Read (From External Memory) 6-21

6.30 Target Write (From External Memory) 6-25

6.31 Opcode Fetch, Nonburst 6-28

6.32 Opcode Fetch, Burst 6-30

6.33 Back-to-Back Read 6-32

6.34 Back-to-Back Write 6-34

6.35 Burst Read 6-37

6.36 Burst Write 6-41

Contents xiii

Page 14

6.37 Read Cycle, Norma/Fast Memory (≥ 128 Kbytes),

Single Byte Access 6-44

6.38 Write Cycle, Normal/Fast Memory (≥ 128 Kbytes),

Single Byte Access 6-45

6.39 Read Cycle, Slow Memory (≥ 128 Kbytes) 6-50

6.40 Write Cycle, Slow Memory (≥ 128 Kbytes) 6-51

6.41 Write Cycle, 16 Kbytes ROM 6-53

6.42 LSI53C876 PCI and External Memory Interface Timing 6-54

6.43 Initiator Asynchronous Send 6-55

6.44 Initiator Asynchronous Receive 6-56

6.45 Target Asynchronous Send 6-57

6.46 Target Asynchronous Receive 6-57

6.47 SCSI-1 Transfers (SE, 5.0 Mbytes/s) 6-58

6.48 SCSI-2 Fast Transfers (10.0 Mbytes/s (8-Bit Transfers) or

20.0 Mbytes/s (16-Bit Transfers), 40 MHz Clock 6-59

6.49 SCSI-2 Fast-20 SE Transfers (20.0 Mbytes/s

(8-Bit Transfers) or 40.0 Mbytes/s (16-Bit Transfers),

80 MHz Clock) with Clock Doubled Internally 6-59

A.1 Configuration Registers A-1

A.2 SCSI Registers A-2

xiv Contents

Page 15

Chapter 1

General Description

This chapter includes the following sections:

• Section 1.1, “Wide Ultra SCSI Benefits”

• Section 1.2, “TolerANT

• Section 1.3, “LSI53C876 Benefits”

This manual combines information for the LSI53C876 and LSI53C876E,

which are a PCI to dual SCSI controllers. The LSI53C876E is a minor

modification of the existing LSI53C876 product. It has all of the

functionality of the LSI53C876 with the addition of features to enable it

to comply with the Microsoft PC 97 Hardware Design Guide. Specifically,

the LSI53C876E has a Power Management Support enhancement.

Because there are only slight differences between them, the LSI53C876

and LSI53C876E are referred to as LSI53C876 throughout this technical

manual. Only the new enhancements are referred to as LSI53C876E.

®

Technology”

The LSI53C876 PCI to Dual Channel SCSI Multifunction Controller is a

PCI 2.1 compliant device. It implements two LSI53C875 PCI to Ultra

SCSI controllers on a single chip. The LSI53C876 presents only one load

to the PCI bus, and it uses one REQ/ - GNT/ signal pair in arbitration for

PCI bus mastership.

Two packaging options are available. The 208-pin Plastic Quad Flat Pack

(PQFP) provides a differential Single-Ended (SE) SCSI interface on SCSI

Function A and an SE interface on SCSI Function B. The 256-bump Ball

Grid Array (BGA) provides a differential SE interface on both SCSI

Function A and SCSI Function B.

The LSI53C876 has a local memory bus for storage of the device’s BIOS

ROM in Flash memory or standard EPROMs. The LSI53C876 supports

programming of local Flash memory for updates to BIOS or SCRIPTS™

programs.

LSI53C876/876E PCI to Dual Channel SCSI Multifunction Controller 1-1

Page 16

The LSI53C876 reduces the requirement for system BIOS support and

PCI bus bandwidth. It also supports the Wide Ultra SCSI standard. The

LSI53C876 performs Wide Ultra SCSI transfers or Fast SCSI transfers,

and it improves performance by optimizing PCI bus utilization. Figure 1.1

illustrates a typical LSI53C876 system and Figure 1.2 illustrates a typical

LSI53C876 board application.

Figure 1.1 Typical LSI53C876 System Application

PCI Bus

Interface

Controller

Processor Bus

Central

Processing

Unit

(CPU)

Typical PCI Computer

System Architecture

LSI53C876 PCI

to Wide Ultra SCSI

Function A

and

LSI53C876 PCI

to Wide Ultra SCSI

Function B

One PCI Bus Load

PCI Graphic Accelerator

PCI Sound Card

Memory

Controller

Memory

SCSI Bus

SCSI Bus

Fixed Disk, Optical Disk,

Printer, Tape, and Other

Peripherals

Fixed Disk, Optical Disk,

Printer, Tape, and Other

Peripherals

1-2 General Description

Page 17

Figure 1.2 Typical LSI53C876 Board Application

Function A

68 Pin

Wide SCSI

Connector

Function B

68 Pin

Wide SCSI

Connector

SCSI Data,

Parity, and

Control Signals

LSI53C876

PCI

SCSI Data,

Parity, and

Control Signals

PCI Address, Data, Parity and Control Signals

Dual Channel SCSI

PCI Interface

to

Multifunction

Controller

Memory

Address/Data

A_GPIO/[1:0]

B_GPIO/[1:0]

Bus

Memory Control

Block

Flash EEPROM

Serial EEPROM

Function A

Serial EEPROM

Function B

The LSI53C876 integrates a high-performance SCSI core, a PCI bus

master DMA core, and the LSI Logic SCSI SCRIPTS processor to meet

the flexibility requirements of SCSI, Fast SCSI, and Wide Ultra SCSI

standards. It is designed to implement multithreaded I/O algorithms with

a minimum of processor intervention, solving the protocol overhead

problems of previous intelligent and nonintelligent controller designs.

The LSI53C876 is fully supported by the LSI Logic Storage Device

Management System (SDMS™), a software package that supports the

Advanced SCSI Protocol Interface (ASPI). SDMS software provides

BIOS and driver support for hard disk, tape, removable media products,

and CD-ROM under the major PC operating systems.

In addition, LSI Logic provides a SYMplicity™ I2O Hardware Device

Module for the LSI53C876 to support the device in I2O-ready systems.

The SYMplicity I2O architecture is compliant with the I2O specification.

I2O is a split driver architecture that increases system efficiency by

transferring I/O intensive processing tasks from the host CPU to

intelligent peripheral platforms.

1-3

Page 18

1.1 Wide Ultra SCSI Benefits

Wide Ultra SCSI is an extension of the SCSI-3 family of standards that

expands the bandwidth of the SCSI bus and allows faster synchronous

SCSI transfer rates. When enabled, Wide Ultra SCSI performs

40 megatransfers per second during an I/O operation, resulting in

approximately twice the synchronous transfer rates of Fast SCSI. The

LSI53C876 can perform Ultra SCSI synchronous transfers at

20 Mbytes/s. It can also perform Wide Ultra SCSI transfers at

40 Mbytes/s. This advantage is most noticeable in heavily loaded

systems or large block size requirements, such as video on-demand and

image processing.

An advantage of Wide Ultra SCSI is that it significantly improves SCSI

bandwidth while preserving existing hardware and software investments.

The LSI53C876 is compatible with all existing LSI53C875 software.

1.2 TolerANT®Technology

The LSI53C876 features TolerANT technology, which includes active

negation on the SCSI drivers and input signal filtering on the SCSI

receivers. Active negation actively drives the SCSI Request,

Acknowledge, Data, and Parity signals HIGH rather than allowing them

to be passively pulled up by terminators. Active negation is enabled by

setting bit 7 in the SCSI Test Three (STEST3) register.

TolerANT receiver technology improves data integrity in unreliable

cabling environments where other devices would be subject to data

corruption. TolerANT receivers filter the SCSI bus signals to eliminate

unwanted transitions, without the long signal delay associated with

RC-type input filters. This improved driver and receiver technology helps

eliminate double clocking of data, the single biggest reliability issue with

SCSI operations. TolerANT input signal filtering is a built in feature of the

LSI53C876 and all LSI Logic Fast SCSI and Ultra SCSI devices.

The benefits of TolerANT technology include increased immunity to noise

on the deasserting signal edge, better performance due to balanced duty

cycles, and improved Fast SCSI transfer rates. In addition, TolerANT

SCSI devices do not cause glitches on the SCSI bus at power-up or

1-4 General Description

Page 19

power-down, so other devices on the bus are also protected from data

corruption. TolerANT technology is compatible with both the Alternative

One and Alternative Two termination schemes proposed by the American

National Standards Institute (ANSI).

1.3 LSI53C876 Benefits

This section provides an overview of the LSI53C876 features and

benefits. It contains information on PCI Performance, SCSI Performance,

Testability, Integration, and Reliability.

1.3.1 PCI Performance

To improve SCSI performance, the LSI53C876:

• Complies with PCI 2.1 specification

• Presents a single electrical load to the PCI bus (True PCI

multifunction device).

• Supports 32-bit word data bursts with variable burst lengths of 2, 4,

8, 16, 32, 64 or 128 Dwords across the PCI bus.

• Prefetches up to 8 Dwords of SCSI SCRIPTS.

• Bursts SCSI SCRIPTS opcode fetches across the PCI bus.

• Performs zero wait-state bus master data bursts up to 132 Mbytes/s

(@ 33 MHz).

• Supports PCI Cache Line Size register.

• Supports PCI Write and Invalidate, Read Line, and Read Multiple

commands.

• Complies with PCI Bus Power Management Specification

(LSI53C876E) Revision 1.0.

1.3.2 SCSI Performance

To improve SCSI performance, the LSI53C876:

• Includes 4 Kbytes internal RAM on each channel for SCRIPTS

instruction storage.

• Wide Ultra SCSI SE Interface.

LSI53C876 Benefits 1-5

Page 20

• Performs Wide Ultra SCSI synchronous transfers as fast as

40 Mbytes/s.

• Supports 536-byte DMA FIFO for more effective PCI and SCSI bus

utilization.

• Supports 16 levels of SCSI synchronous offset.

• Supports variable block size and scatter/gather data transfers

• Minimizes SCSI I/O start latency.

• Performs complex bus sequences without interrupts, including

restore data pointers.

• Reduces interrupt service routine overhead through a unique

interrupt status reporting method.

• Supports Load and Store SCRIPTS instructions to increase the

performance of data transfers to and from chip registers.

• Supports target disconnect and later reconnect with no interrupt to

the system processor.

• Supports multithreaded I/O algorithms in SCSI SCRIPTS with fast

I/O context switching.

• Supports expanded Register Move instructions.

• Compatible with LSI53C875 software (drivers and SCRIPTS).

• Enables Ultra SCSI with 40 MHz SCSI clock input with integrated

clock doubler.

1.3.3 Testability

The LSI53C876 contains these testability features:

• All SCSI signals accessible through programmed I/O.

• SCSI loopback diagnostics.

• SCSI bus signal continuity checking.

• Support for single step mode operation.

• Test mode (AND-tree) to check pin continuity to the board.

1-6 General Description

Page 21

1.3.4 Integration

1.3.5 Reliability

The LSI53C876 contains these integration features:

• Dual channel SCSI multifunction controller.

• 3.3 V/5 V PCI interface.

• Full 32-bit PCI DMA bus master.

• Memory-to-Memory Move instructions allow use as a third-party PCI

bus DMA controller.

• High-performance SCSI core.

• Integrated SCRIPTS processor.

The LSI53C876 contains these reliability features:

• 2 kV ESD protection on SCSI signals.

• Typical 300 mV SCSI bus hysteresis.

• Protection against bus reflections due to impedance mismatches.

• Controlled bus assertion times (reduces EMI, improves reliability, and

eases FCC certification).

• Latch-up protection greater than 150 mA.

• Voltage feed-through protection (minimum leakage current through

SCSI pads).

• Power and ground isolation of I/O pads and internal chip logic.

• TolerANT technology, which provides:

– Active negation of SCSI Data, Parity, Request, and Acknowledge

signals for improved fast SCSI transfer rates.

– Input signal filtering on SCSI receivers improves data integrity,

even in noisy cabling environments.

LSI53C876 Benefits 1-7

Page 22

1-8 General Description

Page 23

Chapter 2

Functional Description

Chapter 2 is divided into the following sections:

• Section 2.1, “PCI Functional Description”

• Section 2.2, “SCSI Functional Description”

• Section 2.3, “Parallel ROM Interface”

• Section 2.4, “Serial EEPROM Interface”

• Section 2.5, “Power Management”

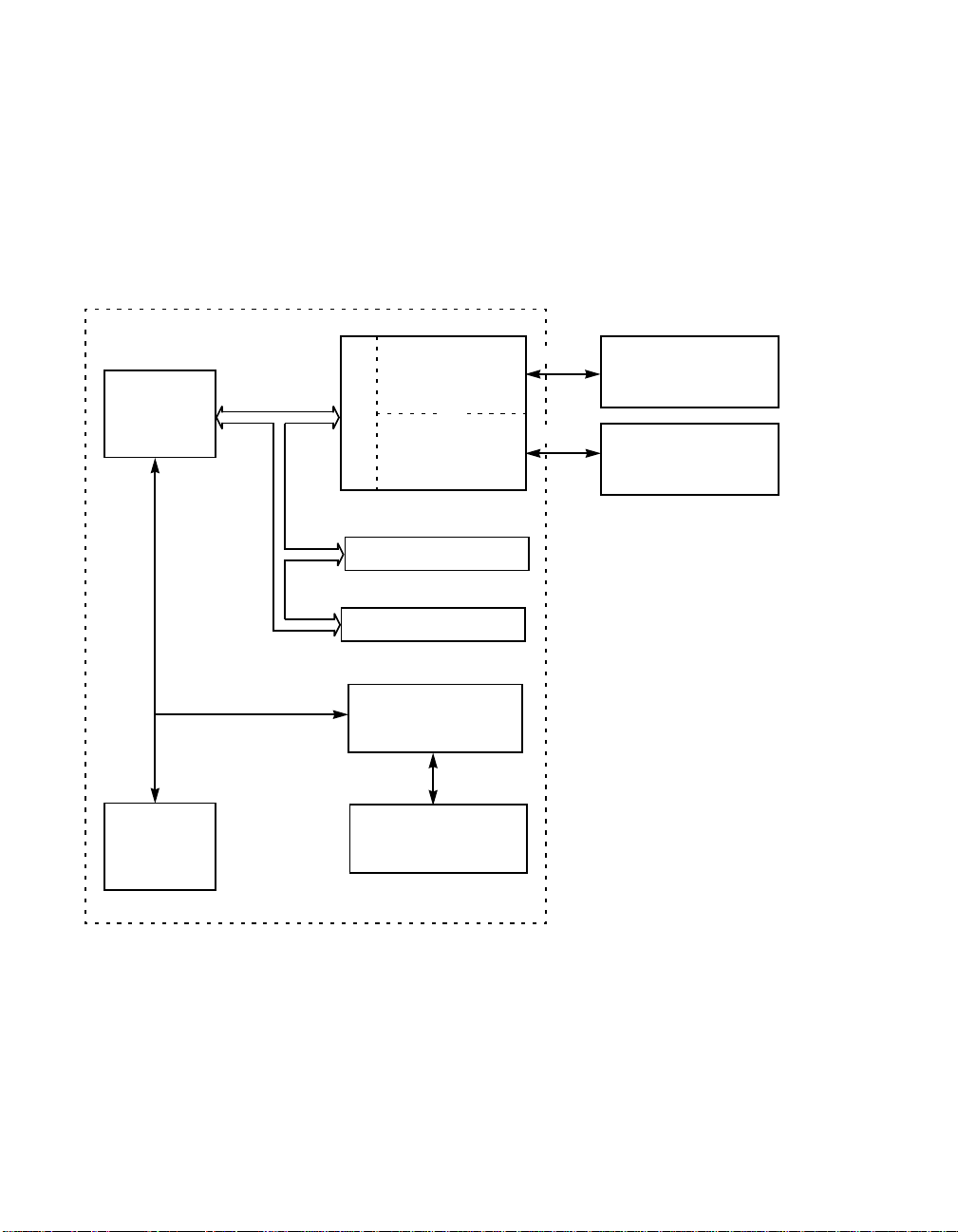

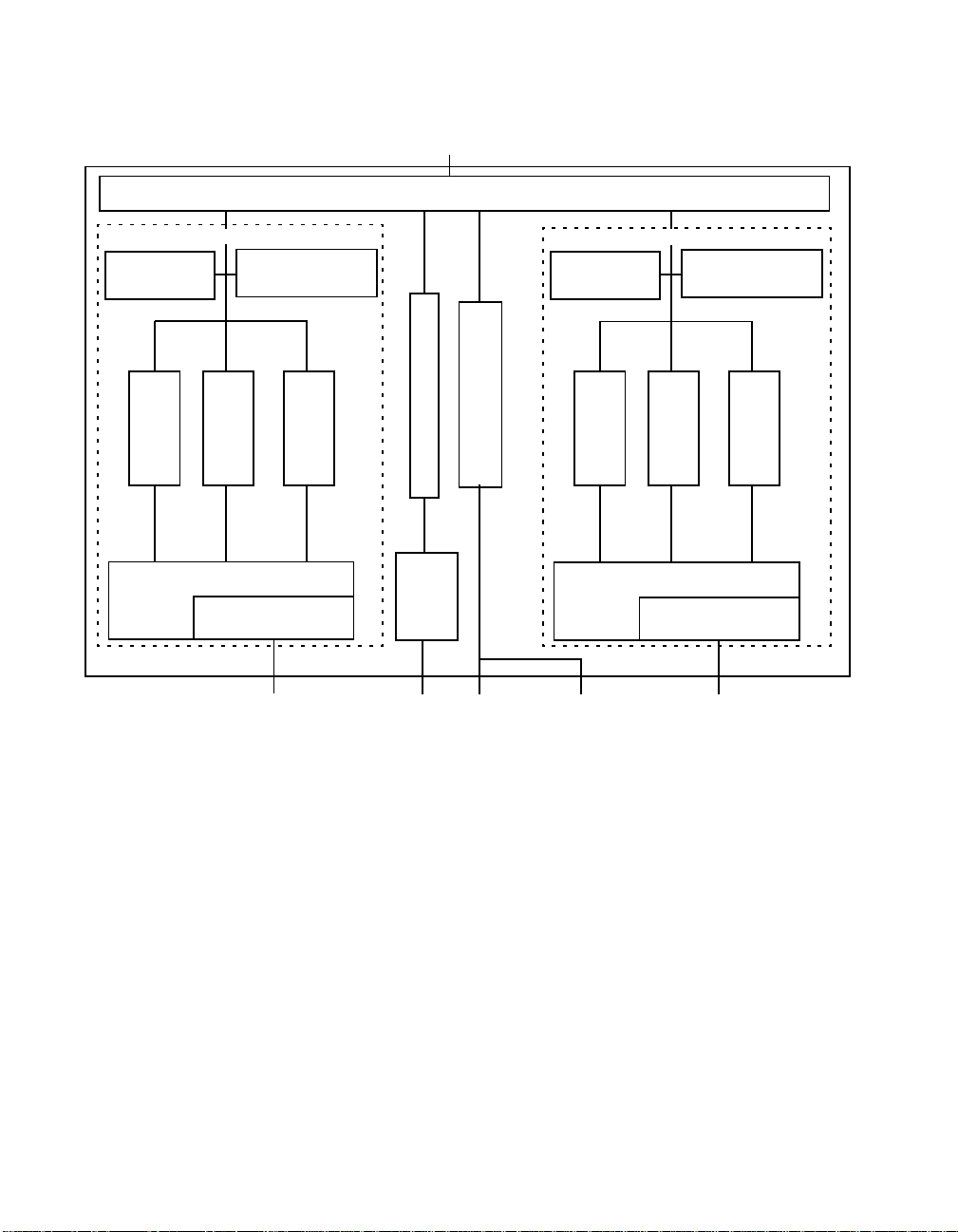

The LSI53C876 is a multifunction device composed of the following

modules:

• PCI Interface

• Two independent PCI-to-Wide Ultra SCSI Controllers

• ROM/Flash Memory Controller

• Serial EEPROM Controller

Figure 2.1 illustrates the relationship between these modules.

LSI53C876/876E PCI to Dual Channel SCSI Multifunction Controller 2-1

Page 24

Figure 2.1 LSI53C876 Block Diagram

PCI Bus

PCI Master and Slave Control Block, PCI Configuration Registers (2 sets), and SCSI Function Arbitration

Wide Ultra SCSI Controller

4 Kbyte

SCRIPTS RAM

536 Byte

DMA FIFO

SCSI FIFO and SCSI Control Block

8 Dword SCRIPTS

Prefetch Buffer

Registers

Processor

SCSI SCRIPTS

TolerANT

Drivers and Receivers

SCSI Function A

Wide Ultra

SCSI Bus

Operating

Local

Memory

ROM/Flash

Memory

Bus

ROM/Flash Memory Control

Bus

2-Wire Serial

EEPROM Bus

SCRIPTS RAM

and Autoconfiguration

Serial EEPROM Controller

Wide Ultra SCSI Controller

4 Kbyte

Registers

Operating

SCSI FIFO and SCSI Control Block

2-Wire Serial

EEPROM Bus

8 Dword SCRIPTS

Prefetch Buffer

Processor

SCSI SCRIPTS

TolerANT

Drivers and Receivers

SCSI Function B

Wide Ultra

SCSI Bus

536 Byte

DMA FIFO

2-2 Functional Description

Page 25

2.1 PCI Functional Description

The LSI53C876 implements two PCI-to-Wide Ultra SCSI controllers in a

single package. This configuration presents only one load to the PCI bus

and uses one REQ/ - GNT/ pair to arbitrate for PCI bus mastership.

However, separate interrupt signals are generated for SCSI Function A

and SCSI Function B.

2.1.1 PCI Addressing

There are three physical PCI-defined address spaces:

• Configuration Space

• I/O Space

• Memory Space

2.1.1.1 Configuration Space

Two independent sets of configuration space registers are defined, one

set for each SCSI function. The Configuration registers are accessible

only by system BIOS during PCI configuration cycles. The configuration

space is a contiguous 256 x 8-bit set of addresses. Decoding C_BE/[3:0]

determines if a PCI cycle is intended to access configuration register

space. The IDSEL bus signal is a “chip select” that allows access to the

configuration register space only. A configuration read/write cycle without

IDSEL is ignored. The eight lower order address bits AD[7:0], are used

to select a specific 8-bit register. Since the LSI53C876 is a PCI

multifunction device, AD[10:8] decodes either SCSI Function A

Configuration register (AD [10:8] = 000 binary) or SCSI Function B

Configuration register (AD [10:8] = 001 binary). The host processor uses

this configuration space to initialize the LSI53C876.

At initialization time, each PCI device is assigned a base address for

memory accesses and I/O accesses. In the case of the LSI53C876, the

upper 24 bits of the address are selected. On every access, the

LSI53C876 compares its assigned base addresses with the value on the

Address/Data bus during the PCI address phase. If the upper 24 bits

match, the access is for the LSI53C876 and the low-order eight bits

define the register being accessed. A decode of C_BE/[3:0] determines

which registers and what type of access is to be performed.

PCI Functional Description 2-3

Page 26

I/O Space – The PCI specification defines I/O space as a contiguous

32-bit I/O address that is shared by all system resources, including the

LSI53C876. The Base Address Register Zero (I/O) register determines

which 256-byte I/O area this device occupies.

Memory Space – The PCI specification defines memory space as a

contiguous 32-bit memory address that is shared by all system

resources, including the LSI53C876. The Base Address Register One

(Memory) register determines which 256-byte memory area this device

occupies. Each SCSI function uses a 4 K SCRIPT RAM memory space.

The Base Address Register Two (Memory) register determines the

4 Kbyte memory area occupied by SCRIPTS RAM.

2.1.2 PCI Bus Commands and Functions Supported

Bus commands indicate to the target the type of transaction the master

is requesting. Bus commands are encoded on the C_BE/[3:0] lines

during the address phase. PCI bus commands and encoding types

appear in Table 2.1.

Table 2.1 PCI Bus Commands and Encoding Types

C_BE[3:0] Command Type Supported as Master Supported as Slave

0b0000 Interrupt Acknowledge No No

0b0001 Special Cycle No No

0b0010 I/O Read Yes Yes

0b0011 I/O Write Yes Yes

0b0100 Reserved N/A N/A

0b0101 Reserved N/A N/A

0b0110 Memory Read Yes Yes

0b0111 Memory Write Yes Yes

0b1000 Reserved N/A N/A

0b1001 Reserved N/A N/A

2-4 Functional Description

Page 27

Table 2.1 PCI Bus Commands and Encoding Types (Cont.)

C_BE[3:0] Command Type Supported as Master Supported as Slave

0b1010 Configuration Read No Yes

0b1011 Configuration Write No Yes

0b1100 Memory Read Multiple Yes

0b1101 Dual Address Cycle (DAC) No No

0b1110 Memory Read Line Yes

0b1111 Memory Write and Invalidate Yes

1. See theDMA Mode (DMODE) register.

2. See the Chip Test Three (CTEST3) register.

1

1

2

No (defaults to 0110)

No (defaults to 0110)

No (defaults to 0111)

2.1.2.1 Interrupt Acknowledge Command

The LSI53C876 does not respond to this command as a slave and it

never generates this command as a master.

2.1.2.2 Special Cycle Command

The LSI53C876 does not respond to this command as a slave and it

never generates this command as a master.

2.1.2.3 I/O Read Command

The I/O Read command reads data from an agent mapped in I/O

address space. All 32 address bits are decoded.

2.1.2.4 I/O Write Command

The I/O Write command writes data to an agent mapped in I/O address

space. All 32 address bits are decoded.

2.1.2.5 Reserved Command

The LSI53C876 does not respond to this command as a slave and it

never generates this command as a master.

PCI Functional Description 2-5

Page 28

2.1.2.6 Memory Read Command

The Memory Read command reads data from an agent mapped in the

Memory Address Space. The target is free to do an anticipatory read for

this command only if it can guarantee that such a read has no side

effects.

2.1.2.7 Memory Write Command

The Memory Write command writes data to an agent mapped in the

Memory Address Space. When the target returns “ready”, it assumes

responsibility for the coherency (which includes ordering) of the subject

data.

2.1.2.8 Configuration Read Command

The Configuration Read command reads the configuration space of each

agent. An agent is selected during a configuration access when its

IDSEL signal is asserted and AD[1:0] are 0b00. During the address

phase of a configuration cycle, AD[7:2] address one of the 64 Dword

registers (where byte enables address of the bytes within each Dword)

in the configuration space of each device and AD[31:11] are logical don’t

cares to the selected agent. AD[10:8] indicate which device of a

multifunction agent is being addressed.

2.1.2.9 Configuration Write Command

The Configuration Write command transfers data to the configuration

space of each agent. An agent is selected when its IDSEL signal is

asserted and AD[1:0] are 0b00. During the address phase of a

configuration cycle, the AD[7:2] lines address the 64 Dword registers

(where byte enables address of the bytes within each Dword) in the

configuration space of each device,and AD[31:11] are logical don’t cares

to the selected agent. AD[10:8] indicate which device of a multifunction

agent is addressed.

2.1.2.10 Memory Read Multiple Command

This command is identical to the Memory Read command except that it

additionally indicates that the master may intend to fetch more than one

cache line before disconnecting. The LSI53C876 supports PCI Read

Multiple functionality and issues Read Multiple commands on the PCI

2-6 Functional Description

Page 29

bus when the Read Multiple Mode is enabled. This mode is enabled by

setting bit 2 (ERMP) of the DMA Mode (DMODE) register. If cache mode

is enabled, a Read Multiple command is issued on all read cycles, except

opcode fetches, when the following conditions are met:

• The CLSE bit (Cache Line Size Enable, bit 7, DMA Control (DCNTL)

register) and the ERMP bit (Enable Read Multiple, bit 2, DMA Mode

(DMODE) register) are set.

• The Cache Line Size register for each function contains a legal burst

size value (2, 4, 8, 16, 32, 64, or 128) and that value is less than or

equal to the DMA Mode (DMODE) burst size.

• The number of bytes to transfer at the time a cache boundary is

reached is at least twice the full cache line size.

• The chip is aligned to a cache line boundary.

When these conditions are met, the chip issues a Read Multiple

command instead of a Memory Read during all PCI read cycles.

Burst Size Selection – The Read Multiple command reads in multiple

cache lines of data in a single bus ownership. The number of cache lines

to read is a multiple of the cache line size specified in Revision 2.1 of

the PCI specification. The logic selects the largest multiple of the cache

line size based on the amount of data to transfer, with the maximum

allowableburstsizedetermined from the DMA Mode (DMODE) burst size

bits, and the Chip Test Five (CTEST5), bit 2.

2.1.2.11 Dual Address Cycles (DACs) Command

The LSI53C876 does not respond to this command as a slave, and it

never generates this command as a master.

2.1.2.12 Memory Read Line Command

This command is identical to the Memory Read command, except that it

additionally indicates that the master intends to fetch a complete cache

line. This command is intended for use with bulk sequential data transfers

where the memory system and the requesting master might gain some

performance advantage by reading up to a cache line boundary rather

than a single memory cycle. The Read Line function in the previous

LSI53C8XX chips is modified in the LSI53C876 to reflect the PCI Cache

Line Size register specifications. The functionality of the Enable Read

PCI Functional Description 2-7

Page 30

Line bit (DMA Mode (DMODE) register, bit 3) is modified to more

resemble the Write and Invalidate mode in terms of conditions that must

be met before a Read Line command is issued. However, the Read Line

option operates exactly like the previous LSI53C8XX chips when cache

mode is disabled by a CLSE bit reset or when certain conditions exist in

the chip (explained below).

If cache mode is disabled, Read Line commands are issued on every

read data transfer, except opcode fetches, as in previous LSI53C8XX

chips.

If cache mode is enabled, a Read Line command is issued on all read

cycles, except opcode fetches, when the following conditions are met:

• The CLSE (Cache Line Size Enable, bit 7, DMA Control (DCNTL)

register) and ERL (Enable Read Line, bit 3, DMA Mode (DMODE)

register) bits are set.

• The Cache Line Size register for each function must contain a legal

burst size value (2, 4, 8, 16, 32, 64, or 128) and that value is less

than or equal to the DMA Mode (DMODE) burst size.

• The number of bytes to be transferred at the time a cache boundary

is reached is equal to or greater than the DMA Mode (DMODE) burst

size.

• The chip is aligned to a cache line boundary.

When these conditions are met, the chip issues a Read Line command

instead of a Memory Read during all PCI read cycles. Otherwise, it

issues a normal Memory Read command.

Read Multiple with Read Line Enabled – When both the Read

Multiple and Read Line modes are enabled, the Read Line command is

not issued if the above conditions are met. Instead, a Read Multiple

command is issued, even though the conditions for Read Line are met.

If the Read Multiple mode is enabled and the Read Line mode is

disabled, Read Multiple commands are issued if the Read Multiple

conditions are met.

2-8 Functional Description

Page 31

2.1.2.13 Memory Write and Invalidate Command

The Memory Write and Invalidate command is identical to the Memory

Write command, except that it additionally guarantees a minimum

transfer of one complete cache line; that is to say, the master intends to

write all bytes within the addressed cache line in a single PCI transaction

unless interrupted by the target. This command requires implementation

of the PCI Cache Line Size register at address 0x0C in the PCI

configuration space. The LSI53C876 enables Memory Write and

Invalidate cycles when bit 0 (WRIE) in the Chip Test Three (CTEST3)

register and bit 4 (WIE) in the PCI Command register are set. When the

following conditions are met, Memory Write and Invalidate commands

are issued:

• The CLSE bit (Cache Line Size Enable, DMA Control (DCNTL)

register, bit 7), WRIE bit (Write and Invalid Enable, Chip Test Three

(CTEST3) register, bit 0), and PCI configuration Command register,

bit 4 are set.

• The Cache Line Size register for each function contains a legal burst

size value (2, 4, 8, 16, 32, 64, or 128) and that value is less than or

equal to the DMA Mode (DMODE) burst size.

• The chip has enough bytes in the DMA FIFO to complete at least

one full cache line burst.

• The chip is aligned to a cache line boundary.

When these conditions are met, the LSI53C876 issues a Write and

Invalidate command instead of a Memory Write command during all PCI

write cycles.

Multiple Cache Line Transfers – The Write and Invalidate command

can write multiple cache lines of data in a single bus ownership. The chip

issues a burst transfer as soon as it reaches a cache line boundary. The

size of the transfer is not automatically the cache line size, but rather a

multiple of the cache line size as specified in Revision 2.1 of the PCI

specification. The logic selects the largest multiple of the cache line size

based on the amount of data to transfer, with the maximum allowable

burst size determined from the DMA Mode (DMODE) burst size bits, and

Chip Test Five (CTEST5), bit 2. If multiple cache line size transfers are

not desired, set the DMA Mode (DMODE) burst size to exactly the cache

line size and the chip only issues single cache line transfers.

PCI Functional Description 2-9

Page 32

After each data transfer, the chip re-evaluates the burst size based on

the amount of remaining data to transfer and again selects the highest

possible multiple of the cache line size, no larger than the DMA Mode

(DMODE) burst size. The most likely scenario of this scheme is that the

chip selects the DMA Mode (DMODE) burst size after alignment, and

issues bursts of this size. The burst size is, in effect, throttled down

toward the end of a long Memory Move or Block Move transfer until only

the cache line size burst size is left. The chip finishes the transfer with

this burst size.

Latency – In accordance with the PCI specification, the chip's latency

timer is ignored when issuing a Write and Invalidate command such that

when a latency time-out occurs, the LSI53C876 continues to transfer up

to a cache line boundary. At that point, the chip relinquishes the bus, and

finishes the transfer at a later time using another bus ownership. If the

chip is transferring multiple cache lines it continues to transfer until the

next cache boundary is reached.

PCI Target Retry – During a Write and Invalidate transfer, if the target

device issues a retry (STOP with no TRDY, indicating that no data was

transferred), the chip relinquishes the bus and immediately tries to finish

the transfer on another bus ownership. The chip issues another Write

and Invalidate command on the next ownership, in accordance with the

PCI specification.

PCI Target Disconnect – During a Write and Invalidate transfer, if the

target device issues a disconnect the LSI53C876 relinquishes the bus

and immediately tries to finish the transfer on another bus ownership.

The chip does not issue another Write and Invalidate command on the

next ownership unless the address is aligned.

2.1.3 Internal Arbiter

The PCI to SCSI controller uses a single REQ/ - GNT/ signal pair to

arbitrate for access to the PCI bus. The LSI53C876 uses a round robin

arbitration scheme to allow both SCSI functions to arbitrate for PCI bus

access.

An internal arbiter circuit allows the different bus mastering functions

resident in the chip to arbitrate among themselves for the privilege of

arbitrating for PCI bus access. There are two independent bus mastering

functions inside the LSI53C876, one for each of the SCSI functions.

2-10 Functional Description

Page 33

2.1.4 PCI Cache Mode

The LSI53C876 supports the PCI specification for an 8-bit Cache Line

Size register located in the PCI configuration space. The Cache Line

Size register provides the ability to sense and react to nonaligned

addresses corresponding to cache line boundaries. In conjunction with

the Cache Line Size register, the PCI commands Read Line, Read

Multiple, and Write and Invalidate are each software enabled or disabled

to allow the user full flexibility in using these commands.

2.1.4.1 Selection of Cache Line Size

The cache logic for each bus mastering function selects a cache line size

based on the values for the burst size in the DMA Mode (DMODE)

register, and the PCI Cache Line Size register, whichever is appropriate.

Note: Each bus mastering function does not automatically use the

value in its PCI Cache Line Size register as the cache line

size value. The chip scales the value of the Cache Line

Size register down to the nearest binary burst size allowed

by the chip (2, 4, 8, 16, 32, 64, or 128). The SCSI function

compares this value to the DMODE burst size, then selects

the smaller as the value for the cache line size.

2.1.4.2 Alignment

The LSI53C876 uses the calculated line size value to monitor the current

address for alignment to the cache line size. When it is not aligned, the

chip attempts to align to the cache boundary by using a “smart aligning”

scheme. This means that it attempts to use the largest burst size

possible that is less than the cache line size, to reach the cache

boundary quickly with no overflow. This process is a stepping mechanism

that steps up to the highest possible burst size based on the current

address.

The stepping process begins at a 4 Dword boundary. The LSI53C876

first tries to align toa4Dwordboundary (0x0000, 0x0010, 0x0020, etc.)

by using single Dword transfers (no bursting). Once this boundary is

reached the chip evaluates the current alignment to various burst sizes

allowed, and selects the largest possible as the next burst size, while not

exceeding the cache line size. The chip then issues this burst and

re-evaluates the alignment to various burst sizes, again selecting the

PCI Functional Description 2-11

Page 34

largest possible while not exceeding the cache line size, as the next burst

size. This stepping process continues until the chip reaches the cache

line size boundary or runs out of data. Once a cache line boundary is

reached, the chip uses the cache line size as the burst size from then

on, except in the case of multiples (explained below). The alignment

process is finished at this point.

Example: Cache Line Size = 16, Current Address = 0x01 – The chip

is not aligned to a 4 Dword cache boundary (the stepping threshold), so

it issues four single Dword transfers (the first is a 3-byte transfer). At

address 0x10, the chip is aligned to a 4-Dword boundary, but not aligned

to any higher burst size boundaries that are less than the cache line size.

So, the part issues a burst of 4. At this point, the address is 0x20, and

the chip evaluates that it is aligned not only toa4Dwordboundary, but

also to an 8 Dword boundary. It selects the highest, 8, and bursts

8 Dwords. At this point, the address is 0x40, which is a cache line size

boundary. Alignment stops, and the burst size from then on is switched

to 16.

2.1.4.3 Memory Move Misalignment

The LSI53C876 does not operate in a cache alignment mode when a

Memory Move instruction type is issued and the read and write

addresses are different distances from the nearest cache line boundary.

For example,if the read address is 0x21F and the write address is 0x42F,

and the cache line size is 8, the addresses are byte aligned, but they are

not the same distance from the nearest cache boundary. The read

address is 1 byte from the cache boundary 0x220 and the write address

is 17 bytes from the cache boundary 0x440. In this situation, the chip

does not align to cache boundaries.

2-12 Functional Description

Page 35

2.2 SCSI Functional Description

2.2.1 Two SCSI Controllers

The LSI53C876 provides two SCSI controllers on a single chip. Each

SCSI controller provides a SCSI function that supports an 8-bit or 16-bit

bus. Each supports Ultra SCSI synchronous transfer rates up to

40 Mbytes/s, Ultra SCSI synchronous transfer rates up to 20 Mbytes/s,

and asynchronous transfer rates up to 14 Mbytes/s on a wide SCSI bus.

The SCSI functions are programmed with SCSI SCRIPTS, making it

easy to “fine tune” the system for specific mass storage devices or

SCSI-2 requirements.

The LSI53C876 offers low-level register access or a high-level control

interface. Like first generation SCSI devices, the LSI53C876 is accessed

as a register-oriented device. Error recovery and diagnostic procedures

use the ability to sample and/or assert any signal on the SCSI bus. In

support of SCSI loopback diagnostics, each SCSI core may perform a

self-selection and operate as both an initiator and a target.

The LSI53C876 is controlled by the integrated SCRIPTS processor

through a high-level logical interface. Commands controlling the SCSI

core are fetched out of the main host memory or local memory. These

commands instruct the SCSI core to Select, Reselect, Disconnect, Wait

for a Disconnect, Transfer Information, Change Bus Phases and, in

general, implement all aspects of the SCSI protocol. The SCRIPTS

processor is a special high-speed processor optimized for SCSI protocol.

2.2.2 SCRIPTS Processor

The SCSI SCRIPTS processor allows both DMA and SCSI commands

to be fetched from host memory or internal SCRIPTS RAM. Algorithms

written in SCSI SCRIPTS control the actions of the SCSI and DMA

cores. The SCRIPTS processor executes complex SCSI bus sequences

independently of the host CPU.

Algorithms may be designed to tune SCSI bus performance, to adjust to

new bus device types (such as scanners, communication gateways,etc.),

or to incorporate changes in the SCSI-2 or SCSI-3 logical bus definitions

SCSI Functional Description 2-13

Page 36

without sacrificing I/O performance. SCSI SCRIPTS are hardware

independent, so they can be used interchangeably on any host or CPU

system bus.

2.2.2.1 Internal SCRIPTS RAM

The LSI53C876 has 4 Kbytes (1024 x 32 bits) of internal, general

purpose RAM. The RAM is designed for SCRIPTS program storage, but

is not limited to this type of information. When the chip fetches SCRIPTS

instructions or Table Indirect information from the internal RAM, these

fetches remain internal to the chip and do not use the PCI bus. Other

types of access to the RAM by the chip use the PCI bus, as if they were

external accesses. The MAD5 pin disables the 4 K internal RAM. To

disable the internal RAM, connect a 4.7 kΩ resistor between the MAD5

pin and VSS(ground). The SCRIPTS RAM powers up enabled by default.

The RAM can be relocated by the PCI system BIOS anywhere in 32-bit

address space. The Base Address Register Two (Memory) register in

PCI configuration space contains the base address of the internal RAM.

This register is similar to the ROM Base Address register in PCI

configuration space. To simplify loading of the SCRIPTS instructions, the

base address of the RAM appears in the Scratch Register B

(SCRATCHB) register when bit 3 of the Chip Test Two (CTEST2) register

is set. The RAM is byte accessible from the PCI bus and is visible to any

bus mastering device on the bus. External accesses to the RAM (by the

CPU) follow the same timing sequence as a standard slave register

access, except that the required target wait-states drop from 5 to 3.

A complete set of development tools is available for writing custom

drivers with SCSI SCRIPTS. For more information on the SCSI SCRIPTS

instructions supported by the LSI53C876, see Chapter 5, “SCSI

SCRIPTS Instruction Set.”

2.2.2.2 Prefetching SCRIPTS Instructions

When enabled by setting the Prefetch Enable bit (bit 5) in the DMA

Control (DCNTL) register, the prefetch logic in the LSI53C876 fetches

8 Dwords of instructions. The prefetch logic automatically determines the

maximum burst size that it can perform based on the burst length as

determined by the values in the DMA Mode (DMODE) register. If the unit

cannot perform bursts of at least four Dwords, it disables itself. While the

2-14 Functional Description

Page 37

chip is prefetching SCRIPTS instructions, the PCI Cache Line Size

register value does not have any effect and the Read Line, Read

Multiple, and Write and Invalidate commands are not used.

Note: This feature is only useful if fetching SCRIPTS instructions

from main memory. Due to the short access time of

SCRIPTS RAM, prefetching is not necessary when fetching

instructions from this memory.

The LSI53C876 may flush the contents of the prefetch unit under certain

conditions, listed below, to ensure that the chip always operates from the

most current version of the SCRIPTS instruction. When one of these

conditions apply, the contents of the prefetch unit are automatically

flushed.

• On every Memory Move instruction. The Memory Move instruction

often places modified code directly into memory. To make sure that

the chip executes all recent modifications, the prefetch unit flushes

its contents and loads the modified code every time a instruction is

issued. To avoid inadvertently flushing the prefetch unit contents, use

the No Flush option for all Memory Move operations that do not

modify code within the next 8 Dwords. For more information on this

instruction, refer to Chapter 5, “SCSI SCRIPTS Instruction Set.”

• On every Store instruction. The Store instruction may also be used

to place modified code directly into memory. To avoid inadvertently

flushing the prefetch unit contents use the No Flush option for all

Store operations that do not modify code within the next 8 Dwords.

• On every write to the DMA SCRIPTS Pointer (DSP) register.

• On all Transfer Control instructions when the transfer conditions are

met. This is necessary because the next instruction to execute is not

the sequential next instruction in the prefetch unit.

• When the Prefetch Flush bit (DMA Control (DCNTL) register, bit 6)

is set. The unit flushes whenever this bit is set. The bit is

self-clearing.

2.2.2.3 OpCode Fetch Burst Capability

Setting the Burst OpCode Fetch Enable bit (bit 1) in the DMA Mode

(DMODE) register (0x38) causes the LSI53C876 to burst in the first two

Dwords of all instruction fetches. If the instruction is a Memory-to-

SCSI Functional Description 2-15

Page 38

Memory Move, the third Dword is accessed in a separate ownership. If

the instruction is an indirect type, the additional Dword is accessed in a

subsequent bus ownership. If the instruction is a Table Indirect Block

Move, the chip uses two accesses to obtain the four Dwords required, in

two bursts of two Dwords each.

Note: This feature is only useful if prefetching is disabled and

SCRIPTS instructions are fetched from main memory. Due

to the short access time of SCRIPTS RAM, burst opcode

fetching is not necessary when fetching instructions from

this memory.

2.2.2.4 Load/Store Instructions

The LSI53C876 supports the Load and Store instruction type, which

simplifies the movement of data between memory and the internal chip

registers. It also enables the chip to transfer bytes to addresses relative

to the Data Structure Address (DSA) register. For more information on

the Load and Store instructions, refer to Chapter 5, “SCSI SCRIPTS

Instruction Set.”

2.2.3 JTAG Boundary Scan Testing

The LSI53C876 includes support for JTAG boundary scan testing in

accordance with the IEEE 1149.1 specification with one exception, which

is explained in this section. This device accepts all required boundary

scan instructions including the optional CLAMP, HIGH-Z, and IDCODE

instructions.

The LSI53C876 uses an 8-bit instruction register to support all boundary

scan instructions. The data registers included in the device are the

Boundary Data register, the IDCODE register, and the Bypass register.

This device can handle a 10 MHz TCK frequency for TDO and TDI.

Due to design constraints, the RST/ pin (system reset) always 3-states

the SCSI pins when it is asserted. Boundary scan logic does not control

this action, and this is not compliant with the specification. There are two

solutions that resolve this issue:

2-16 Functional Description

Page 39

1. Use the RST/ pin as a boundary scan compliance pin. When the pin

deasserts, the device is boundary scan compliant and when it

asserts, the device is noncompliant. To maintain compliance the

RST/ pin must be driven high.

2. When RST/ asserts during boundary scan testing the expected

output on the SCSI pins must be the HIGH-Z condition, and not what

is contained in the boundary scan data registers for the SCSI pin

output cells.

2.2.4 SCSI Loopback Mode

The LSI53C876 loopback mode allows testing of both initiator and target

functions and, in effect, lets the chip communicate with itself. When the

Loopback Enable bit is set in the SCSI Test Two (STEST2) register, bit 4,

the LSI53C876 allows control of all SCSI signals, whether the chip is

operating in the initiator or target mode. For more information on this

mode of operation, refer to the

Guide

.

2.2.5 Parity Options

The LSI53C876 implements a flexible parity scheme that allows control

of the parity sense, allows parity checking to be turned on or off, and has

the ability to deliberately send a byte with bad parity over the SCSI bus

to test parity error recovery procedures. Table 2.2 defines the bits that

are involved in parity control and observation. Table 2.3 describes the

parity control function of the Enable Parity Checking and Assert SCSI

Even Parity bits in the SCSI Control One (SCNTL1) register, bit 2.

Table 2.4 describes the options available when a parity error occurs.

Figure 2.2 shows where parity checking is done in the LSI53C876.

SCSI SCRIPTS Processors Programming

SCSI Functional Description 2-17

Page 40

Table 2.2 Bits Used for Parity Control and Generation

BIt Name Location Description

Assert SATN/ on Parity

Errors

Enable Parity Checking SCSI Control

Assert Even SCSI Parity SCSI Control

Disable Halton SATN/or

a Parity Error (Target

Mode Only)

Enable Parity Error

Interrupt

Parity Error SCSI Interrupt

Status of SCSI Parity

Signal

SCSI SDP1 Signal SCSI Status Two

SCSI Control

Zero (SCNTL0),

Bit 1

Zero (SCNTL0),

Bit 3

One (SCNTL1),

Bit 2

SCSI Control

One (SCNTL1),

Bit 5

SCSI Interrupt

Enable Zero

(SIEN0), Bit 0

Status Zero

(SIST0), Bit 0

SCSIStatusZero

(SSTAT0), Bit 0

(SSTAT2), Bit 0

Causes the LSI53C876 to automatically assert SATN/

when it detects a parity error while operating as an

initiator.

Enables the LSI53C876 to check for parity errors. The

LSI53C876 checks for odd parity.

Determines the SCSI parity sense generated by the

LSI53C876 to the SCSI bus.

Causes the LSI53C876 not to halt operations when a

parity error is detected in target mode.

Determines whether the LSI53C876 generates an

interrupt when it detects a SCSI parity error.

This status bit is set whenever the LSI53C876 detects

a parity error on the SCSI bus.

This status bit represents the active HIGH current state

of the SCSI SDP0 parity signal.

This bit represents the active HIGH current state of the

SCSI SDP1 parity signal.

Latched SCSI Parity SCSI Status Two

Master Parity Error

Enable

Master Data Parity Error DMA Status

Master Data Parity Error

Interrupt Enable

(SSTAT2), Bit 3

and SCSI Status

One (SSTAT1),

Bit 3

Chip Test Four

(CTEST4), Bit 3

(DSTAT), Bit 6

DMA Interrupt

Enable (DIEN),

Bit 6

2-18 Functional Description

These bits reflect the SCSI odd parity signal

corresponding to the data latched into the SCSI Input

Data Latch (SIDL) register.

Enables parity checking during master data phases.

Set when the LSI53C876, as a PCI master, detects a

target device signaling a parity error during a data

phase.

By clearing this bit, a Master Data Parity Error does not

cause assertion of INTA/ (or INTB/), but the status bit

is set in the DMA Status (DSTAT) register.

Page 41

Table 2.3 SCSI Parity Control

EPC AESP Description

0 0 Does not check for parity errors. Parity is generated when sending

0 1 Does not check for parity errors. Parity is generated when sending

1 0 Checks for odd parity on SCSI data received. Parity is generated

1 1 Checks for odd parity on SCSI data received. Parity is generated

1. Key:

EPC = Enable Parity Checking (bit 3, SCSI Control Zero (SCNTL0)).

ASEP = Assert SCSI Even Parity (bit 2, SCSI Control One (SCNTL1)).

SCSI data. Asserts odd parity when sending SCSI data.

SCSI data. Asserts even parity when sending SCSI data.

when sending SCSI data. Asserts odd parity when sending SCSI

data.

when sending SCSI data. Asserts even parity when sending SCSI

data.

Table 2.4 SCSI Parity Errors and Interrupts

DPH PAR Description

0 0 Halts when a parity error occurs in the target or initiator mode and

0 1 Halts when a parity error occurs in the target mode and generates

does not generate an interrupt.

an interrupt in target or initiator mode.

1 0 Does not halt in target mode when a parity error occurs until the

1 1 Does not halt in target mode when a parity error occurs until the

Key:

DHP = Disable Halt on SATN/ or Parity Error (bit 5, SCSI Control One (SCNTL1).

PAR = Parity Error (bit 0, SCSI Interrupt Enable Zero (SIEN0).

end of the transfer. An interrupt is not generated.

end of the transfer. An interrupt is generated.

SCSI Functional Description 2-19

Page 42

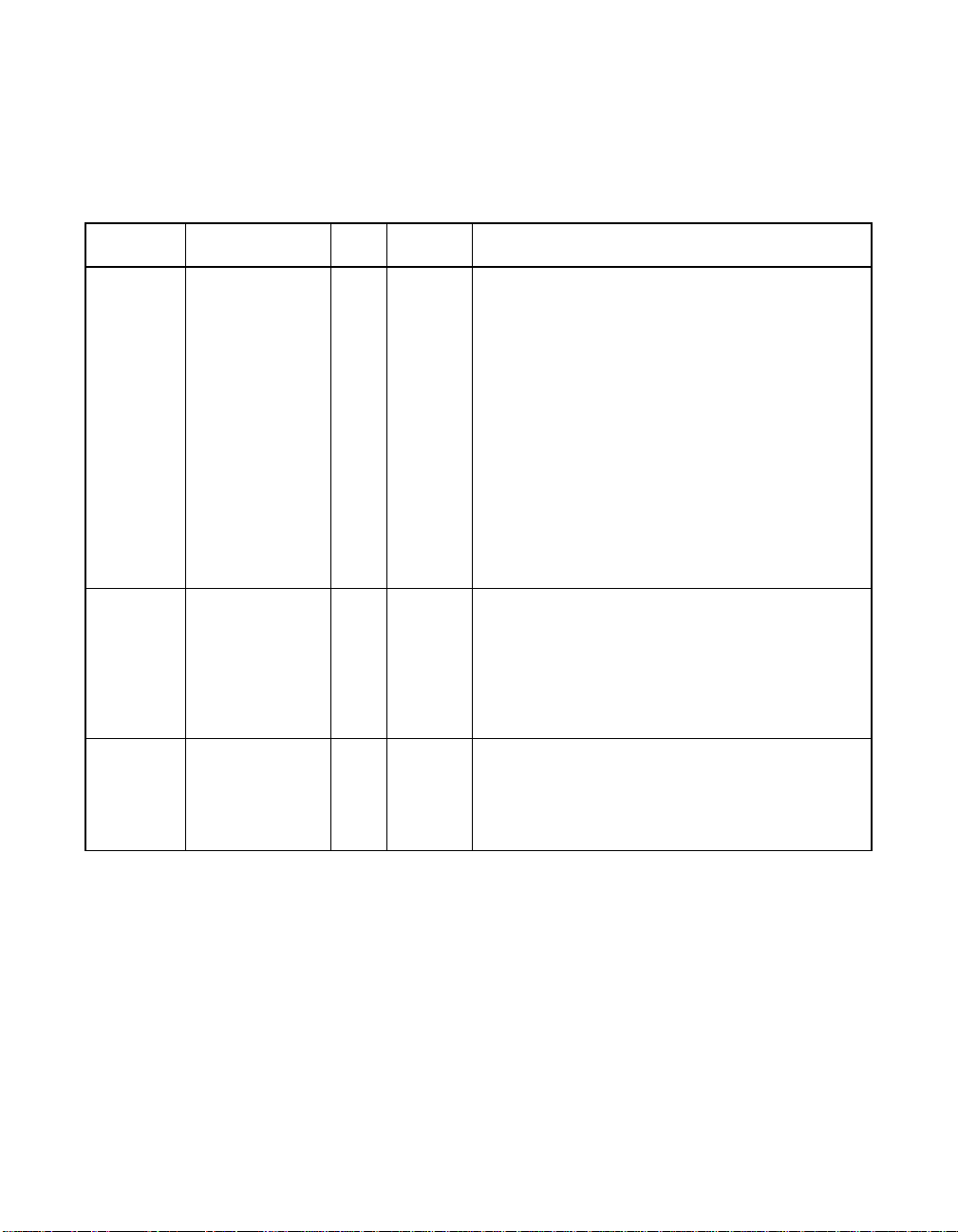

Figure 2.2 Parity Checking/Generation

Asynchronous

SCSI Send

PCI Interface**

X

DMA FIFO*

(32 Bits x 134)

SODL Register*

S

SCSI Interface**

X - Check parity

G - Generate 32-bit even PCI parity

S - Generate 8-bit odd SCSI parity

Asynchronous

SCSI Receive

PCI Interface**

DMA FIFO*

(32 Bits x 134)

SIDL Register*

SCSI Interface**

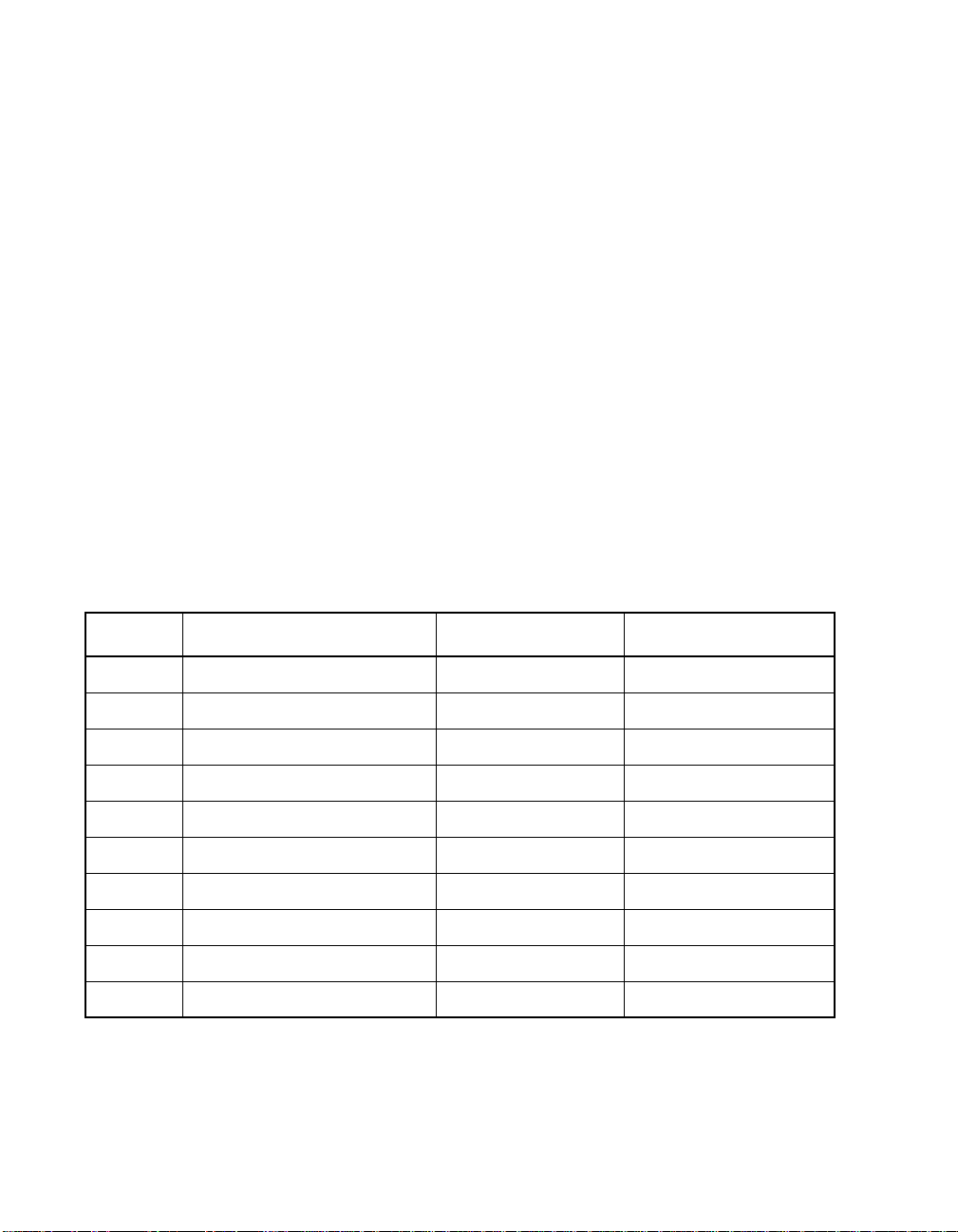

2.2.6 DMA FIFO

The DMA FIFO is 4 bytes wide by 134 transfers deep. The DMA FIFO is

illustrated in Figure 2.3. The default DMA FIFO size is 88 bytes to assure

compatibility with older products in the LSI53C8XX family.

The DMA FIFO size may be set to 536 bytes by setting the DMA FIFO

Size bit, bit 5, in the Chip Test Five (CTEST5) register.

Synchronous

SCSI Send

PCI Interface**

G

(32 Bits x 134)

SODL Register*

X

SODR Register*

SCSI Interface**

X

DMA FIFO*

S

Synchronous

SCSI Receive

PCI Interface**

G

DMA FIFO*

(32 Bits x 134)

X

SCSI FIFO*

(8 or 16 Bits x 16)

X

SCSI Interface**

* = No parity protection

** = Parity protected

Figure 2.3 DMA FIFO Sections

134

134

Transfers

Transfers

Deep

Deep

2-20 Functional Description

.

.

.

8 Bits

8 Bits

Byte Lane 3

Byte Lane 3

8 Bits

8 Bits

Byte Lane 2

Byte Lane 2

32 Bytes Wide

32 Bytes Wide

8 Bits

8 Bits

Byte Lane 1

Byte Lane 1

8 Bits

8 Bits

Byte Lane 0

Byte Lane 0

.

.

.

.

.

.

Page 43

2.2.6.1 Data Paths

The LSI53C876 automatically supports misaligned DMA transfers. A

536-byte FIFO allows the LSI53C876 to support 2, 4, 8, 16, 32, 64, or

128 Dword bursts across the PCI bus interface.

The data path through the LSI53C876 depends on whether data is being

moved into or out of the chip, and whether SCSI data is being transferred

asynchronously or synchronously.

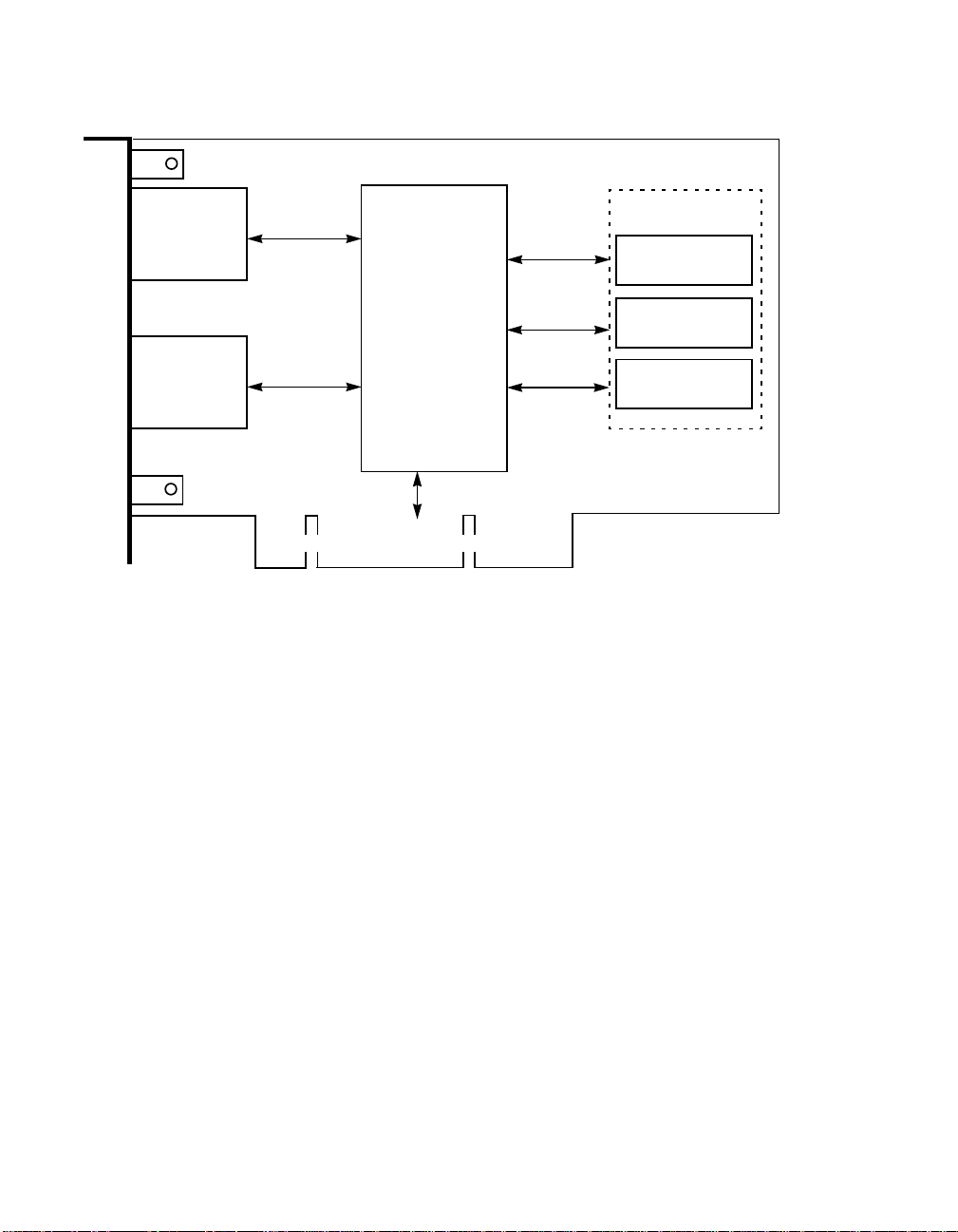

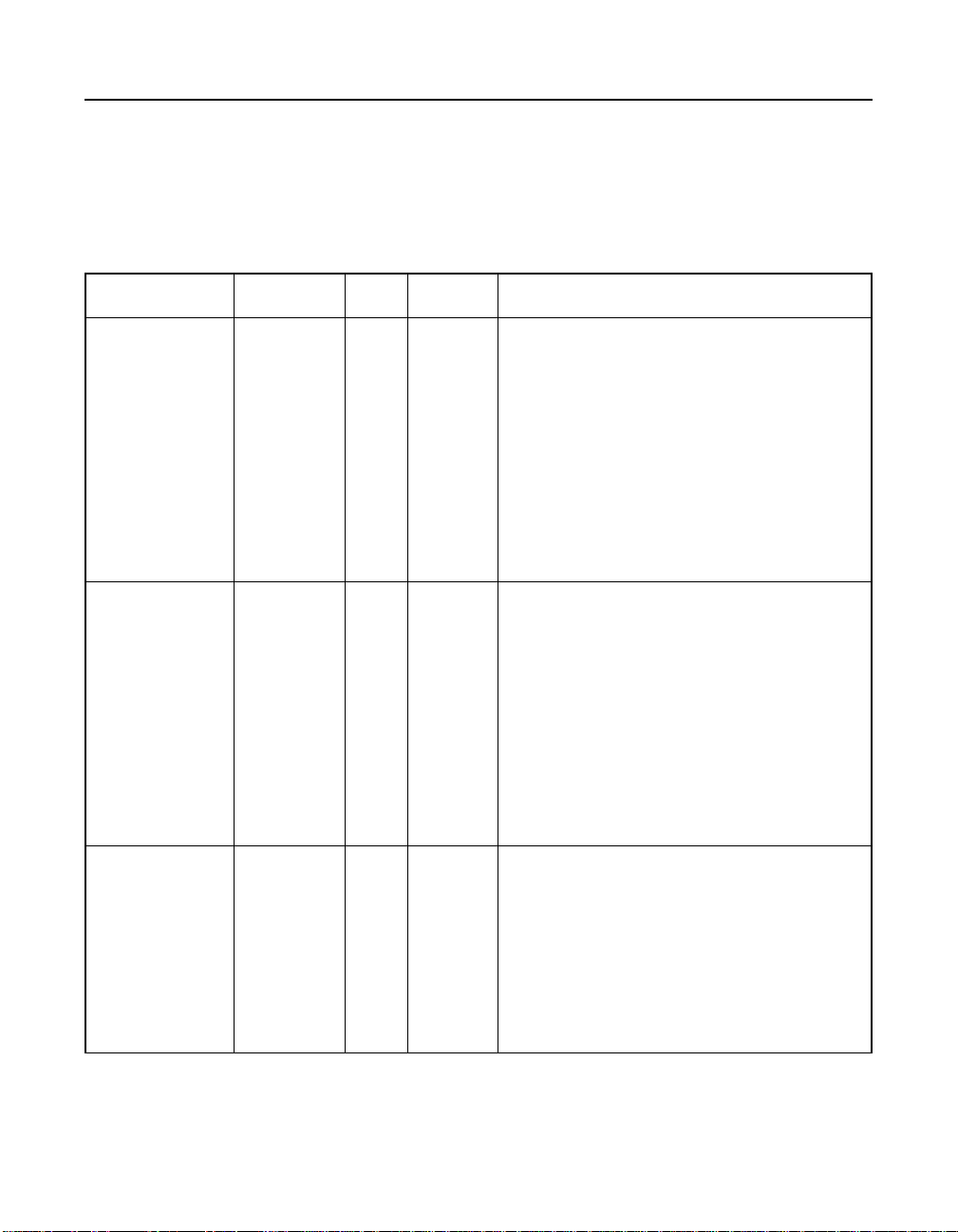

Figure 2.4 shows how data is moved to/from the SCSI bus in each of the

different modes.

The following steps determine if any bytes remain in the data path when

the chip halts an operation:

Asynchronous SCSI Send –

Step 1. If the DMA FIFO size is set to 88 bytes, look at the DMA FIFO

(DFIFO) and DMA Byte Counter (DBC) registers and calculate

if there are bytes left in the DMA FIFO. To make this calculation,

subtract the seven least significant bits of the DMA Byte

Counter (DBC) register from the 7-bit value of the DMA FIFO

(DFIFO) register. AND the result with 0x7F for a byte count

between 0 and 88.

If the DMA FIFO size is set to 536 bytes (using bit 5 of the Chip

Test Five (CTEST5) register), subtract the 10 least significant

bits of the DMA Byte Counter (DBC) register from the 10-bit

value of the DMA FIFO Byte Offset Counter, which consists of

bits [1:0] in the Chip Test Five (CTEST5) register and bits [7:0]

of the DMA FIFO (DFIFO) register. AND the result with 0x3FF

for a byte count between 0 and 536.

Step 2. Read bit 5 in the SCSI Status Zero (SSTAT0) and SCSI Status

Two (SSTAT2) registers to determine if any bytes are left in the

SCSI Output Data Latch (SODL) register. If bit 5 is set in the

SSTAT0 or SSTAT2 register, then the least significant byte or

the most significant byte in the SCSI Output Data Latch (SODL)

register is full, respectively. Checking this bit also reveals bytes

left in the SCSI Output Data Latch (SODL) register from a

Chained Move operation with an odd byte count.

SCSI Functional Description 2-21

Page 44

Synchronous SCSI Send –

Step 1. If the DMA FIFO size is set to 88 bytes, look at the DMA FIFO

(DFIFO) and DMA Byte Counter (DBC) registers and calculate

if there are bytes left in the DMA FIFO. To make this calculation,

subtract the seven least significant bits of the DMA Byte

Counter (DBC) register from the 7-bit value of the DMA FIFO

(DFIFO) register. AND the result with 0x7F for a byte count

between 0 and 88.

If the DMA FIFO size is set to 536 bytes (bit 5 of the Chip Test

Five (CTEST5) register it set), subtract the 10 least significant

bits of the DMA Byte Counter (DBC) register from the 10-bit

value of the DMA FIFO Byte Offset Counter, which consists of

bits [1:0] in the Chip Test Five (CTEST5) register and bits [7:0]

of the DMA FIFO (DFIFO) register. AND the result with 0x3FF

for a byte count between 0 and 536.

Step 2. Read bit 5 in the SCSI Status Zero (SSTAT0) and SCSI Status

Two (SSTAT2) registers to determine if any bytes are left in the

SCSI Output Data Latch (SODL) register. If bit 5 is set in the

SSTAT0 or SSTAT2 register, then the least significant byte or

the most significant byte in the SCSI Output Data Latch (SODL)

register is full, respectively. Checking this bit also reveals bytes

left in the SCSI Output Data Latch (SODL) register from a

Chained Move operation with an odd byte count.

Step 3. Read bit 6 in the SCSI Status Zero (SSTAT0) and SCSI Status

Two (SSTAT2) registers to determine if any bytes are left in the

SODR register. If bit 6 is set in the SCSI Status Zero (SSTAT0)

or SCSI Status Two (SSTAT2) register, then the least significant

byte or the most significant byte in the SODR register is full,

respectively.

Asynchronous SCSI Receive –

Step 1. If the DMA FIFO size is set to 88 bytes, look at the DMA FIFO

(DFIFO) and DMA Byte Counter (DBC) registers and calculate

if there are bytes left in the DMA FIFO. To make this calculation,

subtract the seven least significant bits of the DMA Byte

Counter (DBC) register from the 7-bit value of the DMA FIFO

(DFIFO) register. AND the result with 0x7F for a byte count

between 0 and 88.

2-22 Functional Description

Page 45

If the DMA FIFO size is set to 536 bytes (bit 5 of the Chip Test

Five (CTEST5) register is set), subtract the 10 least significant

bits of the DMA Byte Counter (DBC) register from the 10-bit

value of the DMA FIFO Byte Offset Counter, which consists of

bits [1:0] in the Chip Test Five (CTEST5) register and bits [7:0]

of the DMA FIFO (DFIFO) register. AND the result with 0x3FF

for a byte count between 0 and 536.

Step 2. Read bit 7 in the SCSI Status Zero (SSTAT0) and SCSI Status

Two (SSTAT2) register to determine if any bytes are left in the

SCSI Input Data Latch (SIDL) register. If bit 7 is set in the

SSTAT0 or SSTAT2, then the least significant byte or the most

significant byte is full, respectively.

Step 3. If any wide transfers have been performed using the Chained

Move instruction, read the Wide SCSI Receive bit (SCSI

Control Two (SCNTL2), bit 0) to determine whether a byte is left

in the SCSI Wide Residue (SWIDE) register.

Synchronous SCSI Receive –

Step 1. If the DMA FIFO size is set to 88 bytes, subtract the seven least

significant bits of the DMA Byte Counter (DBC) register from

the 7-bit value of the DMA FIFO (DFIFO) register. AND the

result with ox7F for a byte count between 0 and 88.

If the DMA FIFO size is set to 536 bytes (bit 5 of the Chip Test

Five (CTEST5) register is set), subtract the 10 least significant

bits of the DMA Byte Counter (DBC) register from the 10-bit

value of the DMA FIFO Byte Offset Counter, which consists of

bits [1:0] in the Chip Test Five (CTEST5) register and bits [7:0]

of the DMA FIFO (DFIFO) register. AND the result with 0x3FF

for a byte count between 0 and 536.

Step 2. Read the SCSI Status One (SSTAT1) register and examine bits

[7:4], the binary representation of the number of valid bytes in

the SCSI FIFO, to determine if any bytes are left in the SCSI

FIFO.

Step 3. If any wide transfers have been performed using the Chained

Move instruction, read the Wide SCSI Receive bit (SCSI

Control Two (SCNTL2), bit 0) to determine whether a byte is left

in the SCSI Wide Residue (SWIDE) register.

SCSI Functional Description 2-23

Page 46

Figure 2.4 shows how data is moved to/from the SCSI bus in each of the

different modes.

Figure 2.4 LSI53C876 Host Interface SCSI Data Paths

Asynchronous

SCSI Send

PCI Interface

DMA FIFO

(32 Bits x 134)

SODL Register

SCSI Interface

Asynchronous

SCSI Receive

PCI Interface

DMA FIFO

(32 Bits x 134)

SIDL Register

SCSI Interface

2.2.7 SCSI Bus Interface

All SCSI signals are active LOW. The LSI53C876 contains the SE output

drivers and can be connected directly to the SCSI bus. Each output is

isolated from the power supply to ensure that a powered-down

LSI53C876 has no effect on an active SCSI bus (CMOS “voltage

feed-through” phenomena). TolerANT technology provides signal filtering

at the inputs of SREQ/ and SACK/ to increase immunity to signal

reflections.

SWIDE Register

Synchronous

SCSI Send

PCI Interface

DMA FIFO

(32 Bits x 134)

SODL Register

SODR Register

SCSI Interface

Synchronous

SCSI Receive

PCI Interface

DMA FIFO

(32 Bits x 134)

SWIDE Register

SCSI FIFO

(8 or 16 Bits x 16)

SCSI Interface

2.2.7.1 Differential Mode

In differential mode, the SDIR[15:0], SDIRP[1:0], IGS, TGS, RSTDIR,

BSYDIR, and SELDIR signals control the direction of external differential

pair transceivers. The LSI53C876 is placed in differential mode by setting

the DIF bit, bit 5 of the SCSI Test Two (STEST2) register (0x4E). Setting

this bit 3-states the BSY/, SEL/, and RST/ pads so they can be used as

pure input pins. When TolerANT active negation is enabled, the

recommended resistor value on the REQ/, ACK/, MSG/, C_D/, I_O/,

2-24 Functional Description

Page 47

ATN/, SD[15:0], and SDP[1:0]/ signals is 1.5 kΩ. In addition to the

standard SCSI lines, the following signals defined in Table 2.5 are used

during differential operation by the LSI53C876:

Table 2.5 Differential Mode

Signal Function

BSYDIR, SELDIR,

RSTDIR

SDIR[15:0],

SDIRP[1:0]

IGS Active HIGH signal used to control direction of the differential driver for initiator

TGS Active HIGH signal used to control direction of the differential drivers for target

DIFFSENS Input to the LSI53C876 used to detect the presence of an SE device on a

Active HIGH signals used to enable the differential drivers as outputs for SCSI

signals BSY/, SEL/, and RST/, respectively.

Active HIGH signals used to control direction of the differential drivers for SCSI

data and parity lines, respectively.

group signals ATN/ and ACK/.

group signals MSG/, C/D/, I/O/, and REQ/.

differential system. If a logical zero is detected on this pin, then it is assumed

that an SE device is on the bus and all SCSI outputs will be 3-stated to avoid

damage to the transceiver.

See Figure 2.5 for an example differential wiring diagram, in which the

LSI53C876 is connected to the TI SN75976A differential transceiver. The

recommended value of the pull-up resistor on the REQ/, ACK/, MSG/,

C/D/, I/O/, ATN/, SD[15:0]/, SDP0/, and SDP1/ lines is 680 Ω when the

Active Negation portion of LSI Logic TolerANT technology is not enabled.

When TolerANT technology is enabled, the recommended resistor value

on the REQ/, ACK/, SD[7:0]/, and SDP0/ signals is 1.5 kΩ. The electrical

characteristics of these pins change when TolerANT is enabled,

permitting a higher resistor value.

To interface the LSI53C876 to the SN75976A, connect the DIR pins, as

well as IGS and TGS, of the LSI53C876 directly to the transceiver

enables (nDE/RE/). These signals control the direction of the channels

on the SN75976A.

The SCSI bidirectional control and data pins (SD[15:0]/, SDP0/, SDP1/,

REQ/, ACK/, MSG/, I_O/, C_D/, and ATN/) of the LSI53C876 connect to

the bidirectional data pins (nA) of the SN75976A with a pull-up resistor.

The three remaining pins, SEL/, BSY/, and RST/ are connected to the

SN75976A with a pull-down resistor. The pull-down resistors are required

SCSI Functional Description 2-25

Page 48

when the pins (nA) of the SN75976A are configured as inputs. When the

data pins are inputs, the resistors provide a bias voltage to both the

LSI53C876 pins (SEL/, BSY/, and RST/) and the SN75976A data pins.