ATMEL AT90LS8535-4PI, AT90LS8535-4PC, AT90LS8535-4JI, AT90LS8535-4JC, AT90LS8535-4AI Datasheet

...

1

Features

•

Utilizes the AVR

®

Enhanced RISC Architecture

•

AVR - High Performance and Low Power RISC Architecture

•

118 Powerful Instructions - Most Single Clock Cycle Execution

•

8K bytes of In-System Programmable Flash AT90S/LS8535

4K bytes of In-System Programmable Flash AT90S/LS4434

– SPI Serial Interface for In-System Programming

– Endurance: 1,000 Write/Erase Cy cles

•

512 bytes EEPROM AT90S/LS8535

256 bytes EEPROM AT90S/LS4434

– Endurance: 100,000 Write/Erase Cycles

•

512 bytes Internal SRAM AT90S/LS8535

256 bytes Internal SRAM AT90S/LS4434

•

8-Channel, 10-Bit ADC

•

32 x 8 General Purpose Working Registers

•

32 Programmable I/O Lines

•

Programmable Serial UART

•

VCC: 4.0 - 6.0V AT90S4434/AT90S8535

•

VCC: 2.7 - 6.0V AT90LS4434/AT90LS8535

•

Speed Grades:

0 - 8 MHz AT90S4434/AT90S8535,

0 - 4 MHz (AT90LS4434/AT90LS8535

•

Power-On Reset Circuit

•

Up to 8 MIPS Throughput at 8 MHz

•

RTC with Separate Oscillator and Counter Mode

•

Two 8-Bit Timer/Counters with Separate Prescaler and Compare Mode

•

One 16-Bit Timer/Counter with Separate Prescaler and Compare and Capture Modes

•

3 PWM channels

•

External and Internal Interrupt Sources

•

Programmable Watchdog Timer with On-Chip Oscillator

•

On-Chip Analog Comparator

•

Three Sleep Modes: Idle, Power Save, and Power Down

•

Programming Lock for Software Security

Description

The AT90S4434/8535 is a low- po wer CMO S 8-bi t mi c roco ntr oller ba se d on the AV R

®

enhanced RISC architecture . By exec uting powe rful instruc tions in a single clock

cycle, the AT90S4434/8535 achieves throughputs approaching 1 MIPS per MHz

allowing the system designer to optimize power consumption versus processing

speed.

Rev. 1041AS–05/98

8-Bit

Microcontroller

with 4K/8K

Bytes In-System

Programmable

Flash

A T90S4434

A T90LS4434

A T90S8535

A T90LS8535

Advance

Information

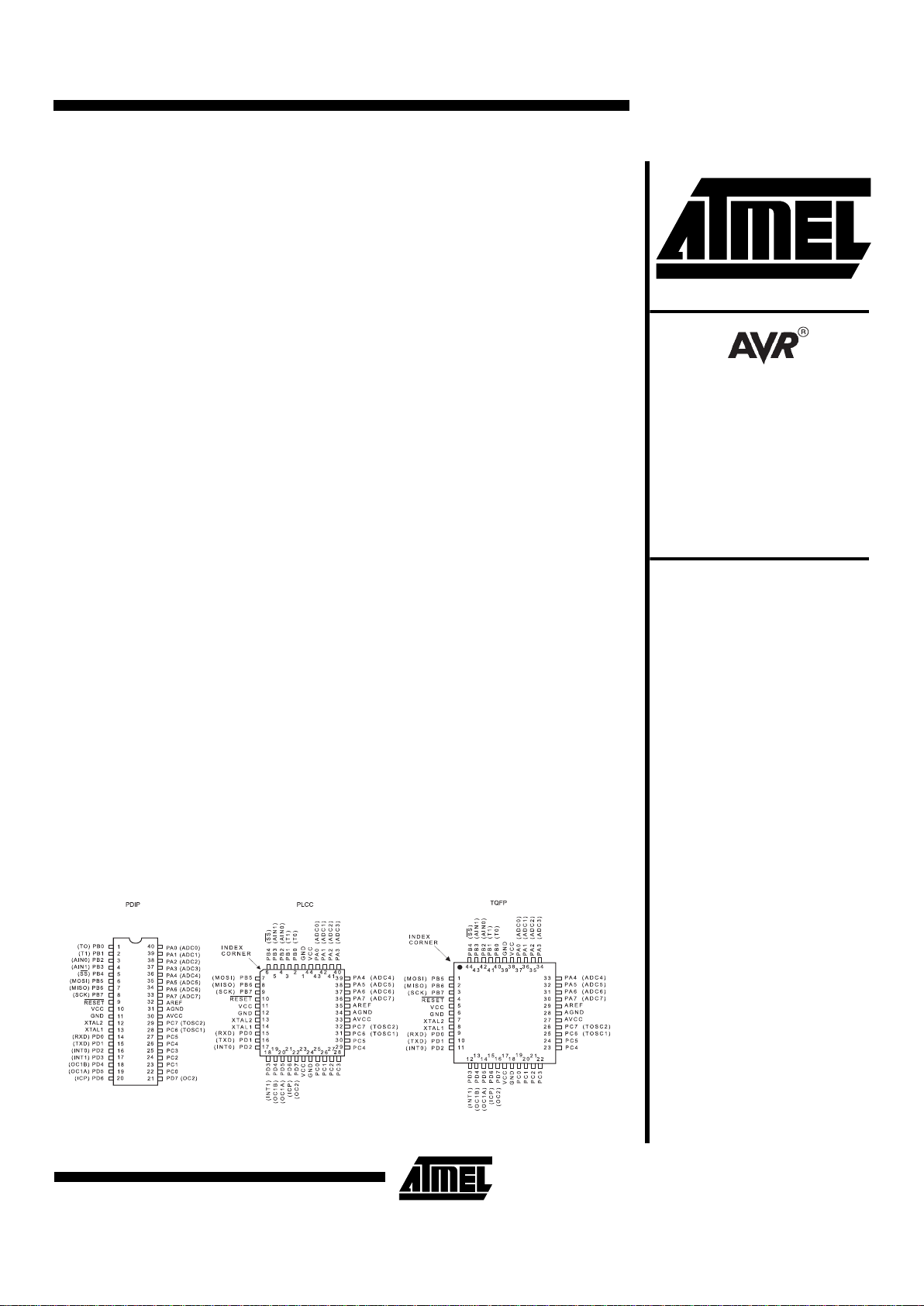

Pin Configurations

(continued)

Note: This is a summary document. For the complete 80 page

document, please visit our website at

www.atmel.com

or e-mail at

literature@atmel.com

and request literature #1041A.

AT90S/LS4434 and AT90S/LS8535

2

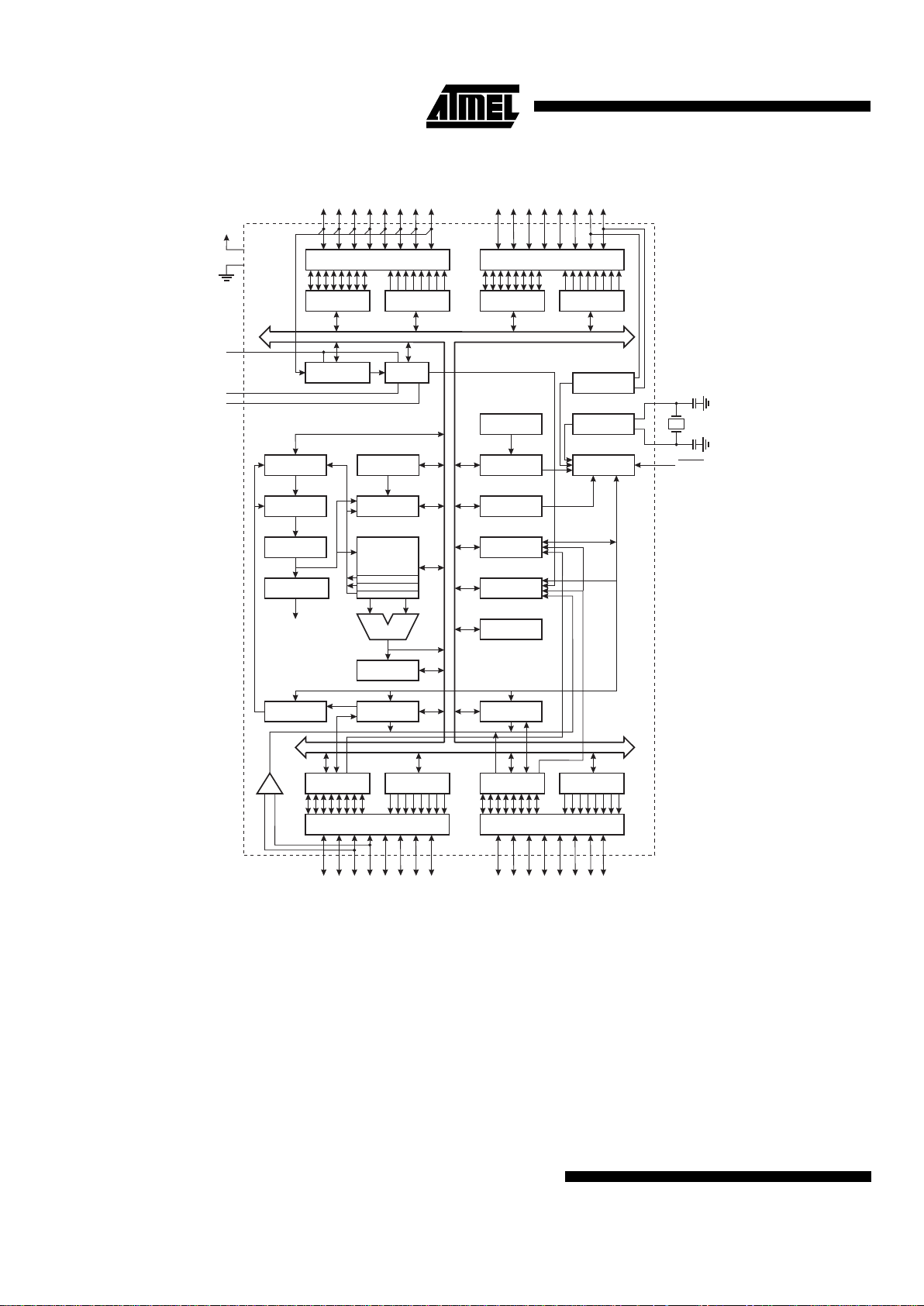

Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. Al l the 32 registers are

directly connected to the Arithmetic Logic Unit (ALU),

allowing two independent registers to be accessed in on e

single instruction executed in one clock cycle. The resulting

architecture is mo re c ode efficient while ach ie ving thr ou ghputs up to ten times faster than conventiona l CISC microcontrollers.

The AT90S4434/8535 provides the following features:

4K/8K bytes of In-System Programmable Flash, 256/512

bytes EEPROM, 256/512 bytes SRAM, 32 general purpose

I/O lines, 32 general purpose working registers, RTC, three

flexible timer/counters with compare modes, internal and

external interrupts, a programmable serial UART, 8-channel, 10-bit ADC, programmable Watchdog Ti mer with inte rnal oscillator, an SPI serial port and three software

selectable pow er saving modes. Th e Idle m ode sto ps the

CPU while allowing the SRAM, timer/counters, SPI port

and interrupt system to continue func tioning. The Power

Down mode saves the register contents but freezes the

oscillator, disabling all other chip function s until the next

interrupt or hardware reset. In Power Save mode, the timer

oscillator continues to run, allowing the user to maintain a

timer base while the rest of the device is sleeping.

The device is manufac tured using Atmel’ s high density

non-volatile memory technology. The on-chip ISP Flash

PROGRAM

COUNTER

INTERNAL

OSCILLATOR

WATCHDOG

TIMER

STACK

POINTER

PROGRAM

FLASH

MCU CONTROL

REGISTER

SRAM

GENERAL

PURPOSE

REGISTERS

INSTRUCTION

REGISTER

TIMER/

COUNTERS

INSTRUCTION

DECODER

DATA DIR.

REG. PORTB

DATA DIR.

REG. PORTA

DATA DIR.

REG. PORTD

DATA DIR.

REG. PORTC

DATA REGISTER

PORTB

DATA REGISTER

PORTA

ANALOG MUX ADC

DATA REGISTER

PORTD

DATA REGISTER

PORTC

PROGRAMMING

LOGIC

TIMING AND

CONTROL

OSCILLATOR

OSCILLATOR

INTERRUPT

UNIT

EEPROM

SPI

UART

STATUS

REGISTER

Z

Y

X

ALU

PORTB DRIVERS

PORTA DRIVERS

PORTD DRIVERS

PORTC DRIVERS

PB0 - PB7

PA0 - PA7

RESET

VCC

AVCC

AGND

AREF

GND

XTAL2

XTAL1

CONTROL

LINES

+

ANALOG

COMPARATOR

PD0 - PD7

PC0 - PC7

8-BIT DATA BUS

AT90S/LS4434 and AT90S/LS8535

3

allows the program memory to be reprogrammed in-system

through an SPI serial interface or by a conventional nonvolatile memory programmer. By combining an 8-bit RISC

CPU with In-System Programmable Flash on a monolithic

chip, the Atmel AT90 S4434/853 5 is a powerful micro controller that provides a highly flexible and cost effective solution to many embedded control applications.

The AT90S4434/853 5 AVR is su pported wi th a full suite of

program and system development tools including: C compilers, macro assemblers, program debugger/simulators,

in-circuit emulators, and evaluation kits.

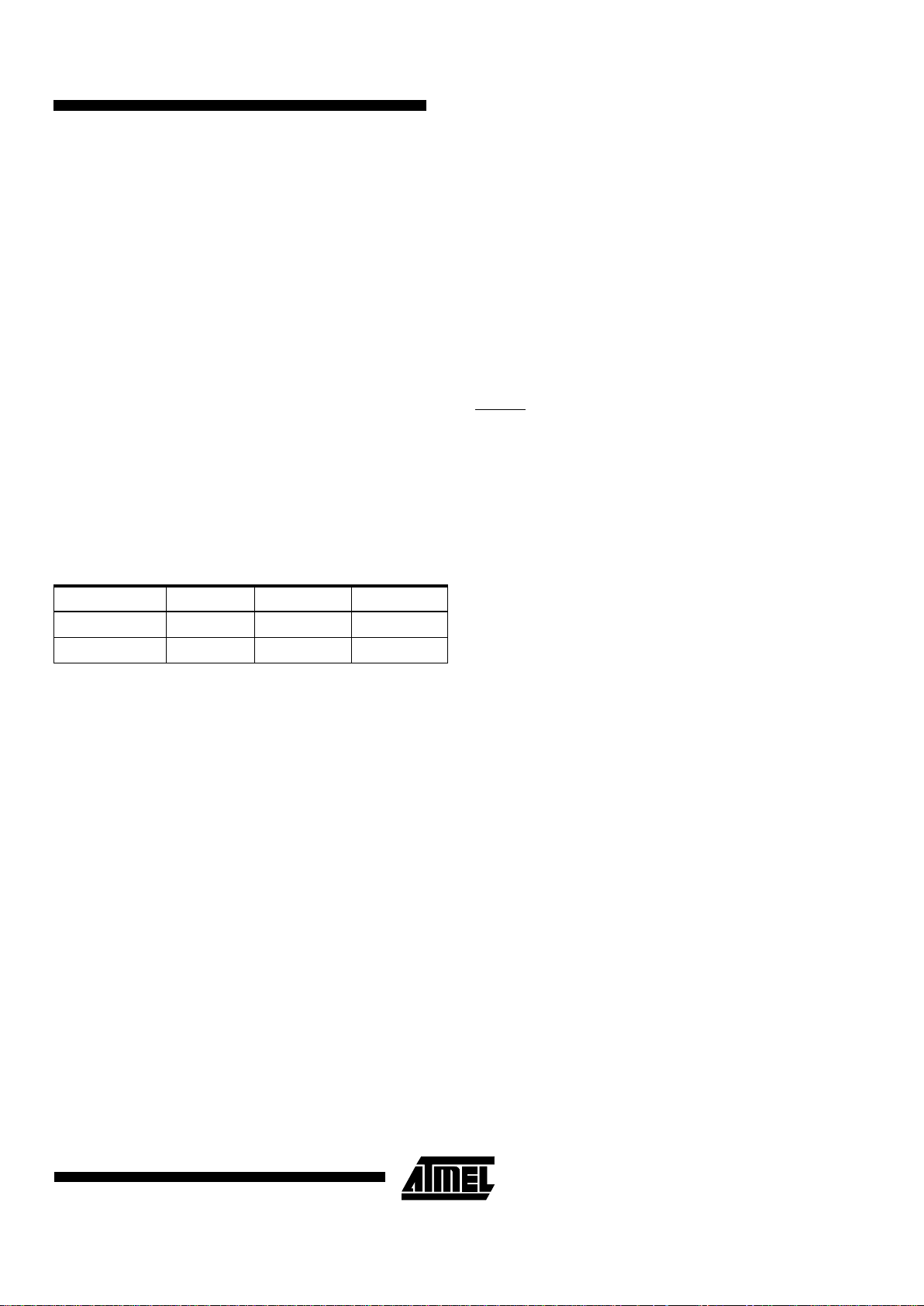

Comparison between AT90S4434 and AT90S8535

The AT90S4434 has 4K bytes of In -S yste m Pr og ramma bl e

Flash, 256 bytes of EEPROM, and 256 bytes of internal

SRAM.

The AT90S8535 has 8K bytes of In -S yste m Pr og ramma bl e

Flash, 512 bytes of EEPROM, and 512 bytes of internal

SRAM.

Table 1 summarizes the dif ferent memory size s for the tw o

devices.

Pin Descriptions

VCC

Digital supply voltage

GND

Digital ground

Port A (PA7..PA0)

Port A is an 8-bit bi-directional I/O port. Port pins can provide internal pull-up resistors (selected for each bit). The

Port A output buffers can sink 20mA and can drive LED displays directly. When pins PA0 to PA7 are used as inputs

and are externally pulled low, they will source cur rent if the

internal pull-up resistors are activated.

Port A also se rves as the analog inp uts to the A/D Converter.

Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O pin s with inte rnal pu ll-up

resistors. The Port B output buffers can sink 20 mA. As

inputs, Port B pins t hat a re ex ternal ly pu ll ed l ow wi ll s our ce

current if the pull-up resistors are activated.

Port B also serves the fu nction s of vario us speci al featur es

of the AT90S4434/8535 as listed on page 52.

Port C (PC7..PC0)

Port C is an 8-bit bi-directional I/O port with internal pullup

resistors. The Port C output buffers can sink 20 mA. As

inputs, Port C pins that are external ly pul le d low will s ourc e

current if the pu ll-up res istors are activated . Two Port C

pins can alternatively be used as oscillator for

Timer/Counter2.

Port D (PD7..PD0)

Port D is an 8-bit bidirectional I/O port with internal pull-up

resistors. The Port D output buffers can sink 20 mA. As

inputs, Port D pins that are external ly pul le d low will s ourc e

current if the pull-up resistors are activated.

Port D also serves th e fu nctions of various special fe atur es

of the AT90S4434/8535 as listed on page 59.

RESET

Reset input. A low on t his pi n for two machi ne cy cles wh ile

the oscillator is running resets the device.

XTAL1

Input to the inverting os cillator ampli fier and input to th e

internal clock operating circuit.

XTAL2

Output from the inverting oscillator amplifier

AVCC

This is the supply voltage pin for the A/D Converter. It

should be externally connected to VCC via a low-pass filter.

See page 47 for details on operation of the ADC.

AREF

This is the analog reference input for the A/D Converter.

For ADC operations, a voltag e in the r ange A GND to AV

CC

must be applied to this pin.

AGND

Analog ground. If the board has a separate analog ground

plane, this pin should be connected to this ground plane.

Otherwise, connect to GND.

Crystal Oscillators

XTAL1 and XTAL2 are input and output, respectively, of an

inverting amplifier which can be configured for use as an

on-chip oscillator, as shown in Figure 1. Either a quartz

crystal or a ceramic resonator may be used. To drive the

device from an external clock source, XTAL2 should be left

unconnected while XTAL1 is driven as shown in Figure 2.

For the Timer Oscillator pins, PC6(OSC1) and PC7(OSC2),

the crystal is connected directly between the pins. No

external capac itors ar e neede d. The osci llator i s optim ized

for use with a 32,768 Hz watch crystal. An external clock

signal applied to t his pin g oes through th e same am plifier

having a bandwidth of 256 kHz. The external clock si gnal

should therefore be in the interval 0 Hz - 256 kHz.

Table 1.

Memory Size Summary

Part Flash EEPROM SRAM

AT90S4434 4K bytes 256 bytes 256 bytes

AT90S8535 8K bytes 512 bytes 512 bytes

Loading...

Loading...