Features

• 80C52 Compatible

– 8051 Pin and Instruction Compatible

– Four 8-bit I/O Ports

– Three 16-bit Tim er/Counters

– 256 Bytes Scratch Pad RAM

– 9 Interrupt Sourc es with 4 Priority Levels

– Dual Data Pointer

• Variable Length MOVX for Slow RAM/Peripherals

• ISP (In-system Programming) Using Standard V

• Boot ROM Contains Low Level Fla sh Programming Routines and a Default Serial

Loader

• High-speed Archit ecture

– In Standard Mode:

40 MHz (Vcc 2.7V to 5.5V, both Inter nal and ext ernal code execution)

60 MHz (Vcc 4.5V to 5.5V and Internal Code execution only)

– In X2 mode (6 Clocks/machine cycle)

20 MHz (Vcc 2.7V to 5.5V, both Inter nal and ext ernal code execution)

30 MHz (Vcc 4.5V to 5.5V and Internal Code execution only)

– 16K/32K Bytes On-chip Fl ash Program/Data Memory

– Byte and Page (128 Bytes) Erase and W rite

– 100K Write Cycles

• On-chip 1024 Bytes Expanded RAM (XRAM)

– Software Selectable Size (0 , 256, 512, 768, 1024 Bytes)

– 256 Bytes Selected at Reset for TS87C51RB2/RC2 Compatibility

• Keyboard Interrupt Interface on Port P1

• SPI Interface (Ma ster/Slave Mode)

• 8-bit Clock Prescaler

• Improved X2 Mode with Independent Selection for CPU and Each Peripheral

• Programmable Counter Array 5 Channels

– High-speed Output

– Compare/Capture

– Pulse Width Modulator

– Watchdog Timer Capabilities

• Asynchronous Port Reset

• Full Duplex Enhanced UART

• Dedicated Baud Rate Generator for UART

• Low EMI (Inhibit ALE)

• Hardware Watchdog Timer (One-time Enabled with Reset-out)

• Power Control Modes

– Idle Mode

– Power-down Mode

– Power-off Flag

• Power Supply:

– 2.7 to 3.6 (3V Version)

– 2.7 to 5.5V (5V Version)

• T em p erature Ranges: Commercial (0 to +70°C) and Industri al ( -40°C to +85°C)

• Packages: PDIL40, PLCC44, VQFP44

Power Supply

CC

8-bit

Microcontroller

with 16K/

32K Bytes Flash

AT89C51RB2

AT89C51RC2

Description

The AT89C51RB2/RC2 is a high-performance Flash version of the 80C51 8-bit microcontrollers. It contains a 16K or 32K Bytes Flash memory block for program and data.

The Flash mem ory can be programmed e ither i n parallel m ode or in serial mode with

the ISP c apability o r wi th software . Th e prog ramm ing voltage i s int ernally g ene rated

from the standard VCC pin.

Rev. 4180E–8051–10/06

AT89C51RB2/RC2

The AT89C51R B2/RC2 retains all features of the 80C52 with 256 Bytes of internal

RAM, a 9-source 4-level interrupt controller and three timer/counters.

In addition, the AT89C51RB2/RC2 has a Programmable Counter Array, an XRAM of

1024 Bytes, a Hardware Watchdog Timer, a Keyboard Interface, an SPI Interface, a

more versatile serial channel that facilitates multiprocessor communication (EUART)

and a speed improvement mechanism (X2 mode).

The Pinout is the standard 40/44 pins of the C52.

The fully static design reduces system power consumption of the AT89C51RB2/ RC2 by

allowing it to bring the clock frequency down to any value, even DC, without loss of data.

The AT 89C5 1RB 2/RC 2 has 2 soft ware -selec tabl e mo des of redu ced acti vity an d 8 -bit

clock prescaler for further reduction in power consumption. In Idle mode, the CPU is frozen while the peripherals and the interrupt system are still operating. In power-down

mode, the RAM is saved and all other functions are inoperative.

The added features of the AT89C51RB2/RC2 make it more powerful for applications

that need pulse width modulation, high speed I/O and counting capabilities such as

alarms, motor control, corded phones, and smart card readers.

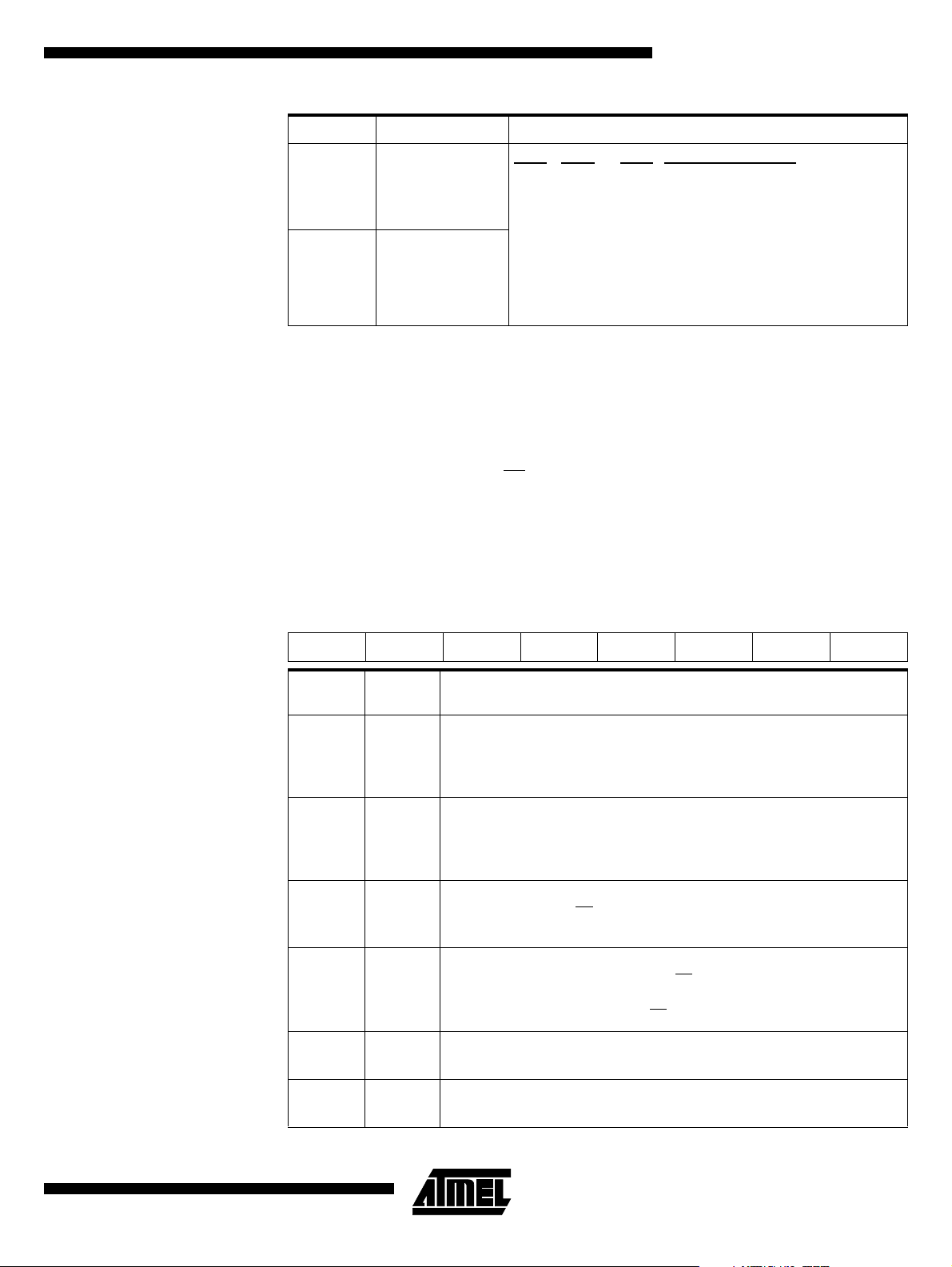

Table 1. Memory Si z e

TOTAL RAM

Part Number Flash (Bytes) XRAM (B ytes)

AT89C51RB2 16K 1024 1280 32

AT89C51RC2 32K 1024 1280 32

AT89C51IC2 32K 1024 1280 32

(Bytes) I/O

2

4180E–8051–10/06

Block Diagram

Figure 1. Block Diagram

AT89C51RB2/RC2

CC

Vss

RxD

TxD

V

PCA

ECI

T2EX

T2

XTAL1

XTAL2

ALE/

PROG

PSEN

EA

(2)

RD

(2)

WR

Notes: 1. Alternate functi on of Por t 1.

2. Alternate function of Port 3.

CPU

RESET

(2)(2)

EUART

BRG

Timer 0

Timer 1

(2) (2) (2) (2)

T0

RAM

+

256x8

C51

CORE

INT

Ctrl

T1

INT0

Flash

32Kx8 or

16Kx8

IB-bus

Parallel I/O Ports & Ext. Bus

Port 0

INT1

Port 1

P0

XRAM

Port 2 Port 3

P1

1Kx8

P2

Boot

ROM

2Kx8

P3

(1)(1)

PCA

Watch

Dog

(1) (1)

Timer2

Key

Board

SPI

(1)(1) (1)

MISO

(1)

SS

MOSI

SCK

4180E–8051–10/06

3

AT89C51RB2/RC2

SFR Mapping The Specia l Function Registers (SFRs) o f the AT89C 51RB2 /RC2 fall into t he follo wing

categories:

• C51 core registers: ACC, B, DPH, DPL, PSW, SP

• I/O port registers: P0, P1, P2, P3

• Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2,

RCAP2L, RCAP2H

• Serial I/O port registers: SADDR, SADEN, SBUF, SCON

• PCA (Programmable Counter Array) registers: CCON, CCAPMx, CL, CH, CCAPxH,

CCAPxL (x: 0 to 4)

• Power and clock control registers: PCON

• Hardware Watchdog Timer registers: WDTRST, WDTPRG

• Interrupt system registers: IEN0, IPL0, IPH0, IEN1, IPL1, IPH1

• Keyb oard Interface registers: KBE, KBF, KBLS

• SPI registers: SPCON, SPST R , SPDAT

• BRG (Baud Rate Generator) registers: BRL, BDRCON

• Flash register: FCON

• Clock Prescaler register: CKRL

• Others: AUXR, AUXR1, CKCON0, CKCON1

4

4180E–8051–10/06

AT89C51RB2/RC2

Table 2. C51 Core SFRs

MnemonicAddName 76543210

ACC E0h Accumulator

B F0h B Register

PSW D0h Program Status Word CY AC F0 RS1 RS0 OV F1 P

SP 81h Stack Pointer

DPL 82h Data Pointer Low Byte

DPH 83h Data Pointer High Byte

Table 3. System Management SFRs

MnemonicAddName 76543210

PCON 87h Power Control SMOD1 SMOD0 - POF GF1 GF0 PD IDL

AUXR 8Eh Auxiliary Register 0 DPU - M0 XRS2 XRS1 XRS0 EXTRAM AO

AUXR1 A2h Auxiliary Register 1 - - ENBOOT - GF3 0 - DPS

CKRL 97h Clock Reload Register CKRL7 CKRL6 CKRL5 CKRL4 CKRL3 CKRL2 CKRL1 CKRL0

CKCKON0 8Fh Clock Control Register 0 - WDTX2 PCAX2 SIX2 T2X2 T1X2 T0X2 X2

CKCKON1AFhClock Control Register 1-------SPIX2

Table 4. Interrupt SFRs

MnemonicAddName 76543210

IEN0 A8h Interrupt Enable Control 0 EA EC ET2 ES ET1 EX1 ET0 EX0

IEN1B1hInterrupt Enable Control 1 -----ESPI EI2C KBD

IPH0 B7h Interrupt Priority Control High 0 - PPCH PT2H PHS PT1H PX1H PT0H PX0H

IPL0 B8h Interrupt Priority Control Low 0 - PPCL PT2L PLS PT1L PX1L PT0L PX0L

IPH1B3hInterrupt Priority Control High 1-----SPIHIE2CHKBDH

IPL1B2hInterrupt Priority Control Low 1-----SPILIE2CLKBDL

Table 5. Port SFRs

MnemonicAddName 76543210

P0 80h 8-bit Port 0

P1 90h 8-bit Port 1

P2 A0h 8-bit Port 2

P3 B0h 8-bit Port 3

4180E–8051–10/06

5

AT89C51RB2/RC2

Table 6. Timer S FR s

MnemonicAddName 76543210

TCON 88h Timer/C o un te r 0 and 1 Co nt rol TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

TMOD 89h Timer/Coun te r 0 and 1 Mo de s GATE1 C/ T1 # M11 M0 1 GATE0 C/T0# M10 M00

TL0 8Ah Timer/Counter 0 Low Byte

TH0 8Ch Timer/Counter 0 High Byte

TL1 8Bh Timer/Counter 1 Low Byte

TH1 8Dh

WDTRST A6h Watchdog Timer Reset

WDTPRGA7hWatchdog Timer Program -----WTO2WTO1WTO0

T2CON C8h Timer/Counter 2 control TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2# CP/RL2#

T2MODC9hTimer/Counter 2 Mode ------T2OEDCEN

RCAP2H CBh

RCAP2L CAh

TH2 CDh Timer/Counter 2 High Byte

TL2 CCh Timer/Counter 2 Low Byte

Timer/Counter 1 High Byte

Tim er/Cou nter 2 Reload /Cap tur e

High Byte

Tim er/Cou nter 2 Reload /Cap tur e

Low Byte

Table 7. PCA SFRs

Mnemonic

CCON D8h PCA Timer/Counter Control CF CR - CCF4 CCF3 CCF2 CCF1 CCF0

CMOD D9h PCA Timer/Counter Mode CIDL WDTE - - - CPS1 CPS0 ECF

CL E9h PCA Timer/Counter Low Byte

AddName 76543210

CH F9h PCA Timer/Counter High Byte

CCAPM0

CCAPM1

CCAPM2

CCAPM3

CCAPM4

CCAP0H

CCAP1H

CCAP2H

CCAP3H

CCAP4H

CCAP0L

CCAP1L

CCAP2L

CCAP3L

CCAP4L

DAh

PCA Timer/Counter Mode 0

DBh

PCA Timer/Counter Mode 1

DCh

PCA Timer/Counter Mode 2

DDh

PCA Timer/Counter Mode 3

DEh

PCA Timer/Counter Mode 4

FAh

PCA Compare Ca pture Module 0 H

FBh

PCA Compare Ca pture Module 1 H

FCh

PCA Compare Ca pture Module 2 H

FDh

PCA Compare Ca pture Module 3 H

FEh

PCA Compare Ca pture Module 4 H

EAh

PCA Compare Capture Module 0 L

EBh

PCA Compare Capture Module 1 L

ECh

PCA Compare Capture Module 2 L

EDh

PCA Compare Capture Module 3 L

EEh

PCA Compare Capture Module 4 L

6

-

CCAP0H7

CCAP1H7

CCAP2H7

CCAP3H7

CCAP4H7

CCAP0L7

CCAP1L7

CCAP2L7

CCAP3L7

CCAP4L7

ECOM0

ECOM1

ECOM2

ECOM3

ECOM4

CCAP0H6

CCAP1H6

CCAP2H6

CCAP3H6

CCAP4H6

CCAP0L6

CCAP1L6

CCAP2L6

CCAP3L6

CCAP4L6

CAPP0

CAPP1

CAPP2

CAPP3

CAPP4

CCAP0H5

CCAP1H5

CCAP2H5

CCAP3H5

CCAP4H5

CCAP0L5

CCAP1L5

CCAP2L5

CCAP3L5

CCAP4L5

CAPN0

CAPN1

CAPN2

CAPN3

CAPN4

CCAP0H4

CCAP1H4

CCAP2H4

CCAP3H4

CCAP4H4

CCAP0L4

CCAP1L4

CCAP2L4

CCAP3L4

CCAP4L4

MAT0

MAT1

MAT2

MAT3

MAT4

CCAP0H3

CCAP1H3

CCAP2H3

CCAP3H3

CCAP4H3

CCAP0L3

CCAP1L3

CCAP2L3

CCAP3L3

CCAP4L3

TOG0

TOG1

TOG2

TOG3

TOG4

CCAP0H2

CCAP1H2

CCAP2H2

CCAP3H2

CCAP4H2

CCAP0L2

CCAP1L2

CCAP2L2

CCAP3L2

CCAP4L2

PWM0

PWM1

PWM2

PWM3

PWM4

CCAP0H1

CCAP1H1

CCAP2H1

CCAP3H1

CCAP4H1

CCAP0L1

CCAP1L1

CCAP2L1

CCAP3L1

CCAP4L1

4180E–8051–10/06

ECCF0

ECCF1

ECCF2

ECCF3

ECCF4

CCAP0H0

CCAP1H0

CCAP2H0

CCAP3H0

CCAP4H0

CCAP0L0

CCAP1L0

CCAP2L0

CCAP3L0

CCAP4L0

AT89C51RB2/RC2

Table 8. Serial I/O Port SFRs

MnemonicAddName 76543210

SCON 98h Serial Control FE/SM0 SM1 SM2 REN TB8 RB8 TI RI

SBUF 99h Serial Data Buffer

SADEN B9h Slave Address Mask

SADDR A9h Slave Address

BDRCON 9Bh Baud Rate Control BRR TBCK RBCK SPD SRC

BRL 9Ah Baud Rate Reload

Table 9. SPI Controller SFRs

MnemonicAddName 76543210

SPCON C3h SPI Control SPR2 SPEN SSDIS MSTR CPOL CPHA SPR1 SPR0

SPSTA C4h SPI Status SPIF WCOL SSERR MODF ---SPDAT C5h SPI Data SPD7 SPD6 SPD5 SPD4 SPD3 SPD2 SPD1 SPD0

Table 10. Keyboard Interface SFRs

MnemonicAddName 76543210

KBLS 9Ch Keyboard Level Selector KBLS7 KBLS6 KBLS5 KBLS4 KBLS3 KBLS2 KBLS1 KBLS0

KBE 9Dh Keyboard Input Enable KBE7 KBE6 KBE5 KBE4 KBE3 KBE2 KBE1 KBE0

KBF 9Eh Keyboard Flag Register KBF7 KBF6 KBF5 KBF4 KBF3 KBF2 KBF1 KBF0

4180E–8051–10/06

7

AT89C51RB2/RC2

Table 11 shows all SFRs with their address and their reset value.

Ta ble 11 . S FR Mapping

Bit

addressable Non Bit addressable

0/8 1/9 2/A 3/B 4/C 5/D 6/E 7/F

F8h

CH

0000 0000

CCAP0H

XXXX

CCAP1H

XXXX

CCAPL2H

XXXX

CCAPL3H

XXXX

CCAPL4H

XXXX

FFh

F0h

E8h

E0h

D8h

D0h

C8h

C0h

B8h

B0h

A8h

A0h

98h

90h

88h

80h

1. FCON access is reserved for the Flash A PI and ISP software.

B

0000 0000

CL

0000 0000

ACC

0000 0000

CCON

00X0 0000

PSW

0000 0000

T2CON

0000 0000

IPL0

X000 000

P3

1111 1111

IEN0

0000 0000

P2

1111 1111

SCON

0000 0000

P1

1111 1111

TCON

0000 0000

P0

1111 1111

0/8 1/9 2/A 3/B 4/C 5/D 6/E 7/F

CMOD

00XX X000

(1)

FCON

XXXX 0000

T2MOD

XXXX XX00

SADEN

0000 0000

IEN1

XXXXX 000

SADDR

0000 0000

SBUF

XXXX XXXX

TMOD

0000 0000

SP

0000 0111

CCAP0L

XXXX XXXX

CCAPM0

X000 0000

RCAP2L

0000 0000

IPL1

XXXXX000

AUXR1

XXXXX0X0

BRL

0000 0000

TL0

0000 0000

DPL

0000 0000

CCAP1L

XXXX XXXX

CCAPM1

X000 0000

RCAP2H

0000 0000

SPCON

0001 0100

IPH1

XXXX X000

BDRCON

XXX0 0000

TL1

0000 0000

DPH

0000 0000

CCAPL2L

XXXX XXXX

CCAPM2

X000 0000

TL2

0000 0000

SPSTA

0000 0000

KBLS

0000 0000

TH0

0000 0000

CCAPL3L

XXXX XXXX

CCAPM3

X000 0000

TH2

0000 0000

SPDAT

XXXX XXXX

KBE

0000 0000

TH1

0000 0000

CCAPL4L

XXXX XXXX

CCAPM4

X000 0000

WDTRST

XXXX XXXX

KBF

0000 0000

AUXR

XX0X 0000

IPH0

X000 0000

CKCON1

XXXX XXX0

WDTPRG

XXXX X000

CKRL

1111 1111

CKCON0

0000 0000

PCON

00X1 0000

F7h

EFh

E7h

DFh

D7h

CFh

C7h

BFh

B7h

AFh

A7h

9Fh

97h

8Fh

87h

Reserved

8

4180E–8051–10/06

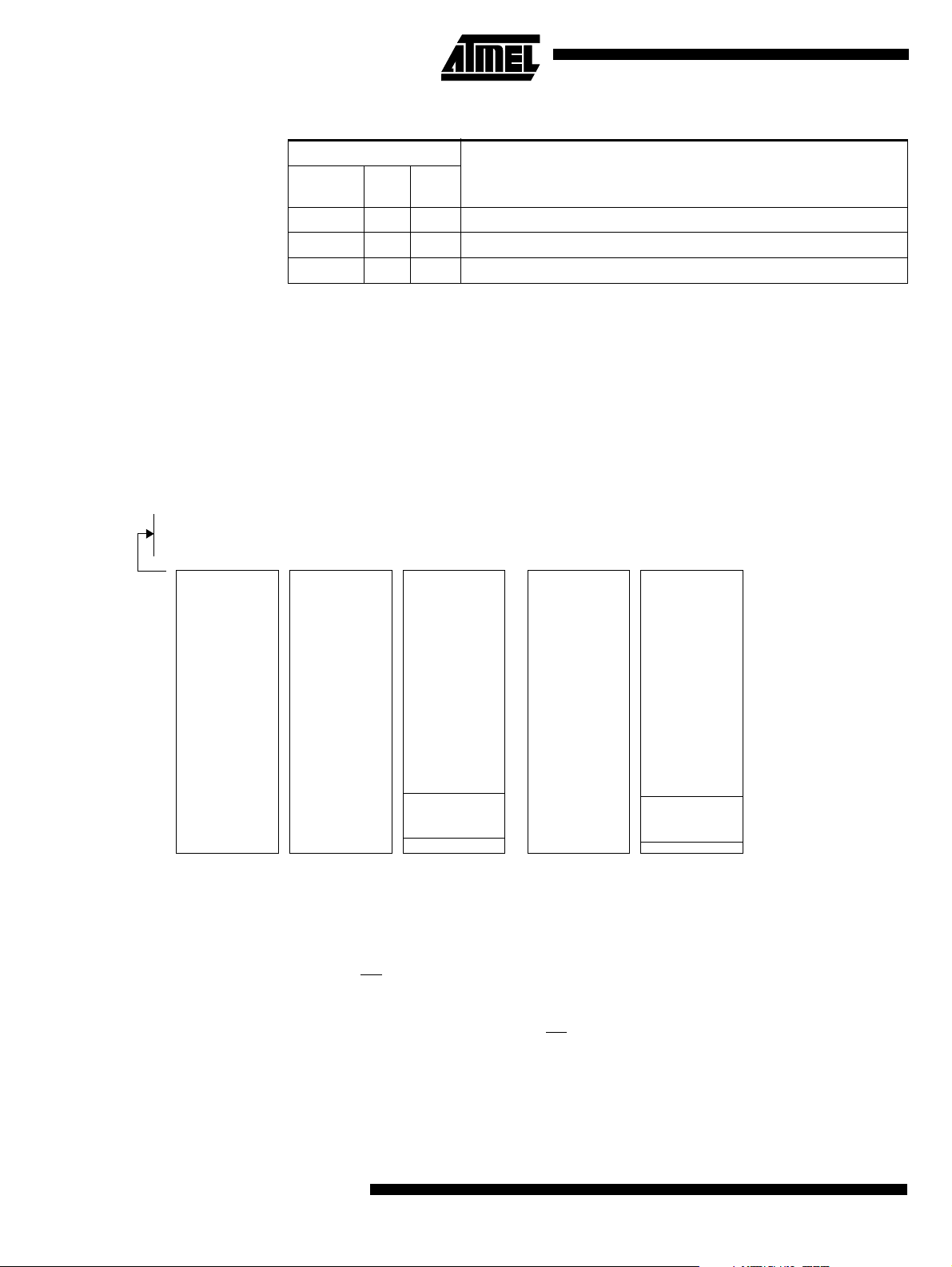

Pin Conf igurations

Figure 2. Pin Configurations

AT89C51RB2/RC2

P1.0/T2

P1.1/T2EX/SS

P1.2/ECI

P1.3CEX0

P1.4/CEX1

P1.5/CEX2/MISO

P1.6/CEX3/SCK

P1.7CEX4/MOSI

RST

P3.0/RxD

P3.1/TxD

P3.2/INT0

P3.3/INT1

P3.4/T0

P3.5/T1

P3.6/WR

P3.7/RD

XTAL2

XTAL1

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

PDIL40

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

VCC

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

EA

ALE/PROG

PSEN

P2.7/A15

.6/A14

P2

P2

.5/A13

12

P2.4/A

11

P2.3/A

P2.2/A

10

9

P2.1/A

P2.0/A8

P1.5/CEX2/MISO

P1.6/CEX3/SCK

P1.7/CEx4/MOSI

RST

P3.0/RxD

NIC*

P3.1/TxD

P3.2/INT0

P3.3/INT1

P3.4/T0

P3.5/T1

P1.4/CEX1

P1.3/CEX0

5 4 3 2 1 6 44 43 42 41 40

7

8

9

10

11

12

13

14

15

16

17

P1.1/T2EX/SS

P1.2/ECI

P1.0/T2

NIC*

VCC

PLCC44

P0.0/AD0

18 19 23222120 262524 27 28

NIC*

VSS

XTAL2

XTAL1

P3.7/RD

P3.6/WR

P2.0/A8

P2.1/A9

P0.1/AD1

P2.2/A10

P0.2/AD2

P2.3/A11

P0.3/AD3

39

38

37

36

35

34

33

32

31

30

29

P2.4/A12

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

EA

NIC*

ALE/PROG

PSEN

P2.7/A15

P2.6/A14

P2.5/A13

*NIC: No Internal Connection

4180E–8051–10/06

P1.5/CEX2/MISO

P1.6/CEX3/SCK

P1.7/CEX4/MOSI

RST

P3.0/RxD

NIC*

P3.1/TxD

P3.2/INT0

P3.3/INT1

P3.4/T0

P3.5/T1

1

2

3

4

5

6

7

8

9

10

11

P1.4/CEX1

P1.3/CEX0

43 42 41 40 3944

P1.0/T2

P1.1/T2EX/SS

P1.2/ECI

NIC*

VCC

38 37 36 35 34

VQFP44 1.4

P0.0/AD0

1213 17161514 201918 2122

VSS

NIC*

XTAL1

P3.6/WR

P3.7/RD

XTAL2

P2.0/A8

P0.2/AD2

P0.3/AD3

P0.1/AD1

P0.4/AD4

33

32

P0.5/AD5

31

P0.6/AD6

30

P0.7/AD7

29

EA

28

NIC*

27

ALE/PROG

26

PSEN

25

P2.7/A15

24

P2.6/A14

23

P2.5/A13

P2.1/A9

P2.3/A11

P2.2/A10

P2.4/A12

9

AT89C51RB2/RC2

Table 12. Pin Description for 40 - 44 Pin Packages

Pin Number

Mnemonic

V

SS

V

CC

P0.0 - P0.7 39 - 32 43 - 36 37 - 30 I/O Port 0: Port 0 is an open-drain, bi-directional I/O port. Port 0 pins that have 1s

P1.0 - P1.7 1 - 8 2 - 9 40 - 44

20 22 16 I Ground: 0V reference

40 44 38 I

1 - 3

1 2 40 I/O P1.0: Input/Output

2 3 41 I/O P1.1: Input/Output

Type Name and FunctionDIL LCC VQFP44 1.4

Power Supply: This is the power supply voltage for normal, idle and power-down

operation

written to them float and ca n be used as high impedance inputs. Port 0 must be

polarize d t o V

is also the multiplexed low-order address and data bus during access to external

program and data memory. In this application, it uses strong internal pull-up when

emitting 1s. Port 0 also inputs the code Bytes during Flash programming. External

pull-ups are required dur ing prog ram verification during whi c h P0 outputs the code

Bytes.

I/O Po rt 1 : Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. Port 1 pins that

have 1s written to them are pulled high by the internal pull-ups and can be used as

inputs. As inputs, Port 1 pins that are externally pulled low will source current

because of the internal pull-ups. Port 1 also receives the low-order address Byte

during memory programming and verification.

Alternate functi on s for AT89C51RB2 /RC2 Port 1 include:

I/O T2 (P1.0): Timer/Counter 2 external count input/Clockout

I T2EX: Timer/Counter 2 Reload/Capture/Direction Control

or VSS in order to prevent any parasitic current consumption. Port 0

CC

I SS

3 4 42 I/O P1.2: Input/Output

I ECI: External Clock for th e PCA

4 5 43 I/O P1.3: Input/Output

I/O CEX0: Capture/Compare External I/O for PCA Module 0

5 6 44 I/O P1.4: Input/Output

I/O CEX1: Capture/Compare External I/O for PCA Module 1

6 7 1 I/O P1.5: Input/Output

I/O CEX2: Capture/Compare External I/O for PCA Module 2

I/O MISO: SPI Master Input Slave Output line

7 8 2 I/O P1.6: Input/Output

I/O CEX3: Capture/Compare External I/O for PCA Module 3

I/O SCK: SPI Serial Clock

8 9 3 I/O P1.7: Input/Output:

: SPI Slave Select

When SPI is in master mode, MISO receives data from the slave peripheral. When

SPI is in slave mode, MISO outputs data to the master controller.

SCK outputs clock to the slave periphe ral

10

4180E–8051–10/06

Table 12. Pin Description for 40 - 44 Pin Packages (Continued)

Pin Number

AT89C51RB2/RC2

Mnemonic

P1.0 - P1.7 I/O MOSI: SPI Master Output Slave Input line

XTAL1 19 21 15 I

XTAL2 18 20 14 O Cry stal 2: Output from the inverting oscillator amplifier

P2.0 - P2.7 21 - 28 24 - 31 18 - 25 I/O Port 2 : Port 2 is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins that

P3.0 - P3.7 10 - 17 11,

13 - 19

5,

7 - 13

Type Name and FunctionDIL LCC VQFP44 1.4

I/O CEX4: Capture/Compare External I/O for PCA Module 4

When SPI is in master mode, MOSI outputs data to the slave peri pheral. When SPI

is in sla v e mode, MOSI receives data fr om the maste r controller.

Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock

generator circuits.

have 1s written to them are pulled high by the internal pull-ups and can be used as

inputs. As inputs, Port 2 pins that are externally pulled low will source current

because of the internal pull-ups. Port 2 emits the high - order address Byte during

fetches from exter nal program memory and during accesses to external data

memory that use 16-bit addresses (MOV X @D PTR). In this application, it uses

strong internal pull-ups emitting 1s. During accesses to external data memory that

use 8-bit addresses (MOVX @Ri ), port 2 emits the contents of the P2 SFR. Some

Port 2 pi ns receive the high order addr ess bits during EP ROM programming and

verification:

P2.0 to P2.5 for 16 KB devices

P2.0 to P2.6 for 32KB devices

I/O Po rt 3: Port 3 is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins that

have 1s written to them are pulled high by the internal pull-ups and can be used as

inputs. As inputs, Port 3 pins that are externally pulled low will source current

because of the internal pull-ups. Port 3 also serves the special features of the

80C51 family, as li sted below.

10 11 5 I RXD (P3.0): Serial in pu t por t

11 13 7 O TXD (P3.1): Serial output port

12 14 8 I INT0

13 15 9 I INT1

14 16 10 I T 0 (P3.4): Timer 0 external input

15 17 11 I T 1 (P3.5): Timer 1 external input

16 18 12 O WR

17 19 13 O RD

RST 9 10 4 I/O

ALE/PROG

30 33 27 O (I) Address Latch Enable/Progr am Pulse: Output pulse for latchin g th e low Byt e of

(P3.2): Ex te rna l interrupt 0

(P3.3): Ex te rna l interrupt 1

(P3.6): External data memory write strobe

(P3.7): External data memory read strobe

Reset: A high on this pin for two machine cycles while the oscillator is running,

resets the device. An internal diffused resistor to V

only an external capacitor to V

watchdog forces a system reset.

the address during an access to external memory. In normal operation, ALE is

emitted at a constant rate of 1/6 (1/3 in X2 mode) the oscillator frequency, and can

be used for external timing or clocking. Note that one ALE pulse is skipped during

each access to external data memory. This pin is also the program pulse input

(PROG

) duri ng Flas h p rogr a mming . ALE can be di sa bl ed by s ett in g SF R’ s AU XR. 0

bit. With this bit set, ALE will be inactive during internal fetches.

. This pin is an output when the hardware

CC

permits a power-on reset using

SS

4180E–8051–10/06

11

AT89C51RB2/RC2

Table 12. Pin Description for 40 - 44 Pin Packages (Continued)

Pin Number

Mnemonic

PSEN 29 32 26 O Program Strobe Enable: The read strobe to external program memory. When

EA 31 35 29 I External Access Enable: EA

Type Name and FunctionDIL LCC VQFP44 1.4

executing code from the external program memory, PSEN

machine cycle, except that two PSEN

external data memory. PSEN

memory.

fetch code from external program memory locations 0000H to FFFFH (RD). If

security level 1 is programmed, EA

activ atio ns are sk ip pe d d uri ng ea ch ac ces s t o

is not activated during fetches from internal program

must be externally held low to enable the device to

will be internally latched on Reset.

is activa te d t wic e each

12

4180E–8051–10/06

AT89C51RB2/RC2

Port Types AT89C51RB2 /RC2 I/O ports (P1, P2, P3) imp lement the quasi-bid irectional o utput that

is com mon on the 8 0C 51 and mos t of its d eriva tive s. This o utp ut ty pe ca n b e used as

both an i nput and ou tput w ithout the need to rec onfigure the port. This is p ossible

because when the port outputs a logic high, it is weakly driven, allowing an external

device to pull the pin low. When the pin is pulled low, it is dri ven strongly and able to sink

a fairly large current. These features are somew hat similar to an open drain output

except that there are three pull-up transistors in the quasi-bidirectional output that serve

different purposes. One of these pul l-ups, called the "weak " pull-up, is turned on whenever the port latch for the pin contains a logic 1. The weak pull-up sources a very small

current that will pull the pin high if it is left floating. A second pull-up, called the "medium"

pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is

also at a logic 1 level. This pull-up provides the primary s ource current for a quas i-bidirectional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an

external device, the medi um pull-up turn s off, and only the we ak pull-up remains on . In

order to pull the pin low under these conditions, the external device has to sink enough

current to overpow er the me dium pull -up and take the voltage on the port pi n below its

input threshold.

The third pull-up is referred to as the "strong" pull-up. This pull-up is used to speed up

low-to-high transitions on a quasi-bidirectional port pin when the port latch changes from

a logic 0 to a logic 1. When this occurs, the strong pu ll-up turns on for a brief time, two

CPU clocks, in order to pull the port pin high quickly. Then it turns off again.

The DPU bit (bit 7 in AUXR register) allows to disable the perman ent we ak pull up of all

ports when latch data is logical 0.

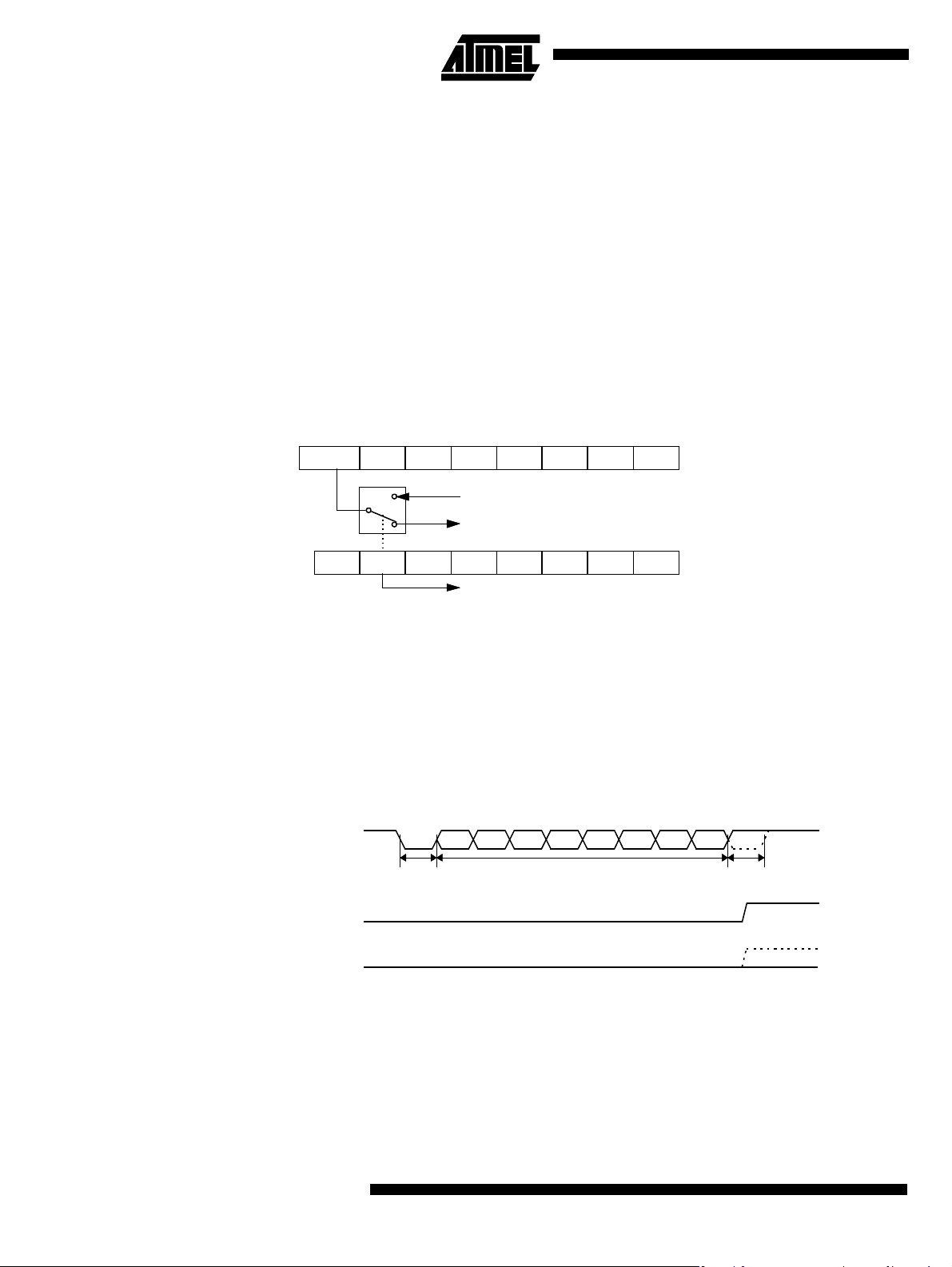

The quasi-bidirectional port configuration is shown in Figure 3.

Figure 3. Quasi-Bidire ction al Output

Port Latch

Data

2 CPU

Clock Delay

Input

Data

P

N

Strong

PP

Weak

DPU

AUXR.7

Medium

Pin

4180E–8051–10/06

13

AT89C51RB2/RC2

Oscillator To optim ize t he p ower c onsu mpti on an d e xecu tion ti me n eede d fo r a sp ecific task, an

internal, prescaler feature has been implemented between the oscillator and the CPU

and peripherals.

Registers Table 13. CKRL Register

CKRL – Clock Reload Register (97h)

76543210

CKRL7 CKRL6 CKRL5 CKRL4 CKRL3 CKRL2 CKRL1 CKRL0

Bit Number Mnemonic Description

7:0 CKRL

Clock Reload Register

Prescaler value

Reset Value = 1111 1111b

Not bit addressable

Table 14. PCON Register

PCON – Power Control Register (87h)

76543210

SMOD1 SMOD0 - POF GF1 GF0 PD IDL

Bit Number Bit Mnemonic Description

7SMOD1

6SMOD0

5-

4POF

Serial Port Mode bit 1

Set to select double baud rate in mode 1, 2 or 3.

Serial Port Mode bit 0

Clear ed to sel ec t SM0 bi t in SC ON r e gist er.

Set to select FE bit in SCON register.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Power-off Flag

Cleared to recognize next reset type.

Set by har dwa re wh en V

also be set by software.

rises fr om 0 to it s nomi na l volt a ge . Can

CC

14

General-pu r pos e Flag

3GF1

2GF0

1PD

0IDL

Cleared by software for general-purpose usage.

Set by software for gene r al -pu rpos e usa ge .

General-pu r pos e Flag

Cleared by software for general-purpose usage.

Set by software for gene r al -pu rpos e usa ge .

Power-down Mode bit

Cleared by hardware when reset occurs.

Set to enter power-down mode.

Idle Mode bit

Cleared by hardware when interrupt or reset occurs.

Set to enter idle mode.

Reset Value = 00X1 0000b Not bit addressable

4180E–8051–10/06

Funct ional Block

F

F

---

F

F

---

Diagram

Figure 4. Functional Oscillator Block Diagram

AT89C51RB2/RC2

Reload

8-bit

Prescaler-Divider

1

0

CKRL = 0xFF?

CLK

PERIPH

CLK

CPU

Idle

Xtal1

Xtal2

Osc

Reset

CKRL

F

OSC

1

:2

0

X2

CKCON0

Prescaler Divider • A hardware RESET puts the prescaler divider in the following state:

•CKRL = FFh: F

CLK CPU

= F

CLK PERIPH

= F

/2 (Standard C51 feature)

OSC

• Any value between F Fh down to 00h can be written by software into CKRL register

in order to divide frequency of the selected osc illator:

• CKRL = 00h: minimum frequency

F

CLK CPU

F

CLK CPU

= F

CLK PERIPH

= F

CLK PERIPH

= F

= F

/1020 (Standard Mode)

OSC

/510 (X2 Mode)

OSC

• CKRL = FFh: maximum frequenc y

F

CLK CPU

F

CLK CPU

F

CLK CPU

and F

= F

CLK PERIPH

= F

CLK PERIPH

CLK PERIPH

= F

= F

/2 (Standard Mode)

OSC

(X2 Mode)

OSC

Peripheral Clock

CPU clock

4180E–8051–10/06

In X2 Mode, for CKRL<>0xFF:

CPU

F=

CLKPERIPH

=

-------------------------------------------2 255 CKRL

OSC

–

()×

In X1 Mode, for CKRL<>0xFF then:

CPU

F=

CLKPERIPH

=

-------------------------------------------4 255 CKRL

OSC

–

()×

15

AT89C51RB2/RC2

Enhanced Features In comp arison to the original 80C52, the AT89C51RB 2/RC2 im plement s some new fea-

tures, which are

• X2 option

• Dual Data Pointer

• Extended RAM

• Programmable Counter Array (PCA)

• Hardware Watchdog

• SPI interface

• 4-level interrupt priority system

• power-off flag

• ONCE mode

• AL E disabling

• Some enha nc ed features are also located in the UART and the timer 2

X2 Feature The AT89C51RB2/RC2 core needs only 6 clock periods per machine cycle. This feature

called ‘X2’ provides the following advantages:

• Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

• Save power consumption while keeping same CPU power (oscillator power saving).

• Sa ve power consum ption by dividing dynam ical ly the operating frequency by 2 in

operating and idle modes.

• Increase CPU power by 2 while keeping same crystal frequency.

:

In order to keep the original C51 compatibility, a divider by 2 is inserted between the

XTAL1 signal and the main clock input of the core (phase generator). This divider m ay

be disabled by software.

Description The clock for the w hole ci rcuit a nd peri pherals i s first divi ded by 2 before being used by

the CPU core and the peripherals.

This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is

bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%.

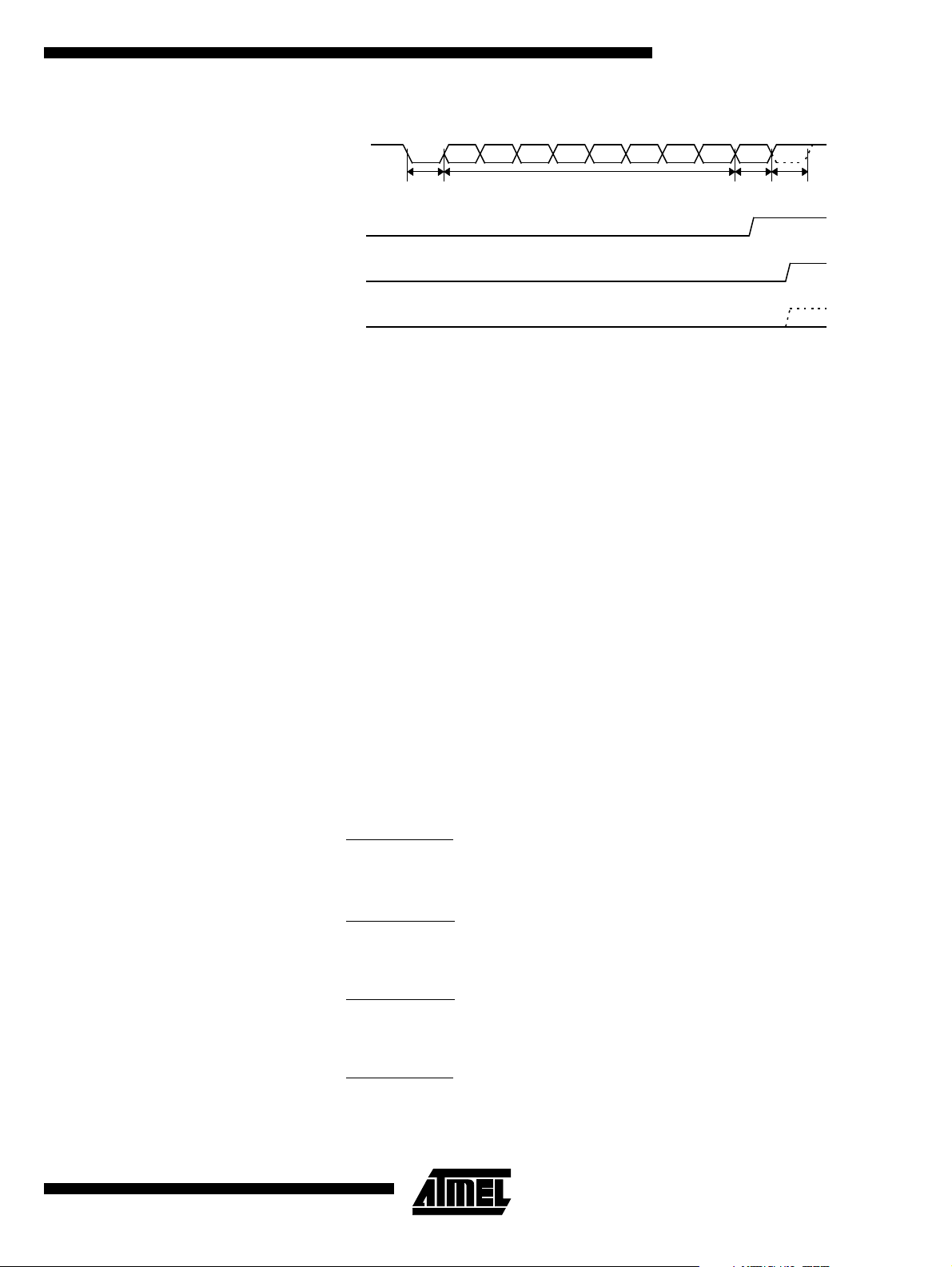

Figure 5 shows the clock generation block diagram. X2 bit is validated on the rising edge

of the XTAL1÷2 to avoid g litches whe n swi tching f rom X2 t o X1 mod e. Figure 6 show s

the switching mode waveforms.

Figure 5. Clock Generation Diagram

CKRL

F

X2

OSC

0

1

8 bit Pre scaler

F

CLK CPU

F

CLK PER IP H

XTAL1

FXTAL

XTAL1:2

2

CKCON0

16

4180E–8051–10/06

Figure 6. Mode Switching Waveforms

XTAL1

XTAL1:2

X2 Bit

CPU Clock

The X2 bit in the CKCON0 register (see Table 15) allows a switch from 12 clock periods

per instruction to 6 clo ck periods and vice versa. At reset , t he speed is set according to

X2 bit of Hardware Security Byte (HSB). By default, Standard mode is active. Setting the

X2 bit activates the X2 feature (X2 mode).

The T0X2, T1X2, T2X2, UARTX2, PCAX2, and WDX 2 bits in the CKCON0 register

(Table 15) and SPIX2 bit in the CKCON1 register (see Table 16) allow a switch from

standard peri phera l spee d ( 12 clo ck p eriod s per p eriph eral clock cyc le) to fa st pe ripheral speed (6 clock periods per peripheral clock cycle). These bits are active only in X2

mode.

AT89C51RB2/RC2

F

OSC

X2 Modex1 Mode X1 Mode

4180E–8051–10/06

17

AT89C51RB2/RC2

Table 15. CKCON0 Register

CKCON0 - Clock Control Register (8Fh)

76543210

- WDX2 PCAX2 SIX2 T2X2 T1X2 T0X2 X2

Bit

Number

7 Reserved

6WDX2

5PCAX2

4SIX2

3T2X2

Bit

Mnemonic Description

Watchdog Clock

(This con tr ol bi t is va li da ted when t he CP U cl ock X2 i s s et ; whe n X2 is lo w, this bit

has no effect).

Cleared to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Programmable Counter Array Clock

(This con tr ol bi t is va li da ted when t he CP U cl ock X2 i s s et ; whe n X2 is lo w, this bit

has no effect).

Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock

periods per peri pheral c lock cycle.

Enhanced UART Clock (Mode 0 and 2)

(This con tr ol bi t is va li da ted when t he CP U cl ock X2 i s s et ; whe n X2 is lo w, this bit

has no effect).

Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock

periods per peri pheral c lock cycle.

Timer 2 Clock

(This con tr ol bi t is va li da ted when t he CP U cl ock X2 i s s et ; whe n X2 is lo w, this bit

has no effect).

Cleared to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Timer 1 Clock

2T1X2

1T0X2

0X2

(This con tr ol bi t is va li da ted when t he CP U cl ock X2 i s s et ; whe n X2 is lo w, this bit

has no effect).

Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock

periods per peri pheral c lock cycle.

Timer0 Clock

(This con tr ol bi t is va li da ted when t he CP U cl ock X2 i s s et ; whe n X2 is lo w, this bit

has no effect).

Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock

periods per peri pheral c lock cycle.

CPU Clock

Cleared to select 12 clock periods per machine cycle (STD, X1 mode) for CPU

and all the peripherals. Set to select 6 clock periods per machine cycle (X2

mode) and to enable the individual peripherals’X2’ bits. Program m ed by

hardware after Power-up regarding Hardware Security Byte (HSB), Default

setting, X2 is cleared.

Reset Value = 0000 000’HSB. X2’b (see Table 65 “Hardware Security Byte”)

Not bit addressable

18

4180E–8051–10/06

AT89C51RB2/RC2

Table 16. CKCON1 Register

CKCON1 - Clock Control Register (AFh)

76543210

-------SPIX2

Bit

Number

7-Reserved

6-Reserved

5-Reserved

4-Reserved

3-Reserved

2-Reserved

1-Reserved

0SPIX2

Bit

Mnemonic Description

SPI (This control bit is validated when the CPU clock X2 is set; when X2 is low,

this bit has no effect).

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Reset Value = XXXX XXX0b

Not bit addressable

4180E–8051–10/06

19

AT89C51RB2/RC2

Dual Data Pointer

External Data Memory

Register (DPTR)

Figure 7. Use of Dual Pointer

AUXR1(A2H)

The addi tion al da ta poin ter ca n be u sed t o spe ed up code exe cuti on and reduc e cod e

size.

The dual D PT R st ru c tur e is a way by w h ic h the c hip will s p e c if y the address of an exter nal data memory location. There are two 16-bit DPTR registers that address the external

memory, and a single bit called DPS = AUXR1.0 (see Table 17) that allows the program

code to switch between them (see Figure 7).

07

DPS

DPTR1

DPTR0

DPH(83H) DPL(82H)

20

4180E–8051–10/06

AT89C51RB2/RC2

Table 17. AUXR1 register

AUXR1- Auxiliary Register 1(0A2h)

76543210

- - ENBOOT - GF3 0 - DPS

Bit

Number

7-

6-

5 ENBOOT

4-

3GF3This bit is a general-purpose user flag.

20Al ways Cleared

1-

0DPS

Bit

Mnemonic Description

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Enable Boot Flash

Cleare d to disa ble bo ot ROM.

Set to map the boot ROM between F800h - 0FFFFh.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

(1)

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Data Pointer Selection

Cleared to select DPTR0.

Set to select DPTR1.

Reset Value = XXXX XX0X0b

Not bit addressable

Note: 1. Bit 2 stuck at 0; this allows using INC AUXR1 to toggle DPS without chan ging GF3.

4180E–8051–10/06

ASSEMBLY LANGUAGE

; Block move using dual data pointe rs

; Modifies DPTR0, DPTR1, A and PSW

; note: DPS exits opposite of entry s tate

; unles s an extra INC AUXR1 is added

;

00A2 AUXR1 EQU 0A2H

;

0000 909000MOV DPTR,#SOURCE ; address of SOURCE

0003 05 A2 INC AUXR1 ; sw itch dat a pointe rs

0005 90 A000 MOV DPTR,#DEST ; address of DEST

0008 LOOP:

0008 05 A2 INC AUXR1 ; sw itch dat a pointe rs

000A E0 MOVX A,@DPTR ; get a Byte from SOURCE

000B A3 INC DPTR ; increment SOURCE address

000C 05A2 INC AUXR1 ; switch data pointers

000E F0 MOVX @DPTR,A ; write the Byte to DEST

000F A3 INC DPTR ; increment DEST address

0010 70 F6JNZ LOOP ; check for 0 t erminator

0012 05A2 INC AUXR1 ; (optional) restore DP S

21

AT89C51RB2/RC2

INC is a short (2 Bytes) a nd fast (12 clocks) way to manipulate the DPS bit in the

AUXR1 SFR. However, note t hat the I NC i nstruction does not directly force the DPS bit

to a particular state, but simply toggles it. In simple routines, such as the block move

example, only the fact that DPS is toggled in the proper sequence matters, not its actual

value. In other words, the block move routine works the same whether DPS is '0' or '1'

on entry. Observe that without the last instruction (INC AUXR 1), the routine will ex it with

DPS in the opposite state.

22

4180E–8051–10/06

AT89C51RB2/RC2

Expanded RAM (XRAM)

The AT89C51RB2/RC2 provides additional bytes of random access memory (RAM)

space for increased data parameter handling and high-level language usage.

AT89C51RB2/RC2 devices have expanded RAM in external data space; maximu m size

and location are described in Table 18.

Table 18. Expanded RAM

Address

Part Number XRAM Size

AT89C51RB2/RC2 1024 00h 3FFh

Start End

The AT89C51RB2/RC2 has internal data memory that is mapped into four separate

segments.

The four segments are:

1. The Lower 128 Bytes of RAM (addresses 00h to 7Fh) are directly and indirectly

addressable.

2. The Upper 128 Bytes of RAM (addresses 80h to FFh) are indirectly addressable

only.

3. The Special Function Registers, SFRs, (addresses 80h to FFh) are directly

addressable only.

4. The expanded RAM Bytes are indirectly accessed by MOVX instructions, and

with the EXTRAM bit cleared in the AUXR register (see Table 18).

The lower 128 Bytes can be accessed by either direct or indirect addressing. The Upper

128 Bytes can be accessed by indirect addressing only. The Upper 128 Bytes occupy

the same address sp ace as the S FR. Th at means they have the same addres s, but are

physically separate from SFR space.

Figure 8. Internal and External Data Memory Address

0FFh or 3FFh

XRAM

00

0FFh

128 Bytes

Indirect Accesses

80h 80h

7Fh

128 Bytes

Direct or Indirect

00

Accesses

When an instruction ac cesses an i nternal location ab ove addres s 7Fh, the CPU knows

whether the access is to the upper 128 Byte s of data RAM or to SFR space by the

addressing mode used in the instruction.

• Instructions that use direct addressing access SFR space. For example:

MOV 0A0H, # data, accesses the SFR at location 0A0h (which is P2).

Upper

Internal

RAM

Lower

Internal

RAM

0FFh

Special

Function

Register

Direct Accesses

00FFh up to 03FFh

0FFFFh

0000

External

Data

Memory

4180E–8051–10/06

23

AT89C51RB2/RC2

• Instruc tions that use indirect addressing access the Upper 128 Bytes of data RAM.

For example: MOV @R0, # data where R0 contains 0A0h, accesses the data Byte

at address 0A0h, rather than P2 (whose address is 0A0h).

• The XRAM Bytes can be accessed by indirect addressing, with EXTRAM bit cleared

and MOVX instructions. This part of memory that is physically located on-chip,

logically occupies the first Bytes of external data memory. The bits XRS0 and XRS1

are used to hide a part of the available XRAM as explained in Table 18. This can be

useful if external peripherals are mapped at addresses already used by the internal

XRAM.

• With EXTRAM = 0,

combination with any of the registers R0, R1 of the selected bank or DPTR. An

access to XRAM will not af fect ports P0, P2, P3 .6 (WR) and P3.7 ( R D) . For

example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H,

accesses the XRAM at address 0A0H rather than external memory. An access to

external data memory locations higher than the accessible size of the XRAM will be

performed with the MOVX DPTR instructions in the same way as in the standard

80C51, with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and

read timing signals. Accesses to XRAM above 0FFH can only be done by the use of

DPTR.

• With EXTRAM = 1

80C51. MOVX @ Ri will provide an eight-bit address multiplexed with data on Port0

and any output port pins can be used to output higher order address bits. This is to

provide the external pag ing c apa b ili ty. MOVX @ D PTR w ill ge nerate a sixteen-bit

address. Port2 outputs the high-order eight address bits (the contents of DPH) while

Port0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ RI and

MOVX @DPTR will generate either read or write signals on P3.6 (WR

(RD

).

the XRAM is indirectly addressed, using the MOVX instruction in

, MOVX @RI and MOVX @DPTR will be similar to the standard

) and P3.7

The stack pointer (SP) may be located anywhere in the 256 Bytes RAM (lower and

upper RAM) internal data memory. The stack may not be located in the XRAM.

The M0 bit allows to stretc h the XRAM tim ings; if M0 is set, the r ead and wr ite pulses

are extended from 6 to 30 clock periods. This is useful to access externa l slow

peripherals.

24

4180E–8051–10/06

Registers Table 19. AUXR Register

AUXR - Auxiliary Register (8Eh)

76543210

DPU - M0 - XRS1 XRS0 EXTRAM AO

AT89C51RB2/RC2

Bit

Number

7DPU

6-

5M0

4-

3XRS1XRAM Size

2XRS0

1 EXTRAM

Bit

Mnemonic Description

Disable Weak Pull-up

Cleared to activate the permanent weak pull up when latch data is logical 1

Set to disactive the weak pull-up (reduce power consumption)

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Pulse Length

Cleared to stretch MOVX control: the RD

periods (default).

Set to stretch MOVX control: the RD

periods.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

XRS1

0 0 256 Bytes (default)

0 1 512 Bytes

1 0 768 Bytes

1 1 1024 Bytes

EXTRAM Bit

Cleared to access internal XRAM using movx @ Ri/ @ DPTR.

Set to access external memory.

Programmed by hardware after Power-up regarding Hardware Security Byte

(HSB), default setting, XRAM selecte d.

and the WR pulse length is 6 clock

and the WR pulse length is 30 clock

XRS0 XRAM size

4180E–8051–10/06

ALE Output Bit

0AO

Clear ed , ALE is em itt e d at a c onst a nt rat e of 1/6 t he osci lla to r freq ue nc y (or 1/3 if

X2 mode is used). (default) Set, ALE is active only during a MOVX or MOVC

instruc tio n is use d.

Reset Value = XX0X 00’HSB. XRAM’0b (see Table 65)

Not bit addressable

25

AT89C51RB2/RC2

Timer 2 The Timer 2 in the AT89C51RB2/RC2 is the standard C52 Timer 2.

It is a 16-bit timer/counter: t he count is maintained by two e ight-bit timer registe rs, TH 2

and TL2 are cascaded. It is controlled by T2CON (Table 20) and T2MOD (Table 21)

registers. Timer 2 operation is similar to Timer 0 and Timer 1C/T2

operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2

allows TL2 to increment by the selected input.

Timer 2 has 3 operating modes: capture, autoreload and Ba ud Rate Generator. These

modes are selected by the combination of RCLK, TCLK and CP/RL2

see the Atm el 8-bit Micro control ler Hardw are d escription f or the des criptio n of Cap ture

and Baud Rate Generator Modes.

Timer 2 includes the following enhancements:

• Auto-reload mode with up or down counter

• Programmable clock-output

selects F

(T2CON).

Auto-reload Mode The auto-re load mod e configu res T imer 2 as a 16 -bit time r or eve nt coun ter with aut o-

matic reload . If DCEN b it in T2MOD i s cleared, Timer 2 behaves as in 8 0C52 (see the

Atmel C51 Microcontroller Hardware d escription). If DCEN bit is s et, Timer 2 acts a s an

Up/down timer/counter as shown in Figure 9. In this mode the T2EX pin controls the

direction of count.

When T2EX is hi gh, Timer 2 c ounts up. T im er overf low occurs at F FF Fh which set s t he

TF2 flag and generat es an interrupt reque st. The overflow also caus es the 16-bit val ue

in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.

/12 (timer

OSC

When T2EX is low, Timer 2 counts down. Timer underflow occurs when the count in the

timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers.

The underflow sets TF2 flag and reloads FFFFh into the timer registers.

The EXF2 bit toggles when Timer 2 overflows or underflows according to the direction of

the count. EXF2 does not generate any interrupt . This bit can be used to provide 17-bit

resolution.

26

4180E–8051–10/06

AT89C51RB2/RC2

T

g

F

Figure 9. Auto-Reload Mode Up/Down Counter (DCEN = 1)

F

CLK PERIPH

:6

T2

0

1

C/T2

T2CON

T2CON

TR2

Programmable Clock-out Mode

(DOWN COUNTING RELOAD VALUE)

FFh

(8-bit)

TL2

(8-bit)

RCAP2L

(

8-bit)

(UP COUNTING RELOAD VALUE)

FFh

(8-bit)

TH2

(8-bit)

RCAP2H

(8-bit)

T2EX:

if DCEN = 1, 1 = UP

if DCEN = 1, 0 = DOWN

if DCEN = 0, up countin

TOGGLE

TF2

T2CON

T2CON

EXF2

TIMER 2

INTERRUP

In the clock-out mode, Timer 2 operates as a 50% duty-cycle, programmable clock generator (see Fi gure 10). The input clock incr emen ts TL2 at freq uenc y F

CLK PERIPH

/2. The

timer repeatedly counts to overflow from a loaded value. At overflow, the contents of

RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, Timer 2

overflows do not generate interrupts. The formula gives the clock-out frequency as a

function of the system oscillator frequency and the value in the RCAP2H and RCAP2L

registers:

Clock O–utFrequency

-------------------------------------------------------------------------------------------- -

=

4 65536 RCAP2HRCAP2L⁄)

(×

CLKPERIPH

–

4180E–8051–10/06

For a 16 MHz system clock, Timer 2 has a programmable frequency range of 61 Hz

(F

CLK PERIPH

16

/2

) to 4 M H z (F

CLK PERIPH

/4). The generated clock signal is brought out to

T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

• Set T2OE bit in T2MOD register.

• Clear C/T 2

bit in T2CON register.

• Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L

registers.

• Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the

reload value or a different one depending on the application.

• T o start the timer, set TR2 run control bit in T2CON register.

It is possible to use Timer 2 as a baud rate generator and a clock generator simulta-

neously. For this configuration, the baud rates and clock frequencies are not

independent since both functions use the values in the RCAP2H and RCAP2L registers.

27

AT89C51RB2/RC2

Figure 10. Clock-Out Mode C/T2 = 0

FCLK PERIPH

:6

TR2

T2CON

TL2

(8-bit)

TH2

(8-bit)

OVERFLOW

T2EX

T2

Toggle

QD

EXEN2

T2CON

RCAP2L

(8-bit)

T2MOD

EXF2

T2CON

RCAP2H

(8-bit)

T2OE

TIMER 2

INTERRUPT

28

4180E–8051–10/06

Registers Table 20. T 2CON Register

T2CON – Timer 2 Control Register (C8h)

76543210

TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2# CP/RL2#

AT89C51RB2/RC2

Bit

Number

7 TF2

6EXF2

5 RCLK

4TCLK

3 EXEN2

2TR2

Bit

Mnemonic Description

Timer 2 Overflow Flag

Must be cleared by software.

Set by hardware on Timer 2 overflow, if RCLK = 0 and TCLK = 0.

Timer 2 External Flag

Set whe n a captur e or a reload is caused by a negative transition on T2EX pin if

EXEN2 = 1.

When set, causes the CPU to vector to Timer 2 interrupt routine when Timer 2

interrupt is enabled.

Must be cleared by software. EXF2 doesn ’t cause an interrupt in Up/down

counter mode (DCEN = 1).

Receive Clock Bit

Cleared to use timer 1 overflow as receive clock for serial port in mode 1 or 3.

Set to use Timer 2 overflow as receive clock for serial port in mode 1 or 3.

Transmit Clock Bit

Cleare d to use time r 1 overflow as transmit clock f or serial port in mode 1 or 3.

Set to use Timer 2 overflow as transmit clock for serial port in mode 1 or 3.

Timer 2 External Enable Bit

Cleared to ignore events on T2EX pin for Timer 2 operation.

Set to cause a capture or reload when a negative transition on T2EX pin is

detected, if Timer 2 is not used to clock the serial port.

Timer 2 Run Control Bit

Cleared to turn off Timer 2.

Set to turn on Timer 2.

4180E–8051–10/06

Timer/Coun ter 2 Select B it

1C/T2#

0CP/RL2#

Cleare d for timer operation (input fr om internal clock system: F

Set for count er oper at ion (i np ut fr o m T2 inp ut pi n, fa ll i ng edg e tr igg er ). Mus t be 0

for clock out mode.

Timer 2 Capture/Reload Bit

If RCLK = 1 or TCLK = 1, CP/RL2# is ignored and timer is forced to auto-reload

on Timer 2 overflow.

Cleare d to auto-reload on Timer 2 overf lows or negative transitions on T2 EX pin

if EXEN2 = 1.

Set to capture on negative transitions on T2EX pin if EXEN2 = 1.

Reset Value = 0000 0000b

Bit addressable

CLK PERIPH

).

29

AT89C51RB2/RC2

Table 21. T2MOD Register

T2MOD – Timer 2 Mode Control Register (C9h)

76543210

------T2OEDCEN

Bit

Number

7-

6-

5-

4-

3-

2-

1T2OE

0 DCEN

Bit

Mnemonic Description

Reserved

The value rea d fro m thi s bit is ind et erm in at e. D o no t set this bit.

Reserved

The value rea d fro m thi s bit is ind et erm in at e. D o no t set this bit.

Reserved

The value rea d fro m thi s bit is ind et erm in at e. D o no t set this bit.

Reserved

The value rea d fro m thi s bit is ind et erm in at e. D o no t set this bit.

Reserved

The value rea d fro m thi s bit is ind et erm in at e. D o no t set this bit.

Reserved

The value rea d fro m thi s bit is ind et erm in at e. D o no t set this bit.

Timer 2 Output Enable Bitt

Cleared to program P1.0/T2 as clock input or I/O port.

Set to program P1.0/T2 as clock output.

Down Counter Enable Bit

Cleare d to disable Timer 2 as up/down counter.

Set to enable Timer 2 as up/down counter.

Reset Value = XXXX XX00b

Not bit addressable

30

4180E–8051–10/06

AT89C51RB2/RC2

Programmable Counter Array (PCA)

The PCA provides more timing capabilities with less CPU intervention than the standard

timer/counters. Its adva ntages in clude reduc ed software ove rhead and improve d accuracy. The PCA consis ts of a dedicated tim er/counter which serv es as the time bas e for

an array of five com pare/ca pture Modu les. Its clock i nput can b e program med to count

any one of the following signals:

• Peripheral clock frequen cy (F

• Peripheral clock frequen cy (F

CLK PERIPH

CLK PERIPH

) ÷ 6

) ÷ 2

• Timer 0 overflow

• External input on ECI (P1.2)

Each compare/capture Modules can be programmed in any one of the following modes:

• Rising and/or falling edge capture

• Software timer

• High-speed output

• Pulse widt h modulator

Module 4 ca n also be pro grammed as a w atchd og time r (see Se ction "PCA Wa tchdo g

Timer", page 42).

When the compare/capture Modules are programmed in the capture mode, software

timer, or high speed output m ode, an interrupt can be generated when the Module executes its function. All five Module s plus the PCA timer overflow share one interrupt

vector.

The PCA timer/counter and compare/capture modules share Port 1 for external I/O.

These pins a re listed belo w. If one or sev eral bits in the po rt are not used for the PCA,

they can still be used for standard I/O.

PCA Component External I/O Pin

16-bit Counter P1.2/ECI

16-bit Module 0 P1.3/CEX0

16-bit Module 1 P1.4/CEX1

16-bit Module 2 P1.5/CEX2

16-bit Module 3 P1.6/CEX3

The PC A ti mer is a co mm on t ime b as e fo r all f ive M odu les ( see Fig ure 11). The ti mer

count source is determined from the CPS1 and CPS0 bits in the CMOD register

(Table 22) and can be programmed to run at:

• 1/6 the

• 1/2 the

periphera l c loc k f requency (F

periphera l c loc k f requency (F

CLK PERIPH

CLK PERIPH

)

)

• The Timer 0 overflow

• The input on the ECI pin (P1.2)

4180E–8051–10/06

31

AT89C51RB2/RC2

Figure 11. PCA Timer/Counter

To PCA

Modules

F

CLK PERIPH

F

CLK PERIPH

T0 OVF

Idle

P1.2

/6

It

CMOD

0xD9

CCON

0xD8

overflow

/2

CIDL CPS1 CPS0 ECF

WDTE

CF CR

CCF4 CCF3 CCF2 CCF1 CCF0

CH CL

16-bit up Counter

32

4180E–8051–10/06

Registers Table 22. CM OD Register

CMOD – PCA Counter Mode Register (D9h)

76543210

CIDL WDTE - - - CPS1 CPS0 ECF

AT89C51RB2/RC2

Bit

Number

7CIDL

6WDTE

5-

4-

3-

2 CPS1 PCA Count Pulse Select

1 CPS0

0ECF

Bit

Mnemonic Description

Counter Idle Co ntrol

Cleared to program the PCA Counter to continue functioning during idle Mode.

Set to program PCA to be gated off during idle.

Watchdog Timer Enable

Cleared to disable Watchdog Timer fu nction on PCA Module 4.

Set to enable Watchdog Timer function on PCA Module 4.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

CPS0 Selected PCA input

CPS1

0 0 Internal clock F

0 1 Internal clock F

1 0 Timer 0 Over flow

1 1 External cl ock at ECI/ P1.2 pin (max rate = fCLK PERIPH/ 4)

PCA Enable Counter O ve rflow Inte rrupt

Cleared to disable CF bit in CCON to inhibit an interrupt.

Set to enable CF bit in CCON to generate an interrupt.

CLK PERIPH

LK PERIPH

/6

/2

4180E–8051–10/06

Reset Value = 00XX X000b

Not bit addressable

The CMOD register includes three additional bits associated with the PCA.

• The CIDL bit which allows the PCA to stop during idle mode.

• The WDT E bit which enables or disables the watchdog function on Mo dule 4.

• The ECF bit which when set causes an interrupt and the PCA overflow flag CF (in

the CCON SFR) to be set when the PCA timer overflows.

The CCON register contains the run control bit for the PCA and the flags for the PCA

timer (CF) and each Module (see Table 23).

• Bit CR (CCON. 6) must be set by software to run the PCA. The PCA is shut off by

clearing this bit.

• Bit CF: The CF bit (CCON. 7) is set when the PCA counter overflows and an

interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can

only be cleared by software.

• Bits 0 through 4 are the flags for the Modules (bit 0 for Module 0, bit 1 for Module 1,

etc. ) and are set by hardware when either a match or a capture occurs. These flags

also can only be cleared by software.

33

AT89C51RB2/RC2

Table 23. CCON Register

CCON – PCA Counter Control Register (D8h)

76543210

CF CR - CCF4 CCF3 CCF2 CCF1 CCF0

Bit

Number

7CF

6CR

5-

4 CCF4

3 CCF3

2 CCF2

1 CCF1

Bit

Mnemonic Description

PCA Counter Overflow Flag

Set by hardware when the counter rolls over. CF flags an interrupt if bit ECF in

CMOD is set. CF may be set by either hardware or software but can only be

cleared by software.

PCA Counter Run Control Bit

Must be cleared by software to turn the PCA counter off.

Set by software to turn the PCA counter on.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

PCA Module 4 Interrupt Flag

Must be cleared by software.

Set by hardware when a match or capture occurs.

PCA Module 3 Interrupt Flag

Must be cleared by software.

Set by hardware when a match or capture occurs.

PCA Module 2 Interrupt Flag

Must be cleared by software.

Set by hardware when a match or capture occurs.

PCA Module 1 Interrupt Flag

Must be cleared by software.

Set by hardware when a match or capture occurs.

34

PCA Module 0 Interrupt Flag

0 CCF0

Must be cleared by software.

Set by hardware when a match or capture occurs.

Reset Value = 000X 0000b

Bit addressable

The watchdog timer function is implemented in Module 4 (see Figure 14).

The PCA interrupt system is shown in Figure 12.

4180E–8051–10/06

Figure 12. PC A Interru p t System

PCA Timer/Coun ter

Module 0

CF CR

AT89C51RB2/RC2

CCF4 CCF3 CCF2 CCF1 CCF0

CCON

0xD8

Module 1

Module 2

Module 3

Module 4

To Interrupt

Priority Decoder

ECF

ECCFn

CCAPMn. 0CMOD. 0

IEN0. 6 IEN0. 7

EC EA

PCA Modules: each one of th e fiv e com pare /cap ture Mo dule s ha s si x pos sibl e func tions. It can perform:

• 16-bit Capture, positive-edge triggered

• 16-bit Capture, negative-edge triggered

• 16-bit Capture, both positive and negative-ed ge triggered

• 16-bit Software Timer

• 16-bit High-speed Output

• 8-bit Pulse Width Modulator

In addition, Module 4 can be used as a Watchdog Timer.

Each Module in the PCA has a special function register associated with it. These regis-

ters are: CC APM0 f or Modu le 0, CCA PM1 for M odule 1, e tc. (see T able 24). The

registers contain the bits that control the mode that each Module will operate in.

• The ECCF bit (CCAPMn. 0 where n = 0, 1, 2, 3, or 4 depending on the Module)

enables the CCF flag in the CCON SFR to generate an interrupt when a match or

compare occurs in the associated Module.

• PW M (CCAPMn. 1) enables the pulse width modulation mode.

• The TOG bit (CCAPMn. 2) when set causes the CEX output associated with the

Module to toggle when there is a match between the PCA counter and the Module's

capture/compare register.

• The match bit MAT (CCAPMn. 3) when set will cause the CCFn bit in the CCON

register to be set when there is a match between the PCA counter and the Module's

capture/compare register.

• The next two bits CAPN (CCAPMn. 4) and CAPP (CCAPMn. 5) determine the edge

that a capture input will be active on. The CAPN bit enables the negative edge, and

the CAPP bit enables the positive edge. If both bits are set both edges will be

enabled and a capture will occur for either transit ion.

• The last bit in the register ECOM (CCAPMn. 6) when set enables the comparator

function.

4180E–8051–10/06

Table 24 shows the CCAPMn settings for the various PCA functions.

35

AT89C51RB2/RC2

Table 24. CCAPMn Registers (n = 0-4)

CCAPM0 – PCA Module 0 Compare/Capture Control Register (0DAh)

CCAPM1 – PCA Module 1 Compare/Capture Control Register (0DBh)

CCAPM2 – PCA Module 2 Compare/Capture Control Register (0DCh)

CCAPM3 – PCA Module 3 Compare/Capture Control Register (0DDh)

CCAPM4 – PCA Module 4 Compare/Capture Control Register (0DEh)

76543210

- ECOMn CAPPn CAPNn MATn TOGn PWMn ECCFn

Bit

Number

7-

6ECOMn

5 CAPPn

4 CAPNn

3MATn

2 TOGn

1PWMn

Bit

Mnemonic Description

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Enable Compa rator

Cleared to disable the comparator function.

Set to enable the comparator function.

Capture Positiv e

Cleared to disable positive edge capture.

Set to enable positive edge capture.

Capture Negati ve

Cleared to disable negative edge capture.

Set to enable negative edge capture.

Match

When MATn = 1, a match of the PCA counter with this Module's

compare/capture reg ister caus es the CCFn bit in CCON to be set, flagging an

interrupt.

Toggle

When TOGn = 1, a match of the PCA counter with this Module's

compare/capture register causes theCEXn pin to toggle.

Pul s e Width Modulation Mode

Cleared to disable the CEXn pin to be used as a p ulse wid th modulat ed output.

Set to enable the CEXn pin to be used as a pulse width modulated output.

36

Enable CCF Interrupt

0 CCF0

Clear ed to disa bl e comp ar e /cap t ure f la g CCFn in t he CCON regi st er t o ge ne rat e

an interrupt.

Set to enable compare/capture flag CCFn in the CCON register to generate an

interrupt.

Reset Value = X000 0000b

Not bit addressable

4180E–8051–10/06

AT89C51RB2/RC2

Table 25. PCA Module Modes (CCAPMn Registers)

ECOMn CAPPn CAPNn MATn TOGn PWMm ECCFn Module Function

0000000 No Operation

X10000X

X01000X

X11000X

100100X

100110X 16-bit High-speed Output

1000010 8-bit PWM

1001X0X Watchdog Timer (Module 4 only)

16-bit capture by a positive-edge

trigger on CEXn

16-bit capture by a negative trigger

on CEXn

16-bit capture by a transition on

CEXn

16-bit Software Timer/Compare

mode.

There are two a dditiona l regist ers associ ated with eac h of the PCA Mo dules. The y are

CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a

capture oc curs or a com pare shou ld oc cur. W hen a M odul e is used in the P WM mod e

these registers are u sed to control the duty cycle of the output (see Table 26 and

Table 27).

Table 26. CCAPnH Registers (n = 0-4)

CCAP0H – PCA Module 0 Compare/Capture Control Register High (0FAh)

CCAP1H – PCA Module 1 Compare/Capture Control Register High (0FBh)

CCAP2H – PCA Module 2 Compare/Capture Control Register High (0FCh)

CCAP3H – PCA Module 3 Compare/Capture Control Register High (0FDh)

CCAP4H – PCA Module 4 Compare/Capture Control Register High (0FEh)

76543210

--------

Bit

Number

7 - 0 -

Bit

Mnemonic Description

PCA Module n Compare/Capture Control

CCAPnH Value

Reset Value = 0000 0000b

Not bit addressable

4180E–8051–10/06

37

AT89C51RB2/RC2

Table 27. CCAPnL Registers (n = 0-4)

CCAP0L – PCA Module 0 Compare/Capture Control Register Low (0EAh)

CCAP1L – PCA Module 1 Compare/Capture Control Register Low (0EBh)

CCAP2L – PCA Module 2 Compare/Capture Control Register Low (0ECh)

CCAP3L – PCA Module 3 Compare/Capture Control Register Low (0EDh)

CCAP4L – PCA Module 4 Compare/Capture Control Register Low (0EEh)

76543210

--------

Bit

Number

7 - 0 -

Bit

Mnemonic Description

PCA Module n Compare/Capture Control

CCAPnL Value

Reset Value = 0000 0000b

Not bit addressable

Table 28. CH Register

CH – PCA Counter Register High (0F9h)

76543210

--------

Bit

Number

7 - 0 -

Bit

Mnemonic Description

PCA Counter

CH Value

Reset Value = 0000 0000b

Not bit addressable

Table 29. CL Register

38

CL – PCA Counter Register Low (0E9h)

76543210

--------

Bit

Number

7 - 0 -

Bit

Mnemonic Description

PCA Counter

CL Value

Reset Value = 0000 0000b

Not bit addressable

4180E–8051–10/06

AT89C51RB2/RC2

PCA Capture Mode To use on e of the PCA M odules in the capture m ode either one or bo th of the CCAP M

bits CAPN and CAPP f or that Module must be set. The external CEX input for t he M odule (on po rt 1) is sam pled for a transiti on. Wh en a valid t ransition occurs t he PCA

hardware l oads the value of th e PC A cou nte r regi sters ( CH and CL) i nto th e Mo dule's

capture registers (CCAPnL and CCAP nH). If the CCFn bit for the Modul e in the CCON

SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated

(see Figure 1 3).

Figure 13. PCA Capture Mode

Cex. n

CF CR

ECOMn

CCF4 CCF3 CCF2 CCF1 CCF0

Capture

CAPNn MATn TOGn PWMn ECCFnCAPPn

CCON

0xD8

PCA IT

PCA Counter/Timer

CH CL

CCAPnH CCAPnL

CCAPMn, n = 0 to 4

0xDA to 0xDE

4180E–8051–10/06

39

AT89C51RB2/RC2

16-bit Software Timer/ Compare Mode

The PCA Modules can be used as software timers by setting both the ECOM and M AT

bits in the Modules CCAPMn register. The PCA timer will be compared to the Module's

capture registers and wh en a ma tch occurs, an i nterrup t will occur if the CCFn (CCO N

SFR) and the ECCFn (CCAPMn SFR) bits for the Module are both set (see Figure 14).

Figure 14. PCA Compare Mode and PCA Wat chdog Timer

CF CCF2 CCF1 CCF0

CR

CCF4

CCF3

CCON

0xD8

Write to

CCAPnH

Write to

CCAPnL

10

Reset

Enable

PCA IT

CCAPnH CCAPnL

Match

16 bit Comparator

(1)

CH CL

PCA Counte r/Ti mer

ECOMn

CIDL CPS1 CPS0 ECF

WDTE

CAPNn MATn TOGn PWMn ECCFnCAPPn

CCAPMn, n = 0 to 4

0xDA to 0xDE

CMOD

0xD9

RESET

Note: 1. Only for Module 4

Before enabling ECOM b it, CCAPnL and CCAPnH should be set with a non z ero value,

otherwise an unwanted match could occur. Writing to CCAPnH will set the ECOM bit.

40

Once ECOM set, writin g CCAPnL will clear E COM so that an un wanted ma tch doe sn’t

occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this

reason, user software should write CCAPnL first, and then CCAPnH. Of course, the

ECOM bit can still be controlled by accessing to CCAPMn register.

4180E–8051–10/06

AT89C51RB2/RC2

High-speed Output Mode In t his mode the CEX output (on port 1) as sociated with the PCA module will toggle

each time a match occurs between the PCA counter and the modules capture registers.

To activate this mode the TOG, MAT, and ECOM bits in the modules CCAPMn SFR

must be set (see Figure 15).

A prior write must be done to CCAPnL and CCAPnH before writing the ECOMn bit.

Figure 15. PCA High-speed Output Mode

CCON

0xD8

PCA IT

Write to

CCAPnH

Write to

CCAPnL

Reset

CF CR

CCAPnH CCAPnL

CCF4 CCF3 CCF2 CCF1 CCF 0

0

1

Enable

16-bit Comparator

CH CL

PCA Counte r/Ti mer

ECOMn

Match

CAPNn MATn TOGn PWMn ECCFnCAPPn

CEXn

CCAPMn, n = 0 to 4

0xDA to 0xDE

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non-zero value,

otherwise an unwanted match could occur.

Once ECOM is set, writing CCAPnL will clear ECOM so that an unwanted match doesn’t

occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this

reason, user software should write CCAPnL first, and then CCAPnH. Of course, the

ECOM bit can still be controlled by accessing to CCAPMn register.

4180E–8051–10/06

41

AT89C51RB2/RC2

Pulse Width Modulator Mode

All of the PCA Modules can be used as PWM outputs. Fi gure 16 shows the PW M func tion. The frequency of the output depends on the source for the PCA timer. All of the

Modules will have the sam e freque ncy of output be cause they all share the PCA timer.

The duty cycle of each Module is independently variable using the module's capture

register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output

will be hig h. Wh en CL ov erfl ows f rom FF t o 00 , CC APL n is r eloa de d wi th th e val ue i n

CCAPHn. This allows updat ing the PWM without glitches . The PWM and E COM bits in

the module's CCAPMn register must be set to enable the PWM mode.

Figure 16. PCA PWM Mode

CCAPnH

CCAPnL

8-bit Com p arator

CL

PCA Counter/T imer

“0”

CEXn

“1”

CCAPMn, n = 0 to 4

0xDA to 0xDE

ECOMn

Overflow

Enable

CAPNn MATn TOGn PWMn ECCFnCAPPn

PCA Watchdog Timer An on-board watchdog timer is available with the PCA to improve the reliability of the

system without increasing chip count. Watchdog timers are useful for systems that are

susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only

PCA Module that can be programmed as a watchdog. Howev er, this Module can s till be

used for other modes if the watchd og is not needed. Figure 14 shows a d iagram of how

the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just

like the other compare modes, this 16-bit value is compared to the PCA timer value. If a

match is allowed to occur, an internal reset will be generated. This will not cause the

RST pin to be driven high.

42

In order to hold off the reset, the user has the following three options:

1. Periodically change the compare value so it will never match the PCA timer.

2. Periodically change the PCA timer value so it will never match the compare

values.

3. Disable the watchdog by clearing the WDTE bit before a match occurs and then

re-enable it.

The first two options are more reliable because th e watchdo g timer is never disabl ed as

in option #3. If the program c ounter ev er g oes ast ray, a ma tch will eventu ally occur and

cause an internal reset. The second option is also not recommended if other PCA Modules are being used. Remember, the PCA timer is the time base for all modules;

4180E–8051–10/06

AT89C51RB2/RC2

changing the time base for other Modules would not be a good idea. Thus, in most applications the first solution is the best option.

This watchdog timer won’t generate a reset out on the reset pin.

4180E–8051–10/06

43

AT89C51RB2/RC2

Serial I/O Port The serial I/O port in the AT89C51RB2/RC2 is compatible with the serial I/O port in the

80C52.

It provides both synchronous and asynchronous communication modes. It operates as a

Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes

(Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously

and at different baud rates

Serial I/O port includes the following enhancements:

• Framing error detection

• Automatic address recognition

Framing Error Detection Framing bi t error de tect ion is provid ed for t he three asyn chro nous m odes (m odes 1, 2

and 3). To enable the framing bit error detection feat ure, set SMOD0 bit in PCON register (See Figure 17).

Figure 17. Framing Error Block Diagram

RITIRB8TB8RENSM2SM1SM0/FE

SCON (98h)

Set FE bit if stop bit is 0 (framing error) (SMOD0 = 1)

SM0 to UART mode control (SMOD0 = 0)

PCON (87h)

IDLPDGF 0GF1POF-SMOD0SMOD1

To UART framing error control

When this feature is enabl ed, the receiver chec ks each incoming da ta frame for a valid

stop bit. An invalid stop bit may result from noise on the serial lines or f rom simultaneous

transmissio n by two C PUs . If a valid stop bit is n ot found, t he Frami ng Error bit (FE) in

SCON register (See Table 33.) bit is set.

Software may exam ine FE b it after each reception to check for data errors. O nce set,

only software or a reset can clear FE bi t. Subsequ ently received frames with valid stop

bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the

last data bit (See Figure 18. and Figure 19.).

Figure 18. UART Timings in Mode 1

RXD

RI

SMOD0=X

FE

SMOD0=1

Start

bit

Data byte

D7D6D5D4D3D2D1D0

Stop

bit

44

4180E–8051–10/06

Figure 19. UART Timings in Modes 2 and 3

AT89C51RB2/RC2

Automatic Address Recognition

RXD

RI

SMOD0=0

RI

SMOD0=1

FE

SMOD0=1

Start

bit

Data byte Ninth

D8D7D6D5D4D3D2D1D0

Stop

bit

bit

The automatic address rec og nition feat ure is e nabled when the multiprocessor comm unication feature is enabled (SM2 bit in SCON register is set).

Implemented in hardw are, auto matic add ress recog nition enh ances the multipro cessor

communication feature by allowing the serial port to examine the address of each

incoming command frame. Only when the serial port recognizes its own address, the

receiver sets RI bit in SCON register to generate an interrupt. This ensures that the CPU

is not interrupted by command frames addressed to other devices.

If desired, the user may ena ble the a utomatic addres s recognit ion feature in m ode 1.In

this configuration, the stop bit takes the place of the ninth data bit. Bit RI is set only when

the received com mand fr ame ad dress matc hes the de vice’s addres s and is term inated