BDTIC www.bdtic.com/ATMEL

Features

• 80C51 Core Architecture

• 256 Bytes of On-chip RAM

• 256 Bytes of On-chip XRAM

• 16K Bytes of On-chip Flash Memory

– Data Retention: 10 Years at 85°C

– Erase/Write Cycle: 100K

• Boot Code Section with Independent Lock Bits

• 2K Bytes of On-chip Flash for Bootloader

• In-System Programming by On-Chip Boot Program (CAN, UART) and IAP Capability

• 2K Bytes of On-chip EEPROM

– Erase/Write Cycle: 100K

• 14-sources 4-level Interrupts

• Three 16-bit Timers/Coun ter s

• Full Duplex UART Compatible 80C51

• Maximum Crystal Frequency 40 MHz. In X2 Mode, 20 MHz (CPU Core, 40 MHz)

• Three or Four Ports: 16 or 20 Digital I/O Lines

• Two-channel 16-bit PCA

– PWM (8-bit)

– High-speed Output

– Timer and Edge Capture

• Double Data Pointer

• 21-bit Watchdog Timer (7 Programmable bits)

• A 10-bit Resolution Analog-to-Digital Converter (ADC) with 8 Multiplexed Inputs

• Full CAN Controller

– Fully Compliant with CAN rev.# 2.0A and 2.0B

– Optimized Structure for Communication Management (Via SFR)

– 4 Independent Message Objects

-Each Message Object Programmable on Transmission or Reception

-Individual Tag and Mask Filters up to 29-bit Identifier/Channel

-8-byte Cyclic Data Regis ter (FIFO)/Message Object

-16-bit Status and Control Register/Message Object

-16-bit Time-Stamping Register/Message Object

-CAN Specification 2.0 Part A or 2.0 Part B Programmable for Each Message

Object

-Access to Message Object Control and D ata Registers Via SFR

-Programmable Reception Buffer Length up to 4 Message Objects

-Priority Management of Reception of Hits on Several Message Objects

Simultaneously (Basic CAN Feature)

-Priority Management for Transmission

-Message Object Overrun Interrupt

– Supports

-Time Triggered Communication

-Autobaud and Listening Mode

-Programmable Automatic Reply Mode

• 1-Mbit/s Maximum Transfer Rate at 8 MHz

• Readable Error Counters

• Programmable Link to On-chip Timer for Time Stamping and Network Synchronization

• Independent Baud Rate Prescaler

• Data, Remote, Error and Overload Frame Handling

• Power-saving Modes

–Idle Mode

– Power-down Mode

• Power Supply: 3 Volts to 5.5 Volts

• Temperature Range: Industrial (-40° to +85°C)

• Packages: SOIC28, SOIC24, PLCC28, VQFP32

(1)

Crystal Frequency In X2 Mode

Enhanced 8-bit

Microcontroller

with CAN

Controller and

Flash

T89C51CC02

AT89C51CC02

Note: 1. At BRP = 1 sampling point will be fixed.

Rev. 4126L–CAN–01/08

AT/T89C51CC02

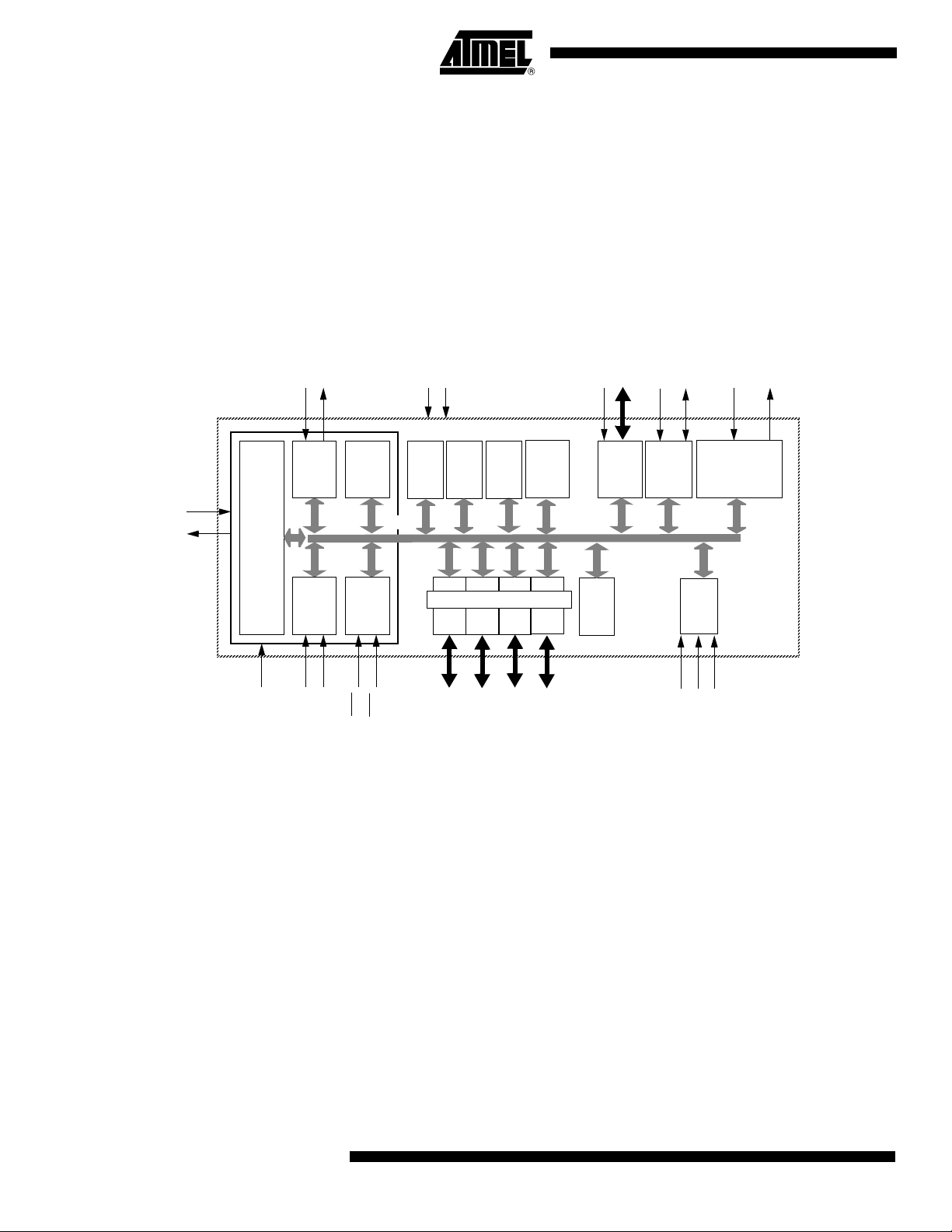

Description Part of the CANary

tions, the T89C51CC02 is a low-pin count 8-bit Flash microcontroller.

In X2 Mode a maximum external clock rate of 20 MHz reaches a 300 ns cycle time.

Besides the full CA N controll er T89C51CC02 p rovides 16K Bytes of Fl ash memory

including In-Sy stem Programm ing (ISP), 2K Byt es Boot Flash Mem ory, 2K Bytes

EEPROM and 512 Bytes RAM.

Special attention is payed to the reduction of the electro-magnetic emission of

T89C51CC02.

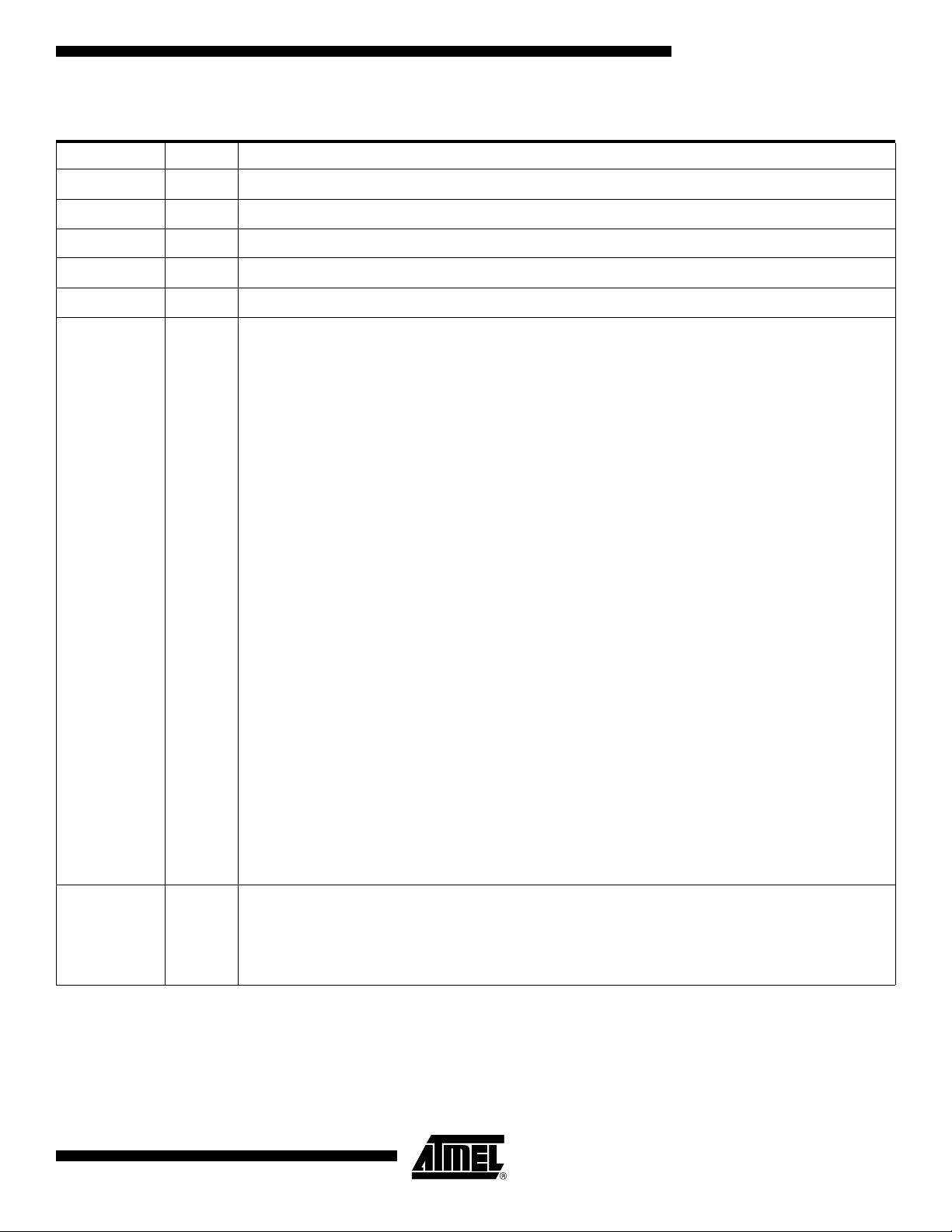

Block Diagram

RxD

TxD

TM

family of 8-bit microcon troll er s dedi ca ted to C AN ne twork appl ica-

TxDC

PCA

Vss

Vcc

ECI

T2EX

T2

RxDC

XTAL1

XTAL2

CPU

C51

CORE

T1

RAM

256x8

INT

Ctrl

INT0

UART

Timer 0

Timer 1

T0

RESET

INT1

IB-bus

Flash

16K x

8

loader

2K x 8

Port 1

Note: 1. 8 analog Inputs/8 Digital I/O.

2. 2-bit I/O Port.

Boot

EE

PROM

2K x 8

Parallel I/O Ports

Port 3

Port 2

P2(2)

P1(1)

P3

XRAM

256 x 8

Port 4

P4(2)

Watch

Dog

PCA

Timer 2

CAN

CONTROLLER

10-bit

ADC

VAREF

VAGND

VAVCC

2

4126L–CAN–01/08

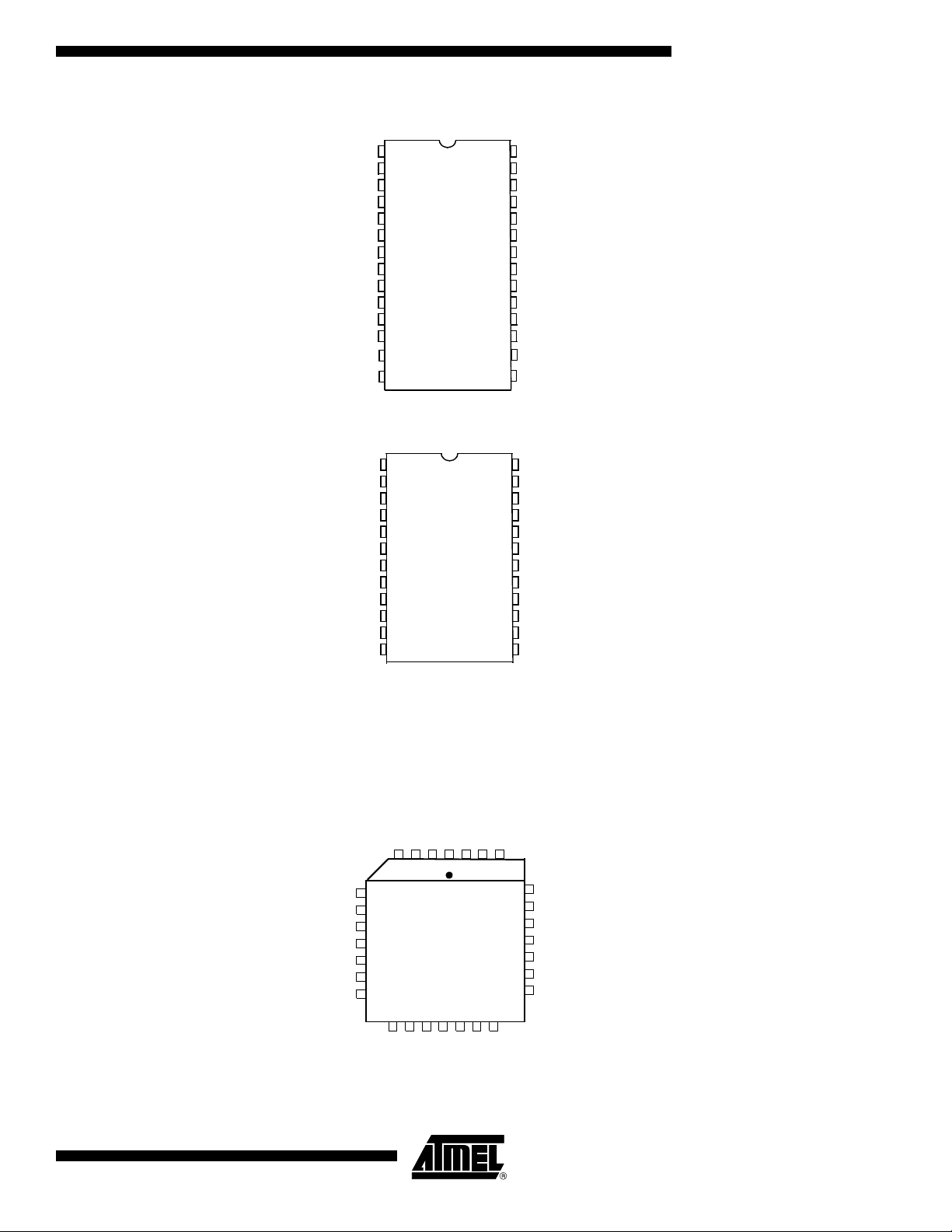

Pin Configurations

AT/T89C51CC02

VAREF

VAGND

VAVCC

P4.1/RxDC

P4.0/TxDC

P2.1

P3.7

P3.6

P3.5/T1

P3.4/T0

P3.3/INT1

P3.2/INT0

P3.1/TxD

P3.0/RxD

VAREF

VAGND

VAVCC

P4.1/RxDC

P4.0/TxDC

P3.5/T1

P3.4/T0

P3.3/INT1

P3.2/INT0

P3.1/TxD

P3.0/RxD

XTAL2

1

2

3

4

5

6

7

SO28

8

9

10

11

12

13

14

1

2

3

4

5

6

7

SO24

8

9

10

11

12

28

P1.0/

27

P1.1/AN1/T2EX

26

P1.2/AN2/ECI

P1.3/AN3/CEX0

25

P1.4/AN4/CEX1

24

P1.5/AN5

23

P1.6/AN6

22

P1.7/AN7

21

P2.0

20

RESE

19

18

VSS

VCC

17

XTAL1

16

XTAL2

15

24

P1.0/

23

P1.1/AN1/T2EX

22

P1.2/AN2/ECI

P1.3/AN3/CEX0

21

P1.4/AN4/CEX1

20

P1.5/AN5

19

P1.6/AN6

18

P1.7/AN7

17

RESE

16

VSS

15

14

VCC

XTAL1

13

AN0/T2

T

AN0/T2

T

4126L–CAN–01/08

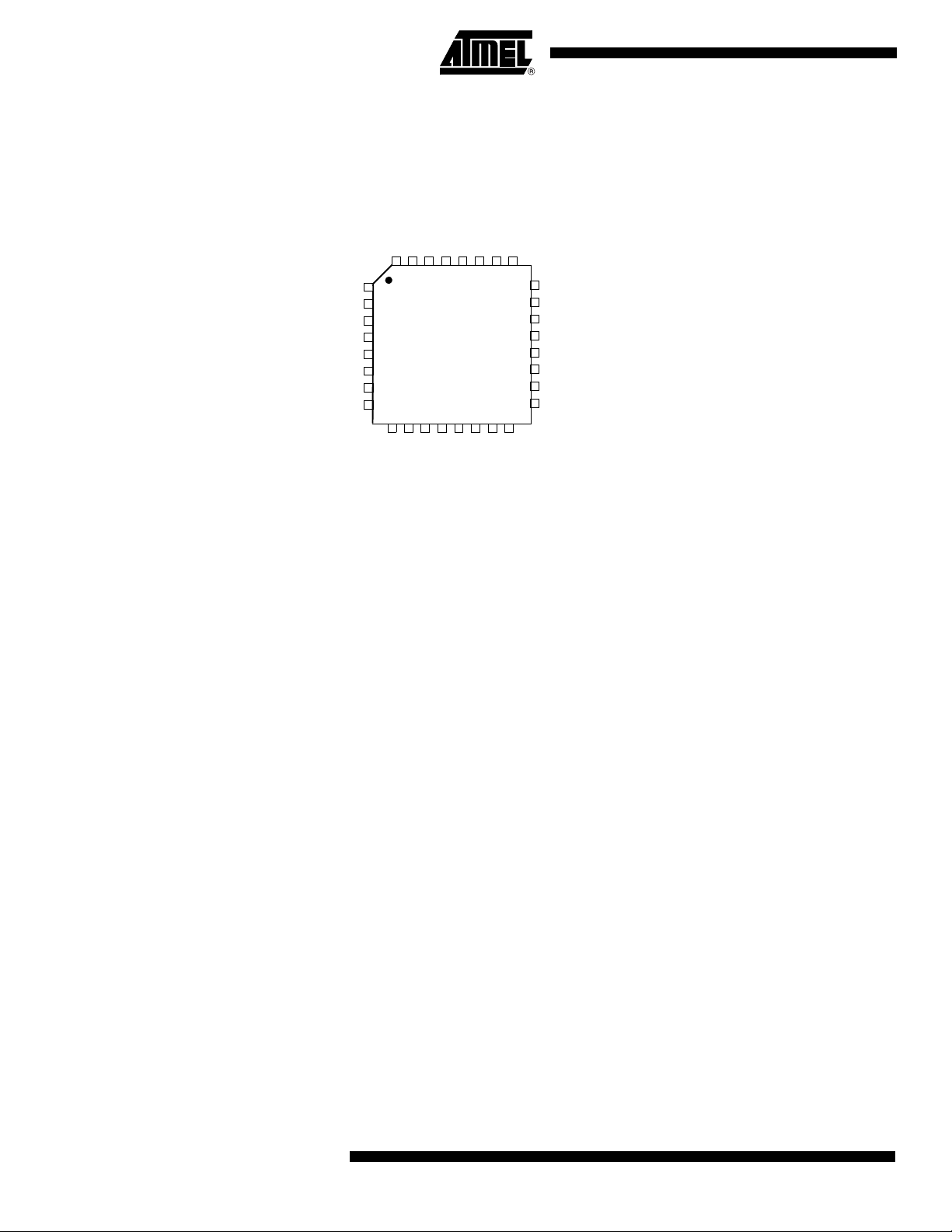

P4.0/TxDC

P2.1

P3.7

P3.6

P3.5/T1

P3.4/T0

P3.3/INT1

VAGND

VAVCC

P4.1/RxDC

432

5

6

7

PLCC-28

8

9

10

11

12131415161718

P3.1/TxD

P3.0/RxD

P3.2/INT0

VAREF

1

XTAL2

P1.1/AN1/T2EX

P1.0/AN 0/T2

282726

VCC

XTAL1

P1.2/AN2/ECI

25

24

23

22

21

20

19

VSS

P1.3/AN3/CEX0

P1.4/AN4/CEX1

P1.5/AN5

P1.6/AN6

P1.7/AN7

P2.0

RESET

3

AT/T89C51CC02

P4.1/RxDC

NC

VAREF

VAGND

VAVCC

P1.0/AN 0/T2

P1.2/AN2/ECI

P1.1/AN1/T2EX

P4.0/TxDC

P2.1

P3.7

P3.6

P3.5/T1

P3.4/T0

NC

P3.3/INT1

1

2

3

4

5

6

7

8

32

9

P3.2/INT0

30

31

QFP-32

101112

NC

P3.1/TxD

P3.0/RxD

28

29

131415

XTAL2

27

25

26

24

P1.3/AN3/CEX0

23

P1.4/AN4/CEX1

22

P1.5/AN5

21

P1.6/AN6

20

P1.7/AN7

19

P2.0

18

NC

17

RESET

16

VSS

VCC

XTAL1

4

4126L–CAN–01/08

Pin Description

Pin Name Type Description

VSS GND Circuit ground

VCC Supply Voltage

VAREF Reference Voltage for ADC (input)

VAVCC Supply Voltage for ADC

VAGND Reference Ground for ADC (internaly connected with the VSS)

P1.0:7 I/O Port 1:

Is an 8-bit bi-directional I/O port w ith internal pull -ups. Port 1 pins can be used for digit al input/o utput or as

analog inputs for the Analog Digital Converter (ADC). Port 1 pins that have 1’s written to them are pulled

high by the internal pull-up transistors and can be used as inputs in this state. As inputs, Port 1 pins that

are being pulled low externally will be the source of curren t (I

because of the internal pull-ups. Port 1 pins are assigned to be used as analog inputs via the ADCCF

register (in this case the internal pull-ups are disconnected).

As a secondary digital function, port 1 contains the Timer 2 external trigger and clock input; the PCA

external clock input and the PCA module I/O.

P1.0/AN0/T2

Analog input channel 0,

External clock input for Timer/counter2.

P1.1/AN1/T2EX

Analog input channel 1,

Trigger input for Timer/counter2.

P1.2/AN2/ECI

Analog input channel 2,

PCA external clock inpu t.

P1.3/AN3/CEX0

Analog input channel 3,

PCA module 0 Entry of input/PWM output.

P1.4/AN4/CEX1

Analog input channel 4,

PCA module 1 Entry of input/PWM output.

P1.5/AN5

Analog input channel 5,

P1.6/AN6

Analog input channel 6,

P1.7/AN7

Analog input channel 7,

It can drive CMOS inputs without external pull-ups.

AT/T89C51CC02

, See section ’Electrical C haracteristic’)

IL

P2.0:1 I/O Port 2:

4126L–CAN–01/08

Is an 2-bit bi-directional I/O port with internal pull-ups. Port 2 pins that have 1’s written to them are pulled

high by the internal pull-ups and can be used as inputs in this state. As inputs, Port 2 pins that are being

pulled low externally will be a source of current (IIL, on the datasheet) because of the internal pull-ups.

In the T89C51CC02 Port 2 can sink or source 5mA. It can drive CMOS inputs without external pull-ups.

5

AT/T89C51CC02

Pin Name Type Description

P3.0:7 I/O Port 3:

Is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins that have 1’s written to them are pulled

high by the internal pull-up transistors and can be used as inputs in this state. As inputs, Port 3 pins that

are being pu lled low externally will be a source of current (I

because of the internal pull-ups.

The output latch corresponding to a secondary function must be programmed to one for that function to

operate (except for TxD and WR

P3.0/RxD: Receiver data input (asynchronous) or data input/output (synchronous) of the serial interface

P3.1/TxD: Transmitter data output (asynchronous) or clock output (synchronous) of the serial interface

P3.2/INT0

P3.3/INT1

P3.4/T0: Timer 0 counter input

P3.5/T1: Timer 1 counter input

P3.6: Regular I/O port pin

P3.7: Regular I/O port pin

P4.0:1 I/O Port 4:

Is an 2-bit bi-directional I/O port with internal pull-ups. Port 4 pins that have 1’s written to them are pulled

high by the internal pull-ups and can be used as inputs in this state. As inputs, Port 4 pins that are being

pulled low externally will be a source of current (IIL, on the datasheet) because of the internal pull-up

transistor.

The output latch corresponding to a secondary function RxDC must be programmed to one for that

function to operate. The secondary functions are assigned to the two pins of port 4 as follows:

P4.0/TxDC:

Transmitter output of CAN controller

P4.1/RxDC:

Receiver input of CAN controller.

It can drive CMOS inputs without external pull-ups.

IL

). The secondary functions are assigned to the pins of port 3 as follows:

: External interrupt 0 input/timer 0 gate control input

: External interrupt 1 input/timer 1 gate control input

, See section ’Electrical Characteristic’)

RESET I/O Reset:

A high level on this pin during two machine cycles while the oscillator is running resets the device. An

internal pull-down resistor to VSS permits power-on reset using only an external capacitor to VCC.

XTAL1 I XTAL1:

Input of the inverting oscillator amplifier and input of the internal clock generator circuits. To drive the

device from an external clock sourc e, XTAL1 should be driven, while XTAL2 is left unconnected. To

operate above a frequency of 16 MHz, a duty cycle of 50% should be maintained.

XTAL2 O XTAL2:

Output from the inverting oscillator amplifier.

6

4126L–CAN–01/08

AT/T89C51CC02

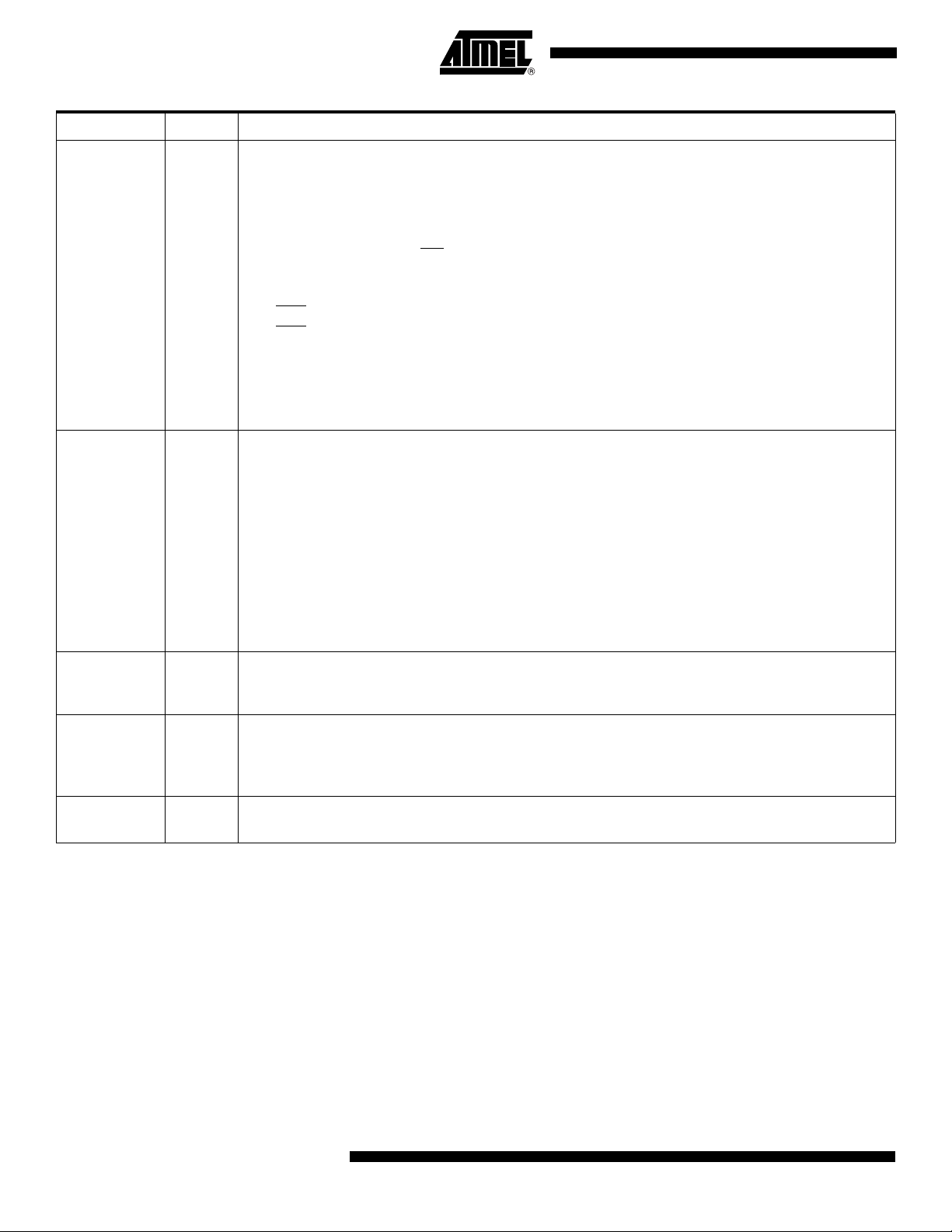

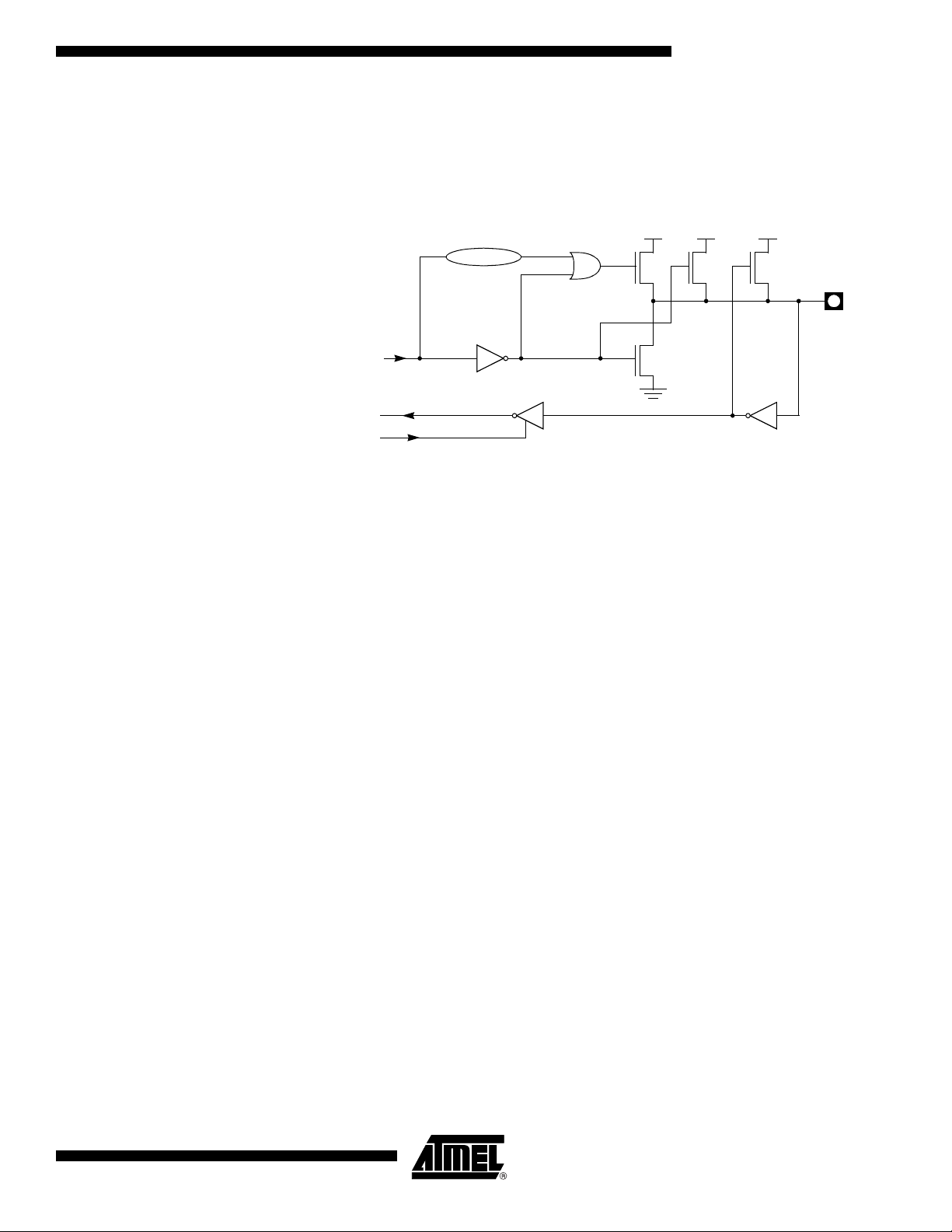

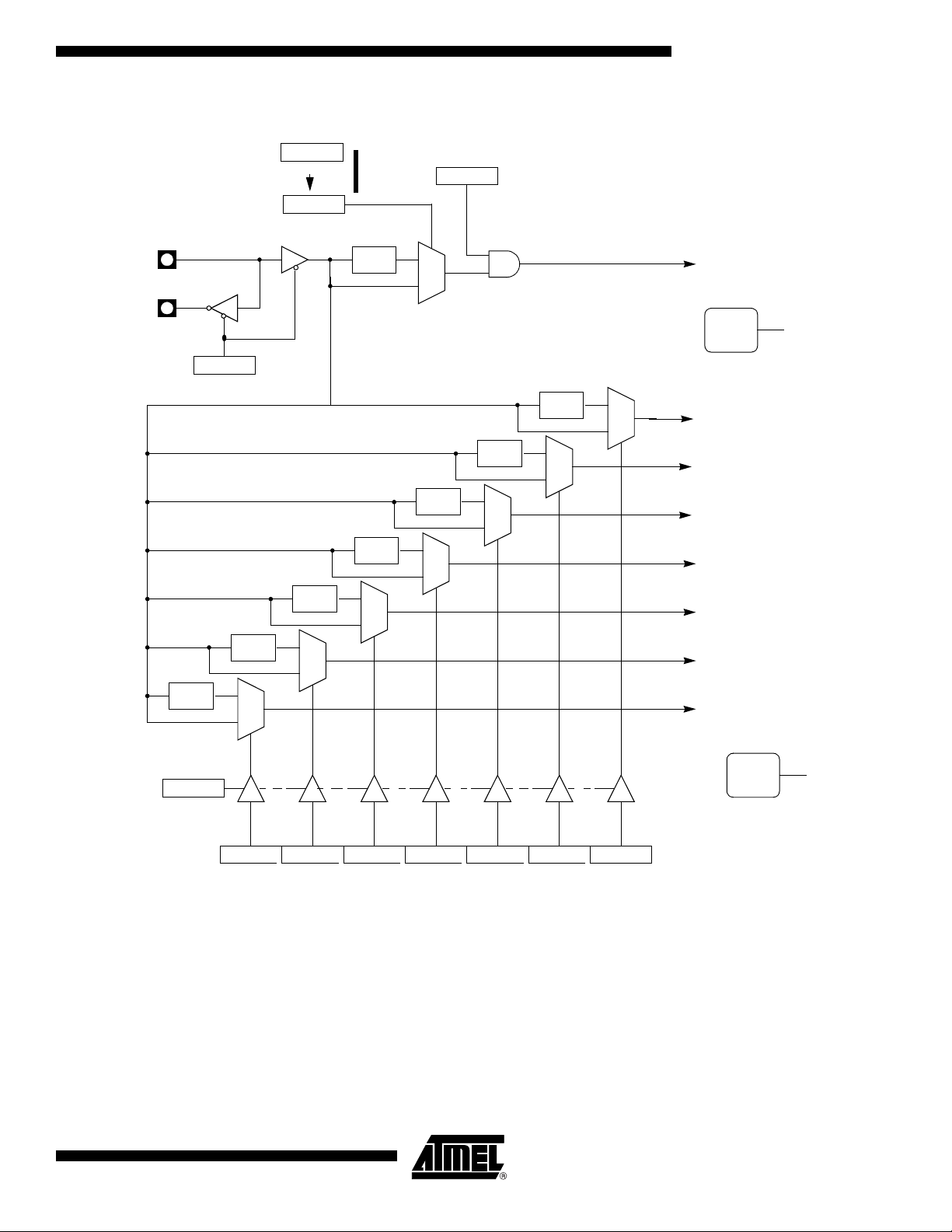

I/O Configurations Each Port SFR operates via type-D latches, as illustrated in Figure 1 for Ports 3 and 4. A

CPU ’write to latch’ signal initiates transfer of internal bus data into the type-D latch. A

CPU ’read latch’ signal transf ers the latched Q out put onto the intern al bus. Similarl y, a

’read pin’ signal transfers the logical level of the Port pin. Some Port data instructions

activate the ’read latch’ signal while others activate the ’read pin’ signal. Latch instructions are referred to as Read-Modify-Write instructions. Each I/O line may be

independently programmed as input or output.

Port Structure Figure 1 shows the structure of Ports, which have internal pull-ups. An external source

can pull the pin low. Each Port pin can be configured either for general-purpose I/O or

for its alternate input output function.

To use a pin for general-purpose output, set or clear the corresponding bit in the Px register (x = 1 to 4). To use a pin for general-purpose input, set the bit in the Px register.

This turns off the output FET drive.

To configure a pin for its al ter nat e fun ction, set the bit in the Px register . W hen the l atch

is set, the ’alterna te outpu t funct ion’ sig nal c ontrols the out put lev el (See Figur e 1) . The

operation of Ports is discussed further in ’Quasi-Bi-directional Port Operation’

paragraph.

Figure 1. Ports Structure

VCC

READ

LATCH

ALTERNATE

OUTPUT

FUNCTION

INTERNAL

PULL-UP (1)

P1.x

P2.x

INTERNAL

BUS

WRITE

TO

LATCH

READ

PIN

D

LATCH

CL

Q

ALTERNATE

INPUT

FUNCTION

P3.x

P4.x

Note: 1. The internal pull-up can be disabled on P1 when analog function is selected.

(1)

4126L–CAN–01/08

7

AT/T89C51CC02

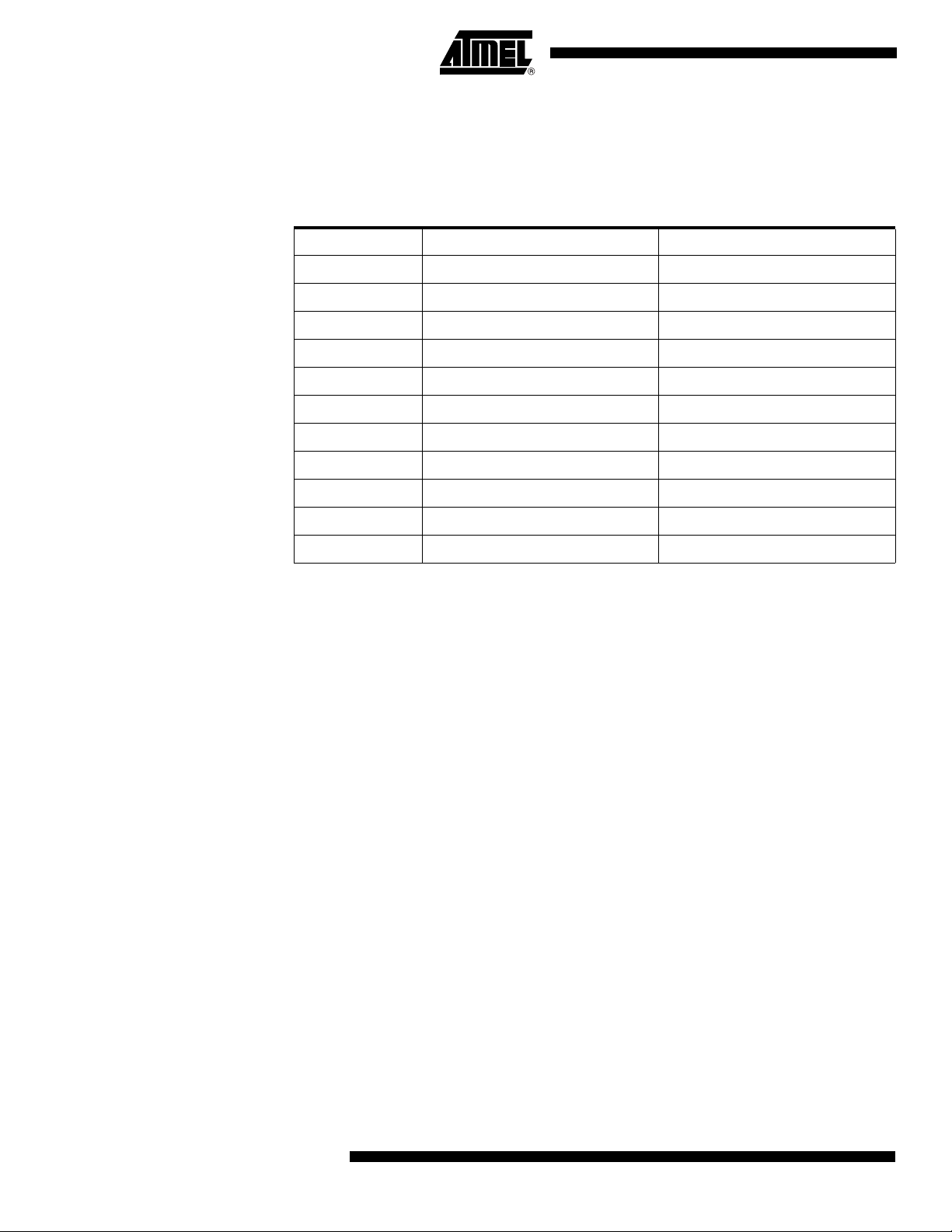

Read-Modify-Write Instructions

Some instructions rea d the l atch data rath er th an the pin da ta. T he latch based inst ructions read the data, m odify the data an d then r ewrit e the latc h. T hese are called ’ReadModify-Write’ instructions. Below is a complete list of these special instructions (See

Table 1). When the destination operand is a Port or a Port bit, these instructions read

the latch rather than the pin:

Table 1. Read/Modify/Write Instructions

Instruction Description Example

ANL Logical AND ANL P1, A

ORL Logical OR ORL P2, A

XRL Logical EX-OR XRL P3, A

JBC Jump if bit = 1 and clear bit JBC P1.1, LABEL

CPL Complement bit CPL P3.0

INC Increment INC P2

DEC Decrement DEC P2

DJNZ Decrement and jump if not zero DJNZ P3, LABEL

MOV Px.y, C Move carry bit to bit y of Port x MOV P1.5, C

CLR Px.y Clear bit y of Port x CLR P2.4

SET Px.y Set bit y of Port x SET P3.3

Quasi Bi-directional Port Operation

It is not obvious t hat t he l as t thr ee in str uc ti ons in thi s lis t a re Rea d -Modify-Write inst ru ctions. These instructions read the port (all 8 bits), modify the specifically addressed bit

and write the new byte back to the latch. These Read-Modify-Write instr uctions are

directed to the latc h rather than the p in in or der to av oid poss ible mi sinterpret ation of

voltage (and there fore, logic) levels at th e pin. For e xampl e, a P ort b it used to dri ve the

base of an external bipolar transistor cannot rise above the transistor’s base-emitter

junction voltage (a v al ue l owe r than VIL). With a logic one wr itt en t o th e bi t, a ttem pts by

the CPU to read the P ort a t the p in are misi nterpret ed as logi c ze ro. A r ead of the l atch

rather than the pins returns the correct logic one value.

Port 1, Port 3 and Port 4 have fixed internal pull-ups and are referred to as ’quasi-bidirectional’ Ports. When configured as an input, the pin impedance appears as logic one

and sources current in response to an external logic zero condition. Resets write logic

one to all Port latch es. If log ical zer o is subs equently w ritten to a P ort latch , it can b e

returned to input conditions by a logic one written to the latch.

Note: Port latch values change near the end of Read-Modify-Write insruction cycles. Output

buffers (and therefore the pin state) are updated early in the instruction after Read-Modify-Write instruction cycle.

Logical zero-to-one transitions in Port 1, Port 3 and Port 4 use an additional pull-up (p1)

to aid this logic tran siti on S ee Fi gure 2. T his in cre ases s witc h s peed. Thi s ext ra p ull-u p

sources 100 times normal internal circuit current during 2 oscillator clock periods. The

internal pull-ups are field-effect transistors rather than linear resistors. Pull-ups consist

of three p-channel FET (pFE T) devi ces. A pFE T is on when th e gate sen ses logic zero

and off when the gate senses log ic one. p FET # 1 is tur ned o n for two osc illator pe riods

immediately after a zero- to-one transition in the Port latc h. A logic one at the Port pin

turns on pFET #3 (a weak pull-up) through the inverter. This inverter and pFET pair form

a latch to drive logic one. pFET #2 is a very weak pull-up switched on whenever the

8

4126L–CAN–01/08

AT/T89C51CC02

associated nFET is switched off. This is tradition al CMOS switch conventio n. Current

strengths are 1/10 that of pFET #3.

Note: During Reset, pFET#1 is not avtivated. During Reset, only the weak pFET#3 pull up the

pin.

Figure 2. Internal Pull-up Configurations

2 Osc. PERIODS

VCCVCCVCC

OUTPUT DATA

INPUT DATA

READ PIN

p1(1)

n

p2

p3

P1.x

P2.x

P3.x

P4.x

4126L–CAN–01/08

9

AT/T89C51CC02

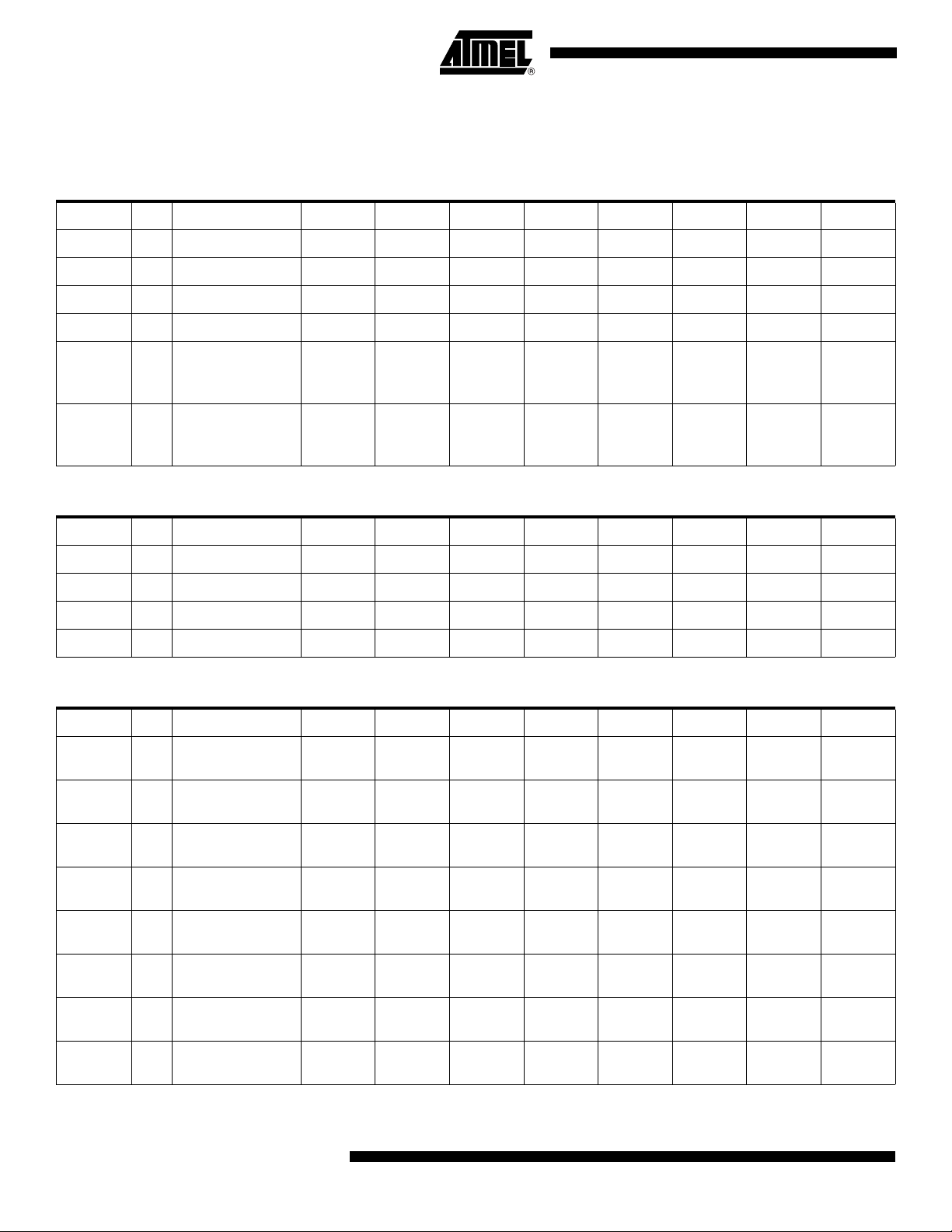

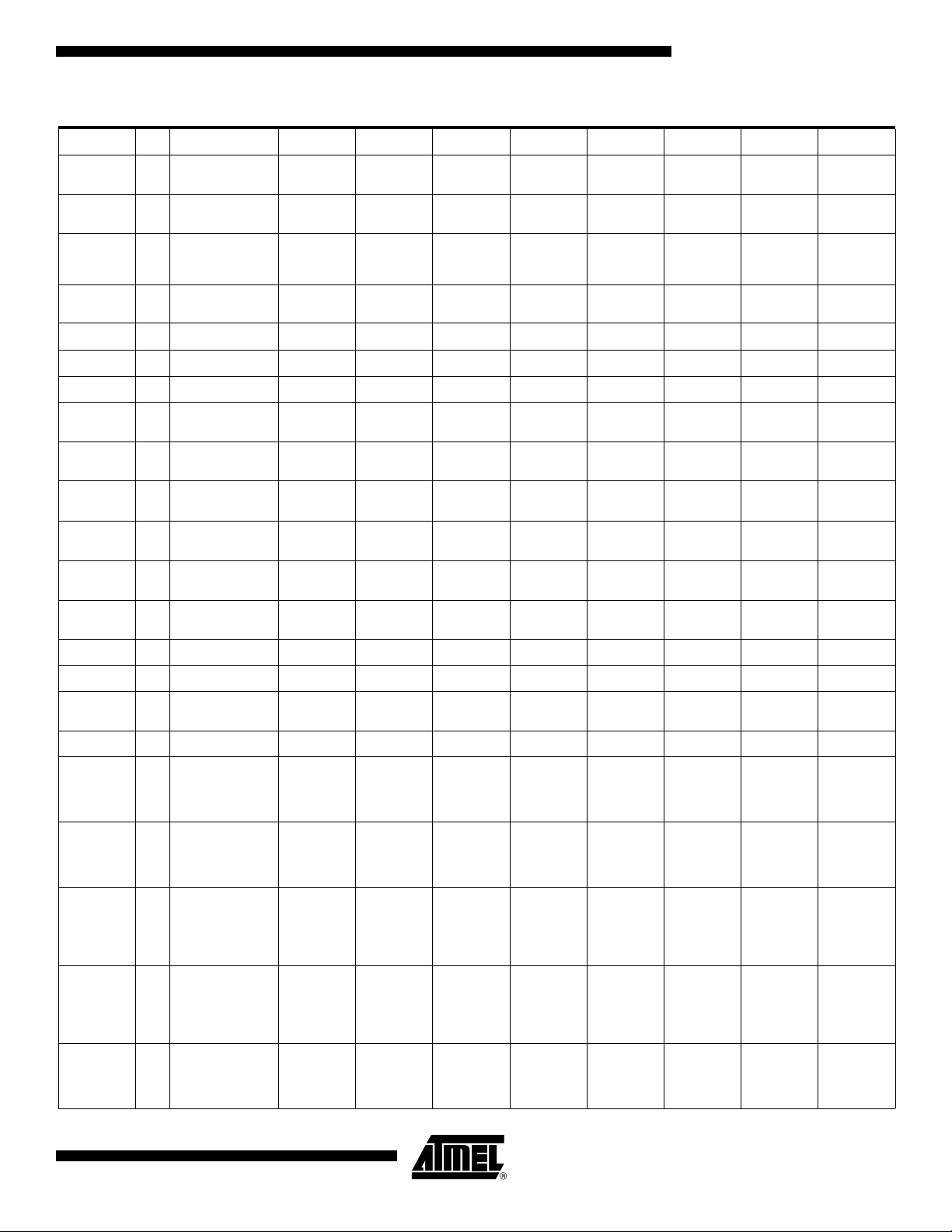

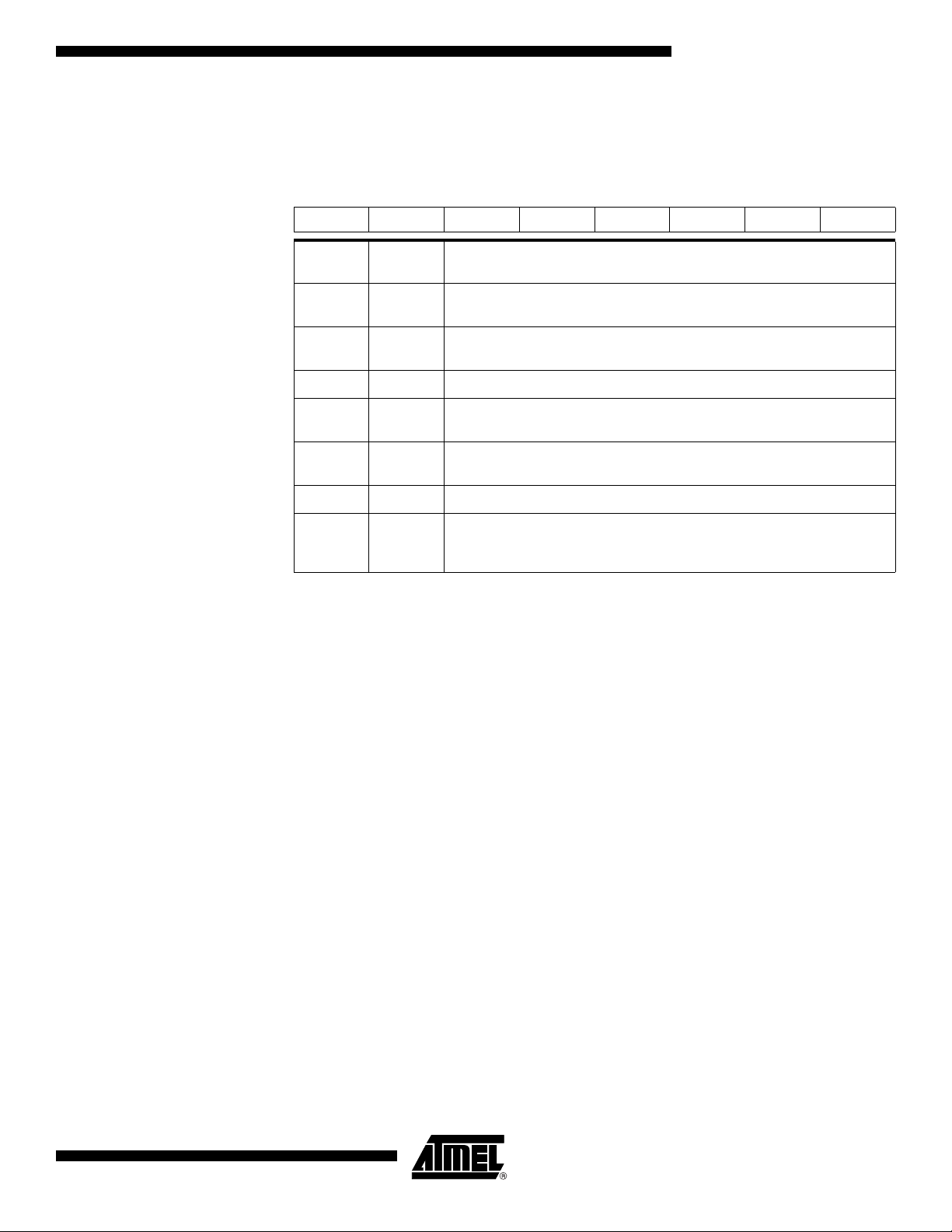

SFR Mapping Tables 3 through Table 11 show the Special Function Registers (SFRs) of the

T89C51CC02.

Table 2. C51 Core SFRs

MnemonicAddName 76543210

ACC E0h Accumulator

B F0h B Register

PSW D0h Program Status Word CY AC F0 RS1 RS0 OV F1 P

SP 81h Stack Pointer

Data Pointer Low

DPL 82h

DPH 83h

Table 3. I/O Port SFRs

MnemonicAddName 76543210

P1 90h Port 1

byte

LSB of DPTR

Data Pointer High

byte

MSB of DPTR

P2 A0h Port 2 (x2)

P3 B0h Port 3

P4 C0h Port 4 (x2)

Table 4. Timers SFRs

MnemonicAddName 76543210

TH0 8Ch

TL0 8Ah

TH1 8Dh

TL1 8Bh

TH2 CDh

TL2 CCh

TCON 88h

Timer/Counter 0 High

byte

Timer/Counter 0 Low

byte

Timer/Counter 1 High

byte

Timer/Counter 1 Low

byte

Timer/Counter 2 High

byte

Timer/Counter 2 Low

byte

Timer/Counter 0 and

1 control

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

TMOD 89h

Timer/Counter 0 and

1 Modes

10

GATE1 C/T1# M11 M 01 GATE0 C/T0# M10 M00

4126L–CAN–01/08

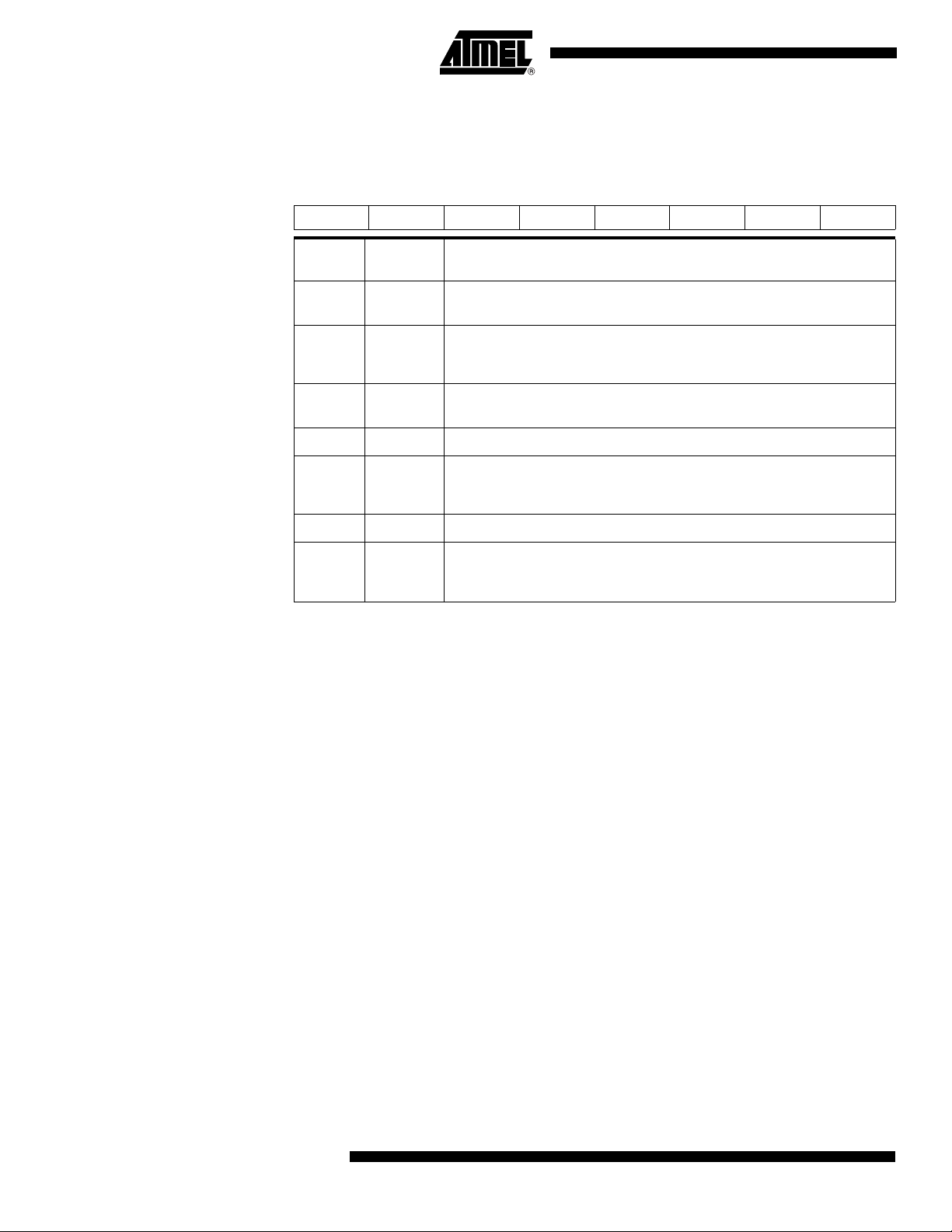

AT/T89C51CC02

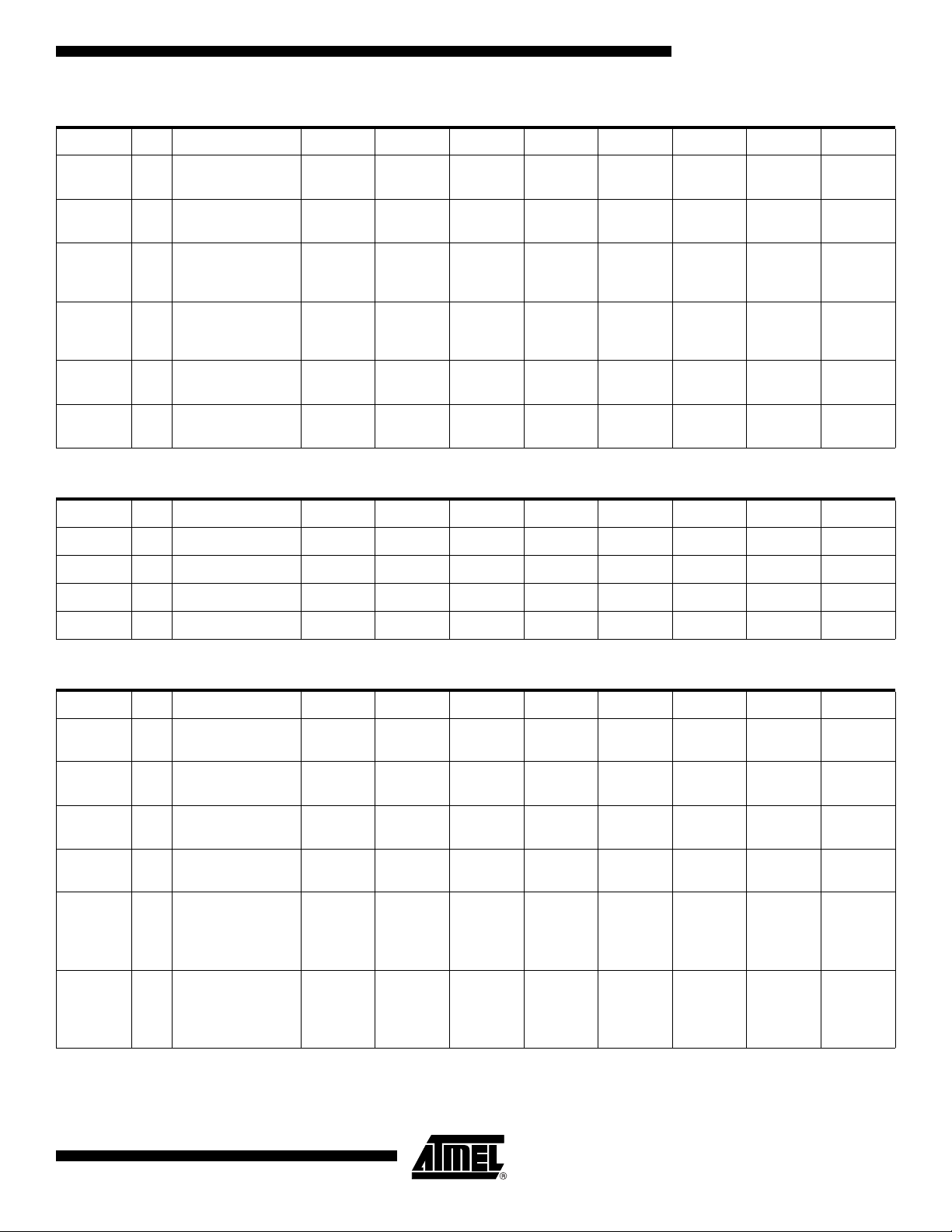

Table 4. Timers SFRs (Continued)

MnemonicAddName 76543210

T2CON C8h

T2MOD C9h

RCAP2H CBh

RCAP2L CAh

WDTRST A6h

WDTPRG A7h

Timer/Counter 2

control

Timer/Counter 2

Mode

Timer/Counter 2

Reload/Capture High

byte

Timer/Counter 2

Reload/Capture Low

byte

WatchDog Timer

Reset

WatchDog Timer

Program

TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2# CP/RL2#

T2OE DCEN

S2 S1 S0

Table 5. Serial I/O Port SFRs

MnemonicAddName 76543210

SCON 98h Serial Cont rol FE/SM0 SM1 SM2 REN TB8 RB8 TI R I

SBUF 99h Serial Data Buffer

SADEN B 9h Slave Address Mask

SADDR A9h Slave Address

Table 6. PCA SFRs

MnemonicAddName 76543210

CCON D8h

CMOD D9h

CL E9h

CH F9h

CCAPM0

CCAPM1

CCAP0H

CCAP1H

DAh

DBh

FAh

FBh

PCA Timer/Counter

Control

PCA Timer/Counter

Mode

PCA Timer/Counter

Low byte

PCA Timer/Counter

High byte

PCA Timer/Counter

Mode 0

PCA Timer/Counter

Mode 1

PCA Compare

Capture Module 0 H

PCA Compare

Capture Module 1 H

CF CR CCF4 CCF3 CCF2 CCF1 CCF0

CIDL CPS1 CPS0 ECF

CCAP0H7

CCAP1H7

ECOM0

ECOM1

CCAP0H6

CCAP1H6

CAPP0

CAPP1

CCAP0H5

CCAP1H5

CAPN0

CAPN1

CCAP0H4

CCAP1H4

MAT0

MAT1

CCAP0H3

CCAP1H3

TOG0

TOG1

CCAP0H2

CCAP1H2

PWM0

PWM1

CCAP0H1

CCAP1H1

CCAP0H0

CCAP1H0

ECCF0

ECCF1

4126L–CAN–01/08

11

AT/T89C51CC02

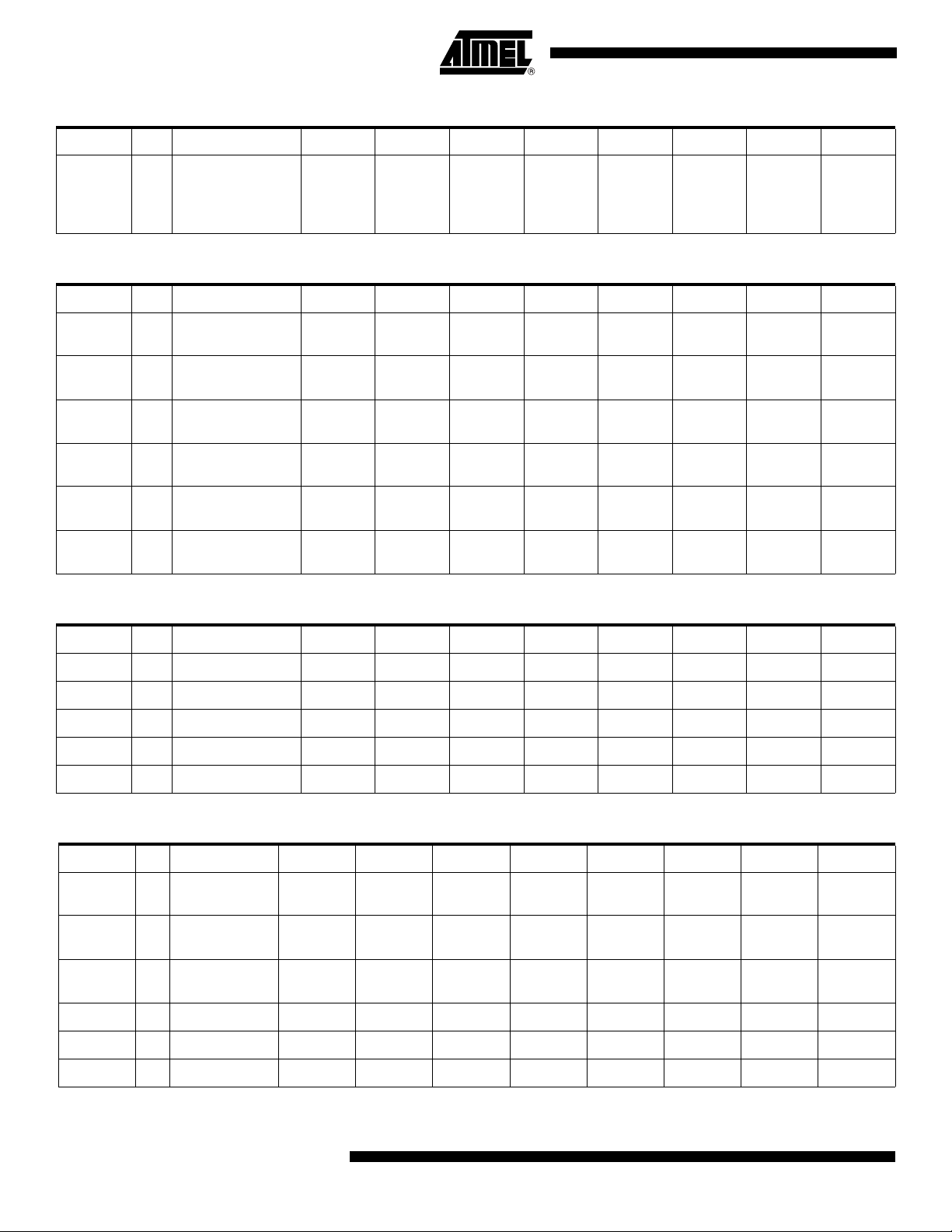

Table 6. PCA SFRs (Continued)

MnemonicAddName 76543210

CCAP0L

CCAP1L

PCA Compare

EAh

Capture Module 0 L

EBh

PCA Compare

Capture Module 1 L

CCAP0L7

CCAP1L7

CCAP0L6

CCAP1L6

CCAP0L5

CCAP1L5

CCAP0L4

CCAP1L4

CCAP0L3

CCAP1L3

CCAP0L2

CCAP1L2

CCAP0L1

CCAP1L1

CCAP0L0

CCAP1L0

Table 7. Interrupt SFRs

MnemonicAddName 76543210

IEN0 A8h

IEN1 E8h

IPL0 B8h

IPH0 B7h

IPL1 F8h

IPH1 F7h

Interrupt Enable

Control 0

Interrupt Enable

Control 1

Interrupt Priorit y

Control Low 0

Interrupt Priorit y

Control High 0

Interrupt Priorit y

Control Low 1

Interrupt Priorit y

Control High1

EA EC ET2 ES ET1 EX1 ET0 EX0

ETIM EADC ECAN

PPC PT2 PS PT1 PX1 PT0 PX0

PPCH PT2H PSH PT1H PX1H PT0H PX0H

POVRL PADCL PCANL

POVRH PADCH PCANH

Table 8. ADC SFRs

MnemonicAddName 76543210

ADCON F3h ADC Control PSIDLE ADEN ADEOC ADSST SCH2 S CH1 SCH0

ADCF F6h ADC Configuration CH7 CH6 CH5 C H4 CH3 CH2 CH 1 CH0

ADCLK F2h ADC Clock PRS4 PRS3 PRS2 PRS1 PRS0

ADDH F5h ADC Data High byte ADAT9 A DAT8 ADAT7 ADAT6 ADAT5 ADAT4 ADAT3 ADAT2

ADDL F4h ADC Data Low byte ADAT1 ADAT0

Table 9. CAN SFRs

MnemonicAddName 76543210

CANGCON ABh

CANGSTA AAh

CANGIT 9Bh

CANBT1 B4h CAN bit Timing 1 BRP5 BRP4 BRP3 BRP2 BRP1 BRP0

CANBT2 B5h CAN bit Timing 2 SJW1 SJW0 PRS2 PRS1 PRS0

CANBT3 B6h CAN bit Timing 3 PHS22 PHS21 PHS20 PHS12 PHS11 PHS10 SMP

CAN General

Control

CAN General

Status

CAN General

Interrupt

ABRQ OVRQ TTC SYNCTTC AUT-BAUD TEST ENA GRES

OVFG TBSY RBSY ENFG BOFF ERRP

CANIT OVRTIM OVRBUF SERG CERG FERG AERG

12

4126L–CAN–01/08

AT/T89C51CC02

Table 9. CAN SFRs (Continued)

MnemonicAddName 76543210

CANEN CFh

CANGIE C1h

CANIE C3h

CANSIT BBh

CANTCON A1h CAN Timer Control TPRESC 7 TPRESC 6 TPRESC 5 TPRESC 4 TPRESC 3 TPRESC 2 TPRESC 1 TPRESC 0

CANTIMH ADh CAN Timer high CANTIM 15 CANTIM 14 CANTIM 13 CANTIM 12 CANTIM 11 CANTIM 10 CANTIM 9 CANTIM 8

CANTIML ACh CAN Timer low CANTIM 7 CANTIM 6 CANTIM 5 CANTIM 4 CANTIM 3 CANTIM 2 CANTIM 1 CANTIM 0

CANSTMPH AFh

CANSTMPL AEh

CANTTCH A5h

CANTTCL A4h CAN Timer TTC low

CANTEC 9Ch

CANREC 9Dh

CAN Enable

Channel byte

CAN General

Interrupt Enable

CAN Interrupt

Enable Channel

byte

CAN Status Interrupt

Channel byte

CAN Timer Stamp

high

CAN Timer Stamp

low

CAN Timer TTC

high

CAN Transmit Error

Counter

CAN Receive Error

Counter

ENCH3 ENCH2 ENCH1 ENCH0

ENRX ENTX ENERCH ENBUF ENERG

IECH3 IE CH2 IECH1 IECH0

SIT3 SIT2 SIT1 SIT0

TIMSTMP 15TIMSTMP 14TIMSTMP 13TIMSTMP

TIMSTMP7 TIMSTMP 6 TIMSTMP 5 TIMSTMP 4 TIMSTMP 3 TIMSTMP 2 TIMSTMP 1 TIMSTMP 0

TIMTTC 15 TIMTTC 14 TIMTTC 13 TIMTTC 12 TIMTTC 11 TIMTTC 10

TIMTTC

7

TEC7 TEC6 TEC5 TEC4 TEC3 TEC2 TEC1 TEC0

REC7 REC6 REC5 REC4 REC3 REC2 REC1 REC0

TIMTTC

6

TIMTTC

5

12

TIMTTC

4

TIMSTMP 11

TIMTTC

3

TIMSTMP

10

TIMTTC

2

TIMSTMP 9 TIMSTMP 8

TIMTTC

9

TIMTTC

1

TIMTTC

8

TIMTTC

0

CANPAGE B1h CAN Page - - CHNB1 CHNB0 AINC INDX2 INDX1 INDX0

CANSTCH B2h CAN Stat us Channel DLCW TXOK RXOK BERR SERR CERR FERR AERR

CANCONCH B3h

CANMSG A3h CAN Message Data MSG7 MSG6 MSG5 MSG4 MSG3 MSG2 MSG1 MSG0

CANIDT1 BCh

CANIDT2 BDh

CANIDT3 BE h

CANIDT4 BFh

CANIDM1 C4h

CAN Control

Channel

CAN Identifier Tag

byte 1(Part A)

CAN Identifier Tag

byte 1(PartB)

CAN Identifier Tag

byte 2 (PartA)

CAN Identifier Tag

byte 2 (PartB)

CAN Identifier

Tag byte 3(PartA)

CAN Identifier

Tag byte 3(PartB)

CAN Identifier

Tag byte 4(PartA)

CAN Identifier

Tag byte 4(PartB)

CAN Identifier Mask

byte 1(PartA)

CAN Identifier Mask

byte 1(PartB)

CONCH1 CONCH0 RPLV IDE DLC3 DLC2 DLC1 DLC0

IDT10

IDT28

IDT2

IDT20

-

IDT12

-

IDT4

IDMSK10

IDMSK28

IDT9

IDT27

IDT1

IDT19

-

IDT11

-

IDT3

IDMSK9

IDMSK27

IDT8

IDT26

IDT0

IDT18

-

IDT10

-

IDT2

IDMSK8

IDMSK26

IDT7

IDT25

-

IDT17

-

IDT9

-

IDT1

IDMSK7

IDMSK25

IDT6

IDT24

-

IDT16

-

IDT8

-

IDT0

IDMSK6

IDMSK24

IDT5

IDT23

-

IDT15

-

IDT7

RTRTAG

IDMSK5

IDMSK23

IDT4

IDT22

-

IDT14

-

IDT6

-

RB1TAG

IDMSK4

IDMSK22

IDT3

IDT21

-

IDT13

-

IDT5

RB0TAG

IDMSK3

IDMSK21

4126L–CAN–01/08

13

AT/T89C51CC02

Table 9. CAN SFRs (Continued)

MnemonicAddName 76543210

CANIDM2 C5h

CANIDM3 C6h

CANIDM4 C7h

CAN Identifier Mask

byte 2(PartA)

CAN Identifier Mask

byte 2(PartB)

CAN Identifier Mask

byte 3(PartA)

CAN Identifier Mask

byte 3(PartB)

CAN Identifier Mask

byte 4(PartA)

CAN Identifier Mask

byte 4(PartB)

IDMSK2

IDMSK20

-

IDMSK12

-

IDMSK4

IDMSK1

IDMSK19

-

IDMSK11-IDMSK10

-

IDMSK3

IDMSK0

IDMSK18

-

IDMSK2

-

IDMSK17-IDMSK16-IDMSK15-IDMSK14-IDMSK13

-

IDMSK9

-

IDMSK1

-

IDMSK8

-

IDMSK0

-

IDMSK7

RTRMSK - IDEMSK

-

IDMSK6

-

IDMSK5

Table 10. Other SFRs

MnemonicAddName 76543210

PCON 87h Power Cont rol SMOD1 SMOD0 POF GF1 GF0 PD IDL

AUXR1 A2h Auxiliary Register 1 ENBOOT GF3 0 DPS

CKCON 8Fh Clock Control CANX2 WDX2 PCAX2 SIX2 T2X2 T1X2 T0X2 X2

FCON D1h Flash Control FPL3 FPL2 FPL1 FPL0 FPS FMOD1 FMOD0 FBUSY

EECON D2h EEPROM Contol EEPL3 EEPL2 EEPL1 EEPL0 EEE EEBUSY

14

4126L–CAN–01/08

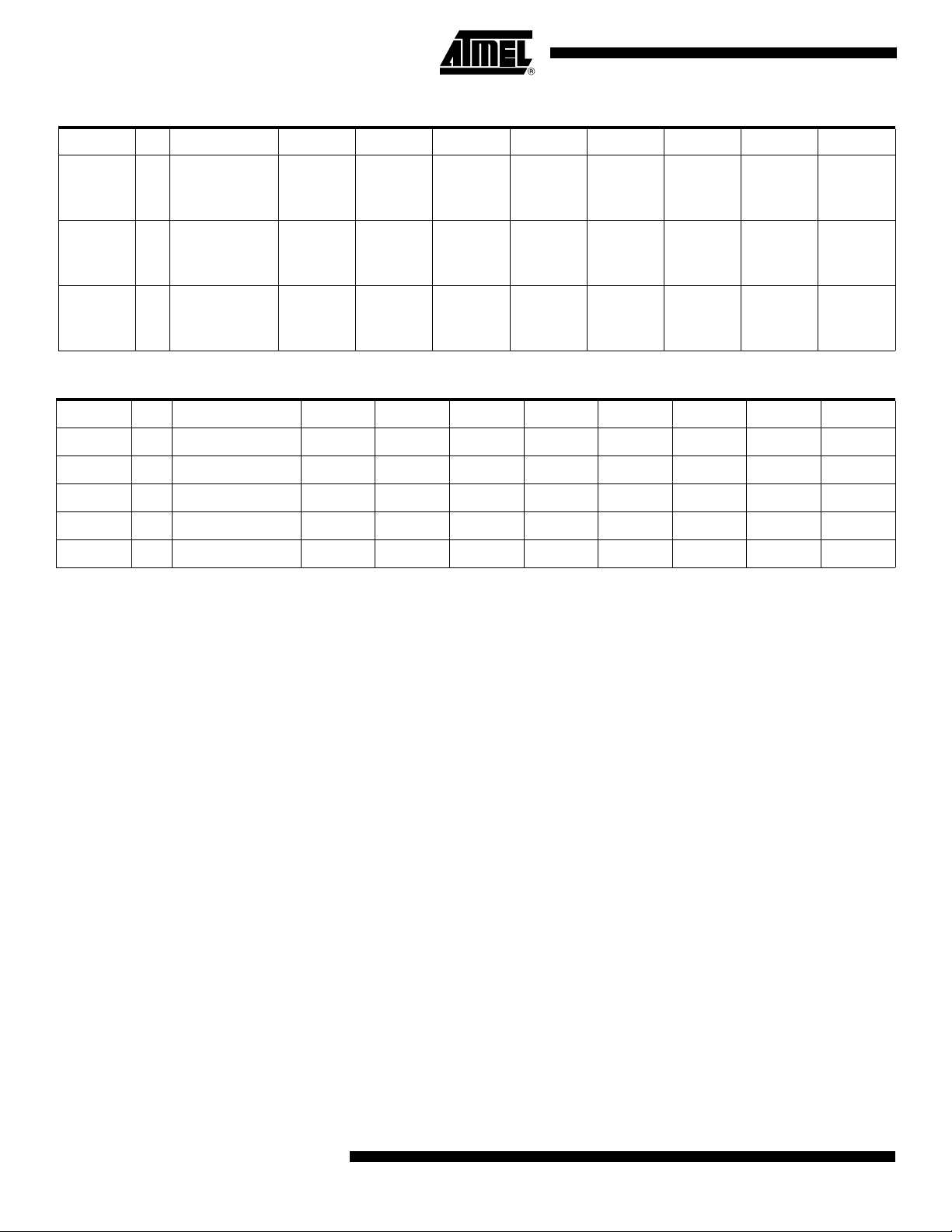

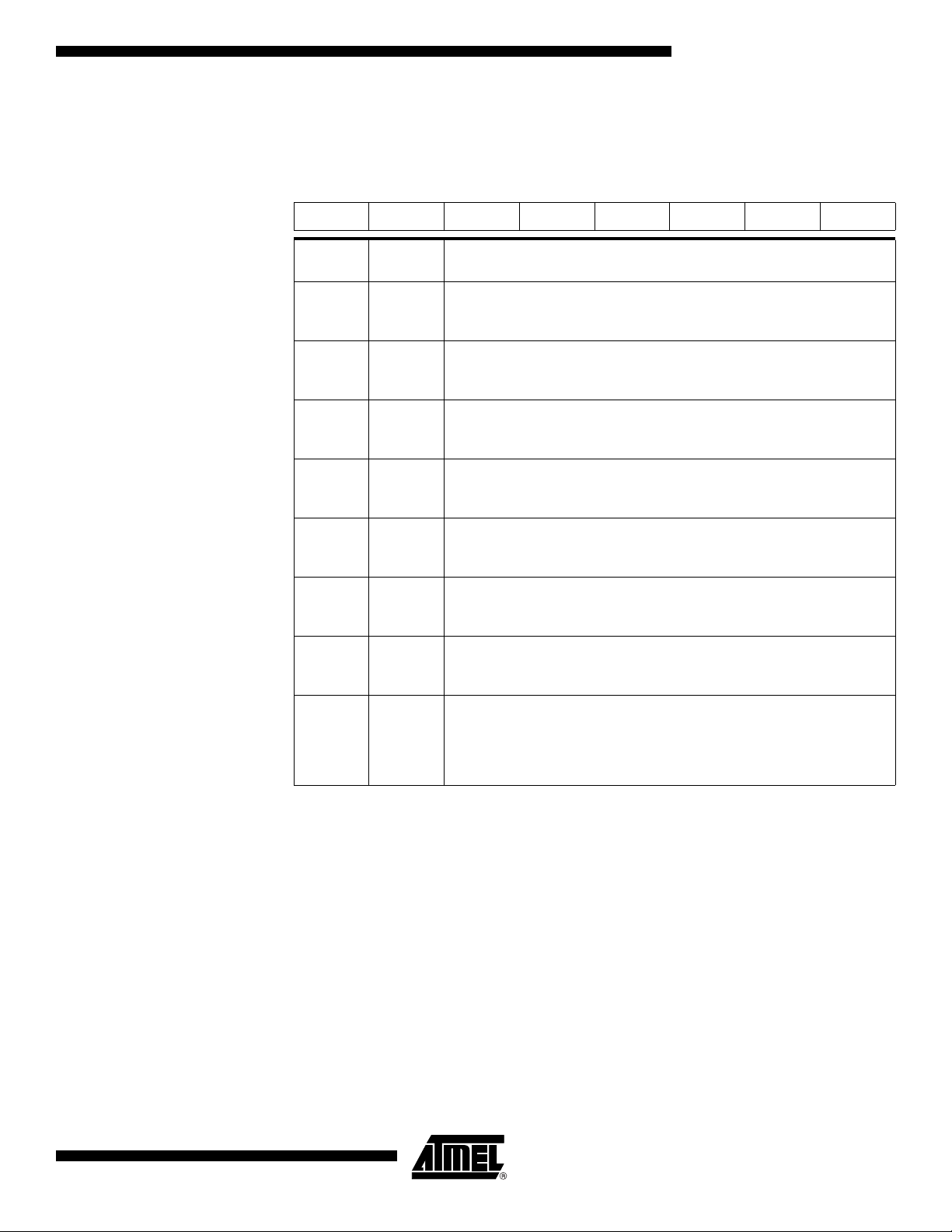

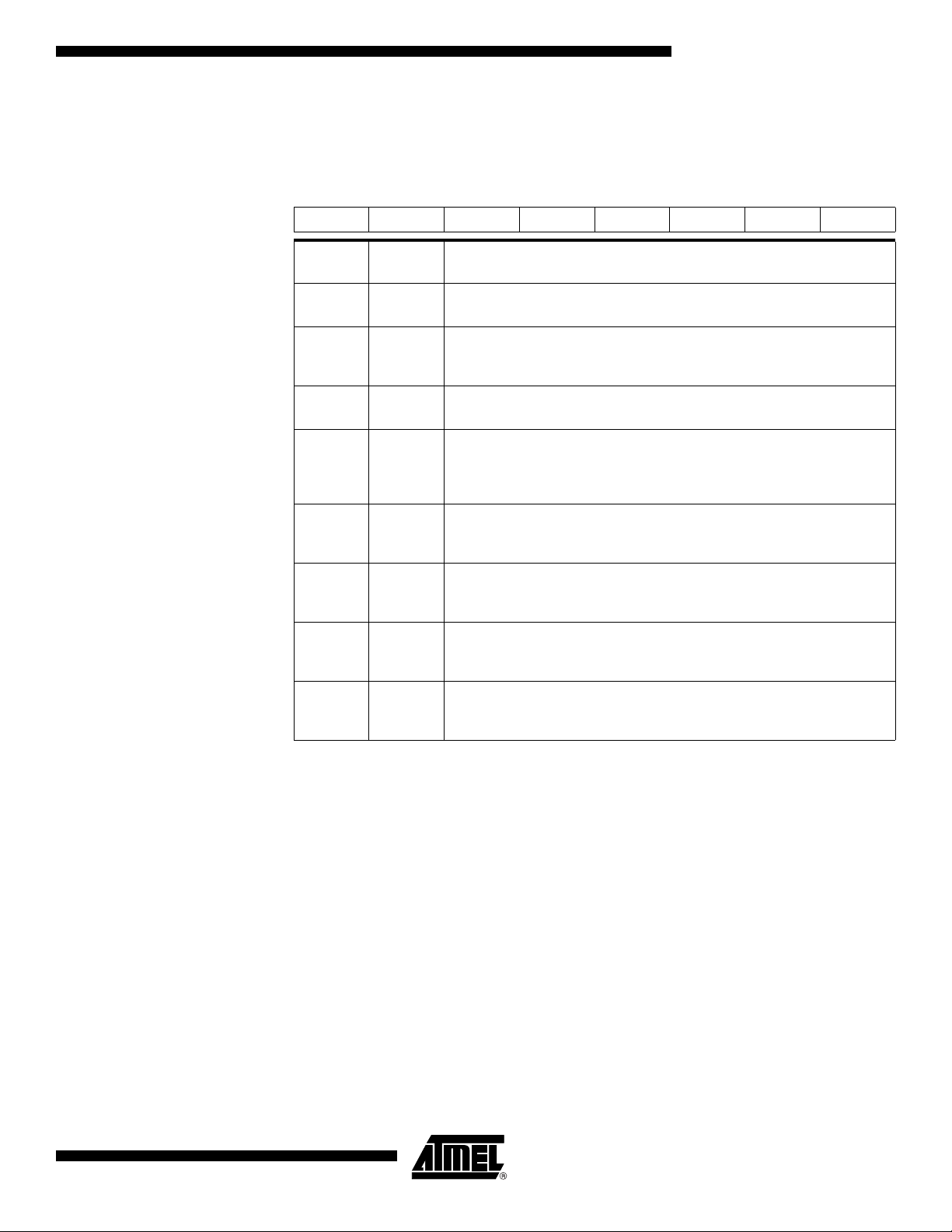

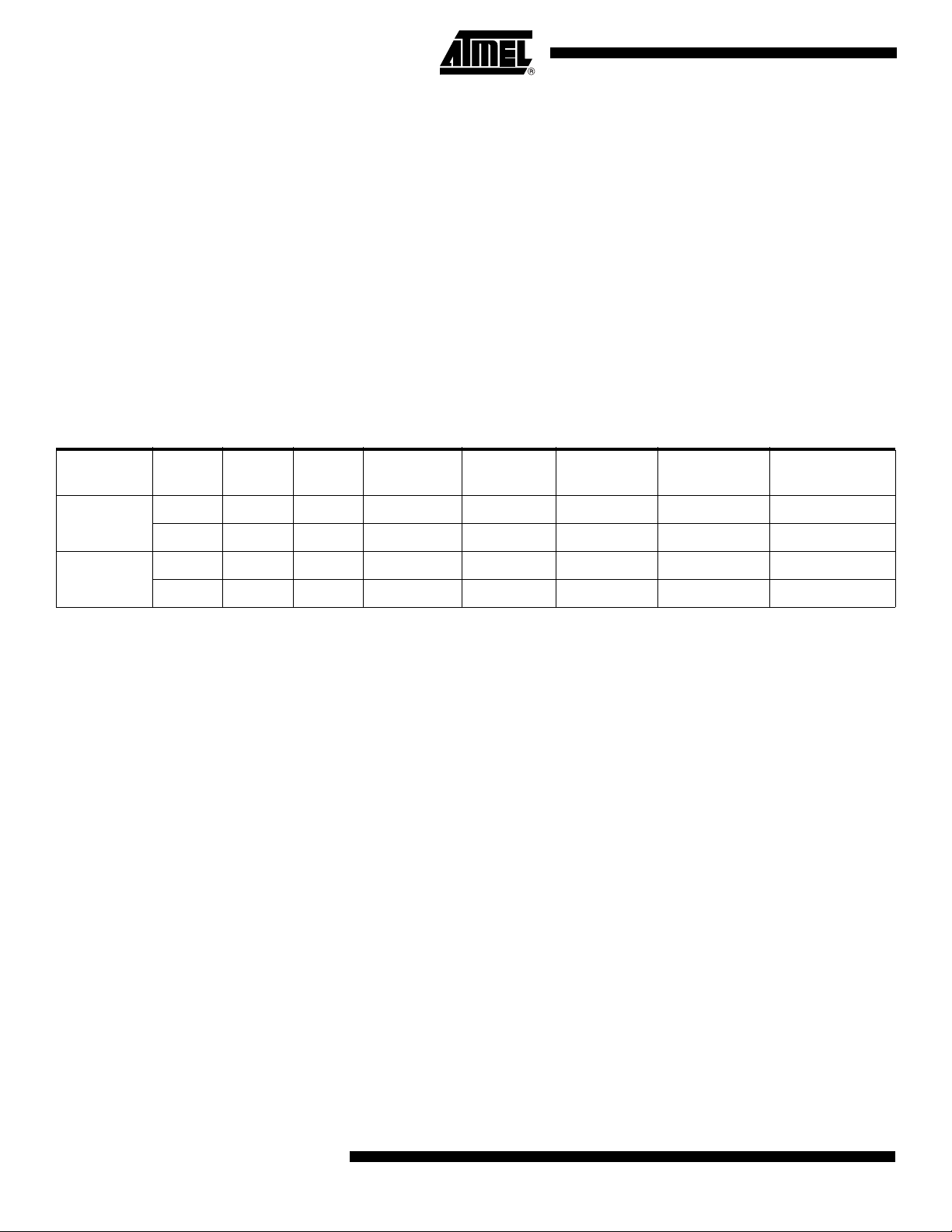

Table 11. SFR Mapping

(1)

0/8

AT/T89C51CC02

1/9 2/A 3/B 4/C 5/D 6/E 7/F

F8h

F0h

E8h

E0h

D8h

D0h

C8h

C0h

B8h

B0h

A8h

A0h

IPL1

xxxx x000

B

0000 0000

IEN1

xxxx x000

ACC

0000 0000

CCON

0000 0000

PSW

0000 0000

T2CON

0000 0000

P4

xxxx xx11

IPL0

x000 0000

P3

1111 1111

IEN0

0000 0000

P2

xxxx xx11

CH

0000 0000

CL

0000 0000

CMOD

0xxx x000

FCON

0000 0000

T2MOD

xxxx xx00

CANGIE

1100 0000

SADEN

0000 0000

CANPAGE

1100 0000

SADDR

0000 0000

CANTCON

0000 0000

CCAP0H

0000 0000

ADCLK

xxx0 0000

CCAP0L

0000 0000

CCAPM0

x000 0000

EECON

xxxx xx00

RCAP2L

0000 0000

CANSTCH

xxxx xxxx

CANGSTA

1010 0000

(2)

AUXR1

xxxx 00x0

CCAP1H

0000 0000

ADCON

x000 0000

CCAP1L

0000 0000

CCAPM1

x000 0000

RCAP2H

0000 0000

CANIE

1111 0000

CANSIT

xxxx 0000

CANCONCH

xxxx xxxx

CANGCON

0000 0000

CANMSG

xxxx xxxx

ADDL

0000 0000

TL2

0000 0000

CANIDM1

xxxx xxxx

CANIDT1

xxxx xxxx

CANBT1

xxxx xxxx

CANTIML

0000 0000

CANTTCL

0000 0000

ADDH

0000 0000

TH2

0000 0000

CANIDM2

xxxx xxxx

CANIDT2

xxxx xxxx

CANBT2

xxxx xxxx

CANTIMH

0000 0000

CANTTCH

0000 0000

ADCF

0000 0000

CANIDM3

xxxx xxxx

CANIDT3

xxxx xxxx

CANBT3

xxxx xxxx

CANSTMPL

xxxx xxxx

WDTRST

1111 1111

IPH1

xxxx x000

CANEN

xxxx 0000

CANIDM4

xxxx xxxx

CANIDT4

xxxx xxxx

IPH0

x000 0000

CANSTMPH

xxxx xxxx

WDTPRG

xxxx x000

FFh

F7h

EFh

E7h

DFh

D7h

CFh

C7h

BFh

B7h

AFh

A7h

98h

90h

88h

80h

SCON

0000 0000

P1

1111 1111

TCON

0000 0000

(1)

0/8

SBUF

0000 0000

TMOD

0000 0000

SP

0000 0111

1/9 2/A 3/B 4/C 5/D 6/E 7/F

TL0

0000 0000

DPL

0000 0000

Reserved

Notes: 1. These registers are bit-addressable.

Sixteen addresses in the SFR space are both byte-addressable and bit-addressable. The bit-addressable SFRs are those

whose address ends in 0 and 8. The bit addresses, in this area, are 0x80 through to 0xFF.

2. AUXR1 bit ENBOOT is initialized with the content of the BLJB bit inverted.

4126L–CAN–01/08

CANGIT

0x00 0000

TL1

0000 0000

DPH

0000 0000

CANTEC

0000 0000

TH0

0000 0000

CANREC

0000 0000

TH1

0000 0000

CKCON

0000 0000

PCON

00x1 0000

9Fh

97h

8Fh

87h

15

AT/T89C51CC02

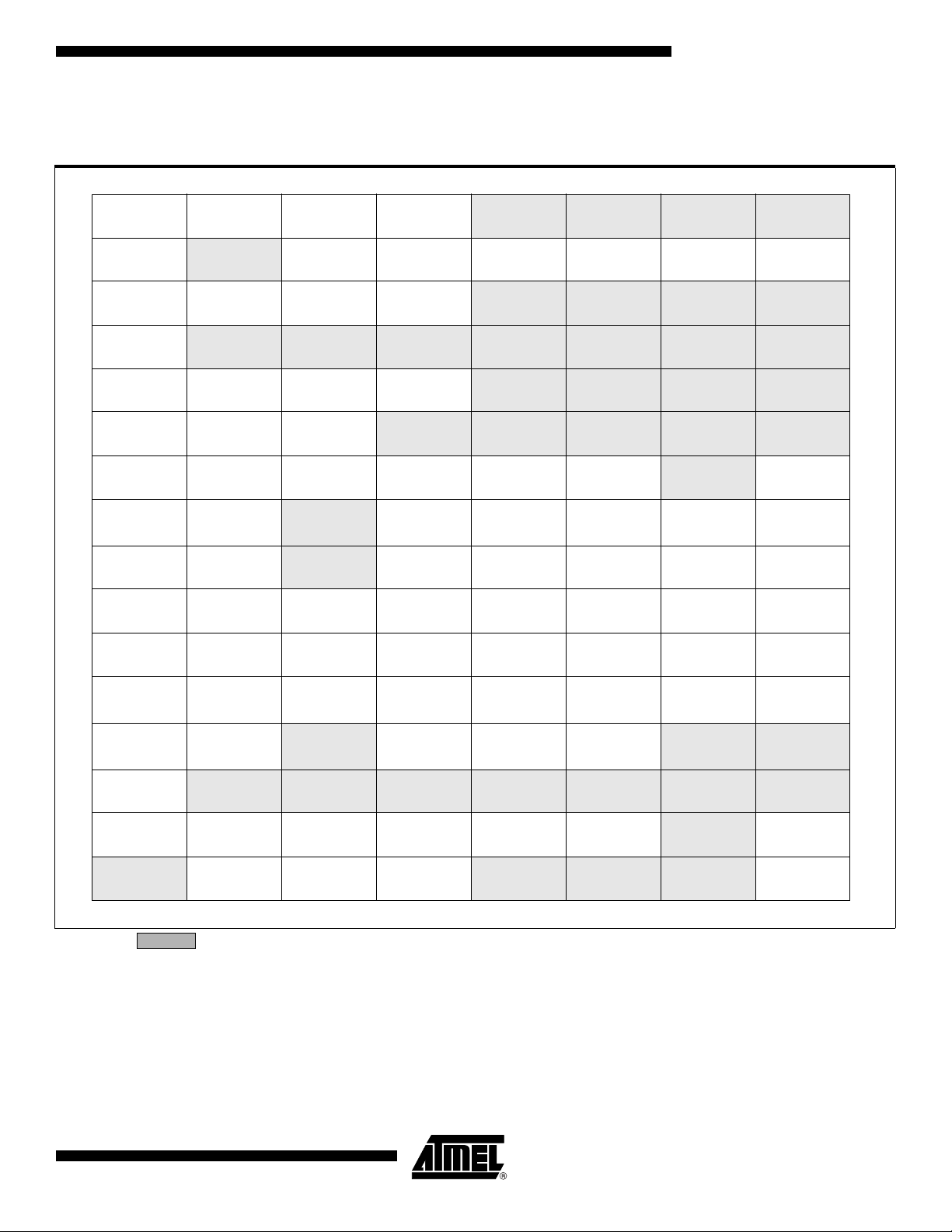

Clock The T89C51CC02 core needs only 6 clock periods per machine cycle. This feature,

called “X2”, provides the following advantages:

• Divides frequency crystals by 2 (cheaper crystals) while keeping the same CPU

power.

• Saves power consumption while keeping the same CPU power (oscillator power

saving).

• Saves power consumption by dividing dynamic operating frequency by 2 in

operating and idle modes.

• Increases CPU power by 2 while keeping the same crystal frequency.

In order to keep the ori ginal C51 com patibil ity, a divider -by-2 is in serted betwe en the

XTAL1 signal and the main clock input of the core (phase generator). This divider may

be disabled by the software.

An extra feature is available to start after Reset in the X2 Mode. This feature can be

enabled by a bit X2B in the Hardware Sec urity Byte. Thi s bit is described in the section

’In-System Programming’.

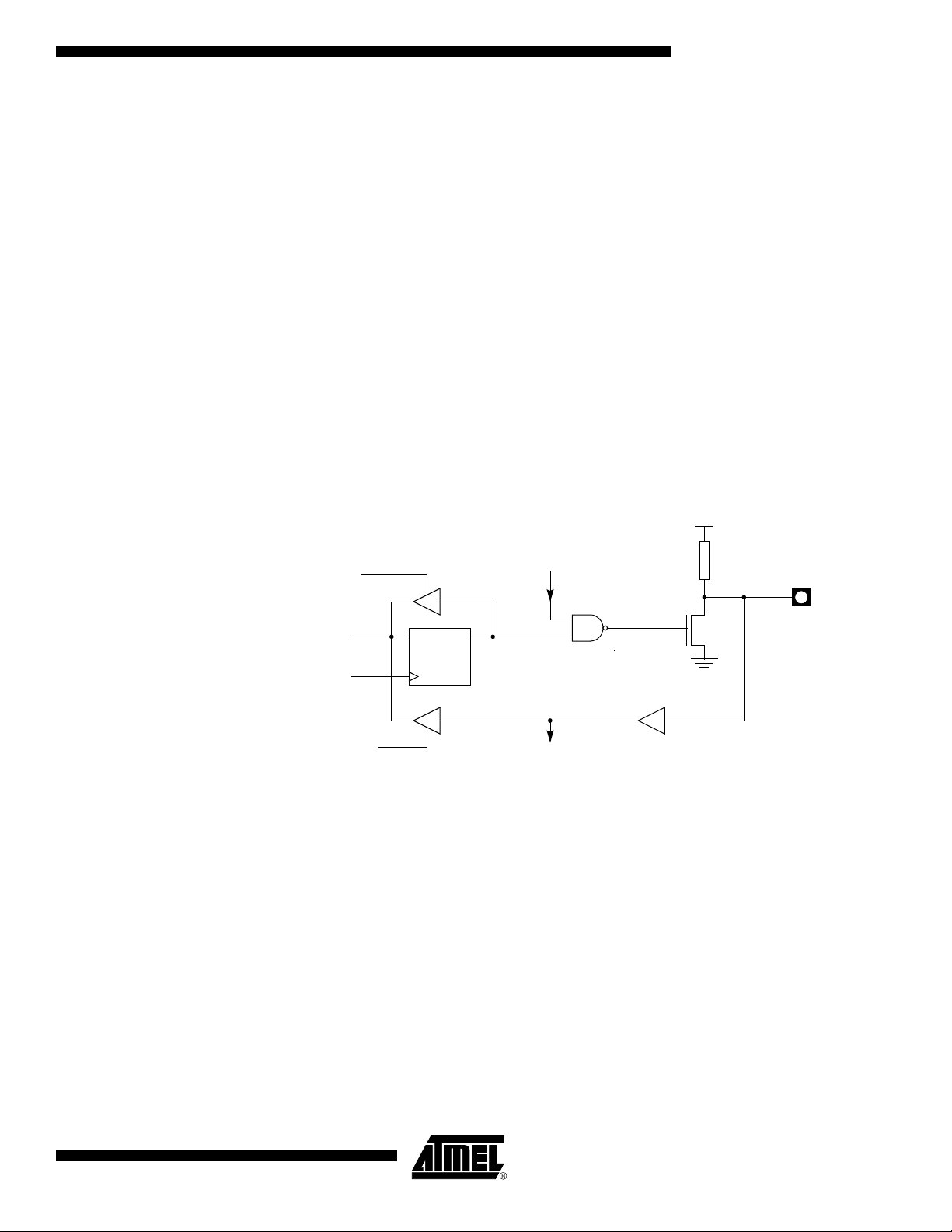

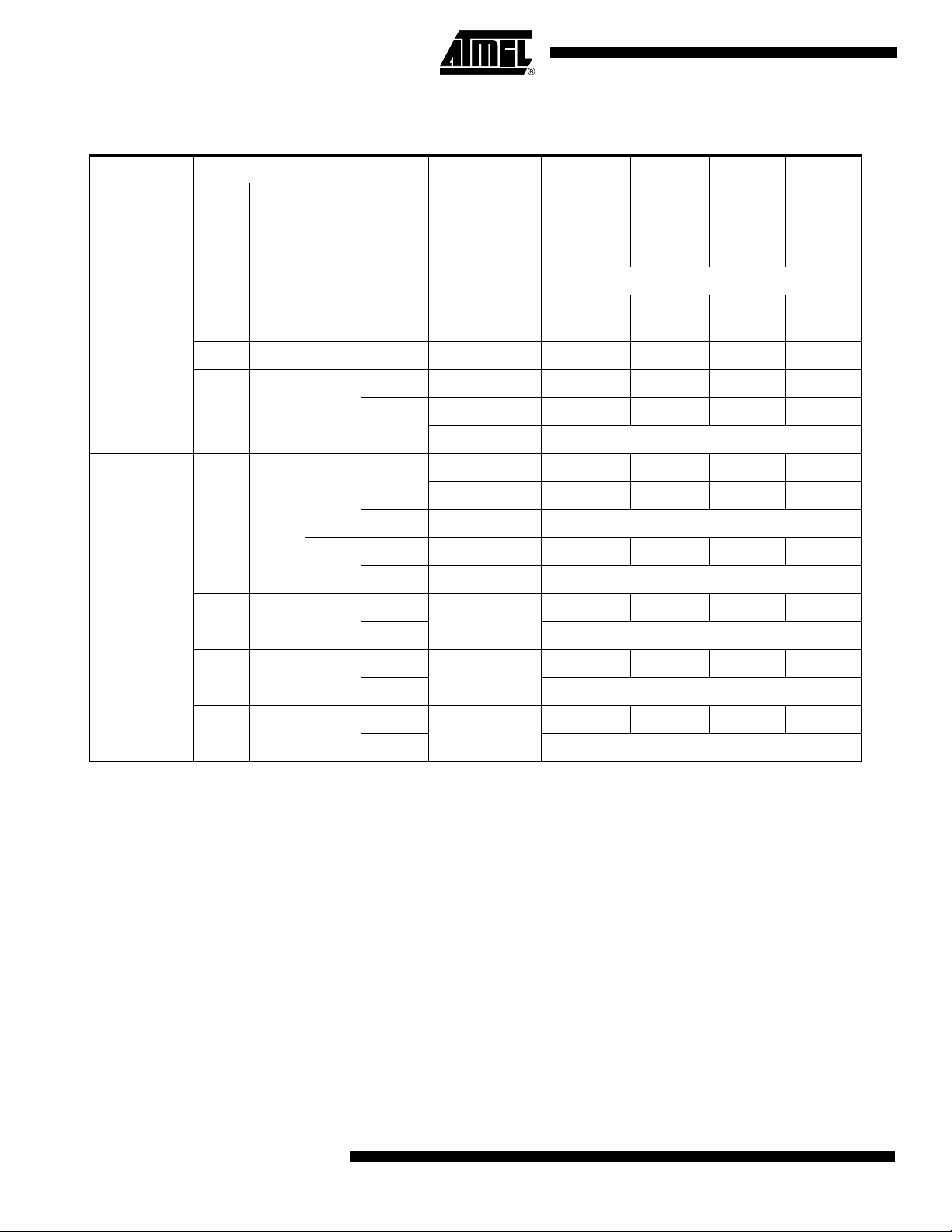

Description The X2 bit in the CKCON regi ster (See T able 12) allows switching from 12 clock cycles

per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated

(STD mode).

Setting this bit activates the X2 feature (X2 Mode) for the CPU Clock only (See Figure

3).

The Timers 0, 1 and 2, Uart, PCA, watchdog or CAN switch in X2 Mode only if the corresponding bit is cleared in the CKCON register.

The clock for the whole circuit and peripheral is first divided by two before being used by

the CPU core and peripherals. This allows any cyclic ratio to be accepted on the XTAL1

input. In X2 Mode, as thi s divid er is bypas s ed, t he s ig nal s o n XTA L1 m us t hav e a cy clic

ratio between 40 to 60%. Figure 3. shows the clock generation block diagram. The X2

bit is validat ed on th e XTAL1 ÷ 2 rising edge to avoid glitches when switching from the

X2 to the STD mode. Figure 4 shows the mode switching waveforms.

16

4126L–CAN–01/08

Figure 3. Clock CPU Generation Diagram

X

X

AT/T89C51CC02

X2B

Hardware Byte

On RESET

PCON.0

IDL

X2

CKCON.0

TAL1

÷ 2

0

1

CPU Core

Clock

TAL2

CPU

CLOCK

PD

PCON.1

÷ 2

÷ 2

÷ 2

÷ 2

÷ 2

÷ 2

1

0

÷ 2

1

0

1

0

1

0

1

0

1

0

CPU Core Clock Symbol

and ADC

1

0

FT0 Clock

FT1 Clock

FT2 Clock

FUart Clock

FPca Cloc k

FWd Clock

FCan Clock

4126L–CAN–01/08

X2

CKCON.0

CANX2

CKCON.7

WDX2

CKCON.6

PCAX2

CKCON.5

SIX2

CKCON.4

T2X2

CKCON.3

T1X2

CKCON.2

PERIPH

CLOCK

Peripheral Clock Symbol

T0X2

CKCON.1

17

AT/T89C51CC02

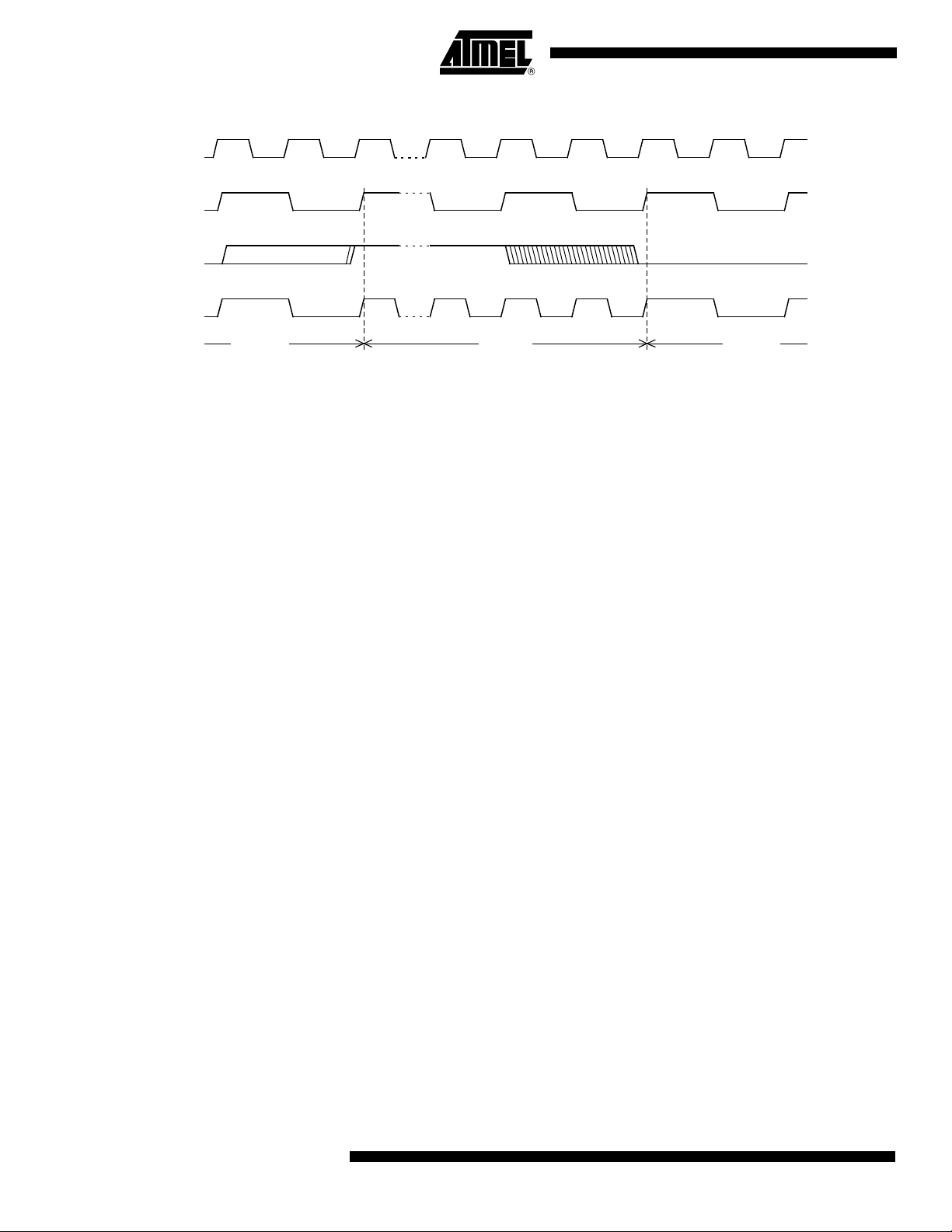

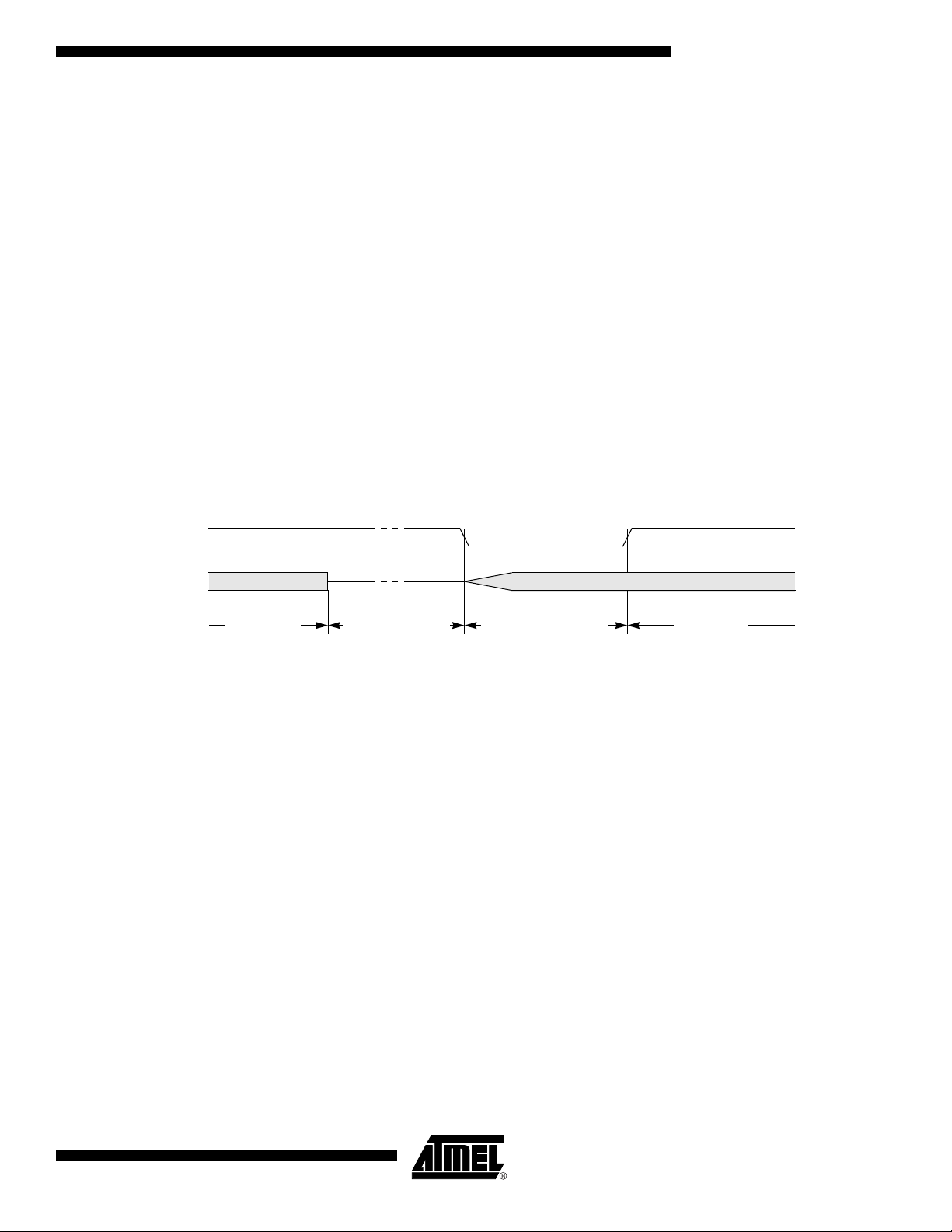

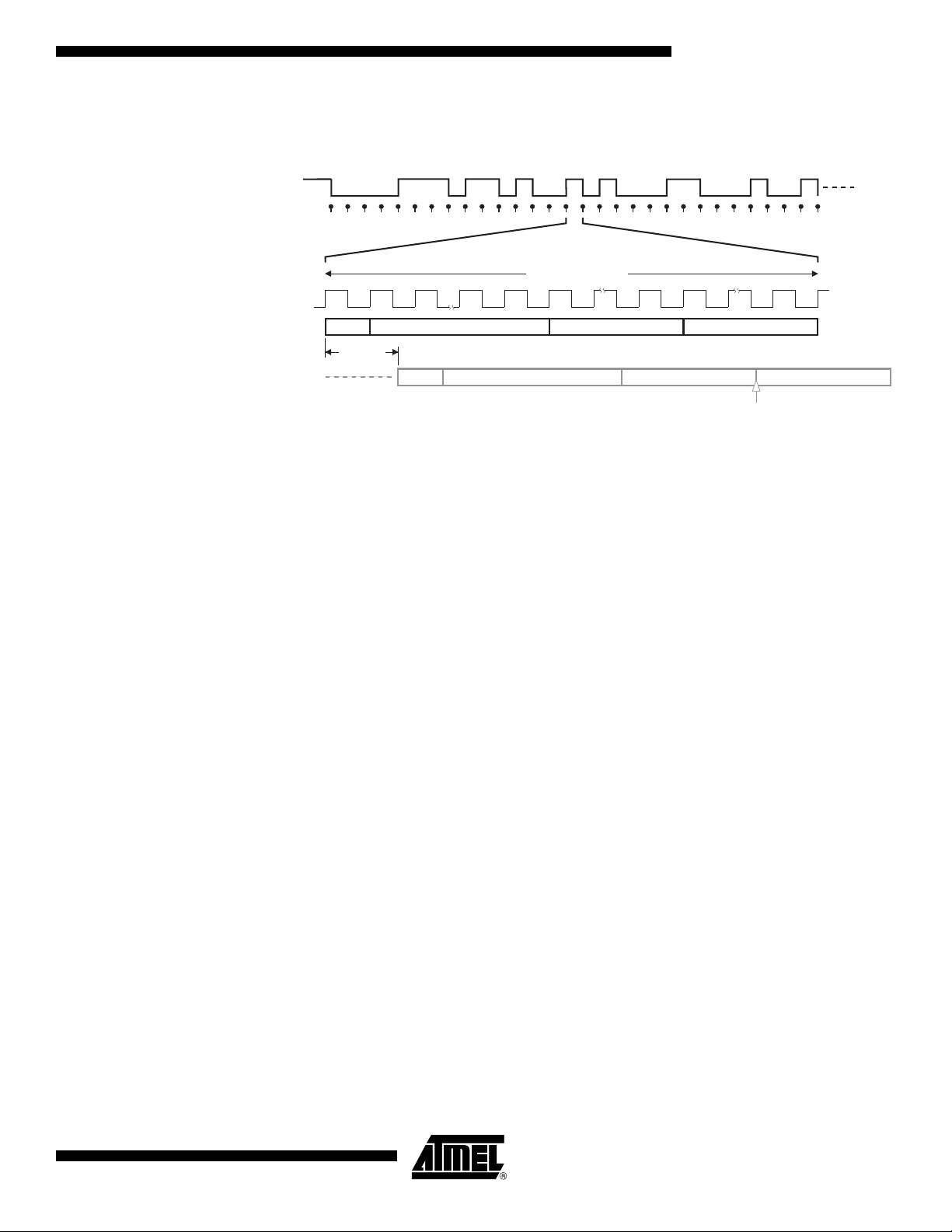

Figure 4. Mode Switching Waveforms

XTAL1

XTAL2

X2 bit

CPU

clock

STD

Mode

(1)

X2

Mode

STD

Mode

Note: 1. In order to prevent any incorrect operation while operating in the X2 Mode, users must be aware that all peripherals using

the clock frequency a s a time ref erence (UAR T, timers...) will have their time referen ce div ided b y 2. Fo r example , a free ru nning timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms. A UART with a 4800 baud rate

will have a 9600 baud rate.

18

4126L–CAN–01/08

Register Table 12. CKCON Register

CKCON (S:8Fh)

Clock Control Register

76543210

CANX2 WDX2 PCAX2 SIX2 T 2X2 T1X2 T0X2 X2

AT/T89C51CC02

Bit

Number

7CANX2

6WDX2

5PCAX2

4SIX2

3T2X2

2T1X2

1T0X2

Bit

Mnemonic Description

CAN Clock

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Watchdog Clock

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Programmable Counter Array Cloc k

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Enhanced UART clock (MODE 0 and 2)

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Timer 2 Clock

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Timer 1 Clock

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Timer 0 Clock

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

(1)

(1)

(1)

(1)

(1)

(1)

(1)

4126L–CAN–01/08

CPU Clock

0X2

Clear to select 12 clock periods per machine cycle (STD mode) for CPU and all

the peripherals.

Set to select 6 clock periods per machine cycle (X2 Mode) and to enable the

individual peripherals ’X2’ bits.

Note: 1. This control bit is validated when the CPU clock bit X2 is set; when X2 is low, this bit

has no effect.

Reset Value = 0000 0000b

19

AT/T89C51CC02

Power Management Two power reduction modes are implemented in the A/T89C51CC02: the Idle mode and

0

the Power-do wn mode . These modes ar e detai led in th e follo wing se ction s. In ad dition

to these power redu cti on mo des , t he cl oc ks o f th e c ore and peripherals can be dy nam ically divided by 2 using the X2 Mode detailed in Section “Clock”.

Reset Pin In order to start- up (c old re se t) or to res tart (warm rese t) pro perly the m icroc ontroll er, a

high level has to be applied on the RST pin. A bad level leads to a wrong initialisation of

the internal registers like S F Rs, P C, etc . and to unp re dicta ble behavior of the microcontroller. A warm reset ca n be applied either dir ectly o n the RST pin or indire ctly by an

internal reset source such as a watchdog, PCA, timer, etc.

At Power-up (cold reset) Two conditions are required before enabling a CPU start-up:

• VDD must reach the specified VDD range,

• The level on xtal1 input must be outside the specification (VIH, VIL).

If one of these two conditions are not met, the microcontroller d oes not start cor rectly

and can execute an instruct ion fetch fro m anywhe re in the progr am spac e. An active

level applied on the RST pin must be mainta ined unti l both of th e above c onditi ons are

met. A reset is active wh en the lev el VIH1 is reached an d when the pu lse wid th covers

the period of time where VDD and the oscillator are not stabilized. Two parameters have

to be taken into account to determine the reset pulse width:

• VDD rise time (vddrst),

• Oscillator startup time (oscrst).

To determine the capacitor the highest value of these two parameters has to be chosen.

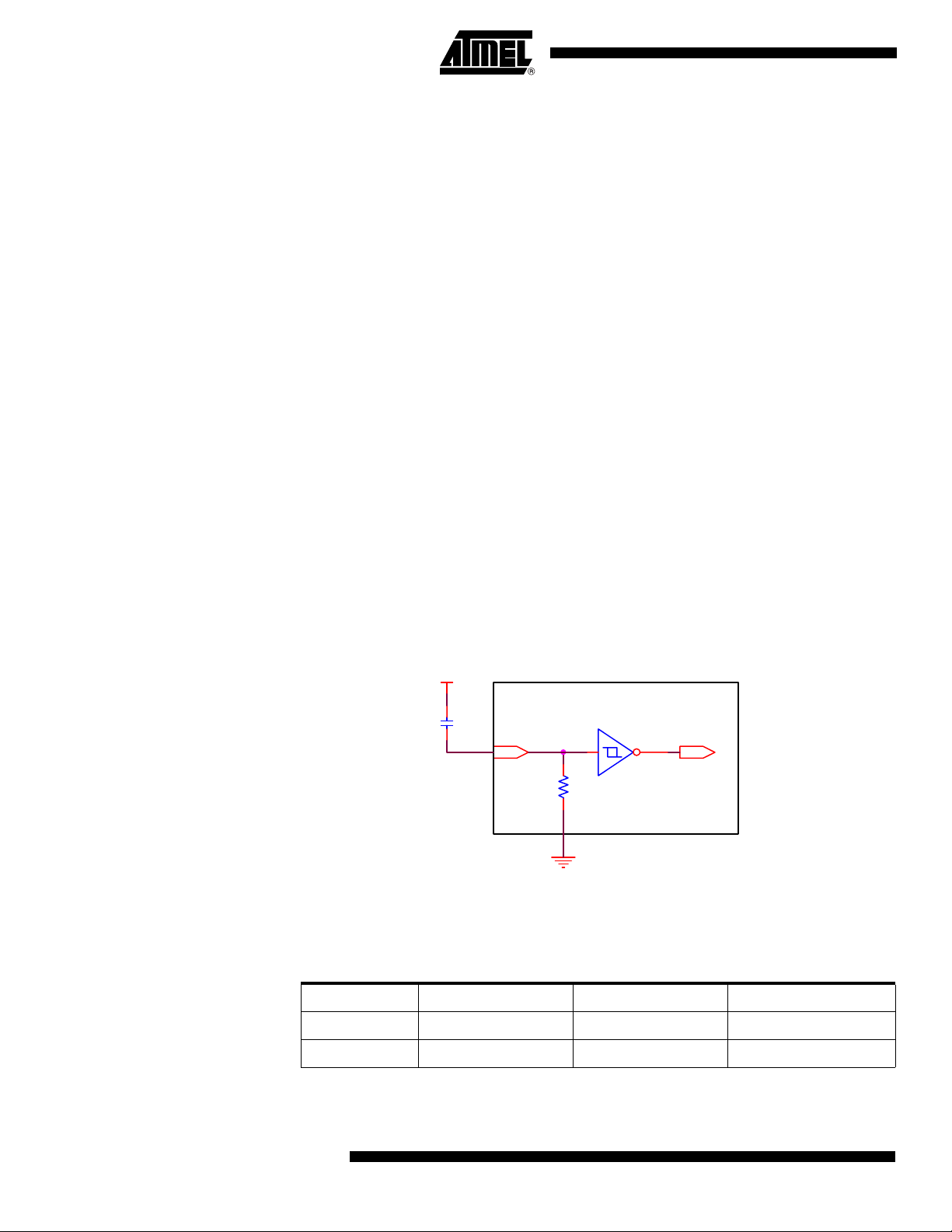

The reset circuitry is shown in Figure 5.

Figure 5. Reset Circuitry

VDD

Crst

RST pin

Rrst

Reset input circuitry

Internal reset

Table 13 and Table 14 give some typical examples for three values of VDD rise times,

two values of oscillator start-up time and two pull-down resistor values.

Table 13. Minimum Reset Capacitor for a 50K Pull-down Resistor

oscrst/vddrst 1ms 10ms 100ms

5ms 820nF 1.2µF 12µF

20

20ms 2.7µF 3.9µF 12µF

4126L–CAN–01/08

AT/T89C51CC02

Table 14. Minimum Reset Capacitor for a 15k Pull-down Resistor

oscrst/vddrst 1ms 10ms 100ms

5ms 2.7µF 4.7µF 47µF

20ms 10µF 15µF 47µF

Note: These values assume VDD starts from 0v to the nominal value. If the time between two

on/off sequences is too fast, the power-supply decoupling capacitors may not be fully

discharged, leading to a bad reset sequence.

During a Normal Operation (Warm Reset)

Reset pin must be maintained for at l ea st 2 m achi ne cy cl es (24 os c illat or c lock pe r iod s)

to apply a reset s equence duri ng normal o peration. The number of cl ock periods is

mode independent (X2 or X1).

Watchdog Reset A 1K resistor must be added in series with the capacitor to allow the use of watchdog

reset pulse output on the RST pin or when an external power-supply supervisor is used.

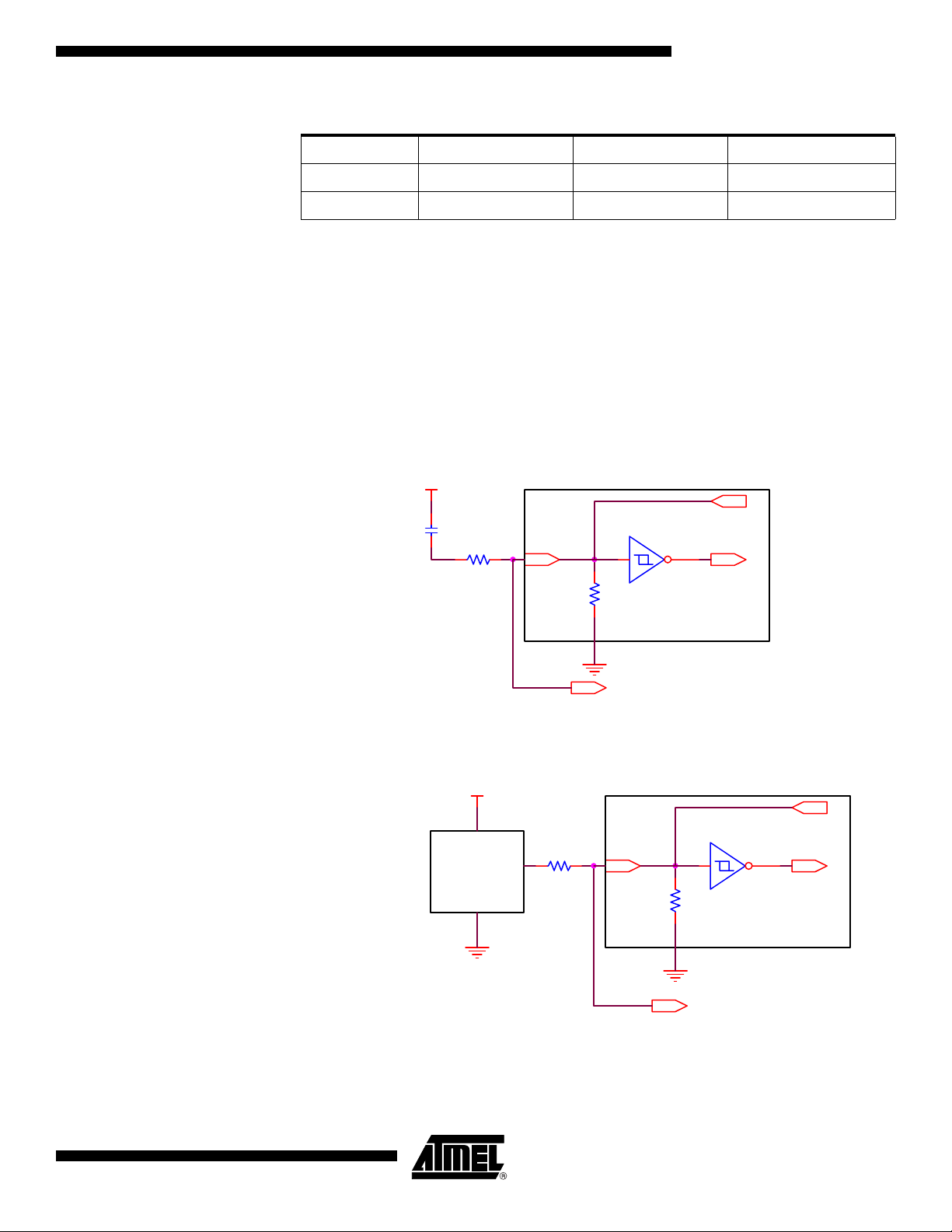

Figure 6 shows the reset circuitry when a capacitor is used.

Figure 6. Reset Circuitry for a Watchdog Configuration

VDD

Crst

1k RST pin

Rrst

Reset input circuitry

To other on-board circuitry

Figure 7 shows the reset circuitry when an external reset circuit is used.

watchdog

Internal reset

4126L–CAN–01/08

Figure 7. Reset Circuitry Example Using an External Reset Circuit

VDD

External reset

circuit

RST

1k RST pin

Rrst

Reset input circuitry

To other on-board circuitry

watchdog

Internal reset

21

AT/T89C51CC02

Reset Recommendation to Prevent Flash Corruption

When a Flash program memory is embedded on-chip, it is strongly recommended to

use an external reset chip (brown out device) to apply a reset (Figure 7). It prevents system malfunction during periods of insufficient power-supply voltage (power-supply

failure, power supply switched off, etc.).

Idle Mode Idle mode is a power reduction mode that reduces the power consumption. In this mode,

program execution halts. Idle mode freezes the cl ock to the CPU at known sta tes while

the peripherals continue to be clocked. The CPU status before entering Idle mode is

preserved, i.e., the program counter and program status word register retain their data

for the duration of Idle mode. The contents of the SFRs and RAM are also retained. The

status of the Port pins during Idle mode is detailed in Table 15.

Entering Idle Mode To enter Idle mode, set the IDL bi t in PCON register (See Table 16). The

A/T89C51CC02 enters Idle mode upon execution of the instruction that sets IDL bit. The

instruction that sets IDL bit is the last instruction executed.

Note: If IDL bit and PD bit are set simultaneously, the A/T89C51CC02 enters Power-down

mode. Then it does not go in Idle mode when exiting Power-down mode.

Exiting Idle Mode There are two ways to exit Idle mode:

1. Generate an enabled interrupt.

Hardware clears IDL bit in PCON register which restores the clock to the CPU. Exe-

cution resumes with the interrupt service routine. Upon completion of the interrupt

service routine, pr o gr am exec uti on r e su mes with the instruction im med iat ely following the instruction that activated Idle mode. The general purpose flags (GF1 and

GF0 in PCON register) may be used to indicate whether an interrupt occurred during normal operati on o r dur i ng I dle mo de. Wh en Idle mode is exite d b y a n i nte rrup t,

the interrupt service routine may examine GF1 and GF0.

2. Generate a reset.

A logic high on the RST pin clears IDL bit in PCON register directly and asynchro-

nously. This restores the c lock to the CPU. Program execu tion momentarily

resumes with the inst ructio n immedia tely follow ing the in structi on that activ ated the

Idle mode and may continue for a number of clock cycles before the internal reset

algorithm takes control. Reset initializes the A/T89C51CC02 and vectors the CPU to

address C:0000h.

Power-down Mode The Power-down mode places the A/T89C51 CC02 in a v ery low po wer state. Powe r-

Entering Power-down Mode To enter Power-down mode, set PD bit in PCON register. The A/T89C51CC02 enters

22

Notes: 1. Dur i ng the t im e th at ex e cuti o n re su me s, th e i nte r na l R AM ca n no t be ac ce ss ed ; ho w -

ever, it is possible for the Port pins to be accessed. To avoid unexpected outputs at

the Port pins, the instruction immediately following the instruction that activated Idle

mode should not write to a Port pin or to the external RAM.

2. If Idle mode is invoked by ADC Idle, the ADC conversion completion will exit Idle.

down mode stops t he osci ll ator , freez es a ll c lock at k nown s tate s. The CPU st atus p rior

to entering Power-down mode is preserved, i.e., the program counter, program status

word register retain their data for the duration of Power-down mode. In addition, the

SFRs and RAM content s a re pres erv ed. T h e s tatu s of the Po rt pins dur in g P ower -do w n

mode is detailed in Table 15.

the Power-down mode upon execution of the instruction that sets PD bit. The instruction

that sets PD bit is the last instruction executed.

4126L–CAN–01/08

AT/T89C51CC02

Exiting Power-down Mode Note: If V

was reduced during the Power-down mode, do not exit Power-down mode until

DD

V

is restored to the normal operating level.

DD

There are two ways to exit the Power-down mode:

1. Generate an enabled external interrupt.

– The A/T89C51CC02 provides capability to exit from Power-down using

INT0#, INT1#.

Hardware clears PD bit in PCON register which starts the oscillator and

restores the clocks to the CPU and peripherals. Using INTx# input,

execution resumes when the input is released (See Figure 8). Execution

resumes with the interrupt service routine. Upon completion of the interrupt

service routine, program execution resumes with the instruction immediately

following the instruction that activated Power-down mode.

Notes: 1. The external interrupt used to exit Power-down mode must be configured as level

sensitive (INT0# and INT1#) and must be assigned the highest priority. In addition,

the duration of the interrupt must be long enough to allow the oscillator to stabilize.

The execution will only resume when the interrupt is deasserted.

2. Exit from power-down by external interrupt does not affect the SFRs nor the internal

RAM content.

Figure 8. Power-down Exit Waveform Using INT1:0#

INT1:0#

OSC

Power-down phase Oscillator restart phase Active phaseActive phase

2. Generate a reset.

– A logic high on the RST pin clears PD bit in PCON register directly and

asynchronously. This starts the oscillator and restores the clock to the CPU

and peripherals. Program execution momentarily resumes with the

instruction immediately following the instruction that activated Power-down

mode and may continue for a number of clock cycles before the internal

reset algorithm takes control. Reset initializes the A/T89C51CC02 and

vectors the CPU to address 0000h.

Notes: 1. Dur i ng the t im e th at ex e cuti o n re su me s, th e i nte r na l R AM ca n no t be ac ce ss ed ; ho w -

ever, it is possible for the Port pins to be accessed. To avoid unexpected outputs at

the Port pins, the instruction immediately following the instruction that activated the

Power-down mode should not write to a Port pin or to the external RAM.

2. Exit from power-down by res et r edefines all the SFRs, b ut do es not af fect the internal

RAM content.

4126L–CAN–01/08

23

AT/T89C51CC02

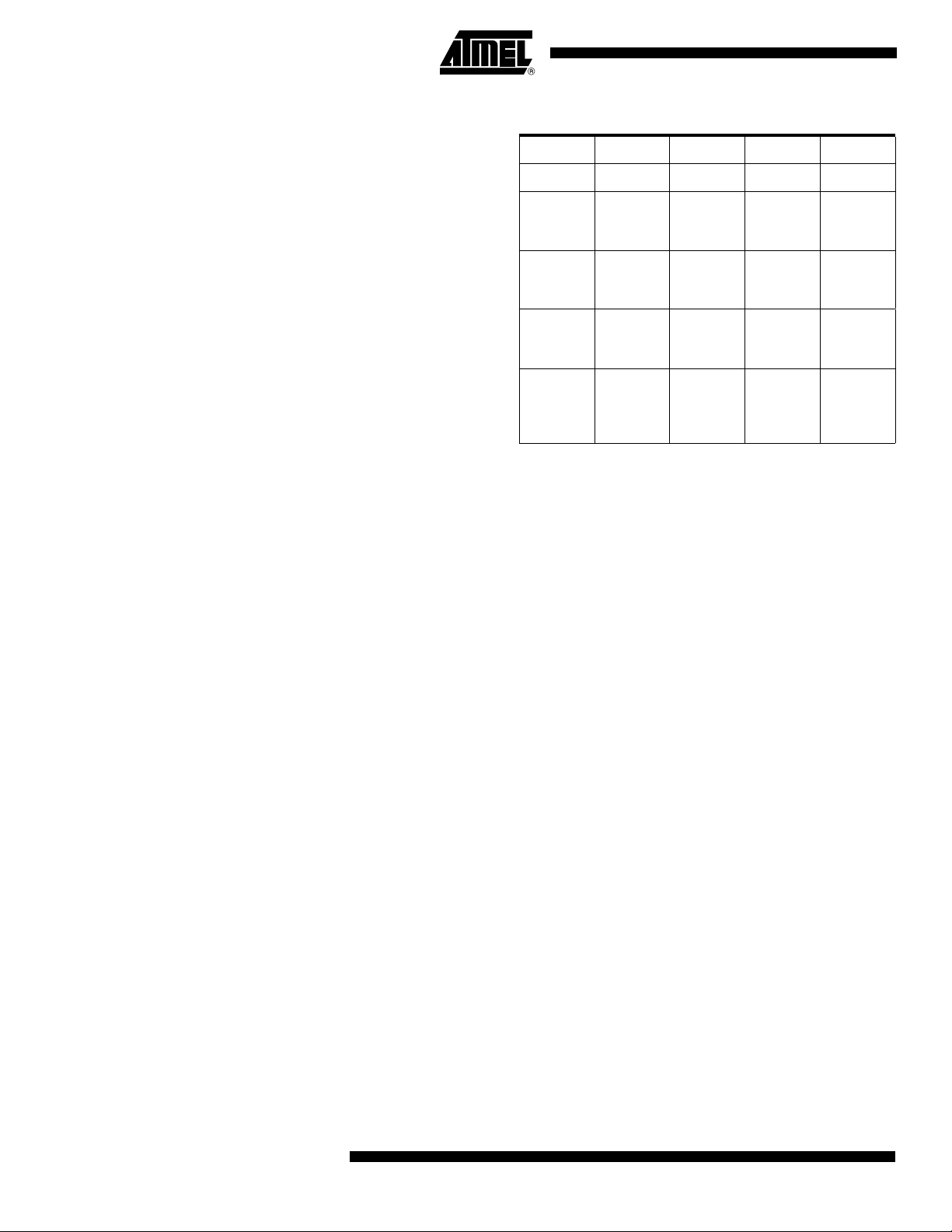

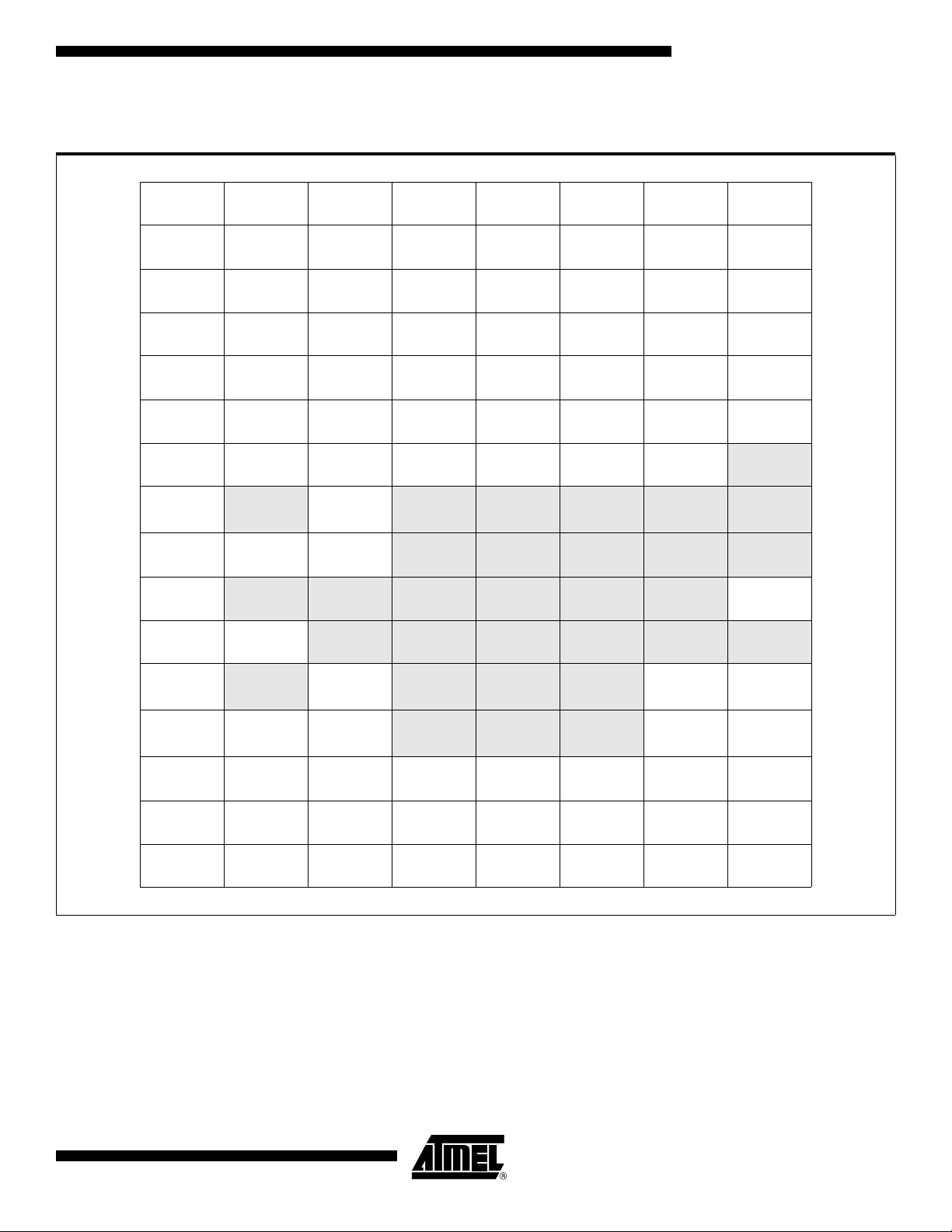

Table 15. Pin Conditions in Special Operating Modes

Mode Port 1 Port 2 Port 3 Port 4

Reset High High High High

Idle

(internal

code)

Idle

(external

code)

Power-

Down(inter

nal code)

Power-

Down

(external

code)

Data Data Data Data

Data Data Data Data

Data Data Data Data

Data Data Data Data

24

4126L–CAN–01/08

Registers Table 16. PCON Register

PCON (S:87h)

Power Control Register

76543210

SMOD1 SMOD0 - POF GF1 GF0 PD IDL

AT/T89C51CC02

Bit

Number

7SMOD1

6SMOD0

5-

4POF

3GF1

2GF0

1PD

0IDL

Bit

Mnemonic Description

Serial port Mode bit 1

Set to select double baud rate in mode 1, 2 or 3.

Serial port Mode bit 0

Clear to select SM0 bit in SCON register.

Set to select FE bit in SCON register.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Power-off Flag

Clear to recognize next reset type.

Set by hardware when V

software.

General purpose Flag

Cleared by user for general purpose usage.

Set by user for general purpose usage.

General purpose Flag

Cleared by user for general purpose usage.

Set by user for general purpose usage.

Power-down Mode bit

Cleared by hardware when reset occurs.

Set to enter power-down mode.

Idle Mode bit

Clear by hardware when interrupt or reset occurs.

Set to enter idle mode.

rises from 0 to its nominal voltage. Can also be set by

CC

4126L–CAN–01/08

Reset Value = 00X1 0000b

Not bit addressable

25

AT/T89C51CC02

Data Memory The T89C51CC02 provides data memory access in two different spaces:

The internal space mapped in three separate segments:

• The lower 128 Bytes RAM segment.

• The upper 128 Bytes RAM segment.

• The expanded 256 Bytes RAM segment (XRAM).

A fourth internal segment is available but dedicated to Special Function Registers,

SFRs, (addresses 80h to FFh) accessible by direct addressing mode.

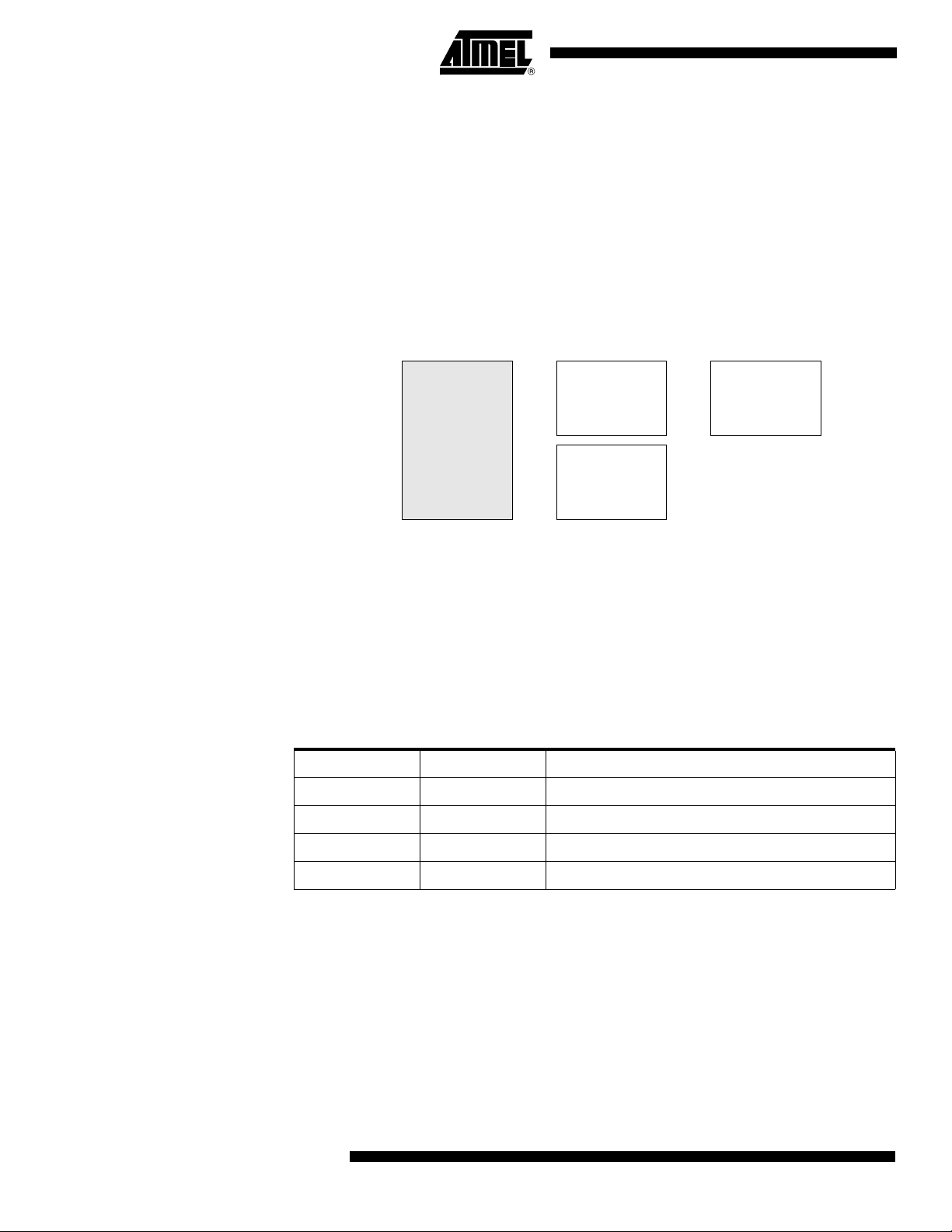

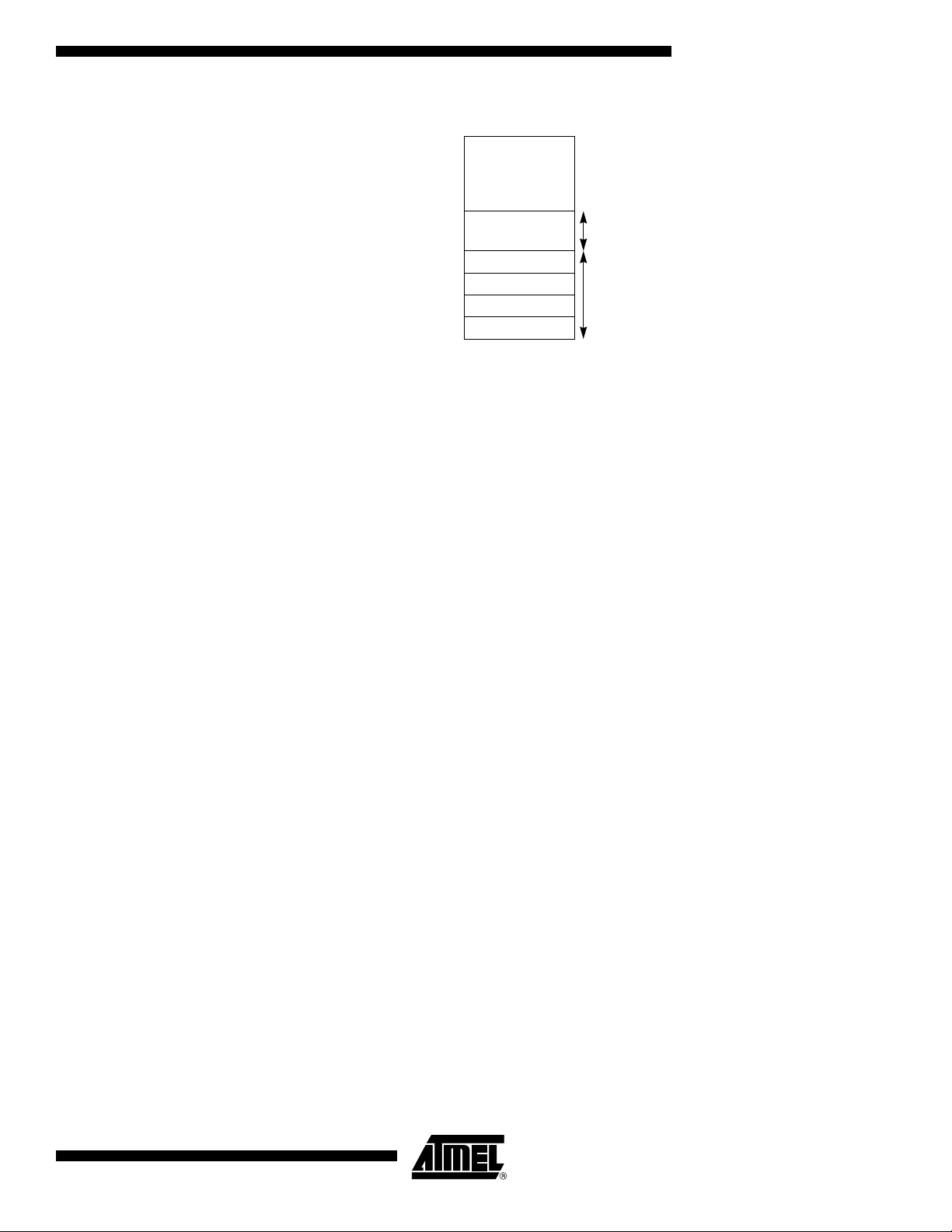

Figure 9 shows the internal data memory spaces organization.

Figure 9. Internal memory - RAM

FFh

00h

256 Bytes

Internal XRAM

FFh

80h 80h

7Fh

00h

Upper

128 Bytes

Internal RAM

Indirect Addressing

Lower

128 Bytes

Internal RAM

Direct or Indirect

Addressing

FFh

Direct Addressing

Special

Function

Registers

Internal Space

Lower 128 Bytes RAM The lower 128 Bytes of RAM (See Figure 10) are accessible from address 00h to 7Fh

using direct or indirect address ing modes. T he lowest 32 Bytes are grouped in to 4

banks of 8 registers (R0 to R7 ). Two bits RS0 and RS 1 in PSW re giste r (See Tabl e 18)

select which bank is in use according to Table 17. This allows more efficient use of code

space, since register instructions are shorter than instructions that use direct addressing, and can be used for context switching in interrupt service routines.

Table 17. Register Bank Selection

RS1 RS0 Description

0 0 Register bank 0 from 00h to 07h

26

0 1 Register bank 0 from 08h to 0Fh

1 0 Register bank 0 from 10h to 17h

1 1 Register bank 0 from 18h to 1Fh

The next 16 Bytes above the register banks form a block of bit-addressable memory

space. The C51 ins truction set i ncludes a wide s election o f singlebit instruct ions, and

the 128 bits in this area can be directly addressed by these instructions. The bit

addresses in this area are 00h to 7Fh.

4126L–CAN–01/08

Figure 10. Lower 128 Bytes Internal RAM Organization

7Fh

AT/T89C51CC02

30h

20h

18h

10h

08h

00h

2Fh

bit-Addressable Space

(bit Addresses 0-7Fh)

1Fh

17h

4 Banks of

8 Registers

0Fh

R0-R7

07h

Upper 128 Bytes RAM The upper 128 Bytes of RAM are accessible from address 80h to FFh using only indirect

addressing mode.

Expanded RAM The on-chip 256 Bytes of expanded RAM (XRAM) are accessible from address 0000h to

00FFh using i ndirect ad dressing mode thro ugh MOVX in structio ns. In this a ddress

range.

Note: Lower 128 Bytes RAM, Upper 128 Bytes RAM, and expanded RAM are made of volatile

memory cells. This means that the RAM content is indeterminate after power-up and

must then be initialized properly.

4126L–CAN–01/08

27

AT/T89C51CC02

Dual Data Pointer

Description The T89C51CC02 imp lements a second data pointer for speeding up code exe cution

and reducing code size in case of intensive usage of external memory accesses.

DPTR0 and DPTR1 are Seen by the CPU as DPT R and are accessed using the SFR

addresses 83h and 84h that are the DPH and DPL addresses. The DPS bit in AUXR1

register (See Figure 19) is used to select whether DPTR is the data pointer 0 or the data

pointer 1 (See Figure 11).

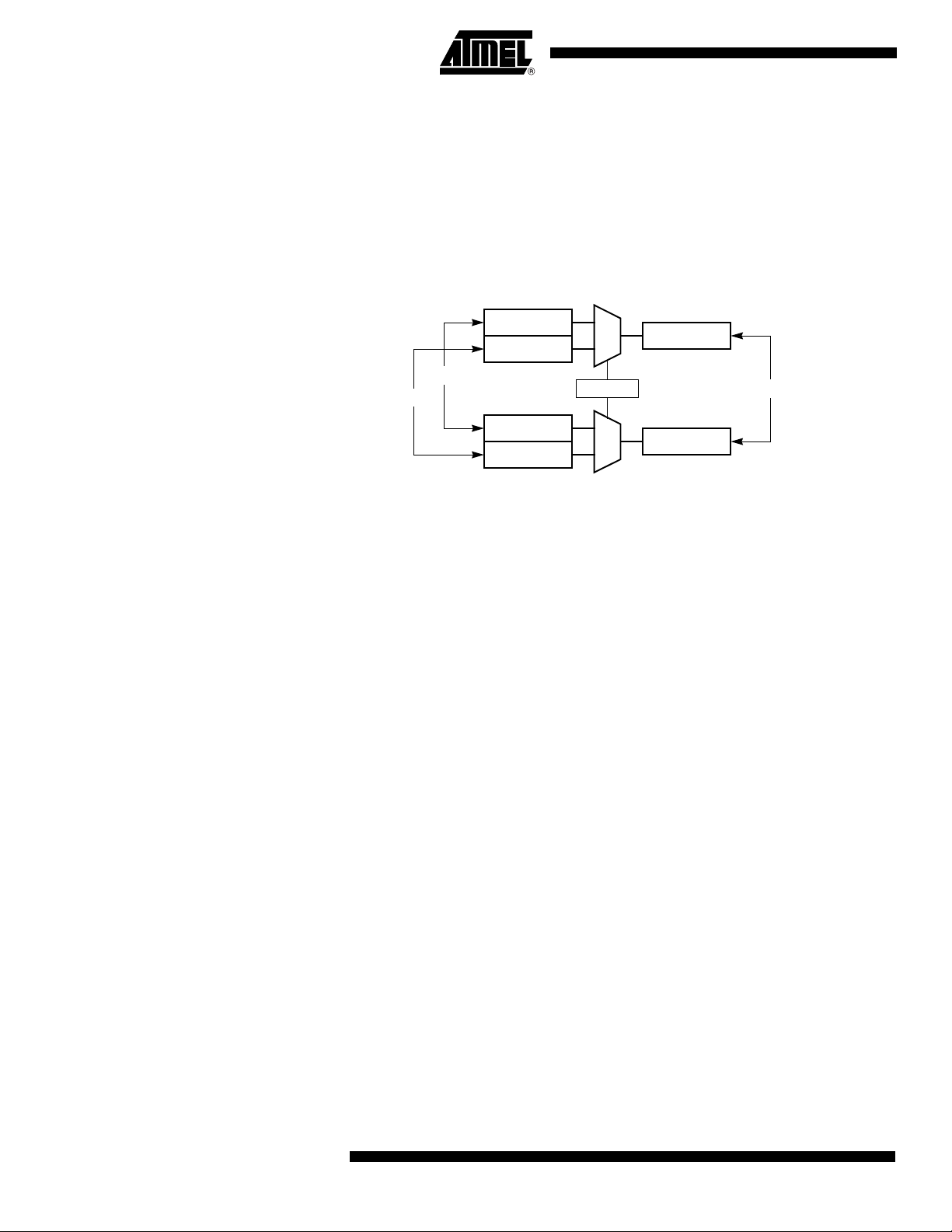

Figure 11. Dual Data Pointer Implementation

DPL0

DPL1

DPTR0

DPTR1

DPH0

DPH1

0

1

DPS

0

1

DPL

AUXR1.0

DPH

DPTR

Application Software can take advantage of the additional data pointers to both increase speed and

reduce code size, for example, block operations (copy, compare…) are well served by

using one data pointer as a “source” pointer and the other one as a “destination” pointer.

Hereafter is an example of block move implementation using the two pointers and coded

in assembler. The latest C compiler takes als o advantag e of this feature b y providin g

enhanced algorithm libraries.

The INC instruction is a short (2 Bytes) and fast (6 machine cycle) way to manipulate the

DPS bit in the AUXR 1 reg ister. H owever , note that th e INC i nstruc tion do es no t direc tly

force the DPS bit to a particular state, but simply toggles it. In simple routines, such as

the block move exa mple, o nly the f act that DP S is tog gled i n the pr oper s equenc e matters, not its actual value. In other words, the block move routine works the same whether

DPS is 0 or 1 on entry.

; ASCII block move using dual data pointers

; Modifies DPTR0, DPTR1, A and PSW

; Ends when encountering NULL character

; Note: DPS exits opposite to the entry state unless an extra INC AUXR1 is

added

28

AUXR1EQU0A2h

move:movDPTR,#SOURCE ; address of SOURCE

incAUXR1 ; switch data pointers

movDPTR,#DEST ; address of DEST

mv_loop:incAUXR1; switch data pointers

movxA,@DPTR; get a byte from SOURCE

incDPTR; increment SOURCE address

incAUXR1; switch data pointers

movx@DPTR,A; write the byte to DEST

incDPTR; increment DEST address

jnzmv_loop; check for NULL terminator

end_move:

4126L–CAN–01/08

Registers Table 18. PSW Register

PSW (S:D0h)

Program Status Word Register

76543210

CY AC F0 RS1 RS0 OV F1 P

AT/T89C51CC02

Bit

Number

7CY

6AC

5F0User Definable Flag 0

4 - 3 RS1:0

2OV

1F1User Definable Flag 1

0P

Bit

Mnemonic Description

Carry Flag

Carry out from bit 1 of ALU operands.

Auxiliary Carry Flag

Carry out from bit 1 of addition operands.

Register Bank Select bits

Refer to Table 17 for bits description.

Overflow Flag

Overflow set by arithmetic operations.

Parity bit

Set when ACC contains an odd number of 1’s.

Cleared when ACC contains an even number of 1’s.

Reset Value = 0000 0000b

4126L–CAN–01/08

29

AT/T89C51CC02

Table 19. AUXR1 Register

AUXR1 (S:A2h)

Auxiliary Control Register 1

76543210

- - ENBOOT - GF3 0 - DPS

Bit

Number

7 - 6 -

5 ENBOOT

4-

3GF3General Purpose Flag 3

20

1-Reserved for Data Pointer Extension

0DPS

Bit

Mnemonic Description

Reserved

The value read from these bits is indeterminate. Do not set these bits.

Enable Boot Flash

(1)

Set this bit to map the boot Flash between F800h -FFFFh

Clear this bit to disable boot Flash.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Always Zero

This bit is stuck to logic 0 to allow INC AUXR1 instruction without affecting GF3

flag.

Data Pointe r Select bit

Set to select second dual data pointer: DPTR1.

Clear to select first dual data pointer: DPTR0.

Reset Value = XXXX 00X0b

Note: 1. ENBOOT is initialized with the invert BLJB at reset. See In-System Programming

section.

30

4126L–CAN–01/08

AT/T89C51CC02

EEPROM Data Memory

Write Dat a i n the Column Latches

The 2K bytes on-chi p EEPRO M memo ry bloc k is l ocated at addres ses 0000h to 07FF h

of the XRAM/XRAM memory space and is selected by setting control bits in the EECON

register. A read in the EEPROM memory is done with a MOVX instruction.

A physical write i n the E EPRO M memo ry is d one in two step s: write data in the co lumn

latches and transfer of all data latches into an EEPROM memory row (programming).

The number of data written on the page may vary from 1 up to 128 Bytes (the page

size). When programm ing, onl y the dat a writte n in the col umn latc h is pro grammed an d

a ninth bit is used to obtain this feature. This provides the capability to program the

whole memory by Bytes, by page or by a number of Bytes in a page. Indeed, each ninth

bit is set when the writing th e corresponding b yte in a row and all these n inth bits are

reset after the writing of the complete EEPROM row.

Data is written by byte to the column latches as for an external RAM memory. Out of the

11 address bits of t he d ata poi nter, the 4 MSBs are used fo r pag e s ele ct ion ( row ) and 7

are used for byte selection. Between two EEPROM programming sessions, all the

addresses in the column lat ches mus t stay on the sa me p age, mea ning tha t the 4 MSB

must no be changed.

The following procedure is used to write to the column latches:

• Save and disable int er ru pt

• Set bit EEE of EECON register

• Load DPTR with the address to write

• Store A register with the data to be written

• Execute a MOVX @DPTR, A

• If needed loop the three last instructions until the end of a 128 Bytes page

• Restore interrupt

Note: The last page address used when loading the column latch is the one used to select the

page programming address.

Programming The EEPROM programming consists of the following actions:

• Write one or more Bytes of one page in the column latches. Normally, all Bytes must

belong to the same page; if not, the last page address will be latched and the others

discarded.

• Launch programming by writing the control sequence (50h followed by A0h) to the

EECON register.

• EEBUSY flag in EECON is then set by hardware to indicate that programming is in

progress and that the EEPROM segment is not available for reading.

• The end of programming is indicated by a hardware clear of the EEBUSY flag.

Note: The sequence 5xh and Axh must be executed without instructions between then other-

wise the programming is aborted.

Read Data The following procedure is used to read the data stored in the EEPROM memory:

• Save and disable int er ru pt

• Set bit EEE of EECON register

• Load DPTR with the address to read

• Execute a MOVX A, @DPTR

• Restore interrupt

4126L–CAN–01/08

31

AT/T89C51CC02

Examples ;*F*************************************************************************

;* NAME: api_rd_eeprom_byte

;* DPTR contain address to read.

;* Acc contain the reading value

;* NOTE: before execute this function, be sure the EEPROM is not BUSY

;***************************************************************************

api_rd_eeprom_byte:

; Save and clear EA

MOV EECON, #02h; map EEPROM in XRAM space

MOVX A, @DPTR

MOV EECON, #00h; unmap EEPROM

; Restore EA

ret

;*F*************************************************************************

;* NAME: api_ld_eeprom_cl

;* DPTR contain address to load

;* Acc contain value to load

;* NOTE: in this example we load only 1 byte, but it is possible upto

;* 128 Bytes.

;* before execute this function, be sure the EEPROM is not BUSY

;***************************************************************************

api_ld_eeprom_cl:

; Save and clear EA

MOV EECON, #02h ; map EEPROM in XRAM space

MOVX @DPTR, A

MOVEECON, #00h; unmap EEPROM

; Restore EA

ret

32

;*F*************************************************************************

;* NAME: api_wr_eeprom

;* NOTE: before execute this function, be sure the EEPROM is not BUSY

;***************************************************************************

api_wr_eeprom:

; Save and clear EA

MOV EECON, #050h

MOV EECON, #0A0h

; Restore EA

ret

4126L–CAN–01/08

Registers Table 20. EECON Register

EECON (S:0D2h)

EEPROM Control Register

76543210

EEPL3 EEPL2 EEPL1 EEPL0 - - EEE EEBUSY

Bit

Bit Number

Mnemonic Description

AT/T89C51CC02

7 - 4 EEPL3-0

3-

2-

1EEE

0EEBUSY

Programming Launch Command bits

Write 5Xh followed by AXh to EEPL to launch the programming.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Enable EEPROM Space bit

Set to map the EEPROM space during MOVX instructions (Write in the column

latches)

Clear to map the XRAM space during MOVX.

Programming Busy Flag

Set by hardware when programming is in progress.

Cleared by hardware when programming is done.

Can not be set or cleared by software.

Reset Value = XXXX XX00b

Not bit addressable

4126L–CAN–01/08

33

AT/T89C51CC02

Program/Code Memory

The T89C51CC02 implement 16K Bytes of on-chip program/code memory.

The Flash memory increa ses EP ROM and ROM func tional ity by in-cir cui t electric al era-

sure and programming. Thanks to the internal charge pump, the high voltage needed for

programming or erasing Flash ce lls is gene rated on-chip usi ng the standard V

DD

voltage. Thus, the Flash memory can be programmed using only one voltage and allows InSystem Progr ammi ng (IS P). Har dwar e prog rammin g mode is also availab le usi ng specific programming tool.

Figure 12. Program/Code Memory Organization

3FFFh

16K Bytes

Internal

Flash

0000h

Flash Memory Architecture

T89C51CC02 features two on-chip Flash memories:

•Flash memory FM0:

•Flash memory FM1:

The FM0 can be program by both parallel programming and Serial ISP whereas FM1

supports only parallel programming by pr ogrammers. The ISP mod e is detailed in the

’In-System Programming’ section.

All Read/Write access operations on Flash memory by user application are managed by

a set of API described in the ’In-System Programming’ section.

Figure 13. Flash Memory Architecture

Hardware Security (1 byte)

Extra Row (128 Bytes)

Column Latches (128 Bytes)

3FFFh

containing 16K Bytes of program memory (user space) organized into 128 bytes

pages,

2K Bytes for boot loader and Application Programming Interfaces (API).

FFFFh

F800h

16K Bytes

Flash Memory

User Space

FM0

2K Bytes

Flash Memory

Boot Space

FM1

FM1 mapped between F800h and

FFFFh when bit ENBOOT is set in

AUXR1 register

34

0000h

4126L–CAN–01/08

AT/T89C51CC02

FM0 Memory Architecture The Flash memory is made up of 4 blocks (See Figure 13):

1. The memory array (user space) 16K Bytes

2. The Extra Row

3. The Hardware security bits

4. The column latch registers

User Space This space is composed of a 16K Bytes Flash memory organized in 128 pages of 128

Bytes. It contains the user’s application code.

Extra Row (XRow) This row is a pa rt of FM0 and has a size of 12 8 B yt es. T he ex tra r ow may con t ain i nfo r-

mation for boot loader usage.

Hardware Security Byte The Hardware security Byte space is a part of FM0 and has a size of 1 byte.

The 4 MSB can be read/written by software, the 4 LSB can only be read by software and

written by hardware in parallel mode.

Column Latches The column latches, also part of FM0, have a size of full page (128 Bytes).

The column latches are the entrance buffers of the three previous memory locations

(user array, XROW and Hardware security byte).

Cross Flash Memory Access

Description

The FM0 memory can be programmed as describe on Table 21. Programming FM0

from FM0 is impossible.

The FM1 memory can be program only by parallel programming.

Table 21 show all software Flash access allowed.

Table 21. Cross Flash Memory Access

Code executing from

FM0

(user Flash)

FM1

(boot Flash)

Action

Read ok -

Load column latch ok -

Write - -

Read ok ok

Load column latch ok -

Write ok -

FM0

(user Flash)

FM1

(boot Flash)

4126L–CAN–01/08

35

AT/T89C51CC02

Overview of FM0 Operations

The CPU interfaces the Flash memory through the FCON register and AUXR1 register.

These registers are used to:

• Map the memory spaces in the adressable space

• Launch the programming of the memory spaces

• Get the status of the Flash memory (busy/not busy)

Mapping of the Memory Space By default, the user space is accessed by MOVC instruction for read only. The column

latches space is made accessible by setting the FPS bit in FCON register. Writing is

possible from 0000h to 3FFFh, address bits 6 to 0 are used to select an address within a

page while bits 14 to 7 are used to select the programming address of the page.

Setting FPS bit takes precedence on the EEE bit in EECON register.

The other memory spaces (user, extra row, hardware security) are made accessible in

the code segment by programming bits FMOD0 and FMOD1 in FCON register in accordance with Table 22. A MOVC instruction is then used for reading these spaces.

Table 22. FM0 blocks Select bits

FMOD1 FMOD0 FM0 Adressable Space

0 0 User (0000h-3FFFh)

0 1 Extra Row(FF80h-FFFFh)

1 0 Hardware Security Byte (0000h)

11Reserved

Launching Programming FPL3:0 bits i n FCON regist er are us ed to s ecure th e launc h of pr ogrammi ng. A s pecific

sequence must be written in these bits to unlock the write protection and to launch the

programming. This sequence is 5xh followed by Axh. Table 23 summarizes the memory

spaces to program according to FMOD1:0 bits.

Table 23. Programming Spaces

Write to FCON

OperationFPL3:0 FPS FMOD1 FMOD0

5 x 0 0 No action

User

Extra Row

Hardware

Security

Byte

Reserved

Note: The sequence 5xh and Axh must be executing without instructions between them other-

wise the programming is aborted.

Interrupts that may occur during programming time must be disabled to avoid any spurious exit of the programming mode.

Ax00

5 x 0 1 No action

Ax01

5 x 1 0 No action

A x 1 0 Write the fuse bits space

5 x 1 1 No action

A x 1 1 No action

Write the column latches in user

space

Write the column latches in extra row

space

36

4126L–CAN–01/08

AT/T89C51CC02

Status of the Flash Memory The bit FBUSY in FCON register is used to indicate the status of programming.

FBUSY is set when programming is in progress.

Selecting FM1 The bit ENBOOT in AUXR1 register is used to map FM1 from F800h to FFFFh.

Loading the Column Latches Any num ber of data fr om 1 byte to 128 Bytes can be lo ade d i n the column latches. T his

provides the capability to program the whole memory by byte, by page or by any number

of Bytes in a page.

When progra mmin g is laun ched, a n aut omati c erase of the loc atio ns load ed in th e col umn latches is first performed, then programming is effectively done. Thus no page or

block erase is needed and only the loaded data are programmed in the corresponding

page.

The following procedure is used to load the column latches and is summarized in

Figure 14:

• Save then disable interrupt and map the column latch space by setting FPS bit.

• Load the DPTR with the address to load.

• Load Accumulator register with the data to load.

• Execute the MOVX @DPTR, A instruction.

• If needed loop the three last instructions until the page is completely loaded.

• unmap the column latch and Restore Interrupt

4126L–CAN–01/08

37

AT/T89C51CC02

Figure 14. Column Latches Loading Procedure

Column Latches

Loading

Save & Disable IT

EA = 0

Column Latches Mapping

FCON = 08h (FPS = 1)

Data Load

DPTR = Address

ACC = Data

Exec: MOVX @DPTR, A

Last Byte

to load?

Data Memory Mapping

FCON = 00h (FPS = 0)

(1)

Restore IT

Note: 1. The last page address used when loading the column latch is the one used to select

the page programming address.

Programming the Flash Spaces

User The following procedure is used to program the User space and is summarized in

Figure 15:

• Load up to one page of data in the column latches from address 0000h to 3FFFh.

• Save then disable the interrupts.

• Launch the programming by writing the data sequence 50h followed by A0h in

FCON register.This step must be executed from FM1.

The end of the programming indicated by the FBUSY flag cleared.

• Restore the interrupts.

Extra Row The following procedure is used to pr ogra m the Extra Row space a nd is summ arized i n

Figure 15:

• Load data in the column latches from address FF80h to FFFFh.

• Save then disable the interrupts.

• Launch the programming by writing the data sequence 52h followed by A2h in

FCON register. This step of the procedure must be executed from FM1.

The end of the programming indicated by the FBUSY flag cleared.

• Restore the interrupts.

38

4126L–CAN–01/08

Figure 15. Flash and Extra row Programming Procedure

Flash Spaces

Programming

Column Latches Load i n g

See Figure 14

Save & Disable IT

EA = 0

Launch Programming

FCON = 5xh

FCON = Axh

FBusy

Cleared?

AT/T89C51CC02

Hardware Security Byte

Clear Mode

FCON = 00h

End Programming

Restore IT

The following procedure is used to program the Hardware Security Byte space

and is summarized in Figure 16:

• Set FPS and map Hardware byte (FCON = 0x0C)

• Save then disable the interrupts.

• Load DPTR at address 0000h.

• Load Accumulator register with the data to load.

• Execute the MOVX @DPTR, A instruction.

• Launch the programming by writing the data sequence 54h followed by A4h in

FCON register. This step of the procedure must be executed from FM1.

The end of the programming indicated by the FBusy flag cleared.

• Restore the interrupts

4126L–CAN–01/08

39

AT/T89C51CC02

Figure 16. Hardware Programming Procedure

Flash Spaces

Programming

Save & Disable IT

EA = 0

FCON = 0Ch

Save & Disable IT

EA = 0

Launch Programming

FCON = 54h

FCON = A4h

Data Load

DPTR = 00h

ACC = Data

Exec: MOVX @DPTR, A

End Loading

Restore IT

FBusy

Cleared?

Clear Mode

FCON = 00h

End Programming

RestoreIT

Reading the Flash Spaces

User The following procedure is used to read the User space:

• Read one byte in Accumulator by executing MOVC A,@A+DPTR with A+DPTR is

the address of the code byte to read.

Note: FCON must be cleared (00h) when not used.

Extra Row The following procedure is used to read the Extra Row space and is summarized in

Figure 17:

• Map the Extra Row space by writing 02h in FCON register.

• Read one byte in Accumulator by executing MOVC A,@A+DPTR with A= 0 &

DPTR= FF80h to FFFFh.

• Clear FCON to unmap the Extra Row.

Hardware Security Byte

40

The following procedure is used to read the Hardware Security Byte and is summarized in Figure 17:

• Map the Hardware Security space by writing 04h in FCON register.

• Read the byte in Accumulator by executing MOVC A,@A+DPTR with A= 0 &

DPTR= 0000h.

• Clear FCON to unmap the Hardware Security Byte.

4126L–CAN–01/08

Figure 17. Reading Procedure

Flash Spaces Reading

Flash Spaces Mapping

FCON = 00000aa0b

Data Read

DPTR = Address

Exec: MOVC A, @A+DPTR

Note: aa = 10 for the Hardware Security Byte.

ACC= 0

Clear Mode

FCON = 00h

AT/T89C51CC02

Flash Protection from Parallel

Programming

The three lock bits in Hardware Security Byte ( See ’In-System Prog ramming’ section)

are programmed according to Table 24 provide different level of protection for the onchip code and data located in FM0 and FM1.

The only way to write this bits are the parallel mode. They are set by default to level 3.

Table 24. Program Lock bit

Program Lock bits

Security

Level

1 U U U No program lock features enabled.

2 P U U Parallel programming of the Flash is disabled.

3UPU

4UUPSame as 3

LB0 LB1 LB2

Protection Description

Same as 2, also verify through parallel programming interface is

disabled. This is the factory defaul programming.

Note: 1. Program Lock bits

U: unprogrammed

P: programmed

WARNING: Security level 2, 3 and 4 should only be programmed after Flash and Core

verification.

Preventing Flash Corruption See Section “Power Management”.

4126L–CAN–01/08

41

AT/T89C51CC02

Registers Table 25. FCON Register

FCON Register FCON (S:D1h)

Flash Control Register

76543210

FPL3 FPL2 FPL1 FPL0 FPS FMOD1 FMOD0 FBUSY

Bit

Number

7 - 4 FPL3:0

3FPS

2 - 1 FMOD1:0

0FBUSY

Bit

Mnemonic Description

Programming Launch Command bits

Write 5Xh followed by AXh to launch the programming according to FMOD1:0.

(See Table 23.)

Flash Map Program Space

Set to map the column latch space in the data memory space.

Clear to re-map the data memory space.

Flash Mode

See Table 22 or Table 23.

Flash Busy

Set by hardware when programming is in progress.

Clear by hardware when programming is done.

Can not be changed by software.

Reset Value = 0000 0000b

42

4126L–CAN–01/08

AT/T89C51CC02

4126L–CAN–01/08

43

AT/T89C51CC02

Operation Cross Memory Access

Table 26. Cross Memory Access

Action RAM ERAM Boot FLASH FM0 E² Data

Space addressable in read and write are:

•RAM

• ERAM (Expanded RAM access by movx)

• EEPROM DATA

• FM0 ( user flash )

• Hardware byte

•XROW

•Boot Flash

• Flash Column latch

The table below prov ides the differen t kin d of m emory wh ich can be acce ssed f rom d if-

ferent code location.

Hardware

Byte XROW

boot FLASH

Read OK OK OK OK Write - OK

Read OK OK OK -OK -

FM0

Write - OK (idle) OK

Note: 1. RWW: Read While Write

(1)

OK

(1)

(1)

(1)

OK

--OK

OK

(1)

44

4126L–CAN–01/08

Sharing Instructions Table 27. Ins tr uctions shared

AT/T89C51CC02

Action RAM ERAM

Read MOV MOVX MOVX MOVC MOVC MOVC M OVC

Write MOV MOVX MOVX - by cl by cl by cl

EEPROM

DATA

Boot

FLASH FM0

Hardware

Byte XROW

Note: by cl : using Column Latch

Table 28. Read MOVX A, @DPTR

EEE bit in

EECON

Register

00XOK

01XOK

10X OK

11XOK

FPS in

FCON Register ENBOOT ERAM

EEPROM

DATA

Flash

Column

Latch

Table 29. Write MOVX @DPTR,A

EEE bit in

EECON

Register

FPS bit in

FCON Register ENBOOT ERAM

EEPROM

Data

Flash

Column

Latch

00XOK

01X OK

10X OK

11X OK

4126L–CAN–01/08

45

AT/T89C51CC02

Table 30. Read MOVC A, @DPTR

Code Execution

From FM0

From FM1

(ENBOOT =1

FCON Register

ENBOOT DPTR FM1 FM0 XROW

0 0000h to 3FFFh OK

00X

01X X

10X X X OK

11X

0

00

1

01X

1

0 000h to 3FFFh OK

1

1

0X NA

1X OK

0X NA

1

0NA

0000h to 3FFFh OK

F800h to FFFFh Do not use this configuration

0000 to 007Fh

(1)

See

0000h to 3FFFh OK

F800h to FFFFh Do not use this configuration

0000h to 3FFF OK

F800h to FFFFh OK

0000h to 007h

(2)

See

OK

OK

Hardware

ByteFMOD1 FMOD0 FPS

10X

11X

1

0NA

1

0NA

X

OK

000h to 3FFFh

OK

1. For DPTR higher than 007Fh o nly lo west 7 b its are dec oded, t hus th e behav ior is the sa me as for addre sses from

0000h to 007Fh

2. For DPTR higher than 007Fh o nly lo west 7 b its are dec oded, t hus th e behav ior is the sa me as for addre sses from

0000h to 007Fh

46

4126L–CAN–01/08

AT/T89C51CC02

h

In-System Programming (ISP)

Flash Programming and Erasure

With the implementation of the User Space (FM0) and the Boot Space (FM1) in Flash

technology the T89C51CC02 allows the system engineer the development of applications with a very high l evel of flex ibility . Th is fle xibili ty is based on the p ossibi lity t o alter

the customer program at any stages of a product’s life:

• Before mounting the chip on the PCB, FM0 flash can be programmed with the

application code. FM1 is always preprogrammed by Atmel with a bootloader (chip

can be ordered with CAN bootloader or UART bootloader).

• Once the chip is mounted on the PCB, it can be programmed by serial mode via the

CAN bus or UART.

Note: 1. The user can also program his own bootloader in FM1.

This ISP allows code modification over the total lifetime of the product.

Besides the default Bootloa ders Atmel prov ide customers all the needed Applic ation-