Page 1

A

B

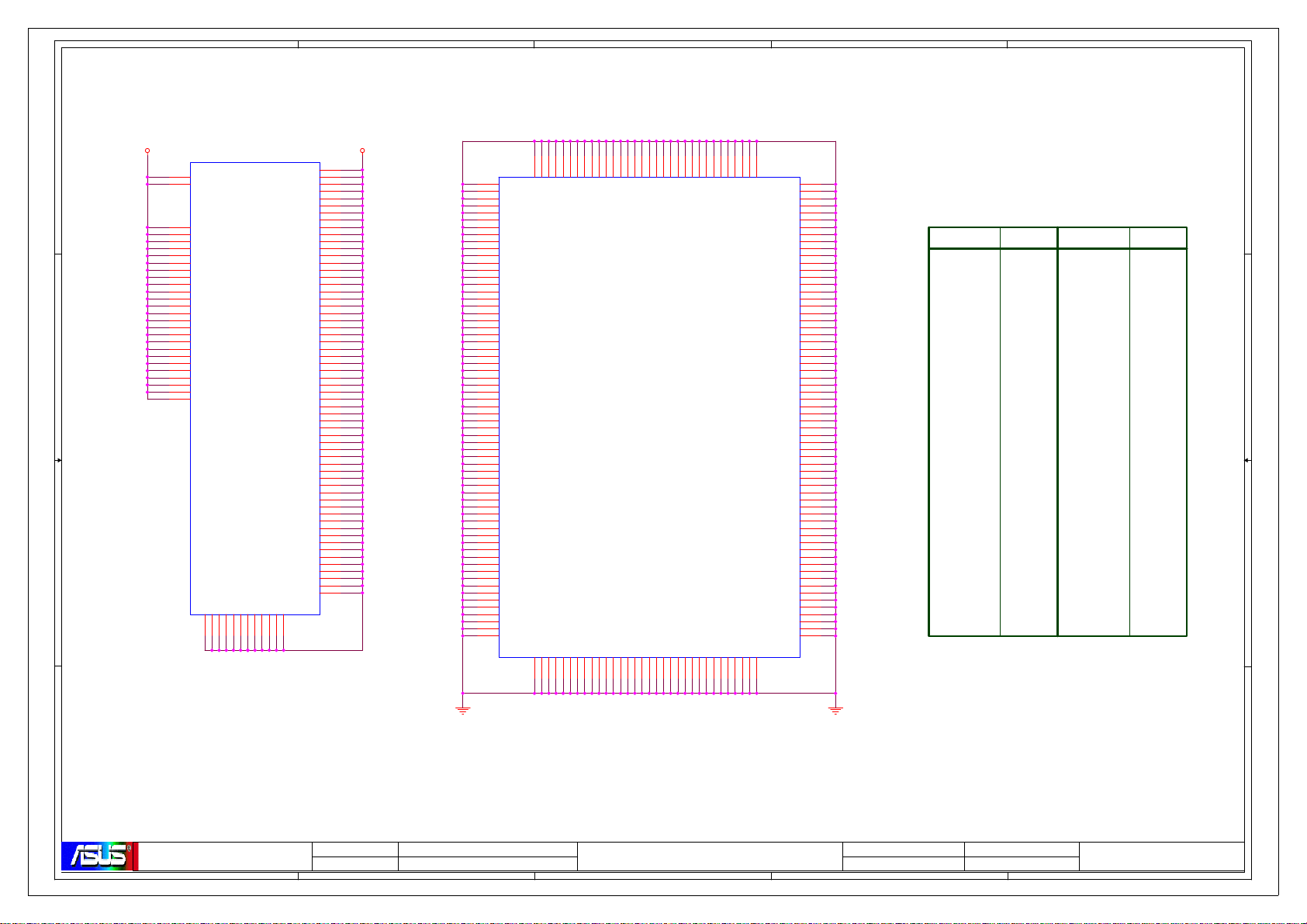

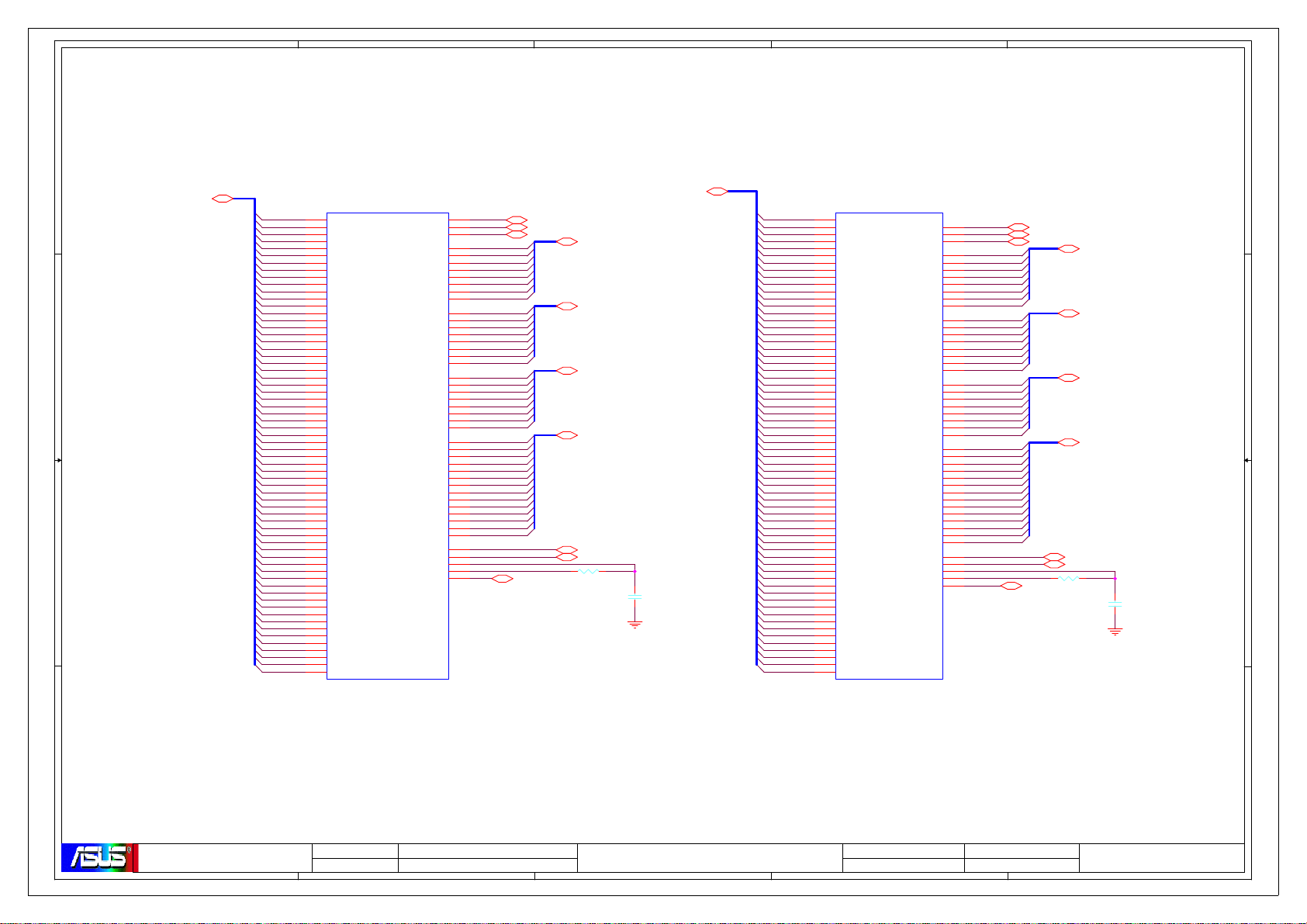

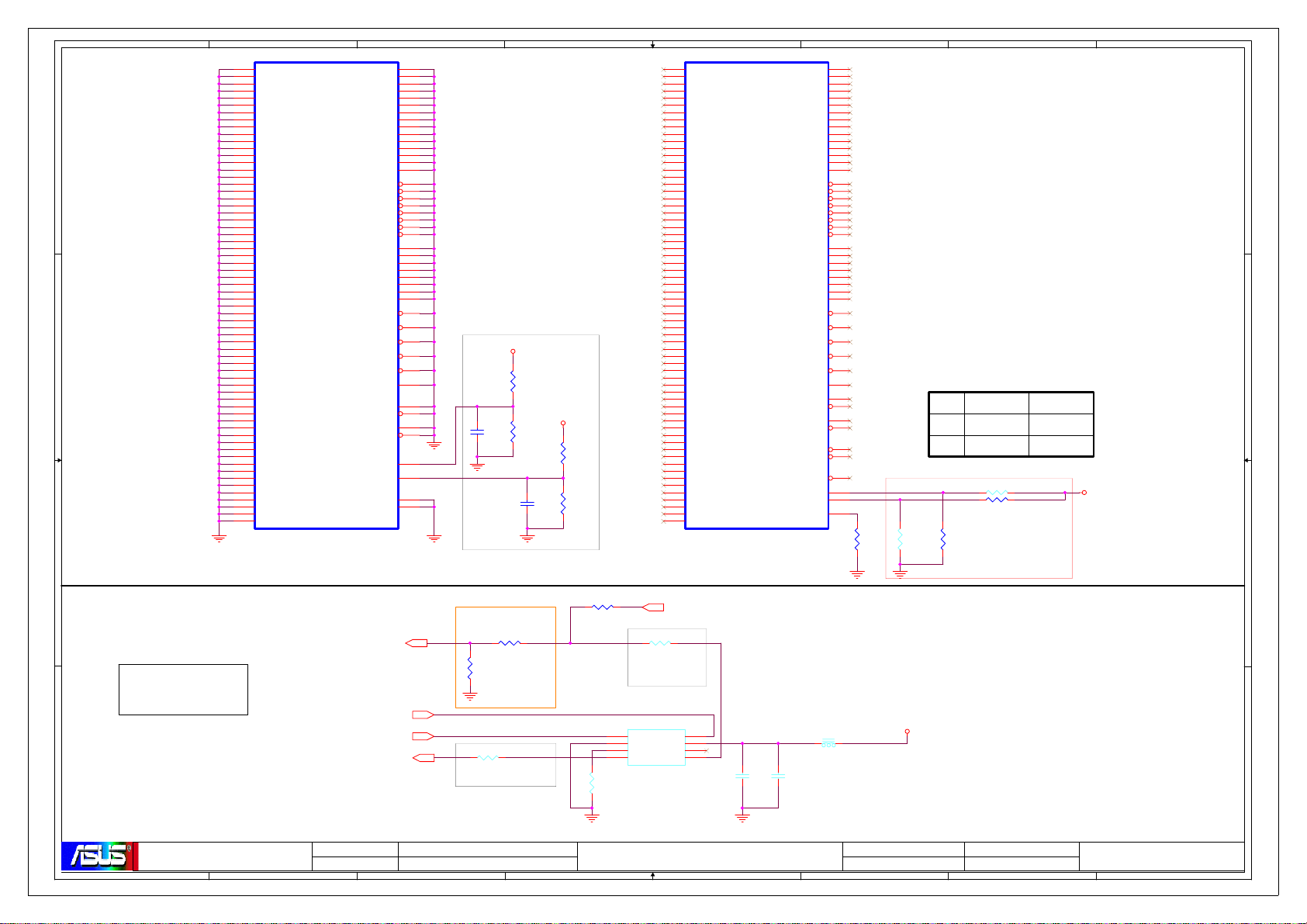

W3V/A SCHEMATIC V2.1

C

D

E

1 1

PAGE Content

SYSTEM PAGE REF.

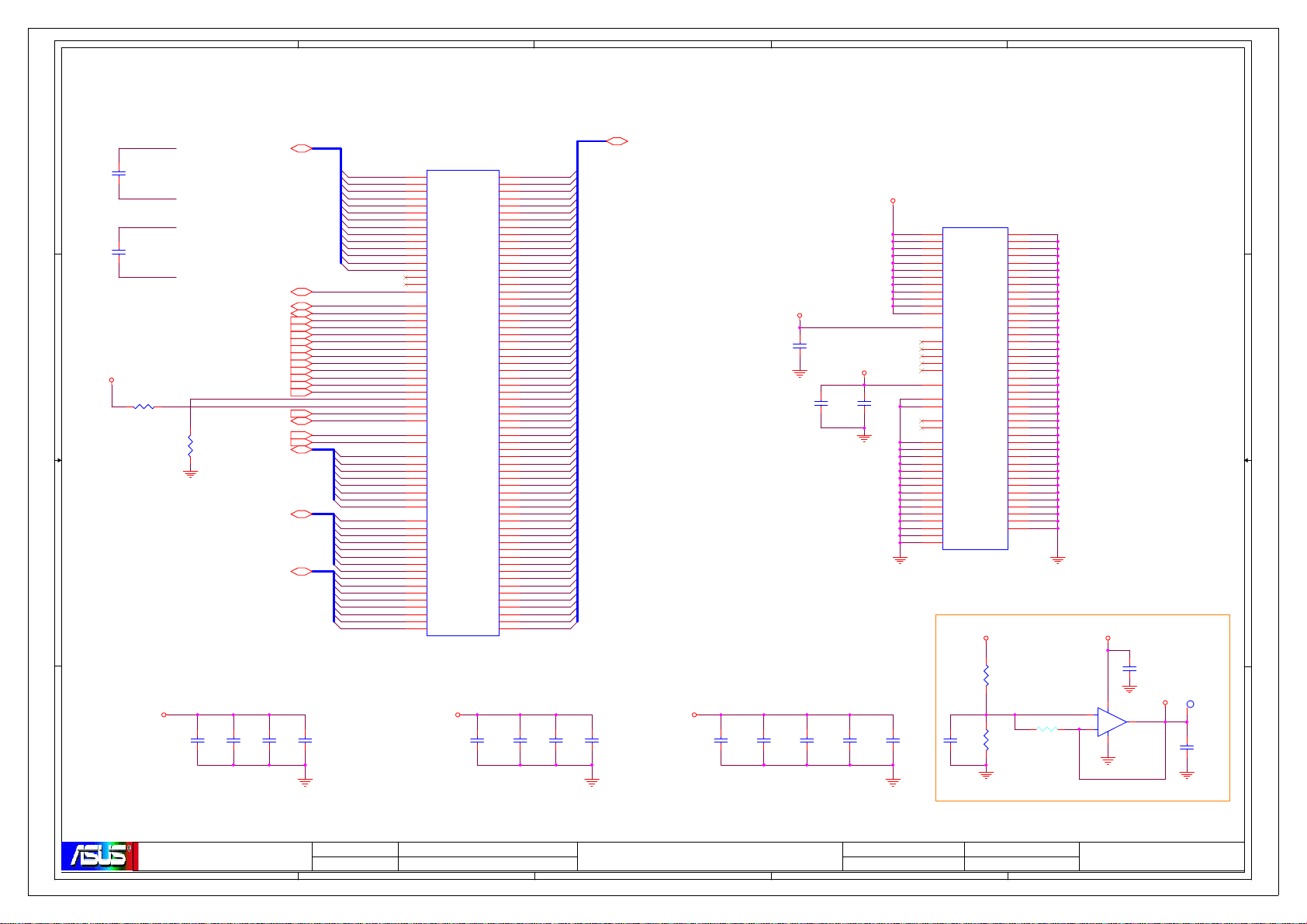

DOTHAN CPU-1

4

DOTHAN CPU-2

5

CPU CAP/THERMAL SENSOR/ITP

6

ALVISO: CPU

7

ALVISO: DDR2 & DMI & PEG

8

9

ALVISO: DDR2

10

ALVISO: POWER & Caps

11

ALVISO: GND & NCTF & Straps

CLOCK GEN (ICS954213)

2 2

3 3

12

13

DDR2 SODIMM(0) & Caps

DDR2 SODIMM(1) & Caps

14

DDR2 TERMINATOR

15

ATI M24: MAIN

16

ATI M24: MEMORY/SS

17

ATI M24: PWR & GND

18

19

ATI M24: Strapping

LVDS/INVERTER

20

21

CRT/TV/TPM CONN

ICH6: SATA/LPC/IDE/ACZ (1)

22

ICH6: PCI/DMI/USB/PCIE(2)

23

24

ICH6M: PWR/GND/CAPS(3)

ICH6: PULL UP & Straping

25

26

SATA to PATA BRIDGE

HDD CON

27

28

SWAP BAY CON

USB PORTS

29

30

SUPER I/O (LPC47N207)

PAGE Content

POWER PAGE REF.

49

VCORE_MAX1987

SYSTEM

50

51

1.5V,1.8V,2.5V,1.05V

5253VGA VCORE

1.5VA & DDR2

54

PIC16C54/BATCON/PWOK

55

CHARGER

56

BATLOW/SD#

57

LOAD SWITCH

58

BATCON

Power Flowchart

59

HISTORY

60

61 DC_IN CONN.

62 ODD CONN.

63 TP&LED CONN

31 FIR & FWH

32

KBC 38857

33

Azalia AUDIO (ALC861-VS)

AUDIO AMP/JACKS

34

35

4 4

5 5

MIC AMP

SMBUS

36

PCI GIGA LAN (88E8001)

37

RJ11_RJ45/MDC/BT

38

39

MINIPCI

40

PCI CARDBUS (R5C841)

PCI PCMCIA SOCKET A

41

IEEE1394A/3in1 CONN

42

43

LEDs & DEBUG PORT

DJ/HOTKEY/TP LED

44

45

PWR SW/RESET/KBC LED

46

FAN & DC_IN

47

POWER-ON SEQUENCE

48

DISCHARGE/EMI/VCCA

bom

PROJECT:

A

W3V

REVISION

2.1

Monday, January 17, 2005

DATE:

SHEET OF

B

1 63

DESCRIPTION:

Content & History

C

RELEASE DATE :

D

DESIGN ENGINEER :SCHEMATIC FILE NAME :

Alice Shih

E

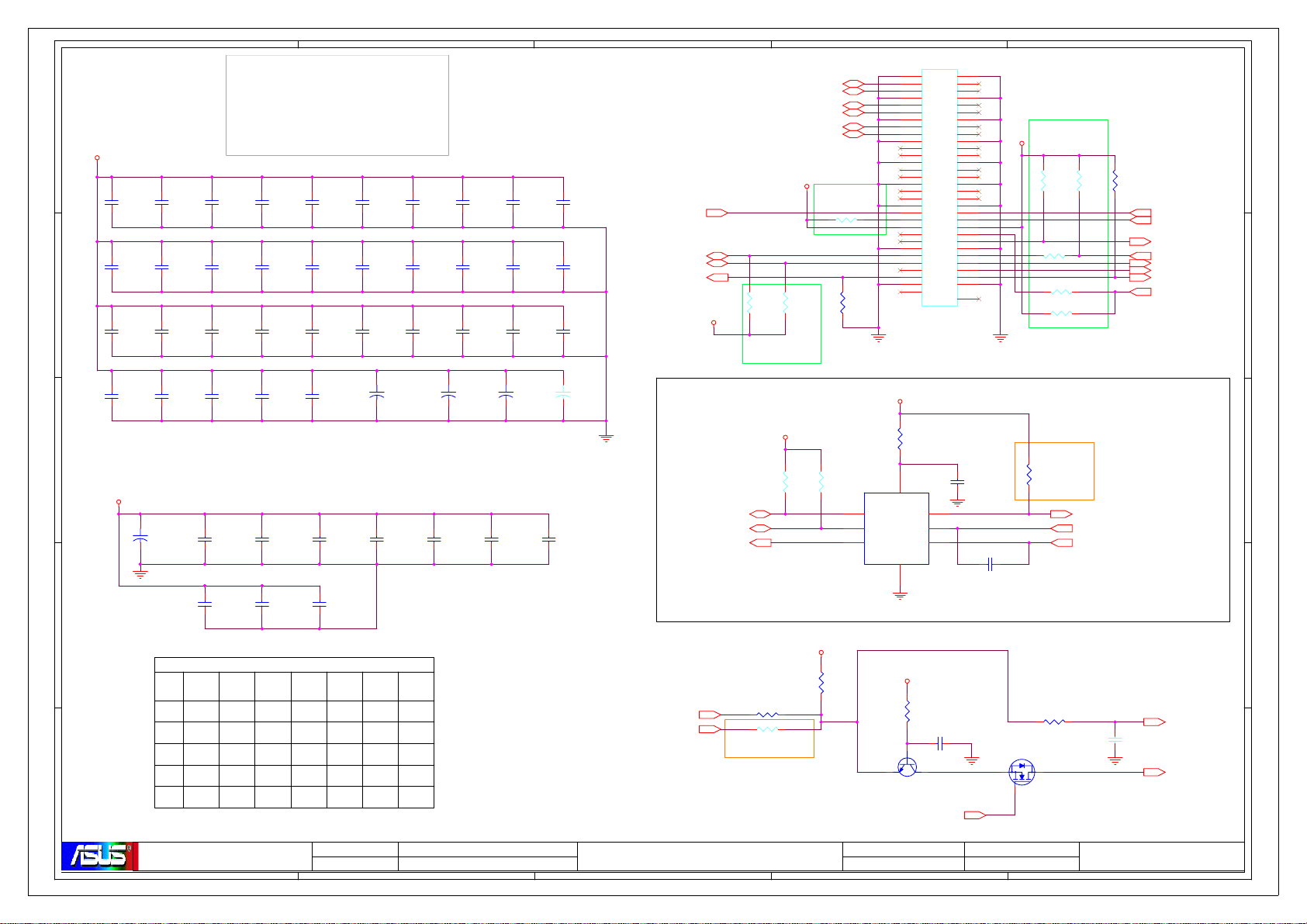

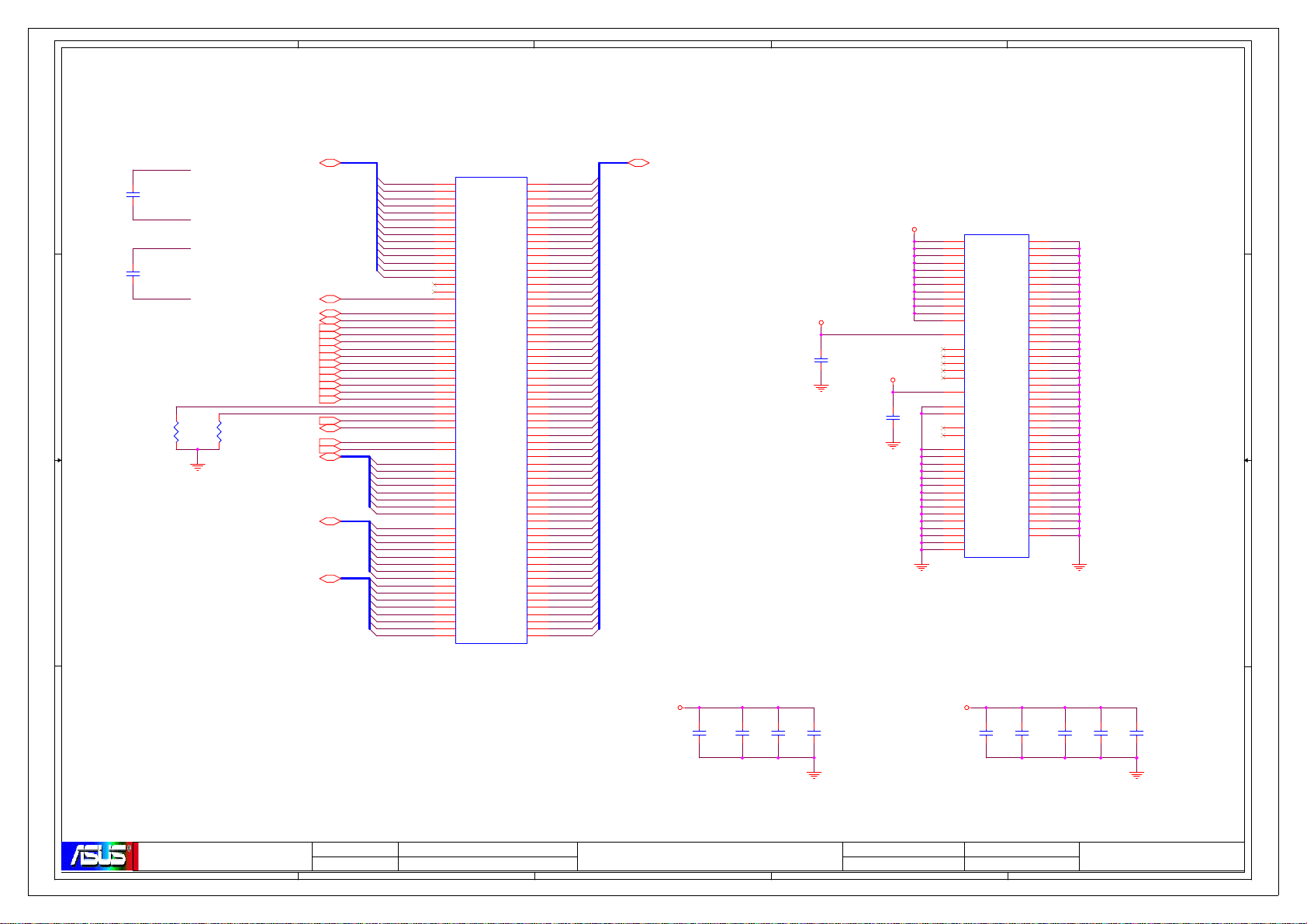

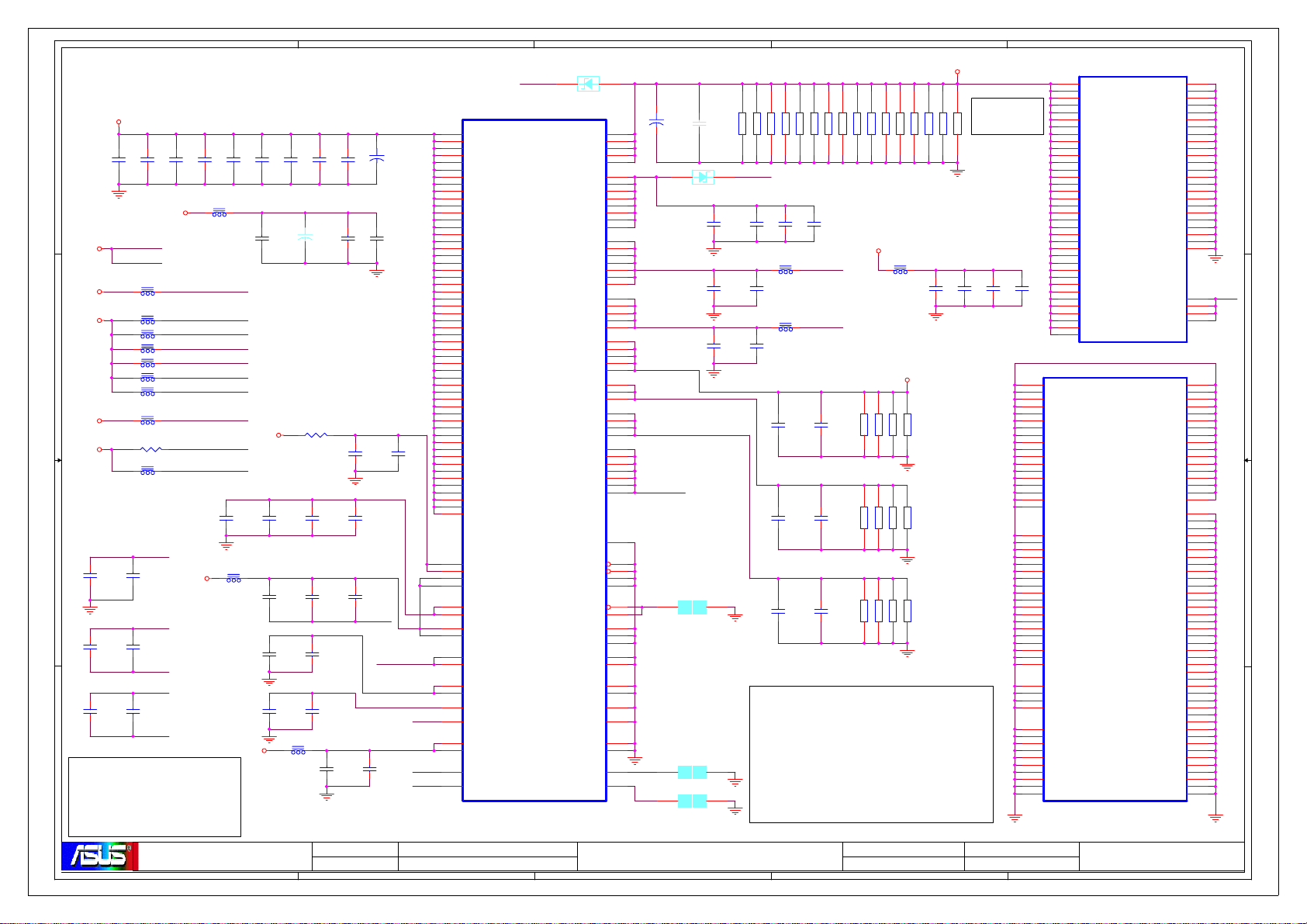

Page 2

A

B

C

D

E

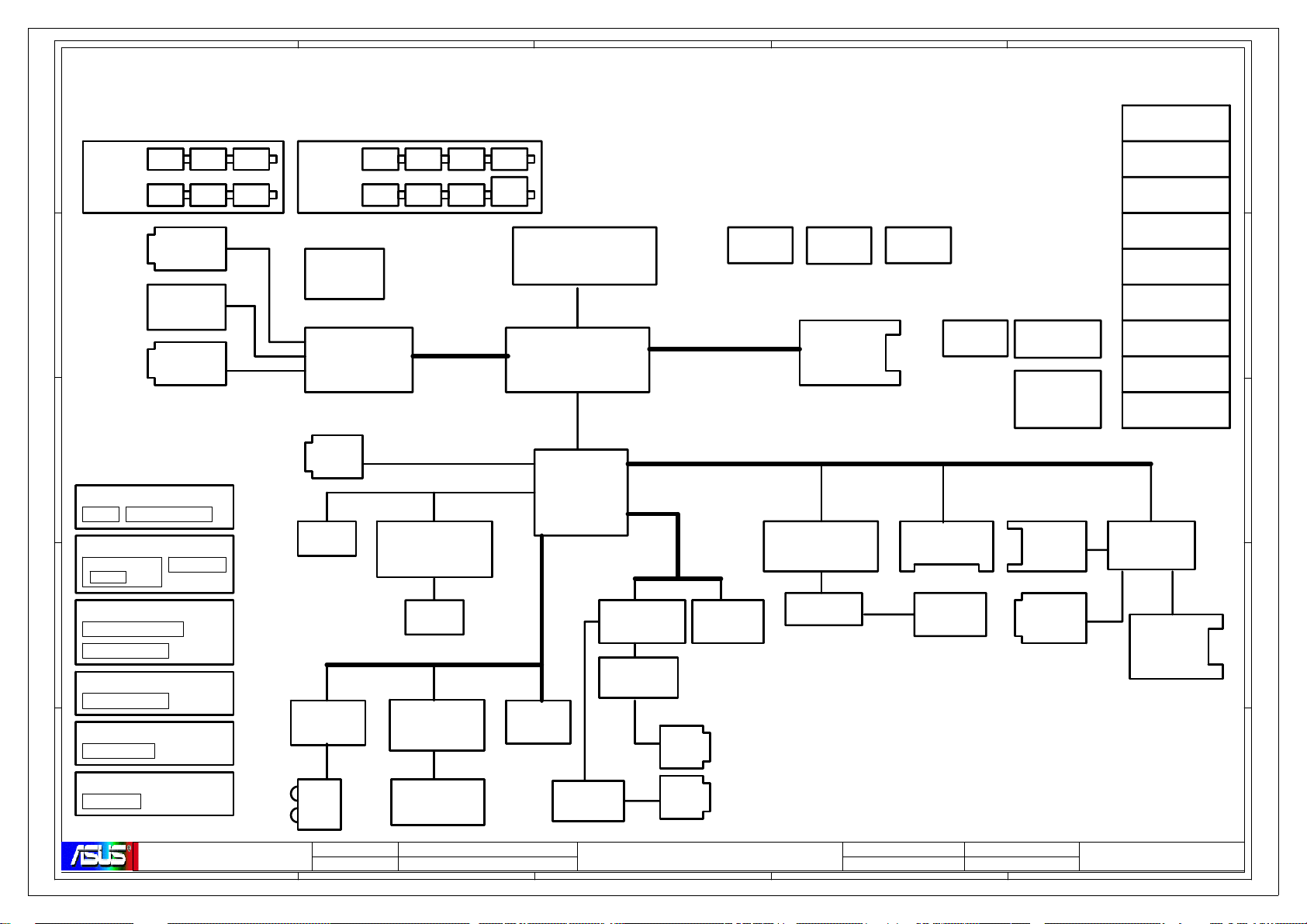

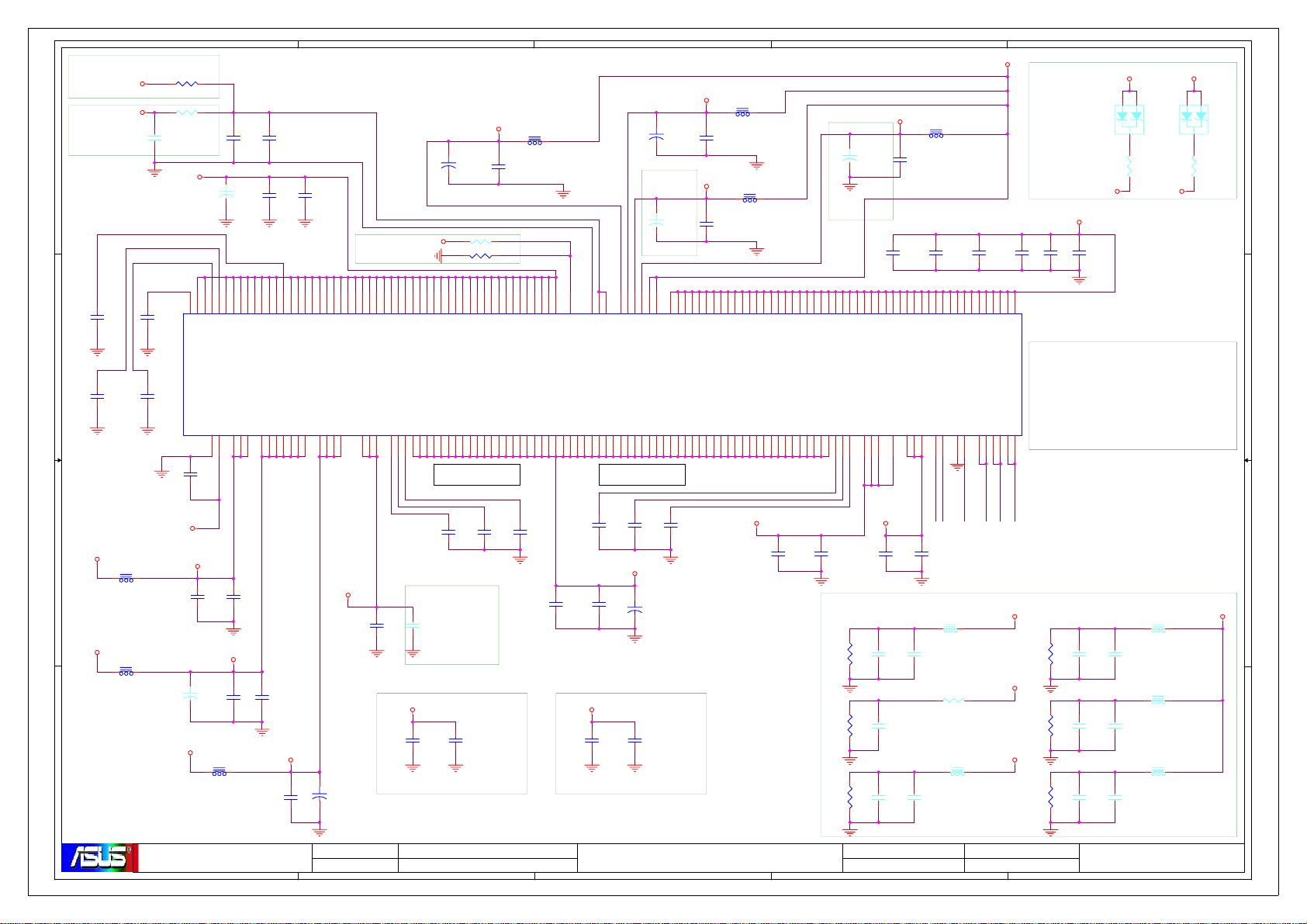

W3V/A:Dothan & Alviso-PM+M24-CSP/Alviso-GM

BLOCK DIAGRAM

1 1

2nd

BATTERY

(3S2P)

58 58

TV CONN

21

2 2

LVDS &

INVERTER

CONN

20

CRT CONN

21

3 3

KEYBOARD COVER FPC

LEDs

LID SENSOR

TOUCHPAD BOARD

LED FPC

LEDs

TOUCHPAD

MAIN

BATTERY

(4S2P)

CLOCK GEN.

ICS954213

ATI

M24/M22

16,17,18,19

USB x3

29

PATA

SWAP

BAY

28

12

PCI-E x16

SATA to PATA

BRIDGE

SILICON IMAGE

Sil3811

USB2.0

IDE_BUS

SATA

26

Dothan

478 uFCPGA

HOST BUS

AGTL 1.468V,133MHZ

ALVISO

1257 uFCBGA

7,8,9,10,11

DMI x4

ICH6-M

609 BGA

22,23,24,25

CPU

....

4,5

DDR2 SDRAM 400/533MHz

PCI_BUS

CAP/RES

3.3V, 33MHz

Azalia

RESET

6

DDR2 400/533

SODIMM X2

+1.8V

+0.9VS

GIGA LAN

MARVELL

88E8001

SM_BUS

45 36

...

13,14

MINI-PCI

37

TYPEII

DDR

CAP/RES

39

15

DCIN

RTC

FAN

CON.

Thermal

Sensor

(MAX6657)

3-IN-1

CARD

READER

46

6

VCORE

SYSTEM

1.5V,1.8V,

1.05V,2.5V

CHARGE

PIC16C54

BATLOW/SD#

LOAD Switch

VGA VCORE

1.5VA,0.9VS

CARDBUS

RICOH

R5C841

49

50

51

55

54

56

57

52

53

4042

PATA

D

RJ11+RJ45

JACK CONN

1394

38

SLOT

42

DESIGN ENGINEER :SCHEMATIC FILE NAME :

CARDBUS

1 SLOT

VCCA, VCCB

VPPA, VPPB

Alice Shih

E

41

AUDIO DJ FPC

AUDIO DJ SWITCH

4 4

AUDIO DJ LED

HDD

27

LPC, 33MHz

HOTKEY FPC

INSTANT KEYS

SUPER I/O

DC-IN BOARD

DC-IN JACK

ODD BOARD

5 5

ODD CON.

bom

PROJECT:

A

W3V

SMSC

47N207

FIR

31

REVISION

2.1

KEYBOARD

CONTROLLER

M3885XHP

INTERNAL

KEYBOARD

DATE:

SHEET OF

B

32

32

Monday, January 17, 2005

2 63

FWH

3130

MIC AMP

NJM2100

Azalia

CODEC

ALC861-VS

AUDIO AMP

TPA0212

35

DESCRIPTION:

C

Azalia

MDC

CONN.

33

34

Headphone

34

MIC IN

34

38

BLOCK DIAGRAM

LAN IO

38

RELEASE DATE :

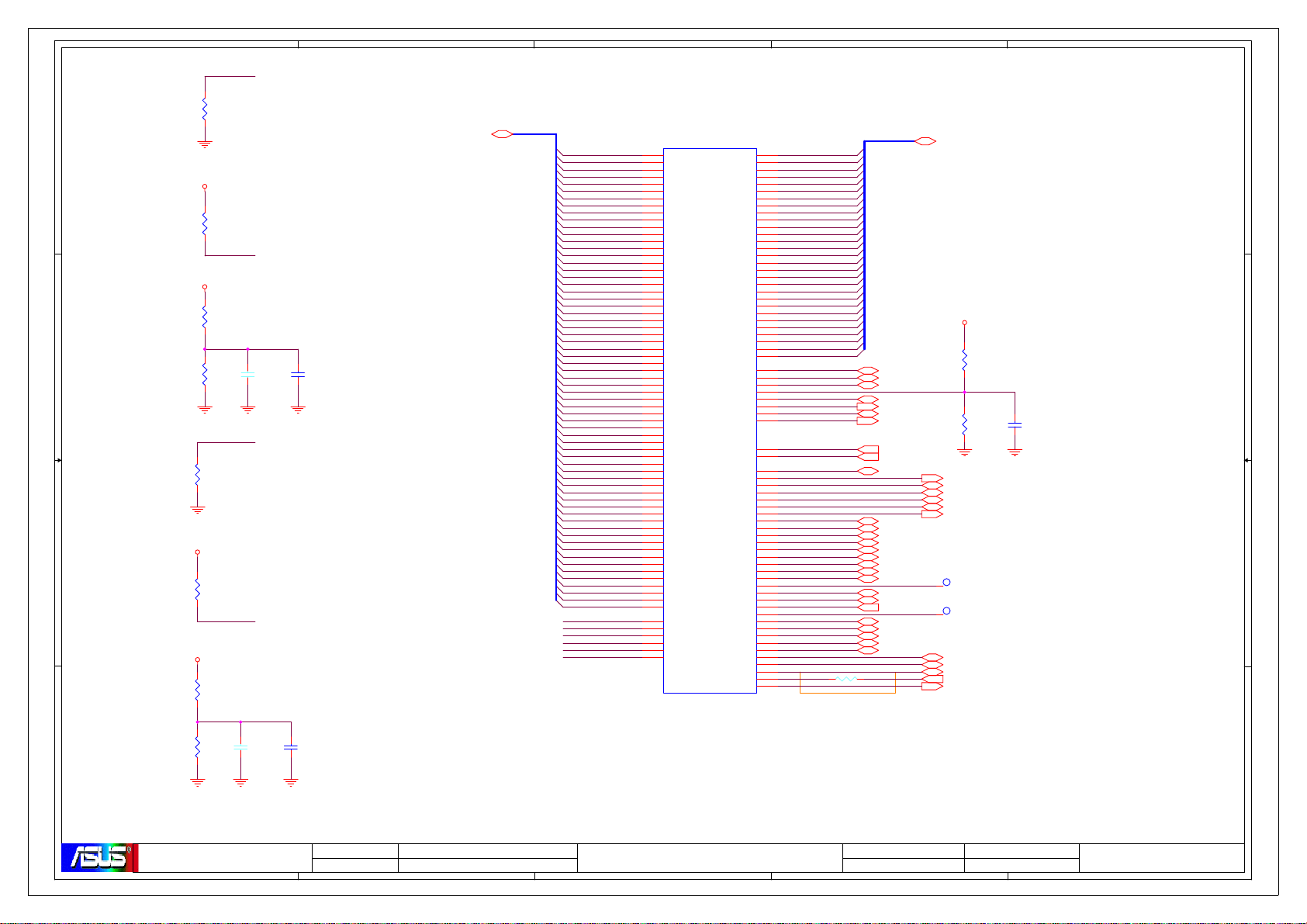

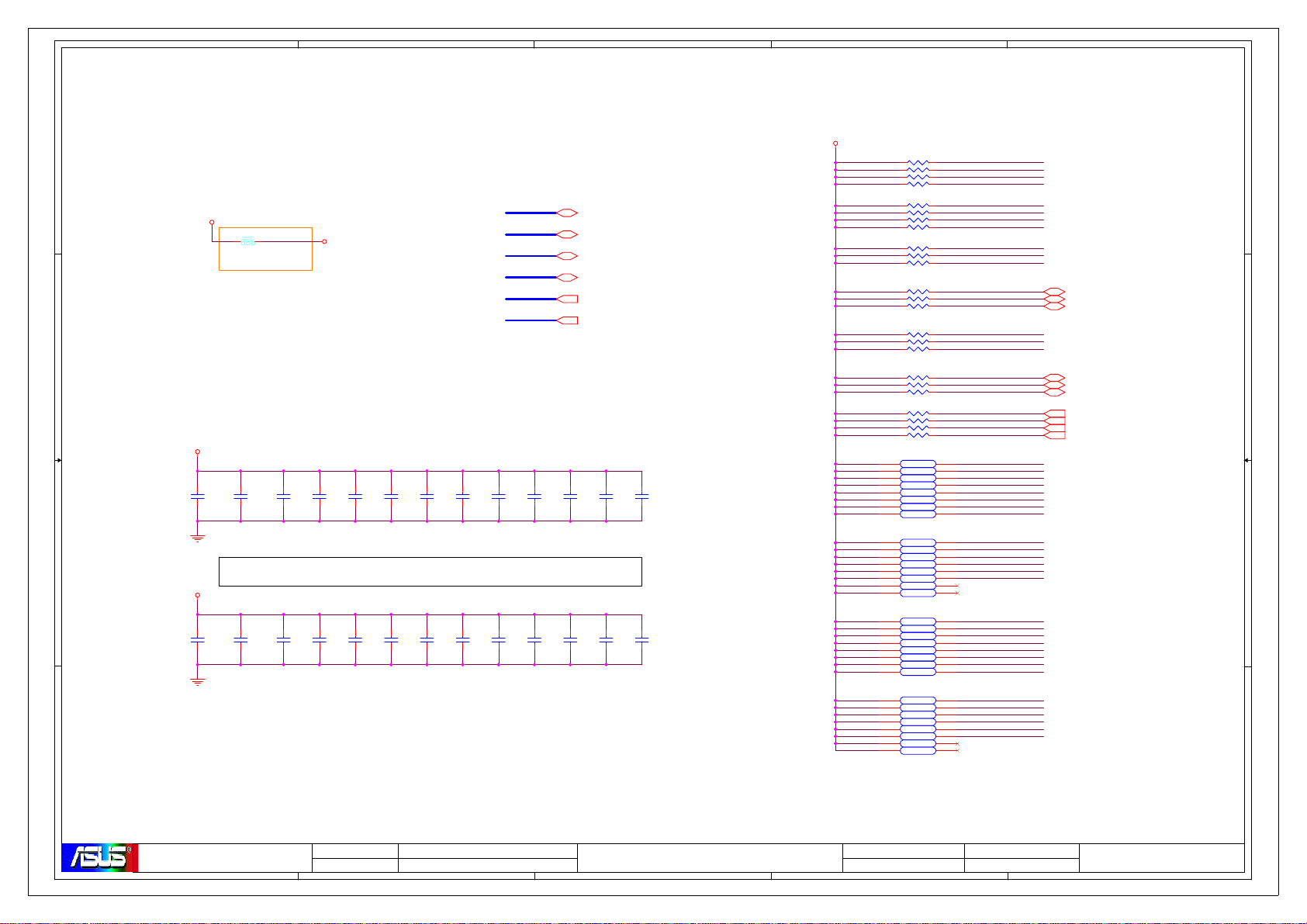

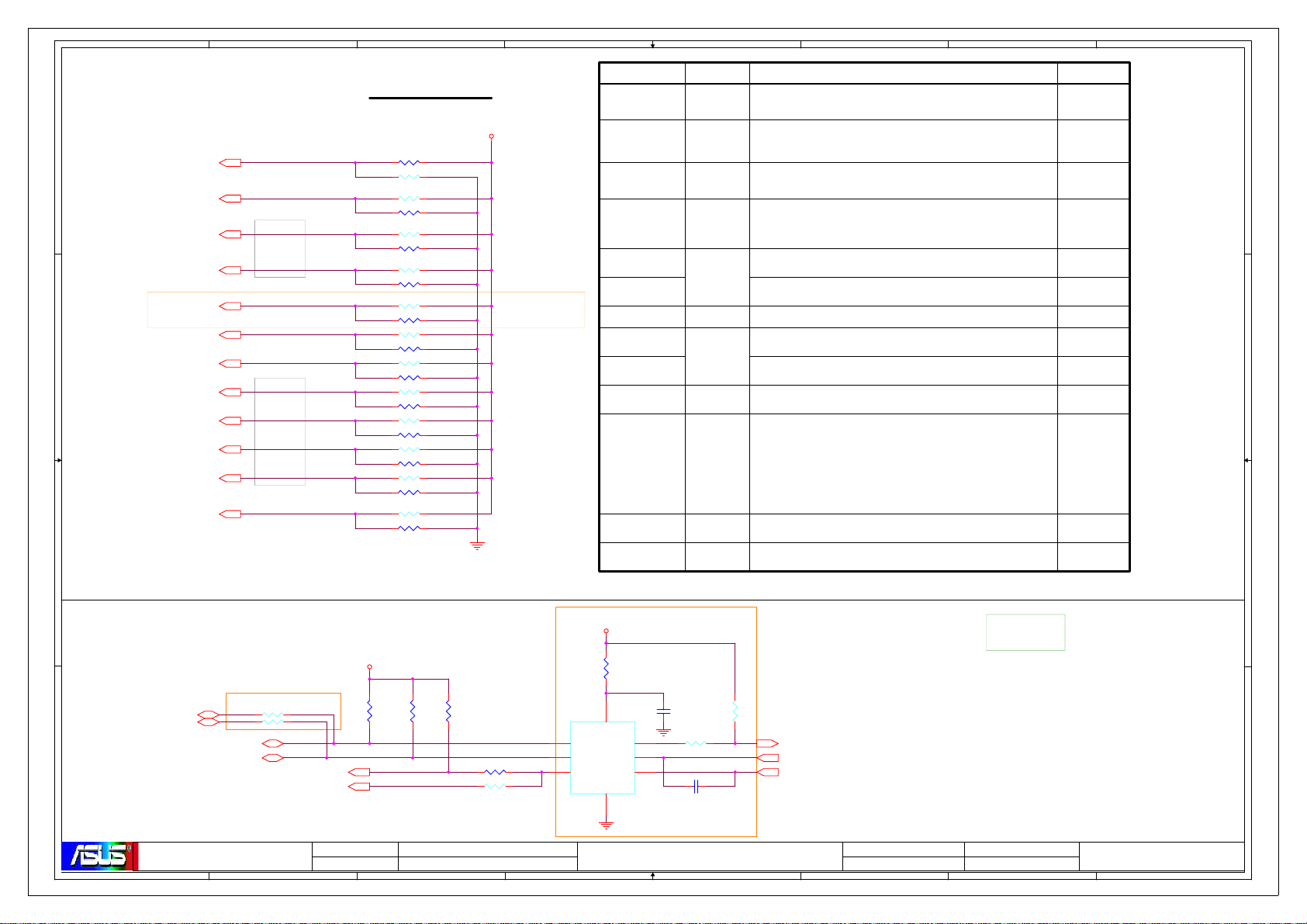

Page 3

A

B

C

D

E

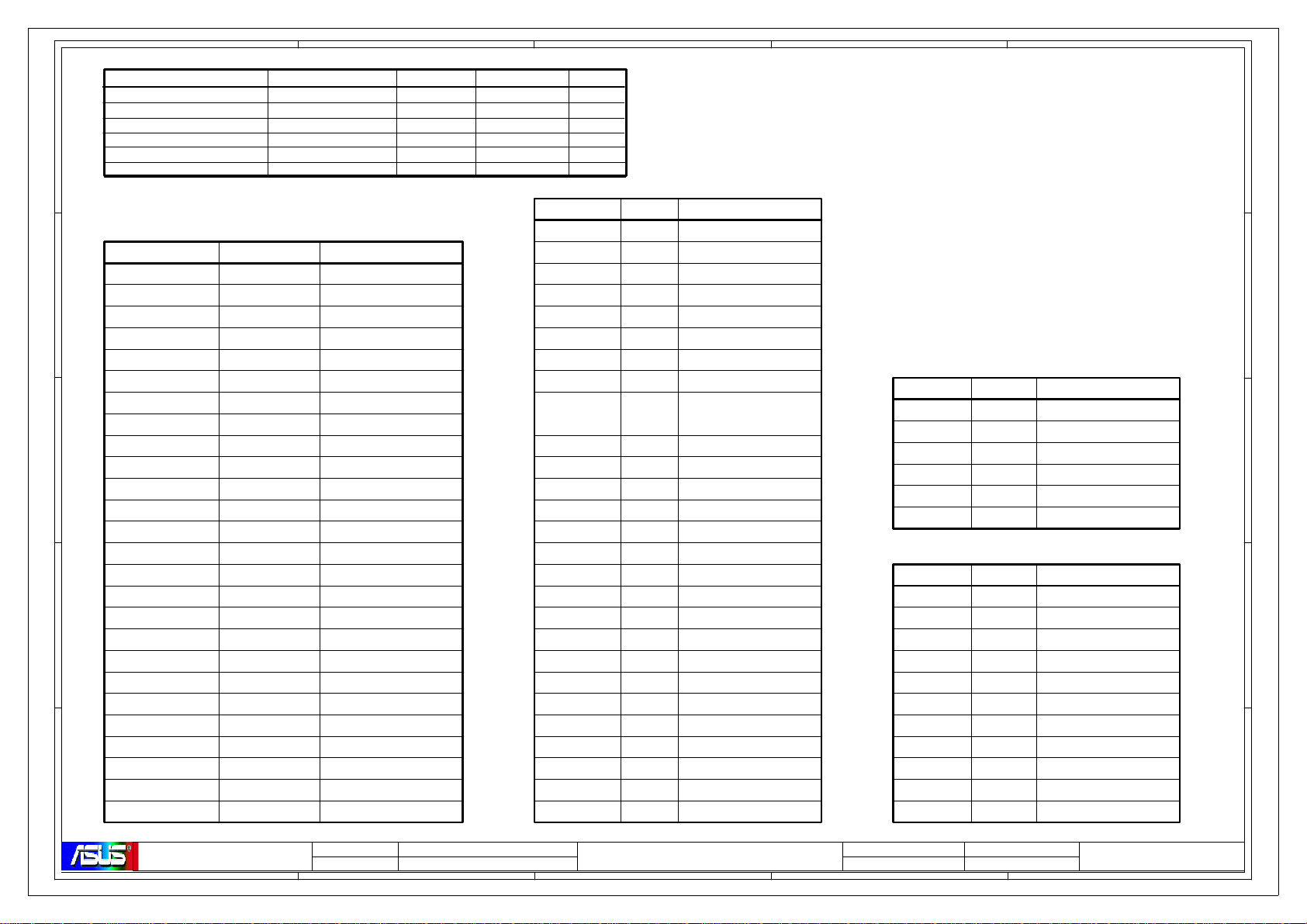

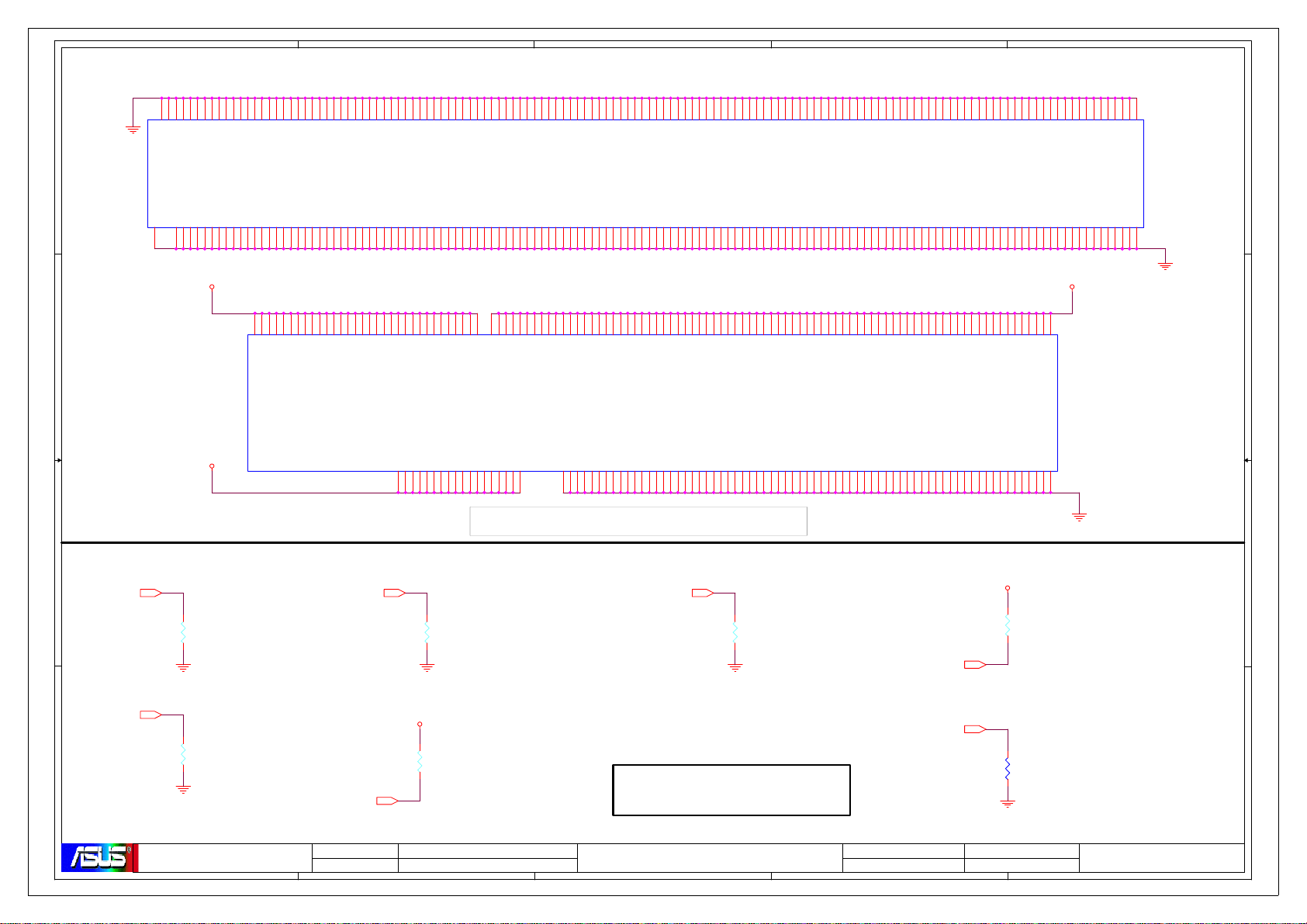

PCI Device

Chipset (Host to PCI)

IDSEL#

(AD30 internal)

AD18

1 1

LAN --88E8001

CardBus

1394

AD16

AD17

AD17

REQ/GNT#

n/a

3Mini_PCI

1

1

Interrupts

B,D

C0

B

A

3 IN 1 1 C

PC/PCI

SMBUS ADDRESS :

Azalia : PCI_INTB#

USB 0,1 : PCI_INTA#

USB 2,3 : PCI_INTD#

USB 4,5 : PCI_INTC#

CLK = 1101001x ( D2 )

DDR_SODIMM0 = 1010010x ( A4 )

DDR_SODIMM1 = 1010000x ( A0 )

M38857_GPIO Used_As Signal_Name

P20

ICH6M_GPIO Used As Signal Name

GPIO00 GPI

2 2

GPIO01 GPI

GPIO06 GPI

GPIO07 GPI

GPIO08 GPI

GPIO11 GPI

GPIO12 GPI

GPIO13 GPI

GPIO14 GPI

3 3

GPIO15 GPI

GPIO16 GPO

GPIO17 GPO

GPIO21 GPO

GPIO23 GPO

GPIO24 GPO

GPIO25 BLINK

4 4

GPIO26 GPI

GPIO27 GPI

GPIO28 GPI

GPIO29 GPI

GPIO30 GPI

GPIO31 GPI

GPIO33 GPO

GPIO34 GPO

5 5

GPIO40 GPI

GPIO41 GPI

bom

PROJECT:

A

W3V

KBDDT0

KBDDT1

PM_BMBUSY#

FIR_SEL

EXTSMI#_3A

LID_ICH#_3A

KBDSCI_3

ATI_OVERTEMP#

GPI14

CHG_EN#_OC

GPO16

GPO17

BACK_OFF#

FWH_WP#

CB_SD#

ICH6_1HZ

SATA_DET_#0

PCB_VID0

PCB_VID1

PCB_VID2

SATA_DET_#2

AGP_EXT

XIDE_EN#_3

OP_SD#

PID0

PID1

REVISION

2.1

DATE:

SHEET OF

Monday, January 17, 2005

B

363

P21 GPO

P22

P23

P42

P43

P44 GPO KBCPURST_3Q

P45

P46 GPO KBSCI_3Q

P50

P51

P52

P53 GPO BAT_LOW#_KBC

P54

P55

P56

P57

P60

P61

P62

P63

P64

P65

P66

P67

P76

P77

DESCRIPTION:

GPO KBCRSM

BAT_SEL

GPO BAT_LEARN

GPO MSK_INSTKEY#

GPO

GPO KBC_GA20

GPIP47 PM_CLKRUN#

GPI BAT_LLOW#_KBC

GPO

GPO WIRELESS_LED#

GPI

GPI

GPO FAN_DA

GPO

GPI

GPI

GPI

GPI

GPI ACIN_OC

GPI

GPO

GPI

GPIO

GPO

WATCHDOG

SWDJ_EN#GPI

DJ_LED_EN

BAYDOCK_IN#

BAT1_IN#_OC

ADJ_BL

BT_#

INTERNET_#

CPUFAN_SPD_A

WIRELESS_#

MARATHON_#

PANLOCK_#

BAT2_IN#_OC

SMD_BAT_KBC

SMC_BAT_KBC

SYSTEM INFORMATION

C

RELEASE DATE :

THERMAL = 1001100x ( 98 )

M38857_GPIO Used_As Signal_Name

P27

P26

P25

P24

P41

P40 GPO KBC_EXTSMI

47N207_GPIO Used_As Signal_Name

GP10

GP11

GP12

GP13

GP14

GP15

GP16

GP17

GP34

GP35

GP36

D

GPO

GPO

GPO

GPO

GPO BT_LED#

GPI

GPI

GPI

GPI

GPIO

GPO

GPO

GPO

GPO OVER_CLK1

GPO

GPO

--

NUM_LED#

CAP_LED#

SET_PCIRSTNS#

BAY_IN0

BAY_IN1

--

SW_RST#

--

BAY_RST

DJKEY_EN

802_EN#

OVER_CLK2

--

<OrgName>

DESIGN ENGINEER :SCHEMATIC FILE NAME :

M.Y.

E

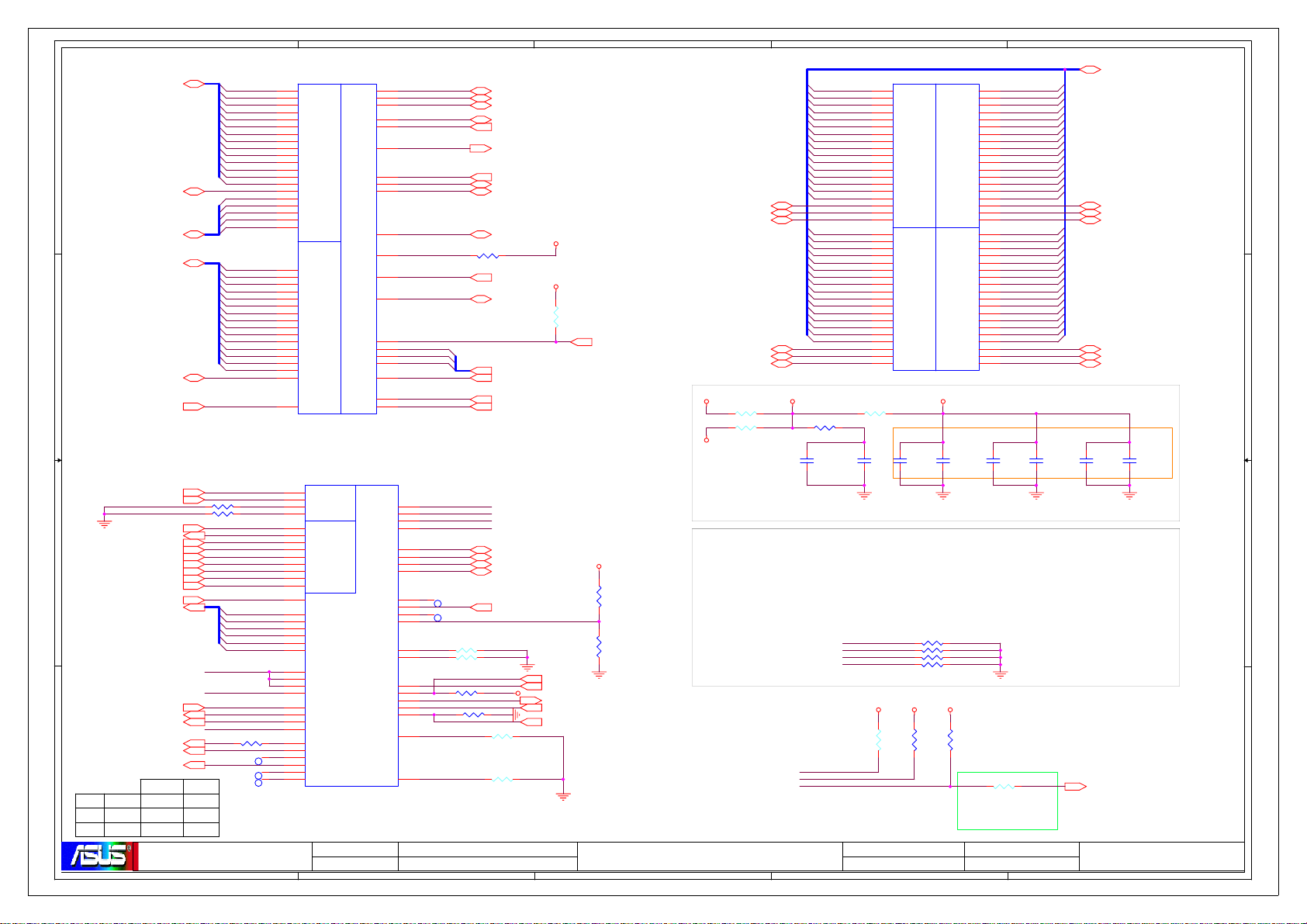

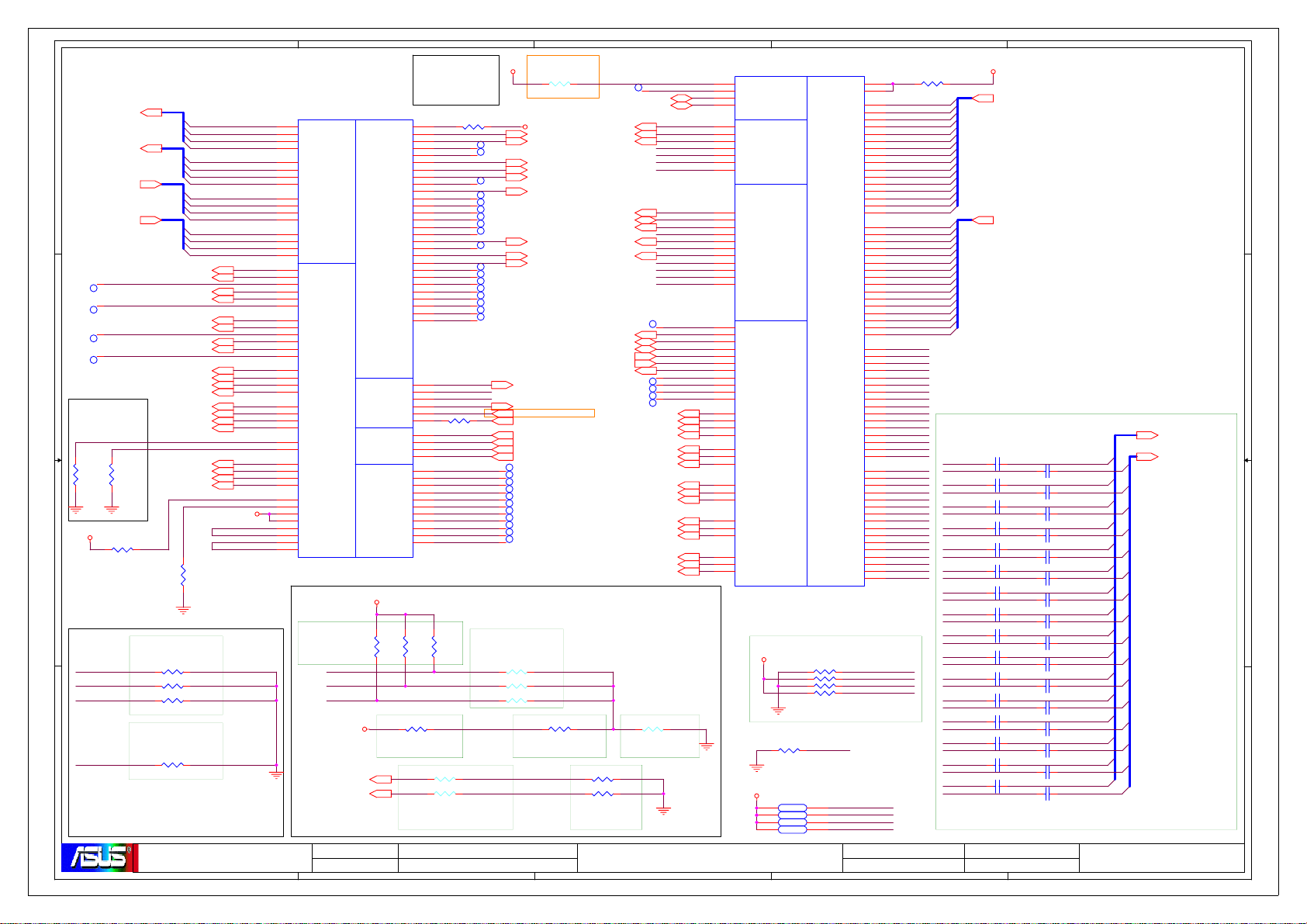

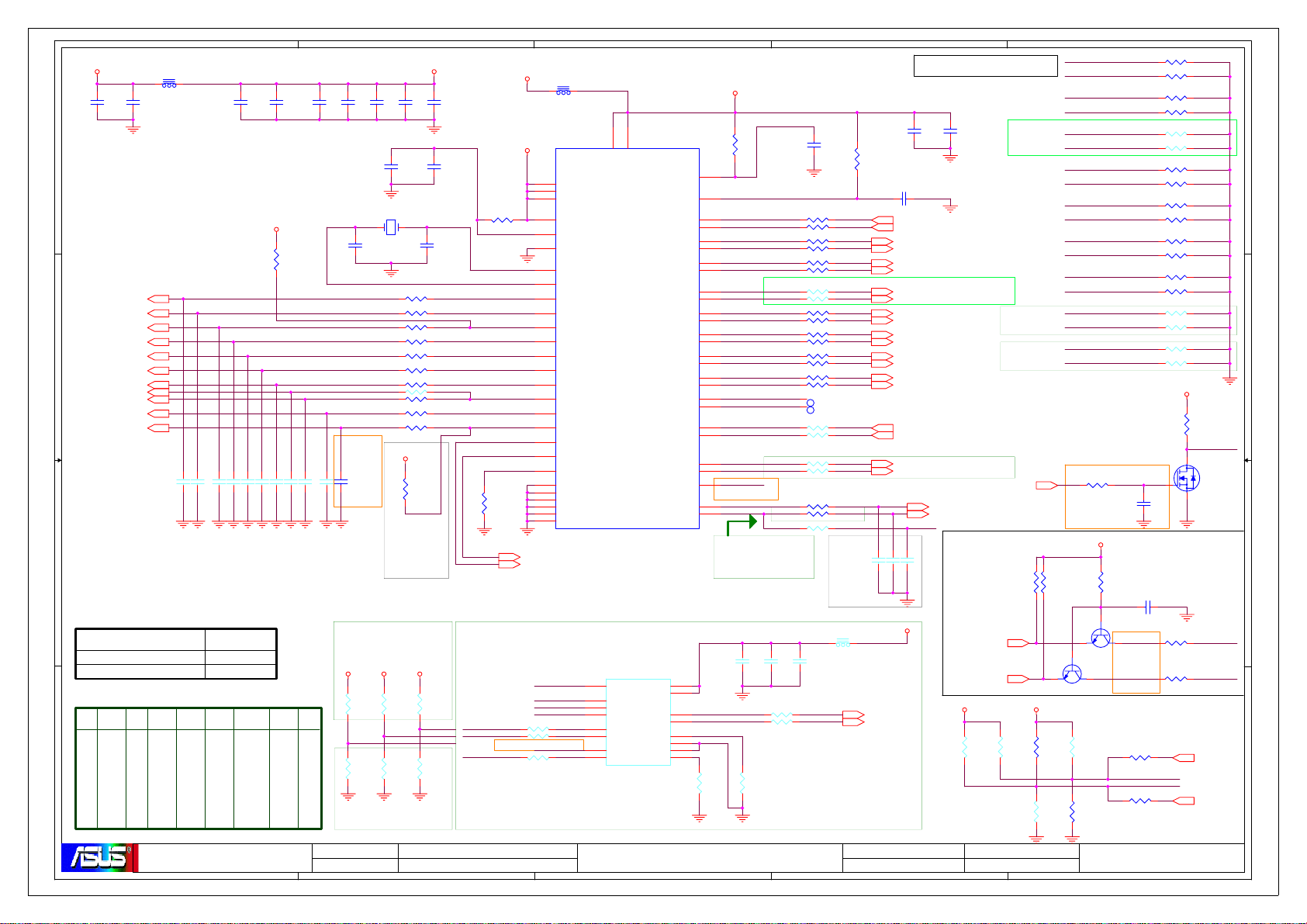

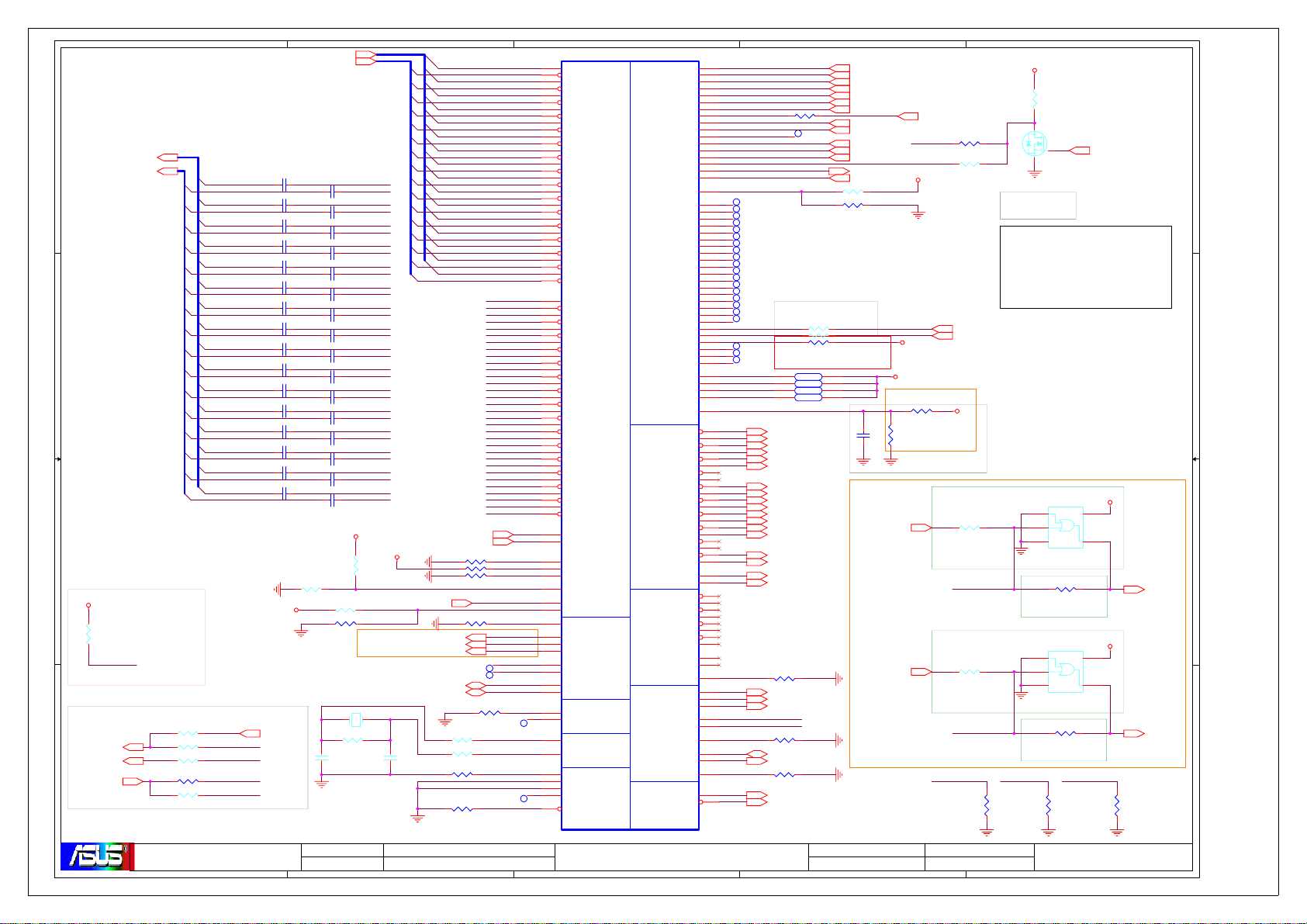

Page 4

5

H_A#[16:3]7

D D

H_ADSTB#07

H_REQ#[4:0]7

H_A#[31:17]7

C C

H_ADSTB#17

DPWR#7

H_A#16

H_A#15

H_A#14

H_A#13

H_A#12

H_A#11

H_A#10

H_A#9

H_A#8

H_A#7

H_A#6

H_A#5

H_A#4

H_A#3

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_A#31

H_A#30

H_A#29

H_A#28

H_A#27

H_A#26

H_A#25

H_A#24

H_A#23

H_A#22

H_A#21

H_A#20

H_A#19

H_A#18

H_A#17

AA2

AA3

AF1

AE1

AF3

AD6

AE2

AD5

AC6

AB4

AD2

AE4

AD3

AC3

AC7

AC4

AF4

AE5

C19

Y3

U1

Y1

Y4

W2

T4

W1

V2

R3

V3

U4

P4

U3

T1

P1

T2

P3

R2

U52B

A[16]#

A[15]#

A[14]#

A[13]#

A[12]#

A[11]#

A[10]#

A[9]#

A[8]#

A[7]#

A[6]#

A[5]#

A[4]#

A[3]#

ADSTB[0]#

REQ[4]#

REQ[3]#

REQ[2]#

REQ[1]#

REQ[0]#

A[31]#

A[30]#

A[29]#

A[28]#

A[27]#

A[26]#

A[25]#

A[24]#

A[23]#

A[22]#

A[21]#

A[20]#

A[19]#

A[18]#

A[17]#

ADSTB[1]#

DPWR#

SOCKET479P

ADS#

PRDY#

PREQ#

BNR#

BPRI#

DBR#

ADDRESS GROUP 0ADDRESS GROUP 1

DEFER#

DRDY#

DBSY#

BR0#

CONTROL

IERR#

INIT#

LOCK#

RESET#

RS[2]#

RS[1]#

RS[0]#

TRDY#

HIT#

HITM#

P/N = 12-046004791

U52C

CLK_CPU_BCLK12

CLK_CPU_BCLK#12

H_A20M#22

H_FERR#22

H_IGNNE#22

H_DPSLP#22

B B

VCCA layout: T/S:

100mil/25mil

H_CPUSLP#7,22

H_STPCLK#22

H_PWRGD22

VR_VID[5:0]49

120mA

THERMDA6

THERMDC6

H_THRMTRIP_S#6

PM_PSI#49

CPU_BSEL012,48

A A

FSB BSEL1 BSEL0 BSEL0

CPU_BSEL112

A-STEP B-STEP

1 2

R756 49.9Ohm 1%

1 2

R754 49.9Ohm 1%

H_INTR22

H_NMI22

H_SMI#22

1.05V OUTPUT

+1.8VS_VCCA

+1.8VS_PROC

H_PROCHOT_S#

R192 0Ohm

H_PWRGD

VR_VID5

VR_VID4

VR_VID3

VR_VID2

VR_VID1

VR_VID0

T124

T312

T125

B15

BCLK[0]

B14

BCLK[1]

A16

ITP_CLK[0]

A15

ITP_CLK[1]

C2

A20M#

D3

FERR#

A3

IGNNE#

A6

SLP#

D1

LINT0

D4

LINT1

B4

SMI#

C6

STPCLK#

E4

PWRGOOD

H4

VID[5]

G4

VID[4]

G3

VID[3]

F3

VID[2]

F2

VID[1]

E2

VID[0]

AC26

VCCA[3]

N1

VCCA[2]

B1

VCCA[1]

F26

VCCA[0]

B18

THERMDA

A18

THERMDC

C17

THERMTRIP#

B17

PROCHOT#

E1

12

RSVD5

C16

RSVD4

C3

1

RSVD3

C14

RSVD2

AF7

1

RSVD1

1

B2

RSVD0

SOCKET479P

COMP[3]

COMP[2]

HOSTCLKLEGACY CPU

COMP[1]

COMP[0]

BPM[3]#DPSLP#

BPM[2]#

BPM[1]#

BPM[0]#

GTLREF[3]

GTLREF[2]

GTLREF[1]

GTLREF[0]

MISC

VCCSENSE

VSSSENSE

400 0 N/A 1

533 0 N/A 0

bom

PROJECT:

5

W3V

REVISION

2.1

4

N2

A10

B10

L1

J3

A7

L4

H2

M2

N4

H_IERR#

A4

B5

J2

B11

H_RS#2

L2

H_RS#1

K1

H_RS#0

H1

M3

K3

K4

AB1

AB2

P26

P25

C9B7

A9

B8

C8

AC1

1

G1

E26

1

AD26

R740 1KOhm /*

C5

TEST1

TEST2

TRST#

R781 1KOhm /*

F23

A13

TCK

C12

TDO

TMS

TDI

R750 150Ohm 1%

A12

C11

B13

VCCSENSE

AE7

VSSSENSE

AF6

Monday, January 17, 2005

DATE:

SHEET OF

4

H_ADS# 7

H_BPM#4 6

H_BPM#5 6

H_BNR# 7

H_BPRI# 7

H_DBRESET# 6,22

H_DEFER# 7

H_DRDY# 7

H_DBSY# 7

H_BR0# 7

R738 56Ohm

H_COMP3

H_COMP2

H_COMP1

H_COMP0

T126

T326

1 2

1 2

R753 680Ohm

12

H_INIT# 22

H_LOCK# 7

H_RS#[2:0] 7

H_TRDY# 7

H_HIT# 7

H_HITM# 7

H_BPM#3 6

H_BPM#2 6

H_BPM#1 6

H_BPM#0 6

H_DPRSTP# 22

12

12

R195 54.9Ohm 1%

R194 54.9Ohm 1%

12

/*

12

/*

4 63

+VCCP

+VCCP

+VCCP

12

R748

54.9Ohm

1%

/*

GTLREF0

TDI 6

TCK 6

TDO 6

TMS 6

TRST# 6

H_CPURST# 6,7

+VCCP

12

R791

1KOhm

R790

2KOhm

1%

1 2

DESCRIPTION:

3

H_DINV#07

H_DSTBN#07

H_DSTBP#07

H_DINV#17

H_DSTBN#17

H_DSTBP#17

+1.8VS

+1.5VS

DOTHAN CPU(1)

3

VCCA_+1.5VS_+1.8VS +1.8VS_VCCA

R784 0Ohm

1 2

/*

R783 0Ohm

1 2

/*

2

H_D#15

H_D#14 H_D#46

H_D#13

H_D#12

H_D#11

H_D#10

H_D#9

H_D#8

H_D#7

H_D#6

H_D#5

H_D#4

H_D#3

H_D#2

H_D#1

H_D#0

H_D#31

H_D#30

H_D#29

H_D#28

H_D#27

H_D#26

H_D#25

H_D#24

H_D#23

H_D#22

H_D#21

H_D#20

H_D#19

H_D#18

H_D#17

H_D#16

1 2

+1.8VS_PROC

12

C769

10UF/10V

R785 0Ohm /*

R782 0Ohm

C25

E23

B23

C26

E24

D24

B24

C20

B20

A21

B26

A24

B21

A22

A25

A19

D25

C23

C22

K25

N25

H26

M25

N24

L26

J25

M23

J23

G24

F25

H24

M26

L23

G25

H23

J26

K24

L24

1 2

12

C770

0.01UF

U52A

D[15]#

D[14]#

D[13]#

D[12]#

D[11]#

D[10]#

D[9]#

D[8]#

D[7]#

D[6]#

D[5]#

D[4]#

D[3]#

D[2]#

D[1]#

D[0]#

DINV[0]#

DSTBN[0]#

DSTBP[0]#

D[31]#

D[30]#

D[29]#

D[28]#

D[27]#

D[26]#

D[25]#

D[24]#

D[23]#

D[22]#

D[21]#

D[20]#

D[19]#

D[18]#

D[17]#

D[16]#

DINV[1]#

DSTBN[1]#

DSTBP[1]#

SOCKET479P

12

C198

10UF/10V

DATA GROUP 0DATA GROUP 1

D[47]#

D[46]#

D[45]#

D[44]#

D[43]#

D[42]#

D[41]#

D[40]#

D[39]#

D[38]#

D[37]#

D[36]#

DATA GROUP 2DATA GROUP 3

D[35]#

D[34]#

D[33]#

D[32]#

DINV[2]#

DSTBN[2]#

DSTBP[2]#

D[63]#

D[62]#

D[61]#

D[60]#

D[59]#

D[58]#

D[57]#

D[56]#

D[55]#

D[54]#

D[53]#

D[52]#

D[51]#

D[50]#

D[49]#

D[48]#

DINV[3]#

DSTBN[3]#

DSTBP[3]#

12

C201

0.01UF

Y25

AA26

Y23

V26

U25

V24

U26

AA23

R23

R26

R24

V23

U23

T25

AA24

Y26

T24

W25

W24

AF26

AF22

AF25

AD21

AE21

AF20

AD24

AF23

AE22

AD23

AC25

AC22

AC20

AB24

AC23

AB25

AD20

AE24

AE25

+1.8VS_VCCA

12

H_D#47

H_D#45

H_D#44

H_D#43

H_D#42

H_D#41

H_D#40

H_D#39

H_D#38

H_D#37

H_D#36

H_D#35

H_D#34

H_D#33

H_D#32

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

H_D#53

H_D#52

H_D#51

H_D#50

H_D#49

H_D#48

C200

10UF/10V

12

C202

0.01UF

Place near CPU pin

Layout note:

COMP0 and COMP2 need to be Zo=27.4ohm traces.

Best estimate is 18mil wide trace for outer layers and

14mil if on internal layer. See RDDP of Banias.

Traces should be shorter than 0.5". Refer to latest CS layout

COMP1, COMP3 should be routed as Zo=55ohm

traces shorter than 0.5"

R190 54.9Ohm 1%

H_COMP3

H_COMP2

H_COMP1

H_COMP0

Reserve for ITP

=> check

H_BPM#5

H_PROCHOT_S#

H_PWRGD

RELEASE DATE :

R189 27.4Ohm 1%

R786 54.9Ohm 1%

R787 27.4Ohm 1%

+VCCP

12

R745

56Ohm

/*

2

12

R757

56Ohm

12

12

12

12

+VCCP+VCCP

12

R737

200Ohm

R736 1KOhm

12

Reserve for ITP

ITP: Stuff

No ITP: N/A

<OrgName>

/*

H_D#[63:0] 7

H_DINV#2 7

H_DSTBN#2 7

H_DSTBP#2 7

H_DINV#3 7

H_DSTBN#3 7

H_DSTBP#3 7

12

C778

10UF/10V

H_PWRGD_ITP 6

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

12

1

R1.1#1

C768

0.01UF

M.Y.

Page 5

5

4

3

2

1

D D

C C

B B

P23

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

L21

M22

N21

P22

R21

T22

U21

U52D

W4

VCCQ[1]

VCCQ[0]

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

K6

VCCP12

L5

VCCP13

VCCP14

M6

VCCP15

VCCP16

N5

VCCP17

VCCP18

P6

VCCP19

VCCP20

R5

VCCP21

VCCP22

T6

VCCP23

VCCP24

VCCP25

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

AE19

AF8

AF10

AF12

AF14

AF16

AF18

VCC

VCC63

VCC62

VCC61

VCC64

VCC65

AE13

AE11

AE9

AE15

AE17

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

SOCKET479P

D6

D8

D18

D20

D22

E5

E7

E9

E17

E19

E21

F6

F8

F18

F20

F22

G5

G21

H6

H22

J5

J21

K22

U5

V6

V22

W5

W21

Y6

Y22

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC9

AC11

AC13

AC15

AC17

AC19

AD8

AD10

AD12

AD14

AD16

AD18

+VCORE+VCCP

AF24

AF21

AF19

AF17

AF15

AF13

AF11

AF9

AF5

AF2

AE26

AE23

AE20

AE18

AE16

AE14

AE12

AE10

AE8

AE6

AE3

AD25

AD22

AD19

AD17

AD15

AD13

AD11

AD9

AD7

AD4

VSS167

VSS90

VSS166

VSS91

AD1

VSS165

VSS164

VSS163

VSS162

VSS95

VSS94

VSS93

VSS92

P2

N26

N23

N22N6N3

P5

VSS161

VSS96

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS150

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

AC24

AC21

AC18

AC16

AC14

AC12

AC10

AC8

AC5

AC2

AB26

AB23

AB21

AB19

AB17

AB15

AB13

AB11

AB9

AB7

AB5

AB3

AA25

AA22

AA20

AA18

AA16

AA14

AA12

AA10

AA8

AA6

AA4

AA1

Y24

Y21

Y5

Y2

W26

W23

W22

W6

W3

V25

V21

V5

V4

V1

U24

U22

U6

U2

T26

T23

T21

T5

T3

R25

R22

R6

R4

R1

P24

P21

Mobile Dothan VID Table

0 0 0 0 0 0 1.708V

0 0 0 0 0 1 1.692V

0 0 0 0 1 0 1.676V

0 0 0 0 1 1 1.660V

0 0 0 1 0 0 1.644V

0 0 0 1 0 1 1.628V

0 0 0 1 1 0 1.612V

0 0 0 1 1 1 1.596V

0 0 1 0 0 0 1.580V

0 0 1 0 0 1 1.564V

0 0 1 0 1 0 1.548V

0 0 1 0 1 1 1.532V

0 0 1 1 0 0 1.516V

0 0 1 1 0 1 1.500V

0 0 1 1 1 0 1.484V

0 0 1 1 1 1 1.468V

0 1 0 0 0 0 1.452V

0 1 0 0 0 1 1.436V

0 1 0 0 1 0 1.420V

0 1 0 0 1 1 1.404V

0 1 0 1 0 0 1.388V

0 1 0 1 0 1 1.372V

0 1 0 1 1 0 1.356V

0 1 0 1 1 1 1.340V

0 1 1 0 0 0 1.324V

0 1 1 0 0 1 1.308V

0 1 1 0 1 0 1.292V

0 1 1 0 1 1 1.276V

0 1 1 1 0 0 1.260V

0 1 1 1 0 1 1.244V

0 1 1 1 1 0 1.228V

0 1 1 1 1 1 1.212V

VID[5..0]VID[5..0]

1 0 0 0 0 0 1.196V

1 0 0 0 0 1 1.180V

1 0 0 0 1 0 1.164V

1 0 0 0 1 1 1.148V

1 0 0 1 0 0 1.132V

1 0 0 1 0 1 1.116V

1 0 0 1 1 0 1.100V

1 0 0 1 1 1 1.084V

1 0 1 0 0 0 1.068V

1 0 1 0 0 1 1.052V

1 0 1 0 1 0 1.036V

1 0 1 0 1 1 1.020V

1 0 1 1 0 0 1.004V

1 0 1 1 0 1 0.988V

1 0 1 1 1 0 0.972V

1 0 1 1 1 1 0.956V

1 1 0 0 0 0 0.940V

1 1 0 0 0 1 0.924V

1 1 0 0 1 0 0.908V

1 1 0 0 1 1 0.892V

1 1 0 1 0 0 0.876V

1 1 0 1 0 1 0.860V

1 1 0 1 1 0 0.844V

1 1 0 1 1 1 0.828V

1 1 1 0 0 0 0.812V

1 1 1 0 0 1 0.796V

1 1 1 0 1 0 0.780V

1 1 1 0 1 1 0.764V

1 1 1 1 0 0 0.748V

1 1 1 1 0 1 0.732V

1 1 1 1 1 0 0.716V

1 1 1 1 1 1 0.700V

VoltageVoltage

A2

A5

A8

A11

A14

A17

A20

A23

A26

B3

B6

B9

B12

B16

B19

B22

B25

C1

C4

C7

C10

C13

C15

C18

C21

C24

D2

D5

D7

D9

D11

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

SOCKET479P

U52E

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

G23

VSS192

VSS65

G26H3H5

VSS191

VSS66

VSS190

VSS67

VSS189

VSS68

VSS188

VSS69

H21

VSS187

VSS186

VSS185

VSS70

VSS71

VSS72

H25J1J4J6J22

VSS184

VSS73

VSS183

VSS74

J24K2K5

VSS182

VSS75

VSS181

VSS76

VSS180

VSS77

K21

VSS179

VSS178

VSS177

VSS176

VSS175

GND

VSS82

VSS81

VSS80

VSS79

VSS78

K26

K23

VSS174

VSS173

VSS172

VSS171

VSS170

VSS169

VSS168

VSS89

VSS88

VSS87

VSS86

VSS85

VSS84

VSS83

M24

M21M5M4M1L25

L22L6L3

A A

bom

PROJECT:

5

W3V

REVISION

2.1

Monday, January 17, 2005

DATE:

SHEET OF

4

5 63

DESCRIPTION:

DOTHAN CPU (2)

3

RELEASE DATE :

2

<OrgName>

DESIGN ENGINEER :SCHEMATIC FILE NAME :

M.Y.

1

Page 6

A

VCORE 10uF/10V* 35

220uF/2V * 4

VCCP 0.1uF * 10 for CPU

150uF * 1 for CPU

0.1uF * 10 for Alviso

150uF * 2 for Alviso

4.7uF * 1 for Alviso

1 1

+VCORE

27A for 1.8G

12

12

2 2

12

10UF/10V

12

10UF/10V

3 3

+VCCP

4 4

12

C231

10UF/10V

C228

10UF/10V

C217

C213

C210

10UF/10V

12

10UF/10V

12

10UF/10V

12

10UF/10V

2.5A for 1.8G

12

+

CE29

150U/4.0V

C241

C218

C225

12

12

10UF/10V

12

10UF/10V

12

10UF/10V

12

0.1UF

12

0.1UF

C211

10UF/10V

C242

C245

C223

C212

C226

2.2uF * 1 for Alviso

0.47uF * 2 for Alviso on A6 B2 G1 V1

0.22uF * 2 for Alviso on A6 B2 G1 V1

Decoupling guide from INTEL

12

12

10UF/10V

12

10UF/10V

12

10UF/10V

12

12

C749

10UF/10V

C234

C229

C233

C216

0.1UF

C207

0.1UF

12

C748

10UF/10V

12

C230

10UF/10V

12

C235

10UF/10V

12

C755

10UF/10V

12

0.1UF

12

0.1UF

C209

C205

12

C237

10UF/10V

12

10UF/10V

12

10UF/10V

DOTHAN VID TABLE

2.1

LFM

0.6G

1G1.4G

0.844V

CPU

HFM

VOLTAGE

FREQ.

1.8G

1.7G

5 5

bom

PROJECT:

1.308V

A

1.6G 1.2G

W3V

REVISION

B

12

C756

10UF/10V

12

C224

C221

12

12

C746

10UF/10V

12

C219

10UF/10V

+

CE14

Do Not Stuff

12

C208

0.1UF

0.1UF

C3/C4

0.748V1.196V1.228V1.260V1.292V

Monday, January 17, 2005

DATE:

SHEET OF

B

12

C754

10UF/10V

12

C723

10UF/10V

12

C215

10UF/10V

12

+

C222

CE30

Do Not Stuff

NEAR CPU

PIN W4

12

+

12

C244

0.1UF

6 63

12

C753

10UF/10V

12

C728

10UF/10V

12

C214

10UF/10V

CE12

220UF/2V

NEAR CPU

PIN P23

12

12

C722

10UF/10V

12

C732

10UF/10V

12

C227

10UF/10V

12

+

CE13

Do Not Stuff

/*

C206

0.1UF

DESCRIPTION:

C

H_BPM#54

H_BPM#44

H_BPM#34

H_BPM#24

H_BPM#14

H_BPM#04

+VCCP

ITP: Stuff

1 2

+3VS

1 2

R821

2.2KOhm

/*

R240

Do Not Stuff

/*

+VCCP

/*

No ITP: N/A

R789 54.9Ohm

1 2

12

H_PWRGD_ITP4

CTL_DATA8

CTL_CLK8

TCK4 TMS 4

R788

+2.5VS

H_THRMTRIP_S#4

GMCH_THRMTRIP#8

2.2KOhm

/*

1 2

ITP: Stuff

No ITP: N/A

SCL_3S12,13,14,19,21,36

SDA_3S12,13,14,19,21,36

PM_THRM#19,22,25

R769 0Ohm

1 2

R767 0Ohm

1 2

R1.1#33

Caps & THERMAL & ITP

C

1 2

1% /*

R822

27.4Ohm

1%

1 2

R239

U18

Do Not Stuff

/*

8

SMBCLK

7

SMBDATA

6

ALERT#

MAX6657

R772

75Ohm

RELEASE DATE :

D

CN28

1

1

3

3

5

5

7

7

9

9

11

11

13

13

15

15

17

17

19

19

21

21

23

23

25

25

27

27

29

29

31

31

33

33

35

35

37

37

39

39

41

41

43

43

45

45

47

47

49

49

51

51

53

53

55

55

57

57

59

59

61

NP_NC1

ITP_CON_60P

/*

ITP

+3VS

R212

200Ohm

1%

1 2

1

VCC

OVERT

DXP

DXN

GND

5

H_THRMTRIP#_R

+VCCP

12

R775

330Ohm

B

C

E12

3

Q132

PMBS3904

BUF_PLT_RST#8,21,22,23,28,30,31,32

D

2

2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

32

32

34

34

36

36

38

38

40

40

42

42

44

44

46

46

48

48

50

50

52

52

54

54

56

56

58

58

60

60

62

NP_NC2

12

4

2

3

SM Bus Address fix at:

1001 100x (98, 99), Resolution :

+/- 1 degree

C767

1 2

0.1UF

C239

0.1UF

1 2

C243 2200PF/10V

S

2

G

+VCCP

<OrgName>

ITP: Stuff

No ITP: N/A

R798

R796

54.9Ohm

220Ohm

1%

/*

1 2

1 2

/*

12

R799 27.4Ohm

1% /*

12

R800 22.6Ohm

1% /*

1 2

R801 220Ohm

/*

Reserve for ITP

Place resistance close ITP

THERMAL SENSOR

R1.1#16

R210

100KOhm

1 2

OS#_OC 47

THERMDA 4

THERMDC 4

R766 56Ohm

1 2

D

3

Q134

1

2N7002

DESIGN ENGINEER :SCHEMATIC FILE NAME :

E

R797

39.2Ohm

1%

1 2

10/10/10 mil

C920

100PF

1 2

/*

M.Y.

E

CLK_ITP_BCLK 12

CLK_ITP_BCLK# 12

H_DBRESET# 4,22

TDO 4

TRST# 4

TDI 4

H_CPURST# 4,7

H_THRMTRIP# 22

OTP_RESET# 47,53

Page 7

5

H_XRCOMP

24.9

R682

24.9Ohm

1%

1%

1 2

D D

+VCCP

54.9

1%

C C

24.9 1%

B B

A A

54.9 1%

221 1%

100 1%

R675

54.9Ohm

1%

1 2

H_XSCOMP

+VCCP

221

R690

221Ohm

1%

1%

1 2

100

1%

1 2

R706

24.9Ohm

1%

1 2

+VCCP

R698

54.9Ohm

1%

1 2

+VCCP

R705

221Ohm

1%

1 2

R704

100Ohm

1%

1 2

R685

100Ohm

1%

H_YRCOMP

H_YSCOMP

H_XSWING

12

C614

10UF/10V

/*

H_YSWING

12

C655

10UF/10V

/*

12

C592

0.1UF

12

C654

0.1UF

4

H_D#[0..63]4

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

3

U48D

E4

HD0#

E1

HD1#

F4

HD2#

H7

HD3#

E2

HD4#

F1

HD5#

E3

HD6#

D3

HD7#

K7

HD8#

F2

HD9#

J7

HD10#

J8

HD11#

H6

HD12#

F3

HD13#

K8

HD14#

H5

HD15#

H1

HD16#

H2

HD17#

K5

HD18#

K6

HD19#

J4

HD20#

G3

HD21#

H3

HD22#

J1

HD23#

L5

HD24#

K4

HD25#

J5

HD26#

P7

HD27#

L7

HD28#

J3

HD29#

P5

HD30#

L3

HD31#

U7

HD32#

V6

HD33#

R6

HD34#

R5

HD35#

P3

HD36#

T8

HD37#

R7

HD38#

R8

HD39#

U8

HD40#

R4

HD41#

T4

HD42#

T5

HD43#

R1

HD44#

T3

HD45#

V8

HD46#

U6

HD47#

W6

HD48#

U3

HD49#

V5

HD50#

W8

HD51#

W7

HD52#

U2

HD53#

U1

HD54#

Y5

HD55#

Y2

HD56#

V4

HD57#

Y7

HD58#

W1

HD59#

W3

HD60#

Y3

HD61#

Y6

HD62#

W2

HD63#

C1

HXRCOMP

C2

HXSCOMP

D1

HXSWING

T1

HYRCOMP

L1

HYSCOMP

P1

HYSWING

ALVISO_BGA1257

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HADSTB0#

HADSTB1#

HVREF

HBNR#

HBPR#

HBREQ0#

HCPURST#

HCLKINN

HOST

HCLKINP

HDBSY#

HDEFER#

HDINV0#

HDINV1#

HDINV2#

HDINV3#

HDPWR#

HDRDY#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HEDRDY#

HHITM#

HLOCK#

HPCREQ#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HRS0#

HRS1#

HRS2#

HCPUSLP#

HTRDY#

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HHIT#

G9

C9

E9

B7

A10

F9

D8

B10

E10

G10

D9

E11

F10

G11

G13

C10

C11

D11

C12

B13

A12

F12

G12

E12

C13

B11

D13

A13

F13

F8

B9

E13

J11

A5

D5

E7

H10

AB1

AB2

C6

E6

H8

K3

T7

U5

G6

F7

G4

K1

R3

V3

G5

K2

R2

W4

F6

D4

D6

B3

A11

A7

D7

B8

C7

A8

A4

C5

B4

G8

B5

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR#

H_BPRI#

H_BR0#

H_CPURST#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

TP_H_EDRDY#

TP_H_PCREQ#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

R115 0Ohm

1 2

H_ADS# 4

H_ADSTB#0 4

H_ADSTB#1 4

H_BNR# 4

H_BPRI# 4

H_BR0# 4

H_CPURST# 4,6

CLK_MCH_BCLK# 12

CLK_MCH_BCLK 12

H_DBSY# 4

H_DRDY# 4

H_DSTBN#0 4

H_DSTBN#1 4

H_DSTBN#2 4

H_DSTBN#3 4

H_DSTBP#0 4

H_DSTBP#1 4

H_DSTBP#2 4

H_DSTBP#3 4

H_HIT# 4

H_HITM# 4

H_LOCK# 4

H_REQ#0 4

H_REQ#1 4

H_REQ#2 4

H_REQ#3 4

H_REQ#4 4

/*

2

H_A#[3..31] 4

+VCCP

100 1%R

R125

100Ohm

1%

1 2

H_VREF

200 1%R

12

1 2

H_DEFER# 4

H_DINV#0 4

H_DINV#1 4

H_DINV#2 4

H_DINV#3 4

DPWR# 4

T55

1

T264

1

H_RS#0 4

H_RS#1 4

H_RS#2 4

H_CPUSLP# 4,22

H_TRDY# 4

R124

200Ohm

1%

C120

0.1UF

1

bom

PROJECT:

5

W3V

REVISION

2.1

Monday, January 17, 2005

DATE:

SHEET OF

4

7 63

DESCRIPTION:

MCH: CPU

3

RELEASE DATE :

2

<OrgName>

DESIGN ENGINEER :SCHEMATIC FILE NAME :

M.Y.

1

Page 8

5

DMI_TXN[0..3]23

DMI_TXP[0..3]23

D D

DMI_RXN[0..3]23

DMI_RXP[0..3]23

TP_SMCK2

1

T109

TP_SMCK5

1

T99

TP_SMCK#2

1

T106

TP_SMCK#5

1

C C

T105

Layout Note:

Route as short as

possible.

R166

R172

40.2Ohm

40.2Ohm

1%

1%

1 2

1 2

+1.8V

1 2

R734 80.6Ohm

B B

TVDAC_A_GM

TVDAC_B_GM

TVDAC_C_GM

TV_REFSET_GM

A A

DisableTV_OUT:

TVDAC A/B/C, TVIRTN A/B/C, TV_REFSET, VCCA_TV,DAC

A/B/C... (ALL TV POWER) connect to GND.

bom

1%

Ext VGA: 0 ohm

Int VGA: 150 ohm_1%

R651 0Ohm

1 2

R650 0Ohm

1 2

R649 0Ohm

1 2

Ext VGA: 0 ohm

Int VGA: 4.99K ohm_1%

R130 0Ohm

1 2

PROJECT:

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3 PEG_RXN11

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

DCLK014

DCLK114

DCLK313

DCLK413

DCLK0#14

DCLK1#14

DCLK3#13

DCLK4#13

SCKE014,15

SCKE114,15

SCKE213,15

SCKE313,15

SCS0#14,15

SCS1#14,15

SCS2#13,15

SCS3#13,15

M_OCDCOMP0

M_OCDCOMP1

ODT014,15

ODT114,15

ODT213,15

ODT313,15

M_RCOMPN

M_RCOMPP

VTT_REF

SMXSLEW

SMYSLEW

R735

80.6Ohm

1%

1 2

TVDAC_A_GM#

TVDAC_B_GM#

TVDAC_C_GM#

W3V

5

U48A

AA31

DMIRXN0

AB35

DMIRXN1

AC31

DMIRXN2

AD35

DMIRXN3

Y31

DMIRXP0

AA35

DMIRXP1

AB31

DMIRXP2

AC35

DMIRXP3

AA33

DMITXN0

AB37

DMITXN1

AC33

DMITXN2

AD37

DMITXN3

Y33

DMITXP0

AA37

DMITXP1

AB33

DMITXP2

AC37

DMITXP3

AM33

SM_CK0

AL1

SM_CK1

AE11

SM_CK2

AJ34

SM_CK3

AF6

SM_CK4

AC10

SM_CK5

AN33

SM_CK0#

AK1

SM_CK1#

AE10

SM_CK2#

AJ33

SM_CK3#

AF5

SM_CK4#

AD10

SM_CK5#

AP21

SM_CKE0

AM21

SM_CKE1

AH21

SM_CKE2

AK21

SM_CKE3

AN16

SM_CS0#

AM14

SM_CS1#

AH15

SM_CS2#

AG16

SM_CS3#

AF22

SM_OCDCOMP0

AF16

SM_OCDCOMP1

AP14

SM_ODT0

AL15

SM_ODT1

AM11

SM_ODT2

AN10

SM_ODT3

AK10

SMRCOMPN

AK11

SMRCOMPP

AF37

SMVREF0

AD1

SMVREF1

AE27

SMXSLEWIN

AE28

SMXSLEWOUT

AF9

SMYSLEWIN

AF10

SMYSLEWOUT

ALVISO_BGA1257

Ext VGA: 0 ohm

Int VGA: N/A

+VCC_GMCH_CORE

DAC_B_GM

DAC_G_GM

DAC_R_GM

DAC_VSYNC_GM16

DAC_HSYNC_GM16

REVISION

2.1

DMIDDR MUXING

PM

DREF_CLKN

CLK

DREF_SSCLKN

DREF_SSCLKP

NC

+VCC_GMCH_CORE

4

SDVO SMbus Int PD

SDVOCRTL_DATA Int PD

0: No SDVO device

1: SDVO device present

R119 1KOhm

G16

CFG0

H13

CFG1

G14

CFG2

F16

CFG3

F15

CFG4

G15

CFG5

E16

CFG6

D17

CFG7

J16

CFG8

D15

CFG9

E15

CFG10

D14

CFG11

E14

CFG12

H12

CFG13

C14

CFG14

H15

CFG15

J15

CFG16

H14

CFG17

G22

CFG18

G23

CFG19

D23

CFG20

G25

RSVD21

G24

RSVD22

J17

RSVD23

A31

RSVD24

A30

RSVD25

D26

RSVD26

D25

RSVD27

J23

BM_BUSY#

J21

EXT_TS0#

H22

EXT_TS1#

F5

THRMTRIP#

AD30

PWROK

AE29

RSTIN#

DREF_CLKP

12

R80

0Ohm

R120 0Ohm

Ext VGA: 0 ohm

Int VGA: N/A

R164 100Ohm

A24

A23

C37

D37

AP37

NC1

AN37

NC2

AP36

NC3

AP2

NC4

AP1

NC5

AN1

NC6

B1

NC7

A2

NC8

B37

NC9

A36

NC10

A37

NC11

12

12

R79

0Ohm

1 2

R76 39Ohm /*

1 2

R77 39Ohm /*

1 2

Ext VGA: N/A

Int VGA: 39 ohm

DATE:

SHEET OF

4

+2.5VS

R1.1#4

1 2

R941 2.2KOhm

/*

CLK_MCH_3GPLL#12

CLK_MCH_3GPLL12

12

+2.5VS

MCH_SEL1 12

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

PM_EXTTS#0

PM_EXTTS#1

TP_NC1

TP_NC2

TP_NC3

TP_NC4

TP_NC5

TP_NC6

TP_NC7

TP_NC8

TP_NC9

TP_NC10

TP_NC11

R78

0Ohm

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

12

1%

REFSET_GM

Ext VGA: N/A

Int VGA: 150 ohm_1%

R92 0Ohm

R88 0Ohm

R93 0Ohm

MCH_SEL0 12

T63

T75

CFG5 11

CFG6 11

CFG7 11

T80

CFG9 11

T69

T42

T61

T71

T62

T70

CFG16 11

T83

CFG18 11

CFG19 11

T57

T77

T68

T87

T268

T267

T76

T263

PM_BMBUSY# 22

GMCH_THRMTRIP# 6

VRM_PWRGD 12,45,48,49,54

BUF_PLT_RST# 6,21,22,23,28,30,31,32

DREFCLK# 12

DREFCLK 12

DREFSSCLK# 12

DREFSSCLK 12

T302

1

T298

1

T304

1

T305

1

T303

1

T300

1

T270

1

T266

1

T269

1

T265

1

T261

1

DisableCRT:

R/G/B, R#/G#/B#, REFSET, VCCA_CRTDAC connect to GMCH Core.

HSYNC/VSYNC/VCC_SYNC connect to GND.

1 2

/*

1 2

/*

1 2

/*

R101 0Ohm

1 2

Ext VGA: 0 ohm

Int VGA: 255 ohm_1%

VSYNC_GM

HSYNC_GM

Monday, January 17, 2005

TVDAC_A_GM21

TVDAC_B_GM21

TVDAC_C_GM21

DDC2BC_GM21

DDC2BD_GM21

DAC_B_GM21

DAC_G_GM21

DAC_R_GM21

LCD_BACKEN_GM20

CTL_DATA6

EDID_CLK_GM20

EDID_DAT_GM20

LCD_VDD_EN_GM20

R1.1_No5

DAC_B_GM#

DAC_G_GM#

DAC_R_GM#

1 2

R90 0Ohm

1 2

R91 0Ohm

Ext VGA: 0 ohm

Int VGA: N/A

DESCRIPTION:

CTL_CLK6

8 63

3

AB29

AC29

H24

H25

A15

C16

A17

J18

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

J20

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

U48F

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CRTL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

ALVISO_BGA1257

+1.5VS

+2.5VS

SDVO_SMDATA

SDVO_SMCLK

T85

1

TVDAC_A_GM

TVDAC_B_GM

TVDAC_C_GM

TV_REFSET_GM

TVDAC_A_GM#

TVDAC_B_GM#

TVDAC_C_GM#

DAC_B_GM

DAC_B_GM#

DAC_G_GM

DAC_G_GM#

DAC_R_GM

DAC_R_GM#

VSYNC_GM

HSYNC_GM

REFSET_GM

T262

1

EDID_CLK_GM

EDID_DAT_GM

1

T47

1

T58

1

T78

1

T65

LVDS_CLKAM_GM20

LVDS_CLKAP_GM20

LVDS_CLKBM_GM20

LVDS_CLKBP_GM20

LVDS_YA0M_GM20

LVDS_YA1M_GM20

LVDS_YA2M_GM20

LVDS_YA0P_GM20

LVDS_YA1P_GM20

LVDS_YA2P_GM20

LVDS_YB0M_GM20

LVDS_YB1M_GM20

LVDS_YB2M_GM20

LVDS_YB0P_GM20

LVDS_YB1P_GM20

LVDS_YB2P_GM20

1 2

R99 0Ohm /*

Ext VGA: N/A

Int VGA: 0 ohm

L_IBG

L_LVBG

L_LVREFH

L_LVREFL

MCH: DDR2/DMI/PEG

3

MISCTVVGALVDS

Ext VGA: 0 ohm

Int VGA: N/A

R647 0Ohm

1 2

R648 0Ohm

1 2

R670 0Ohm

1 2

R671 0Ohm

1 2

1 2

R81 1.5KOhm

1%

1 2

10KOhm

3 4

10KOhm

5 6

10KOhm

7 8

10KOhm

D36

EXP_COMPI

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

L_IBG

D34

E30

F34

G30

H34

J30

K34

L30

M34

N30

P34

R30

T34

U30

V34

W30

Y34

D30

E34

F30

G34

H30

J34

K30

L34

M30

N34

P30

R34

T30

U34

V30

W34

E32

F36

G32

H36

J32

K36

L32

M36

N32

P36

R32

T36

U32

V36

W32

Y36

D32

E36

F32

G36

H32

J36

K32

L36

M32

N36

P32

R36

T32

U36

V32

W36

DREFSSCLK#

DREFSSCLK

PM_EXTTS#0

PM_EXTTS#1

EDID_DAT_GM

EDID_CLK_GM

EXP_ICOMPO

PCI-EXPRESS GRAPHICS

RN4A

RN4B

RN4C

RN4D

RELEASE DATE :

2

R680 24.9Ohm 1%

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

DREFCLK#

DREFCLK

2

1 2

+1.5VS_PCIE

Ext VGA: stuff

Int VGA: N/A

PEG_TXN0

PEG_TXP0

C96 0.1UF

PEG_TXN1

PEG_TXP1

C610 0.1UF

PEG_TXN2

PEG_TXP2

C104 0.1UF

PEG_TXN3

PEG_TXP3

C615 0.1UF

PEG_TXN4

PEG_TXP4

C110 0.1UF

PEG_TXN5

PEG_TXP5

C619 0.1UF

PEG_TXN6

PEG_TXP6

C123 0.1UF

PEG_TXN7

PEG_TXP7

C633 0.1UF

PEG_TXN8

PEG_TXP8

C137 0.1UF

PEG_TXN9

PEG_TXP9

C652 0.1UF

PEG_TXN10

PEG_TXP10

C147 0.1UF

PEG_TXN11

PEG_TXP11

C656 0.1UF

PEG_TXN12

PEG_TXP12

C151 0.1UF

PEG_TXN13

PEG_TXP13

C665 0.1UF

PEG_TXN14

PEG_TXP14

C157 0.1UF

PEG_TXN15

PEG_TXP15

C668 0.1UF

<OrgName>

PEG_RXN[0..15] 16

PEG_RXP[0..15] 16

1 2

C89 0.1UF

1 2

C596 0.1UF

1 2

C102 0.1UF

1 2

C613 0.1UF

1 2

C106 0.1UF

1 2

C616 0.1UF

1 2

C118 0.1UF

1 2

C620 0.1UF

1 2

C127 0.1UF

1 2

C637 0.1UF

1 2

C141 0.1UF

1 2

C653 0.1UF

1 2

C149 0.1UF

1 2

C657 0.1UF

1 2

C153 0.1UF

1 2

C666 0.1UF

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

PEG_G_RXN0

PEG_G_RXP0

PEG_G_RXN1

PEG_G_RXP1

PEG_G_RXN2

PEG_G_RXP2

PEG_G_RXN3

PEG_G_RXP3

PEG_G_RXN4

PEG_G_RXP4

PEG_G_RXN5

PEG_G_RXP5

PEG_G_RXN6

PEG_G_RXP6

PEG_G_RXN7

PEG_G_RXP7

PEG_G_RXN8

PEG_G_RXP8

PEG_G_RXN9

PEG_G_RXP9

PEG_G_RXN10

PEG_G_RXP10

PEG_G_RXN11

PEG_G_RXP11

PEG_G_RXN12

PEG_G_RXP12

PEG_G_RXN13

PEG_G_RXP13

PEG_G_RXN14

PEG_G_RXP14

PEG_G_RXN15

PEG_G_RXP15

DESIGN ENGINEER :SCHEMATIC FILE NAME :

1

1

M.Y.

PEG_G_RXN[0..15] 16

PEG_G_RXP[0..15] 16

Page 9

5

D D

4

3

2

1

M_A_DQ[0..63]14

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

C C

B B

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AP7

AP11

AP10

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AM3

AK2

AK3

AG2

AG1

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

AL9

AL6

AL7

AL4

AL3

U48B

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

ALVISO_BGA1257

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

DDR SYSTEM MEMORY A

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

AK15

AK16

AL21

M_A_DM0

AJ37

M_A_DM1

AP35

M_A_DM2

AL29

M_A_DM3

AP24

M_A_DM4

AP9

M_A_DM5

AP4

M_A_DM6

AJ2

M_A_DM7

AD3

M_A_DQS0

AK36

M_A_DQS1

AP33

M_A_DQS2

AN29

M_A_DQS3

AP23

M_A_DQS4

AM8

M_A_DQS5

AM4

M_A_DQS6

AJ1

M_A_DQS7

AE5

M_A_DQS#0

AK35

M_A_DQS#1

AP34

M_A_DQS#2

AN30

M_A_DQS#3

AN23

M_A_DQS#4

AN8

M_A_DQS#5

AM5

M_A_DQS#6

AH1

M_A_DQS#7

AE4

M_A_A0

AL17

M_A_A1

AP17

M_A_A2

AP18

M_A_A3

AM17

M_A_A4

AN18

M_A_A5

AM18

M_A_A6

AL19

M_A_A7

AP20

M_A_A8

AM19

M_A_A9

AL20

M_A_A10

AM16

M_A_A11

AN20

M_A_A12

AM20

M_A_A13

AM15

AN15

AP16

TP_MA_RCVENIN#

AF29

TP_MA_RCVENOUT#

AF28

AP15

M_A_BS#0 14,15

M_A_BS#1 14,15

M_A_BS#2 14,15

M_A_WE# 14,15

M_A_DM[0..7] 14

M_A_DQS[0..7] 14

M_A_DQS#[0..7] 14

M_A_A[0..13] 14,15

M_A_CAS# 14,15

M_A_RAS# 14,15

R169 0Ohm

1 2

M_B_DQ[0..63]13

AE31

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AH11

AH10

AG9

AG8

AH8

AJ9

AK9

AJ7

AK6

AJ4

AH5

AK8

AJ8

AJ5

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

U48C

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQ40

SBDQ41

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

ALVISO_BGA1257

SB_BS0#

SB_BS1#

SB_BS2#

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

DDR SYSTEM MEMORY B

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

AJ15

AG17

AG21

M_B_DM0

AF32

M_B_DM1

AK34

M_B_DM2

AK27

M_B_DM3

AK24

M_B_DM4

AJ10

M_B_DM5

AK5

M_B_DM6

AE7

M_B_DM7

AB7

M_B_DQS0

AF34

M_B_DQS1

AK32

M_B_DQS2

AJ28

M_B_DQS3

AK23

M_B_DQS4

AM10

M_B_DQS5

AH6

M_B_DQS6

AF8

M_B_DQS7

AB4

M_B_DQS#0

AF35

M_B_DQS#1

AK33

M_B_DQS#2

AK28

M_B_DQS#3

AJ23

M_B_DQS#4

AL10

M_B_DQS#5

AH7

M_B_DQS#6

AF7

M_B_DQS#7

AB5

M_B_A0

AH17

M_B_A1

AK17

M_B_A2

AH18

M_B_A3

AJ18

M_B_A4

AK18

M_B_A5

AJ19

M_B_A6

AK19

M_B_A7

AH19

M_B_A8

AJ20

M_B_A9

AH20

M_B_A10

AJ16

M_B_A11

AG18

M_B_A12

AG20

M_B_A13

AG15

AH14

AK14

TP_MB_RCVENIN#

AF15

TP_MB_RCVENOUT#

AF14

AH16

M_B_BS#0 13,15

M_B_BS#1 13,15

M_B_BS#2 13,15

M_B_CAS# 13,15

M_B_RAS# 13,15

R165 0Ohm

1 2

M_B_WE# 13,15

M_B_DM[0..7] 13

M_B_DQS[0..7] 13

M_B_DQS#[0..7] 13

M_B_A[0..13] 13,15

/*

12

C174

10UF/10V

/*

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

/*

12

C189

10UF/10V

/*

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

A A

bom

PROJECT:

5

W3V

REVISION

2.1

Monday, January 17, 2005

DATE:

SHEET OF

4

9 63

DESCRIPTION:

MCH: DDR2

3

RELEASE DATE :

2

<OrgName>

DESIGN ENGINEER :SCHEMATIC FILE NAME :

M.Y.

1

Page 10

5

Ext VGA: stuff

Int VGA: N/A

+VCC_GMCH_CORE

+2.5VS

Ext VGA: N/A

Int VGA:

D D

stuff

12

C559

0.1UF

C C

12

C581

0.1UF

+1.5VS

B B

L35 120Ohm/100Mhz

+1.5VS

L101 120Ohm/100Mhz

A A

bom

1 2

L32 0Ohm

1 2

L29 0Ohm

/*

12

C138

0.1UF

/*

+VCCP

1.05V

VCCP_GMCH_CAP1

VCCP_GMCH_CAP2

VCCP_GMCH_CAP3

CAP4

12

C618

0.1UF

12

C669

0.1UF

+2.5VS

21

21

VTT48

VTT49

VTT50

VTT51

VSSA_3GBG

G37

C82

0.1UF

1 2

+1.5VS_3GPLL

12

C163

0.1UF

+1.5VS_PCIE

12

+

CE26

150U/4.0V

/*

+1.5VS

L102 120Ohm/100Mhz

PROJECT:

5

VTT47

VCCA_3GBG

F37

12

12

+

CE24

150U/4.0V

/*

VTT46

Y27

12

12

21

C100

0.01UF

VTT41

VTT42

VTT43

VTT44

VTT45

VCC3G6

VCCA_3GPLL0

VCCA_3GPLL1

VCCA_3GPLL2

J37

Y29

Y28

C158

10UF/10V

12

C684

0.1UF

+1.5VS_DDRDLL

W3V

12

C101

0.1UF

12

C650

0.1UF

A6

VTT39

VTT40

VCC3G4

VCC3G5

R37

N37

L37

C687

10UF/10V

VTT38

VCC3G3

U37

12

VTT37

VCC3G2

W37

C708

0.1UF

12

C639

10UF/10V

VTT34

VTT35

VTT36

VCC3G0

VCC3G1

AE37

REVISION

VTT32

VTT33

VCCA_SM2

VCCA_SM3

AF19

AF18

12

+

CE9

150U/4.0V

AP19

2.1

VTT30

VTT31

VCCA_SM0

VCCA_SM1

AF20

+2.5VS

Ext VGA: GND

Int VGA: +2.5VS

VTT27

VTT28

VTT29

VCCTX_LVDS2

A28

A27

4

+1.5VS_MPLL

W10

AG12

VTT13

VCCSM54

12

12

12

P11

N11

M11

L11

K11

VTT9

VTT10

VTT11

VTT12

VCCSM50

VCCSM51

VCCSM52

VCCSM53

AM12

AL12

AK12

AJ12

AH12

12

C699

0.1UF

L100 120Ohm/100Mhz

C672

0.1UF

VCCA_CRTDAC

VCC_SYNC

V11

U11

T11

R11

VTT4

VTT5

VTT6

VTT7

VTT8

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

AF13

AE13

AP12

AN12

12

C704

0.1UF

VTT26

VCCTX_LVDS1

VTT25

VCCTX_LVDS0

B28

12

VTT24

C107

0.1UF

J10Y9W9U9R9P9N9M9L9J9N8M8N7M7N6M6N5M5N4M4N3M3N2M2B2V1N1M1G1

VTT23

VCCSM64

AM1

AE1

+2.5VS

R10

P10

N10

M10

K10

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

AC11

AB11

AB10

AB9

AP8

V1.8_DDR_CAP6

V1.8_DDR_CAP4

V1.8_DDR_CAP3

12

C143

10UF/10V

/*

12

+

CE27

150U/4.0V

R126 0Ohm /*

R140 0Ohm

V10

U10

T10

VTT14

VTT15

VTT16

VCCSM55

VCCSM56

VCCSM57

AF12

AE12

AD11

Note: All VCCSM pins

shorted internally.

12

C688

0.1UF

Ext VGA: N/A

Int VGA: stuff

R1.1#34

+1.5VS +2.5VS

12

12

DATE:

SHEET OF

4

C555

C556

10UF/10V

0.1UF

Place near pin

A25, B25, B26

Monday, January 17, 2005

10 63

W11

AG13

K12

VTT2

VTT3

VCCSM43

VCCSM44

AH13

21

J13

AJ13

K13

VTT1

VCCSM42

AK13

12

VTT0

VCCSM40

VCCSM41

AL13

C285

10UF/10V

F19

E19

G19

H20

VCC_SYNC

VSSA_CRTDAC

VCCA_CRTDAC0

VCCA_CRTDAC1

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

AE17

AE16

AE15

AE14

AP13

AN13

AM13

Note: All VCCSM pins

shorted internally.

12

C707

0.1UF

12

C776

0.1UF

12

C557

0.1UF

Place near pin A35

DESCRIPTION:

AA1

AA2

VCCA_HPLL

VCCA_MPLL

VCCSM31

VCCSM32

AE19

AE18

+1.8V

3

12

+

150U/4.0V

Ext VGA: N/A

Int VGA: stuff

12

+

150U/4.0V

/*

R1.1#34

AC2

AC1

B23

C35

VCCA_DPLLA

VCCA_DPLLB

VCCH_MPLL1

VCCH_MPLL0

VCCSM27

VCCSM28

VCCSM29

VCCSM30

AE24

AE23

AE22

AE21

AE20

12

C694

0.1UF

12

+

CE8

150U/4.0V

12

C558

0.01UF

3

+1.5VS_HPLL

L99 120Ohm/100Mhz

12

K17

VCC48

T18

K18

VCC46

VCC47

C675

0.1UF

+1.5VS_DPLLB

L25 120Ohm/100Mhz

12

C85

0.1UF

K20

V19

U19

K19

W18

V18

VCC41

VCC42

VCC43

VCC44

VCC45

VCC40

CE25

CE5

POWER

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

AN25

AM25

AL25

AK25

AJ25

AH25

AG25

AF25

AE25

V1.8_DDR_CAP5

V1.8_DDR_CAP2

V1.8_DDR_CAP1

12

C702

0.1UF

MCH: POWER

2

21

21

K27

J27

H27

K26

H26

K25

J25

K24

K23

K22

K21

W20

U20

T20

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

AD28

AD27

AC27

AP26

AN26

AM26

AL26

AK26

AJ26

AH26

AG26

AF26

AE26

AP25

+2.5VS

12

12

C71

10UF/10V

C74

0.1UF

+1.5VS_DPLLA

R1.1#34

12

+

CE3

150U/4.0V

/*

Ext VGA: N/A

Int VGA: stuff

U27

T27

R27

P27

N27

M27

L27

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCCHV1

VCCHV2

VCCSM0

VCCSM1

VCCSM2

VCCSM3

B22

B21

A21

AM37

AH37

AP29

+1.5VS

VCCA_TVBG

12

12

R150

0Ohm

VCCD_TVDAC VCCA_TVDACB

12

12

R104

0Ohm

VCCDQ_TVDAC

12

12

R137

0Ohm

RELEASE DATE :

L16 120Ohm/100Mhz

12

C83

0.1UF

12

C146

10UF/10V

L28

K28

J28

H28

G28

V27

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCCD_LVDS1

VCCD_LVDS2

VCCA_LVDS

VCCHV0

B26

B25

A25

A35

12

12

C678

0.1UF

12

C156

C155

0.1UF

0.01UF

/*

/*

C91

0.1UF

/*

12

C133

C134

0.01UF

0.1UF

/*

/*

2

21

12

C119

10UF/10V

R28

P28

N28

M28

VCC10

VCC11

VCC12

VCC13

VCCD_TVDAC

VCCDQ_TVDAC

VCCD_LVDS0

D19

H17

VCCDQ_TVDAC

VCCD_TVDAC

C681

0.01UF

L37 120Ohm/100MHz

1 2

R98 0Ohm /*

L34 120Ohm/100MHz

12

C140

10UF/10V

M29

K29

J29

V28

U28

T28

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCCA_TVDACC0

VCCA_TVDACC1

VCCA_TVBG

VSSA_TVBG

C18

F18

E18

H18

G18

VCCA_TVDACC

VCCA_TVBG

21

/*

21

/*

<OrgName>

+1.5VS

Ext VGA: N/A

Int VGA: stuff

+VCC_GMCH_CORE

1.05V

12

12

C154

C113

0.1UF

0.1UF

T29

R29

N29

U48G

ALVISO_BGA1257

VCC0

VCC1

VCC2

VCC3

1.8V: 1A for DDR2 400 1 channel

2A for DDR2 400 2 channel

1.3A for DDR2 533 1 channel

2.7A for DDR2 533 2 channel

1.05VS:850mA for CPU

3100mA for external gfx

1.5VS: 1264mA

2.5VS: 293mA

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

3VS: 120mA

F17

E17

D18

VCCA_TVDACA

VCCA_TVDACB

Ext VGA: stuff R, no-stuff L,C

Int VGA: stuff L,C, no-stuff R

12

R64

0Ohm

+1.5VS

12

R94

0Ohm

+1.5VS

12

R138

0Ohm

1

+VCC_GMCH_CORE

1

2

3

R631

1KOhm

/*

1 2

+2.5VS +3VS

12

C144

0.1UF

VCCA_TVDACA

12

C68

0.1UF

/*

12

C87

0.1UF

/*

VCCA_TVDACC

12

C142

0.1UF

/*

L23 120Ohm/100MHz

12

C67

0.01UF

/*

L26 120Ohm/100MHz

12

C94

0.01UF

/*

L36 120Ohm/100MHz

12

C148

0.01UF

/*

DESIGN ENGINEER :SCHEMATIC FILE NAME :

M.Y.

1

D52

BAT54C

/*

+1.5VS

1

2

D49

BAT54C

/*

3

R632

1KOhm

/*

1 2

+3VS+3VS

21

/*

21

/*

21

/*

Page 11

5

AL24

AN24

A26

E26

G26

J26

B27

E27

G27

W27

AA27

AB27

AF27

AG27

AJ27

AL27

AN27

E28

W28

AA28

AB28

AC28

A29

D29

E29

F29

G29

H29

L29

P29

VSS267

VSS266

VSS265

VSS264

VSS263

VSS262

VSS261

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

AD15

VSS244

VCCSM_NCTF22

VSS108

VSS243

VSS242

VSS241

VSS240

VSS239

VSS238

AF4

AN4E5W5

AC16

AD16

AC17

AD17

AC18

AD18

AC19

VCCSM_NCTF21

VCCSM_NCTF20

VCCSM_NCTF19

VCCSM_NCTF18

VCCSM_NCTF17

VCCSM_NCTF16

D D

VSSALVDS

VSS271

VSS270

VSS269

VSS268

VSS260

VSS259

VSS258

VSS257

VSS256

VSS255

VSS254

VSS253