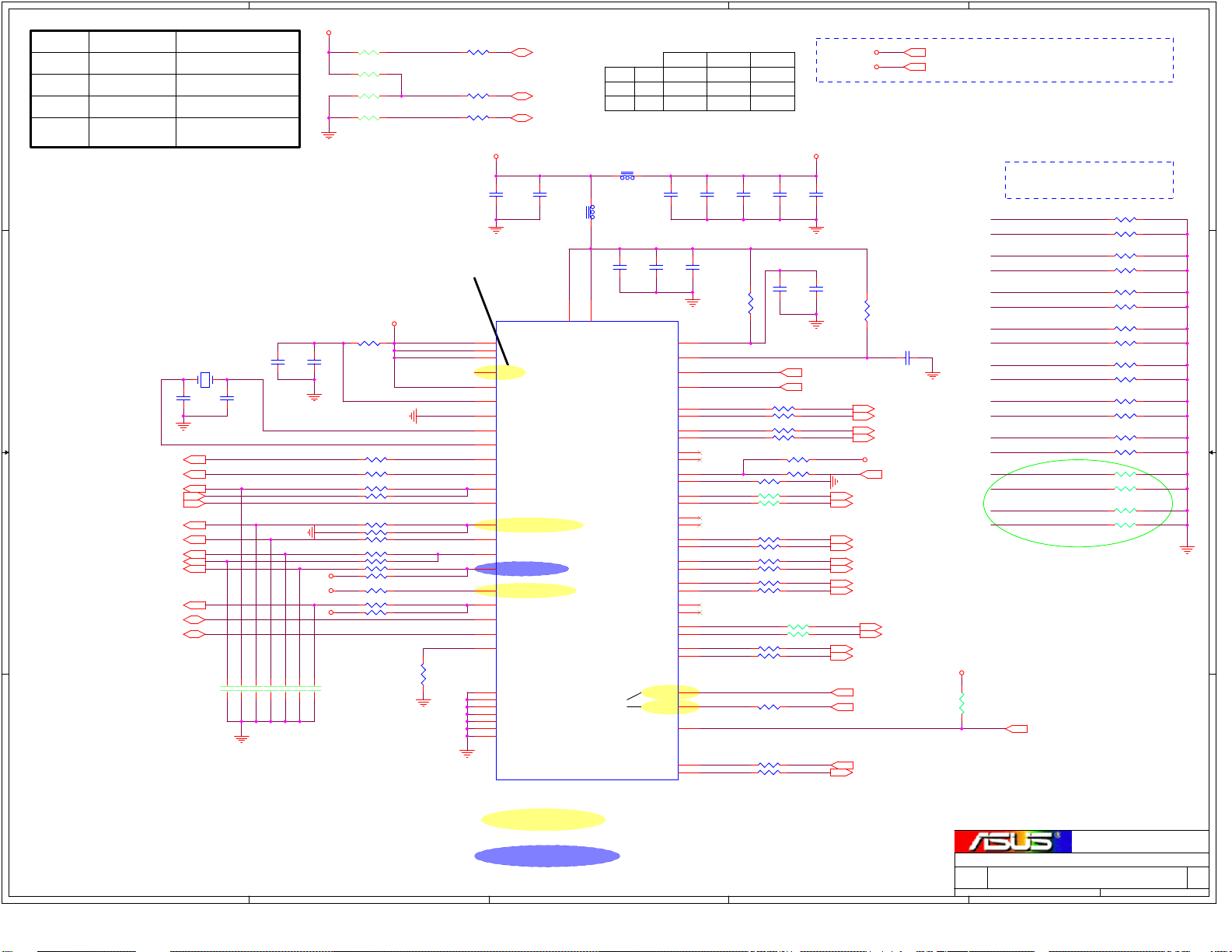

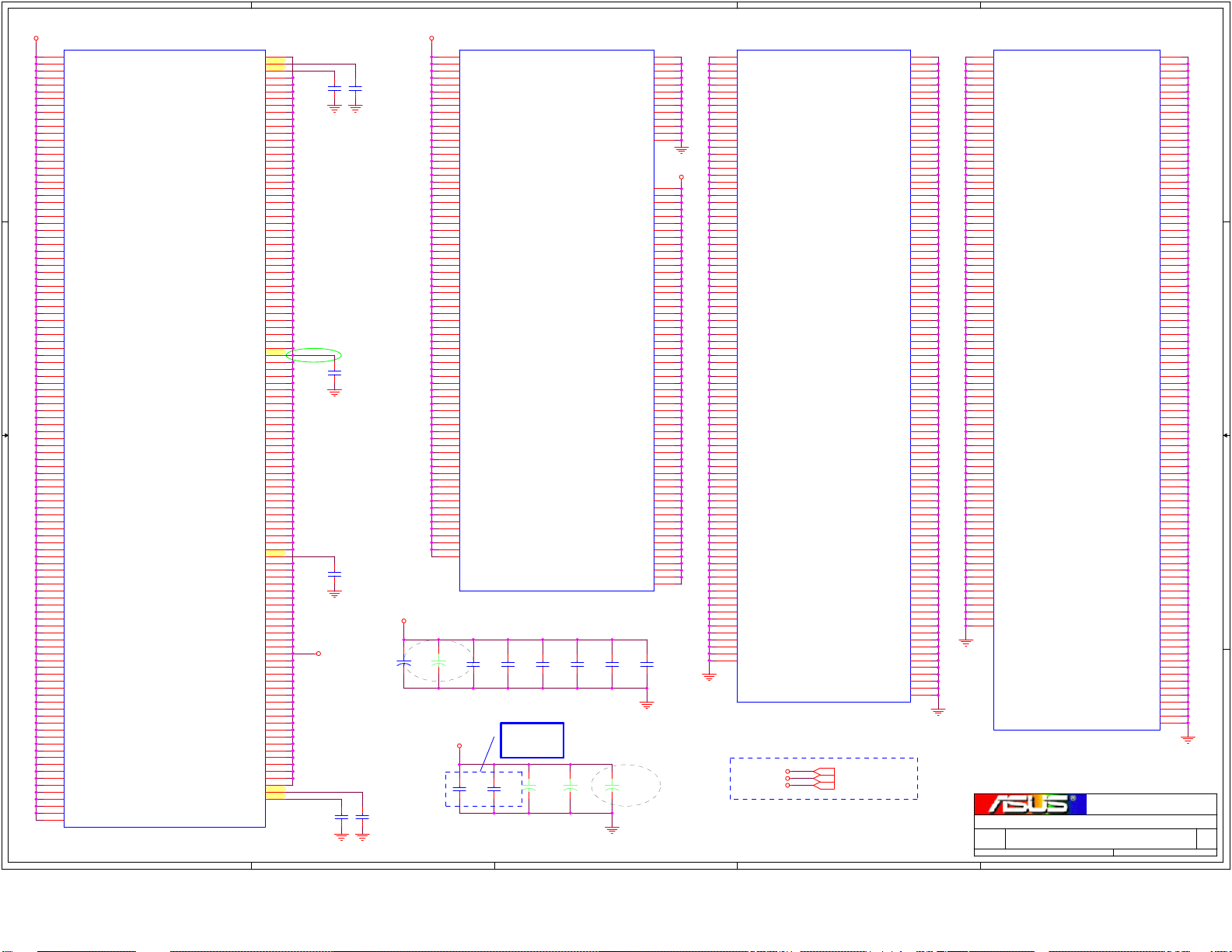

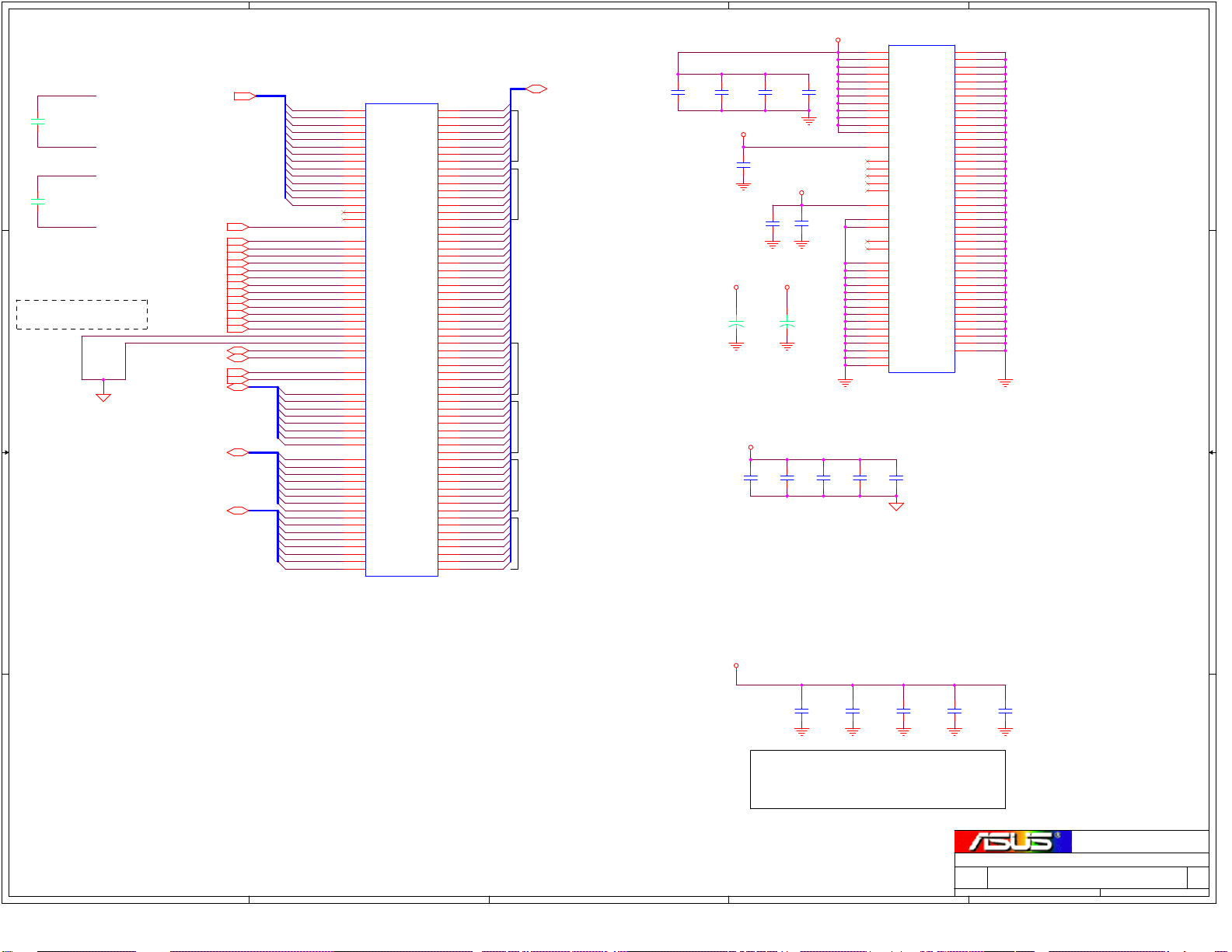

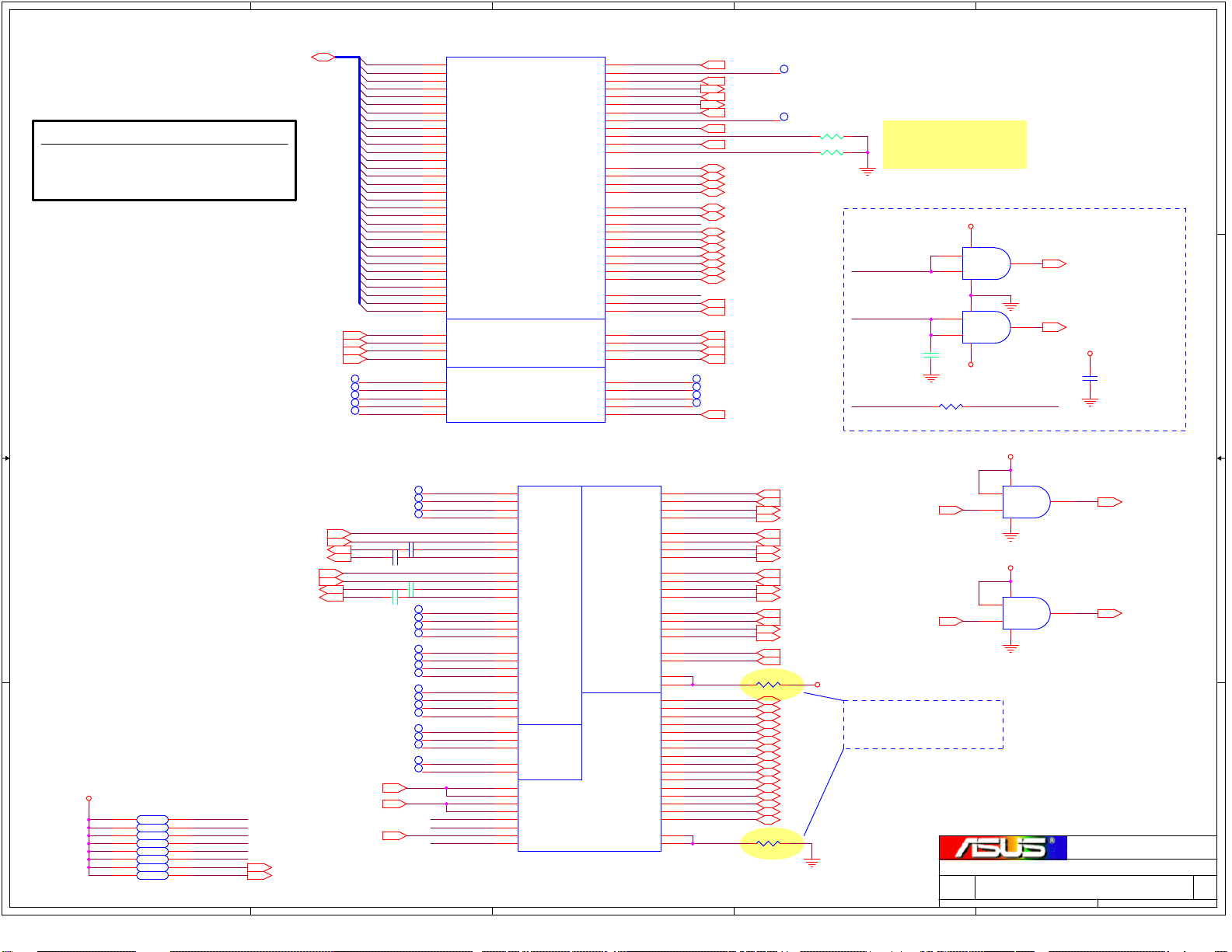

Asus t12fv Schematics

DC/BATT

www.bufanxiu.com

IN

5

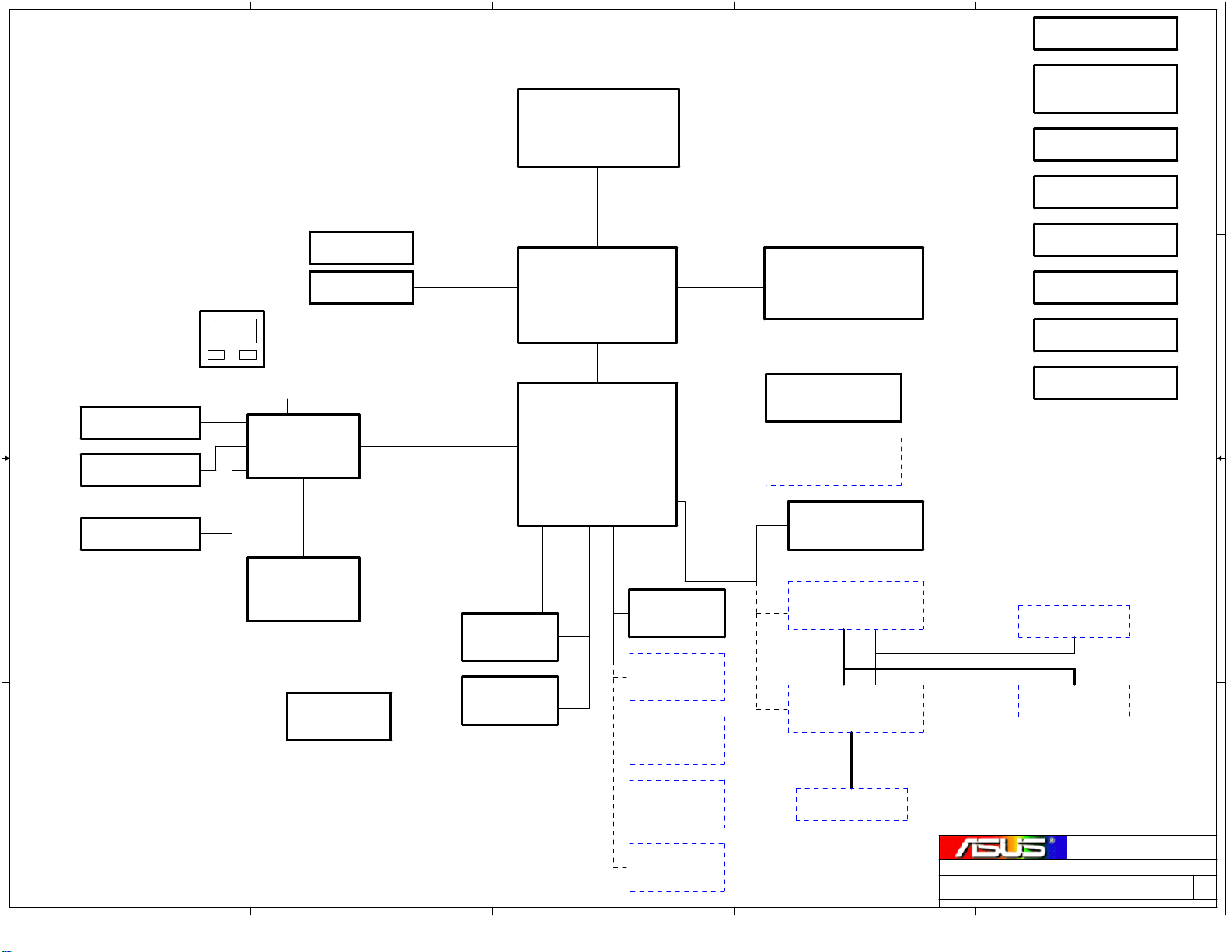

T12F Block Diagram

D D

LVDS &

PAGE 12

CRT & TV OUT

PAGE 13

C C

KEYP

AD

MA

TRIX

PAGE 29

INST

ANT KEY

PAGE 38

LED

Control

PAGE

B B

30,38

T/P

PAGE 30

PAGE 24

EC I

T8511E

PAGE 29,30

ISA

ROM

Azalia Codec

AD1986A

PAGE 21,22,23

4

INV

LPC

33M

Hz

Azalia

PAGE 28

PAGE 28

YONAH-

PAGE 2,3

B0:02G010009121

PAGE 6,7,8,9,10,11

PAGE

17,18,19,20

(PATA,SATA)

B0:02G010008811

SATA2

HD

D

OD

D

3

CPU

2M

FSB

66

7MHz

MCH-M

Calistoga

945GM

DMI interface

ICH7-M

IDE

USB

PAGE 36

PAGE 27

PAGE 12

US

CON

Bl

uetooth

Cam

B 2.0

X4

era

PCIE *1

PCIE *1

DDR2-667

PCI

33MH

z

2

Dual Channel DDR2

SO-DIMM X 2

PAGE 14,15,16

MINI

CARD

WLA

N

PAGE 26

NEW

CARD

PAGE 25

10/100 LAN

RTL8100CL

PAGE 34,35

CardBus

R5C832

PAGE 31,32

CardBus

R5C841

PAGE

43,44

FAN

+ SENSOR

MAX6657MSA

PAGE 4

CLOCK

ICS9

PAGE 5

DISCHARGE

CIRCUI

PAGE 37

Powe

r On Sequence

PAGE 40

DC/BATT

PAGE 41

CPU V

PAGE 50

SYS

TEM PWR

PAGE 51

BAT &

CHARGER

PAGE 57

13

94

PAGE 32

CARD READER

PAGE 33

1

GEN

54310

T

CORE

R

IN

A A

5

4

3

FingerPri

PAGE 39

TP

PAGE 42

nt

M

PAGE 32

PC

MCIA

2

<Variant Name>

ASUSTeK COMPUTER INC

Size

Project Name

Custom

Wednesday, April 19, 2006

Date:

T12F

Title :

Engineer:

Sheet

1

BLOCK DIAGRAM

Leon and George

1

Rev

1.1

61

of

H_A#[16..3]

www.bufanxiu.com

6

H_REQ#[4..0]

6

H_A#[31..17]

6

5

4

3

2

1

T202

H_A#3

D D

H_ADSTB#0

6

C C

H_ADSTB#1

6

H_A20M#

17

H_FERR#

17

H_IGNNE#

17

H_STPCLK#

17

H_INTR

17

H_NMI

17

H_SMI#

17

B B

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_ADSTB#0

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADSTB#1

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

U201A

J4

A[3]#

L4

A[4]#

M3

A[5]#

K5

A[6]#

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

L2

K3

H2

K2

J3

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

B25

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[1]

RSVD[2]

RSVD[3]

RSVD[4]

RSVD[5]

RSVD[6]

RSVD[7]

RSVD[8]

RSVD[9]

RSVD[10]

RSVD[11]

ADDR GROUP 0

ADDR GROUP 1

THERMHCLKRESERVED

THERMTRIP#

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

XDP/ITP SIGNALS

DBR#

PROCHOT#

THERMDA

THERMDC

BCLK[0]

BCLK[1]

RSVD[12]

RSVD[A2]

RSVD[13]

RSVD[14]

RSVD[15]

RSVD[16]

RSVD[17]

RSVD[18]

RSVD[19]

RSVD[20]

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

B1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

TDI

AB3

AB5

AB6

C20

D21

A24

A25

C7

A22

A21

T22

A2

D2

F6

D3

C1

AF1

D22

C23

C24

12G04600479A

1

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BR0#

H_IERR#

H_INIT#

H_LOCK#

H_CPURST#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

H_HIT#

H_HITM#

PRDY#

H_PREQ#

H_TCK

H_TDI

H_TDO

H_T

MS

H_TRST#

CPU_DBR#

H_PROCHOT_S#

CPU_THRM_DA

CPU_THRM_DC

PM_THRMTRIP#

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_ADS#

6

H_BNR#

6

H_BPRI#

6

H_DEFER#

6

H_DRDY#

6

H_DBSY#

6

H_BR0#

6

H_INIT#

17

H_LOCK# 6

H_CPURST#

H_RS#0

6

H_RS#1

6

H_RS#2

6

H_TRDY#

6

H_HIT# 6

H_HITM#

6

+VCCP_AGTL+

T203

1

R203

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

CPU_THRM_DA

CPU_THRM_DC

PM_THRMTRIP#

CLK_CPU_BCLK

CLK_CPU_BCLK#

@

@

R204

1 2

R205

1 2

R206

R207

1 2

R208

1 2

68 ¡Ó 5% pull-up to Vcc1_0

If PROCHOT# is not u

56 pull-up resistor to VCCP.

If PROCHOT# is routed between CPU, IMVP and MCH,

pull-up resistor has to be 75 Ohm ¡Ó 5

R201

56Ohm

1

6

R202

54.9Ohm

T201

GND

1

TP

C28T

4

4

4,7,17

5

5

sed, then it must be terminated with a

T204

12

@

+VCCP_AGTL+

+VCCP_AGTL+

C201

0.1UF/10V

@

GND

+VCCP_AGTL+

12

R213

2KOhm

1%

R209

1KOhm

1%

1 2

<500 mil (55 Ohm)

T/B trace 5

Space 25

1 2

GND

6

6

6

6

6

6

GND

CPU_BSEL0

5

CPU_BSEL1

5

CPU_BSEL2

5

BCLK

133

166L667

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_DSTBN#1

H_DSTBP#1

H_DINV#1

R214

@

1KOhm

R216

51Ohm

1 2

1 2

FSB

533

BSEL2

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DINV#1

GTL_REF

AD26

TEST1

TEST2

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

BSEL1HBSEL0

L

HL

H

U201B

E22

D[0]#

F24

D[1]#

E26

D[2]#

H22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H26

D[12]#

F26

D[13]#

K22

D[14]#

H25

D[15]#

H23

DSTBN[0]#

G22

DSTBP[0]#

J26

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L25

D[20]#

L22

D[21]#

L23

D[22]#

M23

D[23]#

P25

D[24]#

P22

D[25]#

P23

D[26]#

T24

D[27]#

R24

D[28]#

L26

D[29]#

T25

D[30]#

N24

D[31]#

M24

DSTBN[1]#

N25

DSTBP[1]#

M26

DINV[1]#

GTLREF

C26

TEST1

D25

TEST2

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

12G011204792

12G04600479A

DATA GRP 0

DATA GRP 1

MISC

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

DATA GRP 2DATA GRP 3

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DINV#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#3

H_DSTBP#3

H_DINV#3

H_COMP0

H_COMP1

H_COMP2

H_COMP3

H_DPRSTP#

H_DPSLP#

H_DPWR#

H_PWRGD

H_CPUSLP#

PM_PSI#

H_D#[0..63]

R210

R211

R212

R215

1

6

H_DSTBN#2

H_DSTBP#2

H_DINV#2

6

Layout Note:

Comp0,2 connect with Z0=27.4 ohm,

make trace length shorter than 0.5".

Comp1,3 connect with Z0=54.9 ohm,

make trace length shorter than 0.5".

Comp[3:0] at least 25 mils a

any other toggling signa

27.4 ohm connects with an ~18mil

wide trace to comp0.

54.9 ohm connect with 5mil-wide

to comp1

H_DSTBN#3

H_DSTBP#3

H_DINV#3

6

27.4Ohm

1 2

54.9Ohm

1 2

27.4Ohm

1 2

54.9Ohm

1 2

H_DPRSTP#

H_DPSLP#

17

H_DPWR#

6

H_PWRGD

T205

H_CPUSLP#

PM_PSI#

6

6

way from

l.

6

6

1%

GND

1%

1%

1%

17,50

17

6,17

50

+VCCP_AGTL+

JP201

1 2

SHORT_PIN

2.5A

+VCCP

+VCCP_AGTL+

A A

5

+VCCP

@

+VCCP

6,9,20,52

+VCCP_AGTL+

3,5,6,9

H_PROCHOT_S#

29

4

H_PROCHOT_S#

+VCCP_AGTL+

R217

56Ohm

H_PWRGD

3

+VCCP_AGTL+

R218

56Ohm

@

<Variant Name>

Title :

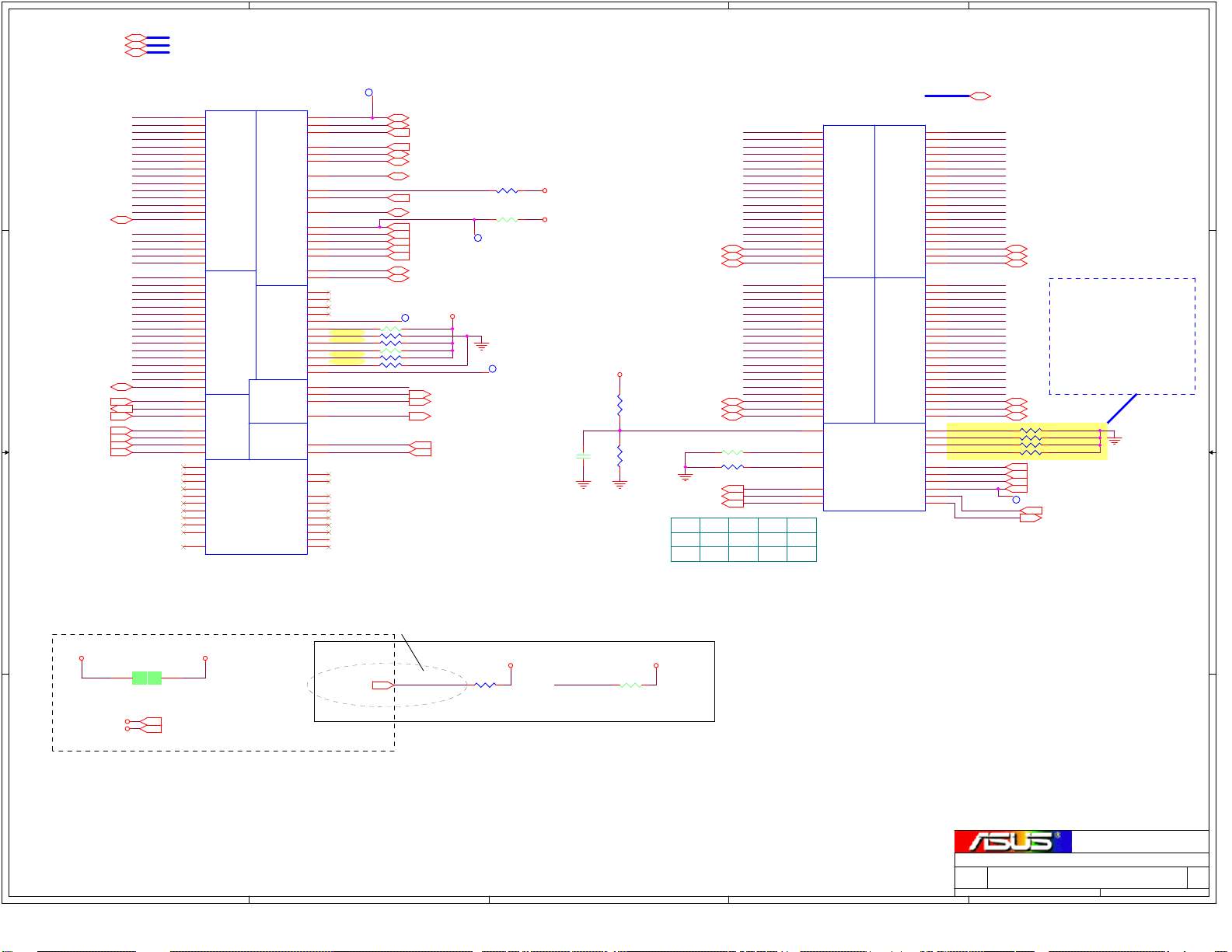

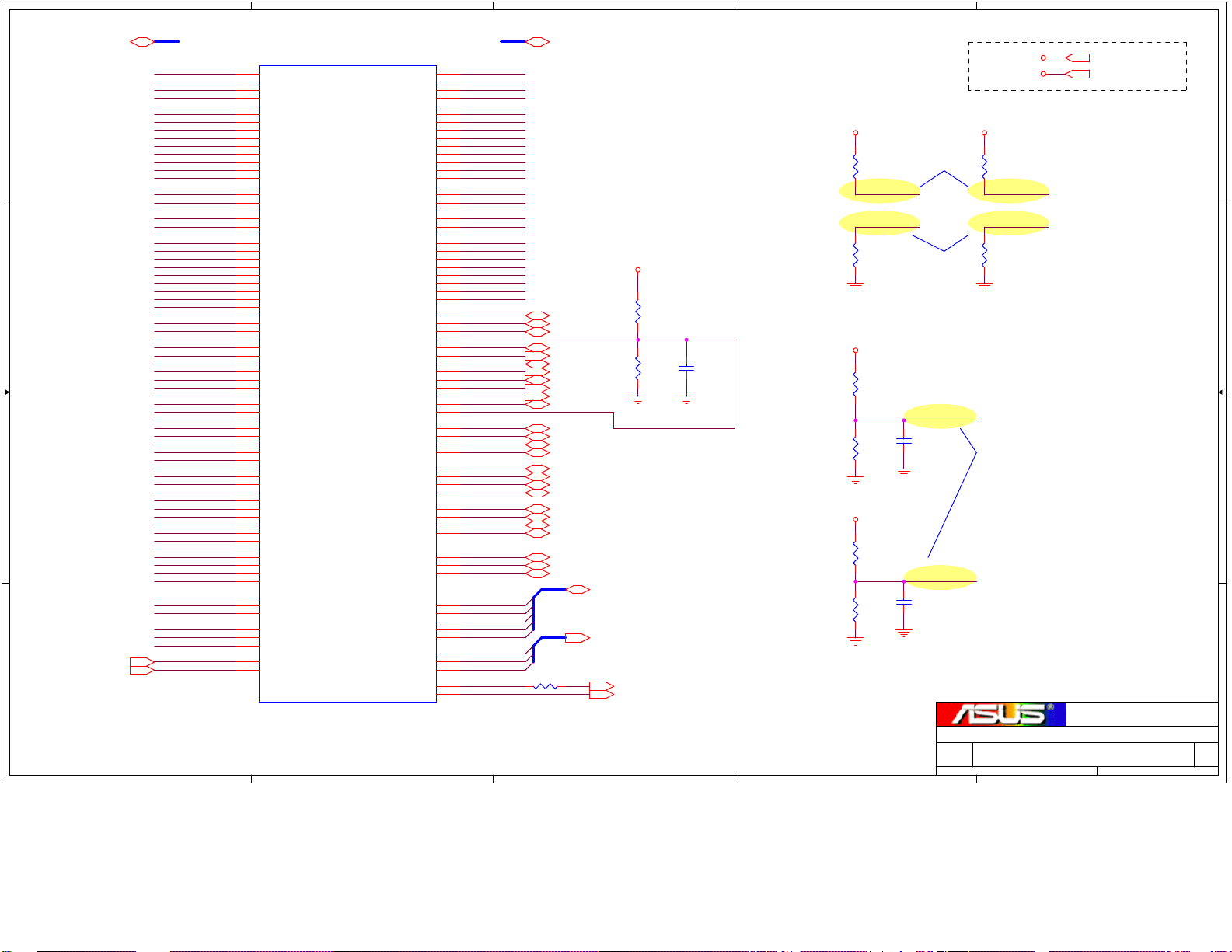

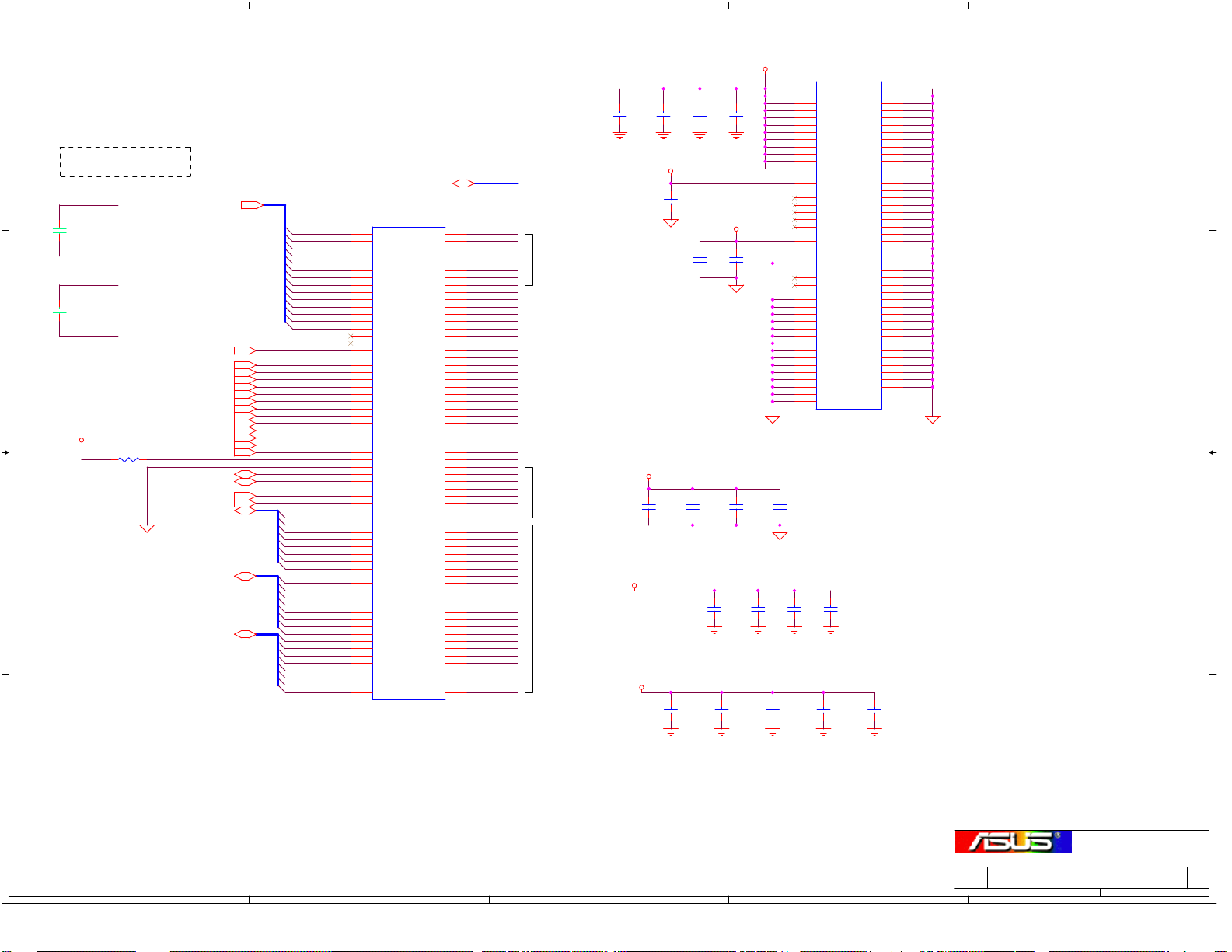

YONAH CPU (1)

Sheet

1

Leon and George

2

61

of

Rev

1.0

ASUSTeK COMPUTER INC

Size

Project Name

Custom

2

Date:

T12F

Wednesday, April 26, 2006

Engineer:

5

www.bufanxiu.com

4

3

2

1

YUNAH FSB667

LFM TYP HFM

VCC 1.14V 1.2V 1.356V

C4 C3 C0

ICC 0.9A 7.59A 27A

D D

+VCORE

U201C

A7

VCC[1]

A9

VCC[2]

A10

VCC[3]

A12

VCC[4]

A13

VCC[5]

A15

VCC[6]

A17

VCC[7]

A18

VCC[8]

A20

VCC[9]

B7

VCC[10]

B9

VCC[11]

B10

VCC[12]

B12

VCC[13]

B14

VCC[14]

B15

VCC[15]

B17

VCC[16]

B18

VCC[17]

B20

VCC[18]

C9

VCC[19]

C10

VCC[20]

C12

VCC[21]

C13

VCC[22]

C15

VCC[23]

C17

VCC[24]

C18

C C

B B

D10

D12

D14

D15

D17

D18

E10

E12

E13

E15

E17

E18

E20

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

VCC[25]

D9

VCC[26]

VCC[27]

VCC[28]

VCC[29]

VCC[30]

VCC[31]

VCC[32]

E7

VCC[33]

E9

VCC[34]

VCC[35]

VCC[36]

VCC[37]

VCC[38]

VCC[39]

VCC[40]

VCC[41]

F7

VCC[42]

F9

VCC[43]

VCC[44]

VCC[45]

VCC[46]

VCC[47]

VCC[48]

VCC[49]

VCC[50]

VCC[51]

VCC[52]

VCC[53]

VCC[54]

VCC[55]

VCC[56]

VCC[57]

VCC[58]

VCC[59]

VCC[60]

VCC[61]

VCC[62]

VCC[63]

VCC[64]

VCC[65]

VCC[66]

VCC[67]

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

VCC[77]

VCC[78]

VCC[79]

VCC[80]

VCC[81]

VCC[82]

VCC[83]

VCC[84]

VCC[85]

VCC[86]

VCC[87]

VCC[88]

VCC[89]

VCC[90]

VCC[91]

VCC[92]

VCC[93]

VCC[94]

VCC[95]

VCC[96]

VCC[97]

VCC[98]

VCC[99]

VCC[100]

VCCP[1]

VCCP[2]

VCCP[3]

VCCP[4]

VCCP[5]

VCCP[6]

VCCP[7]

VCCP[8]

VCCP[9]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

12G04600479A

YUNAH FSB667

Min Typ Max

VCCP 0.997V 1.05V 1.102V

Min Typ Max

ICCP

+VCORE

+VCCA

+VCCP_A

GTL+

+VCCA

120mA / 20mil

Close to Pin B26

12

10UF/10V

H_VID0

1 2

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

VCCSENSE

VSSSENSE

0Ohm

3 4

0Ohm

5 6

0Ohm

7 8

0Ohm

1 2

0Ohm

3 4

0Ohm

5 6

0Ohm

12

R302

100Ohm

2.5A

JP301

1 2

1 2

1MM_

@

7 8

C301

GND

RN302A

RN302B

RN302C

RN302D

RN303A

RN303B

RN303C

R301

1 2

100Ohm

OPEN_5MIL

RN303D

0Ohm

12

C318

0.01UF/25V

checklist suggests

10uF POSCAP

VR_VID0

VR_VID1

VR_VID2

VR_VID3

VR_VID4

VR_VID5

VR_VID6

+VCORE

VCCSENSE

VSSSENSE

U201D

A4

VSS[1]

A8

VSS[2]

A11

VSS[3]

A14

VSS[4]

A16

VSS[5]

A19

VSS[6]

A23

VSS[7]

A26

VSS[8]

B6

VSS[9]

B8

VSS[10]

B11

VSS[11]

B13

VSS[12]

B16

VSS[13]

B19

VSS[14]

B21

VSS[15]

B24

VSS[16]

C5

VSS[17]

C8

VSS[18]

C11

VSS[19]

C14

VSS[20]

C16

VSS[21]

C19

VSS[22]

C2

VSS[23]

C22

VSS[24]

C25

VSS[25]

D1

VSS[26]

D4

VSS[27]

D8

VSS[28]

D11

M22

M25

N23

N26

D13

D16

D19

D23

D26

E11

E14

E16

E19

E21

E24

F11

F13

F16

F19

F22

F25

G23

G26

H21

H24

K23

K26

L21

L24

VSS[29]

VSS[30]

VSS[31]

VSS[32]

VSS[33]

VSS[34]

E3

VSS[35]

E6

VSS[36]

E8

VSS[37]

VSS[38]

VSS[39]

VSS[40]

VSS[41]

VSS[42]

VSS[43]

F5

VSS[44]

F8

VSS[45]

VSS[46]

VSS[47]

VSS[48]

VSS[49]

F2

VSS[50]

VSS[51]

VSS[52]

G4

VSS[53]

G1

VSS[54]

VSS[55]

VSS[56]

H3

VSS[57]

H6

VSS[58]

VSS[59]

VSS[60]

J2

VSS[61]

J5

VSS[62]

J22

VSS[63]

J25

VSS[64]

K1

VSS[65]

K4

VSS[66]

VSS[67]

VSS[68]

L3

VSS[69]

L6

VSS[70]

VSS[71]

VSS[72]

M2

VSS[73]

M5

VSS[74]

VSS[75]

VSS[76]

N1

VSS[77]

N4

VSS[78]

VSS[79]

VSS[80]

P3

VSS[81]

+1

.5VO

50

50

50

50

50

50

50

50

50

12G04600479A

VSS[82]

VSS[83]

VSS[84]

VSS[85]

VSS[86]

VSS[87]

VSS[88]

VSS[89]

VSS[90]

VSS[91]

VSS[92]

VSS[93]

VSS[94]

VSS[95]

VSS[96]

VSS[97]

VSS[98]

VSS[99]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

+VCORE

1215---PWR comp

12

+

GND

Place these

12

C302

22UF/6.3V

GND GND

Place these lower s

12

C308

22UF/6.3V

@

GND GND

Place these

12

C314

22UF/6.3V

GND

Place these lower s

12

C319

22UF/6.3V

@

GND

GNDGND

Place the cap on North

CE301

of Secondary side

220UF/4V

@

upper side inside socket cavity on L1

12

22UF/6.3V

C303

12

C304

22UF/6.3V

GND

ide inside socket cavity on L1

12

22UF/6.3V

@

C309

12

C310

22UF/6.3V

@

GND

upper side inside socket cavity on L6

12

22UF/6.3V

GND

C315

12

C316

22UF/6.3V

N/A

GND

ide inside socket cavity on L6

C320

12

C321

22UF/6.3V

@

GNDGND

12

22UF/6.3V

@

GND GND

GND

GND

GND

+VCCP_A

GTL+

+VCORE

+1.5VS

Vcc Core Decoup

Primary side => Bot

Secondar

C305

C311

C317

C322

12

22UF/6.3V

12

22UF/6.3V

@

GND

C306

C312

12

22UF/6.3V

12

22UF/6.3V

@

12

22UF/6.3V

N/A

12

22UF/6.3V

@

+VCCP_A

GTL+

+VCORE

+1.5VS 9,10,20,25,26,37,52

2,5,6,9

50

ling Caps

tom side

y side => Top side

12

C307

22UF/6.3V

GND

12

C313

22UF/6.3V

@

GND

+VCCP_A

GTL+

+1.05V Decoupling Capacitor

Place near CPU

12

12

C323

C324

c0402

c0402

0.1UF/10V

0.1UF/10V

12

C325

c0402

0.1UF/10V

12

C326

c0402

0.1UF/10V

12

C327

c0402

0.1UF/10V

12

C328

c0402

0.1UF/10V

12

GND

+

CE302

100UF/2.5V

GND

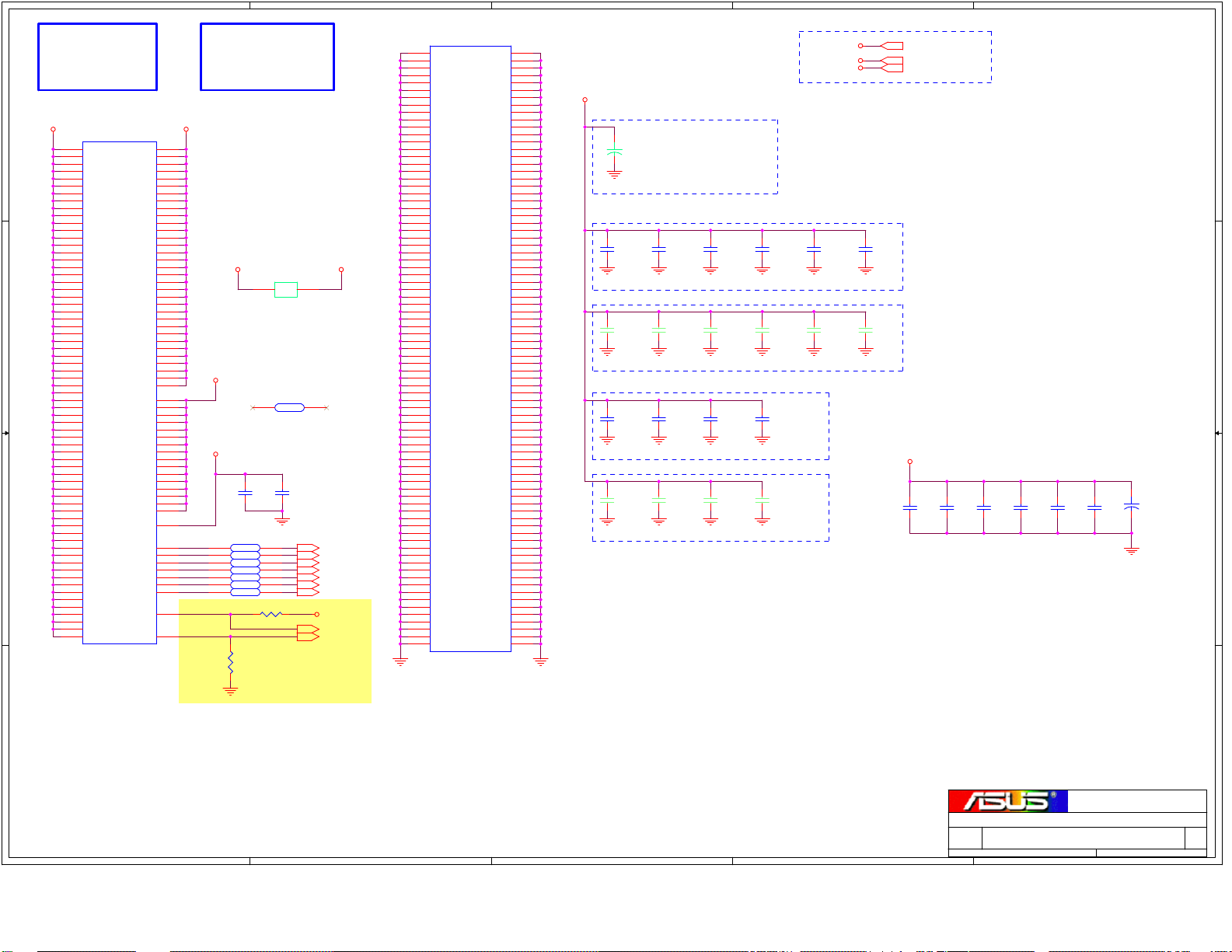

Layout Note:

VCCSENSE/VSSSENSE lines between the

CPU and the VR should have a trace width of

A A

5

18 mils on 7 mils spacing, with trace

impedance of Zo=27.4 Ohm.

The VCCSENSE/VSSSENSE should be

length matched to within 25 mils.

These resistors should be placed within 2

inch of the CPU.

<Variant Name>

Title :

ASUSTeK COMPUTER INC

SizeProject Name

A3

4

3

2

Date:

T12F

Wednesday, April 26, 2006

Engineer:

Yonah CPU (2)

Leon and George

3

Sheet of

1

Rev

1.0

61

5

www.bufanxiu.com

4

3

2

1

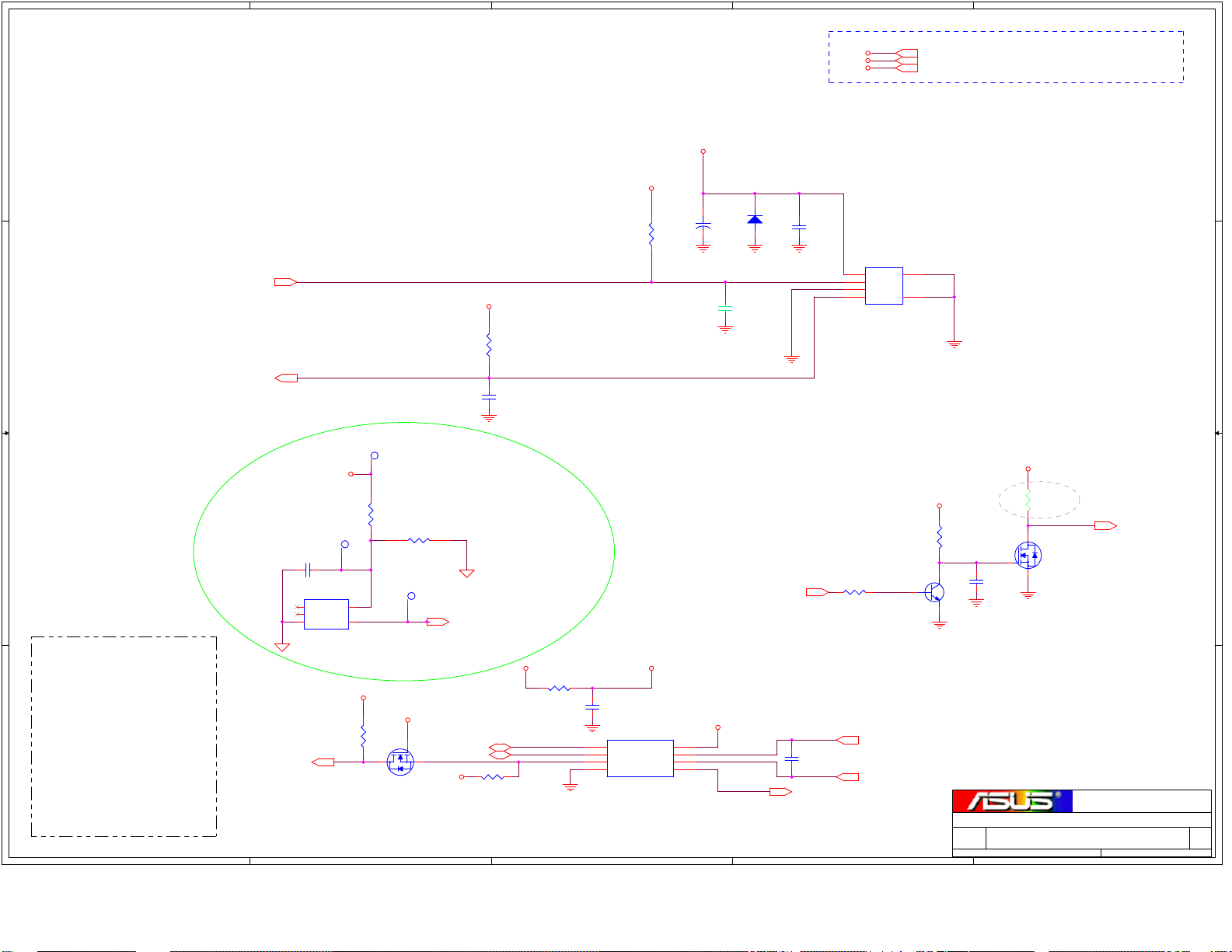

+5VS

+3VS

C402

0.1UF/10V

C406

2200PF/50V

N/A

+3VA

4

3

2

1 5

R407

1 2

330Ohm

CPU_THRM_DA

CPU_THRM_DC

29,38

CON401

4

3

2

1

WtoB_4P

Fan Speed Control

D D

+5VS

KBC will issue a

analog ( a voltage

level ) signal.

SW: FAN_DA1 must

be low du

C C

B B

Route H_THERMDA and H_THERMDC

on the same layer

------------------OTHER

12 mils

===============GND

10 mils

=========H_THERMDA(10 mils)

10 mils

A A

=========H_THERMDC(10 mils)

10 mils

=========GND

12 mils

---------------------OT

SIGNALS

HER SIGNALS

FAN_PWM

29

FAN0_TACH

29

ring S3

R1.2

THRM_CPU#

29

FAN_PWM

FAN0_TACH

C407

12

0.01UF/50V

1

NC

2

SUB

3 4

GND

PST9013NR

GND

U402

VCC

VOUT

+3VA

T4

02

TPC28

1

R409

10KOhm

r040

2

T

5

+3VA_EC

1 2

T4

03

TPC28

T

1

R411

7.68KOhm

1 2

Q40

3

3 2

3

D

2N7002

R412

100KOhm

T4

TPC28

1

+5VS

1

1

+3VS

R403

10KOhm

r0402_h

16

1 2

12

C401

2200PF/50V

N/A

GND

THERMAL PROTECT

PLACE

UNDER CPU

ION

(105 DEGREE C)

12

12

GN

D

01

T

FORCE_OFF#

SMB1_

29

G

SMB1_DAT

29

2

S

+3VS

29,41,51,60

CLK

1 2

R410

4.7KOhm

+3VS

SMB1_

SMB1_DAT

SM

R408

1 2

0Ohm

r040

CLK

BALERT#

12

2

8

7

6

5

r0402_h

+3VS_T

C405

0.1UF/10V

c0402

U401

SCLK

SDA

ALERT#

GND

MAX6657MS

R402

10KOhm

+3VS_TH

HM

+3VS

16

OVERT#

A

1 2

M

VCC

DXP

DXN

12

+

CE401

100UF/10V

GND

Sta

ndby Mode: 3uA(Max. 10uA)

Full Active: 0.5 mA(Max. 1m

+3VS_T

1

CPU_THRM_DA

2

CPU_THRM_DC

3

4

GND GND

12

C403

100PF/50V

@

GND

2,7,17

HM

EC_RST_SW#

1 2

PM_THRMT

D1

1N4148W

A)

12

GND

RIP#

4"-8"

12

4"-8"

EC_RST_SW#

Avoid BPSB,Power

5

4

3

2

SIDE2

SIDE1

TRIP_R

+5VS

13,19,20,21,22,28,29,30,37,38,50,61

+3VS

5,7,9,11,12,13,14,15,19,20,21,22,23,25,26,27,28,29,30,31,32,33,37,39,40,42,43,50,52,60,61

+3VA

12,20,22,29,37,38,40,54,59,63

6

GND

+3

VA

11/29

12

1

1

G

GND

T12F

3

2

32

D

S

R405

10KOhm

r040

2

@

VSUS_ON

Q40

2N7002

1

Engineer:

VSUS_ON

Title :

THER-SENSOR,FAN

Leon and George

Sheet

1

PM

Q40

B

1

BS3904

2

2

+3VS

12

R406

1MOh

m

VSUS_ON_G

3

2

C

E

2

GND

GND

<Variant Name>

ASUSTeK COMPUTER INC

SizeProject Name

A3

Date:

12

C404

0.22UF/6.3V

Wednesday, April 26, 2006

25,29,51

Rev

4

1.0

61

of

5

www.bufanxiu.com

+VCCP_AGTL+

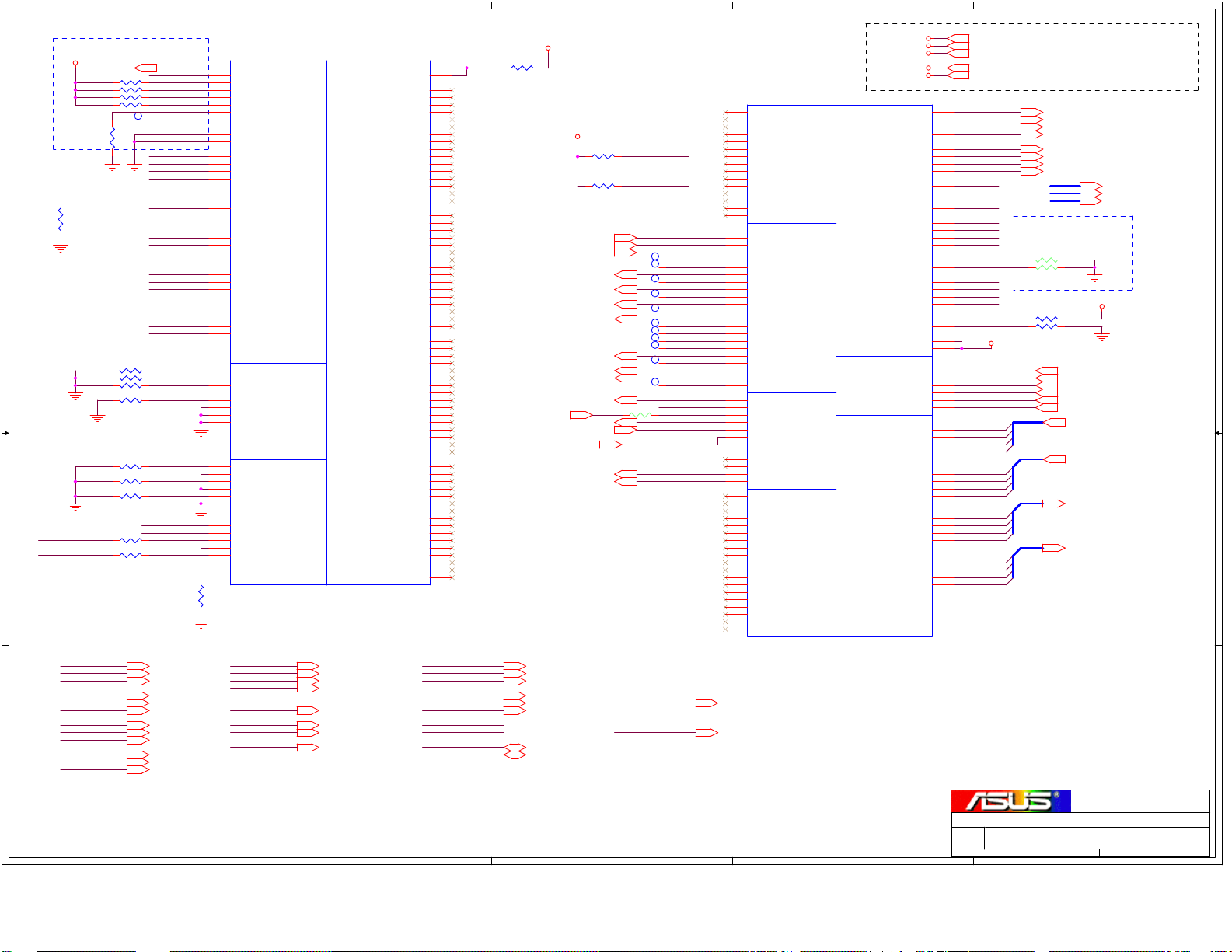

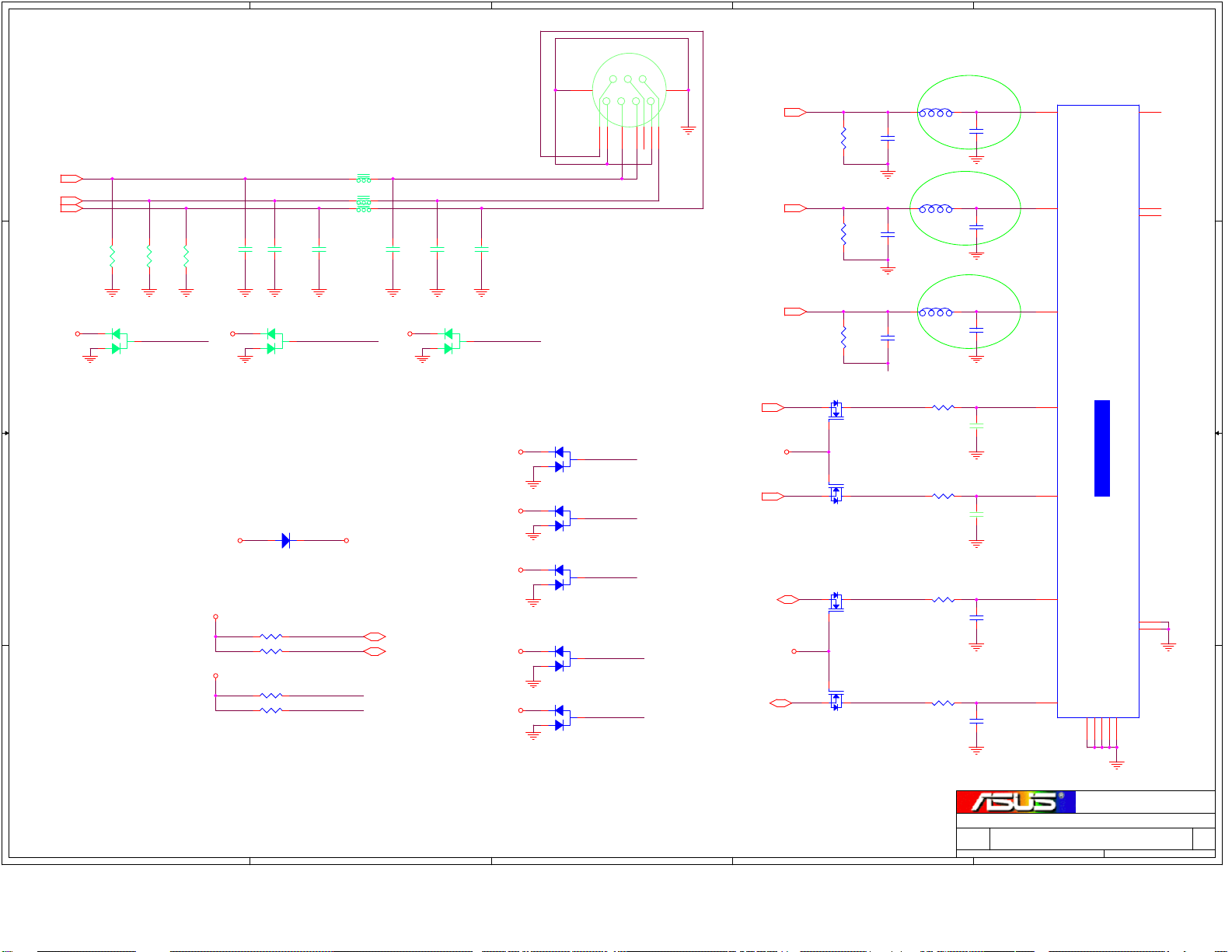

Control ne

Request

PCIE_REQ1#PCIE0(#),PCIE6(

PCIE_REQ2

#

PCIE_REQ3

PCIE_REQ4

#

#

14,15,19,25,26

14,15,19,25,26

D D

C C

B B

SELPCIE0_LCD#:

0-->pin17,pin18=LCDCLK(96MHz) or

27M/27M_SS

A A

SELLCD_27#/PCICLK_F1:

1-->pin17,pin18=LCDCLK(96MHz)

PCICLK2/REQ_SEL:

1-->pin40,pin41=PREQ1#,PREQ2#

ITP_EN/PCICLK_F0:

1-->CPU_ITP pair

t

PCIE1(#),PCIE8(

PCIE2(#),PCIE4(

PCIE3(#),PCIE5(

PCIE7(#

)

CLK_LCD_SSCG

7

CLK_LCD_SSCG#

7

CLK_USB48

19

CPU_BSEL0

2

CPU_BSEL1

2

CLK_LAN_PCI

34

CLK_CBPCI

31,43

CLK_FWHPCI

26

CLK_TPMPCI

42

CLK_ECPCI

29

CLK_ICHPCI

18

SMB_CLK_S

SMB_DA

5

#)

#)

#)

#),

GND

T_S

Net nam

e

None

None

CLK_PCIE_MINICARD

CLK_MCH_3GPLL(

+/-30ppm/20PF

X5

01

14.318Mh

1 2

12

C516

22PF/25V

z

@

12

C517

22PF/25V

C524 10PF/50V

@

1 2

GND

(#)

#)

GND

12

12

C514

C515

10UF/10V

0.1UF/10V

GND

GND

+3VS_CLK

+3VS_CLK

+3VS_CLK

C519 10PF/50V

C520 10PF/50V

C522 10PF/50V

C521 10PF/50V

C523 10PF/50V

C518 10PF/50V

@

@

@

@

@

1 2

1 2

1 2

1 2

1 2

1 2

Realtek:Mount R519,Remove R550 R534

R530

R532

R535

R539

R541

R544

R565

R546

R552

R536

R540

R548

R550

R553

4

R501

1KOhm

R503

1KOhm

R504

1KOhm

R506

1KOhm

R517

2.2Ohm

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

4

@

12

@

12

@

12

@

12

+3VS_CLK

12

GND

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

33Ohm

33Ohm

33Ohm

2.2KOhm

33Ohm

10KOhm

33Ohm

33Ohm

33Ohm

33Ohm

10KOhm

10KOhm

33Ohm

10KOhm

R558

475Ohm

GND

+3VS_VDDA

ICS_X1

ICS_X2

LCD_SSCG

LCD_SSCG#

FSA

PCICLK5

PCICLK4

PCICLK3

PCICLK2

PCICLK_F0

ICS_IREF

1 2

R502

1 2

R505

1 2

R507

1 2

GND

0Ohm

0Ohm

0Ohm

+3V

S

12

0.1UF/10V

GND

C501

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

12

C502

0.1UF/10V

Pin34 is PWRSAVE#

U501

21

VDDPCIEX1

28

VDDPCIEX2

42

VDDPCIEX3

34

VDD

50

VDDCPU

45

VDDA

46

GNDA

58

X1

57

X2

17

27FIX/LCD_SSCGT/PCIEX0T

18

27SS/LCD_SSCGC/PCIEX0C

12

FSLA/USB_48MHz

16

FSLB/TEST_MODE

5

SELPCIEX0_LCD#PCICLK5

4

PCICLK4

3

PCICLK3

64

PCICLK2/REQ_SEL

9

SELLCD_27#/PCICLK_F1

8

ITP_EN/PCICLK_F0

54

SCLK

55

SDATA

47

IREF

2

GND1

6

GND2

13

GND3

29

GND4

37

GND5

53

GND6

59

GND7

ICS954310CGLFT

Internal Pull-Up Resistor

Internal Pull-Down Resistor

3

7

7

7

120Ohm/100Mhz

21

L502

120Ohm/100Mhz

+3VS_VDDPCI

1

7

VDDPCI1

VDDPCI2

CPUCLKT2_ITP/PCIEXT8

CPUCLKC2_ITP/PCIEXC8

intern

al

pull hi

REF1/FSLC/TEST_SEL

3

Bclk

FS

B

133

533

667

166

L501

21

12

12

C508

0.1UF/10V

0.1UF/10V

VDD48

VDDREF

PCI/PCIEX_STOP#

CPU_STOP#

CPUCLKT1

CPUCLKC1

CPUCLKT0

CPUCLKC0

PEREQ1#/PCIEXT7

PEREQ2#/PCIEXC7

PCIEXT6

PCIEXC6

PCIEXT5

PCIEXC5

PCIEXT4

PCIEXC4

PCIEXT3

PCIEXC3

PCIEXT2

PCIEXC2

PCIEXT1

PCIEXC1

SATACLKT

SATACLKC

DOTT_96MHz

DOTC_96MHz

PEREQ3#

gh

PEREQ4#

Vtt_PwrGd#/PD

FSLC FSL

BSE

L2

L

L H

+3VS_CLK

12

C503

10UF/10V

C509

GND

11

56

63

62

49

48

52

51

44

43

41

40

39

38

36

35

30

31

24

25

22

23

19

20

26

27

14

15

32

33

10

61

60

REF0

BSE

12

C504

0.1UF/10V

12

C510

10UF/10V

+3VS_VDD48

+3VS_VDDREF

STP_PCI#

STP_CPU#

CLK_CPU

CLK_CPU#

CLK_MCH

CLK_MCH#

PEREQ#1

PEREQ#2

PCIE6

PCIE#6

PCIE4

PCIE#4

PCIE3

PCIE#3

PCIE2

PCIE#2

CLK_SATA

CLK_SATA#

DOT96

DOT96#

REF1

REF0

B FSLA

L1

12

0.1UF/10V

R513

2.2Ohm

R526

R527

R523

R524

R537

R538

R542

R543

R545

R547

R549

R551

R556

R557

R563

R564

BSE

HL

H

C505

1 2

1 2

1 2

1 2

1 2

R531

R533

R534

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

R554

R555

1 2

1 2

R561

1 2

1 2

L0

+3VS_CLK

12

C506

0.1UF/10V

12

C511

0.1UF/10V

STP_PCI#

STP_CPU#

1 2

10KOhm

12

33Ohm

@

33Ohm

@

33Ohm

33Ohm

33Ohm

33Ohm

33Ohm

33Ohm

1 2

1 2

33Ohm

33Ohm

0Ohm

12

2.2KOhm

33Ohm

12

0.1UF/10V

GND

12

10UF/10V

GND

33Ohm

33Ohm

33Ohm

33Ohm

12

C507

C512

10KOhm

0Ohm

33Ohm

33Ohm

@

@

2

+VCCP_AGTL+

+3

19

19,50

GND

CLK_PCIE_NEWCARD

CLK_PCIE_NEWCARD#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_MINICARD

CLK_PCIE_MINICARD#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_UMA_96M

CLK_UMA_96M#

MCH_CLK_REQ#

CLK_MINICARD_REQ#

CPU_BSEL2

CLK_ICH14

2

VS

R514

1Ohm

1 2

C513

1 2

0.1UF/10V

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_BCLK

CLK_MCH_BCLK#

+3

VS

CLK_NEWCARD_REQ#

CLK_PCIE_SATA

CLK_PCIE_SATA#

2

19

1

+VCCP_AGTL+

+3VS4,7,9,11,12,13,14,15,19,20,21,22,23,25,26,27,28,29,30,31,32,33,37,39,40,42,43,50,52,60,61

25

7

7

26

18

18

GND

2

6

25

26

2,3,6,9

Layout N

ote:

Plac

e termination close to source IC

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_LCD_SSCG

CLK_LCD_SSCG#

CLK_UMA_96M

25

CLK_UMA_96M#

CLK_PCIE_MINICARD

CLK_PCIE_MINICARD#

CLK_PCIE_NEWCARD

CLK_PCIE_NEWCARD#

CLK_PCIE_SATA

CLK_PCIE_SATA#

R1.

1

2

6

R508

R509

R510

R511

R512

R515

R516

R518

R519

R521

R522

R525

R528

R529

R566

R567

R568

R569

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

49.9Ohm

r0402

49.9Ohm

r0402

49.9Ohm

r0402

49.9Ohm

r0402

49.9Ohm

r0402

49.9Ohm

r0402

49.9Ohm

r0402

49.9Ohm

r0402

49.9Ohm

r0402

49.9Ohm

r0402

49.9Ohm

r0402

49.9Ohm

r0402

49.9Ohm

r0402

49.9Ohm

r0402

49.9Ohm

r0402

@

49.9Ohm

r0402

@

49.9Ohm

r0402

@

49.9Ohm

r0402

@

PREQ#1

0=PCIEX 6/0 Not Controlled

1=PCIEX 6/0 Controlled

PREQ#2

17

7

7

7

26

0=PCIEX 8/1 Not Controlled

17

1=PCIEX 8/1 Controlled

PREQ#3

+3VS_CLK

0=PCIEX 4/2 Not Controlled

1=PCIEX 4/2 Controlled

12

R560

10KOhm

@

CLK_EN#

50

PREQ#4

0=PCIEX 7/5/3 Not Controlled

1=PCIEX 7/5/3 Controlled

<Variant Name>

Title :

CLOCK GEN

Sheet

1

Leon and George

5

of

ASUSTeK COMPUTER INC

Size

Project Name

Custom

Wednesday, April 26, 2006

Date:

Engineer:

T12F

GND

Rev

1.0

61

5

www.bufanxiu.com

H_D#[0..63]

2

K11

T10

W11

U11

T11

AB7

AA9

Y10

AB8

AA4

AA7

AA2

AA6

AA10

AA1

AB4

AC9

AB11

AC11

AB3

AC2

AD1

AD9

AC1

AD7

AC6

AB5

AD10

AD4

AC8

AG2

AG1

F1

J1

H1

J6

H3

K2

G1

G2

K9

K1

K7

J8

H4

J3

G4

T3

U7

U9

W9

T1

T8

T4

W7

U5

T9

W6

T5

W4

W3

Y3

Y7

W5

W2

Y8

E1

E2

E4

Y1

U1

W1

U601A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

H_CLKIN

H_CLKIN#

CALIST

OGA_Q137

H_D#0

H_D#1

H_D#2

H_D#3

5

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_XRCOM

P

H_X

SCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

CLK_MCH_BCLK

CLK_MCH_BCLK#

D D

C C

B B

CLK_MCH_BCLK

5

CLK_MCH_BCLK#

A A

5

4

H_A#[31..3]

H_A#3

H9

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_AVREF

H_BNR#

H_BPRI#

H_BREQ#0

H_CPURST#

HOST

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_SLPCPU#

4

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_DVREF

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_TRDY#

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

E8

B9

C13

J13

C6

F6

C7

B7

A7

C3

J9

H8

K13

J7

W8

U3

AB10

K4

T7

Y5

AC4

K3

T6

AA5

AC5

D3

D4

B3

D8

G8

B8

F8

A8

B4

E6

D6

E3

E7

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADS#

H_ADST

B#0

H_ADST

B#1

H_VREF

H_BNR#

H_BPRI#

H_BR0#

H_CPURST#

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTB

P#0

H_DSTB

P#1

H_DSTB

P#2

H_DSTB

P#3

H_HIT#

H_HITM

#

H_LOCK#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

N_CPUSLP#

H_TRDY#

H_ADS#

H_ADST

H_ADST

H_BNR#

H_BPRI#

H_BR0#

H_CPURST#

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTB

H_DSTB

H_DSTB

H_DSTB

H_HIT#

H_HITM#

H_LOCK#

R611

0Ohm

12

2

2

B#0

2

B#1

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

P#0

2

P#1

2

P#2

2

P#3

2

2

2

2

H_REQ#[4..0]

H_RS#[0..2]

+V

3

CCP_AGTL+

R601

100Oh

m

1%

1 2

R606

200Oh

m

1%

1 2

GND

Layou

GND

t Note:

0.1uF should be

less

from GMCH pin.

2

2

H_CPUSLP#

H_TRDY#

3

2,17

2

<500 mil (55 Ohm)

T/B trace 5.5 ,

Space 25

12

C601

0.1UF/10V

placed 100mils or

+VCCP

GND

+VCCP

GND

+VCCP

GND

2

R602

54.9Ohm

1%

H_X

1 2

H_XRCOMP

R604

24.9Ohm

1%

1 2

R607

221Oh

1%

1 2

R608

100Oh

1%

1 2

R609

221Oh

1%

1 2

R610

100Oh

1%

1 2

2

SCOMP

m

m

m

m

12

GND

12

GND

5.5/20 mils

10/20mils

H_XSWING

C602

0.1UF/10V

H_YSWING

C603

0.1UF/10V

<Variant Name>

ASUSTeK COMPUTER INC

SizeProject Name

B

Date:

+VCCP

+V

CCP_AGTL+

+VCCP

R603

54.9Ohm

1%

H_YSCOMP

1 2

H_YRCOMP

R605

24.9Ohm

1%

1 2

GND

10/20mils

Signal vol

tage level =

0.3125

*VCCP

Trace should be 10 mil w

with 20 mil spac

Wednesday, April 26, 2006

ing

T12F

1

+VCCP

+V

CCP_AGTL+

ide

Title :

Engineer:

Sheet

1

2,9,20,52

2,3,5,9

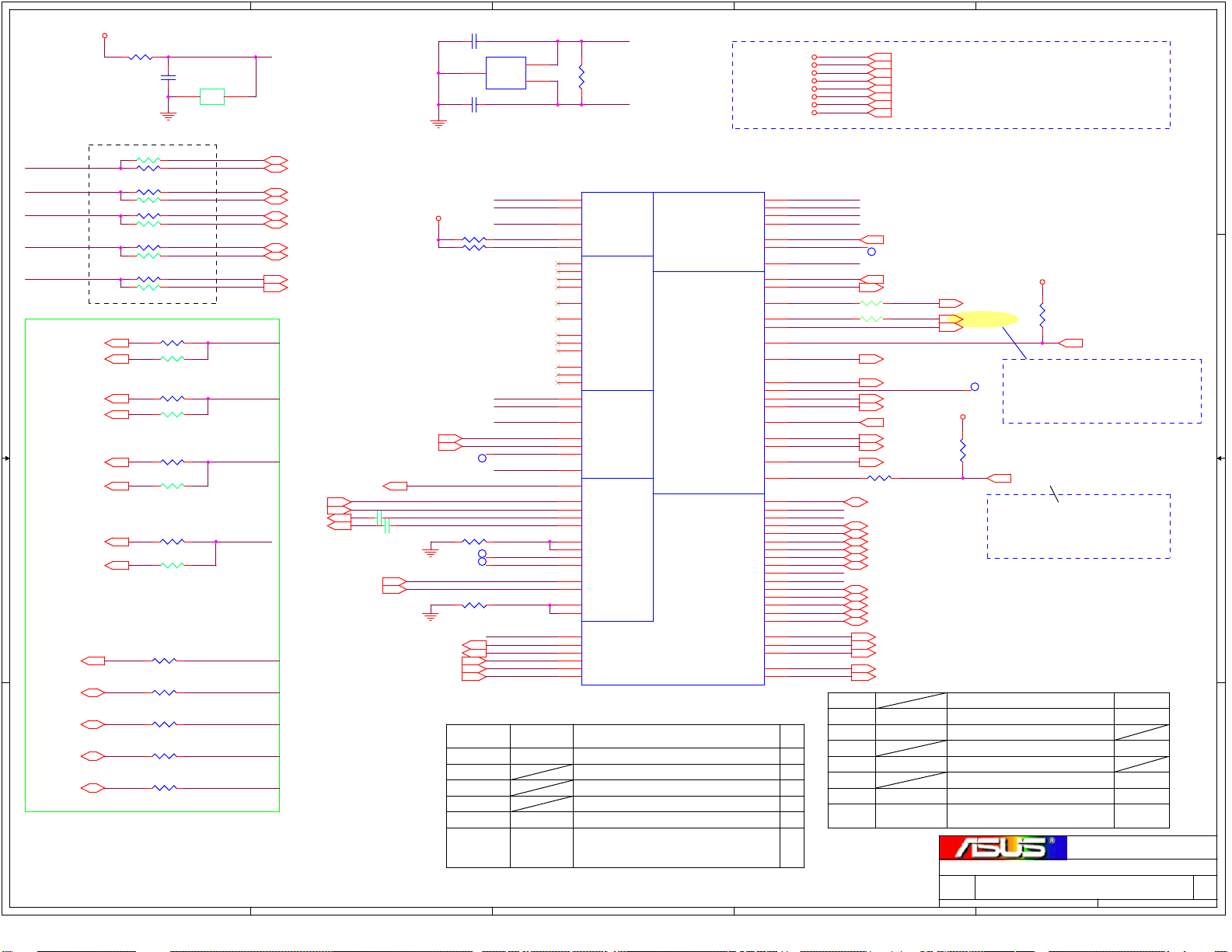

Calistoga MCH (1)

Leon and George

6

Rev

1.0

61

of

5

4,5,9,11,12,13,14,15,19,20,21,22,23,25,26,27,28,29,30,31,32,33,37,39,40,42,43,50,52,60,61

www.bufanxiu.com

4

3

2

1

+1.5VS_PCIE

+3VS

L_

BKLTCTL

12

R703 10KOhm

1 2

R704 10KOhm

1 2

R705 10KOhm

1 2

R706 10KOhm

D D

1 2

GND

C C

B B

A A

DAC_HSYNC_GM

DAC_VSYNC_GM

R707

1.5KOhm

1%

L_BKL

TEN

R710

100KOhm

R715 150Ohm

R716 150Ohm

R717 150Ohm

GND

GND

R720 150Ohm

R721 150Ohm

R722 150Ohm

GND

LVDS_L0N

LVDS_L2N

LVDS_L0P

LVDS_L1P

LVDS_L2P

LVDS_U0N

LVDS_U1N

LVDS_U2N

LVDS_U0P

LVDS_U1P

LVDS_U2P

1 2

12

GND

1 2

1 2

T7

02

GND

R701

4.99KOhm

1%

R723

39Ohm

R724

39Ohm

5

L_

BKLTCTL

L_BKLT

L_CTLA_CLK

L_CTLB_

EDID_CLK

EDID_DAT

L_IBG

L_VB

1

L_VDDEN

L_VREFH

L_VREFL

LVDS_LCLKN

LVDS_LCLKP

LVDS_UCLKN

LVDS_UCLKP

LVDS_L0N

LVDS_L1N

LVDS_L2N

LVDS_L0P

LVDS_L1P

LVDS_L2P

LVDS_U0N

LVDS_U1N

LVDS_U2N

LVDS_U0P

LVDS_U1P

LVDS_U2P

TV_CV

12

TV_Y

12

TV_

12

1%

TV_IREF

12

CRT_BLUE

12

1%

CRT_GREEN

12

1%

CRT_RED

12

1%

CRT_DDC_CLK

CRT_DDC_DATA

N_HSYNC

N_VSYNC

R725

255Ohm

1%

LVDS_L0N

LVDS_L1N

LVDS_L2N

LVDS_L0P

LVDS_L1P

LVDS_L2P

LVDS_U0N

LVDS_U1N

LVDS_U2N

LVDS_U0P

LVDS_U1P

LVDS_U2P

G

C

EN

BS

12

12

12

DATA

GND

GND

12

12

12

12

12

12

12

12

12

D32

J30

H30

H29

G26

G25

B38

C35

F32

C33

C32

A33

A32

E27

E26

C37

B35

A37

B37

B34

A36

G30

D30

F29

F30

D29

F28

A16

C18

A19

J20

B16

B18

B19

E23

D23

C22

B22

A21

B21

GND

C26

C25

G23

J22

H23

CRT_IREF

12

U601C

L_BKLTCTL

L_BKLTEN

L_CLK_CTLA

L_DATA_CTLB

L_DDC_CLK

L_DDC_DATA

L_IBG

L_VBG

L_VDDEN

L_VREFH

L_VREFL

LA_CLK#

LA_CLK

LB_CLK#

LB_CLK

LA_DATA#_0

LA_DATA#_1

LA_DATA#_2

LA_DATA_0

LA_DATA_1

LA_DATA_2

LB_DATA#_0

LB_DATA#_1

LB_DATA#_2

LB_DATA_0

LB_DATA_1

LB_DATA_2

TV_DACA_OUT

TV_DACB_OUT

TV_DACC_OUT

TV_IREF

TV_IRTNA

TV_IRTNB

TV_IRTNC

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_IREF

CRT_VSYNC

CALISTOGA_Q13

LVDS_LCLKN

LVDS_LCLKPLVDS_L1N

LVDS_UCLKN

LVDS_UCLKP

L_BKLT

EN

EDID_CLK

EDID_DAT

L_VDDEN

EXP_A_C

EXP_A_COMPI

EXP_A_COMPO

EXP_A_RXN_0

EXP_A_RXN_1

EXP_A_RXN_2

EXP_A_RXN_3

EXP_A_RXN_4

EXP_A_RXN_5

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXN_8

EXP_A_RXN_9

EXP_A_RXN_10

EXP_A_RXN_11

EXP_A_RXN_12

EXP_A_RXN_13

PCI-EXPRESS GRAPHICS

12

12

12

EXP_A_RXN_14

EXP_A_RXN_15

EXP_A_RXP_0

EXP_A_RXP_1

EXP_A_RXP_2

EXP_A_RXP_3

EXP_A_RXP_4

EXP_A_RXP_5

EXP_A_RXP_6

EXP_A_RXP_7

EXP_A_RXP_8

EXP_A_RXP_9

EXP_A_RXP_10

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_TXN_0

EXP_A_TXN_1

EXP_A_TXN_2

EXP_A_TXN_3

EXP_A_TXN_4

EXP_A_TXN_5

EXP_A_TXN_6

EXP_A_TXN_7

EXP_A_TXN_8

EXP_A_TXN_9

EXP_A_TXN_10

EXP_A_TXN_11

EXP_A_TXN_12

EXP_A_TXN_13

EXP_A_TXN_14

EXP_A_TXN_15

EXP_A_TXP_0

EXP_A_TXP_1

EXP_A_TXP_2

EXP_A_TXP_3

EXP_A_TXP_4

EXP_A_TXP_5

EXP_A_TXP_6

EXP_A_TXP_7

EXP_A_TXP_8

EXP_A_TXP_9

EXP_A_TXP_10

EXP_A_TXP_11

EXP_A_TXP_12

EXP_A_TXP_13

EXP_A_TXP_14

EXP_A_TXP_15

12

12

12

12

4

LVDS

TV

VGA

7

LVDS_LCLKN

LVDS_LCLKP

LVDS_UCLKN

LVDS_UCLKP

L_BKLTEN12

EDID_CLK

EDID_DAT

L_VDDEN

D40

D38

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

TV_C

VBS

TV_Y

TV_

C

CRT_RED

CRT_GREEN

CRT_BLUE

DAC_HSYNC_GM

DAC_VSYNC_GM

CRT_DDC_CLK

CRT_DDC_DATA

OMP

19,50

R702

1 2

24.9Ohm

1%

PM_DPRSLPVR

2,4,17

19,29

18,19,25,28,29,42

18

TV_C

TV_Y

TV_C13

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_DDC_CLK

CRT_DDC_DATA

+3

VS

MCH_BSEL0

5

MCH_BSEL1

5

MCH_BSEL2

5

MCH_CFG_5

11

MCH_CFG_7

11

MCH_CFG_9

11

MCH_CFG_11

11

MCH_CFG_16

11

MCH_CFG_18

11

MCH_CFG_19

11

PM_BMBUSY#

19

PM_THRMT

ICH_PWROK

PLT_RST#

MCH_ICH_SYNC#

MCH_CLK_REQ#

5

VBS

13

13

13

13

13

R708

1 2

10KOhm

R709

1 2

10KOhm

R718

RIP#

13

13

PM_E

PM_E

T7

T7

T7

T7

T7

T7

T7

T7

T7

T7

T7

0Ohm

1 2

@

DAC_VSYNC_GM

DAC_HSYNC_GM

3

XTTS#0

XTTS#1

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

MCH_CFG_3

03

1

MCH_CFG_4

01

1

MCH_CFG_5

MCH_CFG_6

04

1

MCH_CFG_7

MCH_CFG_8

05

1

MCH_CFG_9

MCH_CFG_10

06

1

MCH_CFG_11

MCH_CFG_12

07

1

MCH_CFG_13

08

1

MCH_CFG_14

09

1

MCH_CFG_15

10

1

MCH_CFG_16

MCH_CFG_17

11

1

MCH_CFG_18

MCH_CFG_19

MCH_CFG_20

12

1

PM_BMBUSY#

PM_EX

PM_EX

PM_THRM

ICH_PWROK

RST_IN#_MCH

MCH_ICH_SYNC#

MCH_CLK_REQ#

TTS#0

TTS#1

TRIP#

U601B

T32

RSVD_1

R32

RSVD_2

F3

RSVD_3

F7

RSVD_4

AG11

RSVD_5

AF11

RSVD_6

H7

RSVD_7

J19

RSVD_8

K30

TV_DCONSEL_0

J29

TV_DCONSEL_1

A41

RSVD_11

A35

RSVD_12

A34

RSVD_13

D28

RSVD_14

D27

RSVD_15

K16

CFG_0

K18

CFG_1

J18

CFG_2

F18

CFG_3

E15

CFG_4

F15

CFG_5

E18

CFG_6

D19

CFG_7

D16

CFG_8

G16

CFG_9

E16

CFG_10

D15

CFG_11

G15

CFG_12

K15

CFG_13

C15

CFG_14

H16

CFG_15

G18

CFG_16

H15

CFG_17

J25

CFG_18

K27

CFG_19

J26

CFG_20

G28

PM_BMBUSY#

F25

PM_EXTTS#_0

H26

PM_EXTTS#_1

G6

PM_THRMTRIP#

AH33

PWROK

AH34

RSTIN#

H28

SDVO_CTRLCLK

H27

SDVO_CTRLDATA

K28

ICH_SYNC#

H32

CLK_REQ#

D1

NC0

C41

NC1

C1

NC2

BA41

NC3

BA40

NC4

BA39

NC5

BA3

NC6

BA2

NC7

BA1

NC8

B41

NC9

B2

NC10

AY41

NC11

AY1

NC12

AW41

NC13

AW1

NC14

A40

NC15

A4

NC16

A39

NC17

A3

NC18

CALISTOGA_Q13

DAC_VSYNC_GM

DAC_HSYNC_GM

RSVD

DDR MUXINGCLK

CFG

PM

MISC NC

DMI

7

18

18

2

+3VS

M_VREF_MCH

+1.5VS

+1.5VS_PCIE

+1.8V

SM_CK_0

SM_CK_1

SM_CK_2

SM_CK_3

SM_CK#_0

SM_CK#_1

SM_CK#_2

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_OCDCOMP_0

SM_OCDCOMP_1

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP#

SM_RCOMP

SM_VREF_0

SM_VREF_1

G_CLKIN#

G_CLKIN

D_REFCLKIN#

D_REFCLKIN

D_REFSSCLKIN#

D_REFSSCLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

+3VS

M_VREF_MCH

+1.5VS

+1.5VS_PCIE

+1.8V 10,14,15,37,53

M_CLK_DDR0

AY35

M_CLK_DDR1

AR1

M_CLK_DDR2

AW7

M_CLK_DDR3

AW40

M_CLK_DDR#0

AW35

M_CLK_DDR#1

AT1

M_CLK_DDR#2

AY7

M_CLK_DDR#3

AY40

M_CK

E0

AU20

M_CK

E1

AT20

M_CK

E2

BA29

M_CK

E3

AY29

M_CS

#0

AW13

M_CS

#1

AW12

M_CS

#2

AY21

M_CS

#3

AW21

M_OCDCOMP0

AL20

M_OCDCOMP1

AF10

M_ODT

BA13

BA12

AY20

AU21

AV9

AT9

AK1

AK41

AF33

AG33

A27

A26

C40

D41

AE35

AF39

AG35

AH39

AC35

AE39

AF35

AG39

AE37

AF41

AG37

AH41

AC37

AE41

AF37

AG41

0

M_ODT

1

M_ODT

2

M_ODT

3

M_RCO

M_RC

OMP

M_VREF_MCH

CLK_MCH_3GPLL#

CLK_MCH_3GPLL

CLK_UMA

CLK_UMA

CLK_LCD_SSCG#

CLK_LCD_SSCG

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_

TXP0

DMI_

TXP1

DMI_

TXP2

DMI_

TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_R

XP0

DMI_R

XP1

DMI_R

XP2

DMI_R

XP3

<Variant Name>

ASUSTeK COMPUTER INC

SizeProject Name

A3

Wednesday, April 26, 2006

Date:

14,15,16

9,10,20,25,26,37,52

9

Layout Note:

Route as short as possible

R711 40.2Ohm

R712 40.2Ohm

R713 80.6Ohm 1%

MP#

1 2

1 2

R714 80.6Ohm 1%

_96M#

_96M

T12F

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR2

M_CLK_DDR3

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#2

M_CLK_DDR#3

12

12

CLK_MCH_3GPLL#

CLK_MCH_3GPLL

CLK_UMA_

CLK_UMA

CLK_LCD_SSCG#

CLK_LCD_SSCG

DMI_TXN[0..3]

DMI_TXP[0..3]

DMI_RXN[0..3]

DMI_RXP[0..3]

Title :

Engineer:

14

14

15

15

14

14

15

15

M_CKE[0..3]

M_CS#[0..3]

M_ODT[0..3]

@

@

GND

+1.8V

GND

5

5

96M#

5

_96M

5

5

5

18

18

18

18

Calistoga PCI-E (2)

Leon and George

Sheet

1

7

14,15,16

14,15,16

14,15,16

of

Rev

1.0

61

www.bufanxiu.com

D D

C C

B B

5

M_A_D

M_A_D

M_A_D

M_A_D

M_A_D

M_A_D

M_A_D

M_A_D

M_A_D

M_A_D

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

M_A_DQ

U601D

Q0

AJ35

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

AL5

AL2

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

CALISTOGA_Q13

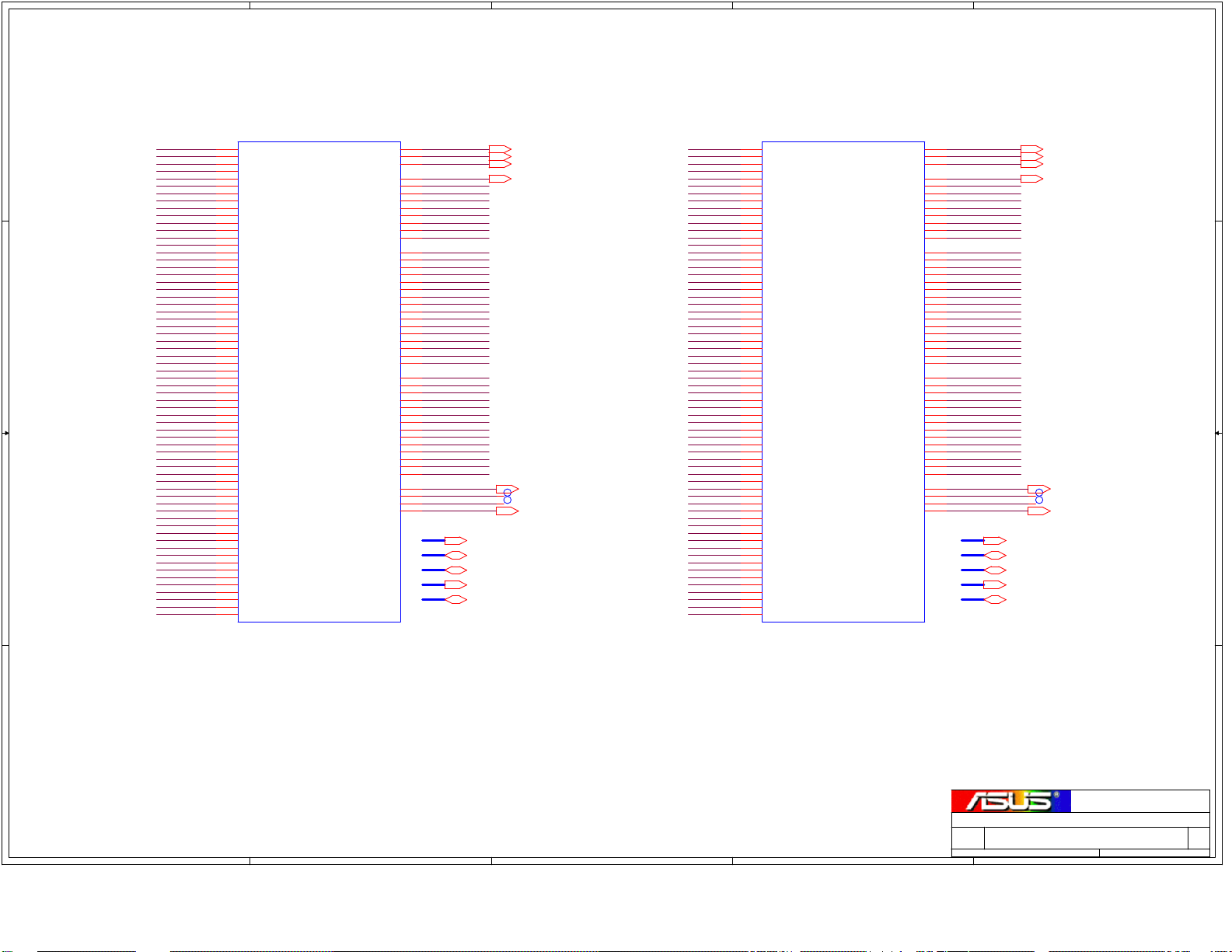

SYSTEM MEMORY A

DDR

7

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

Q9

4

SA_BS_0

SA_BS_1

SA_BS_2

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

AU12

AV14

BA20

AY13

AJ33

AM35

AL26

AN22

AM14

AL9

AR3

AH4

AK33

AT33

AN28

AM22

AN12

AN8

AP3

AG5

AK32

AU33

AN27

AM21

AM12

AL8

AN3

AH5

AY16

AU14

AW16

BA16

BA17

AU16

AV17

AU17

AW17

AT16

AU13

AT17

AV20

AV12

AW14

AK23

AK24

AY14

M_

A_BS#0

M_

A_BS#1

M_

A_BS#2

M_A_CA

S#

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQ

S0

M_A_DQ

S1

M_A_DQ

S2

M_A_DQ

S3

M_A_DQ

S4

M_A_DQ

S5

M_A_DQ

S6

M_A_DQ

S7

M_A_DQ

S#0

M_A_DQ

S#1

M_A_DQ

S#2

M_A_DQ

S#3

M_A_DQ

S#4

M_A_DQ

S#5

M_A_DQ

S#6

M_A_DQ

S#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_RA

S#

M_A_RCVENIN#

M_A_RCVENOUT#

M_A_W

E#

M_A_DM[0..7]

M_A_DQS[0..7]

M_A_DQS#[0..7]

M_A_A[0..13]

M_A_DQ[0..63]

M_A_BS0

M_A_BS1

M_A_BS2

M_A_CAS#14,16

T8

1

T8

1

14

14,16

M_A_R

02

01

M_A_

14

14

14

WE#

AS#

14,16

14,16

14,16

14,16

14,16

3

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

Q10

Q11

Q12

Q13

Q14

Q15

Q16

Q17

Q18

Q19

Q20

Q21

Q22

Q23

Q24

Q25

Q26

Q27

Q28

Q29

Q30

Q31

Q32

Q33

Q34

Q35

Q36

Q37

Q38

Q39

Q40

Q41

Q42

Q43

Q44

Q45

Q46

Q47

Q48

Q49

Q50

Q51

Q52

Q53

Q54

Q55

Q56

Q57

Q58

Q59

Q60

Q61

Q62

Q63

AK39

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AN10

AK13

AH11

AK10

BA10

AW10

BA4

AW4

AY10

AY9

AW5

AY5

AV4

AR5

AK4

AK3

AK5

AJ9

AJ8

AT4

AJ5

AJ3

U601E

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

CALISTOGA_Q13

M_B_

M_B_

M_B_

M_B_

M_B_

M_B_

M_B_

M_B_

M_B_

M_B_

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

M_B_D

2

M_B_BS#0

AT24

SB_BS_0

SB_BS_1

SB_BS_2

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SYSTEM MEMORY B

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

DDR

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

7

AV23

AY28

AR24

AK36

AR38

AT36

BA31

AL17

AH8

BA5

AN4

AM39

AT39

AU35

AR29

AR16

AR10

AR7

AN5

AM40

AU39

AT35

AP29

AP16

AT10

AT7

AP5

AY23

AW24

AY24

AR28

AT27

AT28

AU27

AV28

AV27

AW27

AV24

BA27

AY27

AR23

AU23

AK16

AK18

AR27

M_B_BS#1

M_B_BS#2

M_B_C

AS#

M_B_DM

0

M_B_DM

1

M_B_DM

2

M_B_DM

3

M_B_DM

4

M_B_DM

5

M_B_DM

6

M_B_DM

7

M_B_D

QS0

M_B_D

QS1

M_B_D

QS2

M_B_D

QS3

M_B_D

QS4

M_B_D

QS5

M_B_D

QS6

M_B_D

QS7

M_B_D

QS#0

M_B_D

QS#1

M_B_D

QS#2

M_B_D

QS#3

M_B_D

QS#4

M_B_D

QS#5

M_B_D

QS#6

M_B_D

QS#7

M_B_A

0

M_B_A

1

M_B_A

2

M_B_A

3

M_B_A

4

M_B_A

5

M_B_A

6

M_B_A

7

M_B_A

8

M_B_A

9

M_B_A1

0

M_B_A1

1

M_B_A1

2

M_B_A1

3

M_B_R

AS#

M_B_RCVENIN#

M_B_RCVENOUT#

M_B_

WE#

M_B_BS0

M_B_BS1

M_B_BS2

M_B_C

T8

1

T8

1

M_B_DM[0..7]

M_B_DQS[0..7]

M_B_DQS#[0..7]

M_B_A[0..13]

M_B_DQ[0..63]

15,16

15,16

15,16

AS#

15,16

M_B_R

AS#

03

04

M_B_WE#15,16

15

15

15

15,16

15

1

15,16

A A

<Variant Name>

Title :

Calistoga DDR2 (3)

ASUSTeK COMPUTER INC

SizeProject Name

A3

5

4

3

2

Date:

T12F

Wednesday, April 26, 2006

Engineer:

Leon and George

Sheet

1

Rev

8

1.0

61

of

5

4,5,7,11,12,13,14,15,19,20,21,22,23,25,26,27,28,29,30,31,32,33,37,39,40,42,43,50,52,60,61

www.bufanxiu.com

Layout Note:

Place filter components

+1.5VS

close to GMCH

L90

2

120Ohm/10

D D

L90

1

30Ohm/10

L903

80Ohm/10

L90

4

30Ohm/10

C C

L90

6

30Ohm/10

L90

7

120Ohm/10

L90

8

120Ohm/10

B B

+2.5VS

VCC_SYNC

Pin H22

12

C932

0.1UF/10V

R905

10Ohm

A A

70 mA

L90

9

120Ohm/10

Layout Note:

Caps should be on Top layer

21

12

0Mhz

+

CE902

150UF/4V

@

GND

21

12

0Mhz

C904

0.1UF/10V

GND

0Mhz

21

12

+

CE903

470UF/2.5V

GND

21

12

0Mhz

+

CE904

470UF/2.5V

GND

21

12

0Mhz

+

CE905

470UF/2.5V

GND

21

12

0Mhz

C923

22UF/6.3V

GND

21

12

C927

0Mhz

22UF/6.3V

GND

VCCA_LVDS

Pin A38 10 mA

12

0.01UF/25V

GND GNDGND

+VCCP_GMCH_R

12

VCCA_CRTDAC

Pin E21 F21

21

12

0Mhz

C901

0.022UF/25V

GND GND

5

12

C902

10UF/10V

GND

12

C905

10UF/10V

GND

12

C909

0.1UF/10V

GND

12

@

C912

0.1UF/10V

GND

12

@

C918

0.1UF/10V

GND

12

C924

0.1UF/10V

GND

12

C928

0.1UF/10V

GND

C933

GND GND

3

12

C946

0.1UF/10V

GND

VCCA_3GPLL

+1.5VS_VCCAUX

VCCAUX

1900 mA

+1.5VS_DPLLA

VCCA_DPLLA

50 mA

+1.5VS_DPLLB

VCCA_DPLLB

50 mA

+1.5VS_HPLL

VCCA_HPLL

45 mA

VCCA_MPLL

45 mA

12

C934

0.1UF/10V

D902

BAT5

4C

+1.5VS_PCIE

VCC3G

12

C903

10UF/10V

+1.5VS_3GP

LL

1500

+1.5VS

_MPLL

Layout Note:

0.1uF caps in 1.5VS_xPLL

need to be located as

edge caps within 200 mils.

VCCA_3GBG

Pin G41 2 mA

12

C935

0.1UF/10V

GND

1

+VCCP_GMCH

2

+2.5VS_CRTDAC

Layout Note:

These Caps should

be within 250 mils of

edge of GMCH

+VCCP

+VCCP

mA

+1.5VS

VCCD_LVDS 20 mA

Pin A28 B28 C28

12

C910

0.1UF/10V

GND

+1.5VS

VCCD_TVDAC

Pin D21

12

C913

0.022UF/25V

GND

+1.5VS

VCCD_QTVDAC

H19 C28

12

C919

0.022UF/25V

GND

Layout Note:

These Caps should be within

250 mils of edge of GMCH

VCCTX_LVDS 60 mA

Pin A30 B30 C30

12

C936

0.1UF/10V

4

GMCH VCORE

+1.

05VS

JP902

3500

mA

1 2

SHORT_PIN

@

JP901

1 2

SHORT_PIN

@

12

C911

10UF/10V

GND

12

C914

0.1UF/10V

GND

24 mA

12

C920

0.1UF/10V

GND

Layout Note:

These 0.1uF caps should

be placed within 200 mils

of edge

12

C937

4.7UF/10V

+3VS

VCC_HV 40 mA

Pin A23 B23 B25

12

C944

10UF/10V

GND

4

+VCCP_GMCH

+2.5VS_CRTDAC

GND

+3VS_TVDA

+3VS_TVDA

+3VS_TVDACC

+1.5VS_VCCAUX

12

C945

0.1UF/10V

GND

+1.5VS_3GP

+2.5VS

+1.5VS_DPLLA

+1.5VS_DPLLB

+1.5VS_HPLL

+2.5VS

+1.5VS

_MPLL

+3VS_TVB

+1.5VS

+1.5VS

+1.5VS

+3VS

+1.5VS

+1.5VS_PCIE

GND

G

CA

CB

+2.5VS

GND

LL

GND

AJ41

AB41

AC33

AK31

AF31

AE31

AC31

AL30

AK30

AJ30

AH30

AG30

AF30

AE30

AD30

AC30

AG29

AF29

AE29

AD29

AC29

AG28

AF28

AE28

AH22

AJ21

AH21

AJ20

AH20

AH19

AH15

AH14

AG14

AF14

AE14

AF13

AE13

AF12

AE12

AD12

H22

C30

B30

A30

Y41

V41

R41

N41

G41

H41

F21

E21

G21

B26

C39

AF1

A38

B39

AF2

H20

G20

E19

F19

C20

D20

E20

F20

AH1

AH2

A28

B28

C28

D21

A23

B23

B25

H19

P19

P16

P15

Y14

L41

U601H

VCCSYNC

VCC_TXLVDS0

VCC_TXLVDS1

VCC_TXLVDS2

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GPLL

VCCA_3GBG

VSSA_3GBG

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_LVDS

VSSA_LVDS

VCCA_MPLL

VCCA_TVBG

VSSA_TVBG

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCD_HMPLL0

VCCD_HMPLL1

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCD_TVDAC

VCC_HV0

VCC_HV1

VCC_HV2

VCCD_QTVDAC

VCCAUX0

VCCAUX1

VCCAUX2

VCCAUX3

VCCAUX4

VCCAUX5

VCCAUX6

VCCAUX7

VCCAUX8

VCCAUX9

VCCAUX10

VCCAUX11

VCCAUX12

VCCAUX13

VCCAUX14

VCCAUX15

VCCAUX16

VCCAUX17

VCCAUX18

VCCAUX19

VCCAUX20

VCCAUX21

VCCAUX22

VCCAUX23