5

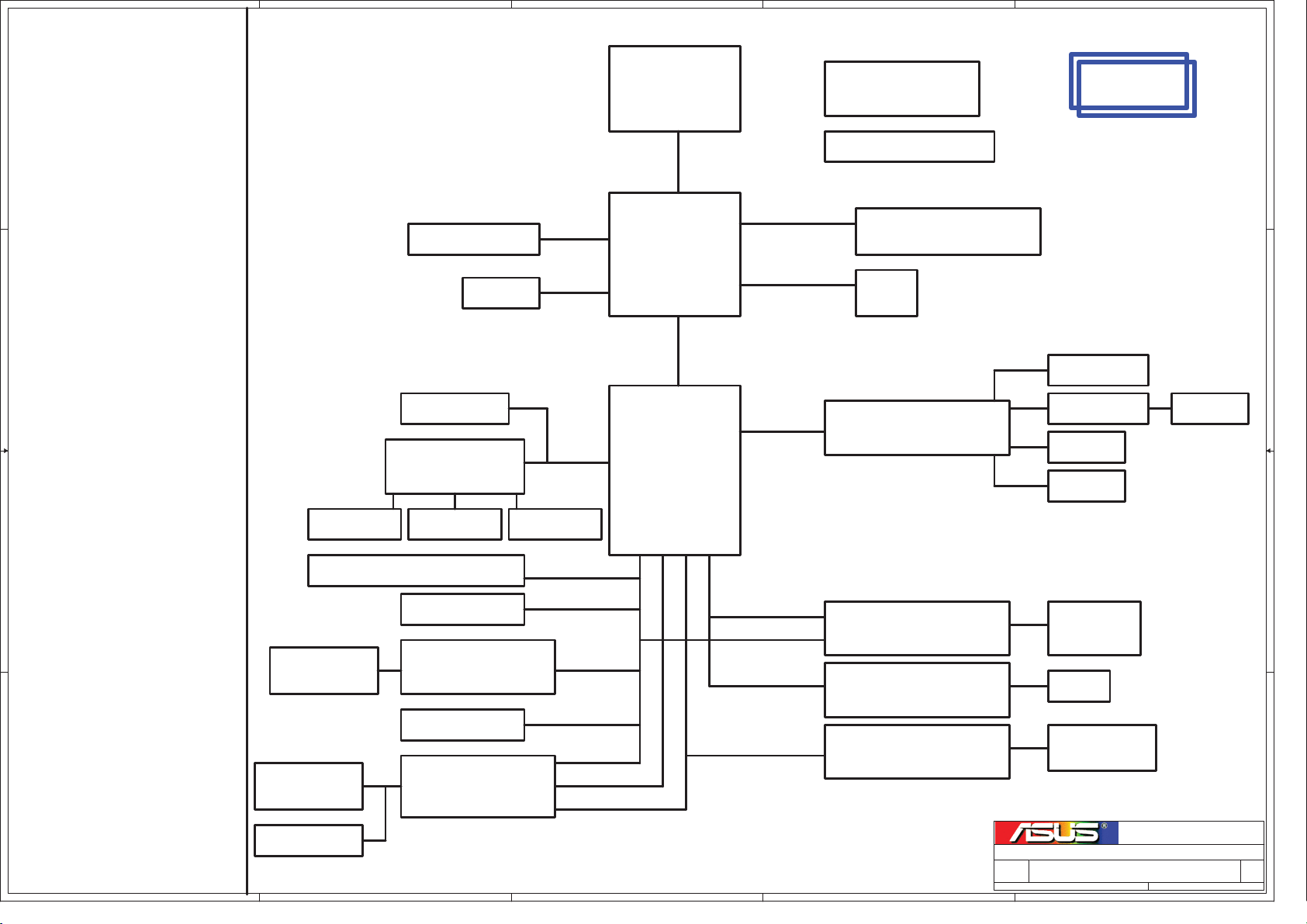

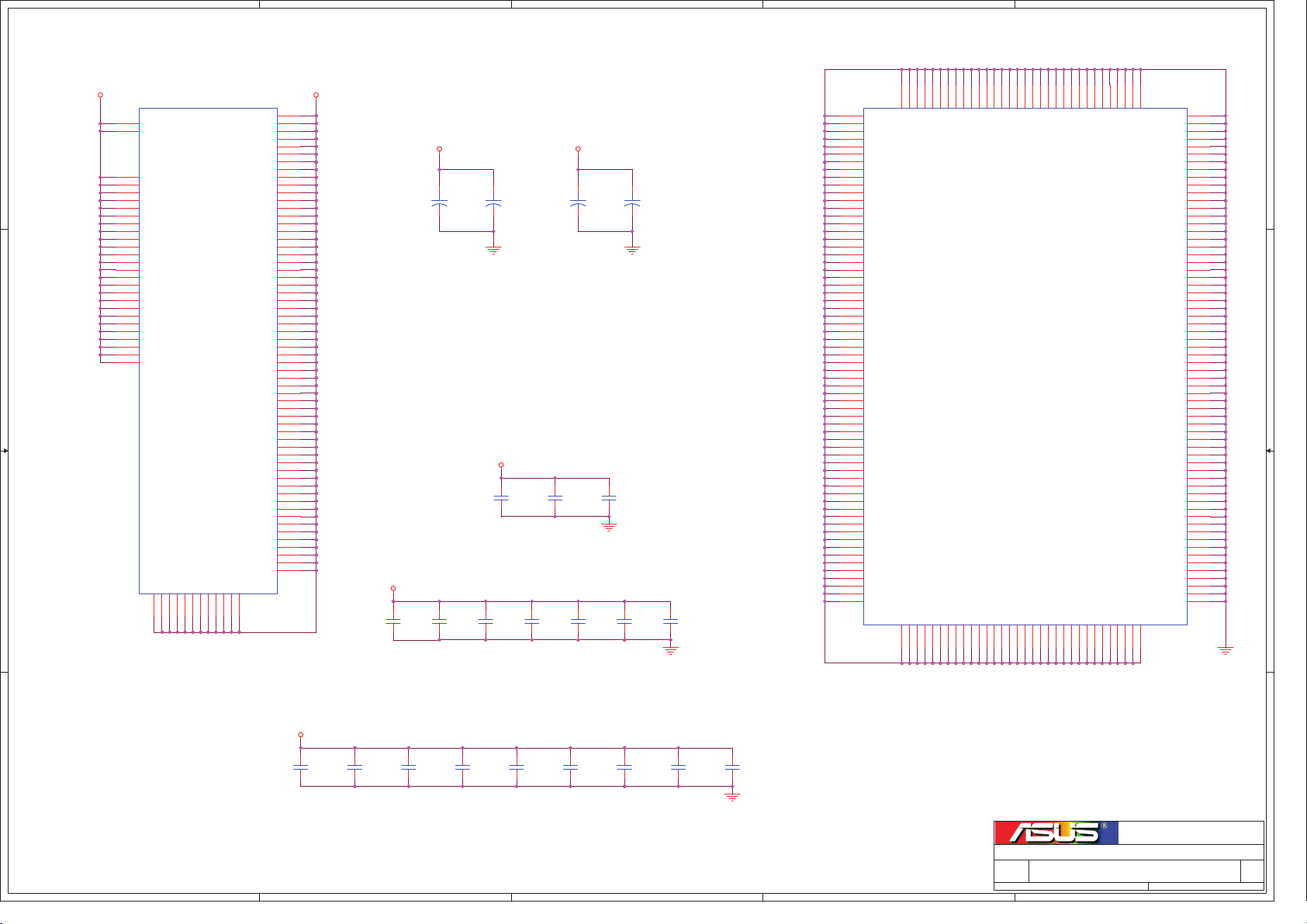

PCIE

FSB400MHz

x4 DMI

AZALIA

PCIE_2

PCIE_3

USB_P5

400MHz

Channel A

USB_P4

USB_P7

USB_P1/2/3

IDE Slave

LPC

RGB

LVDS

USB_P0

SATA1

IDE Master

Channel B

400MHz

USB_P6

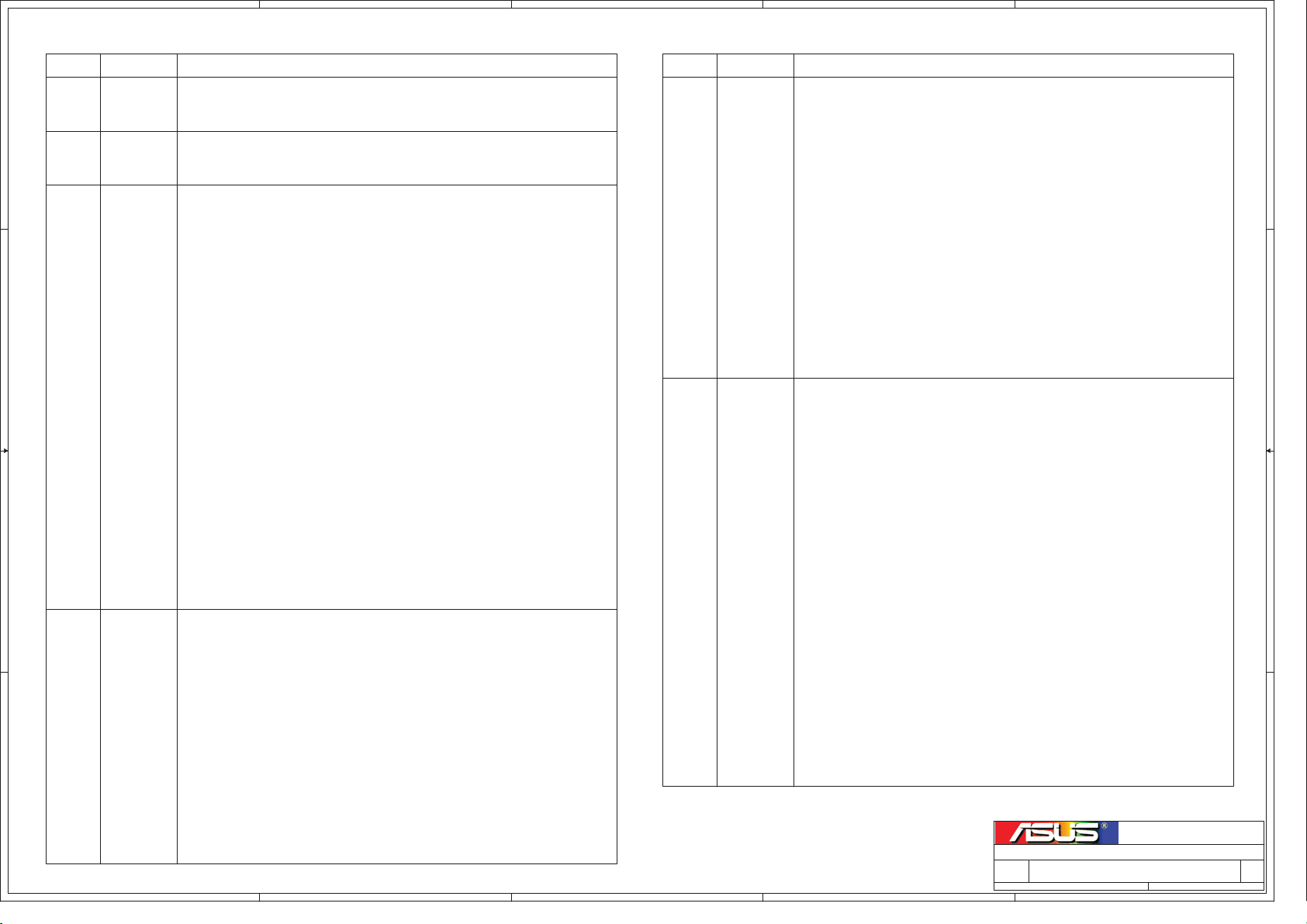

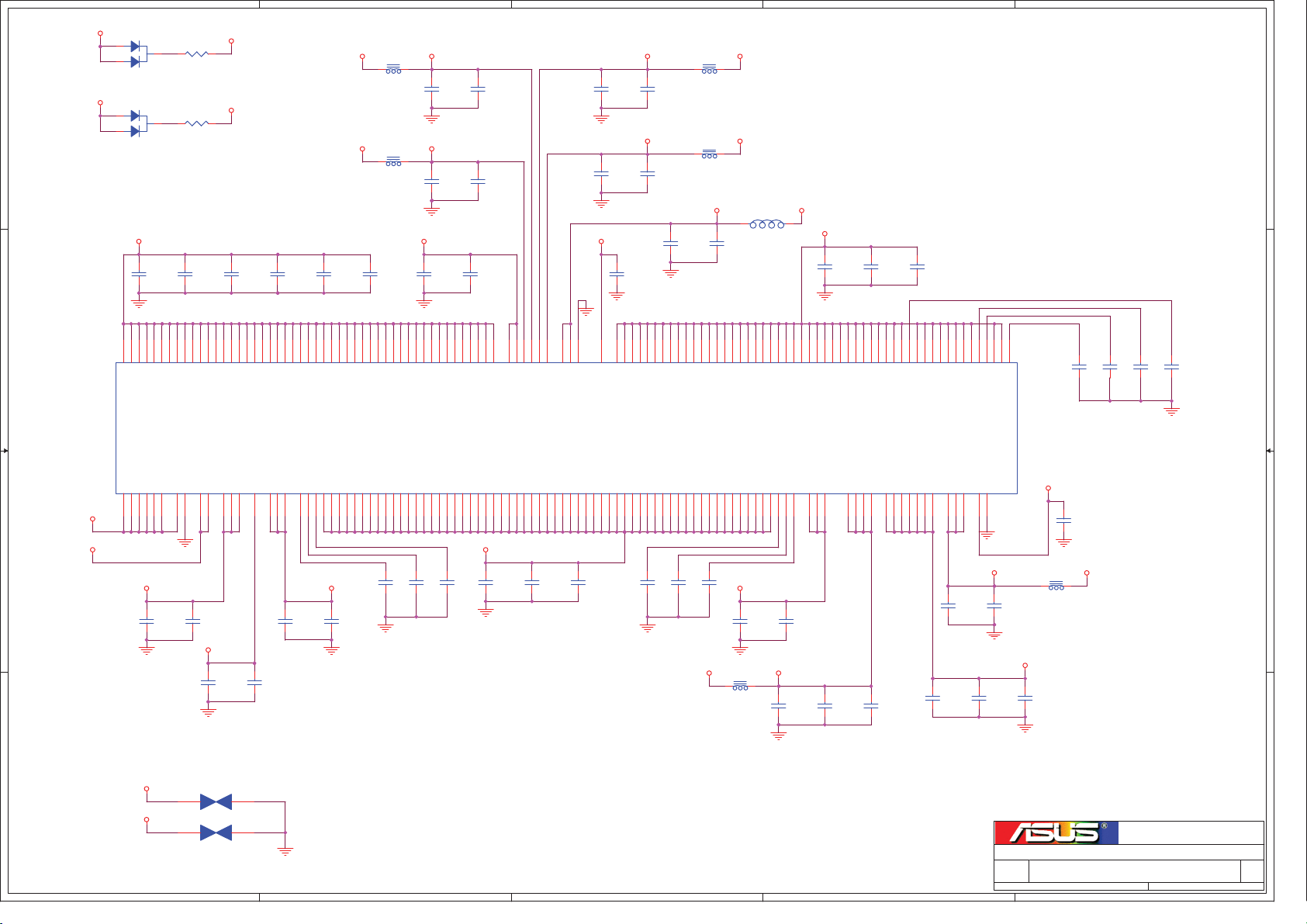

01_Block Diagram

02_System Setting

03_Power Sequence

04_EC Pin Define

05_History

D D

06_*

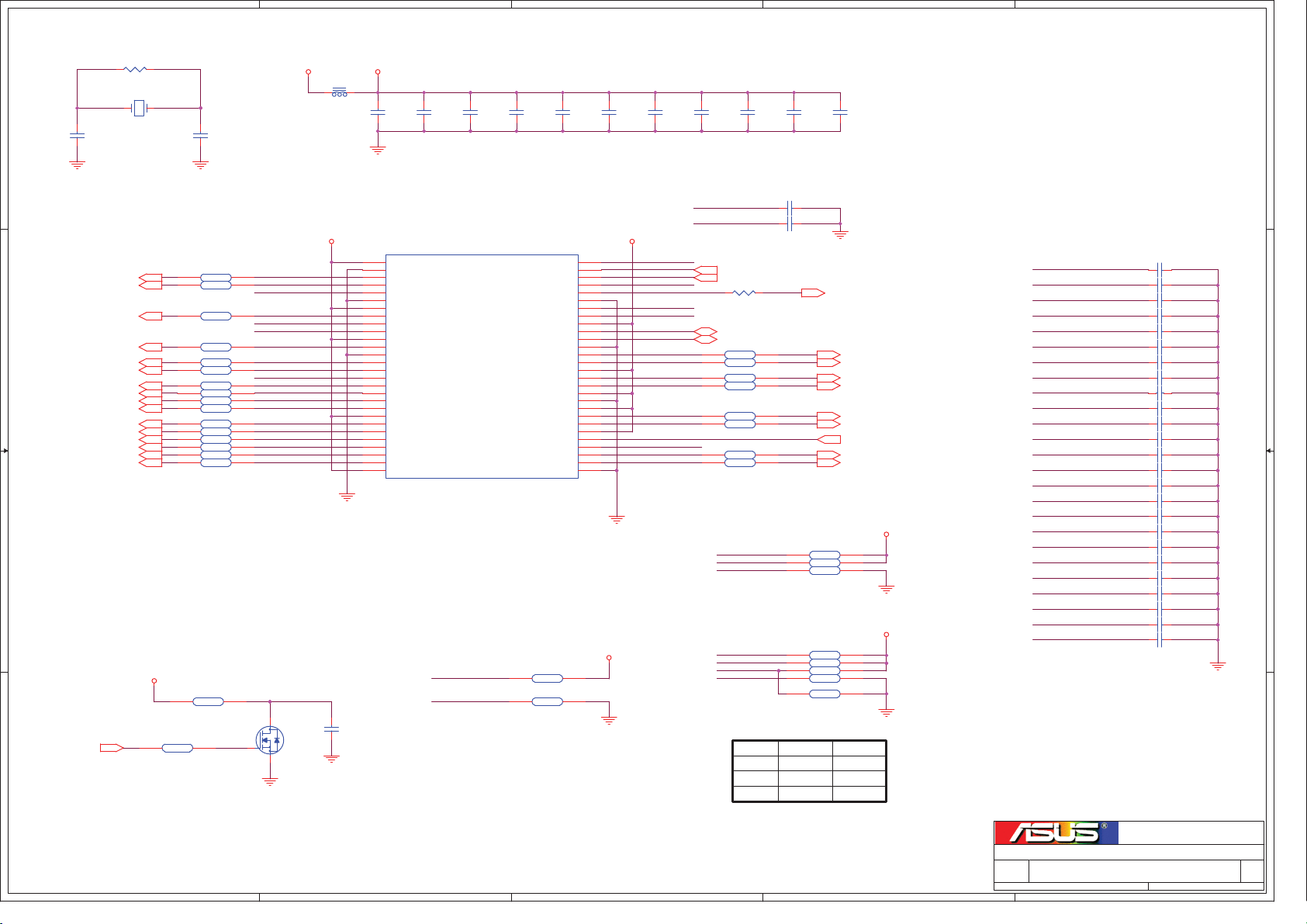

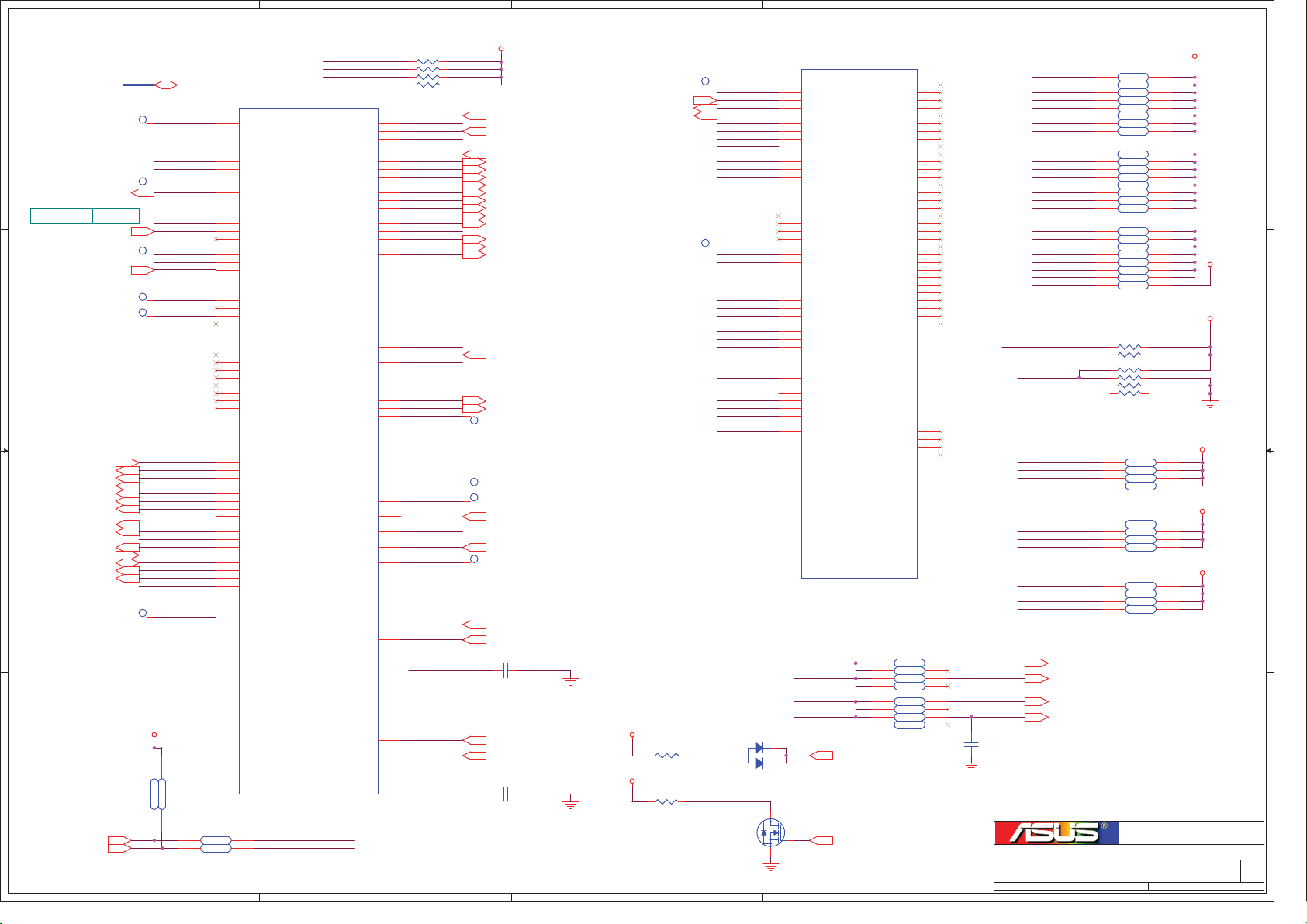

07_Clock Gen_ICS9LPR426

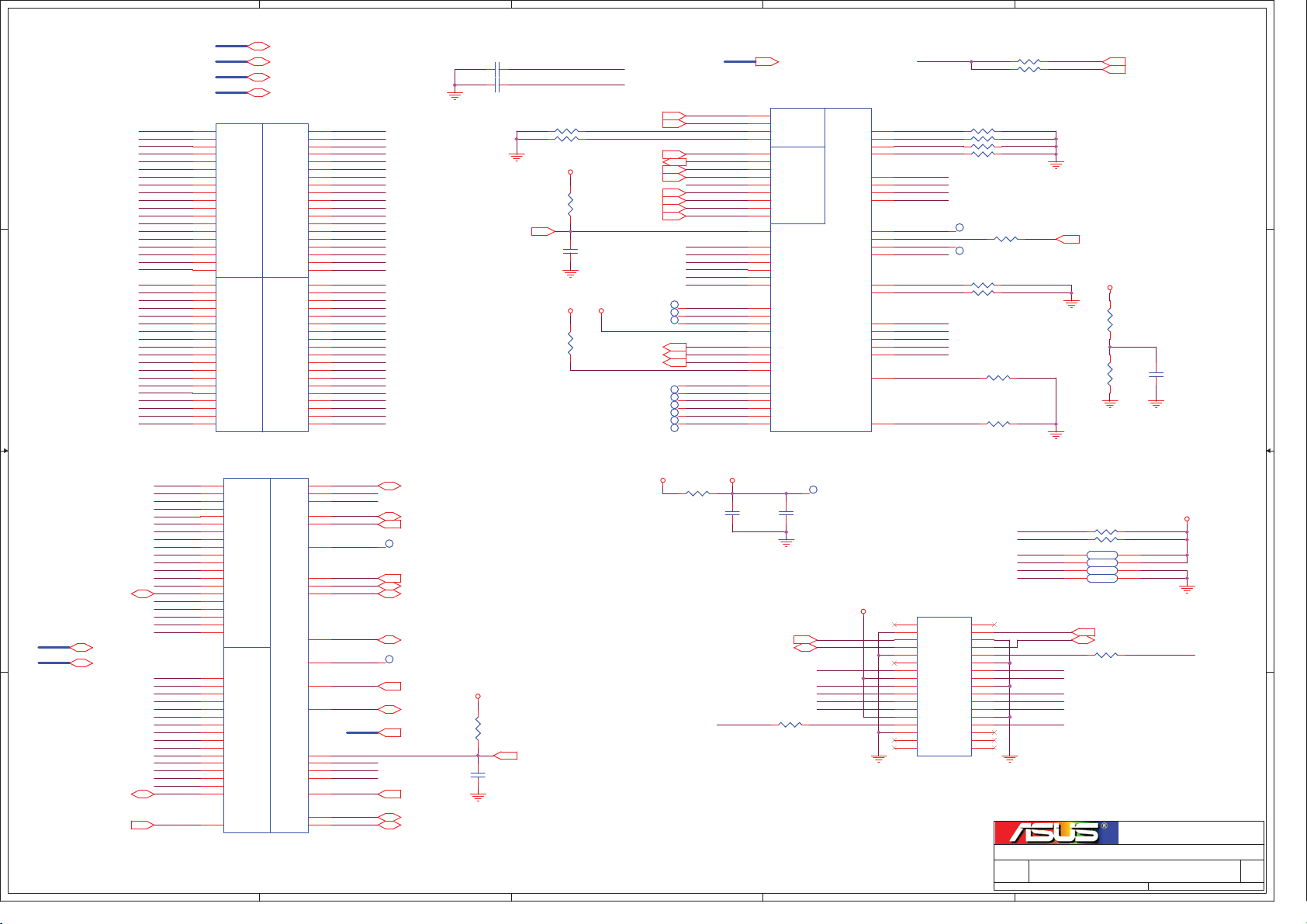

08_Dothan_HOST

09_Dothan_PWR_GND

10_910GML_HOST_DMI

11_910GML_DRAM

12_910GML_VGA_LVDS_TV

13_910GML_PWR

14_910GML_GND

15_ICH6-M_Azalia_GPIO_PCI_LAN

16_ICH6-M_USB_PCIE_DMI_IDE_SATA

17_ICH6-M_PWR_GND

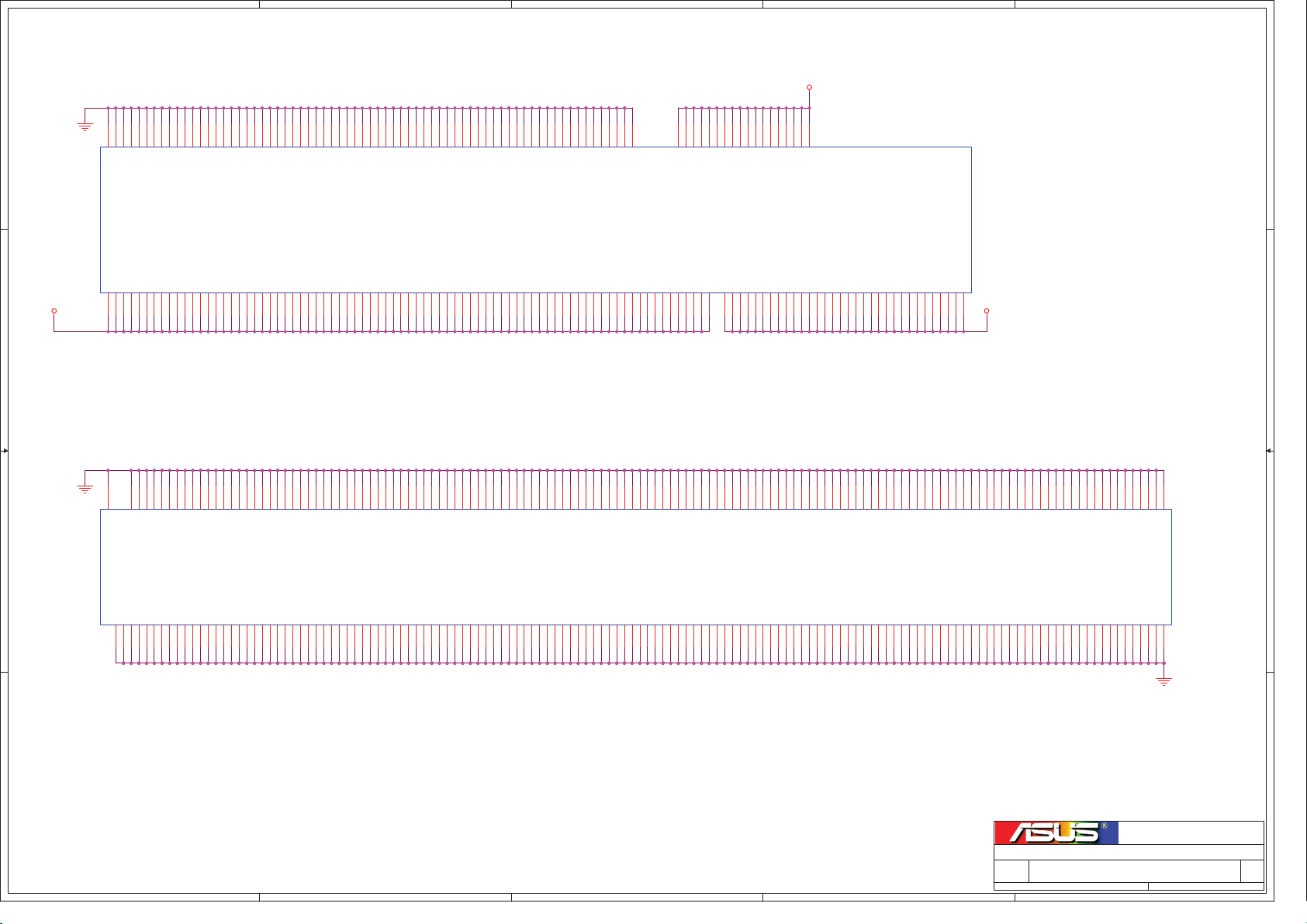

18_DDR2 SODIMM

19_DDR2_Termination

20_Onboard VGA

C C

21_LCD Conn

22_Minicard

23_LAN_Atheros L2

24_RJ45/BlueTooth

25_Onboard Flash

26_Flash Conn

27_USB Port

28_Card Reader_ENE UB6225P

29_Camera Conn

30_Codec_ALC662

31_Audio_AMP_Jack

32_EC_ENE KB3310

33_Switch_SPI ROM_Debug Conn

34_KB_Touch Pad

B B

35_Thermal Sensor_FAN

36_LED_THERMTRIP

37_Discharge

38_PWR Jack

39_Srew Hole

40_EMI

41_POWER FLOW

42_CHARGER

43_VCORE(7A)

44_POWER_3V_5V_VTT_DDR

45_POWER_3VA_3VSB

46_POWER_1.05V_1.5V_2.5V

47_POWER_1.8V_DUAL_5VSB

A A

SD/MMC

Card Reader

NAND Flash

BlueTooth

Card

HD

5

http://laptop-motherboard-schematic.blogspot.com/

4

8.9 AUO LCD

CRT

Debug Conn

EC

ENE KBC3310

Internal KBSPI ROM Touch Pad

AW-BT253

USB Port *3

Card Reader

ENE UB6225P

1.3M Camera

Flash Conn

4

3

CPU

Celeron-M ULV

(Dothan)

FCBGA479

NORTH

BRIDGE

910GML

SOUTH

BRIDGE

ICH6-M

3

2

CLOCK GEN

ICS9LPR426

THERMAL CONTROL

SODIMM 200P

NC

AZALIA CODEC

Realtek ALC662

MINICARD

LAN

Atheros L2

Flash Controller

PHISON

2

1

P900

R1.2G

LINE OUT

AUDIO AMP

EXT MIC

INT MIC

WLAN

AW-GE780

RJ-45

Onboard

NAND Flash

P900_R1.1G_W/O_FLASH

Title :

ASUSTek Computer INC.

Size Project Name

A3

Date: Sheet

P900

Engineer:

1

Speaker

Block Diagram

Tiansen_Wu

147Wednesday, February 27, 2008

of

Rev

1.2G

5

4

3

2

1

D D

C C

B B

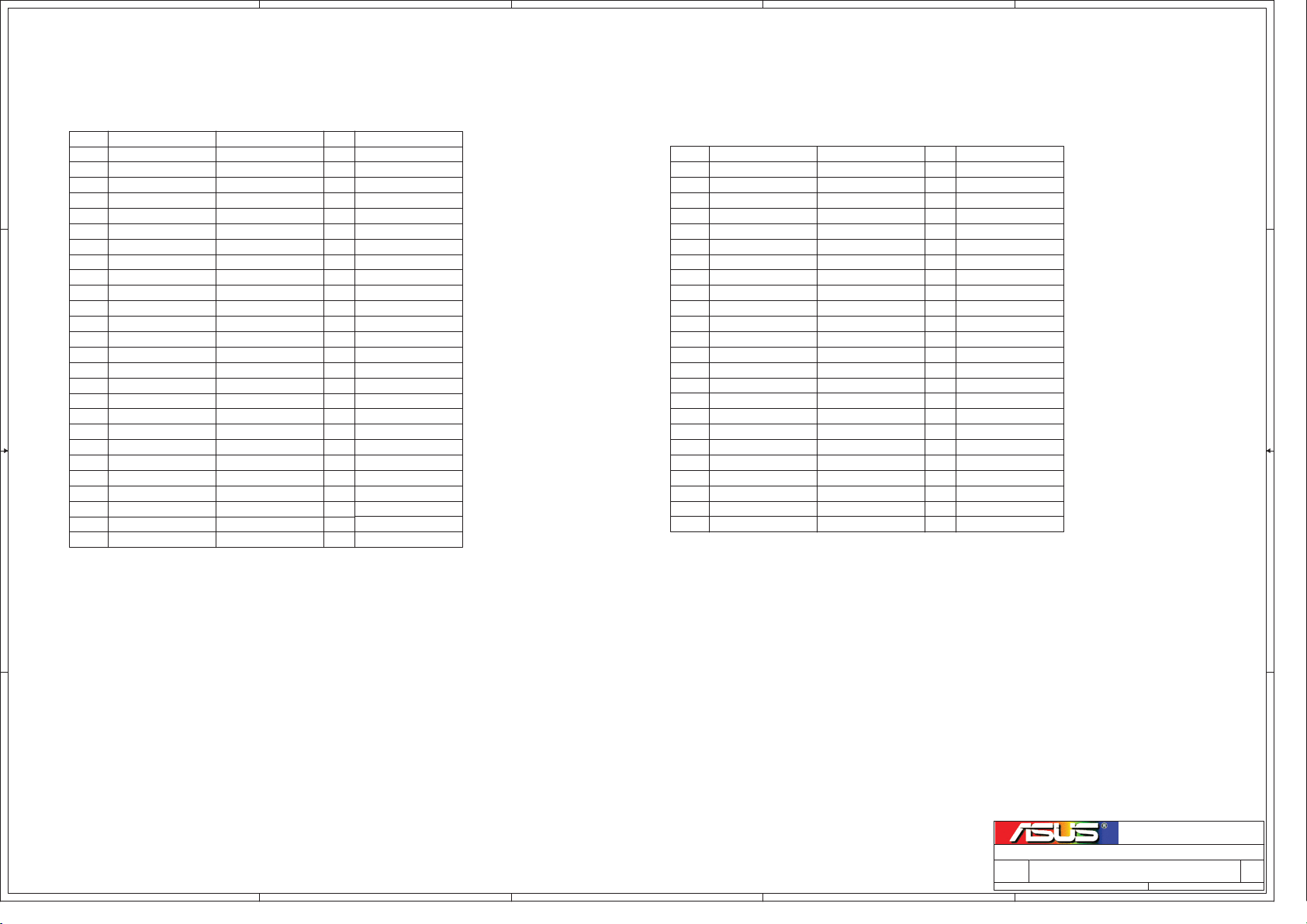

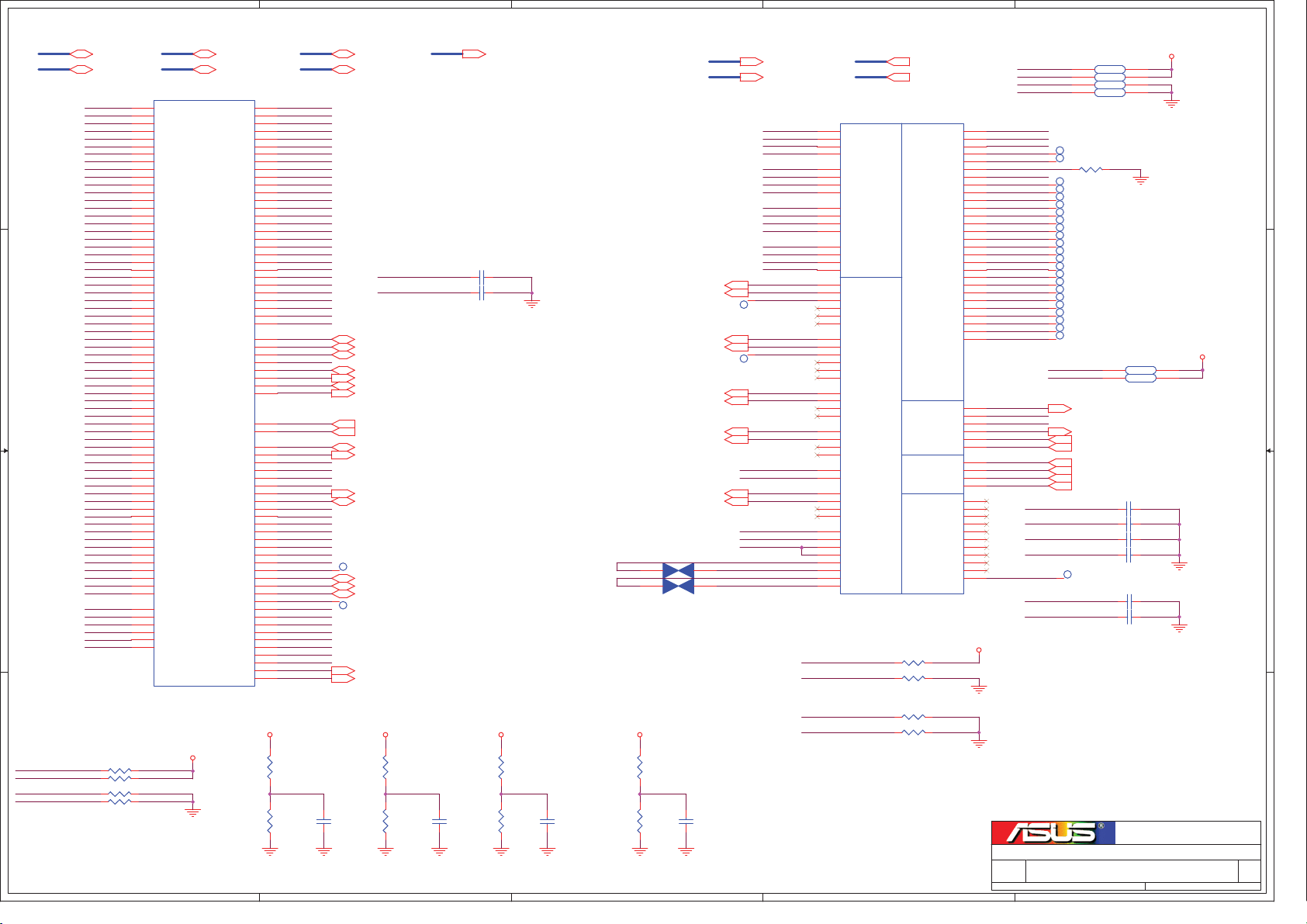

ICH6 GPIO SETTING

Pin

B7

E8

D9

C7

C6

M3

AD19

AE19

R1

C23

D23

W6

M2

R6

C25

C24

D8

F6

AC21

AB21

AD22

AD20

NA

AD21

V3

P5

Pin Name

GPI0/REQ6#

GPI1 / REQ5#

GPI2 / PIRQE#

GPI3 / PIRQF#

GPI4 / PIRQG#

GPI5 / PIRQH#

GPI6 / BMBUSY#

GPI7

GPI8

GPI9/OC4#

GPI10/OC5#

GPI11 / SMBALERT#

GPI12

GPI13

GPI14/OC6#

GPI15 /OC7#

GPO16/GTN6#

GPO17 / GNT5#

GPO18 / STP_PCI#

GPO19

GPO20 / STP_CPU#

GPO21

GPIO22

GPO23

GPIO25

Connect to

10K Pull +3V

10K Pull +3V

10K Pull +3V

10K Pull +3V

10K Pull +3V

NB BMBUSY#

NC

EC KBC_SCI#

10K Pull +3V

10K Pull +3V

S_SMBALERT#

NC

EC EXTSMI#

10K Pull +3V

10K Pull +3V

NC

NC

Clock GEN STP_PCI#

WLAN_LED#

STP_CPU#

CAMERA_EN

NC

SPEAKER_EN#

MINICARD_EN#GPIO24

WLAN_ON#

Type

Input/Output Set

I

fixed as Input only

fixed as Input only

I

fixed as Input only

I

fixed as Input only

I

fixed as Input only

I

fixed as Input only

I

Input

GPI

fixed as Input only

fixed as Input only

GPI

Input PM_VCOREL2

I

I

Input

Input

I

fixed as Input only

GPI

fixed as Input only

GPI

I Input

Input

I

O

Output

O

Output

Output

O

GPO

fixed as Output only

O

Output

GPO

fixed as Output only

NA

NA

GPO

fixed as Output only

Output

I/O

I/O

Output

Pin

AF17

Pin Name

GPI26/SATA0GP

R3

GPIO28

T3

GPI29 / SATA1GP

AE18

GPI30 / SATA2GP

AF18

AG18

GPI31 / SATA3GP

AF19

GPIO32 / CLKRUN#

AF20

GPIO33

AC18 Output

GPIO34

GPIO35

NA

NA

GPIO36

GPIO37

NA

GPIO38

NA

NA

GPIO39

GPI40 / REQ4#

F7

GPI41 / LDRQ1#

P4

NA

GPIO42

NA

GPIO43

GPIO44

NA

NA

GPIO45

NA

GPIO46

NA

GPIO47

E7

GPO48 /GNT4#

GPO49 / CPUPWRGD

AC25

Connect to

NC

CARD_READER_EN#

NC

PCBVER0

NC

PCBVER1

10K Pull +3V

PM_VCOREL1

Type

GPII

I/OGPIO27

I/O

GPI

GPI

GPI

I/O

I/O

Input/Output Set

(GPI)Input

Output

Output

(GPI)Input

(GPI)Input10K Pull +3V

(GPI)Input

Input

Output

I/O

NA

NA

NA

NA

NA

10K Pull +3V

NC

NA

NA

NA

NA

NA

NC Output

CPU Power Ok

NA

NA

NA

NA

NA

I

I

NA

NA

NA

NA

NA

NA

O

O

NA

NA

NA

NA

NA

Input

Input

NA

NANA

NA

NA

NA

NA

Output

A A

P900_R1.1G_W/O_FLASH

1

System Setting

Tiansen_Wu

247Wednesday, February 27, 2008

of

Rev

1.2G

Title :

ASUSTek Computer INC.

Size Project Name

A3

5

http://laptop-motherboard-schematic.blogspot.com/

4

3

2

Date: Sheet

P900

Engineer:

5

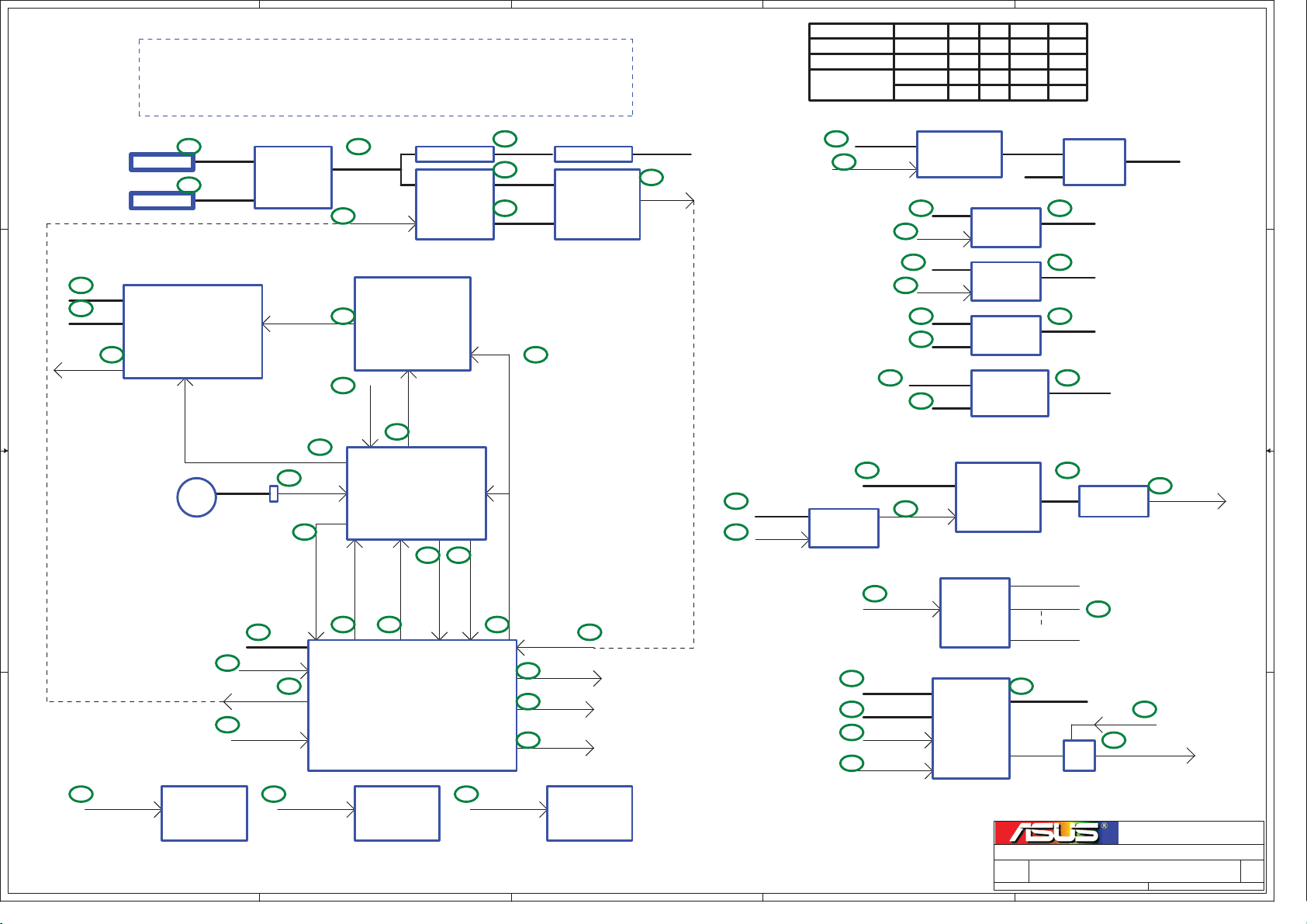

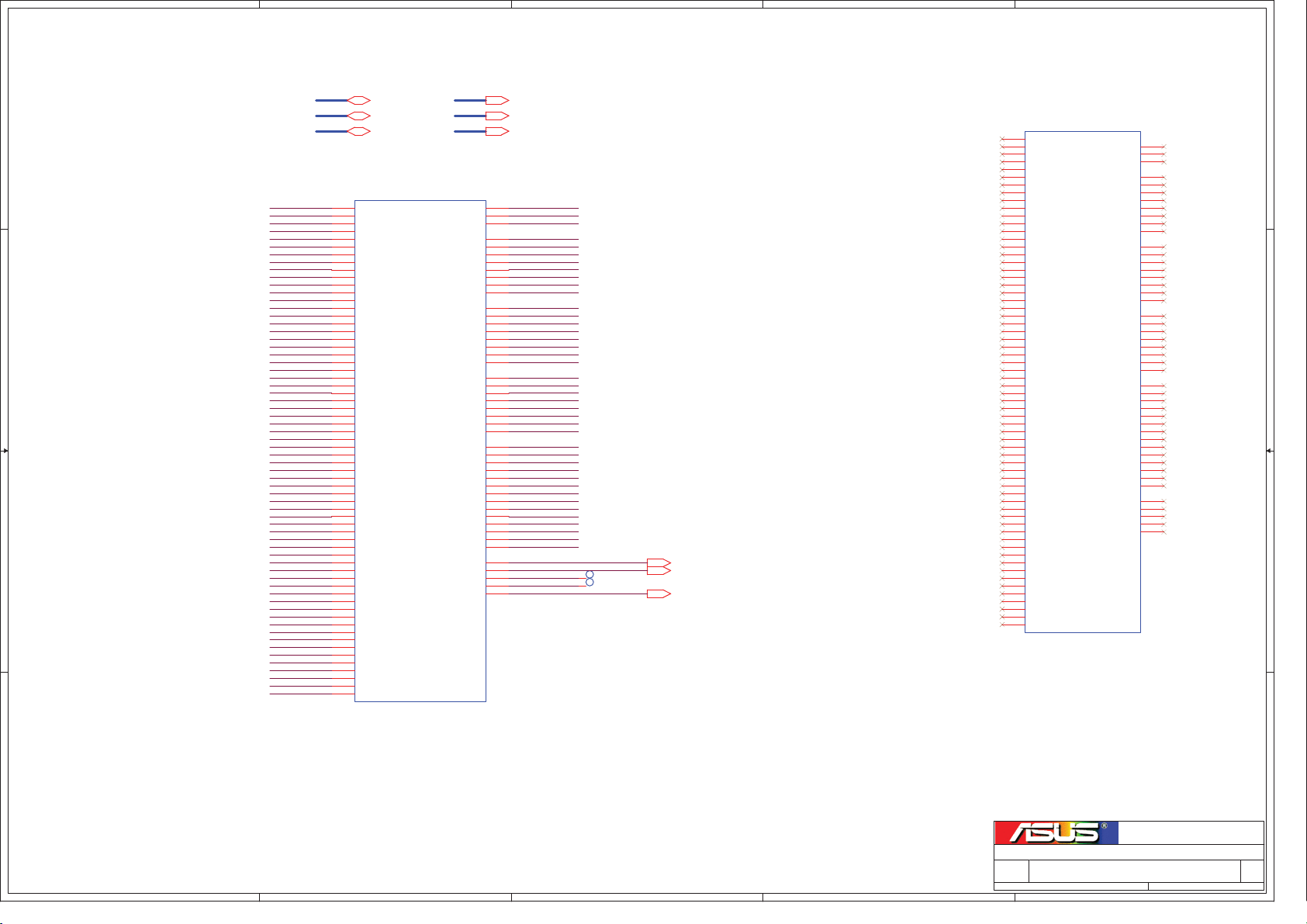

*This sequence is for Battery Plug-in and no Adapter,

if Adapter Plug-in,the sequence change to:

A/D_DOCK_IN--->AC_BAT_SYS--->+3VA--->VSUS_ON--->+3VSB & +5VSB

--->VSUS_GD--->PM_REMRST#--->PWR_SW#--->PM_PWRBTN--->PM_SUSC#--->PM_SUSB#

D D

2

Adapter

Battery

21

+VCCP

24

VCORE

C C

VID[0..5]

23

A/D_DOCK_IN

2

BAT_CON

DOTHAN CPU

MAX8724ETI

H_CPURST#

29

25

(logic AND of

PWROK and

VRM_PWROK)

+

BATT

H_PWRGD

VCC_RTC

1

27

RTCRST#

28

B B

PCI_RST#

4

+3VA

PWR_SW#

5

VSUS_ON

25

A A

28

PCI_RST#

5

IDE FLASH

CONTROLLOR

SM223

6

VRM_PWRGD

28

PLT_RST#

http://laptop-motherboard-schematic.blogspot.com/

3

AC_BAT_SYS

VSUS_ON

6

VRM_PWRGD

PM_RSMRST#

9

EC KB3110

LAN

ATTANSIC L2

4

NB 910GM

PLT_RST#

28

SB ICH6

11

PM_PWRBTN#

10

4

MP2307DN

RT8020A

12

PM_SUSC#

PM_SUSB#

28

4

7

7

PM_PWROK

PM_PWROK

26

PLT_RST#

+5VA

APL5315BI

+3VSB

2*PMBS3904

+2N7002

+5VSB

26

(PLT_RST# is 34--41 RTCC LK( =1 mS )

later than PM_PWROK,H_ CPU RST# i s

1mS after PLT_RST#)

(160mS after VRM_PWRGD)

VSUS_GD

13

14

19

(55mS after SUSB_ON)

8

SUSC_ON

SUSB_ON

CPU_VRON

MINICARD

3

+3VA

8

VSUS_GD

3

7

AC_BAT_SYS

19

CPU_VRON

Only Battery

Adapter In

AC_BAT_SYS

3

SUSC_ON

13

3

2N7002

22

3

AC_BAT_SYS

14

23

CPU_VRON

19

2

Signal

VSUS_ON

SUSC_ON

7

14

7

14

15

15

AC_BAT_SYS

3

15

AC_BAT_SYS

20

P_VCC_EN_10

VCCP_OK

+5V

VID[0..5]

2

S0/S1

H

HSUSB_ON

H

MP2307DN

+5VSB

SUSB_ON

+3VSB

SUSB_ON

+3V

+5V

+5V

MP2307DN

CYS28442

ISL6218CRZ

S3

S4/S5LPower

VSBVSUS_ON H LH

H

L

VSB

H

Main

L

DUALH

+1.8V_DUAL

RT9173

+5V

15

+5V

SI4835BDY

15

+3V

SI4835BDY

16

+2.5V

SI4835BDY

16

MP2307DN

+1.5V

21

+VCCP

DELAY

CLK_PCI_EC

CLK_PCIE_ICH

CLK_BCLK_CPU

24

VCORE

VCORE_PG

P900_R1.1G_W/O_FLASH

ASUSTek Computer INC.

Size Project Name

A3

Date: Sheet

AND

P900

23

VCCP_OK

25

Engineer:

1

VTT_DDR

22

22

VRM_PWRGD

Title :

1

VCCP_OK

Power Sequence

Tiansen_Wu

347Wednesday, February 27, 2008

of

Rev

1.2G

5

4

3

2

1

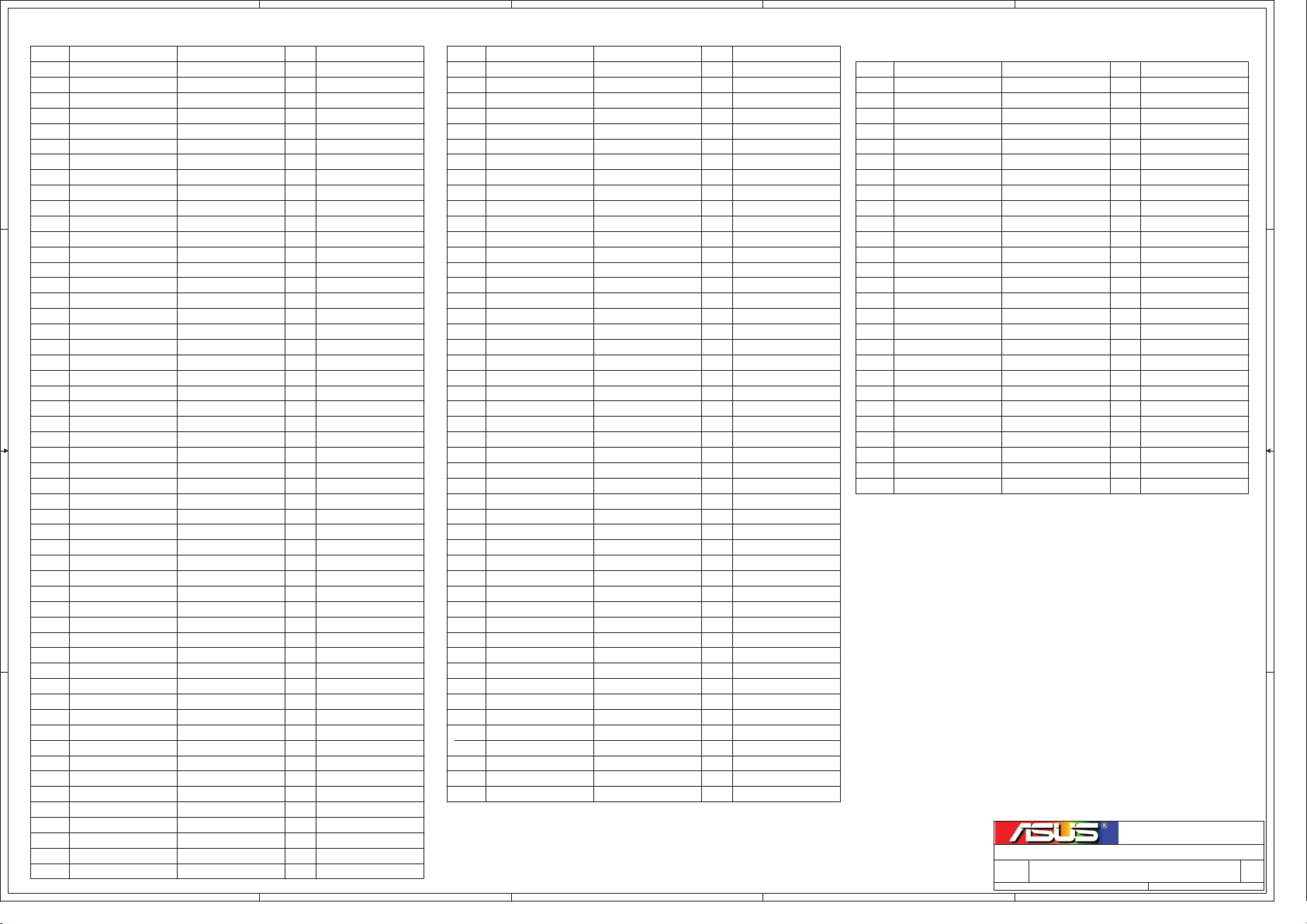

EC KB3310 GPIO SETTING

Type

Pin No.

1

2

6

13

D D

14

15

16

17

18

19

20

21

23

25

26

27

28

29

C C

30

31

32

34

36

38

39

40

41

42

Pin Name

GA20

KBRST#

GPIO04

PCIRST#

GPIO07

GPIO08

GPIO0A

GPIO0B

GPIO0C

GPIO0D

SCI#

PWM1

PWM2

GPIO11

FANPWM1

FANPWM2

FANFB1

FANFB2

GPIO16

GPIO17

GPIO18

GPIO19

GPIO1A

CLKRUN#

KSO0

KSO1

KSO2

KSO3

43

KSO5

44

45

KSO6

KSO7

46

47

B B

KSO8

KSO9

48

KSO10

KSO11

50

KSO12

51

KSO13

52

KSO14

53

54

KSO15

KSI0

55

KSI1

56

KSI2

57

KSI3

58

59

KSI4

60

KSI5

61

A A

KSI6

62

KSI7

63

AD0

64

AD1

65

AD2

AD3

66

GPO3C

68

5

Signal Name

A20GATE

RC_IN#

EMAIL_SW#

PCI_RST#

BAT_EXT

EXTSMI#

LID_EC# P

NC

NC

DISTP_SW#

BL_PWM_DA

BAT_CRITICAL

PM_PWRBTN#

FAN0_PWM

FAN1_PWM

FAN0_TACH

FAN1_TACH

E51_TX

E51_RX

PWR_SW#

MAIL_LED# CAP_LED#

NUM_LED#

N.C

KSO0

KSO1

KSO2

KSO3

KSO4

KSO5

KSO6

KSO7

KSO8

KSO9

KSO1049

KSO11

KSO12

KSO13

KSO14

KSO15

KSI0

KSI1

KSI2

KSI3

KSI4

KSI5

KSI6

KSI7

BAT_ICHG

BAT_CONFIG

BAT_SENT

BAT_TS

DOC

NOTE

Type

A20GATE

O

O

KBRST#

I

EMAIL_SW# , *

I

PCI Reset

Reserved

O

EXTSMI#, 10K Pull +3VSUS

O

I

LID_EC#, *

LCD chip select

O

I/O

LCD Data

Touch Pad Disabled,*

I

KBC_SCI#, 10K Pull +3VSUS

O

LCD Light Switch

O

O

LCD clock

OD

Power Button to SB, *

CPU Fan(Unused)

O

VGA Fan(Unused)

O

I

CPU FanTach(Unused)

I

VGA FanTach(Unused)

O

RS232 debug port

O

Reserved

power button, *

I

Mail LED(Unused)

O

EC H/W controls(Unused)

O

Reserved

O

For Keyboard interface

O

For Keyboard interface

O

For Keyboard interface

O

O

For Keyboard interface

O

For Keyboard interface

For Keyboard interface

O

For Keyboard interface

O

O

For Keyboard interface

O

For Keyboard interface

O

For Keyboard interface

O

For Keyboard interface

For Keyboard interface

O

For Keyboard interface

O

O

For Keyboard interface

For Keyboard interface

O

For Keyboard interface

O

For Keyboard interface

I

For Keyboard interface

I

For Keyboard interface

I

I

For Keyboard interface

I

For Keyboard interface

For Keyboard interface

I

I

For Keyboard interface

I

For Keyboard interface

I

Sense Power Loading

sense Battery

I

I

Reserved

I

Reserved

O

Trigger Clock Gen

http://laptop-motherboard-schematic.blogspot.com/

4

Pin No.

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85 Reserved

86

87

88

89

90

91

92

93

95

97

98

99

100

101

102

103

104

105

106

107

108

109

110

112

114

115

116

117

118

121

126

127

Pin Name

GPO3D

GPO3E

GPO3F

GPIO40

GPIO41

GPIO42

GPIO43

SCL1

SDA1

SCL2

SDA2

KSO16

KSO17

PSCLK1

PSDAT1

PSCLK2

PSDAT2

PSCLK3

PSDAT3

GPIO50

GPIO52

GPIO53

GPIO54

GPIO55

GPIO56

GPXOA00

GPXOA01

GPXOA02

GPXOA03

GPXOA04

GPXOA05

GPXOA06

GPXOA07

GPXOA08

GPXOA09

GPX0A10

GPXOA11

GPXID0

GPXID1

GPXID2

GPXID3

GPXID4

GPXID5

GPXID6

GPXID7

GPIO57

SPICLK

GPIO59

Signal Name

LCD_BACKOFF#

CLK_PWRSAVE#

PM_BATLOW#

AC_OK

PM_RSMRST#

N.C

N.C

SMB1_CLK

SMB1_DAT

SMB2_CLK

SMB2_DAT

N.C

N.C

LCD_SCL

LCD_SDA

LCD_CSB

LCD_VSYNC

TP_CLK

TP_DAT

BATSEL_3S

CHG_LED_UP#

PWR_LED_UP

SCRL_LED#

PWR4G_SW#

SPI_MODE#

SUSC_ON

VSUS_ON

CPU_VRONKSO4

SUSB_ON

PWROK

PM_LEVELDOWN#

CHG_EN#

PRECHG

SPI_WP#

OP_SD#

BAT_LEARN

BATSEL_2P#

CPU_LEVELDOWN#

THRO_CPU

SUSB#

SUSC#

CPUPWR_GD

VSUS_GD

BAT_VOLSEL

INTERNET#

SPI_CLK

N.C

3

NOTE

LCD_BACKOFF#

O

Active when BAT_IN=1 and

O

AC_OK=0(Unused)

Battery Low Low

O

I

AC Adaptor Plug in

O

10K Pull GND

Reserved

O

Reserved

O

I/OD

4.7K Pull +3VA_EC

I/OD

4.7K Pull +3VA_EC

10K Pull +3VS

I/OD

10K Pull +3VS

I/OD

Reserved

O

Reserved

O

O

Reserved

Reserved

O

O

O

Reserved

I/OD

10K Pull +3VS

10K Pull +3VS

I/OD

Battery series. Hi:3S,

O

Lo:4S(Unused)

charger LED

O

O

EC H/W controls

EC H/W blinking

O

EC H/W controls

O

*

I

"HW Strap for SPI Flash deExternal

O

Pull Down 100K ohm to GND"

O

O

O

O

O

Reserved

O

Battery charging enabled

O

O

O

Audio OP

O

O

Battery parallel. Hi:1P,

O

Lo:2P~3P

Reserved

O

Active if Batt e r y Temperature

O

is over spec

Pull Down 100K ohm to GND

I

Pull Down 100K ohm to GND

I

10K Pull +3VS

I

Disabled **

I

O

Reserved

*

I

SPI Clock

O

O

Reserved

EC KB3310 Other Pin SETTING

Pin No.

4

5

7

8

9

10

11

12

22

24

33

35

37

67

69

94

96

111

113

119

120

112

123

124

125

128

SERIRQ

LFRAME#

LAD3

LAD2

LAD1

VCC

LAD0

GND

PCICLK

VCCKBC_SCI#

GND

VCC

GND

ECRST#

AVCC

AGND

GND

VCC

VCC

GND

RD#

WR#

XCLKI

XCLKO

V18R

VCC

SPICS#

2

Pin Name

Signal Name

INT_SERIRQ

LPC_FRAME#

LPC_AD3

LPC_AD2

LPC_AD1

+3VA_EC

LPC_AD0

GND

CLK_PCI_EC

+3VA_EC

GND

+3VA_EC

GND

EC_RST#

+3VACC

AGND

GND

+3VA_EC

+3VA_EC

GND

SPI_SO

SPI_SI

32KXCLKI

32KXCLKO

K_V18R

+3VA_EC

SPI_CE#

P900_R1.1G_W/O_FLASH

ASUSTek Computer INC.

Size Project Name

A3

Date: Sheet

P900

NOTE

Type

8.2K Pull +3VS3

I/OD

I

I/O

I/O

I/O

I/O

P

I

P

P

P

P

I

Add 100K ohm to GND

P

P

P

P

P

P

I

O

I

O

Reserved 1uF to GND

P

O

Title :

Engineer:

1

EC Pin Define

Tiansen_Wu

447Wednesday, February 27, 2008

of

Rev

1.2G

5

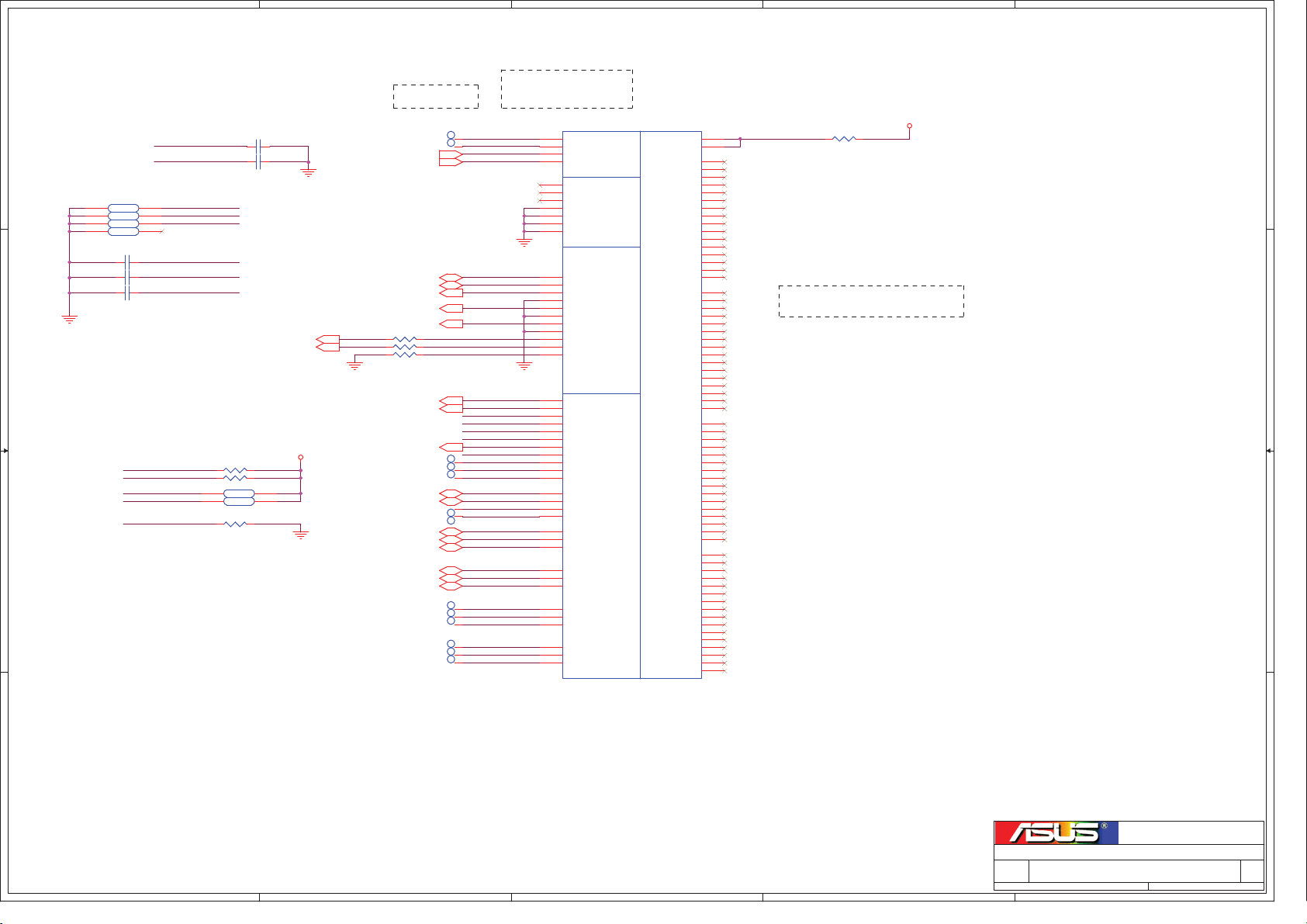

P701 CIRCUIT UPDATED HISTORY

4

3

2

1

Rev

1.0G

D D

1.1G

1.0G

Date

Description Date Description

S701L Schematic 1.0G Beginni ng2007/02/26

~~

2007/03/16

S701L 1.0G Gerber Out

2007/03 / 24 S701L Schematic 1.1G Beginnin g

~~

2007/04/19 S701L 1.1G Gerber Out

2007/04/24

P701(S701L renamed) Schematic 1.0G Beginning

1. PC8054, PR6075 /X to N/A

~~

2. Attansic L2 change to Atheros L2(pin to pin)

3. LC1, LC33 /CAP/X to N/A

4. C87 change to X5R to cost down

5. L1, L2, L3 change to 56 NH, R5, R6 change to 75 Ohm to pass CRT EA m eas ure

6. PR48 change to 22K Ohm, PC35 change to 4700PF to fix no VCORE issue

7. PR6074 change to 4.7K Ohm to fix +3VSB OCP issue

8. Clock Gen CY28442-2 change to ICS9LPR367

C C

9. Phase in Power Level Reduce solution, mark "Taipei0508"

10. Card Reader Socket change to SD Socket 12G25100091E

11. Add System FAN circuit

12. Camera change to USB port 7, Minicard change to USB port 5

13. Use SB GPIO27 to Enable/Disable Card Reader UB6225P

14. Use SB GPIO28 to Enable/Disable Modem

Rev

1.2G

1.2G

2007/06/30~~P701 Schematic 1.2G Beginning

1. Add R174 to short DASP pins of Master IDE device and SLave IDE device

2. Use SB GPIO27 to controll Card Reader UB6225P Power

3. PR606084.2 connect to +5V to fix LCD flash issue

4. Adjust SPEAKER pin define

5. Adjust CHARGE LED and WLAN LED lightn es s

6. Use SB GPI 26, 29, 30, 31 for PCB version

7. Change USB ESD diode for EMI request

8. Add Floating GND TP_GND and Spring TP1 & TP2 for EMI request

9. Change PM_VCOREL1, PM_VCOREL2 default le vel

10. Add PQ48 to controll +3V_PE to fix WLAN AW-GE780 can't detect issue

11. Power Charger part update circuit for new Adapter

12. Use SB GPI12 to detect LID signal level

13. Add H/W THERMTRIP circuit (page 36)

14. Add U40 to prevent system auto power on after clear CMOS

15. Use SB GPI7 for THRO_ CPU

16. Power Charger part update circuit to prevent incorrect Adapter damage boards

17. Q1.1, Q2.1 change to +3V

2007/07/06 P701 1.2G Gerber Out

2007/07 / 26 P701 Schematic 1.3G Beginnin g

1. Add R11 for 801

~~

15. Card Reader UB6225P share 48M clock from CLock Gen with SB USB part

16. Add D29 to fix LCD_CSB leakage current issue

17. LC29, LC30 change to 27PF to pass EA crystal measure

18. Change vaule of PR73, PR74, PC56 and add PC60 to adjust the power sequence timing

between Stand By power and RSMRST#

19. Remove USB port 1

20. Add +5V generate +3V_LCD circuit

21. Remove +5V_CHG generate circuit

22. Use SB GPIO33, GPIO34 to controll the le vel o f VCOR E

B B

23. U31 use APL5315BI-TRL to replace MAX8863TEUK(pin to pin, but reference voltage level

different)

24. PR59 change to 130K Ohm for both 12V Adapter and 9.8V Adapter

P701 1.0G Gerber Out2007/05/22

1.1G

2007/05/31~~P701 Schematic 1.1G Beginning

1. Remove the 48M clock from CLock Gen to Card Reader UB6225P

2. Clock Gen ICS9LPR367 change to ICS9LPR426

3. Flash Connector increase SATA and USB interface

4. Add Onboard Flash(SM223 + NAND Flash x4)

5. BATT_CON pin 5 connect to GND

6. Q34 pin 1 connect to +3V to fix EC reset issu e

7. Remove J1, J2

8. KB pin 28 connect to GND for P701-ISP_CARD

9. Use SB GPO23 to Enable/Disable Audio Amplifi er

A A

2007/06/07 P701 1.1G Gerber Out

5

10. Use SB GPO21 to controll Ca mer a Po wer

11. Use SB GPIO24 to controll Minicard Power

12. Use SB GPIO25 to Enable/Disable WLAN Rat io

13. Atheros L2 and Minicard SMBUS interface directly pull high

14. LCD_CON pin 20 connect to AC_BAT_SYS

http://laptop-motherboard-schematic.blogspot.com/

4

P900_R1.1G_W/O_FLASH

1

History

Tiansen_Wu

547Wednesday, February 27, 2008

of

Rev

1.2G

Title :

ASUSTek Computer INC.

Size Project Name

A3

3

2

Date: Sheet

P900

Engineer:

5

D D

C C

4

3

2

1

B B

A A

P900_R1.1G_W/O_FLASH

1

Blank

Tiansen_Wu

647Wednesday, February 27, 2008

of

Rev

1.2G

Title :

ASUSTek Computer INC.

Size Project Name

A3

5

http://laptop-motherboard-schematic.blogspot.com/

4

3

2

Date: Sheet

P900

Engineer:

5

4

3

2

1

CR1 Do Not Stuff

1 2

CLK_XIN CLK_XOUT

D D

C C

B B

μν

A A

12

CC11

27PF/50V

GND GND

CLK_PCI_EC32

μν

CLK_PCI_DEBUG33

μν

CLK_PCI_ICH15

μν

CLK_48M_USB16

μν

CLK_96M_UMA10

μν

CLK_96M_UMA#10

μν

CLK_LCD_LVDS10

μν

CLK_LCD_LVDS#10

μν

CLK_PCIE_MCH12

μν

CLK_PCIE_MCH#12

μν

CLK_PCIE_ICH16

μν

CLK_PCIE_ICH#16

μν

CLK_PCIE_LAN23

μν

CLK_PCIE_LAN#23

μν

CLK_SATA_ICH16

μν

CLK_SATA_ICH#16

μν

VCCP_OK43,46

/X

CX1

12

14.318Mhz

+3V_CLK

5 6

5

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

3 4

10KOhm

12

CC12

27PF/50V

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

10KOhm

CRN3C

CRN8A

CRN8B

CRN8C

CRN8D

CRN7A

CRN7B

CRN7C

CRN7D

CRN6A

CRN6B

CRN6C

CRN6D

CRN9A

CRN9B

CRN9C

CRN9D

CRN3B

1

1

+3VSB

CLK_PCI3

CLK_PCI4

CLK_SELPCIE_LCD#

CLK_ITP_EN

CLK_SELLCD_27#

CLK_PG#

CLK_FSLA

CLK_96M

CLK_96M#

CLK_FSLB

CLK_LCD

CLK_LCD#

CLK_PCIE1

CLK_PCIE#1

CLK_PCIE2

CLK_PCIE#2

CLK_PCIE3

CLK_PCIE#3

CLK_SATA

CLK_SATA#

CLK_PG#

32

3

D

CQ1

H2N7002

G

S

2

GND

120Ohm/100Mhz

+3V_CLK

+3V_CLK

CL1

21

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28 29

GND

12

CC40

Do Not Stuff

/X

GND

http://laptop-motherboard-schematic.blogspot.com/

12

12

CS9LPR426AGLF

CC2

CC1

0.1UF/16V

Do Not Stuff

/CAP/X

U12

VDDPCI1

GND1

PCICLK3

PCICLK4

*SELPCIEX0_LCD#PCICLK5

GND2

VDDPCI2

ITP_EN/PCICLK_F0

*SELLCD_27#/PCICLK_F1

Vtt_PwrGd#/PD

VDD48

FSLA/USB_48MHz

GND3

DOTT_96MHz

DOTC_96MHz

FSLB/TEST_MODE

27FIX/LCD_SSCGT/PCIEX0T

27SS/LCD_SSCGC/PCIEX0C

PCIEXT1

PCIEXC1

VDDPCIEX1

PCIEXT2

PCIEXC2

PCIEXT3

PCIEXC3

SATACLKT

SATACLKC

VDDPCIEX2 GND4

CLK_ITP_EN

CLK_SELPCIE_LCD#

4

12

12

CC3

0.1UF/16V

PCICLK2/REQ_SEL**

PCI/PCIEX_STOP#

REF1/FSLC/TEST_SEL

CPUCLKT2_ITP/PCIEXT6

CPUCLKC2_ITP/PCIEXC6

PEREQ1#/PCIEXT5

PEREQ2#/PCIEXC5

CC4

0.1UF/16V

CPU_STOP#

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

VDDPCIEX3

1 2

7 8

VDDREF

SDATA

VDDCPU

PCIEXT4

PCIEXC4

10KOhm

10KOhm

12

REF0

GND6

SCLK

GND5

VDD

GNDA

VDDA

CC5

0.1UF/16V

X1

X2

CRN3A

CRN3D

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

12

GND

+3V_CLK

GND

CC6

0.1UF/16V

+3V_CLK

3

CLK_SELREQ

CLK_FSLC

CLK_REF0

CLK_XIN

CLK_XOUT

CLK_BCLK0

CLK_BCLK#0

CLK_BCLK1

CLK_BCLK#1

CLK_BCLK2

CLK_BCLK#2

CLK_PEREQ#2

CLK_PCIE4

CLK_PCIE#4

12

CC7

0.1UF/16V

12

12

CC8

CC9

0.1UF/16V

0.1UF/16V

S_SMB_DATA

S_SMB_CLK

CR21 33Ohm

CC13 Do Not Stuff

CC14 Do Not Stuff

STP_PCI# 15

μν

STP_CPU# 15,43

μν

1 2

S_SMB_DATA 16

S_SMB_CLK 16

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

μν

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

33OHM

CLKREQ#_MINICARD

CLK_SELLCD_27#

CLK_PEREQ#2

CLK_SELREQ

CLK_FSLA

CLK_FSLC

CLK_FSLB

μν

CRN4A

CRN4B

CRN4C

CRN4D

CRN5A

CRN5B

CRN5C

CRN5D

FSB clock fix 100MHz

FSLA

FSLB

FSLC

12

12

12

12

5 6

3 4

7 8

5 6

3 4

7 8

1 2

1 2

CC10

0.1UF/16V

/X

/X

GND

CLK_REF_ICH 15

CLK_BCLK_CPU 8

CLK_BCLK_CPU# 8

CLK_BCLK_MCH 10

CLK_BCLK_MCH# 10

CLK_BCLK_ITP 8

CLK_BCLK_ITP# 8

CLKREQ#_MINICARD 22

CLK_PCIE_MINICARD 22

CLK_PCIE_MINICARD# 22

8.2KOhm

8.2KOhm

8.2KOhm

10KOhm

10KOhm

10KOhm

10KOhm

8.2KOhm

CC41

0.1UF/16V

CRN2C

CRN2B

CRN2D

CRN1C

CRN1B

CRN1D

CRN1A

CRN2A

100MHz 133MHz

11

00

1

0

μν

+3V_CLK

GND

+3V_CLK

GND

2

μν

μν

μν

μν

μν

μν

μν

μν

μν

CLK_BCLK_CPU

CLK_BCLK_CPU#

CLK_BCLK_MCH

CLK_BCLK_MCH#

CLK_BCLK_ITP

CLK_BCLK_ITP#

CLK_PCIE_MCH

CLK_PCIE_MCH#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_PCIE_MINICARD

CLK_PCIE_MINICARD#

CLK_PCIE_LAN

CLK_PCIE_LAN#

CLK_96M_UMA

CLK_96M_UMA#

CLK_LCD_LVDS

CLK_LCD_LVDS#

CLK_SATA_ICH

CLK_SATA_ICH#

CLK_PCI_ICH

CLK_PCI_EC

CLK_PCI_DEBUG

CLK_REF_ICH

CLK_48M_USB

P900_R1.1G_W/O_FLASH

CC15 Do Not Stuff

CC16 Do Not Stuff

CC17 Do Not Stuff

CC18 Do Not Stuff

CC19 Do Not Stuff

CC20 Do Not Stuff

CC21 Do Not Stuff

CC22 Do Not Stuff

CC23 Do Not Stuff

CC24 Do Not Stuff

CC25 Do Not Stuff

CC26 Do Not Stuff

CC27 Do Not Stuff

CC28 Do Not Stuff

CC29 Do Not Stuff

CC30 Do Not Stuff

CC31 10PF/50V

CC32 10PF/50V

CC38 Do Not Stuff

CC39 Do Not Stuff

CC33 Do Not Stuff

CC34 Do Not Stuff

CC35 Do Not Stuff

CC36 Do Not Stuff

CC37 Do Not Stuff

Title :

ASUSTek Computer INC.

Size Project Name

A3

Date: Sheet

P900

Engineer:

1

12

/X

12

/X

12

/X

12

/X

12

/ITP/X

12

/ITP/X

12

/X

12

/X

12

/X

12

/X

12

/X

12

/X

12

/X

12

/X

12

/X

12

/X

12

12

12

/X

12

/X

12

/X

12

/X

12

/DEBUG/X

12

/X

12

/X

GND

Clock Gen_ICS9LPR426

Tiansen_Wu

Rev

747Wednesday, February 27, 2008

1.2G

of

5

H_D#[63:0] 10

μν

H_DINV#[3:0] 10

H_DSTBN#[3:0] 10

H_DSTBP#[3:0] 10

D D

C C

H_D#15

H_D#14

H_D#13

H_D#12

H_D#11

H_D#10

H_D#9

H_D#8

H_D#7

H_D#6

H_D#5

H_D#4

H_D#3

H_D#2

H_D#1

H_D#0

H_DINV#0

H_DSTBN#0

H_DSTBP#0

H_D#31

H_D#30

H_D#29

H_D#28

H_D#27

H_D#26

H_D#25

H_D#24

H_D#23

H_D#22

H_D#21

H_D#20

H_D#19

H_D#18

H_D#17

H_D#16

H_DINV#1

H_DSTBN#1

H_DSTBP#1

U16A

C25

D[15]#

E23

D[14]#

B23

D[13]#

C26

D[12]#

E24

D[11]#

D24

D[10]#

B24

D[9]#

C20

D[8]#

B20

D[7]#

A21

D[6]#

B26

D[5]#

A24

D[4]#

B21

D[3]#

A22

D[2]#

A25

D[1]#

A19

D[0]#

D25

DINV[0]#

C23

DSTBN[0]#

C22

DSTBP[0]#

K25

D[31]#

N25

D[30]#

H26

D[29]#

M25

D[28]#

N24

D[27]#

L26

D[26]#

J25

D[25]#

M23

D[24]#

J23

D[23]#

G24

D[22]#

F25

D[21]#

H24

D[20]#

M26

D[19]#

L23

D[18]#

G25

D[17]#

H23

D[16]#

J26

DINV[1]#

K24

DSTBN[1]#

L24

DSTBP[1]#

860555INT_FCBGA479

DATA GROUP 0DATA GROUP 1

DSTBN[2]#

DSTBP[2]#

DSTBN[3]#

DSTBP[3]#

Y25

D[47]#

AA26

D[46]#

Y23

D[45]#

V26

D[44]#

U25

D[43]#

V24

D[42]#

U26

D[41]#

AA23

D[40]#

R23

D[39]#

R26

D[38]#

R24

D[37]#

V23

D[36]#

U23

D[35]#

DATA GROUP 2DATA GROUP 3

T25

D[34]#

AA24

D[33]#

Y26

D[32]#

T24

DINV[2]#

W25

W24

AF26

D[63]#

AF22

D[62]#

AF25

D[61]#

AD21

D[60]#

AE21

D[59]#

AF20

D[58]#

AD24

D[57]#

AF23

D[56]#

AE22

D[55]#

AD23

D[54]#

AC25

D[53]#

AC22

D[52]#

AC20

D[51]#

AB24

D[50]#

AC23

D[49]#

AB25

D[48]#

AD20

DINV[3]#

AE24

AE25

μν

μν

μν

H_D#47

H_D#46

H_D#45

H_D#44

H_D#43

H_D#42

H_D#41

H_D#40

H_D#39

H_D#38

H_D#37

H_D#36

H_D#35

H_D#34

H_D#33

H_D#32

H_DINV#2

H_DSTBN#2

H_DSTBP#2

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

H_D#53

H_D#52

H_D#51

H_D#50

H_D#49

H_D#48

H_DINV#3

H_DSTBN#3

H_DSTBP#3

4

HC1 Do Not Stuff

12

HC2 Do Not Stuff

12

GND

GND

H_PWRGD15

μν

U16 use 01G011920000PM

CLK_BCLK_CPU

/X

CLK_BCLK_CPU#

/X

CLK_BCLK_CPU7

μν

CLK_BCLK_CPU#7

μν

1 2

HR3 49.9Ohm 1%

1 2

HR5 49.9Ohm 1%

200Ohm

Do Not Stuff

μν

μν

+VCCP

μν

μν

μν

HR9

μν

μν

1%

μν

1 2

12

HC3

Do Not Stuff

/X

GND

+VCCA

+VCCP

HR14

μν

/X

μν

μν

1 2

H_THERMTRIP#10,15,36

3

H_A20M#15

H_FERR#15

H_IGNNE#15

H_DPSLP#15

H_INTR15

H_NMI15

H_SMI#15

H_STPCLK#15

T3 Do Not Stuff

T177Do Not Stuff

T178Do Not Stuff

H_THERMDA35

H_THERMDC35

T170 Do Not Stuff

T4 Do Not Stuff

T5 Do Not Stuff

T6 Do Not Stuff

T7 Do Not Stuff

T8 Do Not Stuff

H_ITP_CLK

H_ITP_CLK#

H_CPUSLP#

VR_VID5

VR_VID4

VR_VID3

VR_VID2

VR_VID1

VR_VID0

H_VCCA3

1

H_VCCA2

1

H_VCCA1

1

H_PROCHOT#

PM_PSI#

1

CPU_BSEL0

1

H_RSVD3

1

CPU_BSEL1

1

H_RSVD1

1

H_RSVD0

1

VR_VID[5:0] 43

U16C

B15

BCLK[0]

B14

BCLK[1]

A16

ITP_CLK[0]

A15

ITP_CLK[1]

C2

A20M#

D3

FERR#

A3

IGNNE#

A6

SLP#

D1

LINT0

D4

LINT1

B4

SMI#

C6

STPCLK#

E4

PWRGOOD

H4

VID[5]

G4

VID[4]

G3

VID[3]

F3

VID[2]

F2

VID[1]

E2

VID[0]

AC26

VCCA[3]

N1

VCCA[2]

B1

VCCA[1]

F26

VCCA[0]

B18

THERMDA

A18

THERMDC

C17

THERMTRIP#

B17

PROCHOT#

E1

RSVD5

C16

RSVD4

C3

RSVD3

C14

RSVD2

AF7

RSVD1

B2

RSVD0

860555INT_FCBGA479

μν

COMP[3]

COMP[2]

HOSTCLKLEGACY CPU

COMP[1]

COMP[0]

BPM[3]#DPSLP#

BPM[2]#

BPM[1]#

BPM[0]#

GTLREF[3]

GTLREF[2]

GTLREF[1]

GTLREF[0]

TEST1

TEST2

MISC

TRST#

VCCSENSE

VSSSENSE

TCK

TDO

TMS

2

H_CPUSLP#

H_COMP3

AB1

H_COMP2

AB2

H_COMP1

P26

H_COMP0

P25

H_BPM#3

C9B7

H_BPM#2

A9

H_BPM#1

B8

H_BPM#0

C8

H_GTLREF3

AC1

H_GTLREF2

G1

H_GTLREF1

E26

H_GTLREF

AD26

H_TEST1

C5

H_TEST2

F23

H_TCK

A13

H_TDI

C12

TDI

H_TDO

A12

TMS

H_

C11

H_TRST#

B13

H_VCCSENSE

AE7

H_VSSSENSE

AF6

HR1 0Ohm

1 2

HR2 Do Not Stuff/X

1 2

HR4 54.9Ohm 1%

1 2

HR6 27.4Ohm 1%

1 2

HR7 54.9Ohm 1%

1 2

HR8 27.4Ohm 1%

1 2

GND

1

1

HR11 Do Not Stuff1% /X

HR12 Do Not Stuff1% /X

T1Do Not Stuff

HR10 Do Not Stuff

1 2

1 2

1 2

HR16 Do Not Stuff

1 2

HR17 Do Not Stuff

1 2

/X

T2Do Not Stuff

1%/X

1%/X

GND

H_DPRSTP# 15

GND

N_CPUSLP# 10

S_CPUSLP# 15

μν

+VCCP

HR13

1KOhm

1%

H_GTLREF

1 2

HR15

2KOhm

1%

1 2

GND GND

1

μν

μν

12

HC4

0.1UF/16V

H_A#16

H_A#15

H_A#14

H_A#13

H_A#12

H_A#11

H_A#10

H_A#9

H_A#8

H_A#7

μν

μν

5

H_A#6

H_A#5

H_A#4

H_A#3

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_A#31

H_A#30

H_A#29

H_A#28

H_A#27

H_A#26

H_A#25

H_A#24

H_A#23

H_A#22

H_A#21

H_A#20

H_A#19

H_A#18

H_A#17

B B

H_ADSTB#010

μν

H_A#[31:3] 10

H_REQ#[4:0] 10

A A

μν

μν

H_ADSTB#110

H_DPWR#10

U16B

AA2

A[16]#

Y3

A[15]#

AA3

A[14]#

U1

A[13]#

Y1

A[12]#

Y4

A[11]#

W2

A[10]#

T4

A[9]#

W1

A[8]#

V2

A[7]#

R3

A[6]#

V3

A[5]#

U4

A[4]#

P4

A[3]#

U3

ADSTB[0]#

T1

REQ[4]#

P1

REQ[3]#

T2

REQ[2]#

P3

REQ[1]#

R2

REQ[0]#

AF1

A[31]#

AE1

A[30]#

AF3

A[29]#

AD6

A[28]#

AE2

A[27]#

AD5

A[26]#

AC6

A[25]#

AB4

A[24]#

AD2

A[23]#

AE4

A[22]#

AD3

A[21]#

AC3

A[20]#

AC7

A[19]#

AC4

A[18]#

AF4

A[17]#

AE5

ADSTB[1]#

C19

DPWR#

860555INT_FCBGA479

ADS#

PRDY#

PREQ#

BNR#

BPRI#

DBR#

ADDRESS GROUP 0ADDRESS GROUP 1

DEFER#

DRDY#

DBSY#

BR0#

CONTROL

IERR#

INIT#

LOCK#

RESET#

RS[2]#

RS[1]#

RS[0]#

TRDY#

HIT#

HITM#

N2

H_BPM#4

A10

H_BPM#5

B10

L1

J3

H_DBR#

A7

L4

H2

M2

N4

H_IERR#

A4

B5

J2

B11

H_RS#2

L2

H_RS#1

K1

H_RS#0

H1

M3

K3

K4

http://laptop-motherboard-schematic.blogspot.com/

1

1

4

H_ADS# 10

μν

H_BNR# 10

μν

H_BPRI# 10

μν

T9Do Not Stuff

H_DEFER# 10

μν

H_DRDY# 10

μν

H_DBSY# 10

μν

H_BR0# 10

μν

T171Do Not Stuff

H_INIT# 15

μν

H_LOCK# 10

μν

H_RS#[2:0] 10

μν

H_TRDY# 10

μν

H_HIT# 10

μν

H_HITM# 10

μν

+VCCP

1 2

12

GND

HR24

Do Not Stuff

/X

HC7

Do Not Stuff

/X

H_CPURST# 10

μν

1 2

3

HR18

0Ohm

r0603_h24

+VCCA+1.5V

12

HC5

22UF/6.3V

CLK_BCLK_ITP#7

μν

μν

H_PWRGD

120 mA

SMB_CLK16,18

1 2

1

12

HC6

0.1UF/16V

GND

HR25

Do Not Stuff

/ITP

H_TCK

H_TDO

H_BPM#0

H_BPM#2

H_BPM#4

ITP_PWRGD

T205Do Not Stuff

+VCCP

GND

μν

μν

H_CPURST#

Dothan_HOST

1

+VCCP

GND

Tiansen_Wu

847Wednesday, February 27, 2008

of

Rev

1.2G

H_BPM#5

HR20 56OHM

1 2

HR21 Do Not Stuff/ITP

1 2

56Ohm

56Ohm

56Ohm

56Ohm

CLK_BCLK_ITP 7

SMB_DATA 16,18

1 2

HR22

Do Not Stuff

/ITP

HRN1A

HRN1B

HRN1C

HRN1D

1 2

3 4

5 6

7 8

31

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

32

ITP

SIDE1

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

SIDE2

Do Not Stuff

/ITP

SIDE4

SIDE3

34

2

2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

33

P900_R1.1G_W/O_FLASH

GND

H_TDO

H_TMS

H_TDI

H_TCK

H_TRST#

ITP_CPURST#

H_TMS

H_TDI

H_BPM#1

H_BPM#3

H_BPM#5

H_TRST#

Title :

ASUSTek Computer INC.

Size Project Name

A3

2

Date: Sheet

P900

Engineer:

5

+VCCP VCORE

2.5 A

U16D

D D

C C

B B

W4

P23

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

L21

M22

N21

P22

R21

T22

U21

VCCQ[1]

VCCQ[0]

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

K6

VCCP12

L5

VCCP13

VCCP14

M6

VCCP15

VCCP16

N5

VCCP17

VCCP18

P6

VCCP19

VCCP20

R5

VCCP21

VCCP22

T6

VCCP23

VCCP24

VCCP25

VCC72

AF18

VCC71

AF16

VCC70

AF14

VCC69

AF12

VCC68

AF10

VCC67

AF8

VCC

VCC63

VCC64

VCC65

VCC66

AE13

AE15

AE17

AE19

VCC62

AE11

D6

VCC1

D8

VCC2

D18

VCC3

D20

VCC4

D22

VCC5

E5

VCC6

E7

VCC7

E9

VCC8

E17

VCC9

E19

VCC10

E21

VCC11

F6

VCC12

F8

VCC13

F18

VCC14

F20

VCC15

F22

VCC16

G5

VCC17

G21

VCC18

H6

VCC19

H22

VCC20

J5

VCC21

J21

VCC22

K22

VCC23

U5

VCC24

V6

VCC25

V22

VCC26

W5

VCC27

W21

VCC28

Y6

VCC29

Y22

VCC30

AA5

VCC31

AA7

VCC32

AA9

VCC33

AA11

VCC34

AA13

VCC35

AA15

VCC36

AA17

VCC37

AA19

VCC38

AA21

VCC39

AB6

VCC40

AB8

VCC41

AB10

VCC42

AB12

VCC43

AB14

VCC44

AB16

VCC45

AB18

VCC46

AB20

VCC47

AB22

VCC48

AC9

VCC49

AC11

VCC50

AC13

VCC51

AC15

VCC52

AC17

VCC53

AC19

VCC54

AD8

VCC55

AD10

VCC56

AD12

VCC57

AD14

VCC58

AD16

VCC59

AD18

VCC60

VCC61

860555INT_FCBGA479

AE9

4

Celeron-M(Dothan) ULV max 7 A

VCORE

12

+

HCE1

Do Not Stuff

/CAP/X

GND GND

+VCCP

12

HC28

10UF/6.3V

12

12

HC27

10UF/6.3V

3

+VCCP

12

+

HCE2

100UF/2V

12

+

HCE3

Do Not Stuff

/CAP/X

12

+

HCE4

Do Not Stuff

/CAP/X

U16 use 01G011920000PM

12

HC24

0.1UF/16V

HC20

Do Not Stuff

/CAP/X

0.1U All X7R

12

HC26

Do Not Stuff

/CAP/X

GND

12

12

HC21

HC22

0.1UF/16V

Do Not Stuff

/CAP/X

VCORE

12

HC23

Do Not Stuff

/CAP/X

HC29

Do Not Stuff

/CAP/X

12

GND

12

HC25

0.1UF/16V

U16E

A2

VSS1

A5

VSS2

A8

VSS3

A11

VSS4

A14

VSS5

A17

VSS6

A20

VSS7

A23

VSS8

A26

VSS9

B3

VSS10

B6

VSS11

B9

VSS12

B12

VSS13

B16

VSS14

B19

VSS15

B22

VSS16

B25

VSS17

C1

VSS18

C4

VSS19

C7

VSS20

C10

VSS21

C13

VSS22

C15

VSS23

C18

VSS24

C21

VSS25

C24

VSS26

D2

VSS27

D5

VSS28

D7

VSS29

D9

VSS30

D11

VSS31

D13

VSS32

D15

VSS33

D17

VSS34

D19

VSS35

D21

VSS36

D23

VSS37

D26

VSS38

E3

VSS39

E6

VSS40

E8

VSS41

E10

VSS42

E12

VSS43

E14

VSS44

E16

VSS45

E18

VSS46

E20

VSS47

E22

VSS48

E25

VSS49

F1

VSS50

F4

VSS51

F5

VSS52

F7

VSS53

F9

VSS54

F11

VSS55

F13

VSS56

F15

VSS57

F17

VSS58

F19

VSS59

F21

VSS60

F24

VSS61

G2

VSS62

G6

VSS63

G22

VSS64

860555INT_FCBGA479

2

AF24

AF21

AF19

AF17

AF15

AF13

AF11

AF9

AF5

AF2

AE26

AE23

AE20

AE18

AE16

AE14

AE12

AE10

AE8

AE6

AE3

AD25

AD22

AD19

AD17

VSS192

VSS191

VSS190

VSS189

VSS188

VSS187

VSS186

VSS185

VSS184

VSS183

VSS182

VSS181

VSS180

VSS179

VSS178

VSS177

VSS176

VSS175

VSS174

VSS173

VSS172

VSS171

VSS170

VSS169

VSS168

GND

VSS89

VSS88

VSS87

VSS86

VSS85

VSS84

VSS83

VSS82

VSS81

VSS80

VSS79

VSS65

G23

VSS66

VSS67

G26H3H5

VSS68

VSS69

H21

VSS70

VSS71

H25J1J4J6J22

VSS72

VSS73

VSS74

VSS75

J24K2K5

VSS76

VSS77

VSS78

K21

K23

K26

M24

M21M5M4M1L25

L22L6L3

AD15

AD13

VSS167

VSS90

AD11

AD9

VSS166

VSS165

VSS92

VSS91

N23

N22N6N3

AD7

AD4

VSS164

VSS163

VSS94

VSS93

P2

N26

1

AD1

VSS162

VSS161

VSS95

VSS96

P5

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS150

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

AC24

AC21

AC18

AC16

AC14

AC12

AC10

AC8

AC5

AC2

AB26

AB23

AB21

AB19

AB17

AB15

AB13

AB11

AB9

AB7

AB5

AB3

AA25

AA22

AA20

AA18

AA16

AA14

AA12

AA10

AA8

AA6

AA4

AA1

Y24

Y21

Y5

Y2

W26

W23

W22

W6

W3

V25

V21

V5

V4

V1

U24

U22

U6

U2

T26

T23

T21

T5

T3

R25

R22

R6

R4

R1

P24

P21

GND

VCORE

12

A A

5

12

HC10

10UF/6.3V

http://laptop-motherboard-schematic.blogspot.com/

HC11

Do Not Stuff

/CAP/X

4

12

HC12

10UF/6.3V

12

HC13

10UF/6.3V

12

HC14

Do Not Stuff

/CAP/X

12

HC15

Do Not Stuff

/CAP/X

12

HC16

Do Not Stuff

/CAP/X

3

12

HC17

10UF/6.3V

12

GND

HC18

Do Not Stuff

/CAP/X

P900_R1.1G_W/O_FLASH

Title :

ASUSTek Computer INC.

Size Project Name

A3

2

Date: Sheet

P900

Engineer:

Dothan_PWR_GND

Tiansen_Wu

1

947Wednesday, February 27, 2008

Rev

1.2G

of

5

4

3

2

1

H_RS#[2:0] 8

12

12

+VCCP

/X

/X

NR15

1KOhm

1%

N_HVREF

1 2

NR23

2KOhm

1%

1 2

GND

μν

GND

12

NC13

0.1UF/16V

JP1

JP2

+1.8V_DUAL

1 2

1 2

GND

3

MCLK_DDR018

μν

MCLK_DDR118

μν

MCLK_DDR0#18

μν

MCLK_DDR1#18

μν

μν

μν

μν

μν

μν

μν

1 2

1 2

NR16

1KOhm

1%

N_MVREF

NR24

1KOhm

1%

GND

T44 Do Not Stuff

T50 Do Not Stuff

MA_CKE018,19

MA_CKE118,19

MA_CS#018,19

MA_CS#118,19

MA_ODT018,19

MA_ODT118,19

Do Not Stuff

Do Not Stuff

12

NC14

0.1UF/16V

DMI_RXN[3:0] 16

DMI_RXP[3:0] 16

DMI_TXN0

DMI_TX

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

MCLK_DDR2

1

MCLK_DDR2#

1

N_MOCDCOMP0

N_MOCDCOMP1

N_MRCOMPN

N_MRCOMPP

N_MVREF

N_MXSLEWIN

N_MXSLEWOUT

N_MYSLEWIN

N_MYSLEWOUT

μν

μν

AA31

N1

AB35

AC31

AD35

Y31

AA35

AB31

AC35

AA33

AB37

AC33

AD37

Y33

AA37

AB33

AC37

AM33

AL1

AE11

AJ34

AF6

AC10

AN33

AK1

AE10

AJ33

AF5

AD10

AP21

AM21

AH21

AK21

AN16

AM14

AH15

AG16

AF22

AF16

AP14

AL15

AM11

AN10

AK10

AK11

AF37

AD1

AE27

AE28

AF9

AF10

N_MRCOMPN

N_MRCOMPP

N_MOCDCOMP0

N_MOCDCOMP1

U1A

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

SM_CK0

SM_CK1

RSVD28

SM_CK3

SM_CK4

RSVD30

SM_CK0#

SM_CK1#

RSVD29

SM_CK3#

SM_CK4#

RSVD31

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SMOCDCOMP0

SMOCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

SMXSLEWIN

SMXSLEWOUT

SMYSLEWIN

SMYSLEWOUT

NQ82915PM

NR9 80.6Ohm

1 2

NR10 80.6Ohm

1 2

NR11 40.2Ohm

1 2

NR12 40.2Ohm

1 2

2

DMI_TXN[3:0] 16

DMI_TXP[3:0] 16

DMIDDR MUXING

DREF_SSCLKN

DREF_SSCLKP

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

PM

EXT_TS1#

THRMTRIP#

PWROK

RSTIN#

DREF_CLKN

DREF_CLKP

CLK

NC

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

1%

1%

1%

1%

μν

μν

G16

H13

G14

F16

F15

G15

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

J23

J21

H22

F5

AD30

AE29

A24

A23

C37

D37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

+1.8V_DUAL

GND

GND

N_CFG0

N_CFG2

N_CFG1

N_CFG6

7 8

1KOhm

5 6

1KOhm

1 2

1KOhm

3 4

1KOhm

FSB fix 100MHz

N_CFG0

N_CFG1

N_CFG2

N_CFG3

N_CFG4

N_CFG5

N_CFG6

N_CFG7

N_CFG8

N_CFG9

N_CFG10

N_CFG11

N_CFG12

N_CFG13

N_CFG14

N_CFG15

N_CFG16

N_CFG17

N_CFG18

N_CFG19

N_CFG20

N_LT_TRUST

N_LT_RST#

N_TESTIN#

N_LADATAN3

N_LADATAP3

N_LBDATAN3

N_LBDATAP3

N_EXT_TS#0

N

_EXT_TS#1

N_NC11

P900_R1.1G_W/O_FLASH

ASUSTek Computer INC.

Date: Sheet

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

CLK_96M_UMA

CLK_96M_UMA#

CLK_LCD_LVDS

CLK_LCD_LVDS#

PM_PWROK

PLT_RST#

Size Project Name

A3

T25Do Not Stuff

T26Do Not Stuff

NR28 Do Not Stuff

1 2

T172Do Not Stuff

T29Do Not Stuff

T30Do Not Stuff

T31Do Not Stuff

T32Do Not Stuff

T33Do Not Stuff

T34Do Not Stuff

T35Do Not Stuff

T36Do Not Stuff

T37Do Not Stuff

T38Do Not Stuff

T39Do Not Stuff

T40Do Not Stuff

T41Do Not Stuff

T42Do Not Stuff

T43Do Not Stuff

T45Do Not Stuff

T46Do Not Stuff

T47Do Not Stuff

T48Do Not Stuff

T49Do Not Stuff

N_EXT_TS#0

N_EXT_TS#1

1

1 2

3 4

PM_BMBUSY# 15

H_THERMTRIP# 8,15,36

PM_PWROK 15,32

PLT_RST# 15,22,23

μν

CLK_96M_UMA# 7

CLK_96M_UMA 7

CLK_LCD_LVDS# 7

CLK_LCD_LVDS 7

NC5 Do Not Stuff

NC6 Do Not Stuff

NC7 Do Not Stuff

NC8 Do Not Stuff

T55Do Not Stuff

NC9 Do Not Stuff

1 2

NC10 Do Not Stuff

1 2

Engineer:

P900

H_D#[63:0] 8

μν

H_A#[31:3] 8

μν

H_D#0

H_D#1

D D

C C

B B

N_HXSCOMP

N_HYSCOMP

A A

N_HXRCOMP

N_HYRCOMP

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15 H_A#18

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

N_HXRCOMP

N_HXSCOMP

N_HXSWING

N_HYRCOMP

N_HYSCOMP

N_HYSWING

NR17 54.9Ohm 1%

1 2

NR18 54.9Ohm 1%

1 2

NR19 24.9Ohm 1%

1 2

NR20 24.9Ohm 1%

1 2

E4

E1

F4

H7

E2

F1

E3

D3

K7

F2

J7

J8

H6

F3

K8

H5

H1

H2

K5

K6

J4

G3

H3

J1

L5

K4

J5

P7

L7

J3

P5

L3

U7

V6

R6

R5

P3

T8

R7

R8

U8

R4

T4

T5

R1

T3

V8

U6

W6

U3

V5

W8

W7

U2

U1

Y5

Y2

V4

Y7

W1

W3

Y3

Y6

W2

C1

C2

D1

T1

L1

P1

5

U1D

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

NQ82915PM

HOST

+VCCP

GND

H_DSTBN#[3:0] 8

H_DSTBP#[3:0] 8

G9

HA3#

C9

HA4#

E9

HA5#

B7

HA6#

A10

HA7#

F9

HA8#

D8

HA9#

B10

HA10#

E10

HA11#

G10

HA12#

D9

HA13#

E11

HA14#

F10

HA15#

G11

HA16#

G13

HA17#

C10

HA18#

C11

HA19#

D11

HA20#

C12

HA21#

B13

HA22#

A12

HA23#

F12

HA24#

G12

HA25#

E12

HA26#

C13

HA27#

B11

HA28#

D13

HA29#

A13

HA30#

F13

HA31#

F8

HADS#

B9

HADSTB0#

E13

HADSTB1#

J11

HVREF

A5

HBNR#

D5

HBPRI#

E7

HBREQ0#

HCLKN

HCLKP

HDBSY#

HDEFER#

HDINV0#

HDINV1#

HDINV2#

HDINV3#

HDPWR#

HDRDY#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

RSVD32

HHIT#

HHITM#

HLOCK#

RSVD33

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HRS0#

HRS1#

HRS2#

HTRDY#

H10

AB1

AB2

C6

E6

H8

K3

T7

U5

G6

F7

G4

K1

R3

V3

G5

K2

R2

W4

F6

D4

D6

B3

A11

A7

D7

B8

C7

A8

A4

C5

B4

G8

B5

+VCCP

GND GND

HCPURST#

HCPUSLP#

μν

μν

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

N_HVREF

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3H_D#55

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

N_HEDRDY#

N_HPCREQ#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

NR13

2.21KOhm

1%

N_HXSWING

1 2

NR21

1KOhm

1%

1 2

H_DINV#[3:0] 8

H_REQ#[4:0] 8

μν

μν

U1 use 02G010007612

CLK_BCLK_MCH

CLK_BCLK_MCH#

H_ADS# 8

μν

H_ADSTB#0 8

H_ADSTB#1 8

H_BNR# 8

μν

H_BPRI# 8

μν

H_BR0# 8

μν

H_CPURST# 8

CLK_BCLK_MCH# 7

CLK_BCLK_MCH 7

H_DBSY# 8

μν

H_DEFER# 8

μν

H_DPWR# 8

μν

H_DRDY# 8

μν

NC11

0.1UF/16V

T54Do Not Stuff

H_HIT# 8

μν

H_HITM# 8

μν

H_LOCK# 8

μν

T56Do Not Stuff

N_CPUSLP# 8

H_TRDY# 8

μν

+VCCP

NR14

2.21KOhm

1%

N_HYSWING

1 2

NR22

1KOhm

1%

1 2

GND

4

1

1

12

GND

http://laptop-motherboard-schematic.blogspot.com/

μν

μν

μν

μν

μν

μν

GND

NC3 Do Not Stuff

NC4 Do Not Stuff

12

NC12

0.1UF/16V

NRN1D

NRN1C

NRN1A

NRN1B

/X

GND

4.7KOhm

4.7KOhm

μν

μν

μν

μν

μν

μν

μν

12

/X

12

/X

12

/X

12

/X

/X

/X

Title :

1

+2.5V

GND

+2.5V

NRN3A

NRN3B

GND

GND

910GML_HOST_DMI

Tiansen_Wu

10 47Wednesday, February 27, 2008

Rev

1.2G

of

5

4

3

2

1

MA_DQ[63:0] 18

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

MA_DQS[7:0] 18

MA_DQS#[7:0] 18

U1B

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

NQ82915PM

D D

MA_DQ0

MA_DQ1

MA_DQ2

MA_DQ3

MA_DQ4

MA_DQ5

MA_DQ6

MA_DQ7

MA_DQ8

MA_DQ9

MA_DQ10

MA_DQ11

MA_DQ12

MA_DQ13

MA_DQ14

MA_DQ15

MA_DQ16

MA_DQ17

C C

B B

MA_DQ18

MA_DQ19

MA_DQ20

MA_DQ21

MA_DQ22

MA_DQ23

MA_DQ24

MA_DQ25

MA_DQ26

MA_DQ27

MA_DQ28

MA_DQ29

MA_DQ30

MA_DQ31

MA_DQ32

MA_DQ33

MA_DQ34

MA_DQ35

MA_DQ36

MA_DQ37

MA_DQ38

MA_DQ39

MA_DQ40

MA_DQ41

MA_DQ42

MA_DQ43

MA_DQ44

MA_DQ45

MA_DQ46

MA_DQ47

MA_DQ48

MA_DQ49

MA_DQ50

MA_DQ51

MA_DQ52

MA_DQ53

MA_DQ54

MA_DQ55

MA_DQ56

MA_DQ57

MA_DQ58

MA_DQ59

MA_DQ60

MA_DQ61

MA_DQ62

MA_DQ63

μν

μν

μν

SA_BS0

SA_BS1

SA_BS2

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

DDR SYSTEM MEMORY A

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

MA_DM[7:0] 18

MA_MA[13:0] 18,19

MA_BA[2:0] 18,19

AK15

AK16

AL21

AJ37

AP35

AL29

AP24

AP9

AP4

AJ2

AD3

AK36

AP33

AN29

AP23

AM8

AM4

AJ1

AE5

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AE4

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

MA_RCVENIN#

AF29

MA_RCVENOUT#

AF28

AP15

μν

μν

μν

MA_BA0

MA_BA1

MA_BA2

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS0

MA_DQS1

MA_DQS2

MA_DQS3

MA_DQS4

MA_DQS5

MA_DQS6

MA_DQS7

MA_DQS#0

MA_DQS#1

MA_DQS#2

MA_DQS#3

MA_DQS#4

MA_DQS#5

MA_DQS#6

MA_DQS#7

MA_MA0

MA_MA1

MA_MA2

_MA3

MA

MA_MA4

MA_MA5

MA_MA6

MA_MA7

MA_MA8

MA_MA9

MA_MA10

MA_MA11

MA_MA12

MA_MA13

U1C

AE31

SB_DQ0

AE32

SB_DQ1

AG32

U1 use 02G010007612

MA_CAS# 18,19

μν

MA_RAS# 18,19

1

1

T57Do Not Stuff

T58Do Not Stuff

μν

MA_WE# 18,19

μν

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AK9

AK6

AH5

AK8

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

AJ9

AJ7

AJ4

AJ8

AJ5

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

NQ82915PM

DDR SYSTEM MEMORY B

SB_RCVENIN#

SB_RCVENOUT#

SB_BS0

SB_BS1

SB_BS2

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

SB_RAS#

SB_WE#

AJ15

AG17

AG21

AF32

AK34

AK27

AK24

AJ10

AK5

AE7

AB7

AF34

AK32

AJ28

AK23

AM10

AH6

AF8

AB4

AF35

AK33

AK28

AJ23

AL10

AH7

AF7

AB5

AH17

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

A A

P900_R1.1G_W/O_FLASH

Title :

ASUSTek Computer INC.

Size Project Name

A3

5

http://laptop-motherboard-schematic.blogspot.com/

4

3

2

Date: Sheet

P900

Engineer:

910GML_DRAM

1

Tiansen_Wu

11 47Wednesday, February 27, 2008

of

Rev

1.2G

5

4

3

2

1

SDVOCRTL_DATA Int PD

SDVO SMbus have

internal pull down

D D

CLK_PCIE_MCH

CLK_PCIE_MCH#

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

/X

12

12

12

N_LCTLA_CLK

N_LCTLB_DATA

N_LDDC_CLK

N_LDDC_DATA

N_LIBG

NRN2B

NRN2C

NRN2D

NRN2A

/X

/X

/X

3 4

5 6

7 8

1 2

NC70 Do Not Stuff

NC71 Do Not Stuff

NC72 Do Not Stuff

GND

C C

B B

NC1 Do Not Stuff

NC2 Do Not Stuff

CRT_BLUE

CRT_GREEN

CRT_RED

CRT_BLUE

CRT_GREEN

CRT_RED

CRT_VSYNC20

μν

CRT_HSYNC20

μν

NR29 4.7KOhm

1 2

NR30 4.7KOhm

1 2

5 6

4.7KOhm

7 8

4.7KOhm

NR7 1.5KOHM

1 2

1%

12

/X

12

/X

NRN3C

NRN3D

GND

+2.5V

GND

T10 Do Not Stuff

T11 Do Not Stuff

CLK_PCIE_MCH#7

μν

CLK_PCIE_MCH7

μν

DDC_CLK20

μν

DDC_DATA20

μν

CRT_BLUE20

μν

CRT_GREEN20

μν

CRT_RED20

μν

NR4 0Ohm

1 2

NR5 0Ohm

1 2

NR6 255Ohm

1 2

LBKLT_CTRL21

μν

LBKLT_EN21

μν

LVDD_EN21

μν

T14 Do Not Stuff

T15 Do Not Stuff

T16 Do Not Stuff

LA_CLKN21

μν

LA_CLKP21

μν

T17 Do Not Stuff

T18 Do Not Stuff

LA_DATAN021

μν

LA_DATAN121

μν

LA_DATAN221

μν

LA_DATAP021

μν

LA_DATAP121

μν

LA_DATAP221

μν

T19 Do Not Stuff

T20 Do Not Stuff

T21 Do Not Stuff

T22 Do Not Stuff

T23 Do Not Stuff

T24 Do Not Stuff

1

1

1%

1

1

1

1

1

1

1

1

1

1

1

0 : No SDVO device

1 : SDVO device present

N_SDVOCTRL_DATA

N_SDVOCTRL_CLK

CRT_VSYNC_R

CRT_HSYNC_R

N_CRT_REFSET

N_LCTLA_CLK

N_LCTLB_DATA

N_LDDC_CLK

N_LDDC_DATA

N_LIBG

N_LVBG

N_LVREFH

N_LVREFL

N_LBCLKN

N_LBCLKP

N_LBDATAN0

N_LBDATAN1

N_LBDATAN2

N_LBDATAP0

N_LBDATAP1

N_LBDATAP2

GND

GNDGND

H24

H25

AB29

AC29

A15

C16

A17

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

J18

J20

U1F

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CRTL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

NQ82915PM

U1 use 02G010007612

N_EXP_COMP

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

D36

D34

E30

F34

G30

H34

J30

K34

L30

M34

N30

P34

R30

T34

U30

V34

W30

Y34

D30

E34

F30

G34

H30

J34

K30

L34

M30

N34

P30

R34

T30

U34

V30

W34

E32

F36

G32

H36

J32

K36

L32

M36

N32

P36

R32

T36

U32

V36

W32

Y36

D32

E36

F32

G36

H32

J36

K32

L36

M32

N36

P32

R36

T32

U36

V32

W36

PCI-E signals can be left NC, If unused.

EXP_COMPI

EXP_ICOMPO

MISCTVVGALVDS

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13