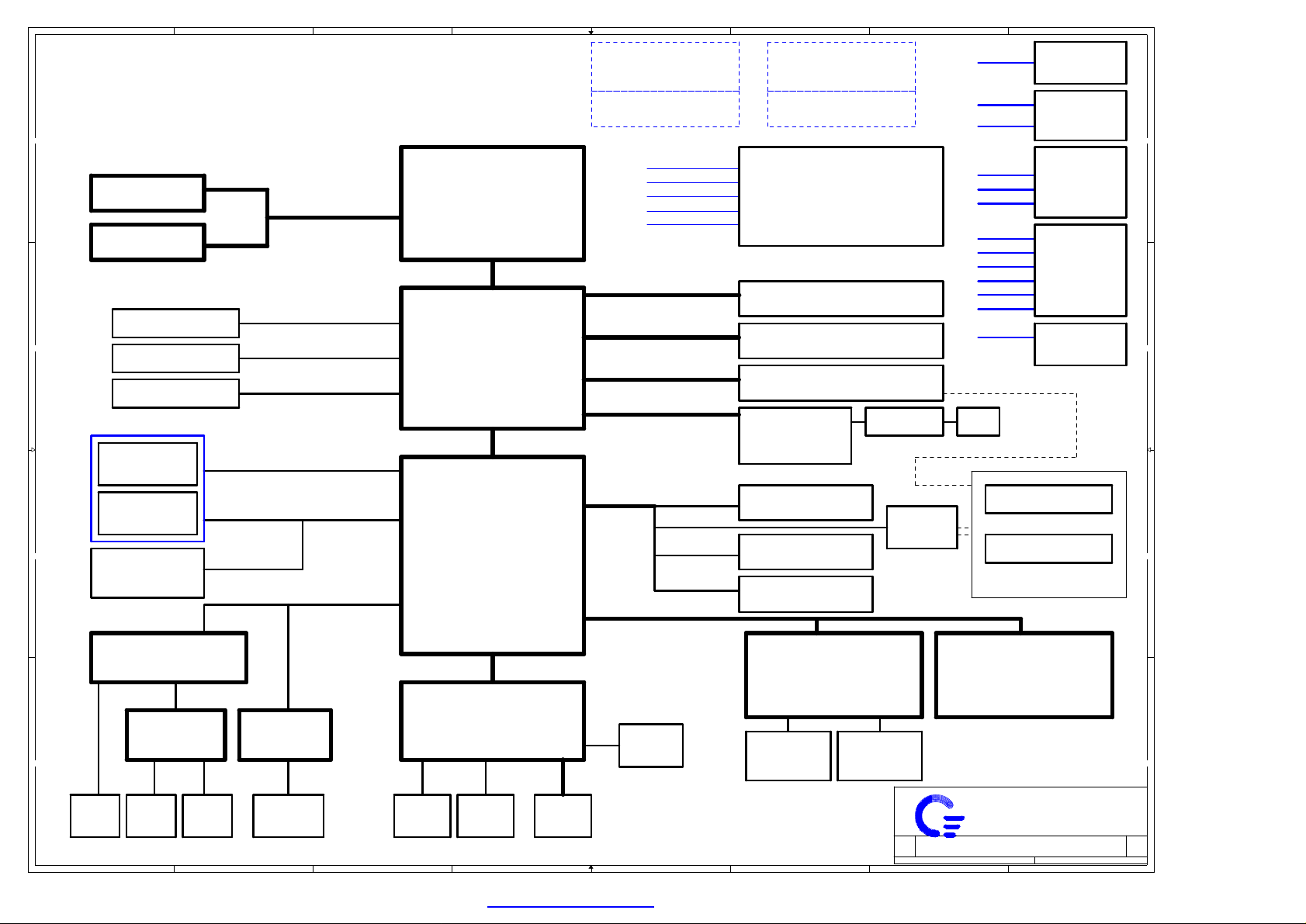

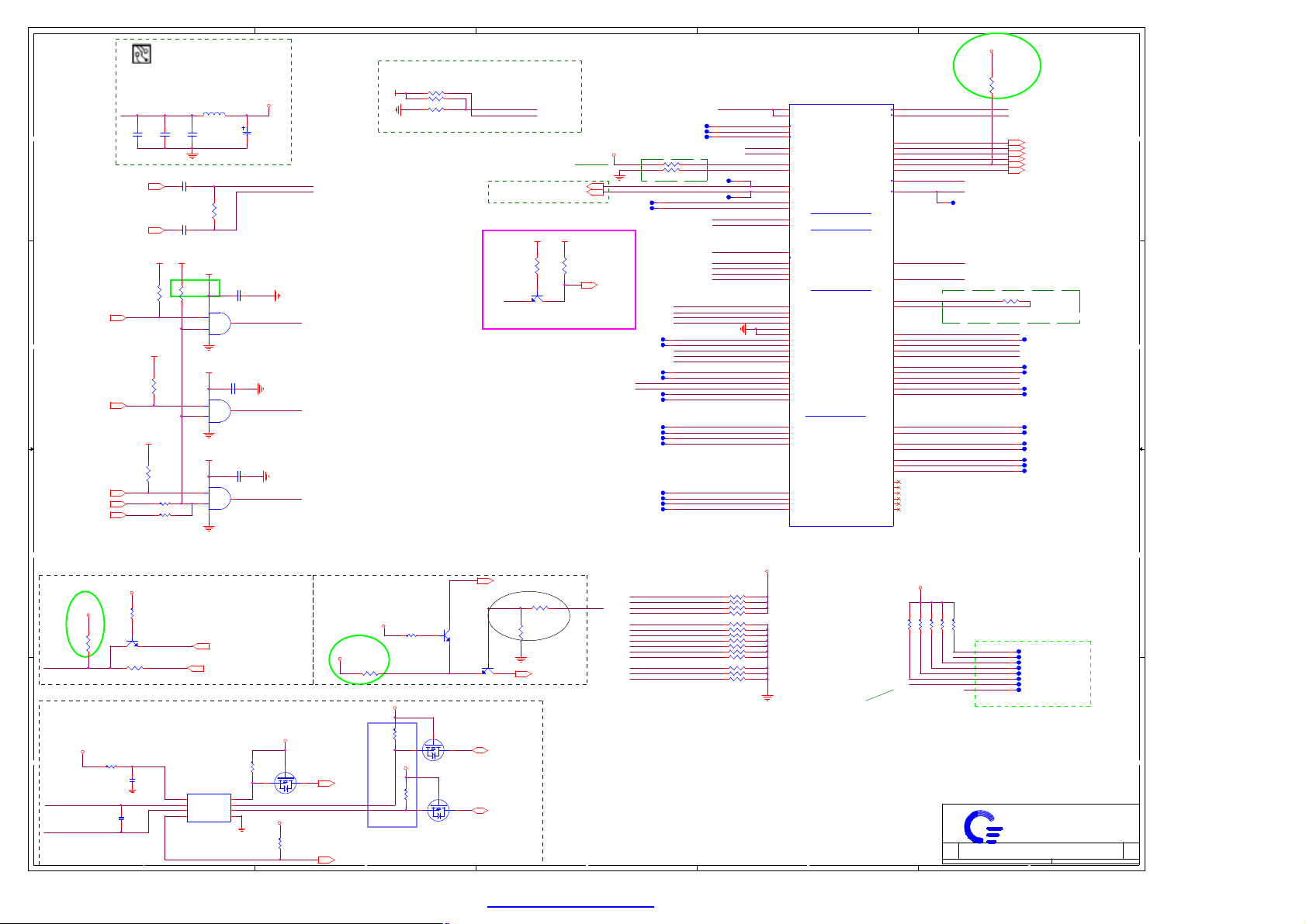

Page 1

1

PCB P/N AND DESCRIPTION

PCB ED5 MB(8L,309X218, REVA)

P/N: DA0ED5MB8A8

PCB ED5 MB(8L,309X218,REVB)

P/N: DA0ED5MB8B6

AA

PCB ED5 USB/B(8L, 47.5X16.8, REVA)

P/N: DA0ED5SB8A5

PCB ED5 USB/B(8L,47.5X16.8,REVB)

P/N: DA0ED5SB8B3

DDRII-SODIMM1

DDRII-SODIMM2

PG 7,8

Panel Connector

BB

S-Video

VGA

SATA - HDD

PG 20

PG 20

PG 20

2

3

ED5

4

SATAPATA

ED5 SATA ASSY P/N

ED5 MB S/S ASSY P/N: 51ED5SS0018

ED5 MB C/S ASSY P/N: 41ED5CS0015

ED5 MB ASSY P/N: 31ED5MB0012

ED5 USB/B S/S ASSY P/N: 4NED5SS0011

ED5 USB/B ASSY P/N: 3NED5UB0011

5

6

ED5 ASSY P/N

ED5 MB S/S ASSY P/N: 51ED5SS0000

ED5 MB C/S ASSY P/N: 41ED5CS0007

ED5 MB ASSY P/N: 31ED5MB0004

ANTW/O ANT

ED5 USB/B S/S ASSY P/N: 4NED5SS0002

ED5 USB/B ASSY P/N: 3NED5UB0003

7

VCC_CORE

+1.2V

+VCCP

8

CPU VR

+1.2V

+VCCP

PG 30

PG 31

533/ 667 MHZ DDR IIPG 7,8

LVDS

TVOUT

VGA

SATA0

AMD S1

Turion 64 Rev.F Dual-Core/

Sempron Rev.F Single-Core

Dual-Core 35W / Single-Core 25W

(638 S1g1 socket)

PG 3,4,5,6

HT_LINK

RS485

465 FCBGA

PG 9,10,11,12

A_LINK

PG 19PG 19

HOST 133/166MHz

PCIE 100MHz

VGA 96MHz

USB 48MHz

REF 14MHz

PCI-E, 1X

PCI-E, 1X

PCI-E, 1X

PCI-E, 1X

CLOCK GENERATOR

ICS951462

PG 13

Express Card

PCIE1 & USB4

Mini PCI-E Card (WLAN)

PCIE2

Mini PCI-E Card (TV)

PCIE3 &

USB5

LAN

RTL8111B-GR

PCIE0

NEW CARD

PCI Express Mini Card

PCI Express Mini Card

PG 23

PG 24

PG 19

PG 19

+1.8VSUS

+1.8V

SMDDR_VTERM

+3VPCU

+3V_S5

+3VSUS

+5VSUS

+5V

+12V

VIN

WIRE

RJ45Magnetics

+1.8VSUS

SMDDR

VTERM

PG 32

3V/5V

PG 33

CHARGER

PG 34

PG 21

PATA - HDD

PATA 100

SB460

PG 21

549 BGA

CC

Internal ODD

CD-ROM

PG 21

Azalia

USB2.0 (P0~P7)

PCI Bus 33MHz

Bluetooth

USB7

USB2.0 I/O Ports

USB0 &

USB1

DSC USB I/F

USB6

PG 22

PG 22

PG 22

B/B CN.

USB2 &

USB3

PG 22

ANTENNA JACK

USB2.0 I/O

USB DAUGHTERBOARD

Azalia Audio

PG 26

LPC

PG 14,15,16,17

KBC

Amplifier

MAX9755A

DD

MIC.

PG 27

INT.

S.P.

PG 27PG 27

1

PG 27

H.P

Azalia MDC

PG 26

MODEM

RJ 11

PG 23

2

3

K/B

CONN.

PG 29

NS97551

Touch

Pad

PG 29

X-Bus

4

PG 28

Flash

ROM

PG 28

SWITCH

LED

PG 29

5

TI PCI8402

AD17

REQ3#, GNT3#

INTE#, INTG#, INTH#

Card Reader

PG 25

6

PG 24,25

IEEE1394 CN.

PG 25

SizeDocument NumberRev

Date:Sheet of

MINI PCI CN.

AD20

REQ2#, GNT2#

INTF#, INTG#

DEBUG PURPOSE ONLY

Quanta Computer Inc.

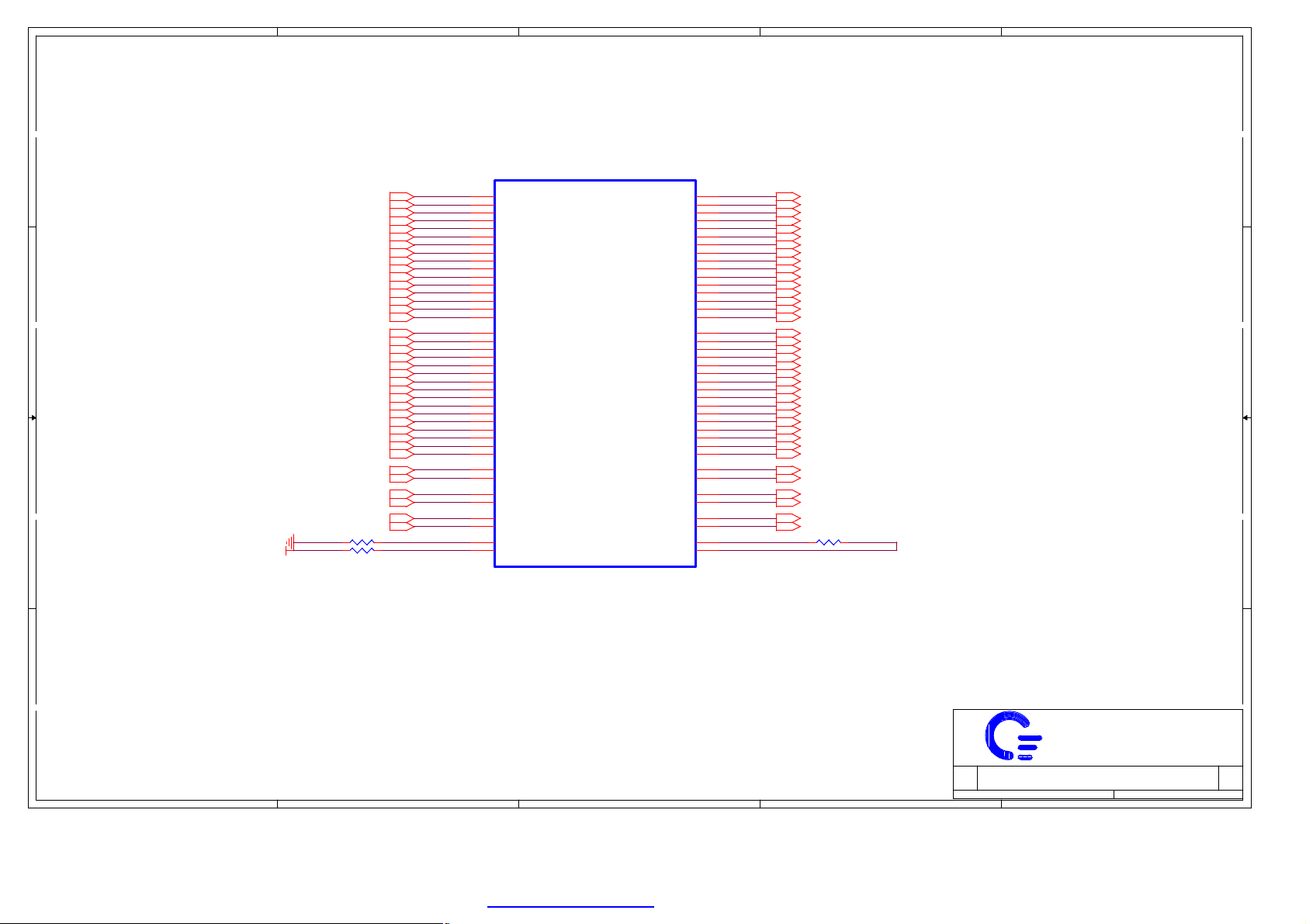

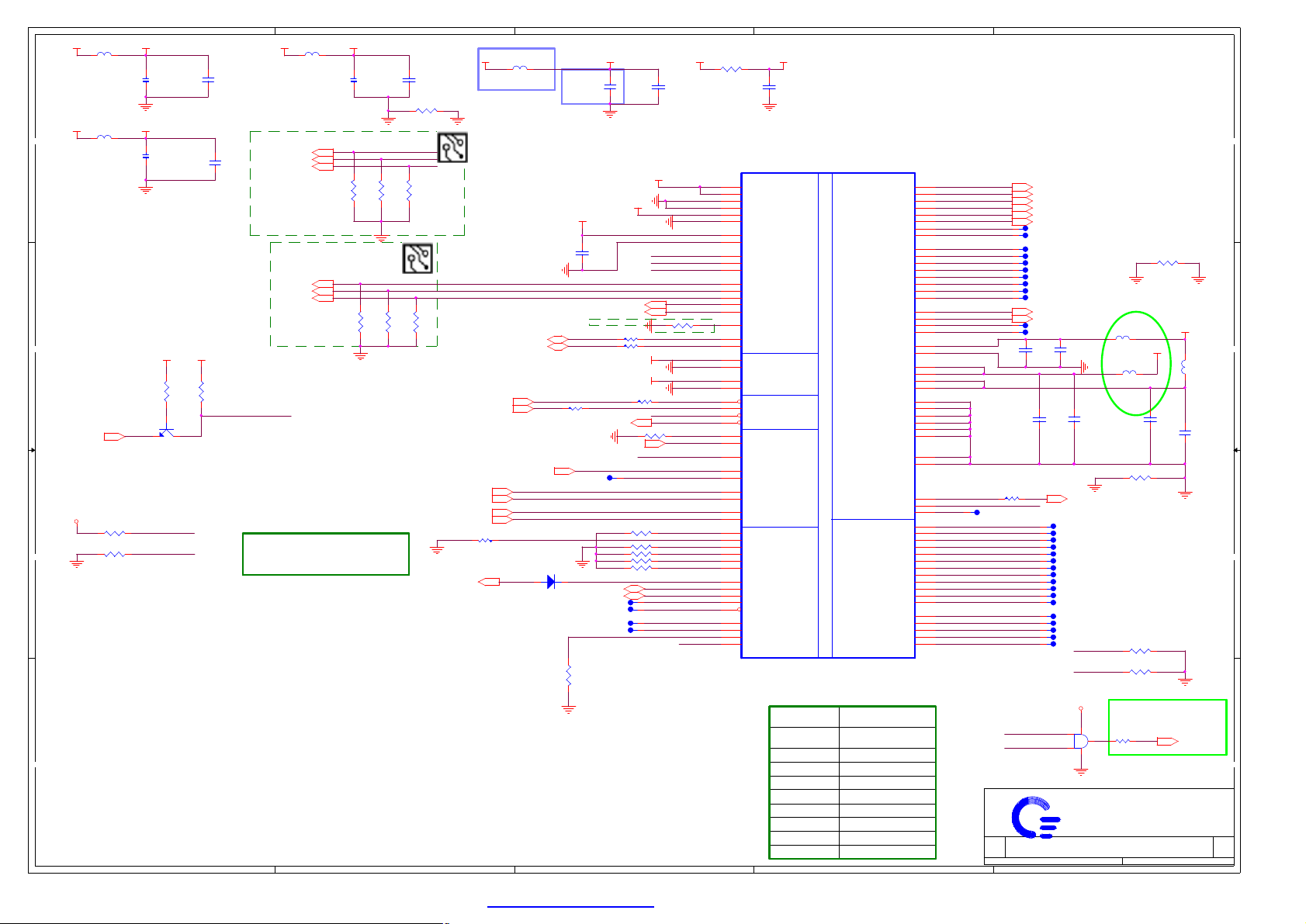

BLOCK DIAGRAM

7

PROJECT : ED5

134Monday, May 22, 2006

PG 18

1A

8

PDF created with FinePrint pdfFactory Pro trial version www.pdffactory.com

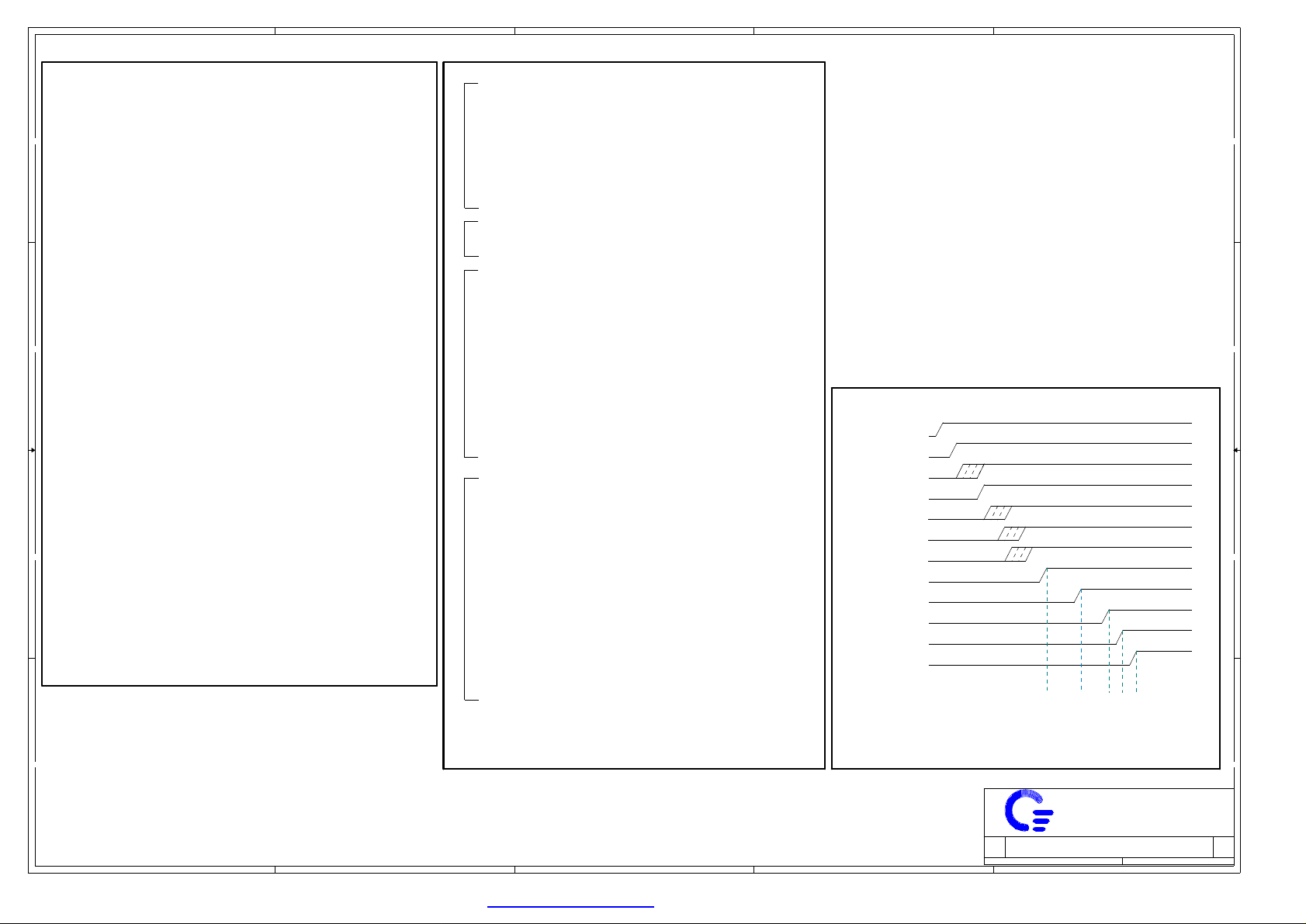

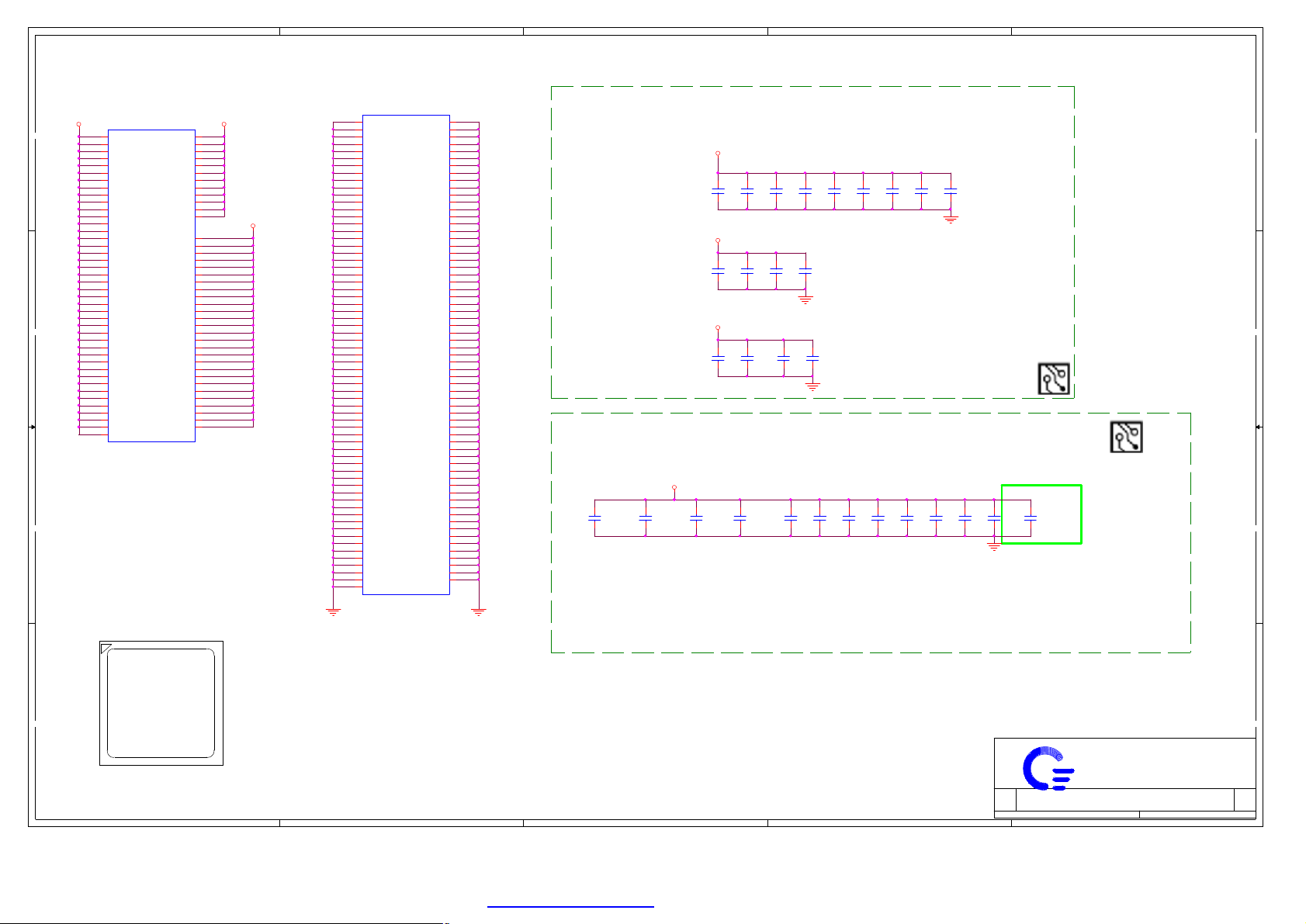

Page 2

5

4

3

2

1

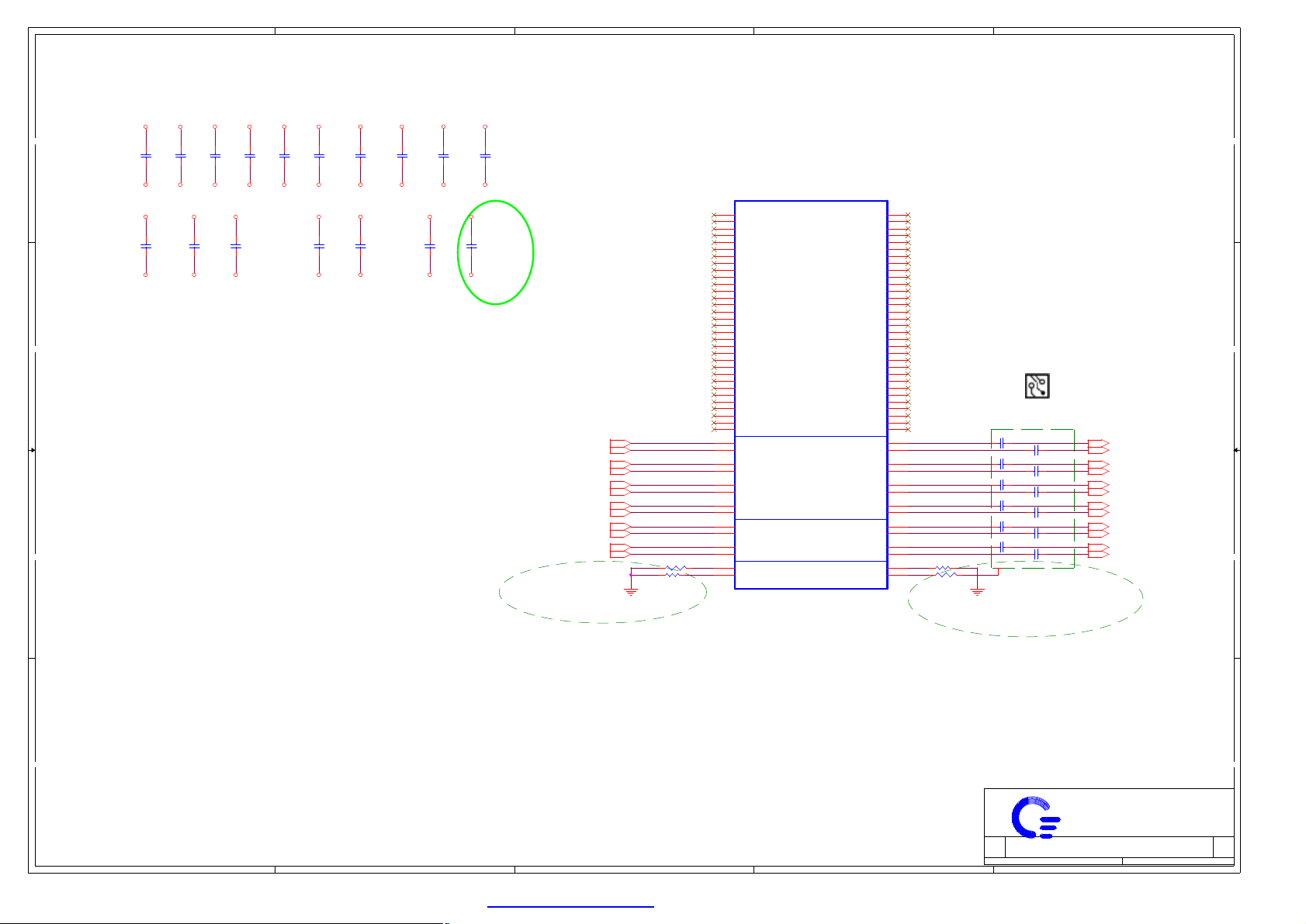

TABLE OF CONTENTS

Page 01 : BLOCK DIAGRAM

Page 02 : TABLE OF CONTENTS

Page 03 : ATHLON64 HT I/F

Page 04 : ATHLON64 DDRII MEMORY

I/F

Page 05 : ATHLON64 CTRL & DEBUG

DD

Page 06 : ATHLON64 PWR & GND

Page 07 : DDRII SODIMMX2

Page 08 : DDRII TERMINATION

Page 09 : RS485-HT LINK0

I/F

Page 10 : RS485-PCIE LINK I/F

Page 11 : RS485-SYSTEM I/F & CLKGEN

Page 12 : RS485-POWER

Page 13 : CLOCK GENERATOR

Page 14 : SB460M-PCIE/PCI/CPU/LPC

Page 15 : SB460M ACPI/GPIO/USB/AC97

Page 16 : SB460M HDD/POWER/DECOUPLI

Page 17 : SB460M STRAPS

Page 18 : MINI PCI

Page 19 : MINI CARD TV & WLAN

Page 20 : CRT&LVDS&S-VIDE0&DCS

CC

Page 21 : HDD & CDROM , HOLES

Page 22 : USB, BLUETOOTH

Page 23 : LAN PCI-E RJ45 & RJ11

Page 24 : PCI8402_1 & NEW CARD

Page 25 : PCI8402_2 (1394/5IN1)

Page 26 : AUDIO(ALC262) & MDC

Page 27 : AUDIO(AMP&POWER&HP CON)

Page 28 : PC97551 & FLASH

Page 29 : LED & SW & KB & TP & FAN

Page 30 : CPU CORE MAX8774

Page 31 : 1.2V/1.5V/2.5V

Page 32 : 1.8V/DDRII

Page 33 : SYSTEM 3V/5V

Page 34 : BATTERY CHARGER

BB

POWERVOLTAGEACTIVE SCOPE

+12V

-12V

+5V

+3.3V

+5VALW

+3.3VALW

SYSTEMRC485

+1.8VALW

+5V_DUAL

+3.3V_DUAL

VCCCORE

VCCP

CPU

VCCA

VCC_NB

VDD_CPU

VDD_MEM

VDD18

VDDA18

VDDA12

AVDD

NB

AVDDQ

PLVDD

LPVDD

LVDDR

VDDR3

VTT_DDR

VDD_CLK

+3.3V_SB

+1.8V_SB

+3.3VALW_SB

+1.8VALW_SB

+1.8V_SUB_PHY

AVDD_CK

V5_REF

CPU-PWR

PCIE_PVDD

PCIE_VDDR

SB460 SB

+1.8V_ATA

PLLVDD_ATA

XTLVDD_ATA

AVDD_USB_TX

AVDD_USB_RX

+3.3V_AVDDC

V_BAT

+12V

-12V

+5V

+3.3V

+5V

+3.3V

+2.5VS0-S5TRACE 30 MIL21

+5V

+3.3V

VID[0..6]

+1.05V

+1.5VOFF IN S3-S5TRACE 20 MIL

+1.2V/1.0V

+1.05V

+1.8V

+1.8VOFF IN S3-S5TRACE 20 MIL12

+3.3V

+1.8V

+1.8V

+1.8V

+1.8V

+3.3V

+1.8V21PLANEOFF IN S3-S5

+3.3V

+1.8V

+1.8V

+1.8V21OFF IN S3-S5

+5V21OFF IN S3-S5

+1.05V21OFF IN S3-S5

+1.8V18OFF IN S3-S5

+1.8V18PLANE+COPEROFF IN S3-S5

+1.8V20PLANEOFF IN S3-S5

+1.8V20OFF IN S3-S5

+1.8V20OFF IN S3-S5

+1.8V19PLANE+COPERS0-S5

+1.8V19PLANE+COPERS0-S5

+3.3V19S0-S5

+3.0V--TRACE 10 MIL18

OFF IN S3-S5

OFF IN S3-S5

OFF IN S3-S5

OFF IN S3-S5

S0-S5

S0-S5

S0-S5

S0-S5

OFF IN S3-S5

OFF IN S3-S5

OFF IN S3-S5

OFF IN S3-S5PLANE+COPER38

S0-S3

OFF IN S3-S512

OFF IN S3-S512

OFF IN S3-S5

OFF IN S3-S5

OFF IN S3-S5

OFF IN S3-S5

OFF IN S3-S5TRACE 30 MIL11

OFF IN S3-S5

OFF IN S3-S5

OFF IN S3-S5

OFF IN S3-S5

S0-S5PLANE21

S0-S5

S0-S5

ROUTING

PLANE

TRACE 20 MIL

PLANE

PLANE

PLANE/ 50 MIL

TRACE 30 MIL

PLANE/ 100 MIL

PLANE/ 50 MIL

PLANE+COPER

PLANE+COPER

PLANE+COPER

PLANE+COPER

COPPER+1.8V

PLANE+COPPER+1.2V

TRACE 20 MIL

TRACE 20 MIL

TRACE 20 MIL

TRACE 20 MIL11

TRACE 30 MIL

PLANE

PLANE

TRACE 30 MIL

TRACE 10 MIL

TRACE 10 MIL

TRACE 20 MIL

TRACE 20 MIL

TRACE 20 MIL

TRACE 20 MIL

TRACE 20 MIL

PAGE

41

41

41

41

41

41

41

41

37

38

38

39

40

11

11

11

11+3.3V

40+0.9VCOPPER

14+3.3VCOPPER

PS_ON, SLP_S3#, SLP_S5#

21

21

21

+5VALW

RSMRST#

+12V,5V,3.3V

VDRM_PWRGD

VCC_NB_PWRGD

VRM_PWRGD

NB_PWRGD

SB_PWRGD

CPU_PWRGD

PCI_RST#

CPU_RST#

BONEFISH POWER UP SEQUENCE

T2

T1>= 70 ms

1ms < T2 < 10ms

1ms < T3 < 5ms

T3T1

AA

PROJECT : ED5

Quanta Computer Inc.

SizeDocument NumberRev

BLOCK DIAGRAM

5

4

3

2

Date:Sheet of

234Monday, May 22, 2006

1

1A

PDF created with FinePrint pdfFactory Pro trial version www.pdffactory.com

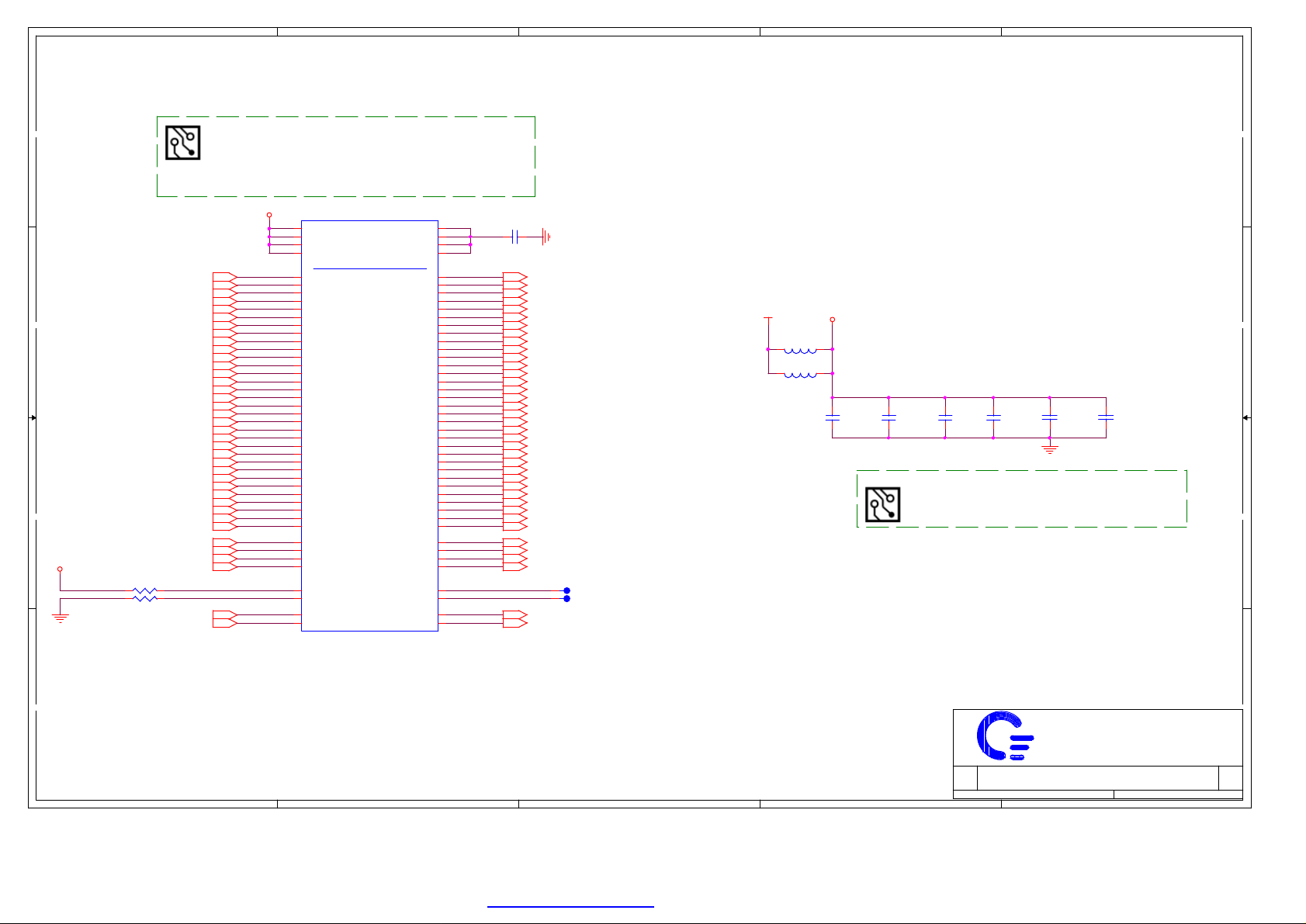

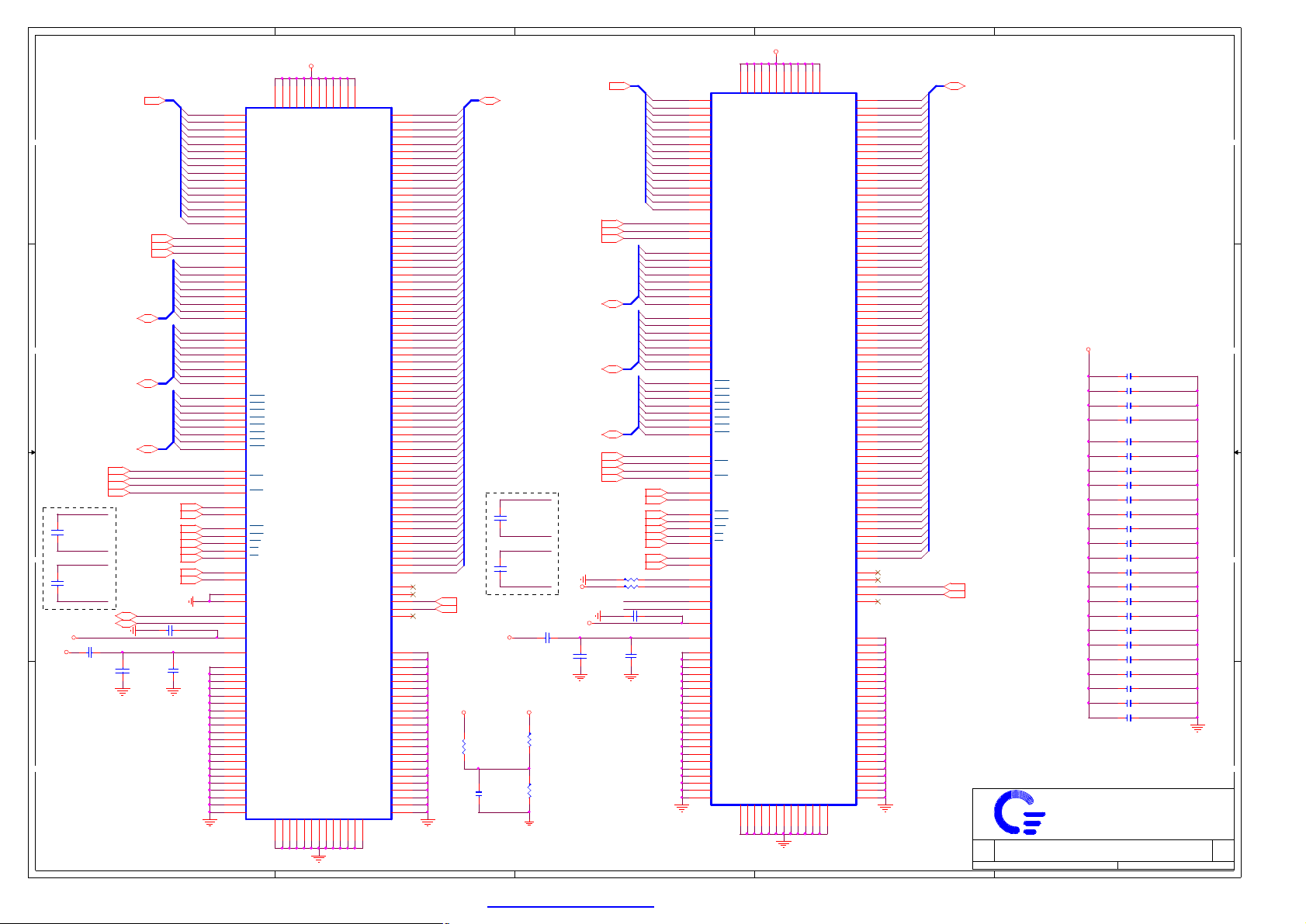

Page 3

5

4

3

2

1

DD

HT_CADIN15_P(9)

HT_CADIN15_N(9)

HT_CADIN14_P(9)

HT_CADIN14_N(9)

HT_CADIN13_P(9)

CC

BB

VLDT_RUN

HT_CADIN13_N(9)

HT_CADIN12_P(9)

HT_CADIN12_N(9)

HT_CADIN11_P(9)

HT_CADIN11_N(9)

HT_CADIN10_P(9)

HT_CADIN10_N(9)

HT_CADIN9_P(9)

HT_CADIN9_N(9)

HT_CADIN8_P(9)

HT_CADIN8_N(9)

HT_CADIN7_P(9)

HT_CADIN7_N(9)

HT_CADIN6_P(9)

HT_CADIN6_N(9)

HT_CADIN5_P(9)

HT_CADIN5_N(9)

HT_CADIN4_P(9)

HT_CADIN4_N(9)

HT_CADIN3_P(9)

HT_CADIN3_N(9)

HT_CADIN2_P(9)

HT_CADIN2_N(9)

HT_CADIN1_P(9)

HT_CADIN1_N(9)

HT_CADIN0_P(9)

HT_CADIN0_N(9)

HT_CLKIN1_P(9)

HT_CLKIN1_N(9)

HT_CLKIN0_P(9)

HT_CLKIN0_N(9)

R7649.9/F

R80

49.9/F

HT_CTLIN0_P(9)

HT_CTLIN0_N(9)

PROCESSOR HYPERTRANSPORT INTERFACE

VLDT_Ax AND VLDT_Bx ARE CONNECTED TO THE LDT_RUN POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

VLDT_RUN

U21A

D4

VLDT_A3

D3

VLDT_A2

D2

VLDT_A1

D1

VLDT_A0

N5

L0_CADIN_H15

P5

L0_CADIN_L15

M3

L0_CADIN_H14

M4

L0_CADIN_L14

L5

L0_CADIN_H13

M5

L0_CADIN_L13

K3

L0_CADIN_H12

K4

L0_CADIN_L12

H3

L0_CADIN_H11

H4

L0_CADIN_L11

G5

L0_CADIN_H10

H5

L0_CADIN_L10

F3

L0_CADIN_H9

F4

L0_CADIN_L9

E5

L0_CADIN_H8

F5

L0_CADIN_L8

N3

L0_CADIN_H7

N2

L0_CADIN_L7

L1

L0_CADIN_H6

M1

L0_CADIN_L6

L3

L0_CADIN_H5

L2

L0_CADIN_L5

J1

L0_CADIN_H4

K1

L0_CADIN_L4

G1

L0_CADIN_H3

H1

L0_CADIN_L3

G3

L0_CADIN_H2

G2

L0_CADIN_L2

E1

L0_CADIN_H1

F1

L0_CADIN_L1

E3

L0_CADIN_H0

E2

L0_CADIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

Athlon 64 S1

Processor Socket

VLDT_B3

VLDT_B2

VLDT_B1

VLDT_B0

AE5

AE4

AE3

AE2

T4

T3

V5

U5

V4

V3

Y5

W5

AB5

AA5

AB4

AB3

AD5

AC5

AD4

AD3

T1

R1

U2

U3

V1

U1

W2

W3

AA2

AA3

AB1

AA1

AC2

AC3

AD1

AC1

Y4

Y3

Y1

W1

T5

R5

R2

R3

HT_CPU_CTLOUT1_PHT_CTLIN1_P

HT_CPU_CTLOUT1_NHT_CTLIN1_N

C118

4.7U/6.3V_6

HT_CADOUT15_P(9)

HT_CADOUT15_N(9)

HT_CADOUT14_P(9)

HT_CADOUT14_N(9)

HT_CADOUT13_P(9)

HT_CADOUT13_N(9)

HT_CADOUT12_P(9)

HT_CADOUT12_N(9)

HT_CADOUT11_P(9)

HT_CADOUT11_N(9)

HT_CADOUT10_P(9)

HT_CADOUT10_N(9)

HT_CADOUT9_P(9)

HT_CADOUT9_N(9)

HT_CADOUT8_P(9)

HT_CADOUT8_N(9)

HT_CADOUT7_P(9)

HT_CADOUT7_N(9)

HT_CADOUT6_P(9)

HT_CADOUT6_N(9)

HT_CADOUT5_P(9)

HT_CADOUT5_N(9)

HT_CADOUT4_P(9)

HT_CADOUT4_N(9)

HT_CADOUT3_P(9)

HT_CADOUT3_N(9)

HT_CADOUT2_P(9)

HT_CADOUT2_N(9)

HT_CADOUT1_P(9)

HT_CADOUT1_N(9)

HT_CADOUT0_P(9)

HT_CADOUT0_N(9)

HT_CLKOUT1_P(9)

HT_CLKOUT1_N(9)

HT_CLKOUT0_P(9)

HT_CLKOUT0_N(9)

HT_CTLOUT0_P(9)

HT_CTLOUT0_N(9)

+1.2V

FBJ3216HS800

FBJ3216HS800

80 ohm(4A)

VLDT_RUN

L58

L57

C105

4.7U/6.3V_6

C104

4.7U/6.3V_6

C110

.22U/6V_4

C116

.22U/6V_4

12

C108

10P_4

12

C112

10P_4

LAYOUT: Place bypass cap on topside of board

NEAR HT POWER PINS THAT ARE NOT CONNECTED DIRECTLY

TO DOWNSTREAM HT DEVICE, BUT CONNECTED INTERNALLY

TO OTHER HT POWER PINS

PLACE CLOSE TO VLDT0 POWER PINS

T29

T30

AA

PROJECT : ED5

Quanta Computer Inc.

SizeDocument NumberRev

ATHLON64 HT I/F

5

4

3

2

Date:Sheet of

334Monday, May 22, 2006

1

1A

PDF created with FinePrint pdfFactory Pro trial version www.pdffactory.com

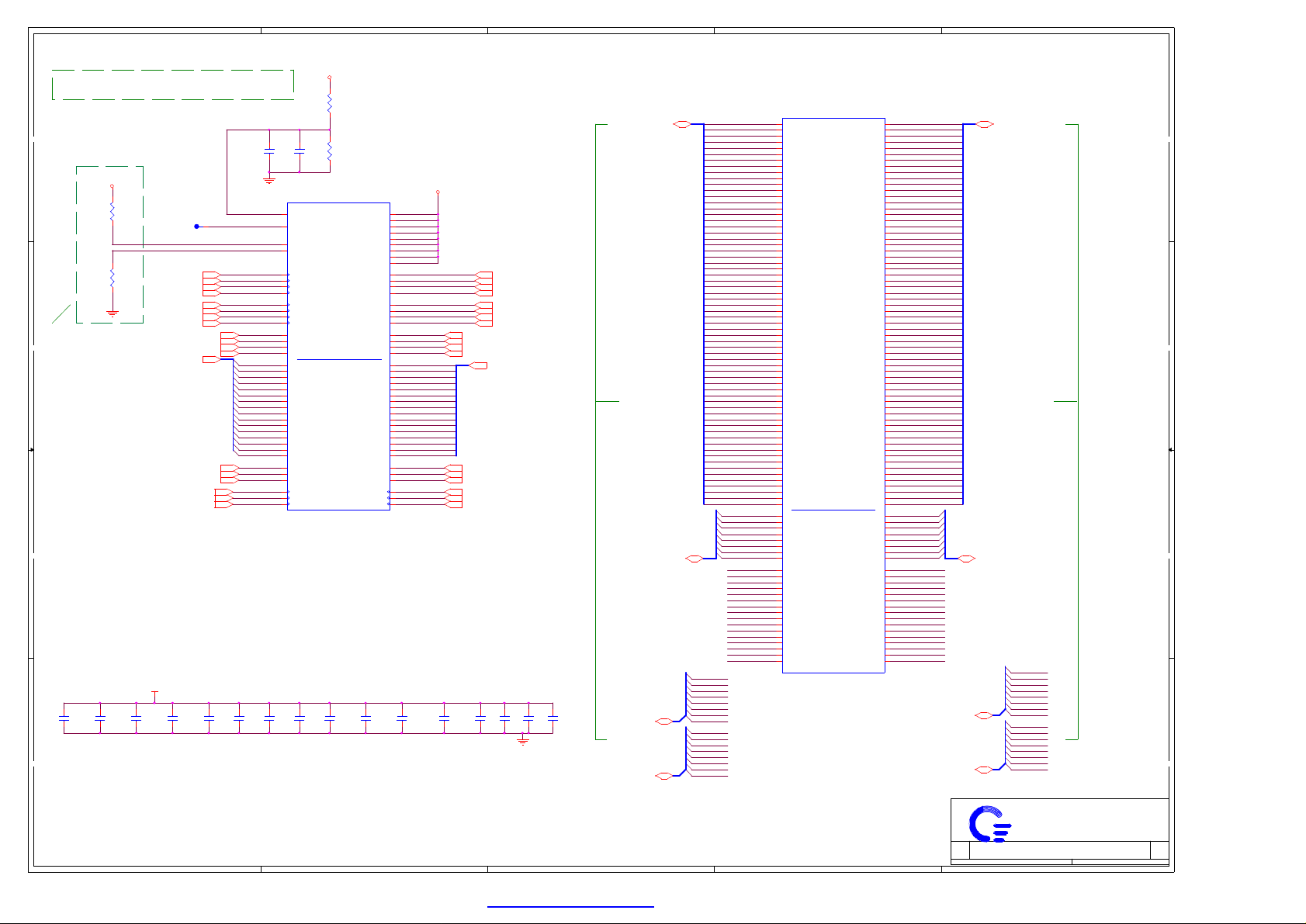

Page 4

A

B

C

D

E

C180

.1U_4

W17

Y10

V19

J22

V22

T19

Y26

J24

W24

U23

H26

J23

J20

J21

K19

K20

V24

K24

L20

R19

L19

L22

L21

M19

M20

M24

M22

N22

N21

R21

K22

R20

T22

T20

U20

U21

C148

.22U/6V_4

C181

1000p/50V_4

U21B

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MA0_CS_L3

MA0_CS_L2

MA0_CS_L1

MA0_CS_L0

MB0_CS_L3

MB0_CS_L2

MB0_CS_L1

MB0_CS_L0

MB_CKE1

MB_CKE0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

C135

.22U/6V_4

+1.8VSUS

R140

2K/F

R141

2K/F

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_ODT1

MB0_ODT0

MA0_ODT1

MA0_ODT0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

MB_WE_L

DDR II: CMD/CTRL/CLK

Athlon 64 S1

Processor Socket

C137

1000p/50V_4

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

C153

1000p/50V_4

D10

C10

B10

AD10

W10

AC10

AB10

AA10

A10

Y16

AA16

E16

F16

AF18

AF17

A17

A18

W23

W26

V20

U19

J25

J26

W25

L23

L25

U25

L24

M26

L26

N23

N24

N25

N26

P24

P26

T24

K26

T26

U26

U24

V26

U22

+0.9V_VTER

M_B_A15

M_B_A14

M_B_A13

M_B_A12

M_B_A11

M_B_A10

M_B_A9

M_B_A8

M_B_A7

M_B_A6

M_B_A5

M_B_A4

M_B_A3

M_B_A2

M_B_A1

M_B_A0

C154

1000p/50V_4

M_ODT3(7,8)

M_ODT2(7,8)

M_ODT1(7,8)

M_ODT0(7,8)

M_B_BS#2(7,8)

M_B_BS#1(7,8)

M_B_BS#0(7,8)

M_B_RAS#(7,8)

M_B_CAS#(7,8)

M_B_WE#(7,8)

C144

1000p/50V_4

M_CLKOUT1(7)

M_CLKOUT1#(7)

M_CLKOUT0(7)

M_CLKOUT0#(7)

M_CLKOUT4(7)

M_CLKOUT4#(7)

M_CLKOUT3(7)

M_CLKOUT3#(7)

M_B_A[0..15](7,8)

C134

C136

180P_4

180P_4

C147

180P_4

C138

180P_4

Processor DDR2 Memory Interface

M_B_DQ[0..63](7)

To SODIMM socket B

(Far)

M_B_DM[0..7](7) M_A_DM[0..7](7)

M_B_DQS[0..7](7)

M_B_DQS#[0..7](7)

M_B_DQ63

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQ48

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ0

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DM7

M_B_DM6

M_B_DM5

M_B_DM4

M_B_DM3

M_B_DM2

M_B_DM1

M_B_DM0

M_B_DQS7

M_B_DQS#7

M_B_DQS6

M_B_DQS#6

M_B_DQS5

M_B_DQS#5

M_B_DQS4

M_B_DQS#4

M_B_DQS3

M_B_DQS#3

M_B_DQS2

M_B_DQS#2

M_B_DQS1

M_B_DQS#1

M_B_DQS0

M_B_DQS#0

AD11

AF11

AF14

AE14

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

AD12

AC16

AE22

AB26

AF12

AE12

AE16

AD16

AF21

AF22

AC25

AC26

Y11

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

E25

A22

B16

A12

F26

E26

A24

A23

D16

C16

C12

B12

U21C

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

DDR: DATA

Athlon 64 S1

Processor Socket

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

AA12

AB12

AA14

AB14

W11

Y12

AD13

AB13

AD15

AB15

AB17

Y17

Y14

W14

W16

AD17

Y18

AD19

AD21

AB21

AB18

AA18

AA20

Y20

AA22

Y22

W21

W22

AA21

AB22

AB24

Y24

H22

H20

E22

E21

J19

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

Y13

AB16

Y19

AC24

F24

E19

C15

E12

W12

W13

Y15

W15

AB19

AB20

AD23

AC23

G22

G21

C22

C21

G16

G15

G13

H13

M_A_DQ63

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ38

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ22

M_A_DQ21

M_A_DQ20

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ10

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ0

M_A_DM7

M_A_DM6

M_A_DM5

M_A_DM4

M_A_DM3

M_A_DM2

M_A_DM1

M_A_DM0

M_A_DQS7

M_A_DQS#7

M_A_DQS6

M_A_DQS#6

M_A_DQS5

M_A_DQS#5

M_A_DQS4

M_A_DQS#4

M_A_DQS3

M_A_DQS#3

M_A_DQS2

M_A_DQS#2

M_A_DQS1

M_A_DQS#1

M_A_DQS0

M_A_DQS#0

M_A_DQS[0..7](7)

M_A_DQS#[0..7](7)

M_A_DQ[0..63](7)

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

To SODIMM socket A

(near)

VDD_VTT_SUS_CPU IS CONNECTED TO THE VDD_VTT_SUS POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

44

+1.8VSUS

R363

39.2F

1 2

R365

39.2F

1 2

PLACE THEM CLOSE TO

CPU WITHIN 1"

33

22

C150

C157

4.7U/6.3V_6

4.7U/6.3V_6

11

+0.9V_VTER

C132

4.7U/6.3V_6

M_A_CS#3(7,8)

M_A_CS#2(7,8)

M_A_CS#1(7,8)

M_A_CS#0(7,8)

M_B_CS#3(7,8)

M_B_CS#2(7,8)

M_B_CS#1(7,8)

M_B_CS#0(7,8)

M_A_A[0..15](7,8)

C151

4.7U/6.3V_6

CPU_M_VREF

VTT_SENSE

T45

M_ZN

M_ZP

M_CKE3(7,8)

M_CKE2(7,8)

M_CKE1(7,8)

M_CKE0(7,8)

M_A_BS#2(7,8)

M_A_BS#1(7,8)

M_A_BS#0(7,8)

M_A_RAS#(7,8)

M_A_CAS#(7,8)

M_A_WE#(7,8)

C133

.22U/6V_4

M_A_A15

M_A_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

C145

.22U/6V_4

AE10

AF10

A

B

C

PDF created with FinePrint pdfFactory Pro trial version www.pdffactory.com

PROJECT : ED5

SizeDocument NumberRev

ATHLON64 DDRII MEMORY I/F

D

Date:Sheet of

Quanta Computer Inc.

E

434Monday, May 22, 2006

1A

Page 5

5

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

CPU_VDDA_RUN

C127

.22U/6V_4

C4893900p/25V

C4883900p/25V

+1.8V +3V

L27BLM18PG330SN1D

C131

3900p/25V

+1.8VSUS

R348

*4.7K/F_4

5

1

2

3

+1.8VSUS

5

1

2

3

+1.8VSUS

5

1

2

3

CPU_EC_PROCHOT#(28)

CPU_PROCHOT#(15)

CPU_VDDA_RUN

MMBT3904

C163

4.7U/6.3V_6

CPUCLK(13)

CPUCLK#(13)

R350

300_4

+1.8V

R114

300_4

+1.8V

R346

300_4

R342*0_4

R3430_4

+1.8V

R70

330_4

Q10

2

13

R72

*0_4

DD

CPU_PWRGD(14,15)

CC

LDT_STOP#(11,14,15)

LDT_RST#(14)

EC_PWRGD(14,15,28)

NB_PWRGD(11,28)

BB

+1.8VSUS

R73

300_4

H_PROCHOT#

+2.5V

C490

100U/6.3V_3528

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

R366

169F

ECN 2A

Remove R348 for Power sequence

C487.1U_4

CPU_ALL_PWROK

4

U20

NC7SZ08P5X_NL

C161.1U_4

CPU_LDTSTOP#

4

U9

NC7SZ08P5X_NL

C484.1U_4

CPU_HT_RESET#

4

U19

NC7SZ08P5X_NL

CPU H/W MONITOR

6

7

8

KBSMDATCPU_TEST5_THERMDC

KBSMCLK

+3V

R340

10K_4

1

Q232N7002E-LF

+3V

10K_4

2

R345

To SB GPIO

3

To FAN

AA

+3V

CPU_TEST4_THERMDA

10 mil trace /

10 mil space

R34147/F_6

15 MIL

3V_THM

C477

.1U_4

C479

2200P/50V_4

5

Address 98H

U17G781

1

VCC

-ALT

3

DXN

SMDATA

2

DXP

SMCLK

4 5

-OVTGND

+1.8VSUS

MAX6648_AL#(15)

MAX6648_OV#(29)

4

If AMD SI is not used, the SID pin can be left unconnected and SIC

should have a 300-Ω (± 5%) pulldown to VSS.

R351*300

+1.8V

R349*300

R347300_4

CPU_SIC_R

CPU_SID_R

place them to CPU within 1"

To Power

D3A:Add LEVEL-SHIFT circuit on PSI# that between

CPU and POWER

PSI#

SB_THERMTRIP#(15)

separated input voltage

0104

+1.8V

ECN E3B

Change from 10k

to 4.7k

4

R78*330_4

H_THERMTRIP#

+3V

R338

4.7K/F_4

+3V

1

R339

4.7K/F_4

1

2

2

Q21

2N7002E-LF

2

Q11

*MMBT3904

1 3

3

Q22

2N7002E-LF

3

Q12

2

MMBT3904

1 3

MBDATA_CPU(28)

MBCLK_CPU(28)

R86

4.7K/F_4

3

ATHLON Control and Debug

COREFB+V(30)

COREFB-(30)

+1.8V +3V

R545

10K_4

2

1 3

Q39

MMBT3904

R90

4.7K/F_4

THERM_SYS_PWR(33)

R546

1K/F_4

EC_PWRGD

VLDT_RUN

PWR_PSI#(30)

3

R7544.2F

R7444.2F

CPU_VDDIO_SUS_FB_H

T21

CPU_VDDIO_SUS_FB_L

T23

T37

T35

T26

T20

T19

T112

T50

T58

T55

T56 T28

T57

T52

T53

T54

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN#

CPU_PRESENT#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_VDDA_RUN

CPU_HT_RESET#

T110

CPU_ALL_PWROK

T111

CPU_LDTSTOP#

T46

T109

T22

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST17_BP3

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

CPU_TEST07_ANALOG_T

CPU_TEST6_DIECRACKMON

CPU_TEST5_THERMDC

CPU_TEST4_THERMDA

CPU_TEST3_GATE0

CPU_TEST2_DRAIN0

CPU_RSVD_MA0_CLK3_P

CPU_RSVD_MA0_CLK3_N

CPU_RSVD_MA0_CLK0_P

CPU_RSVD_MA0_CLK0_N

CPU_RSVD_MB0_CLK3_P

CPU_RSVD_MB0_CLK3_N

CPU_RSVD_MB0_CLK0_P

CPU_RSVD_MB0_CLK0_N

R359300_4

R352300_4

R3541K/F_4

R87510/F_4

R356300_4

R353300_4

R355300_4

R357300_4

R358300_4

R91300_4

R85300_4

R82510/F_4

R89300_4

R123300_4

2

U21D

F8

VDDA2

F9

VDDA1

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

CPU_SIC_R

AF4

SIC

CPU_SID_R

AF5

SID

P6

CPU_HTREF1

HT_REF1

R6

CPU_HTREF0

HT_REF0

F6

VDD_FB_H

E6

VDD_FB_L

W9

VDDIO_FB_H

Y9

VDDIO_FB_L

A9

CLKIN_H

A8

CLKIN_L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9 AE9

TDITDO

E9

TEST25_H

E8

TEST25_L

G9

TEST19

H10

TEST18

AA7

TEST13

C2

TEST9

D7

TEST17

E7

TEST16

F7

TEST15

C7

TEST14

AC8

TEST12

C3

TEST7

AA6

TEST6

W7

TEST5

W8

TEST4

Y6

TEST3

AB6

TEST2

P20

RSVD0

P19

RSVD1

N20

RSVD2

N19

RSVD3

MISC

R26

RSVD4

R25

RSVD5

P22

RSVD6

R22

RSVD7

AMD NPT S1 SOCKET

Processor Socket

+1.8VSUS

IF no use which Net

need pull-up or down

NOTE: HDT TERMINATION IS REQUIRED

FOR REV. Ax SILICON ONLY.

2

THERMTRIP_L

PROCHOT_L

CPU_PRESENT_L

PSI_L

DBREQ_L

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

+1.8VSUS

R81

300_4

AF6

H_THERMTRIP#

H_PROCHOT#

AC7

A5

VID5

C6

VID4

A6

VID3

A4

VID2

C5

VID1

B5

VID0

CPU_PRESENT#

AC6

PSI#

A3

PSI_L is a Power Status Indicator signal. This signal is asserted

T27

when the processor is in a low powerstate. PSI_L should be

connected to the power supply controller, if the controller

supports “skipmode, or diode emulation mode ”. PSI_L is asserted by

the processor during the C3 and S1 states.

CPU_DBREQ#

E10

CPU_TDO

CPU_TEST29_H_FBCLKOUT_P

C9

CPU_TEST29_L_FBCLKOUT_N

C8

CPU_TEST24_SCANCLK1

AE7

CPU_TEST23_TSTUPD

AD7

CPU_TEST22_SCANSHIFTEN

AE8

CPU_TEST21_SCANEN

AB8

CPU_TEST20_SCANCLK2

AF7

CPU_TEST28_H_PLLCHRZ_P

J7

CPU_TEST28_L_PLLCHRZ_N

H8

CPU_TEST27_SINGLECHAIN

AF8

CPU_TEST26_BURNIN#

AE6

CPU_TEST10_ANALOGOUT

K8

CPU_TEST08_DIG_T

C4

CPU_MA_RESET#

H16

CPU_MB_RESET#

B18

CPU_RSVD_VIDSTRB1

B3

CPU_RSVD_VIDSTRB0

C1

CPU_RSVD_VDDNB_FB_P

H6

CPU_RSVD_VDDNB_FB_N

G6

CPU_RSVD_CORE_TYPE

D5

R24

W18

R23

AA8

H18

H19

+1.8VSUS

R36 4 220 _4

R36 1 220 _4

R36 0 220 _4

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

R9280.6F

ROUTE AS 80 Ohm DIFFERENTIAL PAIR

PLACE IT CLOSE TO CPU WITHIN 1"

HDT CONNECTOR

R36 2 220 _4

R120 220_4

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

LDT_RST#

PUT CLOSE ON LAYOUT

SizeDocument NumberRev

ATHLON64 CTRL & DEBUG

Date:Sheet of

Quanta Computer Inc.

1

VID5(30)

VID4(30)

VID3(30)

VID2(30)

VID1(30)

VID0(30)

T113

T36

T44

T42

T24

T48

T49

T25

T32

T40

T31

T47

T43

T34

T41R84300_4

T38

T39

T33

T63

PROJECT : ED5

1

534Monday, May 22, 2006

2A

PDF created with FinePrint pdfFactory Pro trial version www.pdffactory.com

Page 6

5

4

3

2

1

VCC_CORE VCC_CORE

DD

CC

BB

U21E

AC4

VDD1

AD2

VDD2

G4

VDD3

H2

VDD4

J9

VDD5

J11

VDD6

J13

VDD7

K6

VDD8

K10

VDD9

K12

VDD10

K14

VDD11

L4

VDD12

L7

VDD13

L9

VDD14

L11

VDD15

L13

VDD16

M2

VDD17

M6

VDD18

M8

VDD19

M10

VDD20

N7

VDD21

N9

VDD22

N11

VDD23

P8

VDD24

P10

VDD25

R4

VDD26

R7

VDD27

R9

VDD28

R11

VDD29

T2

VDD30

T6

VDD31

T8

VDD32

T10

VDD33

T12

VDD34

T14

VDD35

U7

VDD36

U9

VDD37

U11

VDD38

U13

VDD39

V6

VDD40

V8

VDD41

V10

VDD42

POWER

Athlon 64 S1

Processor Socket

A1

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

V12

V14

W4

Y2

J15

K16

L15

M16

P16

T16

U15

V16

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

+1.8VSUS

A26

AA11

AA13

AA15

AA17

AA19

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AA4

AB2

AB7

AB9

AD6

AD8

B11

B13

B15

B17

B19

B21

B23

B25

D11

D13

D15

D17

D19

D21

D23

D25

F11

F13

F15

F17

F19

F21

F23

F25

H21

H23

U21F

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

E4

VSS51

F2

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

H7

VSS61

H9

VSS62

VSS63

VSS64

J4

VSS65

GROUND

Athlon 64 S1

Processor Socket

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

C206

4.7U/6.3V_6

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

+1.8VSUS

C205

4.7U/6.3V_6

BOTTOMSIDE DECOUPLING

VCC_CORE

VCC_CORE

+1.8VSUS

C204

4.7U/6.3V_6

C100

22U/10V_8

C123

.22U/6V_4

C207

22U/10V_8

4.7U/6.3V_6

C98

22U/10V_8

C124

.22U/6V_4

C208

22U/10V_8

C203

C109

22U/10V_8

C139

.01U_4

C187

.22U/6V_4

C198

.22U/6V_4

C102

22U/10V_8

C143

180P_4

C189

.22U/6V_4

C191

.22U/6V_4

C107

22U/10V_8

C101

22U/10V_8

C190

.22U/6V_4

C114

22U/10V_8

C199

.22U/6V_4

C202

.01U_4

C117

22U/10V_8

C197

.01U_4

C119

22U/10V_8

C201

10P_4

C200

180P_4

C614

180P_4

Athlon 64 S1g1

uPGA638

AA

Top View

AF1

PROCESSOR POWER AND GROUND

PROJECT : ED5

Quanta Computer Inc.

SizeDocument NumberRev

ATHLON64 PWR & GND

5

4

3

2

Date:Sheet of

634Monday, May 22, 2006

1

1A

PDF created with FinePrint pdfFactory Pro trial version www.pdffactory.com

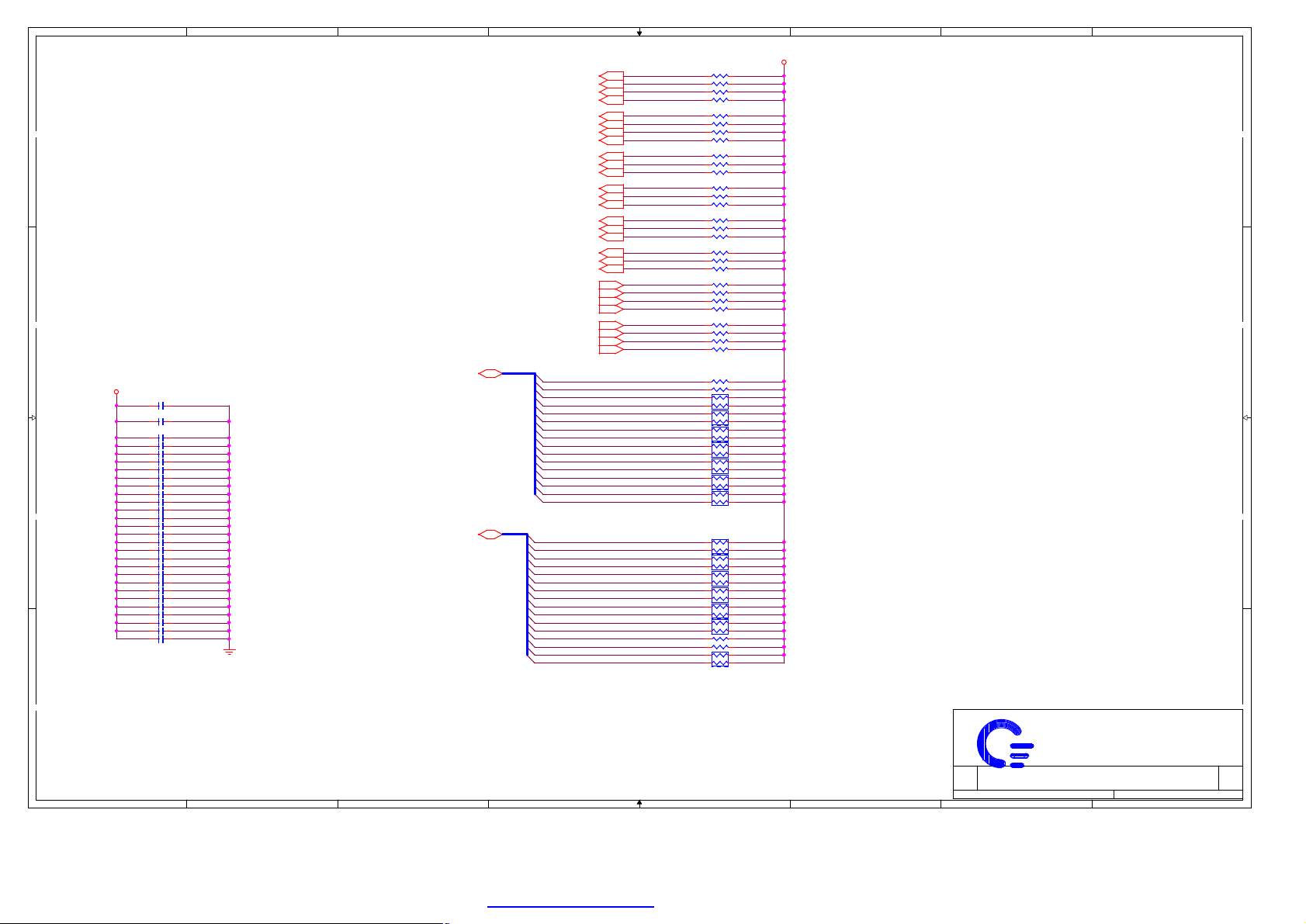

Page 7

A

+1.8VSUS

M_A_A[0..15](4,8)

44

M_A_BS#0(4,8)

M_A_BS#1(4,8)

M_A_BS#2(4,8)

M_A_DM[0..7](4)

33

M_A_DQS[0..7](4)

M_A_DQS#[0..7](4)

M_CLKOUT0(4)

M_CLKOUT0#(4)

M_CLKOUT1(4)

M_CLKOUT1#(4)

M_CLKOUT0

C175

1.5P_4

M_CLKOUT0#

22

M_CLKOUT1

C173

1.5P_4

M_CLKOUT1#

SMBDT(13)

SMBCK(13)

+3V

C322.1U_4

+1.8VSUS

11

M_A_RAS#(4,8)

M_A_CAS#(4,8)

C310.1U_4

MVREF_DIM

C316

2.2U/10V/X5R

1 2

M_A_WE#(4,8)

M_A_CS#0(4,8)

M_A_CS#1(4,8)

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A14

M_A_A15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_CKE0(4,8)

M_CKE1(4,8)

M_ODT0(4,8)

M_ODT1(4,8)

C311

.1U_4

A

818287889596103

102

A0

101

A1

100

105

116

107

106

130

147

170

185

131

148

169

188

129

146

167

186

164

166

108

113

109

110

115

114

119

198

200

195

197

199

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

A10

90

A11

89

A12

A13

86

A14

84

A15

BA0

BA1

85

BA2

10

DM0

26

DM1

52

DM2

67

DM3

DM4

DM5

DM6

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

DQS4

DQS5

DQS6

DQS7

11

DQS0

29

DQS1

49

DQS2

68

DQS3

DQS4

DQS5

DQS6

DQS7

30

CK0

32

CK0

CK1

CK1

79

CKE0

80

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

1

VREF

2

VSS0

3

VSS1

8

VSS2

9

VSS3

12

VSS4

15

VSS5

18

VSS6

21

VSS7

24

VSS8

27

VSS9

28

VSS10

33

VSS11

34

VSS12

39

VSS13

40

VSS14

41

VSS15

42

VSS16

47

VSS17

48

VSS18

53

VSS19

54

VSS20

VDD0

VDD1

(H=5.2)

VSS22

VSS21

VDD2

VDD3

CN26

REVERSE

VSS24

VSS23

111

104

112

VDD4

VDD5

VDD6

VDD8

VDD7

VDD9

SO-DIMM

VSS30

VSS29

VSS28

VSS27

VSS26

VSS25

122

1217877727166656059

117

118

VDD10

VDD11

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC/TEST

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

132

128

127

DDRII_SODIMM_R

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

NC1

NC2

NC3

NC4

B

5

7

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

50

69

83

120

163

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

B

M_A_DQ1

M_A_DQ5

M_A_DQ2

M_A_DQ3

M_A_DQ0

M_A_DQ4

M_A_DQ7

M_A_DQ6

M_A_DQ12

M_A_DQ8

M_A_DQ10

M_A_DQ14

M_A_DQ13

M_A_DQ9

M_A_DQ15

M_A_DQ11

M_A_DQ21

M_A_DQ17

M_A_DQ23

M_A_DQ18

M_A_DQ20

M_A_DQ19

M_A_DQ22

M_A_DQ16

M_A_DQ29

M_A_DQ28

M_A_DQ31

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ27

M_A_DQ30

M_A_DQ32

M_A_DQ36

M_A_DQ37

M_A_DQ35

M_A_DQ33

M_A_DQ38

M_A_DQ34

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ46

M_A_DQ44

M_A_DQ45

M_A_DQ43

M_A_DQ47

M_A_DQ55

M_A_DQ54

M_A_DQ50

M_A_DQ51

M_A_DQ53

M_A_DQ48

M_A_DQ49

M_A_DQ52

M_A_DQ56

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ61

M_A_DQ63

M_A_DQ62

M_A_CS#2(4,8)

M_A_CS#3(4,8)

+1.8VSUS

+0.9V_REF

R276

*0_4

M_A_DQ[0..63](4)

M_CLKOUT3

C176

1.5P_4

M_CLKOUT3#

M_CLKOUT4

C177

1.5P_4

M_CLKOUT4#

MVREF_DIM

C376

1U/10V_4

M_B_DQS#[0..7](4)

C374.1U_4

+1.8VSUS

R277

1K/F_4

R275

1K/F_4

M_B_A[0..15](4,8)

M_B_BS#0(4,8)

M_B_BS#1(4,8)

M_B_BS#2(4,8)

M_B_DM[0..7](4)

M_B_DQS[0..7](4)

M_CLKOUT3(4)

M_CLKOUT3#(4)

M_CLKOUT4(4)

M_CLKOUT4#(4)

+3V

R2790_4

R27810K_4

+3V

C353

2.2U/10V/X5R

1 2

C

M_CLKOUT3

M_CLKOUT3#

M_CLKOUT4

M_CLKOUT4#

M_CKE2(4,8)

M_CKE3(4,8)

M_B_RAS#(4,8)

M_B_CAS#(4,8)

M_B_WE#(4,8)

M_B_CS#0(4,8)

M_B_CS#1(4,8)

M_ODT2(4,8)

M_ODT3(4,8)

SMBDT

SMBCK

C365.1U_4

MVREF_DIM

C364

.1U_4

C

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15M_A_A13

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10

90

A11

89

A12

116

A13

86

A14

84

A15

107

BA0

106

BA1

85

BA2

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS0

29

DQS1

49

DQS2

68

DQS3

129

DQS4

146

DQS5

167

DQS6

186

DQS7

30

CK0

32

CK0

164

CK1

166

CK1

79

CKE0

80

CKE1

108

RAS

113

CAS

109

WE

110

S0

115

S1

114

ODT0

119

ODT1

198

SA0

200

SA1

195

SDA

197

SCL

199

VDDspd

1

VREF

2

VSS0

3

VSS1

8

VSS2

9

VSS3

12

VSS4

15

VSS5

18

VSS6

21

VSS7

24

VSS8

27

VSS9

28

VSS10

33

VSS11

34

VSS12

39

VSS13

40

VSS14

41

VSS15

42

VSS16

47

VSS17

48

VSS18

53

VSS19

54

VSS20

+1.8VSUS

818287889596103

VDD0

111

104

112

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD8

VDD7

VDD9

CN27

REVERSE

SO-DIMM

(H=9.2)

VSS30

VSS29

VSS28

VSS27

VSS26

VSS25

VSS24

VSS23

VSS22

VSS21

122

1217877727166656059

117

118

DQ0

DQ1

DQ2

VDD10

VDD11

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC1

NC2

NC3

NC4

NC/TEST

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

132

128

127

DDRII_SODIMM_R

D

M_B_DQ4

5

M_B_DQ1

7

M_B_DQ2

17

M_B_DQ3

19

M_B_DQ5

4

M_B_DQ0

6

M_B_DQ6

14

M_B_DQ7

16

M_B_DQ8

23

M_B_DQ9

25

M_B_DQ10

35

M_B_DQ15

37

M_B_DQ12

20

M_B_DQ13

22

M_B_DQ14

36

M_B_DQ11

38

M_B_DQ16

43

M_B_DQ21

45

M_B_DQ19

55

M_B_DQ23

57

M_B_DQ20

44

M_B_DQ17

46

M_B_DQ18

56

M_B_DQ22

58

M_B_DQ29

61

M_B_DQ28

63

M_B_DQ26

73

M_B_DQ27

75

M_B_DQ24

62

M_B_DQ25

64

M_B_DQ30

74

M_B_DQ31

76

M_B_DQ32

123

M_B_DQ36

125

M_B_DQ39

135

M_B_DQ35

137

M_B_DQ33

124

M_B_DQ37

126

M_B_DQ34

134

M_B_DQ38

136

M_B_DQ40

141

M_B_DQ41

143

M_B_DQ46

151

M_B_DQ43

153

M_B_DQ44

140

M_B_DQ45

142

M_B_DQ47

152

M_B_DQ42

154

M_B_DQ53

157

M_B_DQ49

159

M_B_DQ55

173

M_B_DQ54

175

M_B_DQ48

158

M_B_DQ52

160

M_B_DQ50

174

M_B_DQ51

176

M_B_DQ60

179

M_B_DQ57

181

M_B_DQ62

189

M_B_DQ59

191

M_B_DQ61

180

M_B_DQ56

182

M_B_DQ63

192

M_B_DQ58

194

50

69

83

120

163

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

M_B_DQ[0..63](4)

M_B_CS#2(4,8)

M_B_CS#3(4,8)

E

+1.8VSUS

*10U/6.3V/X5RC308

*10U/6.3V/X5RC380

10U/10V/X5R_8C338

10U/10V/X5R_8C361

.1U_4C388

.1U_4C362

.1U_4C342

.1U_4C347

.1U_4C349

.1U_4C345

.1U_4C309

.1U_4C299

.1U_4C340

.1U_4C348

.1U_4C325

.1U_4C372

.1U_4C341

.1U_4C370

.1U_4C373

.1U_4C392

.1U_4C391

.1U_4C389

.1U_4C371

.1U_4C378

PROJECT : ED5

Quanta Computer Inc.

SizeDocument NumberRev

DDR-II SODIMM*2

D

Date:Sheet of

734Monday, May 22, 2006

E

1A

PDF created with FinePrint pdfFactory Pro trial version www.pdffactory.com

Page 8

1

2

3

4

5

6

7

8

+0.9V_VTER

M_CKE0(4,7)

M_CKE1(4,7)

M_CKE2(4,7)

M_CKE3(4,7)

M_ODT0(4,7)

M_ODT1(4,7)

AA

BB

+0.9V_VTER

M_A_A[0..15](4,7)

*10U/6.3V/X5RC296

*10U/6.3V/X5RC363

.1U_4C270

.1U_4C393

.1U_4C328

.1U_4C330

.1U_4C329

.1U_4C368

.1U_4C326

.1U_4C385

.1U_4C327

*0.1U_4C346

CC

*0.1U_4C288

.1U_4C290

.1U_4C379

.1U_4C390

.1U_4C339

.1U_4C369

*0.1U_4C387

.1U_4C298

.1U_4C273

.1U_4C350

*0.1U_4C386

.1U_4C275

.1U_4C384

.1U_4C283

*0.1U_4C280

.1U_4C375

M_B_A[0..15](4,7)

M_ODT2(4,7)

M_ODT3(4,7)

M_A_BS#0(4,7)

M_A_BS#1(4,7)

M_A_BS#2(4,7)

M_A_WE#(4,7)

M_A_CAS#(4,7)

M_A_RAS#(4,7)

M_B_BS#0(4,7)

M_B_BS#1(4,7)

M_B_BS#2(4,7)

M_B_WE#(4,7)

M_B_CAS#(4,7)

M_B_RAS#(4,7)

M_A_CS#0(4,7)

M_A_CS#1(4,7)

M_A_CS#2(4,7)

M_A_CS#3(4,7)

M_B_CS#0(4,7)

M_B_CS#1(4,7)

M_B_CS#2(4,7)

M_B_CS#3(4,7)

M_A_A13

M_A_A10

M_A_A0

M_A_A4

M_A_A6

M_A_A2

M_A_A7

M_A_A11

M_A_A12

M_A_A9

M_A_A3

M_A_A1

M_A_A8

M_A_A5

M_A_A14

M_A_A15

M_B_A0

M_B_A2

M_B_A4

M_B_A6

M_B_A7

M_B_A11

M_B_A3

M_B_A1

M_B_A8

M_B_A5

M_B_A12

M_B_A9

M_B_A10

M_B_A13

M_B_A14

M_B_A15

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_A_WE#

M_A_CAS#

M_A_RAS#

M_B_BS#0

M_B_BS#1

M_B_BS#2

M_B_WE#

M_B_CAS#

M_B_RAS#

R20456_4

R23356_4

R27256_4

R28056_4

R23056_4

R19756_4

R28356_4

R26456_4

R20156_4

R23256_4

R20256_4

R20056_4

R19956_4

R23156_4

R26856_4

R28656_4

R27056_4

R26756_4

R26656_4

R28556_4

R22956_4

R19856_4

R20356_4

R22756_4

R28456_4

R26556_4

R27156_4

R28156_4

R22856_4

R21556_4

RP90404-56X2

1 2

3 4

RP100404-56X2

1 2

3 4

RP110404-56X2

1 2

3 4

RP70404-56X2

1 2

3 4

RP50404-56X2

1 2

3 4

RP60404-56X2

1 2

3 4

RP120404-56X2

1 2

3 4

RP160404-56X2

1 2

3 4

RP170404-56X2

1 2

3 4

RP180404-56X2

1 2

3 4

RP130404-56X2

1 2

3 4

RP140404-56X2

1 2

3 4

RP150404-56X2

1 2

3 4

R26956_4

R28256_4

RP190404-56X2

1 2

3 4

DD

PROJECT : ED5

Quanta Computer Inc.

SizeDocument NumberRev

DDR-II TERMINATION

1

2

3

4

5

6

Date:Sheet of

7

834Monday, May 22, 2006

8

1A

PDF created with FinePrint pdfFactory Pro trial version www.pdffactory.com

Page 9

5

DD

HT_CADOUT15_P(3)

HT_CADOUT15_N(3)

HT_CADOUT14_P(3)

HT_CADOUT14_N(3)

HT_CADOUT13_P(3)

HT_CADOUT13_N(3)

HT_CADOUT12_P(3)

HT_CADOUT12_N(3)

HT_CADOUT11_P(3)

HT_CADOUT11_N(3)

HT_CADOUT10_P(3)

HT_CADOUT10_N(3)

HT_CADOUT9_P(3)

HT_CADOUT9_N(3)

HT_CADOUT8_P(3)

CC

BB

VDDHT_PKG

HT_CADOUT8_N(3)

HT_CADOUT7_P(3)

HT_CADOUT7_N(3)

HT_CADOUT6_P(3)

HT_CADOUT6_N(3)

HT_CADOUT5_P(3)

HT_CADOUT5_N(3)

HT_CADOUT4_P(3)

HT_CADOUT4_N(3)

HT_CADOUT3_P(3)

HT_CADOUT3_N(3)

HT_CADOUT2_P(3)

HT_CADOUT2_N(3)

HT_CADOUT1_P(3)

HT_CADOUT1_N(3)

HT_CADOUT0_P(3)

HT_CADOUT0_N(3)

HT_CLKOUT1_P(3)

HT_CLKOUT1_N(3)

HT_CLKOUT0_P(3)

HT_CLKOUT0_N(3)

HT_CTLOUT0_P(3)

HT_CTLOUT0_N(3)

R33649.9/F R59100/F_4

R335

49.9/F

4

HT_RXCALP

HT_RXCALN

W19

W20

AC21

AB22

AB20

AA20

AA19

AA25

AA24

AB23

AA23

AB24

AB25

AC24

AC25

W21

W22

W25

R19

R18

R21

R22

U22

U21

U18

U19

Y19

T24

R25

U25

U24

V23

U23

V24

V25

Y24

P24

P25

A24

C24

U16A

HT_RXCAD15P

HT_RXCAD15N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD0P

HT_RXCAD0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCTLP

HT_RXCTLN

HT_RXCALP

HT_RXCALN

RS485M A11 HT

PART 1 OF 5

HYPER T R A NSPORT CPU

I/F

3

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCTLP

HT_TXCTLN

HT_TXCALP

HT_TXCALN

P21

P22

P18

P19

M22

M21

M18

M19

L18

L19

G22

G21

J20

J21

F21

F22

N24

N25

L25

M24

K25

K24

J23

K23

G25

H24

F25

F24

E23

F23

E24

E25

L21

L22

J24

J25

N23

P23

C25

D24

HT_TXCALP

HT_TXCALN

HT_CADIN15_P(3)

HT_CADIN15_N(3)

HT_CADIN14_P(3)

HT_CADIN14_N(3)

HT_CADIN13_P(3)

HT_CADIN13_N(3)

HT_CADIN12_P(3)

HT_CADIN12_N(3)

HT_CADIN11_P(3)

HT_CADIN11_N(3)

HT_CADIN10_P(3)

HT_CADIN10_N(3)

HT_CADIN9_P(3)

HT_CADIN9_N(3)

HT_CADIN8_P(3)

HT_CADIN8_N(3)

HT_CADIN7_P(3)

HT_CADIN7_N(3)

HT_CADIN6_P(3)

HT_CADIN6_N(3)

HT_CADIN5_P(3)

HT_CADIN5_N(3)

HT_CADIN4_P(3)

HT_CADIN4_N(3)

HT_CADIN3_P(3)

HT_CADIN3_N(3)

HT_CADIN2_P(3)

HT_CADIN2_N(3)

HT_CADIN1_P(3)

HT_CADIN1_N(3)

HT_CADIN0_P(3)

HT_CADIN0_N(3)

HT_CLKIN1_P(3)

HT_CLKIN1_N(3)

HT_CLKIN0_P(3)

HT_CLKIN0_N(3)

HT_CTLIN0_P(3)

HT_CTLIN0_N(3)

2

1

AA

PROJECT : ED5

Quanta Computer Inc.

SizeDocument NumberRev

RS485-HT LINK0 I/F

5

4

3

2

Date:Sheet of

934Monday, May 22, 2006

1

1A

PDF created with FinePrint pdfFactory Pro trial version www.pdffactory.com

Page 10

5

VDD33

VIN

VIN

+1.8V

C52

.1U_4

+5VSUS

C156

.1U_4

+3V

+1.8VSUS

C253

.1U_4

VIN

VA

VA

DD

CC

BB

C113

.1U_4

VIN VDD33

VLDT_RUN

C97

.1U_4

VCC_CORE

C440

.1U_4

VIN

C111

.1U_4

VCC_CORE

VIN

C85

.1U_4

+1.8VSUS

VCC_CORE

+1.2V

C169

.1U_4

C26

.1U_4

4

VIN

+3V

+1.8V

VLDT_RUN

C51

C121

.1U_4

.1U_4

+3V

+1.8V

+1.2V

+5V

C68

.1U_4

+3V

+5V

GND

C65

.1U_4

C473

.1U_4

+1.8VSUS

+0.9V_VTER

+1.2V

C548

.1U_4

C103

.1U_4

LAN_PCIE_RXP0(23)

LAN_PCIE_RXN0(23)

MINI_PCIE_RXP2(19)

MINI_PCIE_RXN2(19)

MINI_PCIE_RXP3(19)

MINI_PCIE_RXN3(19)

R214:

10KOhm FOR RS485

1.47KOhm FOR

RS690

R213:

8.25KOhm FOR RS485

DNI FOR RS690

PCIE_RXP1(24) PCIE_TXP1(24)

PCIE_RXN1(24)

A_RX0P(14)

A_RX0N(14)

A_RX1P(14)

A_RX1N(14)

3

R4710K_4

R548.25K/F_6

U16B

G5

GFX_RX0P

G4

GFX_RX0N

J8

GFX_RX1P

J7

GFX_RX1N

J4

GFX_RX2P

J5

GFX_RX2N

L8

GFX_RX3P

L7

GFX_RX3N

L4

GFX_RX4P

L5

GFX_RX4N

M8

GFX_RX5P

M7

GFX_RX5N

M4

GFX_RX6P

M5

GFX_RX6N

P8

GFX_RX7P

P7

GFX_RX7N

P4

GFX_RX8P

P5

GFX_RX8N

R4

GFX_RX9P

R5

GFX_RX9N

R7

GFX_RX10P

R8

GFX_RX10N

U4

GFX_RX11P

U5

GFX_RX11N

W4

GFX_RX12P

W5

GFX_RX12N

Y4

GFX_RX13P

Y5

GFX_RX13N

V9

GFX_RX14P

W9

GFX_RX14N

AB7

GFX_RX15P

AB6

GFX_RX15N

W11

GPP_RX0P

W12

GPP_RX0N

AA11

GPP_RX1P

AB11

GPP_RX1N

Y7

GPP_RX2P

AA7

GPP_RX2N

AB9

GPP_RX3P

AA9

GPP_RX3N

W14

SB_RX0P

W15

SB_RX0N

AB12

SB_RX1P

AA12

SB_RX1N

AA14

PCE_ISET(PCE_CALI)

AB14

PCE_TXISET(NC)

RS485M A11 HT

PART 2 OF 5

PCIE I/F

GFX

PCIE I/F GPP

PCIE I/F SB

PCE_PCAL(PCE_CALRP)

PCE_NCAL(PCE_CALRN)

2

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

J1

H2

K2

K1

K3

L3

L1

L2

N2

N1

P2

P1

P3

R3

R1

R2

T2

U1

V2

V1

V3

W3

W1

W2

Y2

AA1

AA2

AB2

AB1

AC1

AE3

AE4

GPP_TX0P_C

AD8

GPP_TX0N_C

AE8

GPP_TX1P_C

AD7

GPP_TX1N_C

AE7

GPP_TX2P_C

AD4

GPP_TX2N_C

AE5

GPP_TX3P_C

AD5

GPP_TX3N_C

AD6

A_TX0P_C

AE9

A_TX0N_C

AD10

A_TX1P_C

AC8

A_TX1N_C

AD9

R49150/F_4

AD11

R46100/F_4

AE11

C63.1U_4

C62.1U_4

C41.1U_4

C48.1U_4

C32.1U_4

C34.1U_4

C35.1U_4

C36.1U_4

C54.1U_4

C66.1U_4

C44.1U_4

C50.1U_4

VDDA12_PKG2

R216:

R215:

Place these caps

close to connector

150 Ohm FOR RS485

562 Ohm FOR RS690

Ward update to 100 Ohm FOR RS485

2KOhm FOR RS690

1

LAN_PCIE_TXP0(23)

LAN_PCIE_TXN0(23)

PCIE_TXN1(24)

MINI_PCIE_TXP2(19)

MINI_PCIE_TXN2(19)

MINI_PCIE_TXP3(19)

MINI_PCIE_TXN3(19)

A_TX0P(14)

A_TX0N(14)

A_TX1P(14)

A_TX1N(14)

AA

PROJECT : ED5

Quanta Computer Inc.

SizeDocument NumberRev

RS485-PCIE LINK I/F

5

4

3

2

Date:Sheet of

1034Monday, May 22, 2006

1

1A

PDF created with FinePrint pdfFactory Pro trial version www.pdffactory.com

Page 11

5

R222K/F

R2310K_4

HTPVDD+1.8V

C475

10U/10V/X5R_8

C40

10U/10V/X5R_8

+1.8V +3V

1 3

Q5

MMBT3904

STRP_DATA

TV_SWITCH

5

R26

10K_4

2

C93

4.7U/6.3V_6

C49

4.7U/6.3V_6

R21

1K/F_4

TV_C/R_SYS(20)

TV_Y/G_SYS(20)

TV_COMP_SYS(20)

VGA_RED(20)

VGA_GRN(20)

VGA_BLU(20)

LDT_STOP#_NBLDT_STOP#_NB

LOAD_ROM#: LOAD ROM STRAP ENABLE

High, LOAD ROM STRAP DISABLE

Low, LOAD ROM STRAP ENABLE

L22

BK1608HS600

+1.8V PLLVDD

DD

CC

BB

AA

L12

BK1608HS600

LDT_STOP#(5,14,15)

+3V

L20

BK1608HS600

AVDDQ+1.8V

C83

10U/10V/X5R_8

GND_AVSSQ

R63

R64

150/F_6

150/F_6

close to NB

R66

150/F_6

4

1 2

R3330_6

close to NB

R62

150/F_6

R67

150/F_6

4

C88

2.2U/10V/X5R

R68

150/F_6

+3V

BK1608LM252-T

F3C UPDATE P/N FOR

CRT RIPPLE

ALINK_RST#(14,19,21,23,24)

NB_PWRGD(5,28)

NBSRC_CLKP(13)

NBSRC_CLKN(13)

SBLINK_CLKP(13)

SBLINK_CLKN(13)

R383K

BMREQ#(14)

L21

GND_AVSSQ

DDCCLK(20)

DDCDAT(20)

NB_OSC(13)

R370_4

LOAD_ROM#

D6RB751

2 1

10U/6.3V_6

AVDDQ

ALLOW_LDTSTOP(14)

PHL_CLK(20)

PHL_DATA(20)

R34

4.7K/F_4

AVDD_NB

C472

C471

.1U_4

VSYNC(20)

HSYNC(20)

R250_4

R240_4

R400_4

HTREFCLK(13)

T91

R29*2.7K_4

R30*2.7K_4

R31*2.7K_4

R35*2.7K_4

R36*2.7K_4

T6

T10

T4

T2

3

C91

.1U_4

AVDD_NB

AVDD1

TV_C/R_SYS

TV_Y/G_SYS

TV_COMP_SYS

R337715/F

PLLVDD

HTPVDD

NB_RST#

R5810K_4

TV_SWITCH

PLLVDD12

DFT_GPIO0

DFT_GPIO2

DFT_GPIO3

DFT_GPIO4

DFT_GPIO5

3

+1.8V AVDD1

R3320_6

2.2U/10V/X5R

1 2

U16C

B22

AVDD1

C22

AVDD2

G17

AVSSN1

H17

AVSSN2

A20

AVDDDI

B20

AVSSDI

A21

AVDDQ

A22

AVSSQ

C21

C_R

C20

Y_G

D19

COMP_B

E19

RED

F19

GREEN

G19

BLUE

C6

DACVSYNC

A5

DACHSYNC

B21

RSET

B6

DACSCL

A6

DACSDA

A10

PLLVDD(PLLVDD18)

B10

PLLVSS

B24

HTPVDD

B25

HTPVSS

C10

SYSRESET#

C11

POWERGOOD

C5

LDTSTOP#

B5

ALLOW_LDTSTOP

C23

HTTSTCLK

B23

HTREFCLK

C2

TVCLKIN

B11

OSCIN

A11

OSCOUT(PLLVDD12)

F2

GFX_CLKP

E1

GFX_CLKN

G1

SB_CLKP

G2

SB_CLKN

D6

DFT_GPIO0

D7

DFT_GPIO1

C8

DFT_GPIO2

C7

DFT_GPIO3

B8

DFT_GPIO4

A8

DFT_GPIO5

B2

BMREQb

A2

I2C_CLK

B4

I2C_DATA

AA15

THERMALDIODE_P

AB15

THERMALDIODE_N

C14

TMDS_HPD

B3

DDC_DATA

C3

A3

TESTMODE

STRP_DATA

STRP_DATA

RS485M A11 HT

OSCOUT(A11)

DVO_D0(AD14)

DVO_D1(AD15)DVO_D1

DVO_D3(AD16)

DVO_D7(AE19)

DVO_D8(AD19)

DVO_D9(AE20)

C469

PART 3 OF 5

CRT/TVOUT

PLL

PM

CLOCKs

MIS.

LVDS

PWR

DVO

RS485

OSCOUT

DVO_D0

DVO_D3

DVO_D4

DVO_D7

DVO_D8

DVO_D9

DVO_D10DVO_D10(AD20)

2

TXOUT_L0P

TXOUT_L0N

TXOUT_L1P

TXOUT_L1N

TXOUT_L2P

TXOUT_L2N

TXOUT_L3P

TXOUT_L3N

TXOUT_U0P

TXOUT_U0N

TXOUT_U1P

TXOUT_U1N

TXOUT_U2P

TXOUT_U2N

TXOUT_U3P

TXOUT_U3N

TXCLK_LP

TXCLK_LN

TXCLK_UP

TXCLK_UN

LPVDD

LPVSS

LVDDR18D_1

LVDDR18D_2

LVDDR18A_1

LVDDR18A_2

LVSSR1

LVSSR3

LVSSR5

LVSSR6

LVSSR7

LVSSR8

LVSSR12

LVSSR13

LVDS_DIGON

LVDS_BLON

LVDS_BLEN

DVO_D0(GPP_TX4P)

DVO_D1(GPP_TX4N)

DVO_D2(NC)

DVO_D3(GPP_RX4P)

DVO_D4(GPP_RX4N)

DVO_D5(NC)

DVO_D6(NC)

DVO_D7(GPP_TX5N)

DVO_D8(GPP_TX5P)

DVO_D9(GPP_RX5N)

DVO_D10(GPP_RX5P)

DVO_D11(NC)

DVO_VSYNC(NC)

DVO_DE(NC)

DVO_HSYNC(NC)

DVO_IDCKP(NC)

DVO_IDCKN(NC)

RS690

PLLVDD12

GPP_TX4P

GPP_TX4N

GPP_RX4P

GPP_RX4NDVO_D4(AE16)

GPP_TX5N

GPP_TX5P

GPP_RX5N

GPP_RX5P

2

B14

B15

B13

A13

H14

G14

D17

E17

A15

B16

C17

C18

B17

A17

A18

B18

E15

D15

H15

G15

D14

E14

A12

B12

C12

C13

A16

A14

D12

C19

C15

C16

F14

F15

E12

G12

F12

AD14

AD15

AE15

AD16

AE16

AC17

AD18

AE19

AD19

AE20

AD20

AE21

AD13

AC13

AE13

AE17

AD17

1

TXLOUT0+(20)

TXLOUT0-(20)

TXLOUT1+(20)

TXLOUT1-(20)

TXLOUT2+(20)

TXLOUT2-(20)

T13

T9

T94

T100

T15

T95

T98

T97

T102

T104

TXLCLKOUT+(20)

TXLCLKOUT-(20)

LCD_PON

LVDS_BLON

R3310_4

T3

LVDS_BLON

NB_PWRGD

NC7SZ08P5X_NL

T7

T8

C72

.1U_4

C84

4.7U/6.3V_6

C73

C71

4.7U/6.3V_6

.1U_4

LCD_POWER_ON(20)

T96

T5

T93

T11

T101

T18

T14

T17

T106

T16

T108

T107

T99

T103

T92

T12

T105

LCD_PON

LVDS_BLON

+3V

53

1

2

CHECK

L19BK1608HS600

TO

220OHM

GND_LPVSS

BK1608HS600

R550_6

R3302K/F

R452K/F

ECN 2A:

BOM Lose and stuff R43

U7

R430_4

4

PROJECT : ED5

Quanta Computer Inc.

SizeDocument NumberRev

RS485-SYSTEM I/F & CLKGEN

Date:Sheet of

1

R560_6

GND_LPVSS

RS485: LVDDR18A=1.8V

+1.8V

+1.8V

1134Monday, May 22, 2006

C81

.1U_4

L56

BK1608HS600

C79

4.7U/6.3V_6

GND_LVSSR

BLON(20)

L13

2A

PDF created with FinePrint pdfFactory Pro trial version www.pdffactory.com

Page 12

5

V12

M3

DD

VSS A1

4

V11

V14F3V15A1H1G3J2H3J6F1L6M2M6J3P6T1N3R6U2T3U3U6Y1W6AC2Y3Y9

VSS A2

VSS A3

VSS A4

VSS A5

VSS A6

AE6

AE10

VSS A7

VSS A8

VSS A9

VSS A10

VSS A11

VSS A13

VSS A15

VSS A16

VSS A17

VSS A18

VSS A19

VSS A20

VSS A14

VSS A12

VSS A21

AC4

P9

VSS A22

VSS A24

VSS A25

VSS A26

VSS A27

VSS A28

VSS A30

VSS A29

VSS A23

3

Y11R9AD1

AC5

AC6

AC7

AD3

AC9

AC10

Y15

VSS A32

VSS A33

VSS A34

VSS A35

VSS A36

VSS A37

VSS A31

G6

Y12

Y14

AA3

VSS A38

VSS A39

VSS A40

VSS A41

VSS A42

VSS A43

VSS A44

VSS A45

VSS A46

VSS A47

VSS A48

U16E

RS485M A11 HT

2

1

GROUND

C87

1U/10V_4

C31

1U/10V_4

VDDHT_PKG

VDDA12_PKG1

VDDA12_PKG2

VDDA12_PKG1

C446

10U/10V/X5R_8

PAR 5 OF 5

VSS 1

VSS 2

VSS 3

VSS 4

VSS 5

VSS 6

VSS 7

VSS 8

VSS 9

VSS 1 0

VSS 1 1

VSS 1 2