5

4

3

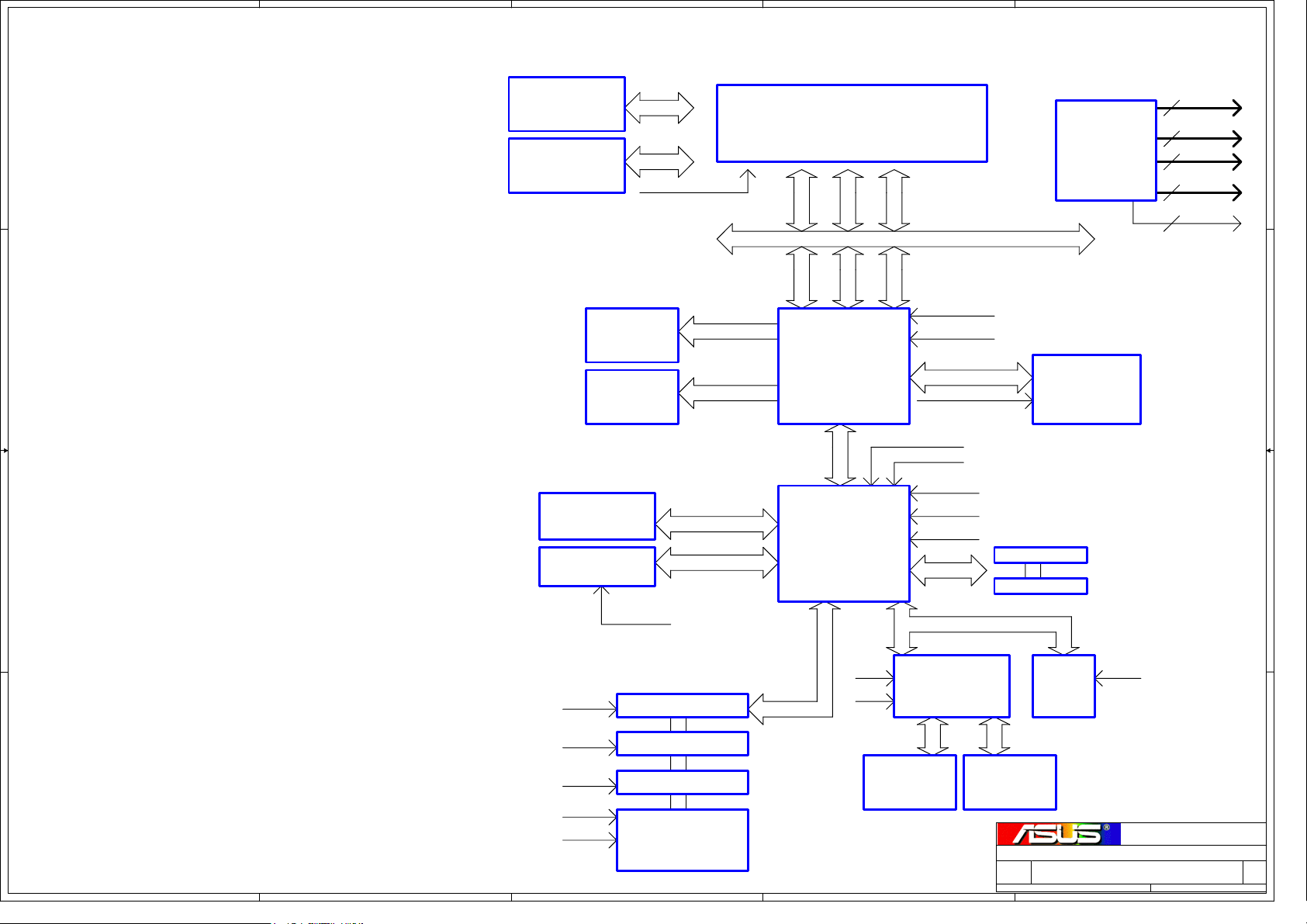

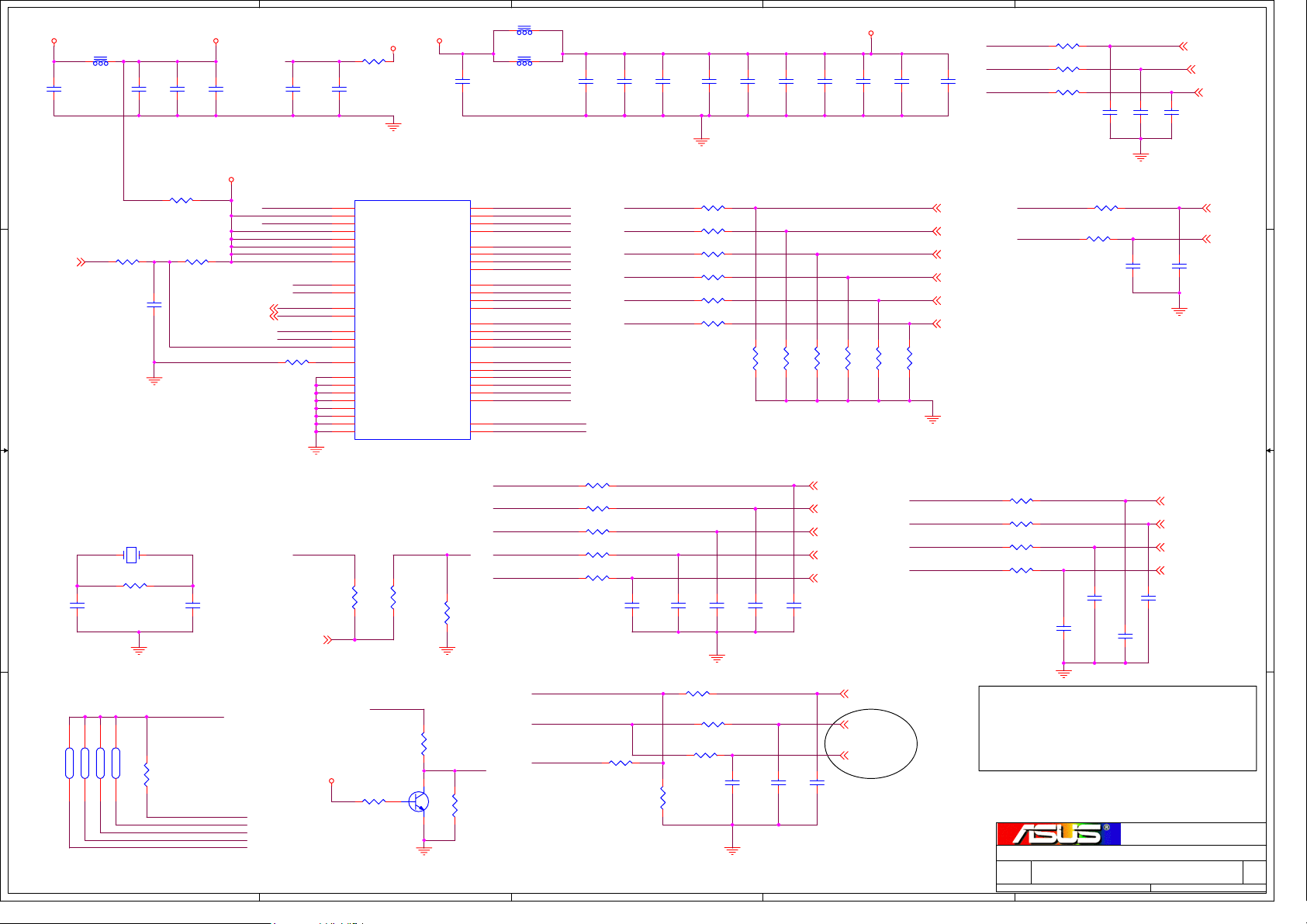

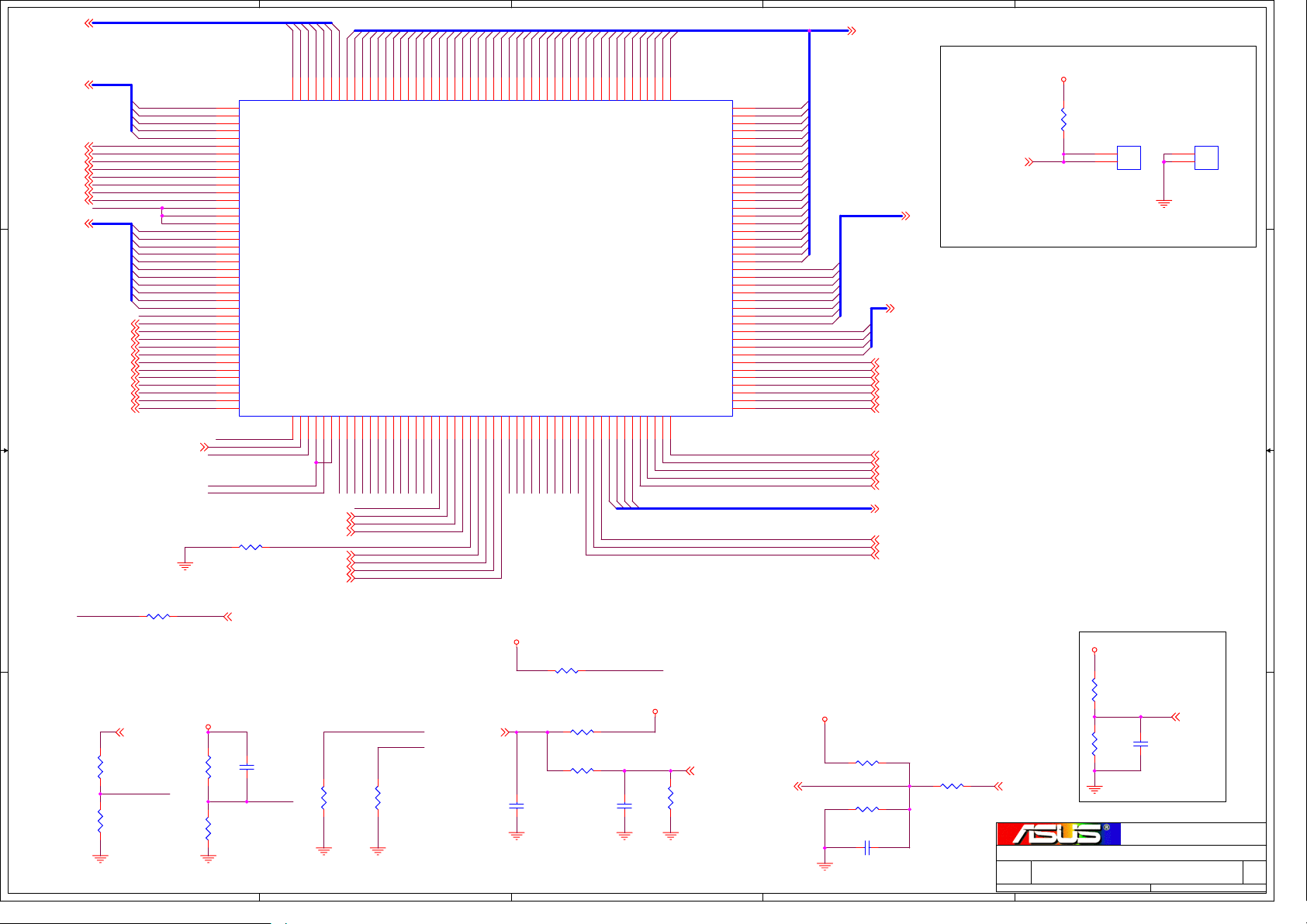

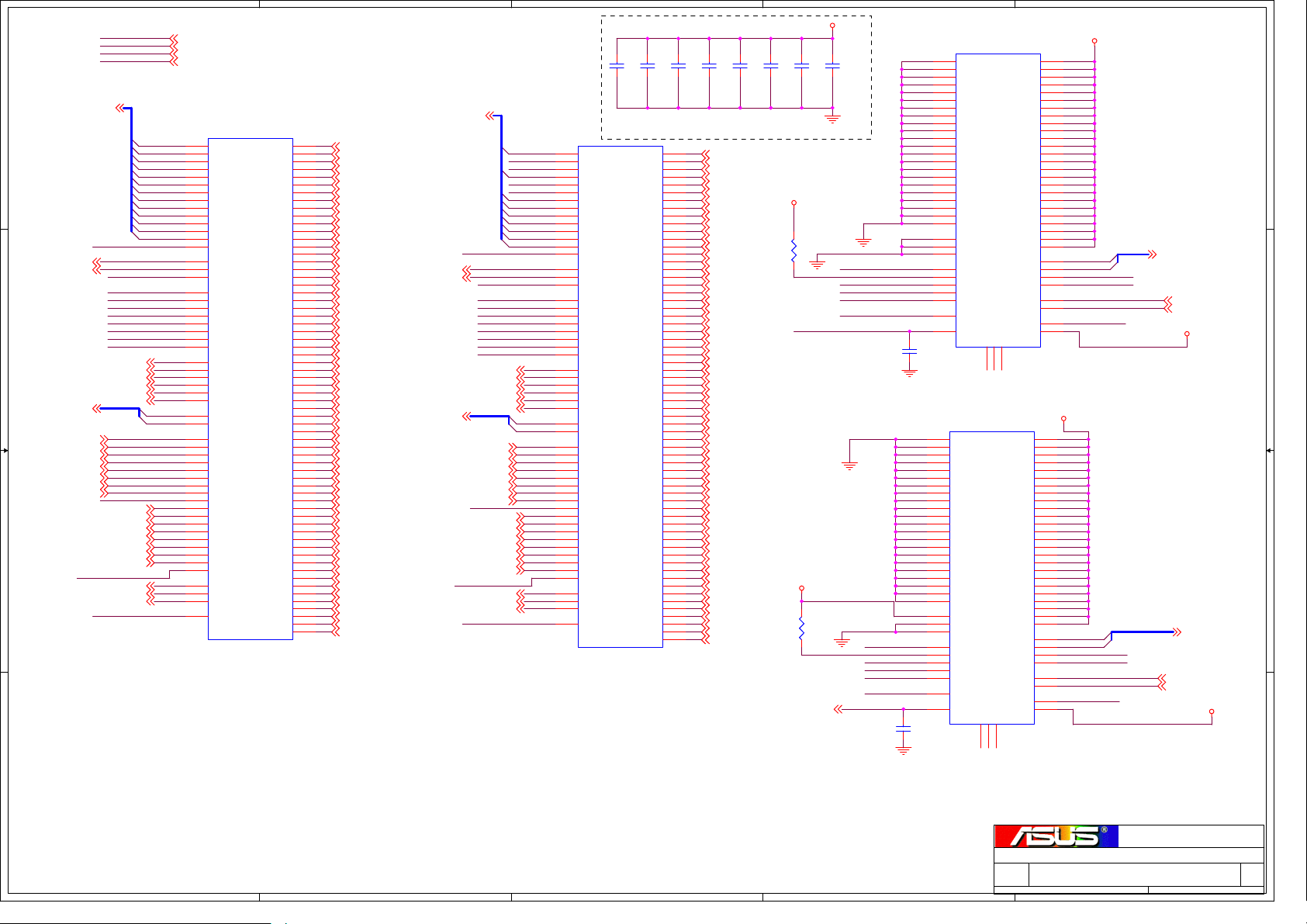

RAINIER-CR PROJECT

2

1

Rev.A03 : 01/28/2003

D D

Page 1. BLOCK DIAG., INDEX

Page 2. CLOCK DISTRIBUTION

Page 3. RESET MAP

Page 4. POWER DISTRIBUTION

Page 5. POWER FLOW

Page 6. POWER SEQUENCE

Page 7. CLOCK

Page 8. P4-478 CPU-1

C C

Page 9. P4-478 CPU-2

Page 10. BROOKDALE-1

Page 11. BROOKDALE-2

Page 12. BROOKDALE-3

Page 13. BROOKDALE-4

Page 14. DDR SERIAL

Page 15. DDR SOCKET

Page 16. DDR_TERMINATION

Page 17. AGP 4X

B B

Page 18. VGA CONNECTOR

Page 19. ICH4-1

Page 20. ICH4-2

Page 21. ICH4-3

Page 22. IDE

Page 23. USB PORT

Page 24. A97 AUDIO.

Page 25. AUDIO CONN.

Page 26. AUDIO AMP/CONN.

Page 27. PCI SLOT 1&2

A A

Page 28. NIC- LAVON/ KENAI

Page 29. NIC- RJ45 CONN.

Page 30. FWH

5

Page 31. SMSC SIO (47M534)

Page 32. PARALLEL PORT

Page 33. SERIAL PORT

Page 34. KB, MOUSE

Page 35. SMBUS

Page 36. FLOPPY

Page 37. DIAGLED

Page 38. FRONTPANEL

Page 39. POWER GOOD & RESET

Page 40. POWER CONNECTOR

Page 41. CPUCORE

Page 42. DUAL_POWER

Page 43. +2.5V_DUAL

Page 44. +1.5V

Page 45. 1.25V

Page 46. BATTERY

Page 47. EMI

Page 48. OTHER

Page 49. H-RISER

Page 50. BOM OPTION 1

Page 51. BOM OPTION 2

4

VRM on Board

STANDBY

REGULATOR

AGP

SLOT

High-Speed USB

6 ports

AD1981B AC'97

CODEC

33MHz

33MHz

33MHz

25MHz

33MHz

400/533MHz

VGA

480Mb/s

AC'97 LINK

14.318MHz

PCI CONN

PCI CONN

PCI CONN

NIC

82540

RJ45 port

3

Intel Pentium 4 processor /

Northwood processor

478 Pin Package1.5V &

ADDR

CNTL

DATA

CNTL

ADDR

350Mpixels/s

DATA

BrookdaleG

GMCH

760 FC-BGA

HUB LINK

ICH4

421 mBGA

48MHz

33MHz

PCI BUS

LPTx/COMx/IR

Floppy

2

HOST BUS

66/133MHz

48MHz

200/266MHz

33MHz

48MHz

14.318MHz

66MHz

32.768KHz

IDE BUS

LPC BUS

LPC Super

I/O

Keyboard/Mouse

MISC HEADER

CLOCK

CK-408

MEMORY

2 DDR DIMM

MODULES

PRIMARY IDE

SECONDARY IDE

FWH

82802AB

32 PLCC

ASUStek Computer Inc.

Size Project Name

A3

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

Date: Sheet

33MHz

Title :

Engineer:

66MHZ

66/133 MHz

33MHz

14.318MHz

48MHz

BLOCK DIAGRAM

1

William Yu

151Tuesday, January 28, 2003

of

Rev

A03

5

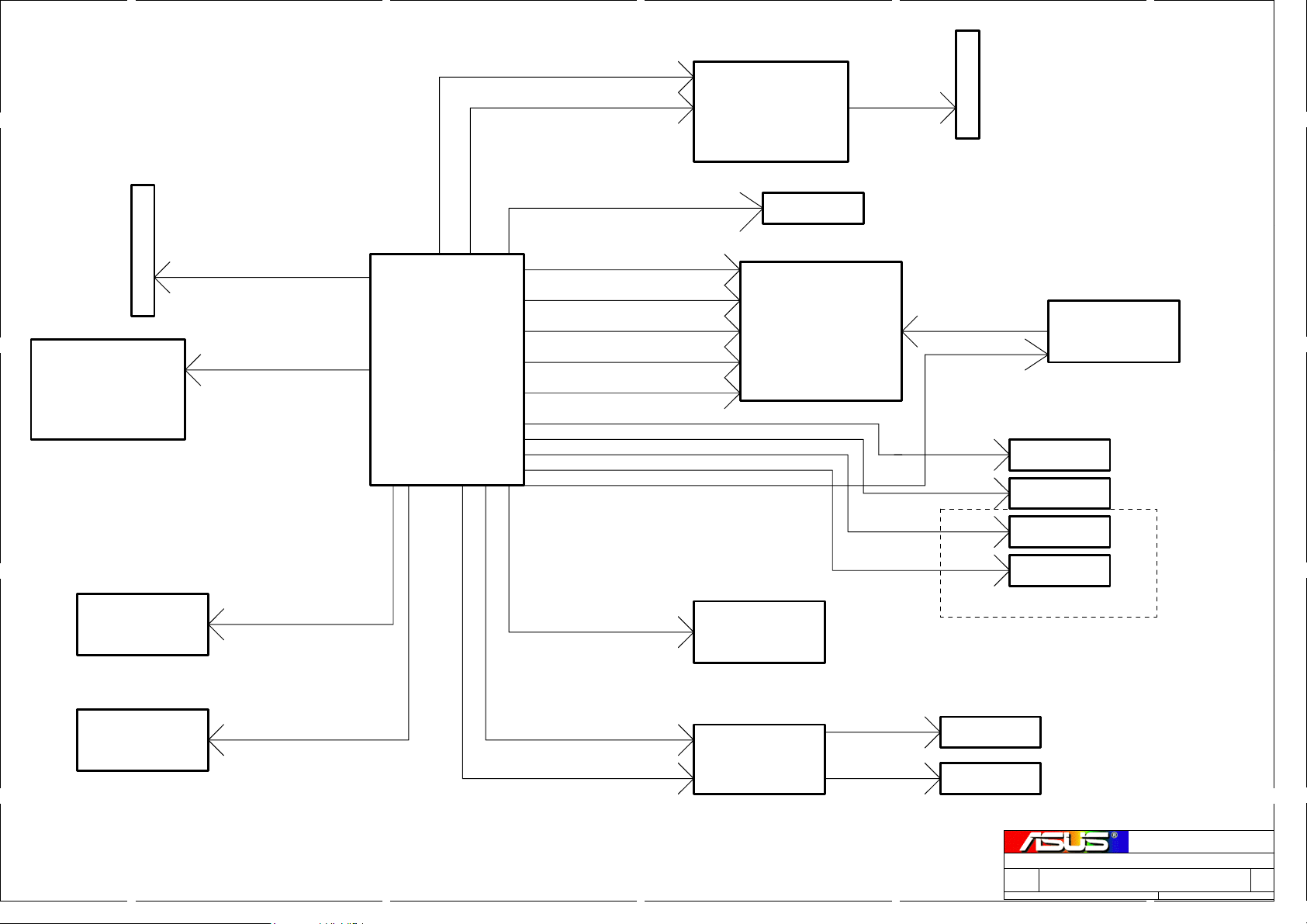

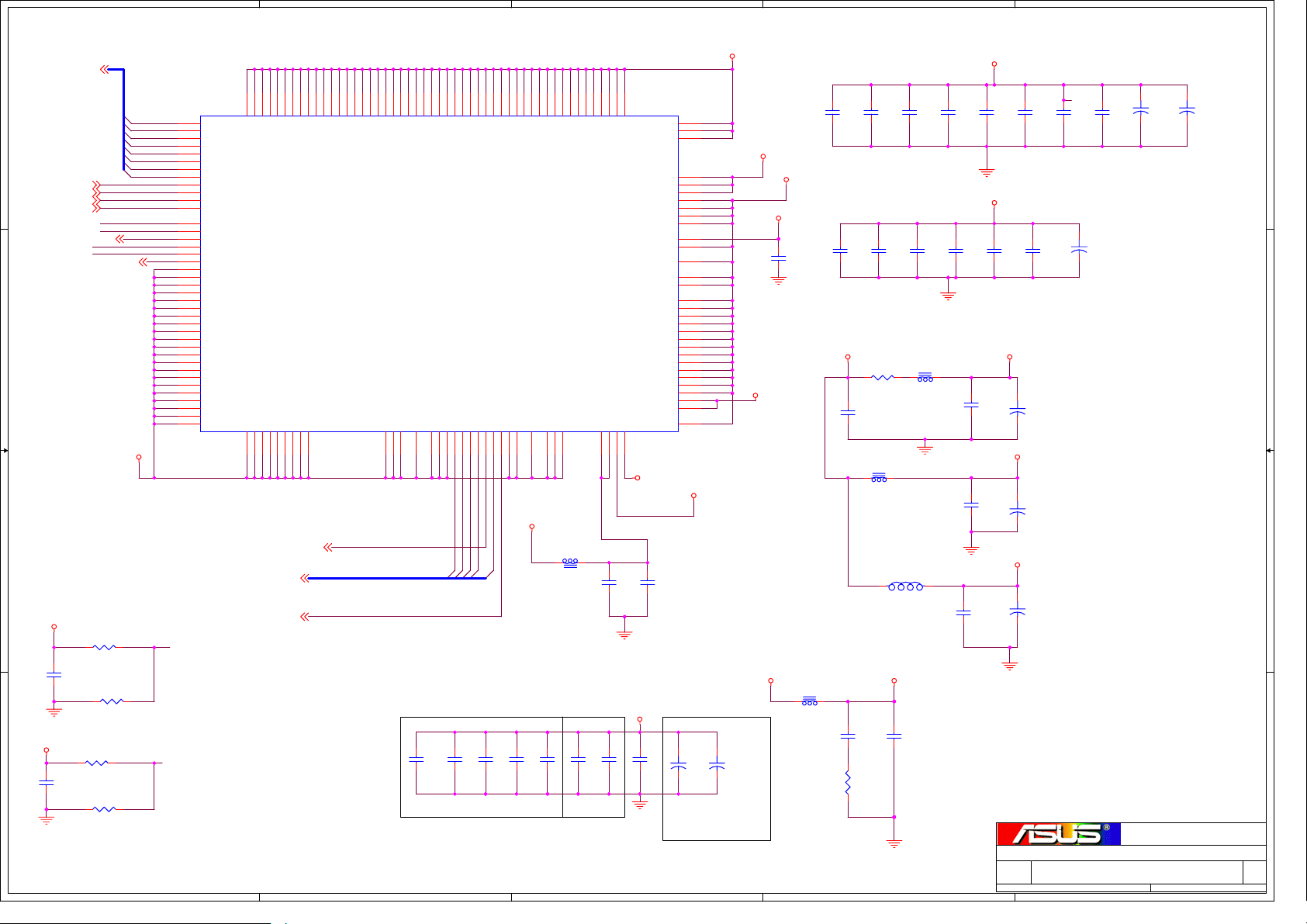

A

4

3

2

1

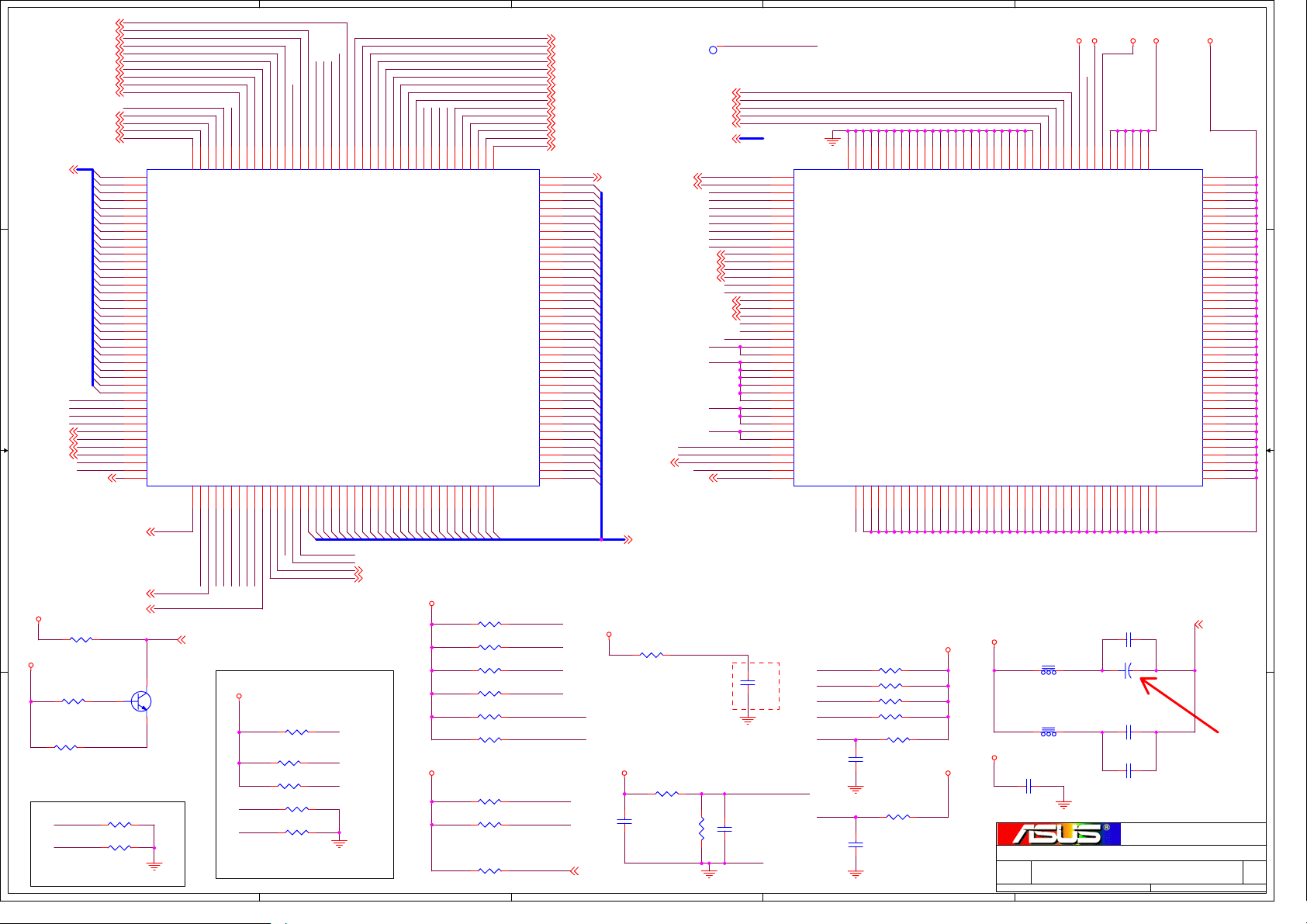

BROOK DALE

D D

CK_100/133_MCH

HL_CK_66M_MCH

AGP_CK_66M_HL

AGP 4X

G_CK_66M

CK TITAN

CLOCK CHIP

C C

CK_100/133_CPU/#

NORTHOOD

PCI_CLK_ICH

CK_14M_ICH_REF

CK_14M_AUD_ICH

CK_48M_USB

HL_CK_66M_ICH

PCI_CK_33M_SLOT1

PCI_CK_33M_SLOT2

PCI_CK_33M_SLOT3

PCI_CK_33M_SLOT4

AC97_CK_14M_AUD

MCH

AGP_SL1

ICH4

M_CHA_SCK[0..7]/#

DDR-1,2

AC97_BITCLK

AC'97

PCI_SL1

PCI_SL2

PCI_SL3

B B

FWH

PCI_CK_33M_FWH

PCI_CK_33M_LAN

NIC

PCI_SL4

GD82540

ITP

CK_100/133_ITP/#

SIO_CK_14M

KB_CLK

Keyboard

SUPER I/O

PCI_CK_33M_SIO

5

4

3

SMSC 47M554&534

MSE_CLK

Mouse

Title :

ASUStek Computer Inc.

Size Project Name

A3

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

Date: Sheet

Engineer:

2

Clock Distribution

1

William Yu

251Tuesday, January 28, 2003

of

Rev

A03

A

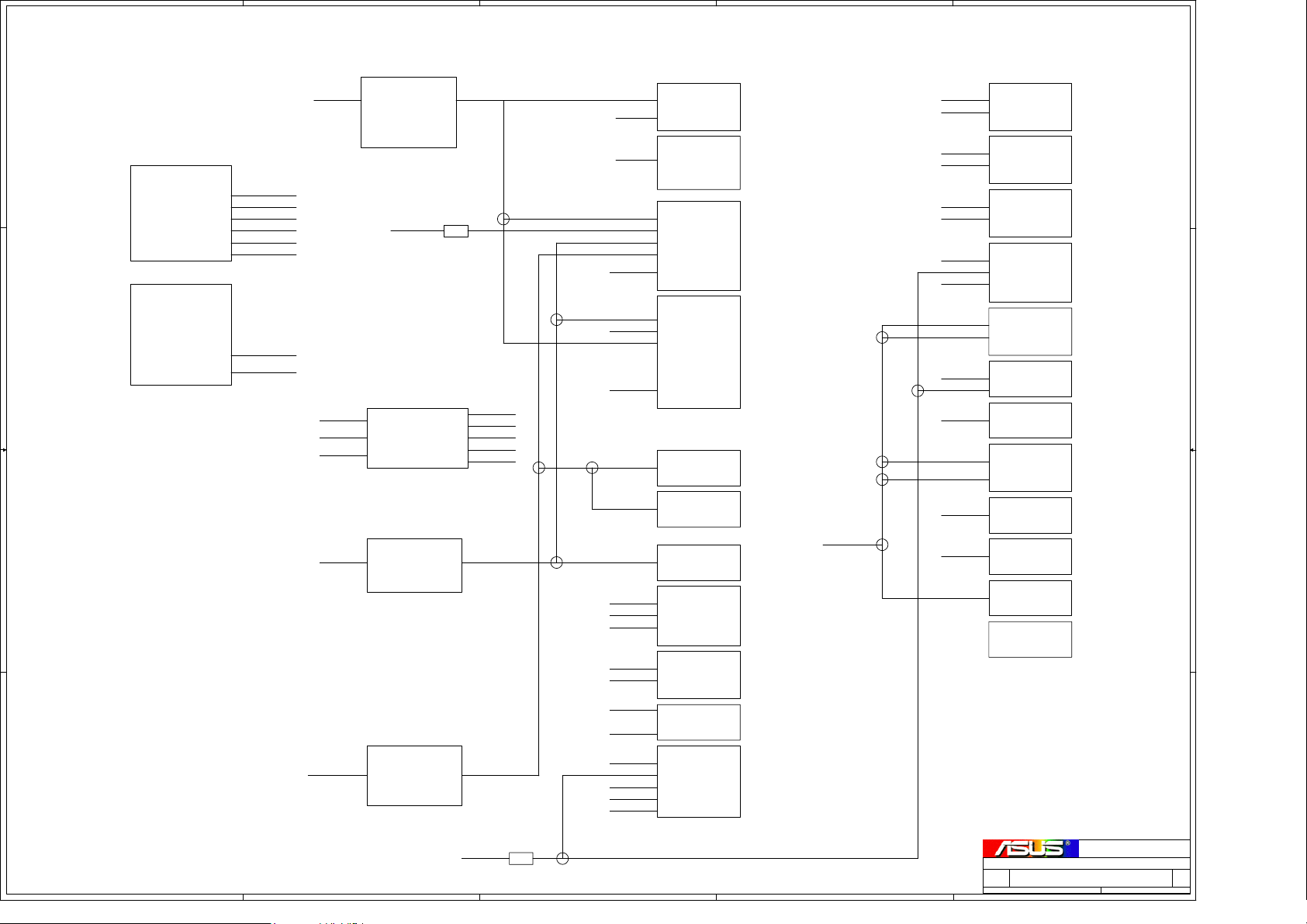

5

A

4

3

2

1

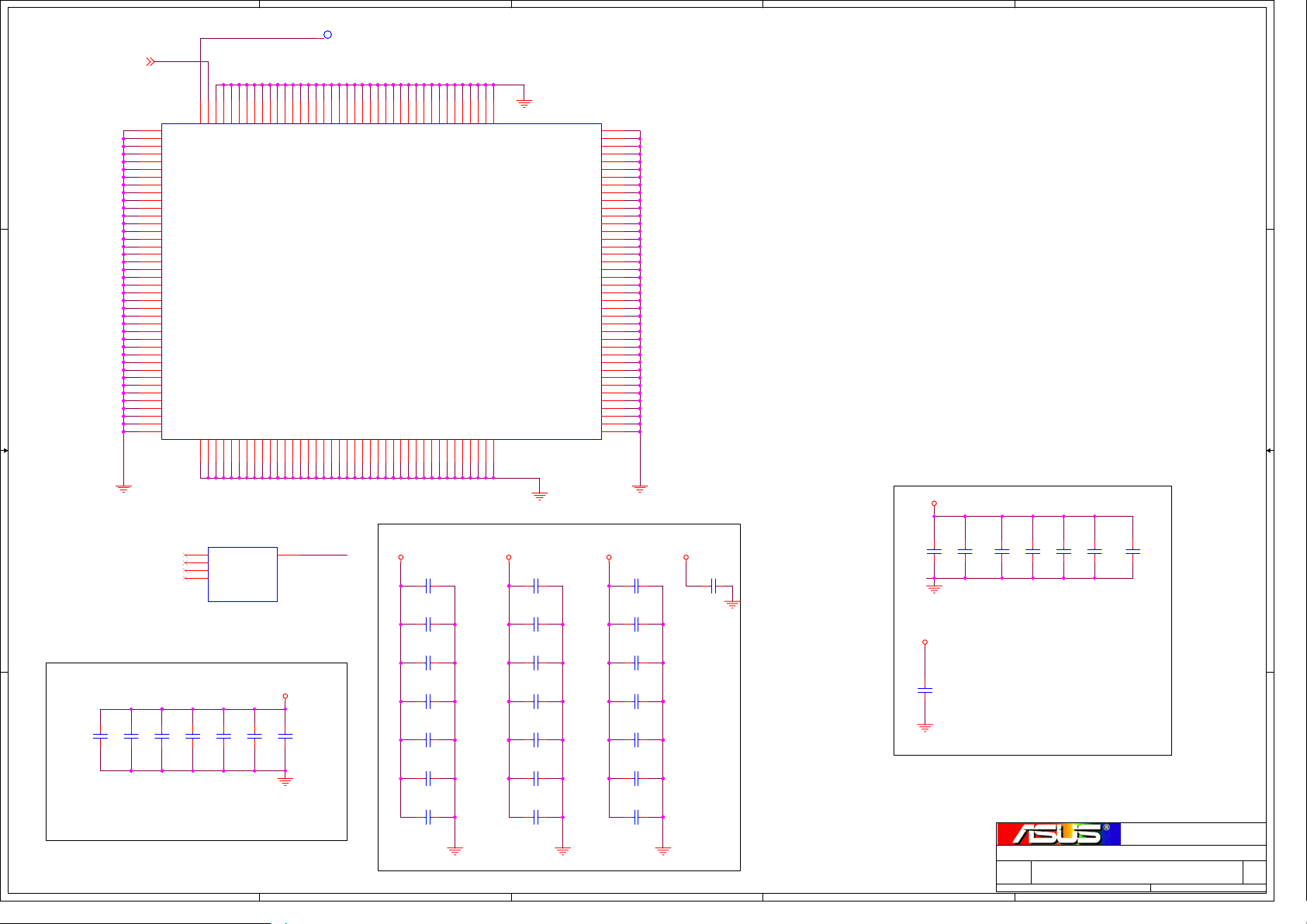

PCI_RST_SYS#

D D

VRM

FMB2

VRM_PWRGOOD

POWER CONTROL

& REGULATION

PWRGOOD

POWER

DIAG. LED

SUPPLY

3.3V_PWRGOOD#

VRM_PWRGOOD

3.3V_PWRGOOD

C C

RESET

PB_RESET#

BUTTON

BATTERY

RTCRST#

ICH_PWROKSYSTEM_PWRGOOD

ICH4

R

H_RESET#

H_DBR#

H_INIT#

H_INIT#

PCI_RST#

SM_BUS

SUPER

I/O

GMCH

845G/GL

P4 CPU

SOCKET 478

PCI_RST_SYS#

PCI_RST_SYS#

PCI_RST#

H_INIT#

PCI_RST#

GPO_PCI_SLT_EN

PCI_RST_SYS#

GPO_FWH_RST#

LEVEL SHIFT

PCI_RST_SYS#

PCI_RST_SYS#

FWH_INIT#

PCI_RST_SLOTS#

AGP

NIC

FWH

LPC HEADER

B B

RESUME

RESET

AC'97

CODEC

ICH_RSMRST#

AC97_RST#

PCI_RST#

PCI_RST#

IDE_PRST#

IDE_SRST#

IDE1

IDE2

PCI-1

PCI-2

EDGE CONNECTOR

<Variant Name>

A

Title :

ASUStek Computer Inc.

Size Project Name

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

A3

Date: Sheet

5

4

3

2

Engineer:

RESET MAP

Willliam Yu

1

Rev

351Tuesday, January 28, 2003

A03

of

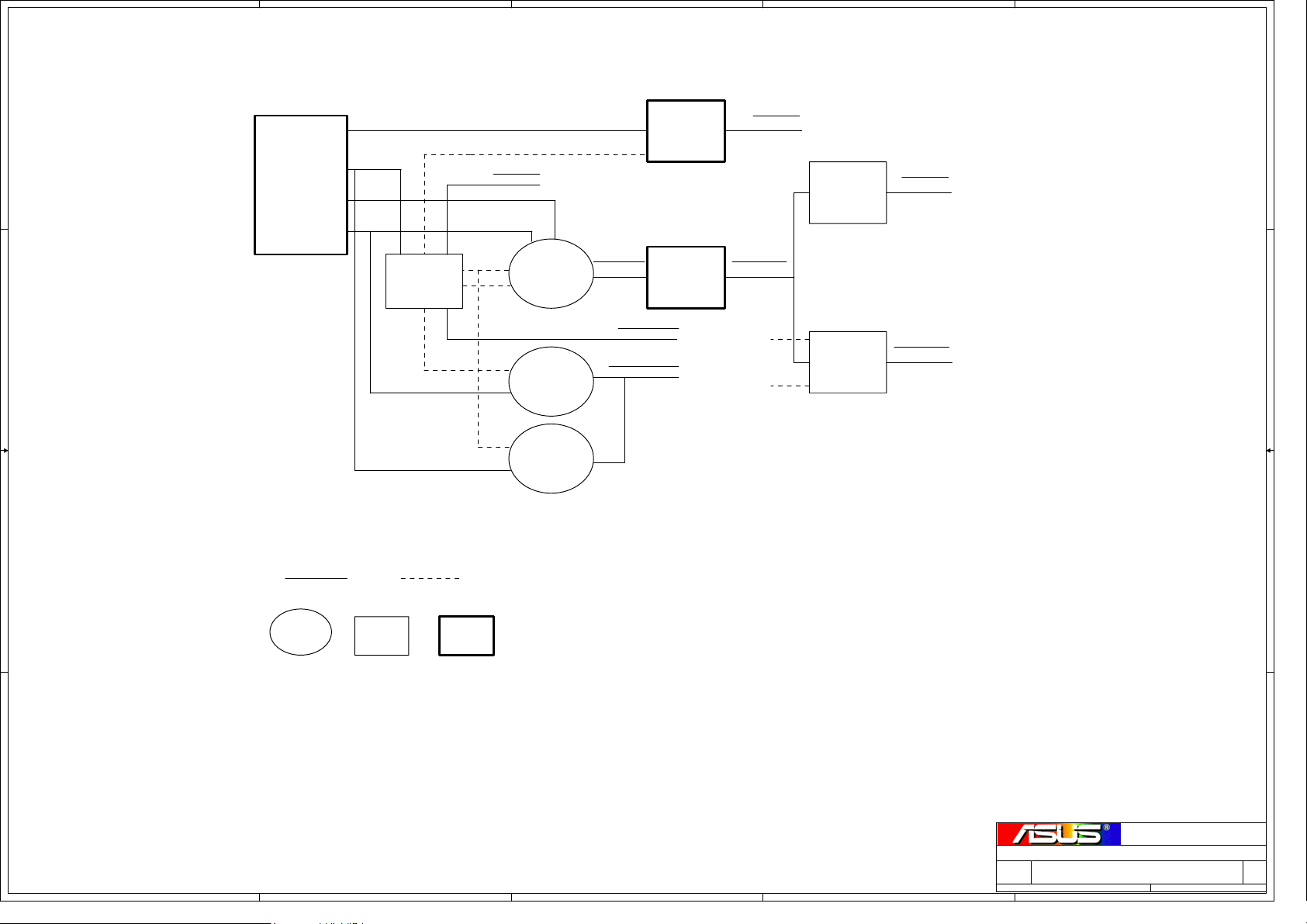

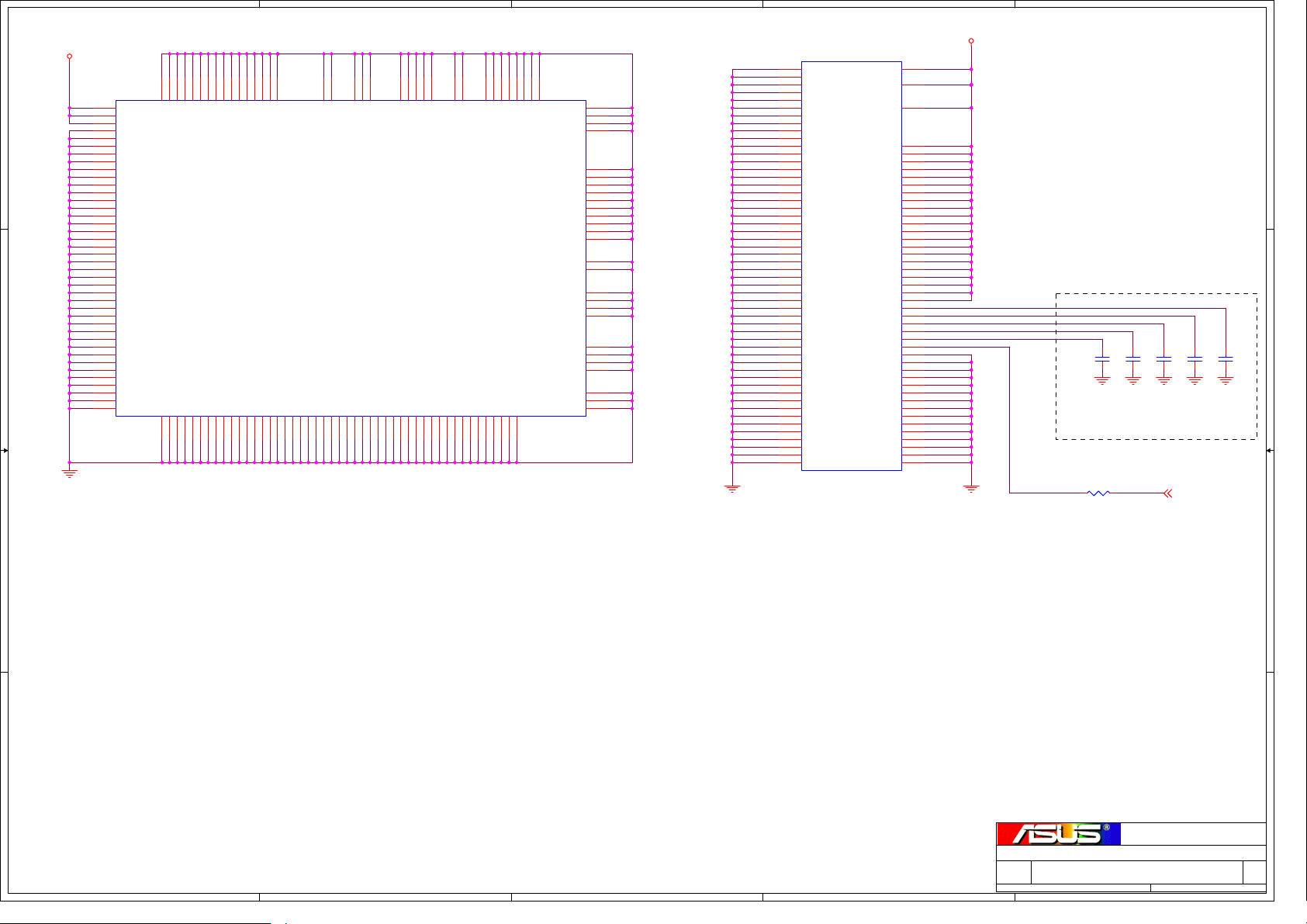

5

4

3

2

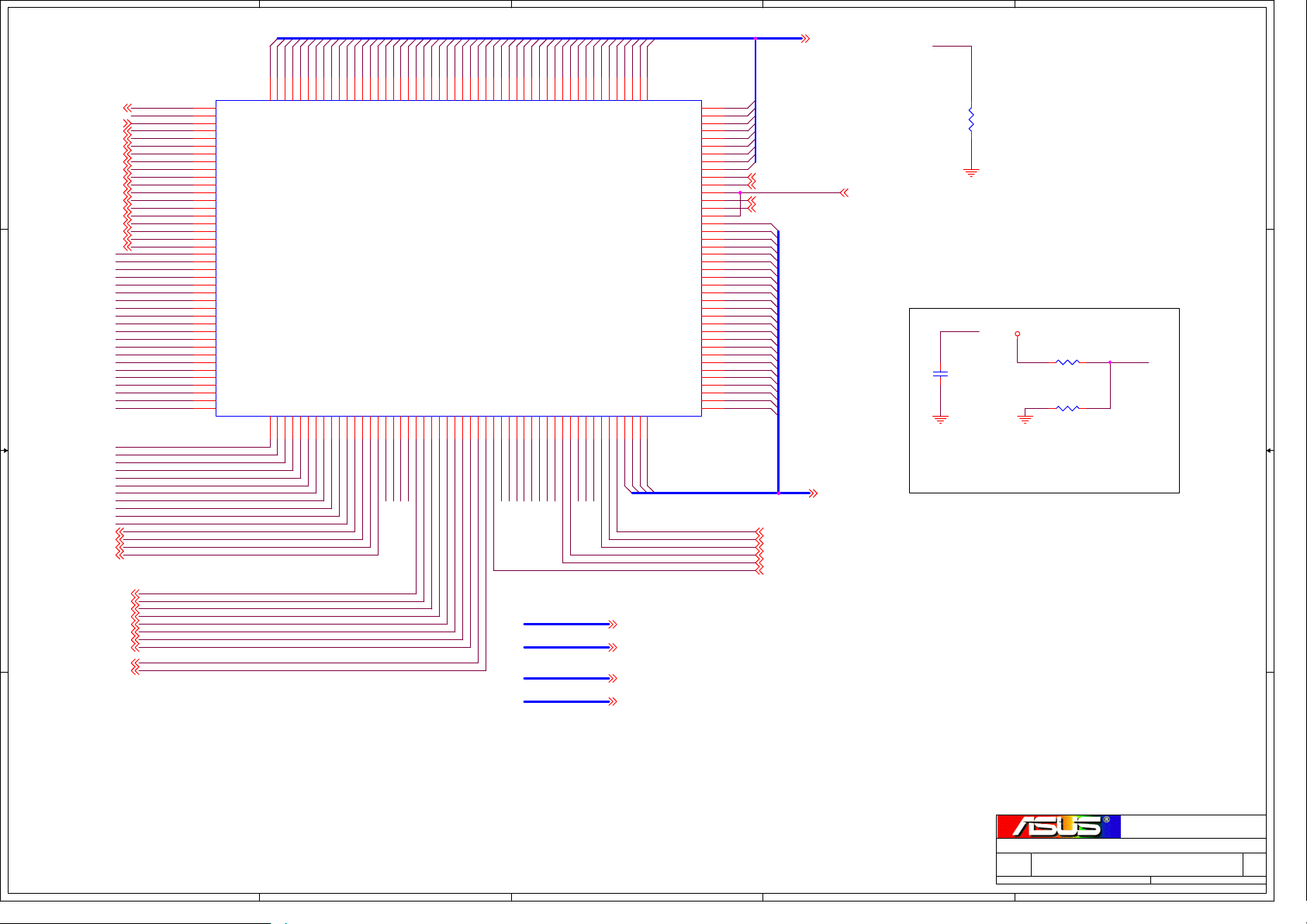

1

VRM 9.2 ON Board

+12V

FMB2:Iout=66A

7.9A 95W ->

D D

POWER SUPPLY

FOR JAZZ

200W TOTAL

80W SHARED

3.0 Volt

BATTERY

CR2032

220 mAh

C C

20mA Max

+3.3V

+5V_AUX

VBAT

ICH_VBAT

B B

A A

+12V

+5V

-5V

-12V

10A 120W

12.6A 63W

10A 33W

2A 10W

POWER SUPPLY

POWER SUPPLY

0.25uA 0.75uW

5uA 15uW

+3.3V

+5V_AUX

+5V

+2.5VSTBY

V_5P0_DUAL

85% efficient

14W Loss

S0,S1

+2.5VSTBY

ON BOARD REG

ISL6504

10.74A

ONBOARD 1.5V REG

6.12A 6.06W >

85% efficient

S0,S1

2.5VSTBY REG

14.95A

85% efficient

S0,S1,S3

FET

CPUCORE

+1.2V

+1.2V_PG

+1.5V_AUX

+3.3V_AUX

V_5P0_DUAL

1.5V

6.12A

+2.5VSTBY

+1.5V

+1.2V

+3.3V

+1.5V

+1.25V

+1.5V

+2.5VSTBY

+3.3V

+1.5V

+3.3V

+1.5V

ICH_VBAT

+2.5VSTBY

+2.5VSTBY

+1.5V

+3.3V

+5V

+12V

+5V

+3.3V

+1.5V

+3.3V

+3.3V

+3.3V_AUX

+5V

+12V

-12V

NORTHWOOD

66A 80W

S0,S1

CLOCK

0.28A 0.9W

S0,S1

BROOKDALE-GL

2.4A 3.6W

3.2A 4W

2.985A 4.48W

2.8A 7W

0.03A 0.09W

S0,S1,S3,S5

ICH4

1.06A 1.59W

610mA 200mW

45mA 68mW

5uA 15uW

S0,S1,S3,S5

DDR CORE

5.92A 14.8W

S0,S1,S3

DDR SPD

2.1A 5.25W

S0,S1

AGP I/O

2A 6.6W

S0,S1

AGP CORE

2.8A 9.3W

2A 10W

1A 12W

S0,S1

AUDIO

50mA 250mW

21mA 70mW

S0,S1

NIC

0.2A 0.8Waux

S0,S1,S3,S5

PCI/SLOT/RISER

7.6A 25W

0.04A 0.13W

5A 25W

0.5A 6W

0.1A 1.2W

+3.3V_AUX

+3.3V_AUX

+3.3V_AUX

V_5P0_DUAL

+5V

+12V

+5V

+12V

+5V

+12V

+3.3V

V_BAT

+5V

+5V_AUX

+12V

+5V

+5V

+5V_AUX

+12V

HDD 36G

0.7A 3.5W

0.7A 8.4W

S0

CD ROM

0.7A 3.5W

0.7A 8.4W

S0

FLOPPY

475mA 2.8W

0.25A 3W

S0

SUPER I/O

50mA 165mW

25A 83mW

250nA 750nW

S0,S1,S3,S5

PS2 KB/M

0.1A 0.5W

0.1A 0.5Waux

S0,S1,S3

2 SERIAL

2mA 20mW

100uA 330uW

PARALLEL

15mA 74mW

S0,S1

USB 6 PORT

3A 15W

0.1A 0.5W

S0,S1,S3

FWH

67mA 220mW

S0,S1

FAN / ea

0.5A 6W

S0,S1

CTRL_PNL

??A ??W

S0,S1

DIAG_LEDs

??A ??W

S0,S1

+3.3V_AUX

5

4

FET

ASUStek Computer Inc.

Size Project Name

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

C

3

2

Date: Sheet

Title :

Engineer:

1

Power Distribution

Rong Lin

Rev

A03

of

451Tuesday, January 28, 2003

5

4

3

2

1

D D

Silver Box

+12V

-12V

+3.3V

+1.2V

Idc=24mA

VRM OUTEN

ADP3160

Iocp

100A

66A

Imax

82%

eff.

+5V

CPUCORE

Idc=53A

AMS1505

Iocp

5A

4.12A

Imax

60%

eff.

+1.5V

Idc=3.3A

+5V_AUX

&

V_5P0_DUAL

Idc=9.5A

+1.5V_AUX

Idc=65mA

+3.3V_AUX

Idc=1.33A

ISL6520

Iocp

Imax

eff.

+12V_GATE

ISL6504

C C

+5VSB_GATE

3V3DLSB

PHD55N03LTA

BSL211SP

MJD44H11

+12V_GATE

N/A

14.95A

85%

+2.5VSTBY

Idc=12A

+12V

-12V

LM358D

+

SI4501DY

Iocp

Imax

eff.

N/A

2.1A

50%

+1.25V

Idc=1.68A

PHD45N03LTA

Note:

1. Referance document: Brookdale-G Chipset Platform Design

Guide, REV. 1.5, page 250, Fig. 14-1.

2. There is no power sequencing requirements

B B

Linear

Control Signal

Switching

Power Rail

Switch

ON/OFF

for 3.3V and 1.5V rails on Intel ICH4, page

260.

3. V5REF must be powered up before or simultaneously to

3.3V and there must not exist a difference of more than

two volts between the planes. This criterion had been

down by power supply vender, page 260.

4. Imax is mean to peak current refered to

power distribution on page 4.

5. Idc is mean to the sustain current , and is 80%

of Imax current.

6. Iocp is 1.5~2.0 times of Imax.

A A

Title :

ASUStek Computer Inc.

Size Project Name

A3

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

5

4

3

2

Date: Sheet

Engineer:

1

POWER FLOW

Rong Lin

551Tuesday, January 28, 2003

of

Rev

A03

5

4

3

2

1

S5->S0

+5V_AUX

D D

+3.3V_AUX

+1.5V_AUX

0

1-5ms

C C

0

1.CPUCORE must rise after the voltage across 90% of +1.2V,andthe interval

is within 1-5ms

2.VRM_OUTEN rises after the voltage across 90% of its specified

value

+3.3V_AUX

+1.5V_AUX

VRM_PWRGOOD

+12V

V_5P0_DUAL

&

+3.3V

+2.5VSTBY

CPUCORE

+1.5V

+1.25V

+1.2V

VRM_OUTEN

PS-ON

0

0

S0->S3

+12V

V_5P0_DUAL

B B

A A

+3.3V_AUX

+2.5VSTBY

CPUCORE

+1.5V_AUX

+1.25V

+1.2V

0

VRM_PWRGOOD

VRM_OUTEN

PS-OFF

0

S0:

Windows Running

S3:

Windows Standby

AC Power On Only

S5:

&

&

+3.3V

+1.5V

+12V,V_5P0_DUAL,+3.3V,+3.3V_AUX,+2.5VSTBY,CPUCORE,+1.5V,+1.5V_AUX,+1.25V,+1.2V existed

V_5P0_DUAL,+3.3V_AUX,+1.5V_AUX,+2.5VSTBY existed

+5V_AUX,+3.3V_AUX,+1.5V_AUX existed

5

V_5P0_DUAL

+3.3V_AUX

+2.5VSTBY

+1.5V_AUX

0

0

4

S0->S5

S3->S0

+12V

&

V_5P0_DUAL

+3.3V_AUX

+2.5VSTBY

CPUCORE

+1.5V_AUX

+1.25V

+1.2V

0

VRM_PWRGOOD

VRM_OUTEN

PS-OFF

0

+5V_AUX

+3.3V_AUX

+2.5VSTBY

+1.5V_AUX

0

0

1.CPUCORE must rise after the voltage across 90% of +1.2V,andthe interval

is within 1-5ms

2.VRM_OUTEN rises after the voltage across 90% of its specified

value

&

&&

+3.3V

+1.5V

1-5ms

V_5P0_DUAL

+5V_AUX

+3.3V_AUX

+1.5V_AUX

+3.3V_AUX

+1.5VSB

0

0

V_5P0_DAUL

&

+2.5VSTBY

CPUCORE

&

+1.25V

+1.2V

VRM_PWRGOOD

VRM_OUTEN

+12V

+3.3V

+1.5V

0

PS-ON

Title :

ASUStek Computer Inc.

Size Project Name

A

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

3

Date: Sheet

2

Engineer:

0

POWER SEQUENCE

William Yu

of

651Tuesday, January 28, 2003

1

Rev

A03

5

,

+3.3V V3_PLL_CLKGEN

D D

ICH_SLP_S3#

40,42)

C C

12

C12

0.1U

NI

L2

21

600OHM/200mA

NI

R10 4.7K

1 2

C22

0.1U

12

C13

4.7U

NI

1 2

12

12

C14

0.1U

NI

R466

0

R11

1 2

8.2K

NI

12

C15

0.1U

V_3P3_CLKPWR_L

V_3P3_CLKPWR_L

VMAIN_SMB_CLK(15,35)

VMAIN_SMB_AD(15,35)

R21 475

Iref=2.32mA

V3_48M_CLKGEN

12

C486

4.7U

V3_48M_CLKGEN

V3_PLL_CLKGEN

14M_X1

14M_X2

NC_CK_RST

CLKVCC_PG#

CLK_PWR_DWN#

1 2

1%

SMBus must routed 5/15

1 2

12

C16

24

2

34

46

39

32

9

18

3

4

26

25

20

19

42

35

21

47

33

43

36

29

5

13

0.1U

4

+3.3V

R2

10

GND

U35

VDD_48MHZ

VDD_REF

VDD_CORE

VDD_CPU_46

VDD_CPU_39

VDD_3V66

VDD_PCI_9

VDD_PCI_18

X1

X2

SCLK

SDATA

RST#

VTT_PWRGD#

PWR_DWN#

IREF

GND_48MHZ

GND_REF

GND_CORE

GND_CPU_43

GND_CPU_36

GND_3V66

GND_PCI_5

GND_PCI_13

CY28323

+3.3V

3V66_31

3V66_30

3V66_28

3V66_27

CPU0#_1

CPU0#_2

CPU1#_1

CPU1#_2

CPU_ITP#

CPU_ITP

FSO/48MHZ

FS1/24_48MHZ

FS2/PCI_F0

FS3/PCI_F1

PCI_F2

FS4/PCI0

PCI1

PCI2

PCI3

PCI4

PCI5

PCI6

MULTSEL0/REF0

MULTSEL1/REF1

12

C1

0.1U

31

30

28

27

CK_100M_MCH_R#

40

CK_100M_MCH_R

41

CK_100M_CPU_R#

37

CK_100M_CPU_R

38

CK_100M_ITP_R#

44

CK_100M_ITP_R

45

CK_48M_DOT_R

22

CK_48M_ICH_R

23

PCI_CK_33M_SLT1_R

6

PCI_CK_33M_ICH_R

7

PCI_CK_33M_VRISER_R

8

PCI_CK_33M_SLT2_R

10

PCI_CK_33M_LAN_R

11

PCI_CK_33M_SLT3_R

12

NC_PCI_3

14

PCI_CK_33M_SLT4_R

15

PCI_CK_33M_SIO_R

16

PCI_CK_33M_FWH_R

17

48

1

L1

21

600OHM/200mA

L3

21

600OHM/200mA

CK_66M_MCH_R

CK_66M_ICH_R

NC_CK_3V66

CK_66M_AGP_R

CK_14M_AUD_CODEC_R

CK_14M_2_R

12

C2

0.1U

3

12

12

CK_100M_CPU_R#

CK_100M_CPU_R

CK_100M_MCH_R#

CK_100M_MCH_R

CK_100M_ITP_R#

CK_100M_ITP_R

C4

C3

0.1U

R5 27.41%

12

C5

0.1U

0.1U

1 2

R7 27.4

1%

1 2

R9 27.41%

1 2

R12 27.41%

1 2

R13 27.41%

1 2

R14 27.41%

1 2

2

V_3P3_CLKPWR_L

12

12

C6

0.1U

R15

49.9

1 2

1%

12

C7

C8

0.1U

0.1U

R16

R17

49.9

49.9

1 2

1 2

1%

1 2

1%

R18

49.9

1%

12

12

C10

C9

4.7U

0.1U

R20

R19

49.9

49.9

1 2

1 2

1%

1%

CK_66M_MCH_R

CK_66M_ICH_R

12

C11

CK_66M_AGP_R

4.7U

CK_100M_CPU# (8)

CK_100M_CPU (8)

CK_100M_MCH# (10)

CK_100M_MCH (10)

CK_100M_ITP# (8)

CK_100M_ITP (8)

R1 33

1 2

R3 33

1 2

R4 33

1 2

AGP

CK_48M_DOT_R

CK_48M_ICH_R

1 2

1 2

27

1

CK_66M_MCH (10)

CK_66M_ICH (19)

12

C19

47PF

NI

12

CK_66M_AGP (17)

CK_48M_DOT (10)

CK_48M_ICH (19)

C21

47PF

NI

12

12

C18

C17

47PF

47PF

NI

27

R8

NI

R6

12

C20

47PF

NI

PCI_CK_33M_SLT1_R

PCI_CK_33M_ICH_R

R152

8.2K

NI, Shasta 8.2K ohm

1 2

R42

4.7K

NI

1 2

PCI_CK_33M_VRISER_R

PCI_CK_33M_SLT2_R

PCI_CK_33M_LAN_R

X14MHZ

12

B B

A A

14M_X1

1 2

12

C23

15P

NI

RN1A10K

RN1B10K

RN1C10K

1 8

2 7

3 6

14.31818MHZ

GND

RN1D

10K

4 5

PCI_CK_33M_SLT2

5

14M_X2

12

R311M NI

1 2

PCI_CK_33M_ICH

PCI_CK_33M_VRISER

C24

V_3P3_CLKPWR_L

R40

10K

CK_48M_DOT

PCI_CK_33M_SLT1

15P

NI

V_3P3_CLKPWR_L

H_BSEL0(8,11)

+CPUCORE

1 2

R33

2.2K

Shasta= NI

1 2

V_3P3_CLKPWR_L

R41

220

4

CK_48M_ICH

R32

8.2K

Shasta= NI

1 2

Q1

B

1

PMBS3904

R38

8.2K

1 2

CLKVCC_PG#

3

C

E

2

R22 33

1 2

R24 33

1 2

R26 33

1 2

R28 33

1 2

R30 33

1 2

CK_14M_AUD_CODEC_R

CK_14M_2_R

V_3P3_CLKPWR_L

R37

1 2

8.2K

NI

12

3

C442

47PF

NI

1 2

12

12

C441

47PF

NI

R34 33

1 2

R35 22

1 2

R36 22

1 2

R39

1K

C440

47PF

NI

12

PCI_CK_33M_SLT1 (27)

PCI_CK_33M_ICH (19)

PCI_CK_33M_VRISER (27)

PCI_CK_33M_SLT2 (27)

PCI_CK_33M_LAN (28)

12

12

C25

47PF

NI

C439

47PF

NI

C438

47PF

NI

CK_14M_AUD_CODEC (24)

CK_14M_ICH (19)

SIO_CK_14M (31)

12

12

C27

C26

47PF

47PF

NI

NI

equal trace length

PCI_CK_33M_SLT3_R

PCI_CK_33M_SLT4_R

PCI_CK_33M_FWH_R

PCI_CK_33M_SIO_R

2

R23 33

1 2

R25 33

1 2

R27 33

1 2

R29 33

1 2

12

C436

47PF

NI

12

C437

47PF

NI

Clock Funcation

FS4 FS3 FS2 FS1 FS0 Function

1 1 1 0 1 100 MHZ CPU

1 1 1 1 1 133 MHZ CPU

ASUStek Computer Inc.

Size Project Name

A3

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

Date: Sheet

12

12

C434

47PF

NI

Title :

Engineer:

1

PCI_CK_33M_SLT3 (49)

PCI_CK_33M_SLT4 (49)

PCI_CK_33M_FWH (30)

PCI_CK_33M_SIO (31)

C435

47PF

NI

CLOCK GEN.

WIlliam Yu

751Tuesday, January 28, 2003

of

Rev

A03

5

H_FERR#(20)

H_HIT#(11)

H_HITM#(11)

H_IGNNE#(20)

H_INIT#(20,30)

CK_100M_ITP(7)

CK_100M_ITP#(7)

H_INTR(20)

H_NMI(20)

H_LOCK#(11)

D D

C C

B B

+CPUCORE

A A

H_PWRGOOD(20 )

HREQ#0(11)

HREQ#1(11)

HREQ#2(11)

H_A#[3..31](10)

NC_H_A32

NC_H_A33

NC_H_A34

NC_H_A35

H_A20M#(20)

H_ADS#(10)

H_ADSTB#0(10)

H_ADSTB#1(10)

+3.3V

NC_AP#0

NC_AP#1

CK_100M_CPU(7)

CK_100M_CPU#(7)

R44

1 2

8.2K

R52

1 2

1K

R58

1 2

MMBT3904LT1

56

R64 51.1

H_COMP0

1 2

R68 51.1

H_COMP1

1 2

Placed inside the socket cavity

H_A#3

K2

H_A#4

K4

H_A#5

L6

H_A#6

K1

H_A#7

L3

H_A#8

M6

H_A#9

L2

H_A#10

M3

H_A#11

M4

H_A#12

N1

H_A#13

M1

H_A#14

N2

H_A#15

N4

H_A#16

N5

H_A#17

T1

H_A#18

R2

H_A#19

P3

H_A#20

P4

H_A#21

R3

H_A#22

T2

H_A#23

U1

H_A#24

P6

H_A#25

U3

H_A#26

T4

H_A#27

V2

H_A#28

R6

H_A#29

W1

H_A#30

T5

H_A#31

U4

V3

W2

Y1

AB1

C6

G1

L5

R5

AC1

V5

AF22

H_BNR#(10)

H_BPRI#(10)

Q2

1

B

H_PROCHOT#

1%

1%

H_PROCHOT#

CPU1A

A#[03]

A#[04]

A#[05]

A#[06]

A#[07]

A#[08]

A#[09]

A#[10]

A#[11]

A#[12]

A#[13]

A#[14]

A#[15]

A#[16]

A#[17]

A#[18]

A#[19]

A#[20]

A#[21]

A#[22]

A#[23]

A#[24]

A#[25]

A#[26]

A#[27]

A#[28]

A#[29]

A#[30]

A#[31]

A#[32]

A#[33]

A#[34]

A#[35]

A20M#

ADS#

ADSTB#[0]

ADSTB#[1]

AP#[0]

AP#[1]

BCLK[0]

3

C

E

2

1%

1%

GND

5

NC_H_MCERR#

J4K5J1

AB23C3V6G4E5D1AD26

REQ#[1]

REQ#[0]

BINIT#

BNR#

AA3G2AC6

NC_BINIT#

PWRGOOD

PROCHOT#

BPM#[0]

BPM#[1]

AB5

AC4Y6AA5

H_BPM#0

H_BPM#2

H_BPM#1

+CPUCORE

LOCK#

MCERR#

BPM#[2]

BPM#[3]

H_BPM#3

H_BPM4/PRDY#

H_TRST#

H_TCK

REQ#[2]

BCLK[1]

AF23

GPI_PROCHOT# (31)

AC26W5B2

INIT#

LINT1

LINT0

IGNNE#

ITP_CLK1

ITP_CLK0

BPM#[4]

BPM#[5]

BPRI#

BR0#

BSEL0

BSEL1

AB4D2H6

AD6

AD5

NC_H_BSEL1

H_BPM5/PREQ#

1 2

150

1%

1 2

1 2

1%

R63 680

1 2

R67 27

1 2

H_GTLREF0

NC_GTLREF3

NC_GTLREF2

NC_H_IEER#

AC3E3F3F6F20

AA6

HIT#

IERR#

HITM#

GTLREF4

GTLREF3

GTLREF2

P4_SOCKET478

COMP[0]

COMP[1]

D#[0]

D#[01]

D#[02]

D#[03]

L24P1B21

B22

A23

A25

H_D#1

H_D#3

H_D#0

H_D#2

H_COMP1

H_COMP0

INTERPOSER

R56

H_TDI

R5939

H_TMS

R6075

H_TDO

GND

4

Choose the closest GTLREFx pins to

contact H_GTL_REF0

NC_GTLREF1

NC_H_DP#3

AA21B6W23

P23

J23

F21

W22

R22

K22

E22H2L25

DSTBP#[0]

DSTBN#[3]

DSTBN#[2]

DSTBN#[1]

D#[09]

D#[10]

D#[11]

D#[12]

G22

H21

C26

H_D#11

H_D#12

H_D#10

4

DSTBN#[0]

D#[13]

D23

J21

H_D#14

H_D#13

DP#[3]

DRDY#

D#[14]

D#[15]

D25

H_D#15

+CPUCORE

+CPUCORE

FERR#

GTLREF1

D#[04]

D#[05]

C21

D22

B24

H_D#5

H_D#4

H_D#6

DSTBP#[3]

DSTBP#[2]

DSTBP#[1]

D#[06]

D#[07]

D#[08]

C23

C24

B25

H_D#9

H_D#8

H_D#7

H_BSEL0 (7,11)

H_BREQ#0 (10)

NC_H_DP#1

NC_H_DP#2

K26

K25

J26E2H5

DP#[2]

DP#[1]

DP#[0]

D#[16]

D#[17]

D#[18]

H22

E24

G23

H_D#18 NC_H_DP#0

H_D#16

H_D#17

AE25

V21

P26

G25

DBR#

DBSY#

DBI#[3]

DBI#[2]

DBI#[1]

DEFER#

D#[19]

D#[20]

D#[21]

D#[22]

D#[23]

D#[24]

F23

F24

E25

F26

D26

L21

H_D#20

H_D#19

H_D#21

H_D#22

H_D#23

H_D#24

R43 49.9

1 2

1%

R45 49.9

1 2

1%

R47 49.9

1 2

1%

R51 49.9

1 2

R54 49.9

1 2

R57 49.9

1 2

R62 56

1 2

R65 330

1 2

R69

1 2

220

DBI#[0]

D#[63]

D#[62]

D#[61]

D#[60]

D#[59]

D#[58]

D#[57]

D#[56]

D#[55]

D#[54]

D#[53]

D#[52]

D#[51]

D#[50]

D#[49]

D#[48]

D#[47]

D#[46]

D#[45]

D#[44]

D#[43]

D#[42]

D#[41]

D#[40]

D#[39]

D#[38]

D#[37]

D#[36]

D#[35]

D#[34]

D#[33]

D#[32]

D#[31]

D#[30]

D#[29]

D#[28]

D#[27]

D#[26]

D#[25]

1%

1%

1%

H_DSTBP#3 (11)

H_DSTBP#2 (11)

H_DSTBP#1 (11)

H_DSTBP#0 (11)

H_DSTBN#3 (11)

H_DSTBN#2 (11)

H_DSTBN#1 (11)

H_DSTBN#0 (11)

H_DRDY# (10)

H_DEFER# (1 0)

H_DBSY# (10)

H_DBR# (39)

H_DBI#3 (10)

H_DBI#2 (10)

H_DBI#1 (10)

E21

H_D#63

AA24

H_D#62

AA22

H_D#61

AA25

H_D#60

Y21

H_D#59

Y24

H_D#58

Y23

H_D#57

W25

H_D#56

Y26

H_D#55

W26

H_D#54

V24

H_D#53

V22

H_D#52

U21

H_D#51

V25

H_D#50

U23

H_D#49

U24

H_D#48

U26

H_D#47

T23

H_D#46

T22

H_D#45

T25

H_D#44

T26

H_D#43

R24

H_D#42

R25

H_D#41

P24

H_D#40

R21

H_D#39

N25

H_D#38

N26

H_D#37

M26

H_D#36

N23

H_D#35

M24

H_D#34

P21

H_D#33

N22

H_D#32

M23

H_D#31

H25

H_D#30

K23

H_D#29

J24

H_D#28

L22

H_D#27

M21

H_D#26

H24

H_D#25

G26

H_BPM#0

H_BPM#1

H_BPM#2

H_BPM#3

H_BPM4/PRDY#

H_BPM5/PREQ#

H_FERR#

H_PWRGOOD

H_BREQ#0

3

H_DBI#0 (10)

H_THERMTRP#(20)

TRCPU/TR1001G Routing

10/10,use ground guards

enclosed

H_D#[0..63] (10,11)

+CPUCORE

R46 49.9

1 2

+CPUCORE

1 2

12

C487

0.1U

H_BREQ#0 (10)

3

H_VID[0..4](41)

HREQ#3(11)

HREQ#4(11)

H_RESET#(10)

H_RS#0(11)

H_RS#1(11)

H_RS#2(11)

H_CPUSLP#(20)

H_STPCLK#(20)

NC_H_THRM_ANODE

NC_H_THRM_CATHODE

H_THERMTRP#

H_TRDY#(11)

CAD NOTES:

1%

R61 49.9

1%

R66

100

1%

T1

TP_33X47

NC

H_VID0(41)

H_VID1(41)

H_VID2(41)

H_VID3(41)

H_VID4(41)

NC_H_RSVD1

NC_H_RSVD2

NC_H_RSVD3

NC_H_RSVD4

NC_H_RSVD5

NC_H_RSVD6

NC_H_RSVD7

NC_H_RSVD8

H_SMI#(20)

TESTHI_PU_0

TESTHI_PU_2

TESTHI_PU_8

TESTHI_PU_11

H_TMS

H_RESET#

12

GND

2

1

NC_H_RSP#

NC_H_AF26

NC_H_VCCSENSE

BOTTOMSIDE FOR ICT

J3

H3

A22

A7

AD2

AD3

AE21

AF3

AF24

AF25

AB25

F1

G5

F4

AB2

AF26

AB26

B5

Y4

H_TCK

D4

H_TDI

C1

H_TDO

D5

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

A6

AD25

B3

C4

A2

F7

J6

GND

CPU1B

REQ#[3]

REQ#[4]

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

RESERVED7

RESERVED8

RESET#

RS#[0]

RS#[1]

RS#[2]

RSP#

SKTOCC#

SLP#

SMI#

STPCLK#

TCK

TDI

TDO

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

THERMDA

THERMDC

THERMTRIP#

TMS

TRDY#

AB14

VSS25

AB12

AB10

VSS24

TRST#

E6

A10

H_TRST#

VSS23

VCC1

NEED +1.2V@50mA

AA9

AA7

AA4

AA26

AA23

AA19

AA17

AA15

VSS22

VSS21

VSS20

VSS19

VSS18

VSS17

VSS16

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

A12

A14

A16

A18

A20A8AA10

AA12

AA13

VSS15

VSS14

VCC9

VCC10

AA14

AA11

VSS13

VCC11

AA16

AA1A9A3

VSS12

VSS11

VCC12

VCC13

AA18

AA8

VSS10

VCC14

AB11

A26

VSS9

VCC15

AB13

A24

VSS8

VCC16

AB15

A21

VSS7

VCC17

AB17

A19

A17

A15

A13

A11

D10

AE1

AE2

VID4

VSS4

VSS3

VSS2

VSS1

VID3

VSS6

VSS5

P4_SOCKET478

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AE3

AC8

VID2

VCC26

AE4

VID1

VCC27

AD11

AE5

AF4A5AE23

VID0

VCCVID

VCC28

VCC29

AD13

AD15

NC_H_VCCSENSE

AD20F9F19

VCCA

VCCIOPLL

VCCSENSE

VCC30

VCC31

VCC32

AD17

AD19

AD7

AD9

VCC85

VCC33

VCC84

VCC34

AE10

F17

VCC83

VCC35

AE12

F15

AE14

DATA: same group, route within +/-100mils of associated strobes (pad to pad length).

ADDRESS: same group, route within +/-200mils of associated strobes (pad to pad length).

STROBES: a strobe and its complement should be routed to +/-25mils of the same length.

Data, Address, Strobe and Clock should be routed 7mils with a 13mil spacing.

1 2

22U/10V

C281UNI

C29

+

C31

22U

C32

1U

Title :

Engineer:

GND

12

12

C30

22P

NI

reserved

H_GTLREF0

C34

0.1U

Near CPU PINS

TESTHI_PU_0

TESTHI_PU_2

TESTHI_PU_8

TESTHI_PU_11

H_INIT#

H_BSEL0

1 2

1 2

1 2

1 2

12

C540

0.1U

NI

12

C541

0.1U

NI

R4862

R5062

R5362

R5562

R498

1 2

220

NI

R499

1 2

220

NI

2

+CPUCORE

+3.3V

+CPUCORE

L4

VCCA H_VSSA

21

4.7UH/50mA

L5

VCCIOPLL

21

+1.2V

4.7UH/50mA

C33

12

0.1U

ASUStek Computer Inc.

Size Project Name

A3

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

Date: Sheet

VCC82

VCC36

1

F13

AE16

12

NI

12

12

1

VCC81

VCC37

+CPUCORE +CPUCOREVCCIOPLL+1.2V VCCA

F11

VCC80

VCC38

AE18

VCC79

VCC78

VCC77

VCC76

VCC75

VCC74

VCC73

VCC72

VCC71

VCC70

VCC69

VCC68

VCC67

VCC66

VCC65

VCC64

VCC63

VCC62

VCC61

VCC60

VCC59

VCC58

VCC57

VCC56

VCC55

VCC54

VCC53

VCC52

VCC51

VCC50

VCC49

VCC48

VCC47

VCC46

VCC45

VCC44

VCC43

VCC42

VCC41

VCC40

VCC39

AE20

P4-478 CPU-1

Willam Yu

851Tuesday, January 28, 2003

E8

E20

E18

E16

E14

E12

E10

D9

D7

D19

D17

D15

D13

D11

C8

C20

C18

C16

C14

C12

C10

B9

B7

B19

B17

B15

B13

B11

AF9

AF7

AF5

AF21

AF2

AF19

AF17

AF15

AF13

AF11

AE8

AE6

H_VSSA (9)

Note: the

board file

correct it by

silkscreen

only

of

Rev

A03

5

NC_H_VSSENSE

H_VSSA(8)

T2

1

TP_33X47

NC

4

BOTTOM SIDE FOR

ICT/ FVS

3

2

1

A4

AD22Y5Y25

Y22Y2W6W3W24

W21V4V26

V23V1U5

U25

U22U2T6T3T24

T21R4R26

R23R1P5

P25

P22P2N6N3N24

VSS156

VSS155

VSS93

VSS94

C495

10U

1 2

C499

10UNI

1 2

C502

10U NI

1 2

C505

10U

1 2

C508

10U

1 2

C511

10U

1 2

C514

10U

1 2

VSS154

VSS153

VSS95

VSS96

D14

D16

N21M5M25

VSS152

VSS151

VSS97

VSS98

D18

D20

VSS150

VSS149

VSS99

VSS100

D21

D24D3D6

D D

C C

GND

B B

12

C242

0.1U

A A

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

12

C243

0.1U

5

CPU1C

VSS26

VSS27

VSS28

VSS29

VSSSENSE

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

AF10

AF12

CPU1D

MH1

MH2

MH3

MH4

P4_SOCKET478

12

12

C245

C244

0.1U

0.1U

Decoupling

VSSA

VSS181

VSS180

VSS67

VSS68

VSS69

AF14

AF16

post_nc1

post_nc2

post_nc3

post_nc4

12

VSS179

VSS70

AF18

AF20

C246

0.1U

VSS178

VSS177

VSS71

VSS72

AF6

AF8

12

VSS176

VSS175

VSS174

VSS73

VSS74

VSS75

B10

B12

B14

NC

+CPUCORE

C247

0.1U

VSS173

VSS172

VSS76

VSS77

B16

B18

B1

12

C248

0.1U

GND

VSS171

VSS170

VSS169

VSS168

VSS167

VSS166

VSS165

VSS164

VSS163

P4_SOCKET478

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

B20

B23

B26B4B8

C11

C13

C15

NC_H_B1

VSS162

VSS87

C17

C19C2C22

VSS161

VSS160

VSS88

VSS89

4

VSS159

VSS158

VSS157

VSS90

VSS91

VSS92

C25C5C7C9D12

+CPUCORE

GND

M22M2L4

VSS144

VSS143

GND

C496

10U

C500

10UNI

C503

10U

C512

10U

C515

10U

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS148

VSS147

VSS146

VSS145

VSS101

VSS102

VSS103

VSS104

D8

+CPUCORE +CPUCORE

1 2

1 2

1 2

C506 10U

1 2

C509 10U

1 2

1 2

1 2

L26

L23

L1

K6

K3

K24

K21

J5

J25

J22

J2

H4

H26

H23

H1

G6

G3

G24

G21

F8

F5

F25

F22

F2

F18

F16

F14

F12

F10

E9

E7

E4

E26

E23

E19

E17

E15

E13

E11

E1

GND

C497

10U

1 2

C501

10UNI

1 2

C504

10U

1 2

C507

10U

1 2

C510

10U

1 2

C513

10U

1 2

C516

10U

1 2

+CPUCORE

12

+CPUCORE

C498

10U

1 2

12

C489

C488

10U

10U

12

C491

10U

12

C492

10U

NI

12

12

C494

C493

10U

10U

12

C490

10U

Placed on the socket's Cave

+CPUCORE

12

C517

10U

Title :

ASUStek Computer Inc.

Size Project Name

A3

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

3

2

Date: Sheet

Engineer:

1

P4-478 CPU-2

Willliam Yu

951Tuesday, January 28, 2003

of

Rev

A03

5

4

3

2

1

H_D#[0..63] (8,11)

H_D#56

H_D#55

H_D#58

H_D#57

B23

B24

U2A

M34

G15

H16

U33

D22

U31

N36

N33

C35

B33

C26

U36

D14

T36

L2

W2

T34

D7

C7

V4

V2

W4

W5

U5

U4

U2

V3

T2

T3

T4

R2

R5

R7

T8

P3

P8

K4

K2

J2

M3

ADS#

AGP_RCOMP

AGP_VREF

BLUE

BLUE#

BNR#

BPRI#

BREQ0#

CPURST#

DBSY#

DDCA_CLK

DDCA_DATA

DEFER#

DINV_0#

DINV_1#

DINV_2#

DINV_3#

DRDY#

DREFCLK

GAD_0

GAD_1

GAD_2

GAD_3

GAD_4

GAD_5

GAD_6

GAD_7

GAD_8

GAD_9

GAD_10

GAD_11

GAD_12

GAD_13

GAD_14

GAD_15

GAD_16

GAD_17

GAD_18

GAD_19

GAD_20

RG82845G

H_ADS#(8)

D D

C C

B B

G_VREF_CG(17)

GRP_BLUE#(18)

H_BREQ#0(8)

H_RESET#(8)

H_DBSY#(8)

GRP_DDC_CLK_3V(18)

GRP_DDC_DATA_3V(18)

H_DEFER#(8)

CK_48M_DOT(7)

Shasta=845GL DPN:7W765

G_ADSTB0(17)

G_ADSTB#0(17)

G_ADSTB1(17)

G_ADSTB#1(17)

CK_66M_MCH(7)

GRP_GREEN(18)

GRP_GREEN#(18)

GRP_BLUE(18)

H_BPRI#(8)

H_DBI#0(8)

H_DBI#1(8)

H_DBI#2(8)

H_DBI#3(8)

H_DRDY#(8)

G_DEVSEL#(17)

G_FRAME#(17)

G_GNT#(17)

G_IRDY#(17)

G_PAR(17)

G_PIPE#(17)

G_RBF#(17)

G_RCOMP

H_BNR#(8)

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

E23

HD_56#

HD_57#

HD_58#

GAD_21

GAD_22

GAD_23

L5L4H4G2K3J4J5J7H3K8G4V8U7M8L7R4N4M2H2

C24

HD_55#

GAD_24

H_D#54

B25

H_D#53

HD_54#

GAD_25

H_D#49

H_D#50

H_D#52

H_D#48

H_D#51

D26

D28

B26

G27

H26

HD_49#

HD_50#

HD_51#

HD_52#

HD_53#

GAD_26

GAD_27

GAD_28

GAD_29

GAD_30

B27

H_D#47

HD_48#

GAD_31

H_D#42

H_D#41

H_D#40

H_D#45

H_D#39

H_D#43

H_D#44

H_D#46

D31

G29

C32

B31

B32

B30

B29

E27

C28

HD_40#

HD_41#

HD_42#

HD_43#

HD_44#

HD_45#

HD_46#

HD_47#

GADSTB_0

GADSTB_0#

GADSTB_1

GADSTB_1#

GCBE_0#

GCBE_1#

GCBE_2#

GCBE_3#

AE7N2M4B5N7P4H8G7E15

G_CBE#3

G_CBE#0

G_CBE#1

G_CBE#2

H_D#37

H_D#38

C34

B34

HD_37#

HD_38#

HD_39#

GCLKIN

GDEVSEL#

GFRAME#

H_D#36

H_D#33

H_D#32

H_D#34

H_D#31

H_D#35

H_D#30

G31

C36

D33

D30

D29

E31

D32

HD_30#

HD_31#

HD_32#

HD_33#

HD_34#

HD_35#

HD_36#

GGNT#

GIRDY#

GPAR

GPIPE#

GRBF#

GREEN

GREEN#

F16D5C3C2D3D2E4E2F3F2F4E5C4B4B3P2N5G5W31

H_D#29

B35

HD_29#

GREQ#

H_D#27

H_D#28

E33

E34

HD_27#

HD_28#

GSBA_0

GSBA_1

G_SBA0

G_SBA1

H_D#25

H_D#26

D36

H35

HD_25#

HD_26#

GSBA_2

GSBA_3

G_SBA2

G_SBA3

H_D#23

H_D#24

H34

F35

HD_24#

GSBA_4

G_SBA4

G_SBA5

H_D#21

H_D#22

F34

E36

HD_22#

HD_23#

GSBA_5

GSBA_6

G_SBA7

G_SBA6

H_D#19

H_D#20

D35

F36

HD_20#

HD_21#

GSBA_7

GSBSTB

H_D#18

H_D#17

H_D#16

G36

J33

HD_17#

HD_18#

HD_19#

GSBSTB#

GST_0

GST_1

G_ST0

G_ST1

G_ST2

H_D#15

H_D#14

H_D#13

L34

K35

H36

G34

HD_14#

HD_15#

HD_16#

GST_2

GSTOP#

GTRDY#

G_CBE#[0..3] (17)

G_AD[0..31] (17)

G_ST[0..2] (17)

G_SBA[0..7] (17)

H_D#12

HD_13#

GWBF#

H_A#3

M35

H_D#11

HD_12#

HA_3#

H_A#4

M30

HD_11#

HA_4#

AA33

H_D#10

K36

AB30

H_A#5

H_D#9

HD_10#

HA_5#

H_A#6

K34

HD_9#

HCC_VREF

HADSTB_1#

HADSTB_0#

HA_6#

V34

HD_8#

HD_7#

HD_6#

HD_5#

HD_4#

HD_3#

HD_2#

HD_1#

HD_0#

HCLKP

HCLKN

HA_VREF

HA_31#

HA_30#

HA_29#

HA_28#

HA_27#

HA_26#

HA_25#

HA_24#

HA_23#

HA_22#

HA_21#

HA_20#

HA_19#

HA_18#

HA_17#

HA_16#

HA_15#

HA_14#

HA_13#

HA_12#

HA_11#

HA_10#

HA_9#

HA_8#

HA_7#

J36

P35

L36

L33

R31

N34

R34

R33

T30

K30

J31

P30

AF30

AB35

AD30

AG31

AG33

AH35

AE31

AG36

AG34

AF34

AE33

AF36

AE36

AD34

AE34

AD35

AD36

AF35

AC31

AC36

AB36

Y34

AB34

AC34

AA36

Y35

AC33

Y36

H_D#8

H_D#7

H_D#6

H_D#5

H_D#4

H_D#3

H_D#2

H_D#1

H_D#0

H_A#31

H_A#30

H_A#29

H_A#28

H_A#27

H_A#26

H_A#25

H_A#24

H_A#23

H_A#22

H_A#21

H_A#20

H_A#19

H_A#18

H_A#17

H_A#16

H_A#15

H_A#14

H_A#13

H_A#12

H_A#11

H_A#10

H_A#9

H_A#8

H_A#7

CK_100M_MCH (7)

CK_100M_MCH# (7)

H_ADSTB#1 (8)

H_ADSTB#0 (8)

G_WBF# (17)

G_TRDY# (17)

G_STOP# (17)

G_SBSTB# (17)

G_SBSTB (17)

G_REQ# (17)

MCH_VREF (11)

H_A#[3..31] (8)

G_RCOMP

G_VREF_CG

12

C443

Near GMCH

0.1U

R70

40.2

1%

1 2

PLACE close to MCH

+1.5V

R156

1 2

1 2

G_VREF_CG

1K

1%

R158

1K

1%

A A

CAD NOTE : M_I2CDATA / M_I2CCLK , M_DVI_DATA / M_DVI_CLK routed trace width = 5 mil and

space = 10 mils , 7.5" max. trace length , +/- 250 mils

DVOC_CLK / DVOCCLK# routed differential pair the width = 5 mils and space =

10 mils , the trace length = 7.5" max and mismatch +/- 50 mils".

DVOCD[11:0], DVOCHSYNC, DVOCVSYNC, DVOCBLANK#, DVOCFLDSTL, POUT/DET#,

FLD/STL, DVOBC_INTR# the trace width = 5 mils and space = 10 mils , the

trace length must reference clock trace and mismatch +/- 0.125"

5

4

PLACE NEAR MCH PIN

3

Title :

ASUStek Computer Inc.

Size Project Name

A3

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

Date: Sheet

2

Engineer:

BROOKDALE-GL-1

William Yu

1

Rev

10 51Tuesday, January 28, 2003

A03

of

5

DDR_DQS[0..7](12,14)

DDR_DQS3

DDR_DQS5

DDR_DQS2

DDR_DQS6

DDR_DQS4

DDR_DQS1

H_D#[0..63](8,10)

H_D#59

H_D#60

H_HIT#(8)

H_D#61

H_D#62

H_D#63

HL_0

HL_1

HL_2

HL_3

HL_4

HL_5

HL_6

HL_7

HL_8

HL_9

HL_10

HL_MCH_RCOMP

H_TRDY#(8)

GND

D D

H_DSTBN#0(8)

H_DSTBN#1(8)

H_DSTBN#2(8)

H_DSTBN#3(8)

H_DSTBP#0(8)

H_DSTBP#1(8)

H_DSTBP#2(8)

H_DSTBP#3(8)

C C

B B

MCH_VREF

HL_[0..10](19)

HL_STBF(19)

HL_STBS(19)

HL_SWING(19)

HL_VREF(20)

H_HITM#(8)

H_LOCK#(8)

HREQ#0(8)

HREQ#1(8)

HREQ#2(8)

HREQ#3(8)

HREQ#4(8)

U2B

C22

HD_59#

G25

HD_60#

B22

HD_61#

D24

HD_62#

G23

HD_63#

N31

HDSTB_N0#

G33

HDSTB_N1#

C30

HDSTB_N2#

D25

HDSTB_N3#

L31

HDSTB_P0#

J34

HDSTB_P1#

E29

HDSTB_P2#

E25

HDSTB_P3#

H30

HDVREF_0

H24

HDVREF_1

D27

HDVREF_2

AA7

HI_0

AB8

HI_1

AC7

HI_2

AC5

HI_3

AD8

HI_4

AF4

HI_5

AE4

HI_6

AE5

HI_7

AF3

HI_8

AE2

HI_9

AF2

HI_10

AC2

HI_RCOMP

AC4

HI_STBF

AD4

HI_STBS

AD2

HI_SWING

AD3

HI_VREF

P36

HIT#

M36

HITM#

T35

HLOCK#

V36

HREQ_0#

AA31

HREQ_1#

W33

HREQ_2#

AA34

HREQ_3#

W35

HREQ_4#

BROOKDALE-GShasta=845GL DPN:7W765

GRP_HSYNC_3V

HXRCOMP

HXYSWING

HYRCOMP

R72

1 2

137

1%

3P3V_PW RGOOD(31,39)

PCI_RST_SYS#(17,28,30,31,37,39)

AT29

AT34

SDQS_5

SDQS_6

HSYNC

HTRDY#

B7

V30

AT17

AR24

SDQS_4

HX_RCOMP

B28

H28

GRP_RED(18)

GRP_RED#(18)

AT7

AT12

SDQS_1

SDQS_2

SDQS_3

HX_SWING

HY_RCOMP

HY_SWING

V35

Y30Y2A2

H_RS#0(8)

H_RS#1(8)

H_RS#2(8)

DDR_D63

DDR_DQS0

AK34

AR2

SDQ_63

SDQS_0

MEM_SEL

NC0

NC_MCH_A2

NC_MEM_SEL

DDR_D62

NC_MCH_A36

DDR_D60

DDR_D61

DDR_D59

DDR_D58

AJ36

AP36

AM35

AK35

SDQ_59

SDQ_60

SDQ_61

SDQ_62

NC1

NC2

NC3

NC4

A36B1B37

AH34

NC_MCH_B37

NC_MCH_B1

NC_MCH_AJ35

NC_MCH_AH34

3P3V_PWRGOOD

4

DDR_D56

DDR_D57

AN36

AM36

AK36

SDQ_56

SDQ_57

SDQ_58

NC5

NC6

NC7

AJ35

AT1

AT37

NC_MCH_AT37

NC_MCH_AT1

PSB_SEL

REFSET

DDR_D55

AT35

AU1

NC_MCH_AU1

SDQ_55

NC8

DDR_D54

AP34

SDQ_54

NC9

AU2

NC_MCH_AU2

DDR_D53

AT33

SDQ_53

NC10

AU36

NC_MCH_AU36

DDR_D52

DDR_D51

AP35

AP32

SDQ_52

NC11

AU37Y3E7

NC_MCH_AU37

DDR_D49

DDR_D50

AT32

AR36

SDQ_49

SDQ_50

SDQ_51

PSB_SEL

PWROK

RED

C15

DDR_D48

AR32

SDQ_48

RED#

D16

DDR_D47

DDR_D46

AT30

AT31

SDQ_47

REFSET

B16

R36

DDR_D34

DDR_D37

DDR_D38

DDR_D36

DDR_D35

DDR_D39

AT22

AT23

AT25

AR26

SDQ_36

SDQ_37

SDQ_38

SDQ_39

RSVD3

RSVD4

RSVD5

RSVD6

AA3

AA4

NC_RSVD_AA4

NC_RSVD_Y8

NC_RSVD_AA2

NC_RSVD_AA3

NC_RSVD_AA5

DDR_D33

AP24

AT26

SDQ_34

SDQ_35

RSVD7

RSVD8

AA5

AB2

NC_RSVD_AB2

NC_RSVD_AB3

DDR_D41

DDR_D44

DDR_D45

DDR_D42

DDR_D43

DDR_D40

AP26

AT28

AR30

AP30

AT27

AR28

SDQ_40

SDQ_41

SDQ_42

SDQ_43

SDQ_44

SDQ_45

SDQ_46

RS_0#

RS_1#

RS_2#

RSTIN#

RSVD0

RSVD1

RSVD2

U34

P34

AJ31

A37W7Y4Y8AA2

NC_RSVD_W7

NC_RSVD_A37

NC_RSVD_Y4

(Put NC_RSVD_AB2 at ( 2950 / -3535))

DDR_D32

AP22

SDQ_33

RSVD9

AB3

AR22

SDQ_32

SBA_0

AN27

DDR_D31

AR20

SDQ_31

SBA_1

AP27

DDR_D30

DDR_D29

AP18

SDQ_30

SCAS#

AN29

DDR_CKE0

DDR_D28

AR16

AT16

SDQ_28

SDQ_29

SCKE_0

SCKE_1

AP13

AN13

DDR_CKE1

DDR_D27

DDR_D26

AT18

AT19

SDQ_27

SCKE_2

AK14

AL13

DDR_CKE2

DDR_CKE3

3

DDR_D24

DDR_D25

AT15

AP16

SDQ_25

SDQ_26

SCKE_3

SCMDCLK_0

AL21

AK22

DDR_D23

AP14

SDQ_24

SCMDCLK_0#

AN11

DDR_D22

DDR_D21

AR12

AR14

SDQ_22

SDQ_23

SCMDCLK_1

SCMDCLK_1#

AP11

AM34

SDQ_21

SCMDCLK_5#

SCMDCLK_5

SCMDCLK_4#

SCMDCLK_4

SCMDCLK_3#

SCMDCLK_3

SCMDCLK_2#

SCMDCLK_2

SDQ_20

SDQ_19

SDQ_18

SDQ_17

SDQ_16

SDQ_15

SDQ_14

SDQ_13

SDQ_12

SDQ_11

SDQ_10

SDQ_9

SDQ_8

SDQ_7

SDQ_6

SDQ_5

SDQ_4

SDQ_3

SDQ_2

SDQ_1

SDQ_0

SDM_7

SDM_6

SDM_5

SDM_4

SDM_3

SDM_2

SDM_1

SDM_0

SCS_3#

SCS_2#

SCS_1#

SCS_0#

AT10

AT14

AT13

AT11

AP10

AP8

AT8

AP6

AT6

AR10

AT9

AR6

AT5

AT4

AR4

AP3

AN2

AP5

AT3

AP2

AN4

AL34

AR34

AP28

AT24

AR18

AP12

AR8

AP4

AN31

AK30

AP31

AL29

AN34

AP33

AN9

AP9

AN21

AP21

AL33

DDR_D20

DDR_D19

DDR_D18

DDR_D17

DDR_D16

DDR_D15

DDR_D14

DDR_D13

DDR_D12

DDR_D11

DDR_D10

DDR_D9

DDR_D8

DDR_D7

DDR_D6

DDR_D5

DDR_D4

DDR_D3

DDR_D2

DDR_D1

DDR_D0

DDR_DM7

DDR_DM6

DDR_DM5

DDR_DM4

DDR_DM3

DDR_DM2

DDR_DM1

DDR_DM0

DDR_CS#3

DDR_CS#2

DDR_CS#1

DDR_CS#0

2

DDR_D[0..63] (14)

DDR_CS#[0..3] (15,16)

DDR_SCLK#5 (15)

DDR_SCLK5 (15)

DDR_SCLK#4 (15)

DDR_SCLK4 (15)

DDR_SCLK#3 (15)

DDR_SCLK3 (15)

DDR_SCLK#2 (15)

DDR_SCLK2 (15)

DDR_SCLK#1 (15)

DDR_SCLK1 (15)

DDR_SCLK#0 (15)

DDR_SCLK0 (15)

DDR_CKE[0..3] (15,16)

DDR_CAS# (15,16)

DDR_BA1 (15,16)

DDR_BA0 (15,16)

DDR_DM[0..7] (14)

1

GMCH HEAT SINK DETECTION MECHANISM

+3.3V

R71

8.2K

1 2

GPI_HS_DET#(31)

ADD*_7G090_MCHHS

HEATSINK for Brookdale G Chipset

1

2

HS2

1

2

GREEN

1

2

HS1

1

2

GREEN

GRP_HSYNC_3V

A A

1 2

1 2

R73

1 2

47

H_BSEL0 (7,8) HL_SWING(19)

R78

8.2K

Shasta= NI

PSB_SEL

R87

8.2K

5

GRP_HSYNC_3V_R (18 )

+CPUCORE

12

R79

301

1%

R88

150

1%

1 2

12

C39

0.01UF

HXYSWING

HYRCOMP

HXRCOMP

R83

24.9

1%

1 2

R84

24.9

1%

1 2

4

+1.5V

R74

HL_MCH_RCOMP

12

68

1%

R76

1 2

226

1%

R81

1 2

100

C40

1%

0.01U

12

+1.5V

HL_VREF (20)

V_1P25_SMVREF_R(12)

0.01U

3

R85

100

1%

1 2

12

C41

+2.5VSTBY

R80

1 2

51.1 1%

R86

1 2

51.1

1%

C42

0.1U

R82

1 2

0

12

2

V_1P25_SMVREF (15)

ASUStek Computer Inc.

Size Project Name

A3

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

Date: Sheet

+CPUCORE

R75

49.9

1%

1 2

MCH_VREF

12

R77

C38

100

1%

1 2

0.1U

Place cap near GMCH

Title :

Engineer:

1

MCH_VREF (10)

BROOKDALE-GL-2

William Yu

Rev

11 51Tuesday, January 28, 2003

A03

of

5

4

3

2

1

+2.5VSTBY

DDR_MAA[0..12](15,16)

12

C44

0.1U

12

C52

R90

1

0.1U

L7

0.82UH/35mA

L8

1UH/800mA

4.7U

1

0.1U

21

12

12

C45

12

10UH/15mA

C66

0.1U

0.1U

C53

0.1U

L6

21

21

C57

0.1U

L9

0.68UH/150mA

12

C43

0.1U

12

C51

0.1U

+1.5V

1 2

12

C59

21

12

C65

R92

1 2

U2C

AL17

SMAA_5

AP19

SMAA_6

AP17

SMAA_7

AN17

SMAA_8

AK16

SMAA_9

AK26

SMAA_10

AL15

SMAA_11

AN15

SMAA_12

AP25

SMAB_1

AN23

SMAB_2

AN19

SMAB_4

AK18

SMAB_5

AF10

SMXRCOMP1

AJ34

SMY_RCOMP

AK28

SRAS#

AL23

SRCVEN_IN#

AK24

SRCVEN_OUT#

AP29

SWE#

A9

VCC0

A11

VCC1

B9

VCC2

B10

VCC3

B11

VCC4

B12

VCC5

C9

VCC6

C10

VCC7

C11

VCC8

C12

VCC9

D9

VCC10

D10

VCC11

D11

VCC12

D12

VCC13

E9

VCC14

E11

VCC15

F10

VCC16

F12

VCC17

G11

VCC18

G13

VCC19

H10

VCC20

BROOKDALE-G

Shasta=845GL DPN:7W765

AH2

VCCSM6

AG9

VCCSM5

AG7

VCCSM4

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

AU21

VCCQSM2

AT21

VCCQSM1

AT20

VCCQSM0

AE3

VCCHI4

AD6

VCCHI3

AC9

VCCHI2

AC1

VCCHI1

B6

VCCGPIO

AB10

VCCAGP19

W9

VCCAGP17

V10

VCCAGP15

V6

VCCAGP14

R9

VCCAGP12

R1

VCCAGP11

P10

VCCAGP10

P6

VCCAGP9

L9

VCCAGP8

L1

VCCAGP7

K6

VCCAGP6

G1

VCCAGP5

D6

VCCAGP4

D4

VCCAGP3

C1

VCCAGP2

A7

VCCAGP1

A3

VCCAGP0

AG2

VCCA_SM1

AG1

VCCA_SM0

AD10

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

H12

H14

J11

J13

J15

K10

K12

K14

K16

V_1P25_SMVREF_R(11)

DDR_MAA[0..12](15,16)

DDR_DQS7(14)

VCC39

VCC40

VCC41

VCC43

VCC45

VCC46

VCC47

SMAA_1

AN25

C225

0.1U

W17

W18

W19

DDR_MAA1

12

AP23

DDR_MAA2

C216

0.1U

U17

U19

U21

V19

12

SMAA_2

AK20

DDR_MAA3

SMAA_3

AL25

DDR_MAA0

SMAA_0

AM2

V_1P25_SMVREF_R

12

SM_VREF

SMAA_4

AL19

DDR_MAA4

C217

0.1U

VCC48

SDQS_7

AL36

W20

W21

+1.5V

12

VCC49

C218

0.1U

VCC51

Y19

AA17

0.68UH/150mA

12

VCC53

VCC54

VCC55

AA19

AA21

L27

2 1

C219

0.1U

12

C220

0.1U

HublinkFor AGP

Decoupling

VCCA_DAC0

A15

B14

12

12

VCCA_DAC1

VCCA_DPLL

A13

C61

C221

0.1U

VCCA_HI0

VCCA_FSB

A17

V_1P5_VCCA_FSB

V_1P5_VCCA_DPLL

12

C62

0.01U

1U

+1.5V

12

12

C222

+

0.1U

GND

Place between GMCH and AGP

CE11

820U

V_2P5_VCCQSM

+1.5V

+3.3V

12

GND

V_1P5_VCCA_SM

+2.5VSTBY V_2P5_VCCQSM

12

+

CE12

1000U

SW 1.5V

SMX_RCOMP

SMY_RCOMP

DDR_WE#(15,16)

R91

60.4

1%

1 2

60.4

1%

R93

60.4

1%

R421

60.4

1%

DDR_MAA5

DDR_MAA6

DDR_MAA7

DDR_MAA8

DDR_MAA9

DDR_MAA10

DDR_MAA11

DDR_MAA12

DDR_MAB1

DDR_MAB2

DDR_MAB4

DDR_MAB5

NC_OCLK

NC_RCLK

+1.5V

SMX_RCOMP

R404

SMY_RCOMP

D D

DDR_MAB1(15,16)

DDR_MAB2(15,16)

DDR_MAB4(15,16)

DDR_MAB5(15,16)

DDR_RAS#(15,16)

C C

B B

+2.5VSTBY

1 2

12

C64

0.1U

+2.5VSTBY

1 2

12

A A

C67

0.1U

1 2

AH3

AH4

AH6

AH8

AH10

AH12

AH14

AH18

AH22

AH26

AJ1

AJ2

AJ3

AJ4

AJ5

AJ7

AJ9

AJ11

AJ15

AJ19

AJ23

AJ27

AK2

AK3

AK4

AK6

AK8

AK10

AK32

AL1

AL2

AL3

AL4

AL5

AL7

AL9

AL11

AL37

AM14

AM18

AM22

AM26

AM30

AP7

AP15

AP20

AU5

AU9

AU13

AU17

Place Res<1" from GMCH

5

4

3

2

12

C46

0.1U

12

C54

0.1U

V_1P5_VCCA_DPLL

12

12

12

C63

+2.5VSTBY

12

12

12

12

+CPUCORE

C58

0.1U

C60

0.1U

0.1U

C48

C47

0.1U

0.1U

12

12

C55

C56

0.1U

0.1U

12

+

CE15

680U

V_1P5_VCCA_FSB

12

+

C526

22U/10V

V_1P5_VCCA_SM

12

+

CE17

150U

ASUStek Computer Inc.

Size Project Name

A3

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

Date: Sheet

C50

C49

0.1U

0.1U

12

+

CE55

22U

Engineer:

12

+

CE13

Title :

1

1800U

12

+

CE14

1800U

BROOKDALE-GL-3

William Yu

Rev

12 51Tuesday, January 28, 2003

A03

of

5

4

3

2

1

+2.5VSTBY

Y10

Y17

Y18

Y20

Y21

Y32

AA1

AA9

AA18

AA20

AA29

AA35

AA37

AB4

AB6

AB28

AB32

AC3

AC29

VSS162

VSS52

VSS53

G21

G35H6H22

VSS54

VSS55

AC35

VSS156

VSS56

VSS57

VSS58

H32J1J3J9J17

VSS155

VSS59

VSS60

VSS152

VSS61

VSS62

J21

VSS151

VSS63

J23

J25

VSS150

VSS64

VSS65

J27

J29

VSS66

VSS67

J35

VSS145

VSS146

VSS68

VSS69

J37

K24

VSS144

VSS70

K28

K32L3L29

VSS142

VSS143

VSS71

VSS73

VSS74

VSS75

L35M6M10

VSS138

VSS139

VSS76

VSS77

M32N1N3N9N29

VSS78

VSS79

VSS134

VSS135

VSS80

VSS81

VSS132

VSS133

VSS82

VSS83

N35

N37

VSS130

VSS131

VSS84

VSS128

VSS129

VSS127

VSS126

VSS125

VSS124

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS107

VSS106

VSS103

VSS102

VSS101

VSS100

VSS96

VSS95

VSS94

VSS93

VSS90

VSS89

VSS88

Y6

W36

W34

W29

W3

V32

V28

V21

V20

V18

V17

U37

U35

U29

U20

U18

U9

U3

U1

T32

T10

T6

R35

R29

R3

P32

P28

GND GND

AD32

AE1

AE9

AE29

AE35

AE37

AF6

AF8

AF28

AF32

AG3

AG4

AG5

AG29

AG35

AG37

U2D

AU25

VCCSM57

AU29

D D

C C

GND

VCCSM58

AU33

VCCSM59

A5

VSS0

A21

VSS1

A23

VSS2

A25

VSS3

A27

VSS4

A29

VSS5

A33

VSS6

A35

VSS7

B2

VSS8

B8

VSS9

B13

VSS10

B17

VSS11

B21

VSS12

B36

VSS13

C5

VSS14

C8

VSS15

C13

VSS16

C16

VSS17

C17

VSS18

C21

VSS19

C23

VSS20

C25

VSS21

C27

VSS22

C29

VSS23

C31

VSS24

C33

VSS25

C37

VSS26

D8

VSS27

D13

VSS28

D15

VSS29

D17

VSS30

D21

VSS31

D23

VSS32

D34

VSS33

E1

VSS34

E3

VSS35

E13

VSS36

BROOKDALE-G

SHASTA=845GL/DPN=7W765

VSS177

VSS37

E17

E21

VSS175

VSS176

VSS38

VSS39

E35

E37F6F8

VSS173

VSS174

VSS40

VSS41

VSS171

VSS172

VSS42

VSS43

F14

F22

VSS169

VSS170

VSS44

VSS45

F24

F26

VSS167

VSS168

VSS46

VSS47

F28

F30

VSS165

VSS166

VSS48

VSS49

F32G3G9

VSS163

VSS164

VSS50

VSS51

G17

U2E

AH16

VSS178

AH20

VSS179

AH24

VSS180

AH28

VSS181

AH30

VSS182

AH32

VSS183

AH36

VSS184

AJ13

VSS185

AJ17

VSS186

AJ21

VSS187

AJ25

VSS188

AJ29

VSS189

AJ33

VSS190

AJ37

VSS191

AK12

VSS192

AL27

VSS193

AL31

VSS194

AL35

VSS195

AM3

VSS196

AM4

VSS197

AM6

VSS198

AM8

VSS199

AM10

VSS200

AM12

VSS201

AM16

VSS202

AM20

VSS203

AM24

VSS204

AM28

VSS205

AM32

VSS206

AN1

VSS207

AN3

VSS208

AN5

VSS209

AN7

VSS210

AN33

VSS211

AN35

VSS212

AN37

VSS213

AR1

VSS214

AR3

VSS215

AR5

VSS216

AR7

VSS217

AR9

VSS218

AR11

VSS219

AR13

VSS220

AR15

VSS221

AR17

VSS222

AR19

VSS223

AR21

VSS224

AR23

VSS225

AR25

VSS226

AR27

VSS227

AR29

VSS228

AR31 AR33

VSS229 VSS230

BROOKDALE-G

845GL (DELL P/N 7W765) for Shasta

VTT_DECAP4

VTT_DECAP3

VTT_DECAP2

VTT_DECAP1

VTT_DECAP0

VSSA_DAC1

VSSA_DAC0

VTTFSB30

VTTFSB28

VTTFSB25

VTTFSB20

VTTFSB19

VTTFSB18

VTTFSB17

VTTFSB16

VTTFSB15

VTTFSB14

VTTFSB13

VTTFSB12

VTTFSB11

VTTFSB10

VTTFSB9

VTTFSB8

VTTFSB7

VTTFSB6

VTTFSB5

VTTFSB4

VTTFSB3

VTTFSB2

VTTFSB1

VTTFSB0

VSYNC

VSS242

VSS241

VSS240

VSS239

VSS238

VSS237

VSS236

VSS235

VSS234

VSS233

VSS232

VSS231

AD28

Y28

T28

M28

K26

K22

K20

K18

J19

H20

H18

G19

F20

F18

E19

D20

D19

D18

C20

C19

C18

B20

B19

B18

AC37

R37

L37

G37

A31

C6

C14

B15

AU35

AU31

AU27

AU23

AU15

AU11

AU7

AU3

AT36

AT2

AR37

AR35

+CPUCORE

GRP_VSYNC_3V

VTT_DECAP4

VTT_DECAP3

VTT_DECAP2

VTT_DECAP1

VTT_DECAP0

12

0.1U

12

C70

C71

0.1U

0.1U

12

12

C68

C69

0.1U

GND GND GND GND GND

0.1U CAPS ALL ARE X7R

R94

1 2

47

GRP_VSYNC_3V_R (18)

12

C72

0.1U

B B

A A

Title :

BROOKDALE-GL -4

ASUStek Computer Inc.

Size Project Name

A3

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

5

4

3

2

Date: Sheet

Engineer:

William Yu

Rev

1

13 51Tuesday, January 28, 2003

A03

of

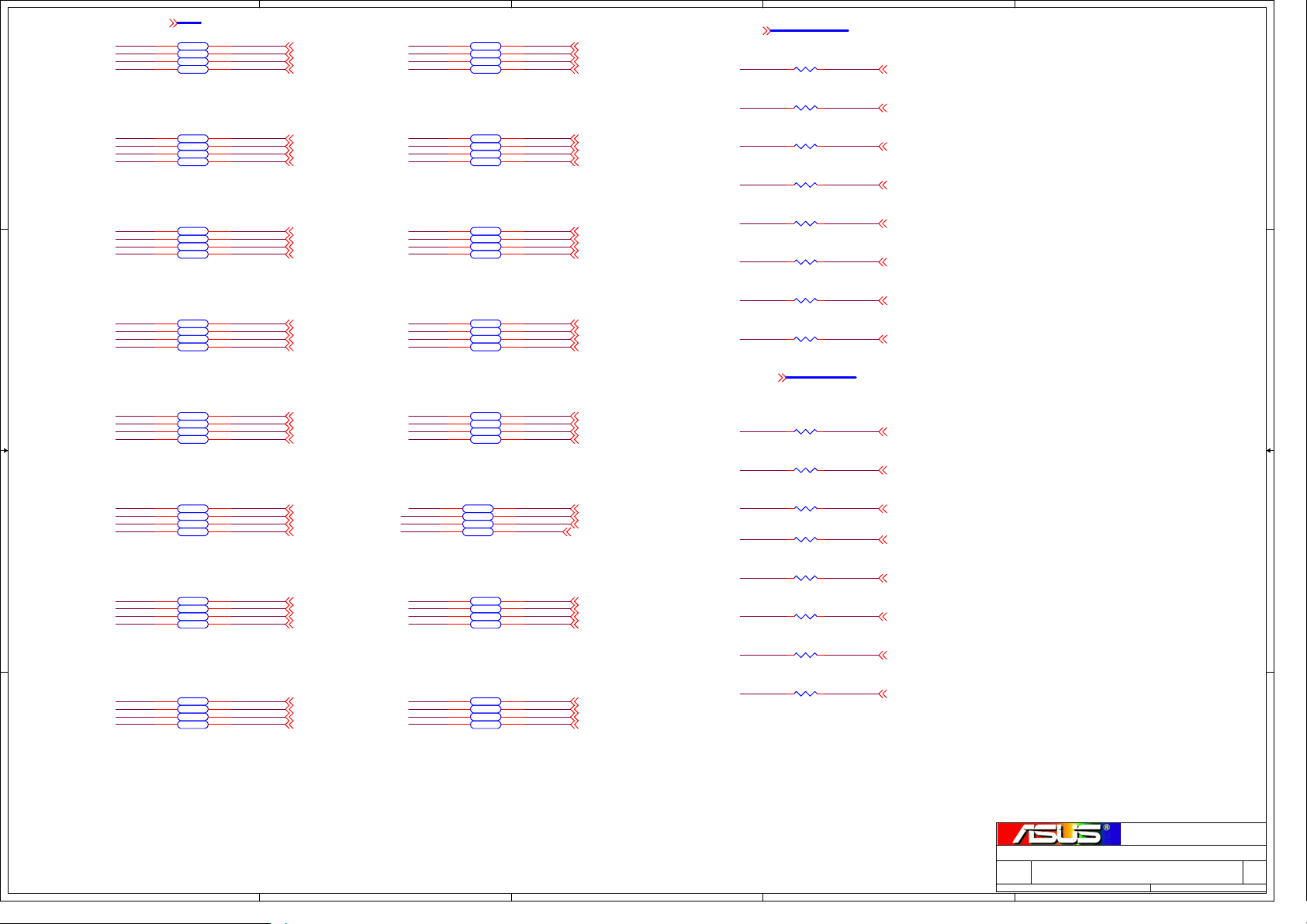

5

DDR_D[0..63](11)

DDR_D1

1 8

DDR_D5

2 7

DDR_D4

3 6

DDR_D0

4 5

D D

C C

DDR_D3

DDR_D7

DDR_D6

DDR_D2

DDR_D13

DDR_D12

DDR_D9

DDR_D8

DDR_D11

DDR_D10

DDR_D15

DDR_D14

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

RN2A

10

RN2B

10

RN2C

10

RN2D

10

RN4A

10

RN4B

10

RN4C

10

RN4D

10

RN6A

10

RN6B

10

RN6C

10

RN6D

10

RN8A

10

RN8B

10

RN8C

10

RN8D

10

DDR_D1_R (15,16)

DDR_D5_R (15,16)

DDR_D4_R (15,16)

DDR_D0_R (15,16)

DDR_D3_R (15,16)

DDR_D7_R (15,16)

DDR_D6_R (15,16)

DDR_D2_R (15,16)

DDR_D13_R (15,16)

DDR_D12_R (15,16)

DDR_D9_R (15,16)

DDR_D8_R (15,16)

DDR_D11_R (15,16)

DDR_D10_R (15,16)

DDR_D15_R (15,16)

DDR_D14_R (15,16)

4

DDR_D37

DDR_D33

DDR_D36

DDR_D32

DDR_D35

DDR_D39

DDR_D38

DDR_D34

DDR_D41

DDR_D45

DDR_D44

DDR_D40

DDR_D47

DDR_D43

DDR_D46

DDR_D42

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

RN3A

10

RN3B

10

RN3C

10

RN3D

10

RN5A

10

RN5B

10

RN5C

10

RN5D

10

RN7A

10

RN7B

10

RN7C

10

RN7D

10

RN9A

10

RN9B

10

RN9C

10

RN9D

10

DDR_D37_R (15,16)

DDR_D33_R (15,16)

DDR_D36_R (15,16)

DDR_D32_R (15,16)

DDR_D35_R (15,16)

DDR_D39_R (15,16)

DDR_D38_R (15,16)

DDR_D34_R (15,16)

DDR_D41_R (15,16)

DDR_D45_R (15,16)

DDR_D44_R (15,16)

DDR_D40_R (15,16)

DDR_D47_R (15,16)

DDR_D43_R (15,16)

DDR_D46_R (15,16)

DDR_D42_R (15,16)

3

DDR_DM[0..7](11)

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_DM4

DDR_DM5

DDR_DM6

DDR_DM7

DDR_DQS[0..7](11,12)

R95

1 2

10

R96

1 2

10

R97

1 2

10

R98

1 2

10

R99

1 2

10

R100

1 2

10

R101

1 2

10

R102

1 2

10

2

DDR_DM0_R (15,16)

DDR_DM1_R (15,16)

DDR_DM2_R (15,16)

DDR_DM3_R (15,16)

DDR_DM4_R (15,16)

DDR_DM5_R (15,16)

DDR_DM6_R (15,16)

DDR_DM7_R (15,16)

1

DDR_D21

1 8

DDR_D17

2 7

DDR_D16

3 6

DDR_D20

4 5

DDR_D23

1 8

DDR_D19

2 7

DDR_D22

3 6

DDR_D18

4 5

B B

DDR_D25

1 8

DDR_D29

2 7

DDR_D28

3 6

DDR_D24

4 5

DDR_D31

1 8

DDR_D27

2 7

DDR_D30

3 6

DDR_D26

4 5

A A

5

RN10A

10

RN10B

10

RN10C

10

RN10D

10

RN12A

10

RN12B

10

RN12C

10

RN12D

10

RN14A

10

RN14B

10

RN14C

10

RN14D

10

RN16A

10

RN16B

10

RN16C

10

RN16D

10

DDR_D21_R (15,16)

DDR_D17_R (15,16)

DDR_D16_R (15,16)

DDR_D20_R (15,16)

DDR_D23_R (15,16)

DDR_D19_R (15,16)

DDR_D22_R (15,16)

DDR_D18_R (15,16)

DDR_D25_R (15,16)

DDR_D29_R (15,16)

DDR_D28_R (15,16)

DDR_D24_R (15,16)

DDR_D31_R (15,16)

DDR_D27_R (15,16)

DDR_D30_R (15,16)

DDR_D26_R (15,16)

DDR_D53

1 8

DDR_D52

2 7

DDR_D49

3 6

DDR_D48

4 5

DDR_D51

1 8

DDR_D50

2 7

DDR_D55

3 6

DDR_D54

4 5

DDR_D57

1 8

DDR_D61

2 7

DDR_D56

3 6

DDR_D60

4 5

DDR_D59

1 8

DDR_D63

2 7

DDR_D58

3 6

DDR_D62

4 5

4

RN11A

10

RN11B

10

RN11C

10

RN11D

10

RN13A

10

RN13B

10

RN13C

10

RN13D

10

RN15A

10

RN15B

10

RN15C

10

RN15D

10

RN17A

10

RN17B

10

RN17C

10

RN17D

10

DDR_D53_R (15,16)

DDR_D52_R (15,16)

DDR_D49_R (15,16)

DDR_D48_R (15,16)

DDR_D51_R (15,16)

DDR_D50_R (15,16)

DDR_D55_R (15,16)

DDR_D54_R (15,16)

DDR_D57_R (15,16)

DDR_D61_R (15,16)

DDR_D56_R (15,16)

DDR_D60_R (15,16)

DDR_D59_R (15,16)

DDR_D63_R (15,16)

DDR_D58_R (15,16)

DDR_D62_R (15,16)

DDR_DQS0

DDR_DQS1

DDR_DQS2

DDR_DQS3

DDR_DQS4

DDR_DQS5

DDR_DQS6

DDR_DQS7

3

R103

1 2

10

R104

1 2

10

R105

1 2

10

R106

1 2

10

R107

1 2

10

R108

1 2

10

R109

1 2

10

R110

1 2

10

DDR_DQS0_R (15,16)

DDR_DQS1_R (15,16)

DDR_DQS2_R (15,16)

DDR_DQS3_R (15,16)

DDR_DQS4_R (15,16)

DDR_DQS5_R (15,16)

DDR_DQS6_R (15,16)

DDR_DQS7_R (15,16)

2

Title :

ASUStek Computer Inc.

Size Project Name

A3

4X703-SCHEM,PLN,GX260,845G,GNIC,CR

Date: Sheet

Engineer:

1

DDR Serial

William Yu

14 51Tuesday, January 28, 2003

of

Rev

A03

5

DDR_MAB1 (12,16)

DDR_MAB2 (12,16)

DDR_MAB4 (12,16)

DDR_MAB5 (12,16)

D D

C C

B B

DDR_MAA[0..12](12,16)

DDR_BA0(11,16)

DDR_BA1(11,16)

DDR_CKE[0..3](11,16)

DDR_DQS0_R(14,16)

DDR_DQS1_R(14,16)

DDR_DQS2_R(14,16)

DDR_DQS3_R(14,16)

DDR_DQS4_R(14,16)

DDR_DQS5_R(14,16)

DDR_DQS6_R(14,16)

DDR_DQS7_R(14,16)

DDR_MAA0

DDR_MAA1

DDR_MAA2

DDR_MAA3

DDR_MAA4

DDR_MAA5

DDR_MAA6

DDR_MAA7

DDR_MAA8

DDR_MAA9

DDR_MAA10

DDR_MAA11

DDR_MAA12

NC_DDR_FETEN_DIMMA

NC_DDR_BA2_DIMMA

NC_DDR_CB0_DIMMA

NC_DDR_CB1_DIMMA

NC_DDR_CB2_DIMMA

NC_DDR_CB3_DIMMA

NC_DDR_CB4_DIMMA

NC_DDR_CB5_DIMMA

NC_DDR_CB6_DIMMA

NC_DDR_CB7_DIMMA

DDR_SCLK0(11)

DDR_SCLK#0(11)

DDR_SCLK1(11)

DDR_SCLK#1(11)

DDR_SCLK2(11)

DDR_SCLK#2(11)

NC_DDR_DQS8_DIMMA

DDR_DM0_R(14,16)

DDR_DM1_R(14,16)