Page 1

RealView Platform Baseboard for

ARM926EJ-S

HBI-0117

User Guide

™

Copyright © 2003-2010 ARM Limited. All rights reserved.

ARM DUI 0224I

Page 2

RealView Platform Baseboard for ARM926EJ-S

User Guide

Copyright © 2003-2010 ARM Limited. All rights reserved.

Release Information

Change History

Date Issue Confidentiality Change

November 2003 A Non-Confidential First release.

April 2004 B Non-Confidential Second release. Added configuration details for USB

November 2005 C Non-Confidential Third release. Corrected reported defects and added

debug, PCI, and Boot Monitor.

requested enhancements.

August 2006 D Non-Confidential Fourth release. Corrected reported defects and added

May 2007 E Non-Confidential Fifth release. Corrected reported defects and added

October 2007 F Non-Confidential Sixth release. Corrected reported defect.

April 2008 G Non-Confidential Seventh release. Corrected reported defect.

March 2009 H Non-Confidential Eighth release. Corrected reported defect.

July 2010 I Non-Confidential Ninth release. Document update.

requested enhancements.

requested enhancements.

Proprietary Notice

®

Words and logos marked with

or ™ are registered trademarks or trademarks owned by ARM Limited, except

as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the

trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document

may be adapted or reproduced in any material form except with the prior written permission of the copyright

holder.

The product described in this document is subject to continuous developments and improvements. All

particulars of the product and its use contained in this document are given by ARM in good faith. However,

all warranties implied or expressed, including but not limited to implied warranties of merchantability, or

fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable

for any loss or damage arising from the use of any information in this document, or any error or omission in

such information, or any incorrect use of the product.

ii Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 3

Confidentiality Status

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to

license restrictions in accordance with the terms of the agreement entered into by ARM and the party that

ARM delivered this document to.

Product Status

The information in this document is final, that is for a developed product.

Web Address

http://www.arm.com

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. iii

Page 4

Note

Conformance Notices

This section contains conformance notices.

Federal Communications Commission Notice

This device is test equipment and consequently is exempt from part 15 of the FCC Rules under section 15.103

(c).

CE Declaration of Conformity

The system should be powered down when not in use.

The PB926EJ-S generates, uses, and can radiate radio frequency energy and may cause harmful interference

to radio communications. However, there is no guarantee that interference will not occur in a particular

installation. If this equipment causes harmful interference to radio or television reception, which can be

determined by turning the equipment off or on, you are encouraged to try to correct the interference by one

or more of the following measures:

• ensure attached cables do not lie across the card

• reorient the receiving antenna

• increase the distance between the equipment and the receiver

• connect the equipment into an outlet on a circuit different from that to which the receiver is connected

• consult the dealer or an experienced radio/TV technician for help

It is recommended that wherever possible shielded interface cables be used.

iv Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 5

Contents

RealView Platform Baseboard for ARM926EJ-S

User Guide

Preface

About this manual ...................................................................................... xviii

Feedback .................................................................................................... xxv

Chapter 1 Introduction

1.1 About the PB926EJ-S ................................................................................. 1-2

1.2 PB926EJ-S architecture .............................................................................. 1-4

1.3 Precautions ................................................................................................. 1-9

Chapter 2 Getting Started

2.1 Setting up the RealView Platform ............................................................... 2-2

2.2 Setting the configuration switches .............................................................. 2-3

2.3 Connecting JTAG debugging equipment .................................................... 2-8

2.4 Connecting the Trace Port Analyzer ......................................................... 2-10

2.5 Supplying power ....................................................................................... 2-13

2.6 Using the PB926EJ-S Boot Monitor and platform library .......................... 2-14

Chapter 3 Hardware Description

3.1 ARM926EJ-S PXP Development Chip ........................................................ 3-3

3.2 FPGA ........................................................................................................ 3-17

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. v

Page 6

Contents

3.3 Reset controller ........................................................................................ 3-22

3.4 Power supply control ................................................................................ 3-33

3.5 Clock architecture ..................................................................................... 3-35

3.6 Advanced Audio Codec Interface, AACI ................................................... 3-56

3.7 Character LCD controller .......................................................................... 3-59

3.8 CLCDC interface ...................................................................................... 3-61

3.9 DMA .......................................................................................................... 3-65

3.10 Ethernet interface ..................................................................................... 3-68

3.11 GPIO interface .......................................................................................... 3-71

3.12 Interrupts .................................................................................................. 3-72

3.13 Keyboard/Mouse Interface, KMI ............................................................... 3-74

3.14 Memory Card Interface, MCI .................................................................... 3-75

3.15 PCI interface ............................................................................................. 3-79

3.16 Serial bus interface ................................................................................... 3-80

3.17 Smart Card interface, SCI ........................................................................ 3-81

3.18 Synchronous Serial Port, SSP .................................................................. 3-84

3.19 User switches and LEDs .......................................................................... 3-87

3.20 UART interface ......................................................................................... 3-88

3.21 USB interface ........................................................................................... 3-92

3.22 Test, configuration, and debug interfaces ................................................ 3-94

Chapter 4 Programmer’s Reference

4.1 Memory map ............................................................................................... 4-3

4.2 Configuration and initialization .................................................................... 4-9

4.3 Status and system control registers ......................................................... 4-17

4.4 AHB monitor ............................................................................................. 4-41

4.5 Advanced Audio CODEC Interface, AACI ................................................ 4-42

4.6 Character LCD display ............................................................................. 4-44

4.7 Color LCD Controller, CLCDC .................................................................. 4-47

4.8 Direct Memory Access Controller and mapping registers ........................ 4-52

4.9 Ethernet .................................................................................................... 4-55

4.10 General Purpose Input/Output, GPIO ....................................................... 4-56

4.11 Interrupt controllers ................................................................................... 4-57

4.12 Keyboard and Mouse Interface, KMI ........................................................ 4-67

4.13 MBX .......................................................................................................... 4-68

4.14 MOVE video coprocessor ......................................................................... 4-69

4.15 MultiMedia Card Interfaces, MCIx ............................................................ 4-70

4.16 MultiPort Memory Controller, MPMC ........................................................ 4-71

4.17 PCI controller ............................................................................................ 4-74

4.18 Real Time Clock, RTC .............................................................................. 4-85

4.19 Serial bus interface ................................................................................... 4-86

4.20 Smart Card Interface, SCI ........................................................................ 4-88

4.21 Synchronous Serial Port, SSP .................................................................. 4-89

4.22 Synchronous Static Memory Controller, SSMC ........................................ 4-91

4.23 System Controller ..................................................................................... 4-95

4.24 Timers ....................................................................................................... 4-96

4.25 UART ........................................................................................................ 4-97

vi Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 7

4.26 USB interface ............................................................................................ 4-99

4.27 Vector Floating Point, VFP9 .................................................................... 4-100

4.28 Watchdog ................................................................................................ 4-101

Appendix A Signal Descriptions

A.1 Synchronous Serial Port interface ............................................................... A-2

A.2 Smart Card interface ................................................................................... A-3

A.3 UART interface ........................................................................................... A-5

A.4 USB interface .............................................................................................. A-6

A.5 Audio CODEC interface .............................................................................. A-7

A.6 MMC and SD flash card interface ............................................................... A-8

A.7 CLCD display interface ............................................................................. A-10

A.8 VGA display interface ............................................................................... A-13

A.9 GPIO interface .......................................................................................... A-14

A.10 Keyboard and mouse interface ................................................................. A-15

A.11 Ethernet interface ...................................................................................... A-16

A.12 RealView Logic Tile header connectors .................................................... A-17

A.13 Test and debug connections ..................................................................... A-33

Appendix B Specifications

B.1 Electrical specification ................................................................................. B-2

B.2 Clock rate restrictions .................................................................................. B-5

B.3 Mechanical details ...................................................................................... B-9

Contents

Appendix C CLCD Display and Adaptor Board

C.1 About the CLCD display and adaptor board .............................................. C-2

C.2 Installing the CLCD display ........................................................................ C-6

C.3 Touchscreen controller interface .............................................................. C-11

C.4 Connectors ............................................................................................... C-15

C.5 Mechanical layout .................................................................................... C-19

Appendix D PCI Backplane and Enclosure

D.1 Connecting the PB926EJ-S to the PCI enclosure ...................................... D-2

D.2 Backplane hardware .................................................................................. D-6

D.3 Connectors ............................................................................................... D-10

Appendix E Memory Expansion Boards

E.1 About memory expansion ........................................................................... E-2

E.2 Fitting a memory board ............................................................................... E-5

E.3 EEPROM contents ...................................................................................... E-6

E.4 Connector pinout ....................................................................................... E-13

E.5 Mechanical layout ..................................................................................... E-20

Appendix F RealView Logic Tile

F.1 About the RealView Logic Tile .................................................................... F-2

F.2 Fitting a RealView Logic Tile ....................................................................... F-3

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. vii

Page 8

Contents

F.3 Header connectors ..................................................................................... F-4

Appendix G Configuring the USB Debug Connection

G.1 Installing the RealView ICE Micro Edition driver ........................................ G-2

G.2 Changes to RealView Debugger ................................................................ G-5

G.3 Using the USB debug port to connect RealView Debugger ....................... G-6

G.4 Using the Debug tab of the RealView Debugger Register pane .............. G-10

viii Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 9

List of Tables

RealView Platform Baseboard for ARM926EJ-S

User Guide

Change History ............................................................................................................. ii

Table 2-1 Selecting the boot device .......................................................................................... 2-4

Table 2-2 Default switch positions ............................................................................................. 2-4

Table 2-3 LED Indicators ........................................................................................................... 2-5

Table 2-4 Boot Monitor commands ......................................................................................... 2-15

Table 2-5 Boot Monitor Configure commands ......................................................................... 2-16

Table 2-6 Boot Monitor Debug commands .............................................................................. 2-16

Table 2-7 Boot Monitor NOR flash commands ........................................................................ 2-17

Table 3-1 Configuration switch S1 ............................................................................................ 3-8

Table 3-2 FPGA image selection ............................................................................................ 3-19

Table 3-3 Reset sources and effects ....................................................................................... 3-24

Table 3-4 Reset signal descriptions ........................................................................................ 3-29

Table 3-5 ARM926EJ-S PXP Development Chip clocks ......................................................... 3-40

Table 3-6 Asynchronous clock signals .................................................................................... 3-46

Table 3-7 HCLKM1 selection .................................................................................................. 3-47

Table 3-8 HCLKM2 selection .................................................................................................. 3-47

Table 3-9 HCLKS selection ..................................................................................................... 3-48

Table 3-10 GLOBALCLK selection ............................................................................................ 3-52

Table 3-11 PB926EJ-S clocks and clock control signals .......................................................... 3-54

Table 3-12 Audio system specification ...................................................................................... 3-56

Table 3-13 AC’97 audio debug signals on J45 .......................................................................... 3-58

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. ix

Page 10

List of Tables

Table 3-14 Display interface signals ......................................................................................... 3-63

Table 3-15 DMA signals for external devices ........................................................................... 3-67

Table 3-16 Ethernet signals ...................................................................................................... 3-68

Table 3-17 MMC/SD interface signals ...................................................................................... 3-75

Table 3-18 MMC signals ........................................................................................................... 3-78

Table 3-19 Serial bus addresses .............................................................................................. 3-80

Table 3-20 Serial bus signals .................................................................................................... 3-80

Table 3-21 Smart Card interface signals .................................................................................. 3-83

Table 3-22 SSP signal descriptions .......................................................................................... 3-85

Table 3-23 Serial interface signal assignment .......................................................................... 3-90

Table 3-24 USB interface signal assignment ............................................................................ 3-93

Table 3-25 JTAG related signals .............................................................................................. 3-98

Table 4-1 Memory map ............................................................................................................. 4-3

Table 4-2 Selecting the boot device ........................................................................................ 4-10

Table 4-3 Memory chip selects and address range ................................................................ 4-16

Table 4-4 Register map for system control registers .............................................................. 4-18

Table 4-5 ID Register, SYS_ID bit assignment ....................................................................... 4-21

Table 4-6 Oscillator Register, SYS_OSCx bit assignment ..................................................... 4-23

Table 4-7 Lock Register, SYS_LOCK bit assignment ............................................................. 4-24

Table 4-8 Configuration register 1 .......................................................................................... 4-26

Table 4-9 Configuration register 2 .......................................................................................... 4-27

Table 4-10 Flag registers .......................................................................................................... 4-30

Table 4-11 Reset level control .................................................................................................. 4-31

Table 4-12 MCI control ............................................................................................................. 4-32

Table 4-13 Flash control ........................................................................................................... 4-32

Table 4-14 SYS_CLCD register ................................................................................................ 4-33

Table 4-15 SYS_CLCDSER register ........................................................................................ 4-34

Table 4-16 BOOT configuration switches ................................................................................. 4-35

Table 4-17 SYS_MISC .............................................................................................................. 4-36

Table 4-18 DMA map registers ................................................................................................. 4-37

Table 4-19 SYS_DMAPSRx, DMA mapping register format .................................................... 4-38

Table 4-20 Oscillator test registers ........................................................................................... 4-40

Table 4-21 AHB monitor implementation .................................................................................. 4-41

Table 4-22 AACI implementation .............................................................................................. 4-42

Table 4-23 Modified AACI PeriphID3 register ........................................................................... 4-43

Table 4-24 Character LCD display implementation .................................................................. 4-44

Table 4-25 Character LCD control and data registers .............................................................. 4-45

Table 4-26 Character LCD display commands ......................................................................... 4-46

Table 4-27 CLCDC implementation .......................................................................................... 4-47

Table 4-28 PrimeCell CLCDC register differences ................................................................... 4-48

Table 4-29 Values for different display resolutions ................................................................... 4-48

Table 4-30 Assignment of display memory to R[7:0], G[7:0], and B[7:0] .................................. 4-49

Table 4-31 PL110 hardware playback mode ............................................................................ 4-51

Table 4-32 DMAC implementation ............................................................................................ 4-52

Table 4-33 DMA channels ........................................................................................................ 4-53

Table 4-34 DMA mapping register format ................................................................................. 4-54

Table 4-35 Ethernet implementation ......................................................................................... 4-55

x Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 11

List of Tables

Table 4-36 GPIO implementation .............................................................................................. 4-56

Table 4-37 VIC Primary Interrupt Controller implementation ..................................................... 4-57

Table 4-38 SIC implementation ................................................................................................. 4-57

Table 4-39 Primary interrupt controller registers ....................................................................... 4-58

Table 4-40 Interrupt signals to primary interrupt controller ........................................................ 4-59

Table 4-41 Secondary interrupt controller registers .................................................................. 4-61

Table 4-42 Interrupt signals to secondary interrupt controller ................................................... 4-62

Table 4-43 KMI implementation ................................................................................................ 4-67

Table 4-44 MBX implementation ............................................................................................... 4-68

Table 4-45 MCI implementation ................................................................................................ 4-70

Table 4-46 MPMC implementation ............................................................................................ 4-71

Table 4-47 SDRAM register values ........................................................................................... 4-72

Table 4-48 PCI controller implementation ................................................................................. 4-74

Table 4-49 PCI bus memory map for AHB M2 bridge ............................................................... 4-75

Table 4-50 PCI controller registers ............................................................................................ 4-75

Table 4-51 PCI_IMAPx register format ..................................................................................... 4-77

Table 4-52 PCI_SELFID register format ................................................................................... 4-77

Table 4-53 PCI_FLAGS register format .................................................................................... 4-78

Table 4-54 PCI_SMAPx register format .................................................................................... 4-79

Table 4-55 PCI backplane configuration header addresses (self-config) .................................. 4-80

Table 4-56 PCI backplane configuration header addresses (normal configuration) .................. 4-80

Table 4-57 PCI configuration space header .............................................................................. 4-81

Table 4-58 PCI bus commands supported ................................................................................ 4-84

Table 4-59 RTC implementation ............................................................................................... 4-85

Table 4-60 Serial bus implementation ....................................................................................... 4-86

Table 4-61 Serial bus register ................................................................................................... 4-86

Table 4-62 Serial bus device addresses ................................................................................... 4-87

Table 4-63 SCI implementation ................................................................................................. 4-88

Table 4-64 SSP implementation ................................................................................................ 4-89

Table 4-65 SSMC implementation ............................................................................................ 4-91

Table 4-66 Register values for Intel flash, standard async read mode, no bursts ..................... 4-92

Table 4-67 Register values for Intel flash, async page mode ................................................... 4-92

Table 4-68 Register values for Samsung SRAM ....................................................................... 4-93

Table 4-69 Register values for Spansion BDS640 .................................................................... 4-93

Table 4-70 Register values for Spansion LV256 ....................................................................... 4-93

Table 4-71 System controller implementation ........................................................................... 4-95

Table 4-72 Timer implementation .............................................................................................. 4-96

Table 4-73 UART implementation ............................................................................................. 4-97

Table 4-74 USB implementation ............................................................................................... 4-99

Table 4-75 USB controller base address .................................................................................. 4-99

Table 4-76 VFP9 implementation ............................................................................................ 4-100

Table 4-77 Watchdog implementation ..................................................................................... 4-101

Table A-1 SSP signal assignment ............................................................................................. A-2

Table A-2 Smartcard connector signal assignment ................................................................... A-3

Table A-3 Signals on expansion connector ............................................................................... A-4

Table A-4 Serial plug signal assignment ................................................................................... A-5

Table A-5 Multimedia Card interface signals ............................................................................. A-9

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. xi

Page 12

List of Tables

Table A-6 CLCD Interface board connector J18 ..................................................................... A-10

Table A-7 VGA connector signals ........................................................................................... A-13

Table A-8 Mouse and keyboard port signal descriptions ........................................................ A-15

Table A-9 Ethernet signals ...................................................................................................... A-16

Table A-10 HDRX (J9) signals .................................................................................................. A-18

Table A-11 HDRY (J12) signals ................................................................................................ A-22

Table A-12 HDRZ (J8) signals .................................................................................................. A-26

Table A-13 Test point functions ................................................................................................. A-34

Table A-14 Trace connector J14 ............................................................................................... A-37

Table A-15 AHB monitor connector J17 .................................................................................... A-39

Table A-16 FPGA debug connector J39 ................................................................................... A-40

Table B-1 PB926EJ-S electrical characteristics ........................................................................ B-2

Table B-2 Current requirements from DC IN (12V) ................................................................... B-3

Table B-3 Current requirements from J34 ................................................................................. B-3

Table B-4 Maximum current load on supply voltage rails .......................................................... B-4

Table B-5 ARM926EJ-S PXP Development Chip bus timing .................................................... B-6

Table B-6 ARM926EJ-S PXP Development Chip memory timing ............................................. B-7

Table B-7 Peripherals and controller timing .............................................................................. B-8

Table C-1 Displays available with adaptor board ...................................................................... C-7

Table C-2 Power configuration .................................................................................................. C-9

Table C-3 Touchscreen host interface signal assignment ....................................................... C-11

Table C-4 CLCD interface connector J2 .................................................................................. C-15

Table C-5 LCD prototyping connector J1 ................................................................................ C-16

Table C-6 Touchscreen prototyping connector J3 ................................................................... C-17

Table C-7 Inverter prototyping connector J4 ........................................................................... C-17

Table C-8 A/D and keypad J13 ............................................................................................... C-18

Table D-1 LED indicators .......................................................................................................... D-7

Table D-2 Configuration switches .............................................................................................. D-8

Table D-3 Power and reset switches ......................................................................................... D-8

Table D-4 Test points ................................................................................................................ D-8

Table D-5 ATX power connector ............................................................................................. D-10

Table D-6 Mictor connector pinout .......................................................................................... D-11

Table E-1 Memory width encoding ............................................................................................ E-4

Table E-2 Chip Select information block ................................................................................... E-7

Table E-3 Example contents of a static memory expansion EEPROM ..................................... E-8

Table E-4 Example contents of a dynamic memory expansion EEPROM .............................. E-11

Table E-5 SDR, Single data rate dynamic memory connector signals .................................... E-14

Table E-6 Static memory connector signals ............................................................................ E-16

Table F-1 RealView Logic Tile clock signals ............................................................................. F-8

Table G-1 Reset behavior register names and values ............................................................ G-11

Table G-2 Device property register names and values ........................................................... G-12

xii Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 13

List of Figures

RealView Platform Baseboard for ARM926EJ-S

User Guide

Key to timing diagram conventions ............................................................................. xx

Figure 1-1 PB926EJ-S layout ..................................................................................................... 1-3

Figure 1-2 PB926EJ-S block diagram ........................................................................................ 1-6

Figure 2-1 Location of S1-1 and S6-1 ........................................................................................ 2-3

Figure 2-2 JTAG connection ....................................................................................................... 2-8

Figure 2-3 USB debug port connection ...................................................................................... 2-9

Figure 2-4 Example of MultiTrace and JTAG connection ......................................................... 2-10

Figure 2-5 Example of RealView ICE and RealView Trace ...................................................... 2-11

Figure 2-6 Power connectors ................................................................................................... 2-13

Figure 3-1 ARM926EJ-S PXP Development Chip block diagram .............................................. 3-4

Figure 3-2 Configuration signals from SYS_CFGDATAx ........................................................... 3-9

Figure 3-3 Example of multiple masters ................................................................................... 3-12

Figure 3-4 AHB map ................................................................................................................. 3-13

Figure 3-5 Core APB and DMA APB map ................................................................................ 3-14

Figure 3-6 Memory devices ...................................................................................................... 3-15

Figure 3-7 AHB monitor connection ......................................................................................... 3-16

Figure 3-8 FPGA block diagram ............................................................................................... 3-17

Figure 3-9 FPGA configuration ................................................................................................. 3-19

Figure 3-10 FPGA reload sequence ........................................................................................... 3-20

Figure 3-11 PB926EJ-S reset logic ............................................................................................ 3-23

Figure 3-12 Reset signal sequence ............................................................................................ 3-25

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. xiii

Page 14

List of Figures

Figure 3-13 Programmable reset level ....................................................................................... 3-26

Figure 3-14 Boot memory remap logic ....................................................................................... 3-28

Figure 3-15 Power-on reset and configuration timing ................................................................ 3-32

Figure 3-16 Standby switch and power-supply control .............................................................. 3-34

Figure 3-17 Clock architecture ................................................................................................... 3-35

Figure 3-18 ARM926EJ-S PXP Development Chip internal multiplexors .................................. 3-39

Figure 3-19 Default clock sources and frequencies ................................................................... 3-42

Figure 3-20 Clock sources for asynchronous AHB bridges ....................................................... 3-45

Figure 3-21 Serial data and SYS_OSCx register format ............................................................ 3-49

Figure 3-22 Example of selecting a tile clock for the AHB S bridge ........................................... 3-53

Figure 3-23 Clock multiplexors ................................................................................................... 3-55

Figure 3-24 Audio interface ........................................................................................................ 3-57

Figure 3-25 Character display .................................................................................................... 3-60

Figure 3-26 Display interface ..................................................................................................... 3-62

Figure 3-27 DMA channels ........................................................................................................ 3-66

Figure 3-28 Ethernet interface architecture ................................................................................ 3-68

Figure 3-29 GPIO block diagram ............................................................................................... 3-71

Figure 3-30 External and internal interrupt sources ................................................................... 3-72

Figure 3-31 KMI block diagram .................................................................................................. 3-74

Figure 3-32 MMI interface .......................................................................................................... 3-77

Figure 3-33 PCI bridge ............................................................................................................... 3-79

Figure 3-34 Serial bus block diagram ........................................................................................ 3-80

Figure 3-35 SCI block diagram .................................................................................................. 3-82

Figure 3-36 SSP block diagram ................................................................................................. 3-84

Figure 3-37 Switch and LED interface ....................................................................................... 3-87

Figure 3-38 UARTs block diagram ............................................................................................. 3-89

Figure 3-39 UART0 interface ..................................................................................................... 3-89

Figure 3-40 Simplified interface for UART[3:1] .......................................................................... 3-90

Figure 3-41 OTG243 block diagram ........................................................................................... 3-92

Figure 3-42 Test and debug connectors, links, and LEDs ......................................................... 3-95

Figure 3-43 JTAG connector signals ........................................................................................ 3-101

Figure 3-44 JTAG signal routing .............................................................................................. 3-102

Figure 3-45 RealView Logic Tile JTAG circuitry ....................................................................... 3-103

Figure 4-1 ARM Data bus memory map .................................................................................... 4-8

Figure 4-2 Booting from NOR flash 1 ....................................................................................... 4-12

Figure 4-3 Booting from static expansion memory ................................................................... 4-13

Figure 4-4 Booting from AHB expansion .................................................................................. 4-14

Figure 4-5 ID Register, SYS_ID ............................................................................................... 4-21

Figure 4-6 SYS_SW ................................................................................................................. 4-21

Figure 4-7 SYS_LED ................................................................................................................ 4-22

Figure 4-8 Oscillator Register, SYS_OSCx .............................................................................. 4-23

Figure 4-9 Lock Register, SYS_LOCK ..................................................................................... 4-24

Figure 4-10 SYS_CFGDATA1 ................................................................................................... 4-25

Figure 4-11 SYS_CFGDATA2 ................................................................................................... 4-26

Figure 4-12 SYS_RESETCTL .................................................................................................... 4-3

Figure 4-13 SYS_MCI ................................................................................................................ 4-32

Figure 4-14 SYS_CLCD ............................................................................................................. 4-33

1

xiv Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 15

List of Figures

Figure 4-15 SYS_CLCDSER ...................................................................................................... 4-34

Figure 4-16 SYS_BOOTCS ........................................................................................................ 4-35

Figure 4-17 SYS_MISC .............................................................................................................. 4-36

Figure 4-18 DMA mapping register ............................................................................................ 4-37

Figure 4-19 Oscillator Register, SYS_OSCRESETx .................................................................. 4-39

Figure 4-20 AACI ID register ...................................................................................................... 4-42

Figure 4-21 SYS_DMAP0-2 mapping register format ................................................................ 4-54

Figure 4-22 Primary interrupt registers ....................................................................................... 4-59

Figure 4-23 Secondary interrupt registers .................................................................................. 4-62

Figure 4-24 AHB M2 to PCI mapping ......................................................................................... 4-76

Figure 4-25 PCI_IMAPx register ................................................................................................. 4-76

Figure 4-26 PCI_SELFID register ............................................................................................... 4-77

Figure 4-27 PCI_FLAGS register ............................................................................................... 4-78

Figure 4-28 PCI to AHB S mapping ............................................................................................ 4-79

Figure 4-29 PCI_SMAPx register ............................................................................................... 4-79

Figure A-1 SSP expansion interface ........................................................................................... A-2

Figure A-2 Smartcard contacts assignment ................................................................................ A-3

Figure A-3 J28 SCI expansion .................................................................................................... A-4

Figure A-4 Serial connector ........................................................................................................ A-5

Figure A-5 USB interfaces .......................................................................................................... A-6

Figure A-6 Audio connectors ...................................................................................................... A-7

Figure A-7 MMC/SD card socket pin numbering ........................................................................ A-8

Figure A-8 MMC card .................................................................................................................. A-8

Figure A-9 CLCD Interface connector J18 ................................................................................ A-12

Figure A-10 VGA connector J19 ................................................................................................. A-13

Figure A-11 GPIO connector ......................................................................................................

A-14

Figure A-12 KMI connector ......................................................................................................... A-15

Figure A-13 Ethernet connector J5 ............................................................................................. A-16

Figure A-14 HDRX, HDRY, and HDRZ (upper) pin numbering ................................................... A-17

Figure A-15 Test points and debug connectors .......................................................................... A-33

Figure A-16 Multi-ICE JTAG connector J31 ................................................................................ A-36

Figure A-17 USB debug connector J30 ...................................................................................... A-36

Figure A-18 Embedded logic analyzer connector J33 ................................................................ A-38

Figure A-19 AMP Mictor connector ............................................................................................. A-38

Figure B-1 Baseboard mechanical details .................................................................................. B-9

Figure C-1 CLCD adaptor board connectors (bottom view) ....................................................... C-2

Figure C-2 Small CLCD enclosure ............................................................................................. C-3

Figure C-3 Large CLCD enclosure ............................................................................................. C-4

Figure C-4 Displays mounted directly onto top of adaptor board. .............................................. C-5

Figure C-5 CLCD adaptor board connection .............................................................................. C-6

Figure C-6 CLCD buffer and power supply control links .......................................................... C-10

Figure C-7 Touchscreen and keypad interface ........................................................................ C-12

Figure C-8 Touchscreen resistive elements ............................................................................. C-12

Figure C-9 CLCD adaptor board mechanical layout ................................................................ C-19

Figure D-1 Installing the platform board into the PCI enclosure ................................................ D-3

Figure D-2 Multiple boards on PCI bus ...................................................................................... D-5

Figure D-3 PCI backplane .......................................................................................................... D-6

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. xv

Page 16

List of Figures

Figure D-4 JTAG signal flow on the PCI backplane ................................................................... D-9

Figure D-5 AMP Mictor connector J4 ........................................................................................ D-11

Figure D-6 PCI expansion board JTAG connector J5 .............................................................. D-12

Figure E-1 Dynamic memory board block diagram .................................................................... E-2

Figure E-2 Static memory board block diagram ......................................................................... E-3

Figure E-3 Memory board installation locations ......................................................................... E-5

Figure E-4 Chip select information block .................................................................................... E-8

Figure E-5 Samtec connector ................................................................................................... E-13

Figure E-6 Dynamic memory board layout ............................................................................... E-20

Figure E-7 Static memory board layout .................................................................................... E-20

Figure F-1 Signals on the RealView Logic Tile expansion connectors ...................................... F-2

Figure F-2 RealView Logic Tile fitted on PB926EJ-S ................................................................. F-3

Figure F-3 HDRX, HDRY, and HDRZ (upper) pin numbering .................................................... F-5

Figure F-4 RealView Logic Tile tristate for I/O ........................................................................... F-6

Figure F-5 Clock signals and the RealView Logic Tile ............................................................. F-10

Figure F-6 Bus signals for RealView Logic Tile and FPGA ...................................................... F-13

Figure G-1 Nodes added to Connection Control window ............................................................ G-5

Figure G-2 The Connection Control window ............................................................................... G-6

Figure G-3 ARM926EJ-S PXP Development Chip detected ...................................................... G-7

Figure G-4 Error shown when unpowered devices are detected ................................................ G-7

Figure G-5 Error shown when no devices are detected .............................................................. G-8

Figure G-6 Error shown when the USB debug port is not functioning ........................................ G-8

Figure G-7 Connection Properties window ................................................................................. G-8

Figure G-8 The Debug tab of the Register pane ....................................................................... G-10

xvi Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 17

Preface

This preface introduces the RealView Platform Baseboard for ARM926EJ-S User

Guide. It contains the following sections:

• About this manual on page xviii

• Feedback on page xxv.

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. xvii

Page 18

Preface

About this manual

This document describes how to set up and use the RealView Platform Baseboard for

the ARM926EJ-S (PB926EJ-S).

Product revision status

The rnpn identifier indicates the revision status of the product described in this manual,

where:

rn Identifies the major revision of the product.

pn Identifies the minor revision or modification status of the product.

Intended audience

This document has been written for experienced hardware and software developers to

aid the development of ARM-based products using the PB926EJ-S as part of a

development system.

Using this manual

This document is organized into the following chapters:

Chapter 1 Introduction

Read this chapter for an introduction to the PB926EJ-S. This chapter

shows the physical layout of the board and identifies the main

components.

Chapter 2 Getting Started

Read this chapter for a description of how to set up and start using the

PB926EJ-S. This chapter describes how to connect the add-on boards and

how to apply power.

Chapter 3 Hardware Description

Read this chapter for a description of the hardware architecture of the

PB926EJ-S. This chapter describes the peripherals, clocks, resets, and

debug hardware provided by the board.

Chapter 4 Programmer’s Reference

Read this chapter for a description of the PB926EJ-S memory map and

registers. There is also basic information on the peripherals and

controllers present in the platform baseboard.

xviii Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 19

Appendix A Signal Descriptions

Refer to this appendix for a description of the signals on the connectors.

Appendix B Specifications

Refer to this appendix for electrical, timing, and mechanical

specifications.

Appendix C CLCD Display and Adaptor Board

Refer to this appendix for details of the CLCD display and interface.

Appendix D PCI Backplane and Enclosure

Refer to this appendix for details of the PCI backplane board.

Appendix E Memory Expansion Boards

Refer to this appendix for details of the memory expansion boards.

Appendix F RealView Logic Tile

Refer to this appendix for details on installing an ARM RealView Logic

Tile product.

Appendix G Configuring the USB Debug Connection

Refer to this appendix for details on configuring the USB debug port for

use with RealView Debugger.

Preface

Conventions

Conventions that this manual can use are described in:

• Typographical

• Timing diagrams on page xx

• Signals on page xxi

• Numbering on page xxi.

Typographical

The typographical conventions are:

italic Highlights important notes, introduces special terminology,

denotes internal cross-references, and citations.

bold Highlights interface elements, such as menu names. Denotes

signal names. Also used for terms in descriptive lists, where

appropriate.

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. xix

Page 20

Preface

Clock

HIGH to LOW

Transient

HIGH/LOW to HIGH

Bus stable

Bus to high impedance

Bus change

High impedance to stable bus

monospace

Denotes text that you can enter at the keyboard, such as

commands, file and program names, and source code.

monospace

Denotes a permitted abbreviation for a command or option. You

can enter the underlined text instead of the full command or option

name.

monospace italic

Denotes arguments to monospace text where the argument is to be

replaced by a specific value.

monospace

bold Denotes language keywords when used outside example code.

< and > Angle brackets enclose replaceable terms for assembler syntax

where they appear in code or code fragments. They appear in

normal font in running text. For example:

•

MRC p15, 0 <Rd>, <CRn>, <CRm>, <Opcode_2>

• The Opcode_2 value selects which register is accessed.

Timing diagrams

The figure named Key to timing diagram conventions explains the components used in

timing diagrams. Variations, when they occur, have clear labels. You must not assume

any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value

within the shaded area at that time. The actual level is unimportant and does not affect

normal operation.

xx Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Key to timing diagram conventions

Page 21

Preface

Signals

The signal conventions are:

Signal level The level of an asserted signal depends on whether the signal is

active-HIGH or active-LOW. Asserted means HIGH for

active-HIGH signals and LOW for active-LOW signals.

Lower-case n Denotes an active-LOW signal.

Prefix A Denotes global Advanced eXtensible Interface (AXI) signals:

Prefix AR Denotes AXI read address channel signals.

Prefix AW Denotes AXI write address channel signals.

Prefix B Denotes AXI write response channel signals.

Prefix C Denotes AXI low-power interface signals.

Prefix H Denotes Advanced High-performance Bus (AHB) signals.

Prefix P Denotes Advanced Peripheral Bus (APB) signals.

Prefix R Denotes AXI read data channel signals.

Prefix W Denotes AXI write data channel signals.

Numbering

The numbering convention is:

<size in bits>'<base><number>

This is a Verilog method of abbreviating constant numbers. For example:

• 'h7B4 is an unsized hexadecimal value.

• 'o7654 is an unsized octal value.

• 8'd9 is an eight-bit wide decimal value of 9.

• 8'h3F is an eight-bit wide hexadecimal value of

0x3F

. This is

equivalent to b00111111.

• 8'b1111 is an eight-bit wide binary value of b00001111.

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. xxi

Page 22

Preface

Further reading

This section lists publications by ARM Limited, and by third parties.

ARM Limited periodically provides updates and corrections to its documentation. See

http://www.arm.com

for current errata sheets, addenda, and the Frequently Asked

Questions list.

ARM publications

This manual contains information that is specific to the PB926EJ-S Platform

Baseboard. See the following documents for other relevant information:

The following publications provide information about the registers and interfaces on the

ARM926EJ-S PXP Development Chip:

• ARM926EJ-S Development Chip Reference Guide (ARM DDI 0287)

• ARM926EJ-S Technical Reference Manual (ARM DDI 0198)

• ARM926EJ-S

™

PrimeXsys Platform Virtual Component Technical Reference

Manual (ARM DDI 0232)

™

• ARM926EJ-S

PrimeXsys Platform Virtual Component User Guide

(ARM DUI 0213)

• ARM MOVE Coprocessor Technical Reference Manual (ARM DDI 0251)

• ARM VFP9-S Coprocessor Technical Reference Manual (ARM DDI 0238)

• ARM MBX HR-S Graphics Core Technical Reference Manual (ARM DDI 0241).

The following publications provide reference information about the ARM architecture:

• AMBA

™

Specification (ARM IHI 0011)

• ARM Architecture Reference Manual (ARM DDI 0100).

The following publications provide information about related ARM products and

toolkits:

• Multi-ICE

• RealView

™

User Guide (ARM DUI 0048)

™

ICE User Guide (ARM DUI 0155)

• Trace Debug Tools User Guide (ARM DUI 0118)

®

• ARM MultiTrace

User Guide (ARM DUI 0150)

• ARM RealView Logic Tile LT-XC2V4000+ User Guide (ARM DUI 0186)

™

• RealView

Debugger User Guide (ARM DUI 0153)

• RealView Compilation Tools Compilers and Libraries Guide (ARM DUI 0205)

• RealView Compilation Tools Developer Guide (ARM DUI 0203)

• RealView Compilation Tools Linker and Utilities Guide (ARM DUI 0206).

xxii Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 23

Preface

The following publications provide information about ARM PrimeCell® and other

peripheral or controller devices:

• ARM PrimeCell Advanced Audio CODEC Interface (PL041) Technical Reference

Manual (ARM DDI 0173)

• ARM PrimeCell Color LCD Controller (PL110) Technical Reference Manual

(ARM DDI 0161)

• ARM PrimeCell DMA (PL080) Technical Reference Manual (ARM DDI 0196)

• ARM Dual-Timer Module (SP804) Technical Reference Manual

(ARM DDI 0271)

• ARM PrimeCell GPIO (PL061) Technical Reference Manual (ARM DDI 0190)

• ARM PrimeCell Keyboard Mouse Controller (PL050) Technical Reference

Manual (ARM DDI 0143)

• ARM PrimeCell Multimedia Card Interface (PL180) Technical Reference Manual

(ARM DDI 0172)

• ARM Multiport Memory Controller (GX175) Technical Reference Manual

(ARM DDI 0277)

• ARM PrimeCell Real Time Clock Controller (PL031) Technical Reference

Manual (ARM DDI 0224)

• ARM PrimeCell Smart Card Interface (PL131) Technical Reference Manual

(ARM DDI 0228)

• ARM PrimeCell Synchronous Serial Port Controller (PL022) Technical Reference

Manual (ARM DDI 0194)

• ARM PrimeCell Synchronous Static Memory Controller (PL093) Technical

Reference Manual (ARM DDI 236)

• ARM PrimeCell System Controller (SP810) Technical Reference Manual

(ARM DDI 0254)

• ARM PrimeCell UART (PL011) Technical Reference Manual (ARM DDI 0183)

• ARM PrimeCell Vector Interrupt Controller (PL190) Technical Reference

Manual (ARM DDI 0181)

• ARM PrimeCell Watchdog Controller (SP805) Technical Reference Manual

(ARM DDI 0270)

• ETM9 Technical Reference Manual (ARM DDI 0157).

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. xxiii

Page 24

Preface

Other publications

This section lists relevant documents published by third parties:

The following publication describes the JTAG ports with which Multi-ICE or RealView

ICE communicates:

• IEEE Standard Test Access Port and Boundary Scan Architecture (IEEE Std.

1149.1).

The following datasheets describe some of the integrated circuits or modules used on

the PB926EJ-S:

• CODEC with Sample Rate Conversion and 3D Sound (LM4549) National

Semiconductor, Santa Clara, CA.

• Mobile DiskOnChip Plus 32/64MByte, M-Systems Inc., Newark, CA.

• MultiMedia Card Product Manual SanDisk, Sunnyvale, CA.

• Serially Programmable Clock Source (ICS307), ICS, San Jose, CA.

• Serial Microwire Bus EEPROM (M93LC46) STMicroelectronics, Amsterdam,

The Netherlands.

• 1.8 Volt Intel StrataFlash

®

Wireless Memory with 3.0 Volt I/O Intel Corporation,

Santa Clara, CA. See the Build of Materials (BOM) file for the part number of the

flash device.

• TFT-LCD Module (LQ084V1DG21) Sharp Corporation, Osaka, Japan.

• Three-In-One Fast Ethernet Controller (LAN91C111) SMSC, Hauppauge, NY.

• Touch Screen Controller (TCS2200) Texas Instruments, Dallas, TX.

xxiv Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 25

Feedback

ARM®Limited welcomes feedback both on the PB926EJ-S and on the documentation.

Feedback on this product

If you have any comments or suggestions about this product, contact your supplier

giving:

• the product name

• a concise explanation of your comments.

Feedback on this manual

Preface

If you have any comments about this document, send email to

errata@arm.com

• the title

• the number

• the relevant page number(s) to which your comments apply

• a concise explanation of your comments.

®

ARM

Limited also welcomes general suggestions for additions and improvements.

giving:

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. xxv

Page 26

Preface

xxvi Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 27

Chapter 1

Introduction

This chapter introduces the PB926EJ-S. It contains the following sections:

• About the PB926EJ-S on page 1-2

• PB926EJ-S architecture on page 1-4

• Precautions on page 1-9.

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. 1-1

Page 28

Introduction

1.1 About the PB926EJ-S

The PB926EJ-S provides a development system that you can use to develop products

around the ARM926EJ-S PXP Development Chip.

You can use the PB926EJ-S as a basic development system with a power supply and a

connection to a JTAG interface unit.

You can expand the PB926EJ-S by adding:

• ARM RealView Logic Tiles containing custom IP

• a PCI expansion enclosure

• Dynamic memory expansion board

• Static memory expansion board

• VGA monitor or CLCD adaptor and CLCD display

• MMC, SD, or SIM cards

• custom devices to the 32-bit GPIO

• USB devices to the three USB ports

• serial devices to the synchronous serial port and the four UARTs

• keyboard and mouse

• audio devices to the onboard CODEC

• an Ethernet network to the onboard Ethernet controller.

The basic system provides a good platform for developing code for the ARM7 and

ARM9 series of processors. The ARM926EJ-S PXP Development Chip is much faster

than a software simulator or a core implemented in RealView Logic Tiles. Code

developed for the ARM926EJ-S PXP Development Chip will also run on the ARM10

and ARM11 processor series.

The expanded system with RealView Logic Tiles can be used to develop

AMBA-compatible peripherals and to test ASIC designs. The fast processor core and

the peripherals present in the ARM926EJ-S PXP Development Chip, PB926EJ-S

FPGA, and RealView Logic Tile FPGA enable you to develop and text complex

systems operating at, or near, their target operating frequency.

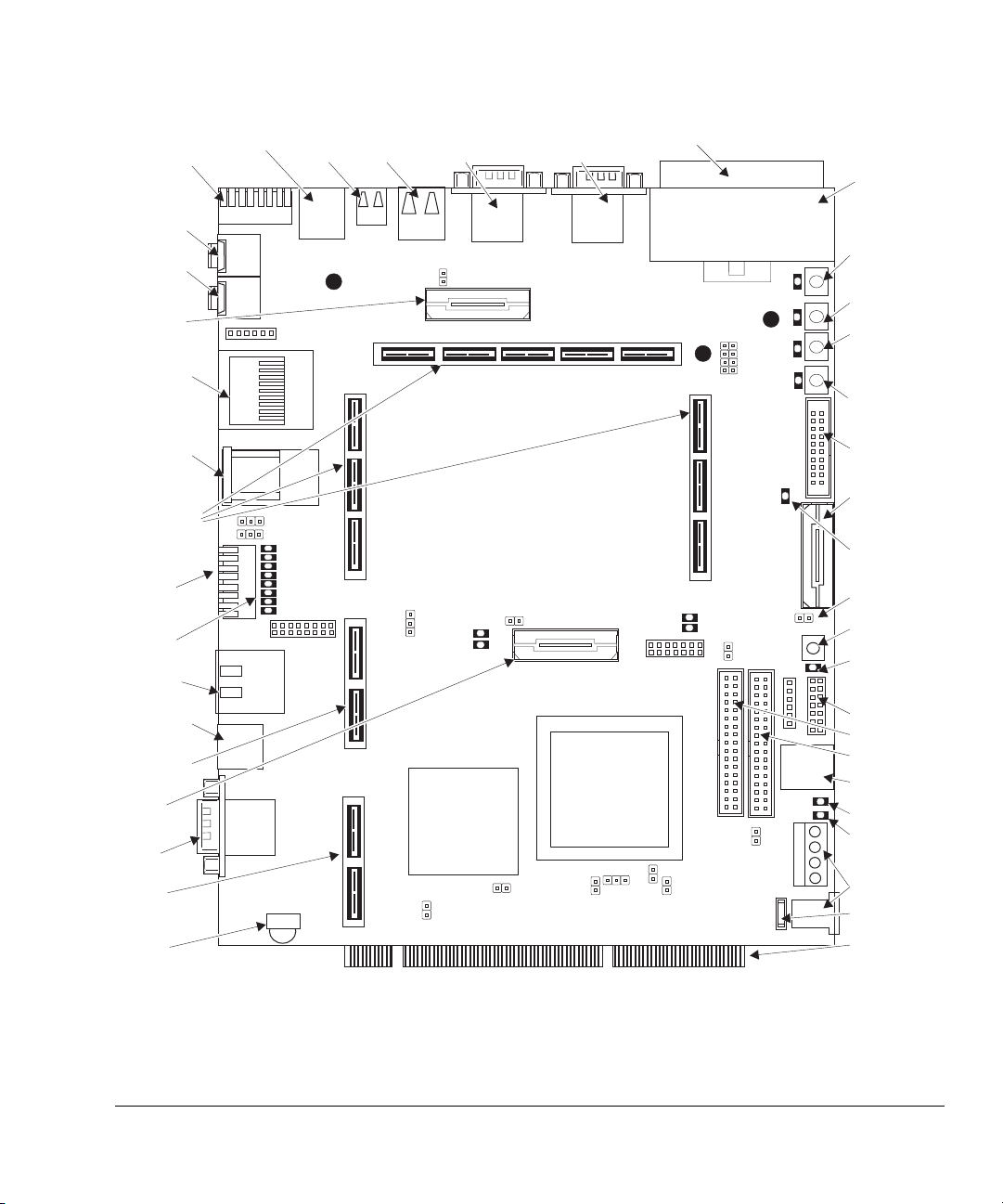

Figure 1-1 on page 1-3 shows the layout of the PB926EJ-S.

1-2 Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 29

Introduction

GP

(user)

LEDs

S6 GP

(user)

switches

Power LED

(red)

Power

S1

configuration

switches

Fuse

CONFIG

link

L

ine in

(bottom)

ine out

(top)

L

Mic in

MMC

0 (top)

1 (bottom)

Smart

card

0 (top)

1 (bottom)

Ethernet

Keyboard

VGA

Battery

PCI

expansion

USB debug

USB

0 (top)

1 (bottom)

UART

0 (top)

1 (bottom)

OTG

USB

Mouse

CLCD expansion

connector

JTAG

Trace

port

Dynamic

memory

expansion

2X16

character

LCD

ARM926EJ-S

Development

Chip

FPGA

GPIO 0,1

Logic Tile

expansion

GPIO 2,3

UART

2 (top)

3 (bottom)

ChipScope

0

1

Static

memory

expansion

CFGEN LED

(orange)

GP PUSH

(green LED)

DEV CHIP

CONFIG

(blue LED)

FPGA

CONFIG

(yellow LED)

RESET

(orange LED)

0

FPGA

debug

AHB

monitor

3V3 OK

(green LED)

5V OK

(green LED)

Standby/

power

Figure 1-1 PB926EJ-S layout

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. 1-3

Page 30

Introduction

1.2 PB926EJ-S architecture

The major components on the platform are:

• ARM926EJ-S PXP Development Chip equipped with:

— ARM926EJ-S processor that supports 32-bit ARM and 16-bit Thumb

instructions sets and includes features for direct execution of Java byte

codes. Executing Java byte codes requires the Java Technology Enabling

Kit (JTEK)

— Tightly-Coupled Memory (TCM) for code (32KB) and data (32KB)

— cache memory for code (32KB) and data (32KB)

— Memory Management Unit (MMU)

— Multi-layer bus matrix that gives highly efficient simultaneous transfers

—MOVE

— MBX graphics accelerator

— Multi-Port Memory Controller (MPMC) for direct connection to dynamic

memory

— Synchronous Static Memory Controller (SSMC) for direct connection to

static (SRAM or flash) memory

— VFP9 Vector Floating Point coprocessor

— two external AHB master bridges and one external AHB slave bridge

— AHB monitor for detailed analysis of bus activity

— System Controller

— DMA controller

— Vectored Interrupt Controller (VIC)

— Color LCD controller (CLCDC)

— Three UARTs,

— Synchronous Serial Port (SSP)

— Smart Card Interface (SCI)

— Four eight-bit GPIOs

— Real Time Clock (RTC)

— Two programmable timers

— Watchdog timer

— Embedded Trace Macrocell (ETM9)

— Embedded-ICE logic for JTAG debugging

— Phase-Locked Loop (PLL)

— Configuration Block.

™

video encoding coprocessor

1-4 Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 31

Introduction

• Field Programmable Gate-Array (FPGA) that implements:

— SSP, Smart Card, two MMC/SD card, UART, and two KMI controllers

— configuration registers

— interface to onboard Ethernet controllers

— interface to onboard audio CODEC

— interface to onboard On-the-Go (OTG) USB controller (three connectors)

— registers for status, ID, onboard switches, LEDs, and clock control

— a secondary interrupt controller and external DMA control logic

— interface to PCI bus (for expansion through optional PCI expansion

enclosure).

• 128MB of 32-bit wide SDRAM

• 2MB of 32-bit wide static RAM

• 128MB of 32-bit wide NOR flash (two devices)

• up to 320MB of static memory in an optional static memory expansion board

• up to 256MB of SDRAM in an optional dynamic memory expansion board

• programmable clock generators

• connectors for VGA, color LCD display interface board, PCI, UART, GPIO,

keyboard, mouse, Smart Card, USB, audio, MMC, SSP, and Ethernet

• RealView Logic Tile connector (one or more optional RealView Logic Tiles can

be used to develop custom IP)

• debug and test connectors for JTAG, AHB monitor, ChipScope, and Trace port

• DIP switches and LEDs

• 2 row by 16 character LCD display

• power conversion circuitry

• Real-Time Clock (RTC)

• time of year clock with backup battery.

ARM DUI 0224I Copyright © 2003-2010 ARM Limited. All rights reserved. 1-5

Page 32

Introduction

MCIKMI

AACI

SCI

Interrupt

controller

3 x

UARTs

RTC

Timers

User

switches

Ethernet

Audio

Codec

LAN

91C911

Ethernet

User

LEDs

FPGA

ARM926EJ-S Dev. Chip

Multi-layer AHB and bus switch

CLCD

expansion

connector

OTG243

USB

2x16 char

LCD

display

VGA

DAC and

PAL

KMI

Serial

bus

Sec. interrupt

controller

DMA

expansion

I/O

LCD

SCI PCIUART USB

Control

registers

Clocks, reset, JTAG, configuration,

and control circuitry

Memory

expansion

connector

SDRAM

Flash

SRAM

Memory

expansion

connector

MUX

SSMC MPMC MBX

AHB bridges

CLCDC

32-bit

GPIO

SSP

Watch

dog

AHB bus

monitor

System

controller

DMAC

Trace Port

Adaptor

ARM 926EJ-S,

VFP9, and MOVE

USB debug

JTAG

interface

Chip scope

interface

Status

LEDs

Control

switches

JTAG

ETM9 JTAG

Realview Logic Tile

expansion connectors

(also shared connections to I/O

signals from GPIO, AHB monitor,

SCI, UART, SSP, and CLCD)

PB926EJ-S

APB

bridge

AHBM1

AHBM2

AHBS

Configuration

Keyboard

Mouse

1.2.1 System architecture

Figure 1-2 shows the architecture of the PB926EJ-S.

Figure 1-2 PB926EJ-S block diagram

1-6 Copyright © 2003-2010 ARM Limited. All rights reserved. ARM DUI 0224I

Page 33

1.2.2 ARM926EJ-S PXP Development Chip

For details on the ARM926EJ-S PXP Development Chip, see ARM926EJ-S PXP

Development Chip on page 3-3 and the ARM926EJ-S PXP Development Chip

Reference Manual.

1.2.3 PB926EJ-S FPGA

The FPGA provides system control and configuration functions for the PB926EJ-S that

enable it to operate as a standalone development system or with expansion RealView

Logic Tiles or PCI cards. See FPGA on page 3-17.

The FPGA also implements additional peripherals, for example the audio CODEC,

USB, Ethernet and PCI interfaces.

1.2.4 Displays

The ARM926EJ-S PXP Development Chip outputs signals for a color LCD display. An

external interface board can be connected to the CLCD connector to drive different size

displays.

The CLCD signals from the ARM926EJ-S PXP Development Chip are converted on the

PB926EJ-S to a VGA signal. The resolution of the VGA signal is configurable. See

Appendix C CLCD Display and Adaptor Board.

Introduction

There is also a two row by sixteen character display mounted on the PB926EJ-S. This

display can be used for debugging or as the output from applications.

1.2.5 RealView Logic Tile expansion

The ARM RealView Logic Tiles, such as the LT-XC2V6000, enable the development

of AMBA AHB and APB peripherals, or custom logic, for use with ARM cores. You

can place standard or custom peripherals in the FPGA on the RealView Logic Tile.

Three AHB buses, the static memory interface, and the DMA and interrupt signals are

brought out to the RealView Logic Tile connectors. See Appendix F RealView Logic