Page 1

Cortex™-R4 and Cortex-R4F

Revision: r1p3

Technical Reference Manual

Copyright © 2009 ARM Limited. All rights reserved.

ARM DDI 0363E (ID013010)

Page 2

Cortex-R4 and Cortex-R4F

Technical Reference Manual

Copyright © 2009 ARM Limited. All rights reserved.

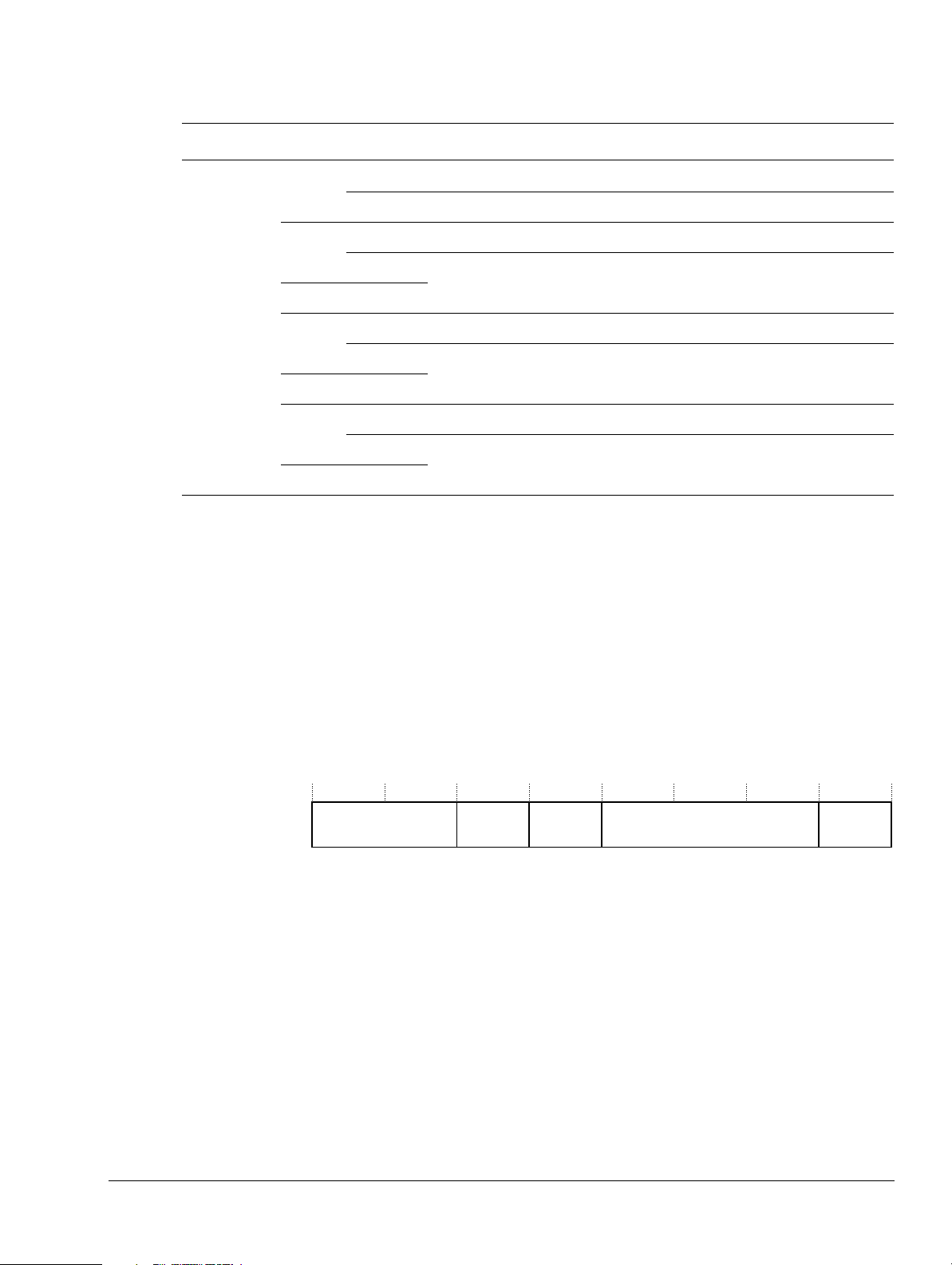

Release Information

The following changes have been made to this book.

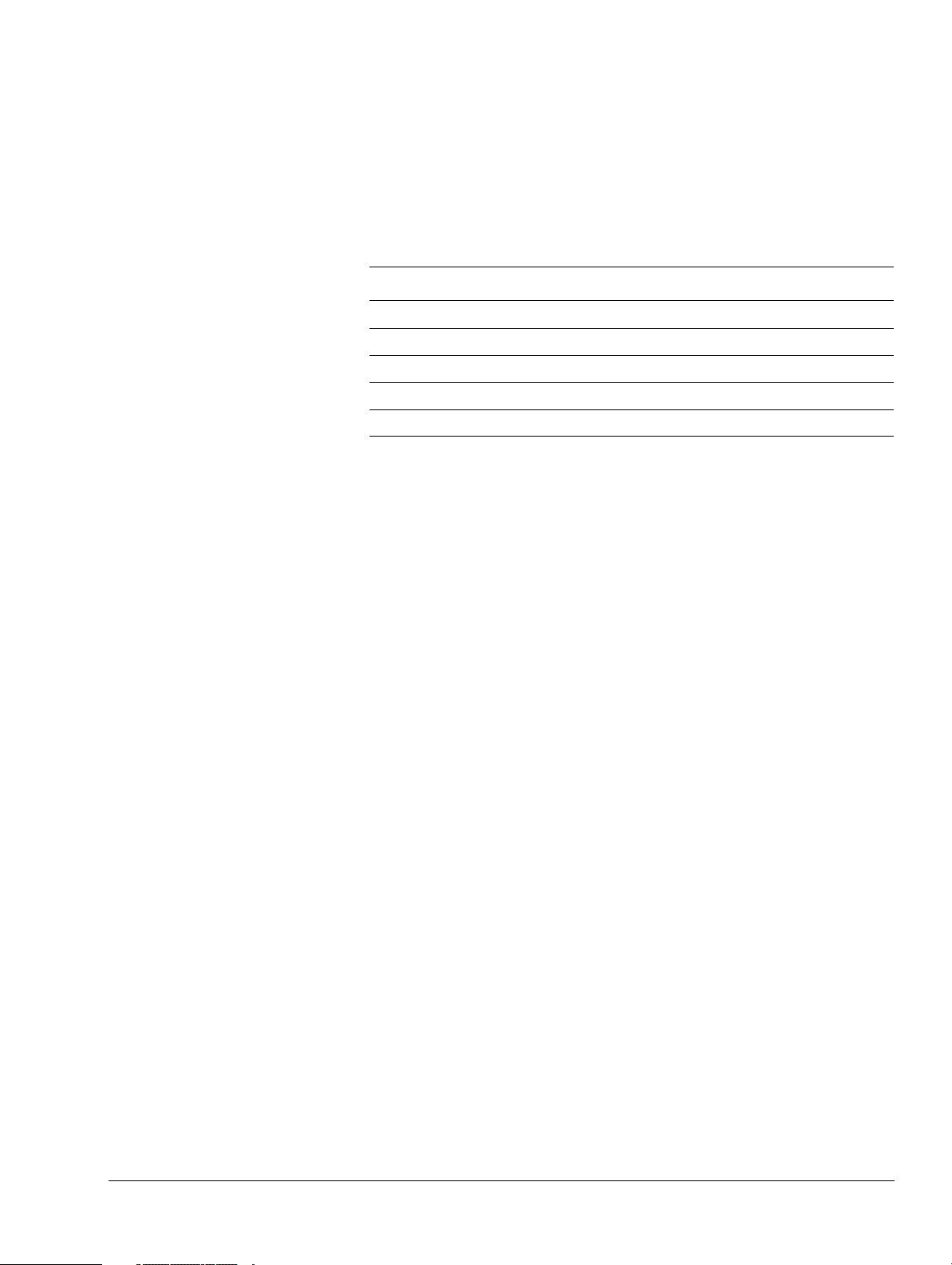

Change History

Date Issue Confidentiality Change

15 May 2006 A Confidential First release for r0p1

22 October 2007 B Non-Confidential First release for r1p2

16 June 2008 C Non-Confidential Restricted Access First release for r1p3

11 September 2009 D Non-Confidential Second release for r1p3

20 November 2009 E Non-Confidential Documentation update for r1p3

Proprietary Notice

Words and logos marked with

countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may

be the trademarks of their respective owners.

®

or ™ are registered trademarks or trademarks of ARM Limited in the EU and other

Neither the whole nor any part of the information contained in, or the product described in, this document may be

adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the

product and its use contained in this document are given by ARM in good faith. However, all warranties implied or

expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or

damage arising from the use of any information in this document, or any error or omission in such information, or any

incorrect use of the product.

Some material in this document is based on ANSI/IEEE Std 754-1985, IEEE Standard for Binary Floating-Point

Arithmetic. The IEEE disclaims any responsibility or liability resulting from the placement and use in the described

manner.

Where the term ARM is used it means “ARM or any of its subsidiaries as appropriate”.

Confidentiality Status

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license

restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this

document to.

Unrestricted Access is an ARM internal classification.

Product Status

The information in this document is final, that is for a developed product.

Web Address

http://www.arm.com

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. ii

ID013010 Non-Confidential, Unrestricted Access

Page 3

Contents

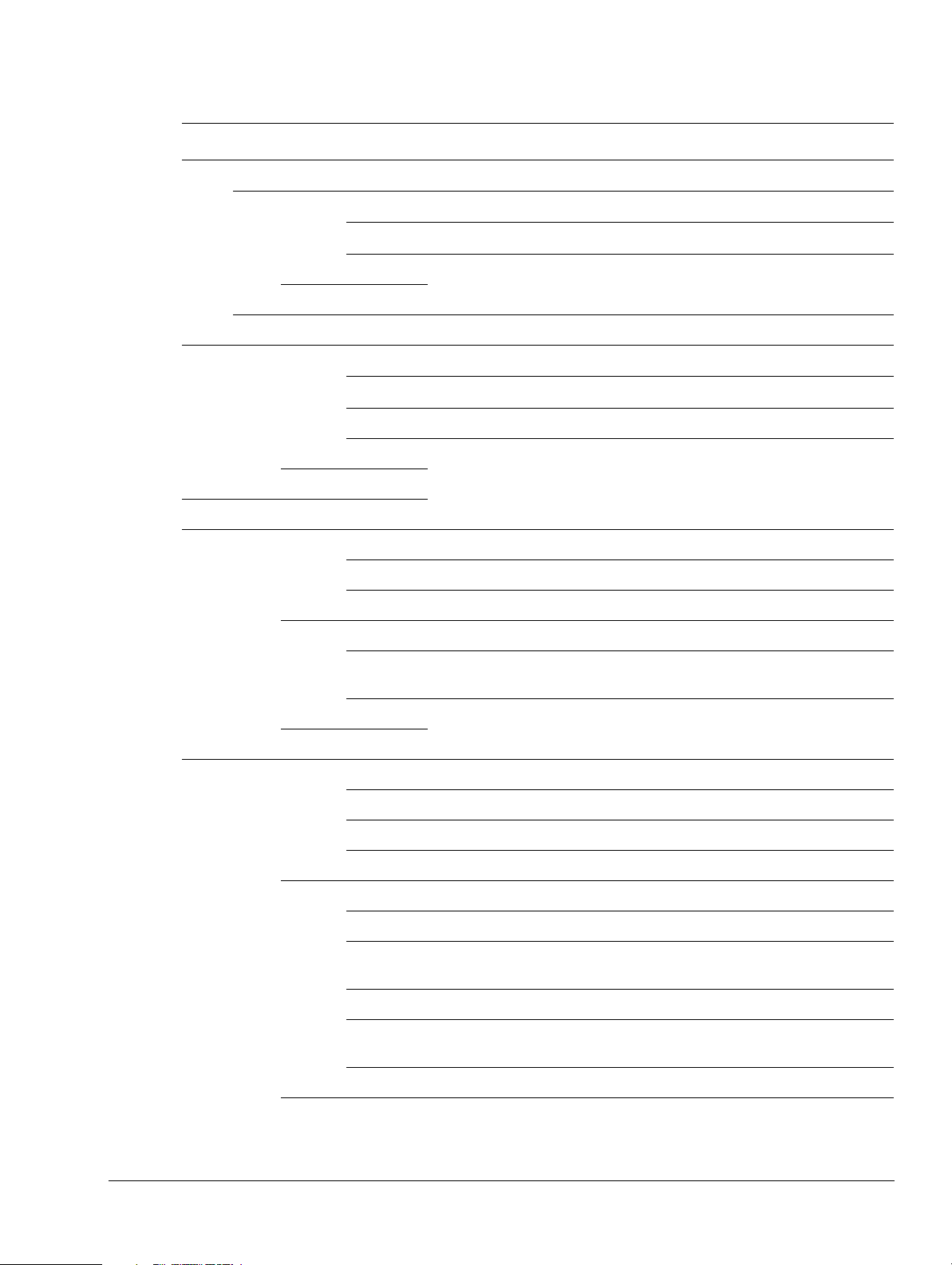

Cortex-R4 and Cortex-R4F Technical Reference

Manual

Preface

About this book ........................................................................................................ xvii

Feedback .................................................................................................................. xxi

Chapter 1 Introduction

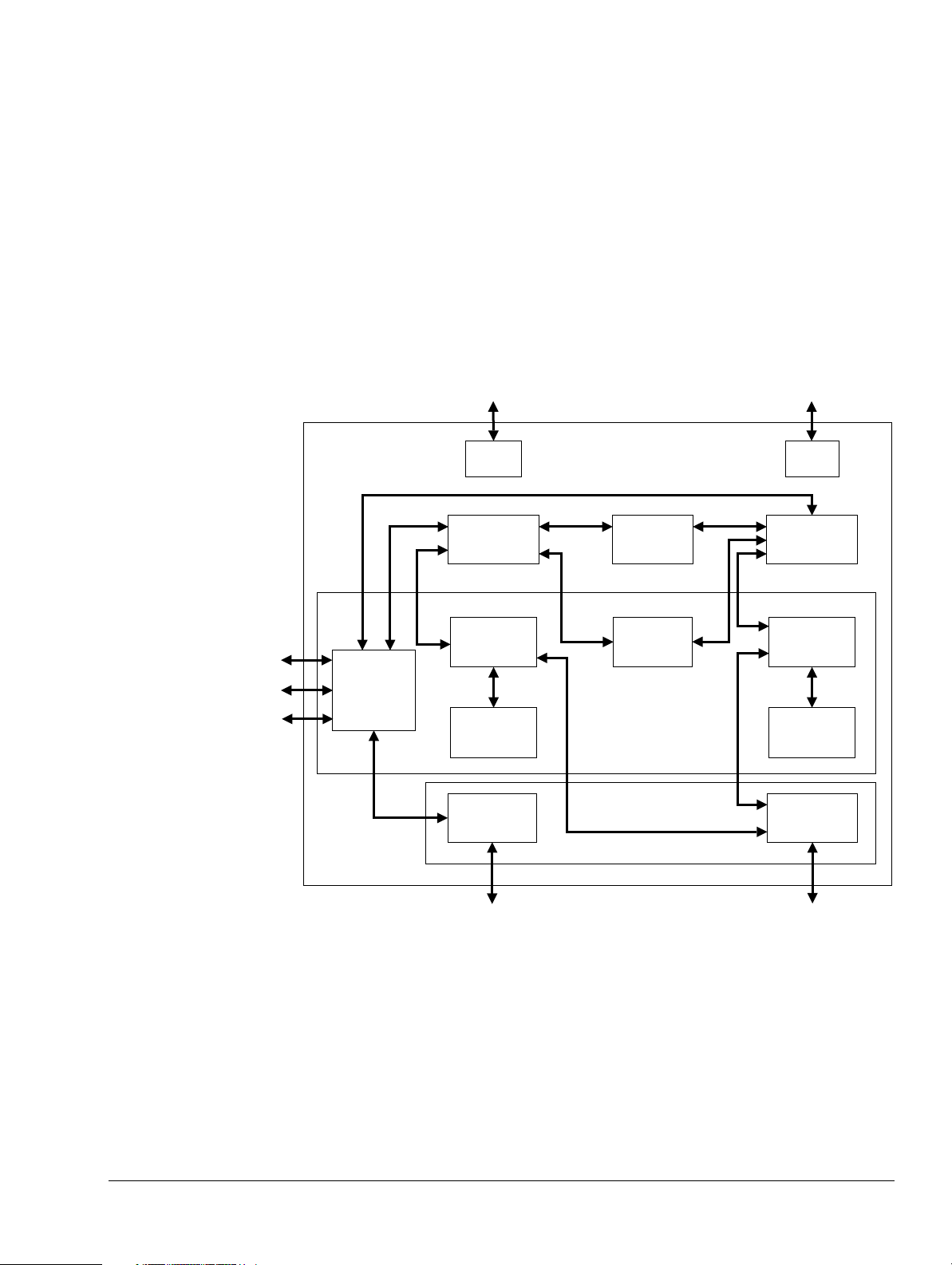

1.1 About the processor ................................................................................................. 1-2

1.2 About the architecture .............................................................................................. 1-3

1.3 Components of the processor .................................................................................. 1-4

1.4 External interfaces of the processor ...................................................................... 1-11

1.5 Power management ............................................................................................... 1-12

1.6 Configurable options .............................................................................................. 1-13

1.7 Execution pipeline stages ...................................................................................... 1-17

1.8 Redundant core comparison .................................................................................. 1-19

1.9 Test features .......................................................................................................... 1-20

1.10 Product documentation, design flow, and architecture .......................................... 1-21

1.11 Product revision information .................................................................................. 1-24

Chapter 2 Programmer’s Model

2.1 About the programmer’s model ............................................................................... 2-2

2.2 Instruction set states ................................................................................................ 2-3

2.3 Operating modes ..................................................................................................... 2-4

2.4 Data types ................................................................................................................ 2-5

2.5 Memory formats ....................................................................................................... 2-6

2.6 Registers .................................................................................................................. 2-7

2.7 Program status registers ........................................................................................ 2-10

2.8 Exceptions ............................................................................................................. 2-16

2.9 Acceleration of execution environments ................................................................ 2-27

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. iii

ID013010 Non-Confidential, Unrestricted Access

Page 4

2.10 Unaligned and mixed-endian data access support ................................................ 2-28

2.11 Big-endian instruction support ............................................................................... 2-29

Chapter 3 Processor Initialization, Resets, and Clocking

3.1 Initialization .............................................................................................................. 3-2

3.2 Resets ...................................................................................................................... 3-6

3.3 Reset modes ............................................................................................................ 3-7

3.4 Clocking ................................................................................................................... 3-9

Chapter 4 System Control Coprocessor

4.1 About the system control coprocessor ..................................................................... 4-2

4.2 System control coprocessor registers ...................................................................... 4-9

Chapter 5 Prefetch Unit

5.1 About the prefetch unit ............................................................................................. 5-2

5.2 Branch prediction ..................................................................................................... 5-3

5.3 Return stack ............................................................................................................. 5-5

Chapter 6 Events and Performance Monitor

6.1 About the events ...................................................................................................... 6-2

6.2 About the PMU ........................................................................................................ 6-6

6.3 Performance monitoring registers ............................................................................ 6-7

6.4 Event bus interface ................................................................................................ 6-19

Contents

Chapter 7 Memory Protection Unit

7.1 About the MPU ........................................................................................................ 7-2

7.2 Memory types .......................................................................................................... 7-7

7.3 Region attributes ...................................................................................................... 7-9

7.4 MPU interaction with memory system ................................................................... 7-11

7.5 MPU faults ............................................................................................................. 7-12

7.6 MPU software-accessible registers ....................................................................... 7-13

Chapter 8 Level One Memory System

8.1 About the L1 memory system .................................................................................. 8-2

8.2 About the error detection and correction schemes .................................................. 8-4

8.3 Fault handling .......................................................................................................... 8-7

8.4 About the TCMs ..................................................................................................... 8-13

8.5 About the caches ................................................................................................... 8-18

8.6 Internal exclusive monitor ...................................................................................... 8-34

8.7 Memory types and L1 memory system behavior ................................................... 8-35

8.8 Error detection events ............................................................................................ 8-36

Chapter 9 Level Two Interface

9.1 About the L2 interface .............................................................................................. 9-2

9.2 AXI master interface ................................................................................................ 9-3

9.3 AXI master interface transfers ................................................................................. 9-7

9.4 AXI slave interface ................................................................................................. 9-20

9.5 Enabling or disabling AXI slave accesses ............................................................. 9-23

9.6 Accessing RAMs using the AXI slave interface ..................................................... 9-24

Chapter 10 Power Control

10.1 About power control ............................................................................................... 10-2

10.2 Power management ............................................................................................... 10-3

Chapter 11 Debug

11.1 Debug systems ...................................................................................................... 11-2

11.2 About the debug unit .............................................................................................. 11-3

11.3 Debug register interface ........................................................................................ 11-5

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. iv

ID013010 Non-Confidential, Unrestricted Access

Page 5

11.4 Debug register descriptions ................................................................................. 11-10

11.5 Management registers ......................................................................................... 11-32

11.6 Debug events ....................................................................................................... 11-39

11.7 Debug exception .................................................................................................. 11-41

11.8 Debug state ......................................................................................................... 11-44

11.9 Cache debug ....................................................................................................... 11-50

11.10 External debug interface ...................................................................................... 11-51

11.11 Using the debug functionality ............................................................................... 11-54

11.12 Debugging systems with energy management capabilities ................................. 11-71

Chapter 12 FPU Programmer’s Model

12.1 About the FPU programmer’s model ..................................................................... 12-2

12.2 General-purpose registers ..................................................................................... 12-3

12.3 System registers .................................................................................................... 12-4

12.4 Modes of operation .............................................................................................. 12-10

12.5 Compliance with the IEEE 754 standard ............................................................. 12-11

Chapter 13 Integration Test Registers

13.1 About Integration Test Registers ........................................................................... 13-2

13.2 Programming and reading Integration Test Registers ........................................... 13-3

13.3 Summary of the processor registers used for integration testing .......................... 13-4

13.4 Processor integration testing ................................................................................. 13-5

Contents

Chapter 14 Cycle Timings and Interlock Behavior

14.1 About cycle timings and interlock behavior ............................................................ 14-3

14.2 Register interlock examples ................................................................................... 14-6

14.3 Data processing instructions .................................................................................. 14-7

14.4 QADD, QDADD, QSUB, and QDSUB instructions ................................................ 14-9

14.5 Media data-processing ........................................................................................ 14-10

14.6 Sum of Absolute Differences (SAD) .................................................................... 14-11

14.7 Multiplies .............................................................................................................. 14-12

14.8 Divide ................................................................................................................... 14-14

14.9 Branches .............................................................................................................. 14-15

14.10 Processor state updating instructions .................................................................. 14-16

14.11 Single load and store instructions ........................................................................ 14-17

14.12 Load and Store Double instructions ..................................................................... 14-20

14.13 Load and Store Multiple instructions .................................................................... 14-21

14.14 RFE and SRS instructions ................................................................................... 14-24

14.15 Synchronization instructions ................................................................................ 14-25

14.16 Coprocessor instructions ..................................................................................... 14-26

14.17 SVC, BKPT, Undefined, and Prefetch Aborted instructions ................................ 14-27

14.18 Miscellaneous instructions ................................................................................... 14-28

14.19 Floating-point register transfer instructions .......................................................... 14-29

14.20 Floating-point load/store instructions ................................................................... 14-30

14.21 Floating-point single-precision data processing instructions ............................... 14-32

14.22 Floating-point double-precision data processing instructions .............................. 14-33

14.23 Dual issue ............................................................................................................ 14-34

Chapter 15 AC Characteristics

15.1 Processor timing .................................................................................................... 15-2

15.2 Processor timing parameters ................................................................................. 15-3

Appendix A Processor Signal Descriptions

A.1 About the processor signal descriptions .................................................................. A-2

A.2 Global signals .......................................................................................................... A-3

A.3 Configuration signals ............................................................................................... A-4

A.4 Interrupt signals, including VIC interface signals ..................................................... A-7

A.5 L2 interface signals .................................................................................................. A-8

A.6 TCM interface signals ............................................................................................ A-13

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. v

ID013010 Non-Confidential, Unrestricted Access

Page 6

A.7 Dual core interface signals .................................................................................... A-16

A.8 Debug interface signals ......................................................................................... A-17

A.9 ETM interface signals ............................................................................................ A-19

A.10 Test signals ............................................................................................................ A-20

A.11 MBIST signals ........................................................................................................ A-21

A.12 Validation signals ................................................................................................... A-22

A.13 FPU signals ........................................................................................................... A-23

Appendix B ECC Schemes

B.1 ECC scheme selection guidelines ........................................................................... B-2

Appendix C Revisions

Glossary

Contents

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. vi

ID013010 Non-Confidential, Unrestricted Access

Page 7

List of Tables

Cortex-R4 and Cortex-R4F Technical Reference

Manual

Change History ............................................................................................................................... ii

Table 1-1 Configurable options ................................................................................................................. 1-13

Table 1-2 Configurable options at reset .................................................................................................... 1-15

Table 1-3 ID values for different product versions .................................................................................... 1-25

Table 2-1 Register mode identifiers ............................................................................................................ 2-8

Table 2-2 GE[3:0] settings ........................................................................................................................ 2-12

Table 2-3 PSR mode bit values ................................................................................................................ 2-14

Table 2-4 Exception entry and exit ............................................................................................................ 2-16

Table 2-5 Configuration of exception vector address locations ................................................................ 2-26

Table 2-6 Exception vectors ...................................................................................................................... 2-26

Table 2-7 Jazelle register instruction summary ......................................................................................... 2-27

Table 3-1 Reset modes ............................................................................................................................... 3-7

Table 4-1 System control coprocessor register functions ........................................................................... 4-3

Table 4-2 Summary of CP15 registers and operations ............................................................................... 4-9

Table 4-3 Main ID Register bit functions ................................................................................................... 4-15

Table 4-4 Cache Type Register bit functions ............................................................................................ 4-16

Table 4-5 TCM Type Register bit functions ............................................................................................... 4-16

Table 4-6 MPU Type Register bit functions .............................................................................................. 4-17

Table 4-7 Processor Feature Register 0 bit functions ............................................................................... 4-19

Table 4-8 Processor Feature Register 1 bit functions ............................................................................... 4-19

Table 4-9 Debug Feature Register 0 bit functions .................................................................................... 4-20

Table 4-10 Memory Model Feature Register 0 bit functions ....................................................................... 4-22

Table 4-11 Memory Model Feature Register 1 bit functions ....................................................................... 4-23

Table 4-12 Memory Model Feature Register 2 bit functions ....................................................................... 4-24

Table 4-13 Memory Model Feature Register 3 bit functions ....................................................................... 4-25

Table 4-14 Instruction Set Attributes Register 0 bit functions ..................................................................... 4-26

Table 4-15 Instruction Set Attributes Register 1 bit functions ..................................................................... 4-28

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. vii

ID013010 Non-Confidential, Unrestricted Access

Page 8

List of Tables

Table 4-16 Instruction Set Attributes Register 2 bit functions ..................................................................... 4-29

Table 4-17 Instruction Set Attributes Register 3 bit functions ..................................................................... 4-30

Table 4-18 Instruction Set Attributes Register 4 bit functions ..................................................................... 4-31

Table 4-19 Current Cache Size Identification Register bit functions ........................................................... 4-33

Table 4-20 Bit field and register encodings for Current Cache Size Identification Register ........................ 4-33

Table 4-21 Current Cache Level ID Register bit functions .......................................................................... 4-34

Table 4-22 Cache Size Selection Register bit functions ............................................................................. 4-35

Table 4-23 System Control Register bit functions ....................................................................................... 4-36

Table 4-24 Auxiliary Control Register bit functions ..................................................................................... 4-38

Table 4-25 Secondary Auxiliary Control Register bit functions ................................................................... 4-42

Table 4-26 Coprocessor Access Register bit functions .............................................................................. 4-45

Table 4-27 Fault Status Register encodings ............................................................................................... 4-45

Table 4-28 Data Fault Status Register bit functions .................................................................................... 4-46

Table 4-29 Instruction Fault Status Register bit functions ........................................................................... 4-47

Table 4-30 ADFSR and AIFSR bit functions ............................................................................................... 4-48

Table 4-31 MPU Region Base Address Registers bit functions .................................................................. 4-50

Table 4-32 Region Size Register bit functions ............................................................................................ 4-51

Table 4-33 MPU Region Access Control Register bit functions .................................................................. 4-52

Table 4-34 Access data permission bit encoding ........................................................................................ 4-52

Table 4-35 MPU Memory Region Number Register bit functions ............................................................... 4-53

Table 4-36 Functional bits of c7 for Set and Way ....................................................................................... 4-56

Table 4-37 Widths of the set field for L1 cache sizes .................................................................................. 4-56

Table 4-38 Functional bits of c7 for address format .................................................................................... 4-57

Table 4-39 BTCM Region Register bit functions ......................................................................................... 4-58

Table 4-40 ATCM Region Register bit functions ......................................................................................... 4-59

Table 4-41 Slave Port Control Register bit functions .................................................................................. 4-60

Table 4-42 nVAL IRQ Enable Set Register bit functions ............................................................................. 4-62

Table 4-43 nVAL FIQ Enable Set Register bit functions ............................................................................. 4-63

Table 4-44 nVAL Reset Enable Set Register bit functions .......................................................................... 4-64

Table 4-45 nVAL Debug Request Enable Set Register bit functions .......................................................... 4-65

Table 4-46 nVAL IRQ Enable Clear Register bit functions ......................................................................... 4-66

Table 4-47 nVAL FIQ Enable Clear Register bit functions .........................................................................

. 4-67

Table 4-48 nVAL Reset Enable Clear Register bit functions ...................................................................... 4-67

Table 4-49 nVAL Debug Request Enable Clear Register bit functions ....................................................... 4-68

Table 4-50 nVAL Cache Size Override Register ......................................................................................... 4-69

Table 4-51 nVAL instruction and data cache size encodings ..................................................................... 4-69

Table 4-52 Correctable Fault Location Register - cache ............................................................................. 4-71

Table 4-53 Correctable Fault Location Register - TCM .............................................................................. 4-71

Table 4-54 Build Options 1 Register ........................................................................................................... 4-72

Table 4-55 Build Options 2 Register ........................................................................................................... 4-73

Table 6-1 Event bus interface bit functions ................................................................................................. 6-2

Table 6-2 PMNC Register bit functions ....................................................................................................... 6-7

Table 6-3 CNTENS Register bit functions ................................................................................................... 6-9

Table 6-4 CNTENC Register bit functions ................................................................................................ 6-10

Table 6-5 Overflow Flag Status Register bit functions .............................................................................. 6-11

Table 6-6 SWINCR Register bit functions ................................................................................................. 6-12

Table 6-7 Performance Counter Selection Register bit functions ............................................................. 6-13

Table 6-8 EVTSELx Register bit functions ................................................................................................ 6-14

Table 6-9 USEREN Register bit functions ................................................................................................ 6-15

Table 6-10 INTENS Register bit functions .................................................................................................. 6-16

Table 6-11 INTENC Register bit functions .................................................................................................. 6-17

Table 7-1 Default memory map ................................................................................................................... 7-2

Table 7-2 Memory attributes summary ....................................................................................................... 7-7

Table 7-3 TEX[2:0], C, and B encodings ..................................................................................................... 7-9

Table 7-4 Inner and Outer cache policy encoding .................................................................................... 7-10

Table 8-1 Types of aborts ......................................................................................................................... 8-11

Table 8-2 Cache parity error behavior ...................................................................................................... 8-21

Table 8-3 Cache ECC error behavior ........................................................................................................ 8-22

Table 8-4 Tag RAM bit descriptions, with parity ........................................................................................ 8-26

Table 8-5 Tag RAM bit descriptions, with ECC ......................................................................................... 8-26

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. viii

ID013010 Non-Confidential, Unrestricted Access

Page 9

List of Tables

Table 8-6 Tag RAM bit descriptions, no parity or ECC ............................................................................. 8-26

Table 8-7 Cache sizes and tag RAM organization .................................................................................... 8-27

Table 8-8 Organization of a dirty RAM line ............................................................................................... 8-27

Table 8-9 Instruction cache data RAM sizes, no parity or ECC ................................................................ 8-29

Table 8-10 Data cache data RAM sizes, no parity or ECC ......................................................................... 8-29

Table 8-11 Instruction cache data RAM sizes, with parity .......................................................................... 8-29

Table 8-13 Data cache RAM bits, with parity .............................................................................................. 8-30

Table 8-14 Instruction cache data RAM sizes with ECC ............................................................................. 8-30

Table 8-12 Data cache data RAM sizes, with parity ................................................................................... 8-30

Table 8-15 Data cache data RAM sizes with ECC ...................................................................................... 8-31

Table 8-16 Data cache RAM bits, with ECC ............................................................................................... 8-31

Table 8-17 Memory types and associated behavior ................................................................................... 8-35

Table 9-1 AXI master interface attributes .................................................................................................... 9-3

Table 9-2 ARCACHEM and AWCACHEM encodings ................................................................................. 9-5

Table 9-3 ARUSERM and AWUSERM encodings ...................................................................................... 9-5

Table 9-4 Non-cacheable LDRB ................................................................................................................. 9-8

Table 9-5 LDRH from Strongly Ordered or Device memory ....................................................................... 9-9

Table 9-6 LDR or LDM1 from Strongly Ordered or Device memory ........................................................... 9-9

Table 9-7 LDM5, Strongly Ordered or Device memory ............................................................................. 9-10

Table 9-8 STRB to Strongly Ordered or Device memory .......................................................................... 9-11

Table 9-9 STRH to Strongly Ordered or Device memory .......................................................................... 9-11

Table 9-10 STR or STM1 to Strongly Ordered or Device memory ............................................................. 9-12

Table 9-11 STM7 to Strongly Ordered or Device memory to word 0 or 1 ................................................... 9-12

Table 9-12 Linefill behavior on the AXI interface ........................................................................................ 9-13

Table 9-13 Cache line write-back ................................................................................................................ 9-13

Table 9-14 LDRH from Non-cacheable Normal memory ............................................................................ 9-13

Table 9-15 LDR or LDM1 from Non-cacheable Normal memory ................................................................ 9-14

Table 9-16 LDM5, Non-cacheable Normal memory or cache disabled ...................................................... 9-14

Table 9-17 STRH to Cacheable write-through or Non-cacheable Normal memory .................................... 9-15

Table 9-18 STR or STM1 to Cacheable write-through or Non-cacheable Normal memory ........................ 9-16

Table 9-19 AXI transaction splitting, all six words in same cache line ........................................................ 9-16

Table 9-20 AXI transaction splitting, data in two cache lines ...................................................................... 9-17

Table 9-21 Non-cacheable LDR or LDM1 crossing a cache line boundary ................................................ 9-17

Table 9-22 Cacheable write-through or Non-cacheable STRH crossing a cache line boundary ................ 9-17

Table 9-23 AXI transactions for Strongly Ordered or Device type memory ................................................ 9-18

Table 9-24 AXI transactions for Non-cacheable Normal or Cacheable write-through memory .................. 9-18

Table 9-25 AXI slave interface attributes .................................................................................................... 9-22

Table 9-26 RAM region decode .................................................................................................................. 9-24

Table 9-27 TCM chip-select decode ........................................................................................................... 9-25

Table 9-28 MSB bit for the different TCM RAM sizes ................................................................................. 9-25

Table 9-29 Cache RAM chip-select decode ................................................................................................ 9-26

Table 9-30 Cache tag/valid RAM bank/address decode ............................................................................. 9-26

Table 9-32 Data format, instruction cache and data cache, no parity and no ECC .................................... 9-27

Table 9-31 Cache data RAM bank/address decode ................................................................................... 9-27

Table 9-33 Data format, instruction cache and data cache, with parity ...................................................... 9-28

Table 9-34 Data format, instruction cache, with ECC ................................................................................. 9-28

Table 9-35 Data format, data cache, with ECC ........................................................................................... 9-28

Table 9-36 Tag register format for reads, no parity or ECC ........................................................................ 9-29

Table 9-37 Tag register format for reads, with parity .................................................................................. 9-29

Table 9-38 Tag register format for reads, with ECC ................................................................................... 9-29

Table 9-39 Tag register format for writes, no parity or ECC ....................................................................... 9-30

Table 9-40 Tag register format for writes, with parity .................................................................................. 9-30

Table 9-41 Tag register format for writes, with ECC ................................................................................... 9-30

Table 9-42 Dirty register format, with parity or with no error scheme ......................................................... 9-31

Table 9-43 Dirty register format, with ECC ................................................................................................. 9-31

Table 11-1 Access to CP14 debug registers ............................................................................................... 11-5

Table 11-2 CP14 debug registers summary ............................................................................................... 11-6

Table 11-3 Debug memory-mapped registers ............................................................................................ 11-6

Table 11-4 External debug interface access permissions ........................................................................... 11-9

Table 11-5 Terms used in register descriptions ........................................................................................ 11-10

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. ix

ID013010 Non-Confidential, Unrestricted Access

Page 10

List of Tables

Table 11-6 CP14 debug register map ....................................................................................................... 11-10

Table 11-7 Debug ID Register functions ................................................................................................... 11-11

Table 11-8 Debug ROM Address Register functions ................................................................................ 11-12

Table 11-9 Debug Self Address Offset Register functions ........................................................................ 11-13

Table 11-10 Debug Status and Control Register functions ......................................................................... 11-14

Table 11-11 Data Transfer Register functions ............................................................................................ 11-19

Table 11-12 Watchpoint Fault Address Register functions ......................................................................... 11-19

Table 11-13 Vector Catch Register functions ............................................................................................. 11-20

Table 11-14 Debug State Cache Control Register functions ...................................................................... 11-21

Table 11-15 Debug Run Control Register functions ................................................................................... 11-22

Table 11-16 Breakpoint Value Registers functions ..................................................................................... 11-23

Table 11-17 Breakpoint Control Registers functions ................................................................................... 11-24

Table 11-18 Meaning of BVR bits [22:20] ................................................................................................... 11-25

Table 11-19 Watchpoint Value Registers functions .................................................................................... 11-26

Table 11-20 Watchpoint Control Registers functions .................................................................................. 11-27

Table 11-21 OS Lock Status Register functions ......................................................................................... 11-29

Table 11-22 Authentication Status Register bit functions ........................................................................... 11-29

Table 11-23 PRCR functions ...................................................................................................................... 11-30

Table 11-24 PRSR functions ....................................................................................................................... 11-31

Table 11-25 Management Registers ........................................................................................................... 11-32

Table 11-26 Processor Identifier Registers ................................................................................................. 11-32

Table 11-27 Claim Tag Set Register functions ........................................................................................... 11-33

Table 11-28 Functional bits of the Claim Tag Clear Register ..................................................................... 11-34

Table 11-29 Lock Status Register functions ............................................................................................... 11-35

Table 11-30 Device Type Register functions .............................................................................................. 11-35

Table 11-31 Peripheral Identification Registers .......................................................................................... 11-36

Table 11-32 Fields in the Peripheral Identification Registers ...................................................................... 11-36

Table 11-33 Peripheral ID Register 0 functions .......................................................................................... 11-36

Table 11-34 Peripheral ID Register 1 functions .......................................................................................... 11-37

Table 11-35 Peripheral ID Register 2 functions .......................................................................................... 11-37

Table 11-36 Peripheral ID Register 3 functions .......................................................................................... 11-37

Table 11-37 Peripheral ID Register 4 functions .......................................................................................... 11-37

Table 11-38 Component Identification Registers ........................................................................................ 11-38

Table 11-39 Processor behavior on debug events ..................................................................................... 11-40

Table 11-40 Values in link register after exceptions ............................................................................

....... 11-42

Table 11-41 Read PC value after debug state entry ................................................................................... 11-44

Table 11-42 Authentication signal restrictions ............................................................................................ 11-52

Table 11-43 Values to write to BCR for a simple breakpoint ...................................................................... 11-58

Table 11-44 Values to write to WCR for a simple watchpoint ..................................................................... 11-59

Table 11-45 Example byte address masks for watchpointed objects ......................................................... 11-60

Table 12-1 VFP system registers ................................................................................................................ 12-4

Table 12-2 Accessing VFP system registers .............................................................................................. 12-4

Table 12-3 FPSID Register bit functions ..................................................................................................... 12-5

Table 12-4 FPSCR Register bit functions ................................................................................................... 12-6

Table 12-5 Floating-Point Exception Register bit functions ........................................................................ 12-8

Table 12-6 MVFR0 Register bit functions ................................................................................................... 12-8

Table 12-7 MVFR1 Register bit functions ................................................................................................... 12-9

Table 12-8 Default NaN values ................................................................................................................. 12-11

Table 12-9 QNaN and SNaN handling ...................................................................................................... 12-12

Table 13-1 Integration Test Registers summary ......................................................................................... 13-4

Table 13-2 Output signals that can be controlled by the Integration Test Registers ................................... 13-5

Table 13-3 Input signals that can be read by the Integration Test Registers .............................................. 13-6

Table 13-4 ITETMIF Register bit assignments ............................................................................................ 13-7

Table 13-5 ITMISCOUT Register bit assignments ...................................................................................... 13-8

Table 13-6 ITMISCIN Register bit assignments .......................................................................................... 13-9

Table 13-7 ITCTRL Register bit assignments ........................................................................................... 13-10

Table 14-1 Definition of cycle timing terms ................................................................................................. 14-4

Table 14-2 Register interlock examples ...................................................................................................... 14-6

Table 14-3 Data Processing Instruction cycle timing behavior if destination is not PC ............................... 14-7

Table 14-4 Data Processing instruction cycle timing behavior if destination is the PC ............................... 14-7

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. x

ID013010 Non-Confidential, Unrestricted Access

Page 11

List of Tables

Table 14-5 QADD, QDADD, QSUB, and QDSUB instruction cycle timing behavior ................................... 14-9

Table 14-6 Media data-processing instructions cycle timing behavior ...................................................... 14-10

Table 14-7 Sum of absolute differences instruction timing behavior ......................................................... 14-11

Table 14-8 Example interlocks .................................................................................................................. 14-11

Table 14-9 Example multiply instruction cycle timing behavior ................................................................. 14-12

Table 14-10 Branch instruction cycle timing behavior ................................................................................. 14-15

Table 14-11 Processor state updating instructions cycle timing behavior .................................................. 14-16

Table 14-12 Cycle timing behavior for stores and loads, other than loads to the PC ................................. 14-17

Table 14-13 Cycle timing behavior for loads to the PC ............................................................................... 14-17

Table 14-14 <addr_md_1cycle> and <addr_md_3cycle> LDR example instruction explanation ............... 14-18

Table 14-15 Load and Store Double instructions cycle timing behavior ..................................................... 14-20

Table 14-16 <addr_md_1cycle> and <addr_md_3cycle> LDRD example instruction explanation ............. 14-20

Table 14-17 Cycle timing behavior of Load and Store Multiples, other than load multiples including the PC .......

14-21

Table 14-18 Cycle timing behavior of Load Multiples, with PC in the register list (64-bit aligned) .............. 14-22

Table 14-19 RFE and SRS instructions cycle timing behavior .................................................................... 14-24

Table 14-20 Synchronization instructions cycle timing behavior ................................................................. 14-25

Table 14-21 Coprocessor instructions cycle timing behavior ...................................................................... 14-26

Table 14-22 SVC, BKPT, Undefined, prefetch aborted instructions cycle timing behavior ......................... 14-27

Table 14-23 IT and NOP instructions cycle timing behavior ....................................................................... 14-28

Table 14-24 Floating-point register transfer instructions cycle timing behavior .......................................... 14-29

Table 14-25 Floating-point load/store instructions cycle timing behavior .................................................... 14-30

Table 14-26 Floating-point single-precision data processing instructions cycle timing behavior ................ 14-32

Table 14-27 Floating-point double-precision data processing instructions cycle timing behavior ............... 14-33

Table 14-28 Permitted instruction combinations ......................................................................................... 14-35

Table 15-1 Miscellaneous input ports timing parameters: ........................................................................... 15-3

Table 15-2 Configuration input port timing parameters ............................................................................... 15-3

Table 15-3 Interrupt input ports timing parameters ..................................................................................... 15-4

Table 15-4 AXI master input port timing parameters .................................................................................. 15-4

Table 15-5 AXI slave input port timing parameters ..................................................................................... 15-5

Table 15-6 Debug input ports timing parameters ........................................................................................ 15-6

Table 15-7 ETM input ports timing parameters ........................................................................................... 15-6

Table 15-8 Test input ports timing parameters ........................................................................................... 15-7

Table 15-9 TCM interface input ports timing parameters ............................................................................ 15-7

Table 15-10 Miscellaneous output port timing parameter ............................................................................. 15-8

Table 15-11 Interrupt output ports timing parameters ................................................................................... 15-8

Table 15-12 AXI master output port timing parameters ................................................................................ 15-8

Table 15-13 AXI slave output ports timing parameters ................................................................................. 15-9

Table 15-14 Debug interface output ports timing parameters ..................................................................... 15-10

Table 15-15 ETM interface output ports timing parameters ........................................................................ 15-11

Table 15-16 Test output ports timing parameters ....................................................................................... 15-11

Table 15-17 TCM interface output ports timing parameters ........................................................................ 15-11

Table 15-18 FPU output port timing parameters ......................................................................................... 15-12

Table A-1 Global signals ............................................................................................................................. A-3

Table A-2 Configuration signals .................................................................................................................. A-4

Table A-3 Interrupt signals .......................................................................................................................... A-7

Table A-4 AXI master port signals for the L2 interface ................................................................................ A-8

Table A-5 AXI master port error detection signals ..................................................................................... A-10

Table A-6 AXI slave port signals for the L2 interface ................................................................................ A-10

Table A-7 AXI slave port error detection signals ....................................................................................... A-12

Table A-8 ATCM port signals .................................................................................................................... A-13

Table A-9 B0TCM port signals .................................................................................................................. A-13

Table A-10 B1TCM port signals .................................................................................................................. A-14

Table A-11 Dual core interface signals ........................................................................................................ A-16

Table A-12 Debug interface signals ............................................................................................................ A-17

Table A-13 Debug miscellaneous signals ................................................................................................... A-17

Table A-14 ETM interface signals ............................................................................................................... A-19

Table A-15 Test signals ............................................................................................................................... A-20

Table A-16 MBIST signals ........................................................................................................................... A-21

Table A-17 Validation signals ...................................................................................................................... A-22

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. xi

ID013010 Non-Confidential, Unrestricted Access

Page 12

List of Tables

Table A-18 FPU signals ............................................................................................................................... A-23

Table C-1 Differences between issue B and issue C .................................................................................. C-1

Table C-2 Differences between issue C and issue D .................................................................................. C-3

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. xii

ID013010 Non-Confidential, Unrestricted Access

Page 13

List of Figures

Cortex-R4 and Cortex-R4F Technical Reference

Manual

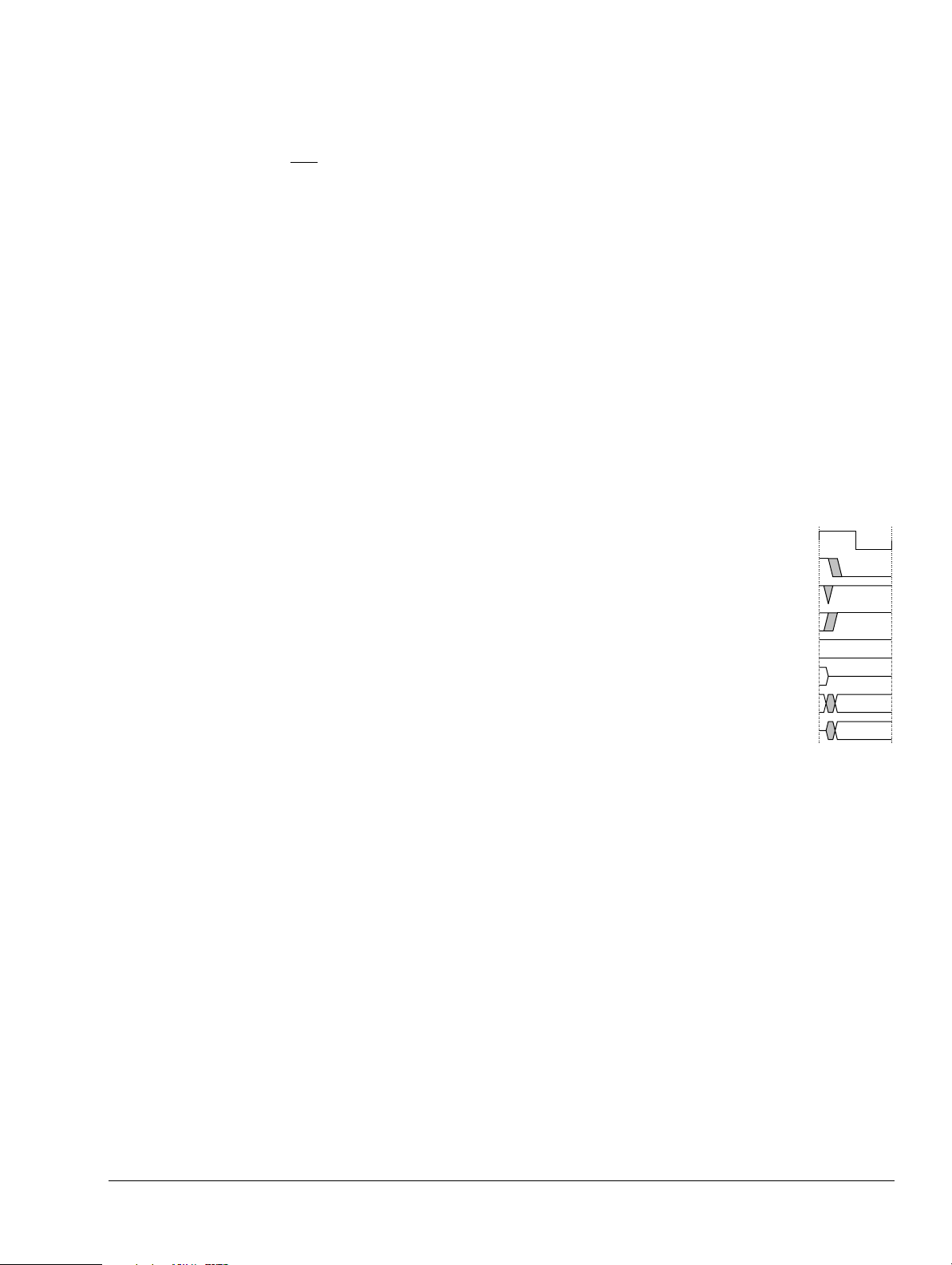

Key to timing diagram conventions .............................................................................................. xix

Figure 1-1 Processor block diagram ............................................................................................................ 1-4

Figure 1-2 Processor Fetch and Decode pipeline stages .......................................................................... 1-17

Figure 1-3 Cortex-R4 Issue and Execution pipeline stages ....................................................................... 1-17

Figure 1-4 Cortex-R4F Issue and Execution pipeline stages ..................................................................... 1-18

Figure 2-1 Byte-invariant big-endian (BE-8) format ...................................................................................... 2-6

Figure 2-2 Little-endian format ..................................................................................................................... 2-6

Figure 2-3 Register organization .................................................................................................................. 2-9

Figure 2-4 Program status register ............................................................................................................. 2-10

Figure 2-5 Interrupt entry sequence ........................................................................................................... 2-21

Figure 3-1 Power-on reset ............................................................................................................................ 3-7

Figure 3-2 AXI interface clocking ................................................................................................................. 3-9

Figure 4-1 System control and configuration registers ................................................................................. 4-4

Figure 4-2 MPU control and configuration registers ..................................................................................... 4-5

Figure 4-3 Cache control and configuration registers .................................................................................. 4-6

Figure 4-4 TCM control and configuration registers ..................................................................................... 4-6

Figure 4-5 System performance monitor registers ....................................................................................... 4-7

Figure 4-6 System validation registers ......................................................................................................... 4-7

Figure 4-7 Main ID Register format ............................................................................................................ 4-14

Figure 4-8 Cache Type Register format ..................................................................................................... 4-15

Figure 4-9 TCM Type Register format ........................................................................................................ 4-16

Figure 4-10 MPU Type Register format ....................................................................................................... 4-17

Figure 4-11 Multiprocessor ID Register format ............................................................................................ 4-18

Figure 4-12 Processor Feature Register 0 format ........................................................................................ 4-18

Figure 4-13 Processor Feature Register 1 format ........................................................................................ 4-19

Figure 4-14 Debug Feature Register 0 format ............................................................................................. 4-20

Figure 4-15 Memory Model Feature Register 0 format ................................................................................ 4-22

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. xiii

ID013010 Non-Confidential, Unrestricted Access

Page 14

List of Figures

Figure 4-16 Memory Model Feature Register 1 format ................................................................................ 4-23

Figure 4-17 Memory Model Feature Register 2 format ................................................................................ 4-24

Figure 4-18 Memory Model Feature Register 3 format ................................................................................ 4-25

Figure 4-19 Instruction Set Attributes Register 0 format .............................................................................. 4-26

Figure 4-20 Instruction Set Attributes Register 1 format .............................................................................. 4-27

Figure 4-21 Instruction Set Attributes Register 2 format .............................................................................. 4-29

Figure 4-22 Instruction Set Attributes Register 3 format .............................................................................. 4-30

Figure 4-23 Instruction Set Attributes Register 4 format .............................................................................. 4-31

Figure 4-24 Current Cache Size Identification Register format .................................................................... 4-33

Figure 4-25 Current Cache Level ID Register format ................................................................................... 4-34

Figure 4-26 Cache Size Selection Register format ...................................................................................... 4-35

Figure 4-27 System Control Register format ................................................................................................ 4-36

Figure 4-28 Auxiliary Control Register format .............................................................................................. 4-38

Figure 4-29 Secondary Auxiliary Control Register format ............................................................................ 4-42

Figure 4-30 Coprocessor Access Register format ....................................................................................... 4-44

Figure 4-31 Data Fault Status Register format ............................................................................................. 4-46

Figure 4-32 Instruction Fault Status Register format .................................................................................... 4-47

Figure 4-33 Auxiliary fault status registers format ........................................................................................ 4-48

Figure 4-34 MPU Region Base Address Registers format ........................................................................... 4-50

Figure 4-35 MPU Region Size and Enable Registers format ....................................................................... 4-51

Figure 4-36 MPU Region Access Control Register format ........................................................................... 4-52

Figure 4-37 MPU Memory Region Number Register format ........................................................................ 4-53

Figure 4-38 Cache operations ...................................................................................................................... 4-55

Figure 4-39 c7 format for Set and Way ........................................................................................................ 4-56

Figure 4-40 Cache operations address format ............................................................................................. 4-56

Figure 4-41 BTCM Region Registers ........................................................................................................... 4-58

Figure 4-42 ATCM Region Registers ........................................................................................................... 4-59

Figure 4-43 Slave Port Control Register ...................................................................................................... 4-60

Figure 4-44 nVAL IRQ Enable Set Register format ...................................................................................... 4-62

Figure 4-45 nVAL FIQ Enable Set Register format ...................................................................................... 4-63

Figure 4-46 nVAL Reset Enable Set Register format ................................................................................... 4-64

Figure 4-47 nVAL Debug Request Enable Set Register format ................................................................... 4-6

Figure 4-48 nVAL IRQ Enable Clear Register format .................................................................................. 4-66

Figure 4-49 nVAL FIQ Enable Clear Register format ................................................................................... 4-66

Figure 4-50 nVAL Reset Enable Clear Register format ............................................................................... 4-67

Figure 4-51 nVAL Debug Request Enable Clear Register format ................................................................ 4-68

Figure 4-52 nVAL Cache Size Override Register format ............................................................................. 4-69

Figure 4-53 Correctable Fault Location Register - cache ............................................................................. 4-70

Figure 4-54 Correctable Fault Location Register - TCM .............................................................................. 4-71

Figure 4-55 Build Options 1 Register format ................................................................................................ 4-72

Figure 4-56 Build Options 2 Register format ................................................................................................ 4-73

Figure 6-1 PMNC Register format ................................................................................................................ 6-7

Figure 6-2 CNTENS Register format ............................................................................................................ 6-9

Figure 6-3 CNTENC Register format ......................................................................................................... 6-10

Figure 6-4 FLAG Register format ............................................................................................................... 6-11

Figure 6-5 SWINCR Register format .......................................................................................................... 6-12

Figure 6-6 PMNXSEL Register format ....................................................................................................... 6-12

Figure 6-7 EVTSELx Register format ......................................................................................................... 6-14

Figure 6-8 USEREN Register format ......................................................................................................... 6-15

Figure 6-9 INTENS Register format ........................................................................................................... 6-16

Figure 6-10 INTENC Register format ........................................................................................................... 6-17

Figure 7-1 Overlapping memory regions ...................................................................................................... 7-5

Figure 7-2 Overlay for stack protection ........................................................................................................ 7-5

Figure 7-3 Overlapping subregion of memory .............................................................................................. 7-6

Figure 8-1 L1 memory system block diagram .............................................................................................. 8-3

Figure 8-2 Error detection and correction schemes ..................................................................................... 8-4

Figure 8-3 Nonsequential read operation performed with one RAM access. ............................................. 8-28

Figure 8-4 Sequential read operation performed with one RAM access .................................................... 8-28

Figure 11-1 Typical debug system ............................................................................................................... 11-2

Figure 11-2 Debug ID Register format ....................................................................................................... 11-11

5

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. xiv

ID013010 Non-Confidential, Unrestricted Access

Page 15

List of Figures

Figure 11-3 Debug ROM Address Register format .................................................................................... 11-12

Figure 11-4 Debug Self Address Offset Register format ............................................................................ 11-13

Figure 11-5 Debug Status and Control Register format ............................................................................. 11-14

Figure 11-6 Watchpoint Fault Address Register format ............................................................................. 11-19

Figure 11-7 Vector Catch Register format .................................................................................................. 11-20

Figure 11-8 Debug State Cache Control Register format .......................................................................... 11-21

Figure 11-9 Debug Run Control Register format ........................................................................................ 11-22

Figure 11-10 Breakpoint Control Registers format ....................................................................................... 11-23

Figure 11-11 Watchpoint Control Registers format ...................................................................................... 11-27

Figure 11-12 OS Lock Status Register format ............................................................................................. 11-29

Figure 11-13 Authentication Status Register format .................................................................................... 11-29

Figure 11-14 PRCR format ........................................................................................................................... 11-30

Figure 11-15 PRSR format ........................................................................................................................... 11-31

Figure 11-16 Claim Tag Set Register format ................................................................................................ 11-33

Figure 11-17 Claim Tag Clear Register format ............................................................................................ 11-34

Figure 11-18 Lock Status Register format .................................................................................................... 11-34

Figure 11-19 Device Type Register format .................................................................................................. 11-35

Figure 12-1 FPU register bank ..................................................................................................................... 12-3

Figure 12-2 Floating-Point System ID Register format ................................................................................. 12-5

Figure 12-3 Floating-Point Status and Control Register format ................................................................... 12-6

Figure 12-4 Floating-Point Exception Register format ................................................................................. 12-7

Figure 12-5 MVFR0 Register format ............................................................................................................ 12-8

Figure 12-6 MVFR1 Register format ............................................................................................................ 12-9

Figure 13-1 ITETMIF Register bit assignments ............................................................................................ 13-7

Figure 13-2 ITMISCOUT Register bit assignments ...................................................................................... 13-8

Figure 13-3 ITMISCIN Register bit assignments .......................................................................................... 13-9

Figure 13-4 ITCTRL Register bit assignments ............................................................................................. 13-9

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. xv

ID013010 Non-Confidential, Unrestricted Access

Page 16

Preface

This preface introduces the Cortex-R4 and Cortex-R4F Technical Reference Manual. It contains

the following sections:

• About this book on page xvii

• Feedback on page xxi.

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. xvi

ID013010 Non-Confidential, Unrestricted Access

Page 17

About this book

Product revision status

Intended audience

Preface

This is the Technical Reference Manual (TRM) for the Cortex-R4 and Cortex-R4F processors.

In this book the generic term processor means both the Cortex-R4 and Cortex-R4F processors.

Any differences between the two processors are described where necessary.

Note

The Cortex-R4F processor is a Cortex-R4 processor that includes the optional Floating Point

Unit (FPU) extension, see Product revision information on page 1-24 for more information.

In this book, references to the Cortex-R4 processor also apply to the Cortex-R4F processor,

unless the context makes it clear that this is not the case.

The rnpn identifier indicates the revision status of the product described in this book, where:

rn Identifies the major revision of the product.

pn Identifies the minor revision or modification status of the product.

Using this book

This book is written for system designers, system integrators, and programmers who are

designing or programming a System-on-Chip (SoC) that uses the processor.

This book is organized into the following chapters:

Chapter 1 Introduction

Read this for an introduction to the processor and descriptions of the major

functional blocks.

Chapter 2 Programmer’s Model

Read this for a description of the processor registers and programming

information.

Chapter 3 Processor Initialization, Resets, and Clocking

Read this for a description of clocking and resetting the processor, and the steps

that the software must take to initialize the processor after reset.

Chapter 4 System Control Coprocessor

Read this for a description of the system control coprocessor registers and

programming information.

Chapter 5 Prefetch Unit

Read this for a description of the functions of the Prefetch Unit (PFU), including

dynamic branch prediction and the return stack.

Chapter 6 Events and Performance Monitor

Read this for a description of the Performance Monitoring Unit (PMU) and the

event bus.

Chapter 7 Memory Protection Unit

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. xvii

ID013010 Non-Confidential, Unrestricted Access

Page 18

Read this for a description of the Memory Protection Unit (MPU) and the access

permissions process.

Chapter 8 Level One Memory System

Read this for a description of the Level One (L1) memory system.

Chapter 10 Power Control