Page 1

ARM926EJ-S

(r0p4/r0p5)

Technical Reference Manual

Copyright © 2001-2003 ARM Limited. All rights reserved.

ARM DDI0198D

Page 2

ARM926EJ-S

Technical Reference Manual

Copyright © 2001-2003 ARM Limited. All rights reserved.

Release Information

Change history

Date Issue Change

26 September 2001 A First release

29 January 2002 B Second release

5 December 2003 C Third release. Includes r0p5 changes. Defects corrected.

26 January 2004 D Fourth release. Includes r0p4. Technically identical to previous release.

Proprietary Notice

Words and logos marked with

as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the

trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document

may be adapted or reproduced in any material form except with the prior written permission of the copyright

holder.

®

or ™ are registered trademarks or trademarks owned by ARM Limited, except

The product described in this document is subject to continuous developments and improvements. All

particulars of the product and its use contained in this document are given by ARM in good faith. However,

all warranties implied or expressed, including but not limited to implied warranties of merchantability, or

fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable

for any loss or damage arising from the use of any information in this document, or any error or omission in

such information, or any incorrect use of the product.

Confidentiality Status

This document is Open Access. This document has no restriction on distribution.

Product Status

The information in this document is final, that is for a developed product.

Web Address

http://www.arm.com

ii Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 3

Contents

ARM926EJ-S Technical Reference Manual

Preface

About this manual ........................................................................................ xvi

Feedback ..................................................................................................... xxi

Chapter 1 Introduction

1.1 About the ARM926EJ-S processor ............................................................. 1-2

Chapter 2 Programmer’s Model

2.1 About the programmer’s model ................................................................... 2-2

2.2 Summary of ARM926EJ-S system control coprocessor (CP15) registers .. 2-3

2.3 Register descriptions .................................................................................. 2-7

Chapter 3 Memory Management Unit

3.1 About the MMU ........................................................................................... 3-2

3.2 Address translation ..................................................................................... 3-5

3.3 MMU faults and CPU aborts ..................................................................... 3-21

3.4 Domain access control .............................................................................. 3-24

3.5 Fault checking sequence .......................................................................... 3-26

3.6 External aborts .......................................................................................... 3-29

3.7 TLB structure ............................................................................................ 3-31

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. iii

Page 4

Contents

Chapter 4 Caches and Write Buffer

4.1 About the caches and write buffer .............................................................. 4-2

4.2 Write buffer ................................................................................................. 4-4

4.3 Enabling the caches ................................................................................... 4-5

4.4 TCM and cache access priorities ............................................................... 4-8

4.5 Cache MVA and Set/Way formats .............................................................. 4-9

Chapter 5 Tightly-Coupled Memory Interface

5.1 About the tightly-coupled memory interface ............................................... 5-2

5.2 TCM interface signals ................................................................................. 5-4

5.3 TCM interface bus cycle types and timing .................................................. 5-8

5.4 TCM programmer’s model ........................................................................ 5-19

5.5 TCM interface examples ........................................................................... 5-20

5.6 TCM access penalties .............................................................................. 5-29

5.7 TCM write buffer ....................................................................................... 5-30

5.8 Using synchronous SRAM as TCM memory ............................................ 5-31

5.9 TCM clock gating ...................................................................................... 5-32

Chapter 6 Bus Interface Unit

6.1 About the bus interface unit ........................................................................ 6-2

6.2 Supported AHB transfers ............................................................................ 6-3

Chapter 7 Noncachable Instruction Fetches

7.1 About noncachable instruction fetches ....................................................... 7-2

Chapter 8 Coprocessor Interface

8.1 About the ARM926EJ-S external coprocessor interface ............................ 8-2

8.2 LDC/STC .................................................................................................... 8-4

8.3 MCR/MRC .................................................................................................. 8-6

8.4 CDP ............................................................................................................ 8-8

8.5 Privileged instructions ................................................................................. 8-9

8.6 Busy-waiting and interrupts ...................................................................... 8-10

8.7 CPBURST ................................................................................................ 8-11

8.8 CPABORT ................................................................................................ 8-12

8.9 nCPINSTRVALID ..................................................................................... 8-13

8.10 Connecting multiple external coprocessors .............................................. 8-14

Chapter 9 Instruction Memory Barrier

9.1 About the instruction memory barrier operation ......................................... 9-2

9.2 IMB operation ............................................................................................. 9-3

9.3 Example IMB sequences ............................................................................ 9-5

Chapter 10 Embedded Trace Macrocell Support

10.1 About Embedded Trace Macrocell support .............................................. 10-2

iv Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 5

Chapter 11 Debug Support

11.1 About debug support ................................................................................. 11-2

Chapter 12 Power Management

12.1 About power management ........................................................................ 12-2

Appendix A Signal Descriptions

A.1 Signal properties and requirements ............................................................ A-2

A.2 AHB related signals .................................................................................... A-3

A.3 Coprocessor interface signals ..................................................................... A-5

A.4 Debug signals ............................................................................................. A-7

A.5 JTAG signals ............................................................................................... A-9

A.6 Miscellaneous signals ............................................................................... A-10

A.7 ETM interface signals ............................................................................... A-12

A.8 TCM interface signals ............................................................................... A-14

Appendix B CP15 Test and Debug Registers

B.1 About the Test and Debug Registers .......................................................... B-2

Glossary

Contents

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. v

Page 6

Contents

vi Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 7

List of Tables

ARM926EJ-S Technical Reference Manual

Change history .............................................................................................................. ii

Table 2-1 CP15 register summary ............................................................................................ 2-3

Table 2-2 Address types in ARM926EJ-S ................................................................................. 2-4

Table 2-3 CP15 abbreviations ................................................................................................... 2-5

Table 2-4 Reading from register c0 ........................................................................................... 2-7

Table 2-5 Register 0, ID code ................................................................................................... 2-8

Table 2-6 Ctype encoding ......................................................................................................... 2-9

Table 2-7 Cache size encoding (M=0) .................................................................................... 2-10

Table 2-8 Cache associativity encoding (M=0) ....................................................................... 2-10

Table 2-9 Line length encoding ............................................................................................... 2-11

Table 2-10 Example Cache Type Register format .................................................................... 2-11

Table 2-11 Control bit functions register c1 ............................................................................... 2-13

Table 2-12 Effects of Control Register on caches ..................................................................... 2-15

Table 2-13 Effects of Control Register on TCM interface .......................................................... 2-16

Table 2-14 Domain access control defines ............................................................................... 2-18

Table 2-15 FSR bit field descriptions ........................................................................................ 2-19

Table 2-16 FSR status field encoding ....................................................................................... 2-20

Table 2-17 Function descriptions register c7 ............................................................................ 2-21

Table 2-18 Cache operations c7 ............................................................................................... 2-22

Table 2-19 Register c8 TLB operations ..................................................................................... 2-25

Table 2-20 Cache Lockdown Register instructions ................................................................... 2-27

Table 2-21 Cache Lockdown Register L bits ............................................................................. 2-28

Table 2-22 TCM Region Register instructions .......................................................................... 2-29

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. vii

Page 8

List of Tables

Table 2-23 TCM Region Register c9 ........................................................................................ 2-30

Table 2-24 TCM Size field encoding ......................................................................................... 2-30

Table 2-25 Programming the TLB Lockdown Register ............................................................. 2-32

Table 2-26 FCSE PID Register operations ............................................................................... 2-34

Table 2-27 Context ID register operations ................................................................................ 2-35

Table 3-1 MMU program-accessible CP15 registers ................................................................ 3-4

Table 3-2 First-level descriptor bits ........................................................................................... 3-9

Table 3-3 Interpreting first-level descriptor bits [1:0] ............................................................... 3-10

Table 3-4 Section descriptor bits ............................................................................................ 3-11

Table 3-5 Coarse page table descriptor bits ........................................................................... 3-12

Table 3-6 Fine page table descriptor bits ................................................................................ 3-13

Table 3-7 Second-level descriptor bits .................................................................................... 3-15

Table 3-8 Interpreting page table entry bits [1:0] .................................................................... 3-16

Table 3-9 Priority encoding of fault status ............................................................................... 3-22

Table 3-10 FAR values for multi-word transfers ....................................................................... 3-23

Table 3-11 Domain access control register, access control bits ............................................... 3-24

Table 3-12 Interpreting access permission (AP) bits ................................................................ 3-24

Table 4-1 CP15 c1 I and M bit settings for the ICache ............................................................. 4-5

Table 4-2 Page table C bit settings for the ICache ................................................................... 4-5

Table 4-3 CP15 c1 C and M bit settings for the DCache .......................................................... 4-6

Table 4-4 Page table C and B bit settings for the DCache ....................................................... 4-6

Table 4-5 Instruction access priorities to the TCM and cache .................................................. 4-8

Table 4-6 Data access priorities to the TCM and cache ........................................................... 4-8

Table 4-7 Values of S and NSETS ......................................................................................... 4-10

Table 5-1 Relationship between DMDMAEN, DRDMACS, and DRIDLE ................................. 5-6

Table 6-1 Supported HBURST encodings ................................................................................ 6-4

Table 6-2 IHPROT[3:0] and DHPROT[3:0] attributes ............................................................... 6-5

Table 8-1 Handshake signal encoding ...................................................................................... 8-5

Table 8-2 CPBURST encoding ............................................................................................... 8-11

Table 11-1 Scan chain 15 format .............................................................................................. 11-2

Table 11-2 Scan chain 15 mapping to CP15 registers ............................................................. 11-4

Table A-1 AHB related signals .................................................................................................. A-3

Table A-2 Coprocessor interface signals .................................................................................. A-5

Table A-3 Debug signals ........................................................................................................... A-7

Table A-4 JTAG signals ............................................................................................................ A-9

Table A-5 Miscellaneous signals ............................................................................................. A-10

Table A-6 ETM interface signals ............................................................................................. A-12

Table A-7 TCM interface signals ............................................................................................. A-14

Table B-1 Debug Override Register .......................................................................................... B-3

Table B-2 Trace Control Register bit assignments .................................................................... B-5

Table B-3 MMU test operation instructions ............................................................................... B-5

Table B-4 Encoding of the main TLB entry-select bit fields ....................................................... B-6

Table B-5 Encoding of the TLB MVA tag bit fields .................................................................... B-7

Table B-6 Encoding of the TLB entry PA and AP bit fields ....................................................... B-8

Table B-7 Main TLB mapping to MMUxWD .............................................................................. B-9

Table B-8 Encoding of the lockdown TLB entry-select bit fields ............................................. B-11

Table B-9 Cache Debug Control Register bit assignments ..................................................... B-12

viii Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 9

List of Tables

Table B-10 MMU Debug Control Register bit assignments ....................................................... B-14

Table B-11 Memory Region Remap Register instructions ......................................................... B-15

Table B-12 Encoding of the Memory Region Remap Register .................................................. B-16

Table B-13 Encoding of the remap fields ................................................................................... B-16

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. ix

Page 10

List of Tables

x Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 11

List of Figures

ARM926EJ-S Technical Reference Manual

Key to timing diagram conventions ............................................................................ xix

Figure 1-1 ARM926EJ-S block diagram ..................................................................................... 1-3

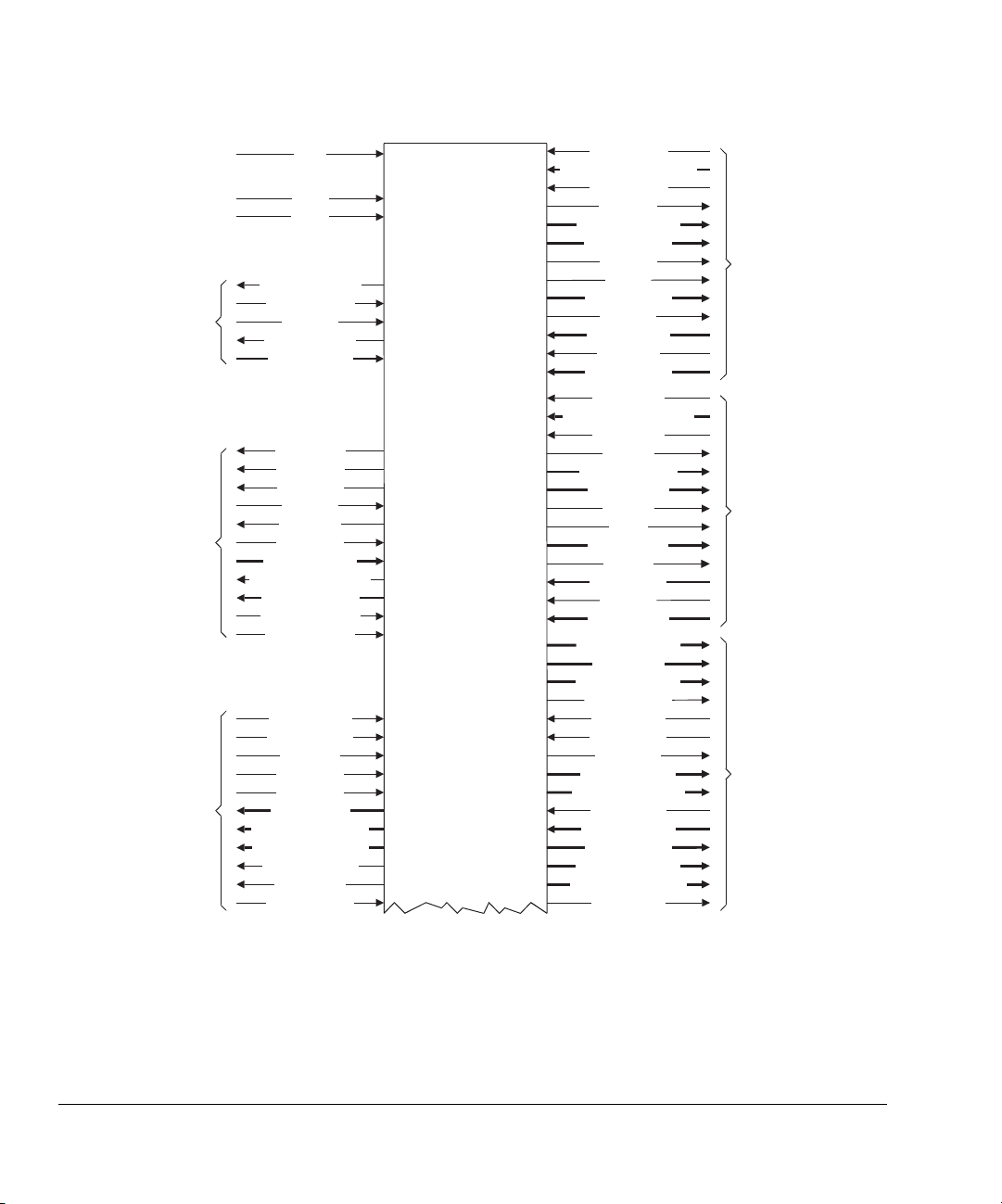

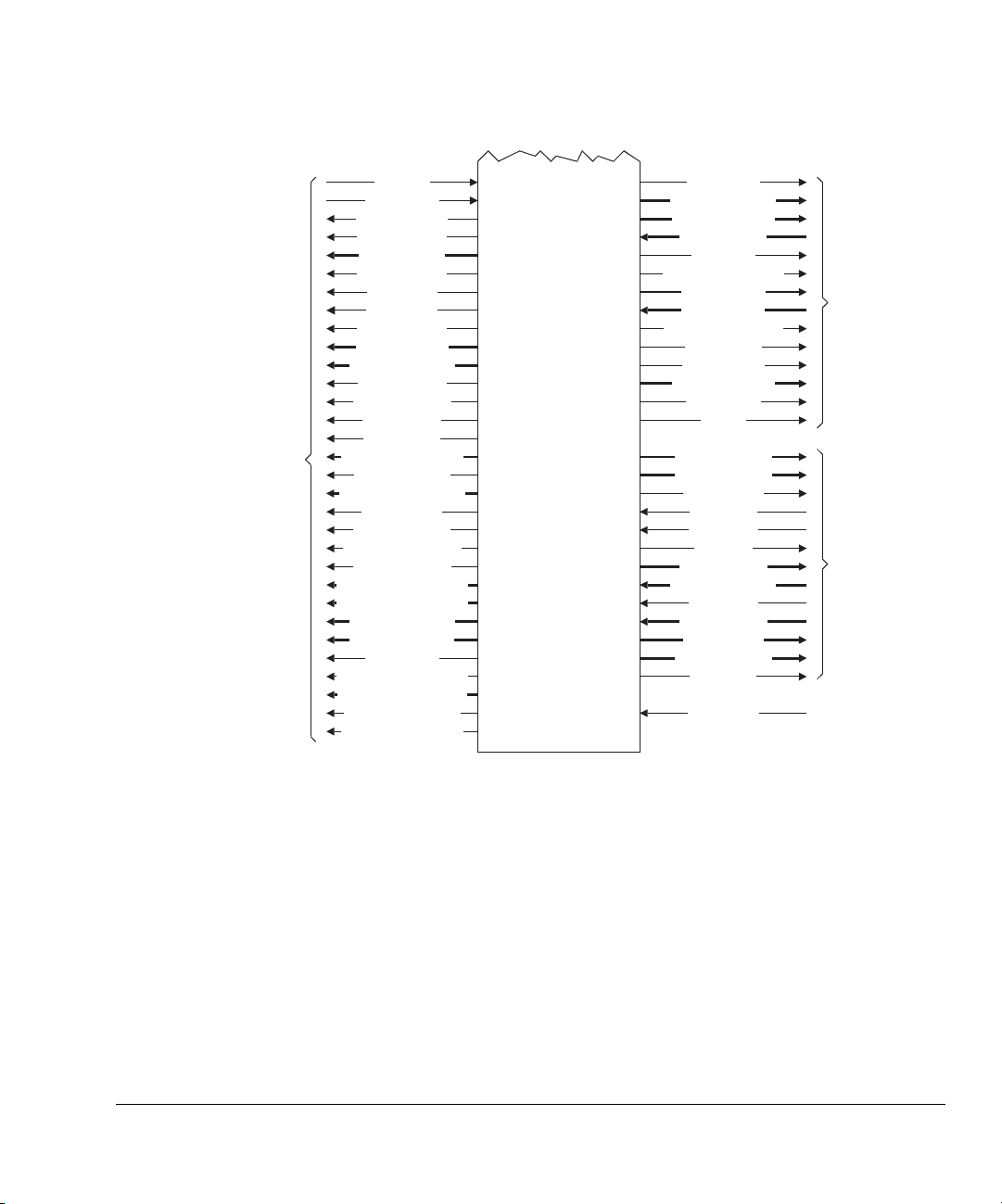

Figure 1-2 ARM926EJ-S interface diagram (part one) ............................................................... 1-4

Figure 1-3 ARM926EJ-S interface diagram (part two) ............................................................... 1-5

Figure 2-1 CP15 MRC and MCR bit pattern ............................................................................... 2-5

Figure 2-2 Cache Type Register format ..................................................................................... 2-9

Figure 2-3 Dsize and Isize field format ....................................................................................... 2-9

Figure 2-4 TCM Status Register format .................................................................................... 2-12

Figure 2-5 Control Register format ........................................................................................... 2-13

Figure 2-6 TTBR format ............................................................................................................ 2-17

Figure 2-7 Register c3 format ................................................................................................... 2-18

Figure 2-8 FSR format .............................................................................................................. 2-19

Figure 2-9 Register c7 MVA format .......................................................................................... 2-23

Figure 2-10 Register c7 Set/Way format .................................................................................... 2-24

Figure 2-11 Register c8 MVA format .......................................................................................... 2-26

Figure 2-12 Cache Lockdown Register c9 format ...................................................................... 2-27

Figure 2-13 TCM Region Register c9 format .............................................................................. 2-30

Figure 2-14 TLB Lockdown Register format ............................................................................... 2-32

Figure 2-15 Process ID Register format ..................................................................................... 2-34

Figure 2-16 Context ID Register format ...................................................................................... 2-35

Figure 3-1 Translation Table Base Register ............................................................................... 3-6

Figure 3-2 Translating page tables ............................................................................................. 3-7

Figure 3-3 Accessing translation table first-level descriptors ...................................................... 3-8

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. xi

Page 12

List of Figures

Figure 3-4 First-level descriptor ................................................................................................. 3-9

Figure 3-5 Section descriptor ................................................................................................... 3-10

Figure 3-6 Coarse page table descriptor .................................................................................. 3-11

Figure 3-7 Fine page table descriptor ...................................................................................... 3-12

Figure 3-8 Section translation .................................................................................................. 3-14

Figure 3-9 Second-level descriptor .......................................................................................... 3-15

Figure 3-10 Large page translation from a coarse page table ................................................... 3-17

Figure 3-11 Small page translation from a coarse page table ................................................... 3-18

Figure 3-12 Tiny page translation from a fine page table ........................................................... 3-19

Figure 3-13 Sequence for checking faults .................................................................................. 3-26

Figure 4-1 Generic virtually indexed virtually addressed cache ................................................. 4-9

Figure 4-2 ARM926EJ-S cache associativity ........................................................................... 4-10

Figure 4-3 ARM926EJ-S cache Set/Way/Word format ............................................................ 4-11

Figure 5-1 Multi-cycle data side TCM access ............................................................................ 5-8

Figure 5-2 Instruction side zero wait state accesses ................................................................. 5-9

Figure 5-3 Data side zero wait state accesses ........................................................................ 5-10

Figure 5-4 Relationship between DRDMAEN, DRDMACS, DRDMAADDR, DRADDR and DRCS ..

5-11

Figure 5-5 DMA access interaction with normal DTCM accesses ........................................... 5-12

Figure 5-6 Generating a single wait state for ITCM accesses using IRWAIT .......................... 5-13

Figure 5-7 State machine for generating a single wait state .................................................... 5-14

Figure 5-8 Loopback of SEQ to produce a single cycle wait state ........................................... 5-14

Figure 5-9 Cycle timing of loopback circuit .............................................................................. 5-15

Figure 5-10 DMA with single wait state for nonsequential accesses ......................................... 5-16

Figure 5-11 Cycle timing of circuit with DMA and single wait state for nonsequential accesses 5-17

Figure 5-12 Zero wait state RAM example ................................................................................. 5-20

Figure 5-13 Byte-banks of RAM example .................................................................................. 5-21

Figure 5-14 Optimizing for power ............................................................................................... 5-23

Figure 5-15 Optimizing for speed ............................................................................................... 5-24

Figure 5-16 TCM subsystem that uses wait states for nonsequential accesses ........................ 5-25

Figure 5-17 Cycle timing of circuit that uses wait states for non sequential accesses ............... 5-26

Figure 5-18 TCM subsystem that uses the DMA interface ........................................................ 5-27

Figure 5-19 TCM test access using BIST .................................................................................. 5-28

Figure 6-1 Multi-layer AHB system example ............................................................................. 6-8

Figure 6-2 Multi-AHB system example ...................................................................................... 6-9

Figure 6-3 AHB clock relationships .......................................................................................... 6-10

Figure 8-1 Producing a coprocessor clock ................................................................................. 8-2

Figure 8-2 Coprocessor clocking ............................................................................................... 8-2

Figure 8-3 LDC/STC cycle timing ............................................................................................... 8-4

Figure 8-4 MCR/MRC cycle timing ............................................................................................. 8-6

Figure 8-5 Interlocked MCR ....................................................................................................... 8-7

Figure 8-6 Latecanceled CDP .................................................................................................... 8-8

Figure 8-7 Privileged instructions ............................................................................................... 8-9

Figure 8-8 Busy waiting and interrupts ..................................................................................... 8-10

Figure 8-9 CPBURST and CPABORT timing ........................................................................... 8-12

Figure 8-10 Arrangement for connecting two coprocessors ...................................................... 8-14

Figure 12-1 Deassertion of STANDBYWFI after an IRQ interrupt ............................................. 12-2

xii Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 13

List of Figures

Figure 12-2 Logic for stopping ARM926EJ-S clock during wait for interrupt .............................. 12-3

Figure B-1 CP15 MRC and MCR bit pattern ............................................................................... B-2

Figure B-2 Rd format for selecting main TLB entry ..................................................................... B-6

Figure B-3 Rd format for accessing MVA tag of main or lockdown TLB entry ............................ B-7

Figure B-4 Rd format for accessing PA and AP data of main or lockdown TLB entry ................ B-8

Figure B-5 Write to the data RAM ............................................................................................. B-10

Figure B-6 Rd format for selecting lockdown TLB entry ........................................................... B-11

Figure B-7 Cache Debug Control Register format .................................................................... B-12

Figure B-8 MMU Debug Control Register format ...................................................................... B-14

Figure B-9 Memory Region Remap Register format ................................................................. B-15

Figure B-10 Memory region attribute resolution .......................................................................... B-17

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. xiii

Page 14

List of Figures

xiv Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 15

Preface

This preface introduces the ARM926EJ-S Revision r0p4/r0p5 Technical Reference

Manual (TRM). It contains the following sections:

• About this manual on page xvi

• Feedback on page xxi.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. xv

Page 16

Preface

About this manual

This is the Technical Reference Manual for the ARM926EJ-S processor.

Product revision status

The rnpn identifier indicates the revision status of the product described in this manual,

where:

rn Identifies the major revision of the product.

pn Identifies the minor revision or modification status of the product.

Intended audience

This document has been written for experienced hardware and software engineers who

have previous experience of ARM products, and who wish to use an ARM926EJ-S

processor in their system design.

Using this manual

This document is organized into the following chapters:

Chapter 1 Introduction

Read this chapter for an overview of the ARM926EJ-S processor.

Chapter 2 Programmer’s Model

Read this chapter for details of the programmer’s model and

ARM926EJ-S registers.

Chapter 3 Memory Management Unit

Read this chapter for details of the Memory Management Unit (MMU)

and address translation process and how to use the CP15 register to

enable and disable the MMU.

Chapter 4 Caches and Write Buffer

Read this chapter for a description of the instruction cache, the data

cache, the write buffer, and the physical address tag RAM.

Chapter 5 Tightly-Coupled Memory Interface

Read this chapter for a description of the Tightly-Coupled Memory

(TCM) interface and how to use the CP15 region register to enable and

disable the caches. It includes examples on how various RAM types can

be connected.

xvi Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 17

Chapter 6 Bus Interface Unit

Read this chapter for a description of the Bus Interface Unit (BIU)

interface to AMBA.

Chapter 7 Noncachable Instruction Fetches

Read this chapter for a description of how speculative noncachable

instruction fetches are used in the ARM926EJ-S processor to improve

performance.

Chapter 8 Coprocessor Interface

Read this chapter for a description of the coprocessor interface. The

chapter includes timing diagrams for coprocessor operations.

Chapter 9 Instruction Memory Barrier

Read this chapter for the Instruction Memory Barrier (IMB) description

and how IMB operations are used to ensure consistency between data and

instruction streams processed by the ARM926EJ-S processor.

Chapter 10 Embedded Trace Macrocell Support

Read this chapter to understand how Embedded Trace Macrocell (ETM)

is supported in the ARM926EJ-S processor.

Preface

Chapter 11 Debug Support

Read this chapter for a description of the debug interface and

EmbeddedICE-RT.

Chapter 12 Power Management

Read this chapter for a description of the power management facilities

provided by the ARM926EJ-S processor.

Appendix A Signal Descriptions

This appendix lists the ARM926EJ-S processor signals in functional

groups.

Appendix B CP15 Test and Debug Registers

Read this appendix for detailed information on the registers used for test

and debug.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. xvii

Page 18

Preface

Conventions

This section describes the conventions that this manual uses:

• Typographical

• Timing diagrams

• Signal naming on page xix

• Numbering on page xx.

Typographical

This manual uses the following typographical conventions:

italic Highlights important notes, introduces special terminology,

denotes internal cross-references, and citations.

bold Highlights interface elements, such as menu names. Denotes

ARM processor signal names. Also used for terms in descriptive

lists, where appropriate.

monospace

Denotes text that you can enter at the keyboard, such as

commands, file and program names, and source code.

monospace

Denotes a permitted abbreviation for a command or option. You

can enter the underlined text instead of the full command or option

name.

monospace italic

Denotes arguments to monospace text where the argument is to be

replaced by a specific value.

monospace bold

denotes language keywords when used outside example code.

< and > Angle brackets enclose replaceable terms for assembler syntax

where they appear in code or code fragments. They appear in

normal font in running text. For example:

•

MRC p15, 0 <Rd>, <CRn>, <CRm>, <Opcode_2>

• The Opcode_2 value selects which register is accessed.

Timing diagrams

This manual contains one or more timing diagrams. The figure named Key to timing

diagram conventions on page xix on page xix explains the components used in these

diagrams. When variations occur they have clear labels. You must not assume any

timing information that is not explicit in the diagrams.

xviii Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 19

Preface

Clock

HIGH to LOW

Transient

HIGH/LOW to HIGH

Bus stable

Bus to high impedance

Bus change

High impedance to stable bus

Key to timing diagram conventions

Signal naming

The level of an asserted signal depends on whether the signal is active-HIGH or

active-LOW. Asserted means HIGH for active-HIGH signals and LOW for active-LOW

signals:

Prefix H Denotes Advanced High-performance Bus (AHB) signals.

Prefix n Denotes active-LOW signals except in the case of AHB or Advanced

Peripheral Bus APB reset signals. These are named HRESETn and

PRESETn respectively.

Prefix DH Denotes data side AHB signals.

Prefix IH Denotes instruction side AHB signals.

Prefix DR Denotes data side TCM interface signals.

Prefix IR Denotes instruction side TCM interface signals.

Prefix ETM Denotes ETM interface signals.

Prefix DBG Denotes debug/JTAG signals.

Prefix CP Denotes coprocessor interface signals.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. xix

Page 20

Preface

Further reading

Numbering

<size in bits>’<base><number>

This is a Verilog method of abbreviating constant numbers. For example:

•‘h7B4 is an unsized hexadecimal value.

•‘o7654 is an unsized octal value.

• 8’d9 is an eight-bit wide decimal value of 9.

0x3F

• 8’h3F is an eight-bit wide hexadecimal value of

. This is

equivalent to b00111111.

• 8’b1111 is an eight-bit wide binary value of b00001111.

This section lists publications by ARM Limited, and by third parties.

ARM Limited periodically provides updates and corrections to its documentation. See

http://www.arm.com

for current errata sheets, addenda, and the ARM Limited

Frequently Asked Questions list.

ARM publications

This manual contains information that is specific to the ARM926EJ-S processor. Refer

to the following documents for other relevant information:

• ARM Architecture Reference Manual (ARM DDI 0100)

• ARM AMBA Specification (Rev 2.0) (ARM IHI 0001)

• ARM926EJ-S Implementation Guide (ARM DII 0015)

• ARM926EJ-S Test Chip Implementation Guide (ARM DXI 0131)

• ARM9EJ-S Technical Reference Manual (ARM DDI 0222)

• Multi-layer AHB Overview (ARM DVI 0045)

• ETM9 Technical Reference Manual (ARM DDI 0157).

xx Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 21

Feedback

ARM Limited welcomes feedback on the ARM926EJ-S processor and its

documentation.

Feedback on the product

If you have any comments or suggestions about this product, contact your supplier

giving:

• the product name

• a concise explanation of your comments.

Feedback on this manual

Preface

If you have any comments on this manual, send email to

errata@arm.com

giving:

• the title

• the number

• the relevant page number(s) to which your comments apply

• a concise explanation of your comments.

ARM Limited also welcomes general suggestions for additions and improvements.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. xxi

Page 22

Preface

xxii Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 23

Chapter 1

Introduction

This chapter introduces the ARM926EJ-S processor and its features. It contains the

following section:

• About the ARM926EJ-S processor on page 1-2.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 1-1

Page 24

Introduction

1.1 About the ARM926EJ-S processor

The ARM926EJ-S processor is a member of the ARM9 family of general-purpose

microprocessors. The ARM926EJ-S processor is targeted at multi-tasking applications

where full memory management, high performance, low die size, and low power are all

important.

The ARM926EJ-S processor supports the 32-bit ARM and 16-bit Thumb instruction

sets, enabling the user to trade off between high performance and high code density. The

ARM926EJ-S processor includes features for efficient execution of Java byte codes,

providing Java performance similar to JIT, but without the associated code overhead.

The ARM926EJ-S processor supports the ARM debug architecture and includes logic

to assist in both hardware and software debug. The ARM926EJ-S processor has a

Harvard cached architecture and provides a complete high-performance processor

subsystem, including:

• an ARM9EJ-S integer core

• a Memory Management Unit (MMU)

• separate instruction and data AMBA AHB bus interfaces

• separate instruction and data TCM interfaces.

The ARM926EJ-S processor provides support for external coprocessors enabling

floating-point or other application-specific hardware acceleration to be added. The

ARM926EJ-S processor implements ARM architecture version 5TEJ.

The ARM926EJ-S processor is a synthesizable macrocell. This means that you can

optimize the macrocell for a particular target library, and that you can configure the

memory system to suit your target application. You can individually configure the cache

sizes to be any power of two between 4KB and 128KB.

The tightly-coupled instruction and data memories are instantiated externally to the

ARM926EJ-S macrocell, providing you with the flexibility of optimizing the memory

subsystem for performance, power, and particular RAM type. The TCM interfaces

enable nonzero wait state memory to be attached, as well as providing a mechanism for

supporting DMA.

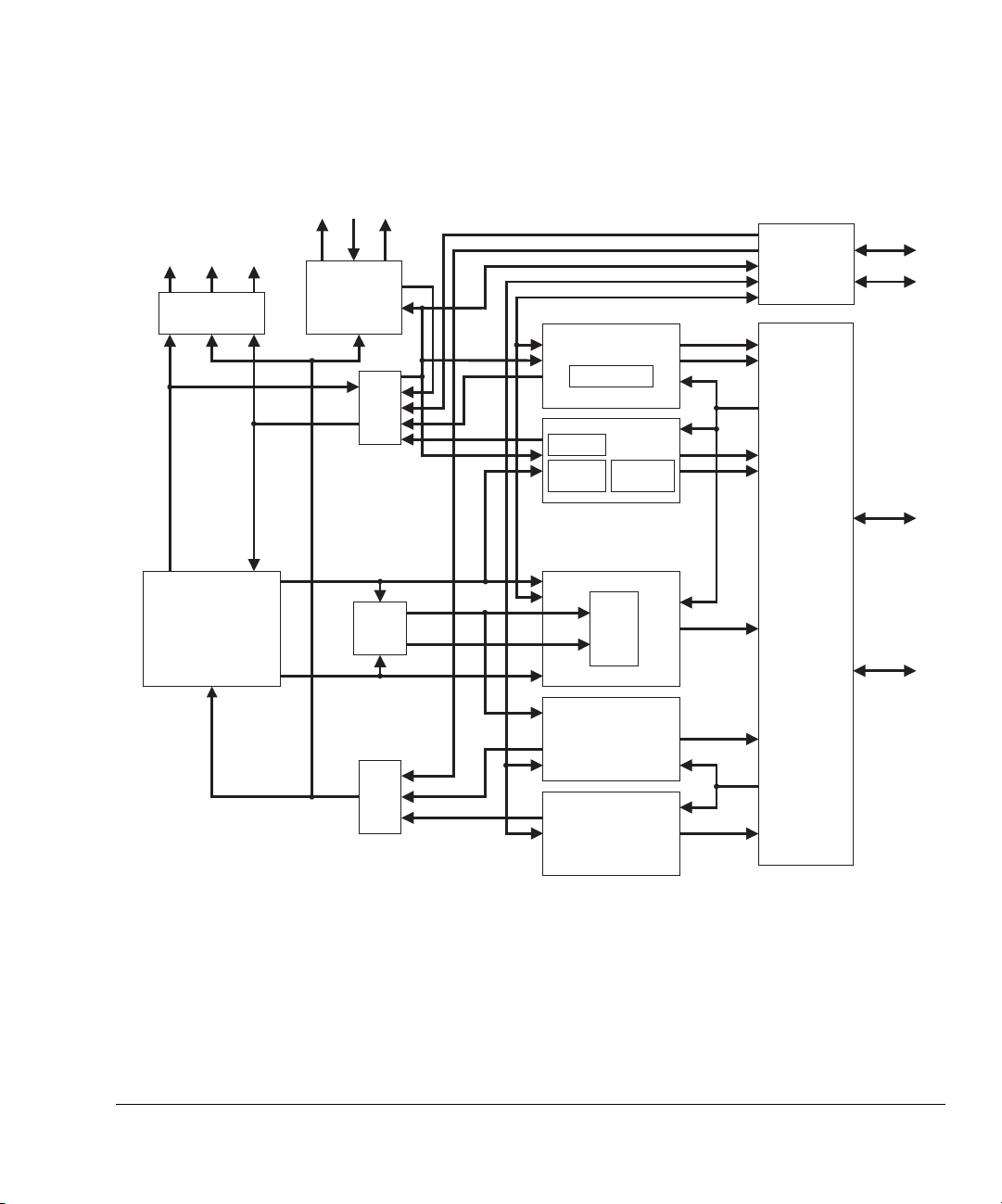

Figure 1-1 on page 1-3 shows the main blocks in the ARM926EJ-S processor.

1-2 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 25

ETM

interface

External

coprocessor

interface

CPDINCPDOUT CPINSTR

Coprocessor

interface

DEXT

DRDATA

IRDATA

DRWDATA

TCM

interface

Introduction

ITCM

DTCM

WDATA RDATA

DA

ARM9EJ-S FCSE

INSTR

IA

DROUTE

IROUTE

DMVA

IMVA

Write buffer

DCACHE

Cache

PA

TAGRAM

ICACHE

write buffer

MMU

TLB

IEXT

Writeback

interfac e

Bus

interface

unit

Instruction

interfac e

Data

AHB

AHB

AHB

AHB

Figure 1-1 ARM926EJ-S block diagram

Figure 1-2 on page 1-4 and Figure 1-3 on page 1-5 show the ARM926EJ-S interfaces.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 1-3

Page 26

Introduction

Clock

Interrupts

Miscellaneous

configuration

JTAG debug

Debug

CLK

nFIQ

nIRQ

STANDBYWFI

BIGENDINIT

VINITHI

CFGBIGEND

TAPID[31:0]

COMMRX

COMMTX

DBGACK

DBGEN

DBGRQI

EDBGRQ

DBGEXT[1:0]

DBGINSTREXEC

DBGRNG[1:0]

DBGIEBRKPT

DBGDEWPT

DBGnTRST

DBGTCKEN

DBGTDI

DBGTMS

DBGTDO

DBGIR[3:0]

DBGSCREG[4:0]

DBGTAPSM[3:0]

DBGnTDOEN

DBGSDIN

DBGSDOUT

ARM926EJ-S

DRDMAEN

DRDMAADDR[17:0]

DRDMACS

DRnRW

DRADDR[17:0]

DRWR[31:0]

DRIDLE

DRCS

DRWBL[3:0]

DRSEQ

DRRD[31:0]

DRWAIT

DRSIZE[3:0]

IRDMAEN

IRDMAADDR[17:0]

IRDMACS

IRnRW

IRADDR[17:0]

IRWR[31:0]

IRIDLE

IRCS

IRWBL[3:0]

IRSEQ

IRRD[31:0]

IRWAIT

IRSIZE[3:0]

DHADDR[31:0]

DHBL[3:0]

DHBURST[2:0]

DHBUSREQ

DHCLKEN

DHGRANT

DHLOCK

DHPROT[3:0]

DHRDATA[31:0]

DHREADY

DHRESP[1:0]

DHSIZE[2:0]

DHTRANS[1:0]

DHWDATA[31:0]

DHWRITE

Data

memory

interface

Instruction

memory interface

Data

AHB

Figure 1-2 ARM926EJ-S interface diagram (part one)

1-4 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 27

Introduction

ETM interface

ETMEN

FIFOFULL

ETMBIGEND

ETMHIVECS

ETMIA[31:0]

ETMInNREQ

ETMISEQ

ETMITBIT

ETMIABORT

ETMDA[31:0]

ETMDMAS[1:0]

ETMDMORE

ETMDnMREQ

ETMDnRW

ETMDSEQ

ETMRDATA[31:0]

ETMDABORT

ETMWDATA[31:0]

ETMnWAIT

ETMDBGACK

ETMINSTREXEC

ETMRNGOUT

ETMID31TO25[6:0]

ETMID15TO11[4:0]

ETMCHSD[1:0]

ETMCHSE[1:0]

ETMPASS

ETMLATECANCEL

ETMPROCID[31:0]

ETMPROCIDWR

ETMINSTRVALID

ARM926EJ-S

CPCLKEN

CPINSTR[31:0]

CPDOUT[31:0]

CPDIN[31:0]

CPPASS

CPLATECANCEL

CHSDE[1:0]

CHSEX[1:0]

nCPINSTRVALID

nCPMREQ

nCPTRANS

CPBURST[3:0]

CPABORT

CPEN

IHADDR[31:0]

IHBURST[2:0]

IHBUSREQ

IHCLKEN

IHGRANT

IHLOCK

IHPROT[3:0]

IHRDATA[31:0]

IHREADY

IHRESP[1:0]

IHSIZE[2:0]

IHTRANS[1:0]

IHWRITE

HRESETn

Coprocessor

Instruction

AHB

AHB

Figure 1-3 ARM926EJ-S interface diagram (part two)

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 1-5

Page 28

Introduction

1-6 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 29

Chapter 2

Programmer’s Model

This chapter describes the ARM926EJ-S registers in CP15, the system control

coprocessor, and provides information for programming the microprocessor. It contains

the following sections:

• About the programmer’s model on page 2-2

• Summary of ARM926EJ-S system control coprocessor (CP15) registers on

page 2-3

• Register descriptions on page 2-7.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 2-1

Page 30

Programmer’s Model

2.1 About the programmer’s model

The system control coprocessor (CP15) is used to configure and control the

ARM926EJ-S processor. The caches, Tightly-Coupled Memories (TCMs), Memory

Management Unit (MMU), and most other system options are controlled using CP15

registers. You can only access CP15 registers with MRC and MCR instructions in a

privileged mode. CDP, LDC, STC, MCRR, and MRRC instructions, and unprivileged

MRC or MCR instructions to CP15 cause the Undefined instruction exception to be

taken.

2-2 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 31

Programmer’s Model

2.2 Summary of ARM926EJ-S system control coprocessor (CP15) registers

CP15 defines 16 registers. Table 2-1 shows the read and write functions of the registers.

Table 2-1 CP15 register summary

Register Reads Writes

0

0

0

a

ID code

Cache type

TCM status

Unpredictable

a

a

Unpredictable

Unpredictable

1 Control Control

2 Translation table base Translation table base

3 Domain access control Domain access control

4 Reserved Reserved

5

5

Data fault status

Instruction fault status

a

a

Data fault status

Instruction fault status

a

6 Fault address Fault address

7 Cache operations Cache operations

8 Unpredictable TLB operations

9

Cache lockdown

b

Cache lockdown

9 TCM region TCM region

10 TLB lockdown TLB lockdown

a

11 and 12 Reserved Reserved

13

13

FCSE PID

Context ID

a

a

FCSE PID

Context ID

a

a

14 Reserved Reserved

15 Test configuration Test configuration

a. Register locations 0, 5, and 13 each provide access to more than one register. The register

accessed depends on the value of the

b. Register location 9 provides access to more than one register. The register accessed depends

on the value of the

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 2-3

CRm

field. See the register descriptions for details.

Opcode_2

field.

Page 32

Programmer’s Model

All CP15 register bits that are defined and contain state are set to 0 by Reset except:

• The V bit is set to 0 at reset if the VINITHI signal is LOW, or 1 if the VINITHI

signal is HIGH.

• The B bit is set to 0 at reset if the BIGENDINIT signal is LOW, or 1 if the

BIGENDINIT signal is HIGH.

• The instruction TCM is enabled at reset if the INITRAM pin is HIGH. This

enables booting from the instruction TCM and sets the ITCM bit in the ITCM

region register to 1.

2.2.1 Addresses in an ARM926EJ-S system

Three distinct types of address exist in an ARM926EJ-S system. Table 2-2 shows the

address types in ARM926EJ-S processor.

Domain ARM9EJ-S Caches and MMU TCM and AMBA bus

Address type Virtual Address (VA) Modified Virtual Address (MVA) Physical Address (PA)

Table 2-2 Address types in ARM926EJ-S

This is an example of the address manipulation that occurs when the ARM9EJ-S core

requests an instruction:

1. The VA of the instruction is issued by the ARM9EJ-S core.

2. The VA is translated using the FCSE PID value to the MVA. The Instruction

Cache (ICache) and Memory Management Unit (MMU) detect the MVA (see

Process ID Register c13 on page 2-33).

3. If the protection check carried out by the MMU on the MVA does not abort and

the MVA tag is in the ICache, the instruction data is returned to the ARM9EJ-S

core.

4. If the protection check carried out by the MMU on the MVA does not abort, and

the cache misses (the MVA tag is not in the cache), then the MMU translates the

MVA to produce the PA. This address is given to the AMBA bus interface to

perform an external access.

2.2.2 Accessing CP15 registers

You can only access CP15 registers with MRC and MCR instructions in a privileged

mode. The instruction bit pattern of the MCR and MRC instructions is shown in

Figure 2-1 on page 2-5.

2-4 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 33

Programmer’s Model

31 28 27 26 25 24 23 21 20 19 16 15 12 11 10 9 8 7 5 4 3 0

Cond

1 1 1 0

Opcode

_1

L CRn Rd 1 1 1 1

Opcode

_2

1 CRm

Figure 2-1 CP15 MRC and MCR bit pattern

The mnemonics for these instructions are:

MCR{cond} p15,<Opcode_1>,<Rd>,<CRn>,<CRm>,<Opcode_2>

MRC{cond} p15,<Opcode_1>,<Rd>,<CRn>,<CRm>,<Opcode_2>

Attempting to read from a write-only register, or writing to a read-only register causes

Unpredictable results. In all instructions that access CP15:

• The Opcode_1 field Should Be Zero except when the values specified are used to

select the desired operations. Using other values results in Unpredictable

behavior.

• The Opcode_2 and CRm fields Should Be Zero except when the values specified

are used to select the desired behavior. Using other values results in Unpredictable

behavior.

Table 2-3 shows the terms and abbreviations used in this chapter.

Table 2-3 CP15 abbreviations

Term Abbreviation Description

Unpredictable UNP For reads: The data returned when reading from

this location is unpredictable. It can have any

value.

For writes: Writing to this location causes

unpredictable behavior, or an unpredictable

change in device configuration.

Undefined UND An instruction that accesses CP15 in the manner

indicated takes the Undefined instruction

exception.

Should Be Zero SBZ When writing to this location, all bits of this field

Should Be Zero.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 2-5

Page 34

Programmer’s Model

Table 2-3 CP15 abbreviations (continued)

Term Abbreviation Description

Should Be One SBO When writing to this location, all bits in this field

Should Be One.

Should Be Zero or

Preserved

SBZP When writing to this location, all bits of this field

Should Be Zero or preserved by writing the same

value that has been previously read from the same

field.

In all cases, reading from, or writing any data values to any CP15 registers, including

those fields specified as Unpredictable, Should Be One, or Should Be Zero does not

cause any physical damage to the chip.

2-6 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 35

2.3 Register descriptions

The following registers are described in this section:

• ID Code, Cache Type, and TCM Status Registers, c0

• Control Register c1 on page 2-12

• Translation Table Base Register c2 on page 2-17

• Domain Access Control Register c3 on page 2-17

• Register c4 on page 2-18

• Fault Status Registers c5 on page 2-18

• Fault Address Register c6 on page 2-20

• Cache Operations Register c7 on page 2-20

• TLB Operations Register c8 on page 2-24

• Cache Lockdown and TCM Region Registers c9 on page 2-26

• TLB Lockdown Register c10 on page 2-32

• Register c11 and c12 on page 2-33

• Process ID Register c13 on page 2-33

• Register c14 on page 2-35

• Test and Debug Register c15 on page 2-36.

Programmer’s Model

2.3.1 ID Code, Cache Type, and TCM Status Registers, c0

Register c0 accesses the ID Register, Cache Type Register, and TCM Status Registers.

Reading from this register returns the device ID, the cache type, or the TCM status

depending on the value of Opcode_2 used:

Opcode_2 = 0 ID value.

Opcode_2 = 1 instruction and data cache type.

Opcode_2 = 2 TCM status.

The CRm field Should Be Zero when reading from these registers. Table 2-4 shows the

instructions you can use to read register c0.

Table 2-4 Reading from register c0

Function Instruction

Read ID code

Read cache type

Read TCM status

MRC p15,0,<Rd>,c0,c0,{0, 3-7}

MRC p15,0,<Rd>,c0,c0,1

MRC p15,0,<Rd>,c0,c0,2

Writing to register c0 is Unpredictable.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 2-7

Page 36

Programmer’s Model

ID Code Register c0

This is a read-only register that returns the 32-bit device ID code.

You can access the ID Code Register by reading CP15 register c0 with the Opcode_2

field set to any value other than 1 or 2. For example:

MRC p15, 0, <Rd>, c0, c0, {0, 3-7} ;returns ID

The contents of the ID Code Register are shown in Table 2-5.

Table 2-5 Register 0, ID code

Register bits Function Value

[31:24] ASCII code of implementer trademark

[23:20] Variant

[19:16] Architecture (ARMv5TEJ)

[15:4] Part number

[3:0] Revision

a. The revision value can be in the range 0x0 to 0x5, depending on the

layout revision you are using..

0x41

0x0

0x6

0x926

0x05

a

Cache Type Register c0

This is a read-only register that contains information about the size and architecture of

the Instruction Cache (ICache) and Data Cache (DCache) enabling operating systems

to establish how to perform such operations as cache cleaning and lockdown.

You can access the cache type register by reading CP15 register c0 with the Opcode_2

field set to 1. For example:

MRC p15, 0, <Rd>, c0, c0, 1; returns cache details

The format of the Cache Type Register is shown in Figure 2-2 on page 2-9.

2-8 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 37

Programmer’s Model

31 30 29 28 25 24 23 12 11 0

0

0 0 Ctype S Dsize Isize

Figure 2-2 Cache Type Register format

Ctype The Ctype field determines the cache type. See Table 2-6.

S bit Specifies if the cache is a unified cache (S=0), or separate ICache and

DCache (S=1). If S=0, the Isize and Dsize fields both describe the unified

cache and must be identical. In the ARM926EJ-S processor, this bit is set

to a 1 to denote separate caches.

Dsize Specifies the size, line length, and associativity of the DCache, or of the

unified cache if the S bit is 0.

Isize Specifies the size, length, and associativity of the ICache, or of the

unified cache if the S bit is 0.

The Ctype field specifies if the cache supports lockdown or not, and how it is cleaned.

The encoding is shown in Table 2-6. All unused values are reserved.

Table 2-6 Ctype encoding

Value Method Cache cleaning Cache lockdown

b1110 Write-back Register 7 operations

a. See Cache Lockdown Register c9 on page 2-26 for more details on

Format C for cache lockdown.

Format C

a

The Dsize and Isize fields in the Cache Type Register have the same format. This is

shown in Figure 2-3.

11 10 9 6 5 3 2 1 0

0 0 Size Assoc M Len

Figure 2-3 Dsize and Isize field format

Size The Size field determines the cache size in conjunction with the M bit.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 2-9

Page 38

Programmer’s Model

Assoc The Assoc field determines the cache associativity in conjunction with

the M bit.

M bit The multiplier bit determines the cache size and cache associativity

values in conjunction with the Size and Assoc fields. If the cache is

present, M must be set to 0. If the cache is absent, M must be set to 1. For

the ARM926EJ-S processor, M is always set to 0.

Len The Len field determines the line length of the cache.

The size of the cache is determined by the Size field and the M bit. The M bit is 0 for

the DCache and ICache. The Size field is bits [21:18] for the DCache and bits [9:6] for

the ICache. The minimum size of each cache is 4KB, and the maximum size is 128KB.

Table 2-7 shows the cache size encoding.

Table 2-7 Cache size encoding (M=0)

Size field Cache size

b0011 4KB

b0100 8KB

b0101 16KB

b0110 32KB

b0111 64KB

b1000 128KB

The associativity of the cache is determined by the Assoc field and the M bit. The M bit

is 0 for the DCache and ICache. The Assoc field is bits [17:15] for the DCache and bits

[5:3] for the ICache. Table 2-8 shows the cache associativity encoding.

Table 2-8 Cache associativity encoding (M=0)

Assoc field Associativity

b010 4-way

Other values Reserved

2-10 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 39

Programmer’s Model

The line length of the cache is determined by the Len field. The Len field is bits [13:12]

for the DCache and bits [1:0] for the ICache. Table 2-9 shows the line length encoding.

Table 2-9 Line length encoding

Len field Cache line length

b10 8 words (32 bytes)

Other values Reserved

The cache type register values for an ARM926EJ-S processor with the following

configuration are shown in Table 2-10:

• separate instruction and data caches

• DCache size = 8KB, ICache size = 16KB

• associativity = 4-way

• line length = eight words

• caches use write-back, register 7 for cache cleaning, and Format C for cache

lockdown.

See Cache Lockdown Register c9 on page 2-26 for more details on Format C for cache

lockdown.

Table 2-10 Example Cache Type Register format

Function Register bits Value

Reserved [31:29] b000

Ctype [28:25] b1110

S [24] b1 = Harvard cache

Dsize Reserved [23:22] b00

Size [21:18] b0100 = 8KB

Assoc [17:15] b010 = 4-way

M[14] b0

Len [13:12] b10 = 8 words per line (32 bytes)

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 2-11

Page 40

Programmer’s Model

Table 2-10 Example Cache Type Register format (continued)

Function Register bits Value

Isize Reserved [11:10] b00

Size [9:6] b0101 = 16KB

Assoc [5:3] b010 = 4-way

M[2] b0

Len [1:0] b10 = 8 words per line (32 bytes)

TCM Status Register c0

This is a read-only register that enables operating systems to establish if TCM memories

are present. See also TCM Region Register c9 on page 2-29.

You can access the TCM Status Register by reading CP15 register c0 with the Opcode_2

field set to 2. For example:

MRC p15,0,<Rd>,c0,c0,2 ;returns TCM details

The format of the TCM Status Register is shown in Figure 2-4.

31 17 16 15 1 0

SBZ/UNP

DTCM

present

Figure 2-4 TCM Status Register format

SBZ/UNP

ITCM

present

2.3.2 Control Register c1

Register c1 is the Control Register for the ARM926EJ-S processor. This register

specifies the configuration used to enable and disable the caches and MMU. It is

recommended that you access this register using a read-modify-write sequence.

For both reading and writing, the CRm and Opcode_2 fields Should Be Zero. To read

and write this register, use the instructions:

MRC p15, 0, <Rd>, c1, c0, 0 ; read control register

2-12 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 41

Programmer’s Model

MCR p15, 0, <Rd>, c1, c0, 0 ; write control register

All defined control bits are set to zero on reset except the V bit and the B bit. The V bit

is set to zero at reset if the VINITHI signal is LOW, or one if the VINITHI signal is

HIGH. The B bit is set to zero at reset if the BIGENDINIT signal is LOW, or one if the

BIGENDINIT signal is HIGH.

Figure 2-5 shows the format of the Control Register.

31 19 18 17 16 15 14 13 12 11 10 9 8 7 6 3 2 1 0

S

S

S

L4R

B

B

B

Z

O

O

V I SBZ R S B SBO C A

R

Figure 2-5 Control Register format

Table 2-11 describes the functions of the Control Register bits.

Table 2-11 Control bit functions register c1

Bit Name Function

MSBZ

[31:19] - Reserved.

When read returns an Unpredictable value.

When written Should Be Zero, or a value read from bits [31:19] on the

same processor.

Using a read-modify-write sequence when modifying this register

provides the greatest future compatibility.

[18] - Reserved, SBO. Read = 1, write = 1.

[17] - Reserved, SBZ. Read = 0, write = 0.

[16] - Reserved, SBO. Read = 1, write = 1.

[15] L4 bit Determines if the T bit is set when load instructions change the PC:

0 = loads to PC set the T bit

1 = loads to PC do not set T bit (ARMv4 behavior).

For more details see the ARM Architecture Reference Manual.

[14] RR bit Replacement strategy for ICache and DCache:

0 = Random replacement

1 = Round-robin replacement.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 2-13

Page 42

Programmer’s Model

Table 2-11 Control bit functions register c1 (continued)

Bit Name Function

[13] V bit Location of exception vectors:

0 = Normal exception vectors selected, address range =

0x0000 001C

1 = High exception vectors selected, address range =

0xFFFF 001C

.

Set to the value of VINITHI on reset.

[12] I bit ICache enable/disable:

0 = ICache disabled

1 = ICache enabled.

[11:10] - SBZ.

[9] R bit ROM protection.

This bit modifies the ROM protection system. See Domain access

control on page 3-24.

[8] S bit System protection.

This bit modifies the MMU protection system. See Domain access

control on page 3-24.

0x0000 0000

0xFFFF 0000

to

to

[7] B bit Endianness: 0 = Little-endian operation 1 = Big-endian operation. Set to

the value of BIGENDINIT on reset.

[6:3] - Reserved. SBO.

[2] C bit DCache enable/disable:

0 = Cache disabled

1 = Cache enabled.

[1] A bit Alignment fault enable/disable:

0 = Data address alignment fault checking disabled

1 = Data address alignment fault checking enabled.

[0] M bit MMU enable/disable:

0 = disabled

1 = enabled.

Effects of Control Register on caches

The bits of the Control Register that directly affect the ICache and DCache behavior are:

• the M bit

• the C bit

• the I bit

2-14 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 43

• the RR bit.

Assuming that TCM regions are disabled, the caches behave as shown in Table 2-12.

Cache MMU Behavior

Programmer’s Model

Table 2-12 Effects of Control Register on caches

ICache disabled Enabled or

disabled

ICache enabled Disabled All instruction fetches are cachable, with no protection checks. All addresses are flat

ICache enabled Enabled Instruction fetches are cachable or noncachable, and protection checks are performed.

DCache disabled Enabled or

disabled

DCache enabled Disabled All data accesses are noncachable nonbufferable. All addresses are flat mapped. That

DCache enabled Enabled All data accesses are cachable or noncachable, and protection checks are performed.

All instruction fetches are from external memory (AHB).

mapped. That is VA = MVA = PA.

All addresses are remapped from VA to PA, depending on the MMU page table entry.

That is, VA translated to MVA, MVA remapped to PA.

All data accesses are to external memory (AHB).

is VA = MVA = PA.

All addresses are remapped from VA to PA, depending on the MMU page table entry.

That is, VA translated to MVA, MVA remapped to PA.

If either the DCache or the ICache is disabled, then the contents of that cache are not

accessed. If the cache is subsequently re-enabled, the contents will not have changed.

To guarantee that memory coherency is maintained, the DCache must be cleaned of

dirty data before it is disabled.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 2-15

Page 44

Programmer’s Model

Effects of the Control Register on TCM interface

The M bit of the Control Register, when combined with the En bit in the respective TCM

region register c9, directly affects the TCM interface behavior, as shown in Table 2-13.

TCM MMU Cache Behavior

Table 2-13 Effects of Control Register on TCM interface

Instruction

TCM disabled

Instruction

TCM enabled

Instruction

TCM enabled

Instruction

TCM enabled

Data TCM

disabled

Data TCM

enabled

Data TCM

enabled

Disabled ICache

disabled

Disabled ICache

disabled

Disabled ICache

enabled

Enabled ICache

enabled

Disabled DCache

disabled

Disabled DCache

disabled

Disabled DCache

enabled

All instruction fetches are from the external memory (AHB).

All instruction fetches are from the TCM interface, or from external memory

(AHB), depending on the setting of the base address in the instruction TCM

region register. No protection checks are made. All addresses are flat mapped.

That is, VA = MVA= PA.

All instruction fetches are from the TCM interface, or from the ICache,

depending on the setting of the base address in the Instruction TCM region

register. No protection checks are made. All addresses are flat mapped. That is,

VA = M VA = PA .

All instruction fetches are from the TCM interface, or from the ICache/AHB

interface, depending on the setting of the base address in the Instruction TCM

region register. Protection checks are made. All addresses are remapped from

VA to PA, depending on the page entry. That is, the VA is translated to an MVA,

and the MVA is remapped to a PA.

All data accesses are to external memory (AHB).

All data accesses are to the TCM interface, or to the external memory, depending

on the setting of the base address in the data TCM region register. No protection

checks are made. All addresses are flat mapped. That is, VA = MVA= PA.

All data accesses are to the TCM interface or to external memory, depending on

the setting of the base address in the data TCM region register. All addresses are

flat mapped. That is, VA =MVA = PA.

Data TCM

enabled

2-16 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Enabled DCache

enabled

All data accesses are either from the TCM interface, or from the DCache/AHB

interface, depending on the setting of the base address in the data TCM region

register. Protection checks are made. All addresses are remapped from VA to PA,

depending on the page entry. That is the VA is translated to an MVA, and the

MVA is remapped to a PA.

Page 45

Note

Read accesses on the TCM interface are not prevented when an ARM9EJ-S core

memory access is aborted. All reads on the TCM interface must be treated as

speculative. ARM92EJ-S processor write accesses that are aborted do not take place on

the TCM interface.

2.3.3 Translation Table Base Register c2

Register c2 is the Translation Table Base Register (TTBR), for the base address of the

first-level translation table.

Reading from c2 returns the pointer to the currently active first-level translation table in

bits [31:14] and an Unpredictable value in bits [13:0].

Writing to register c2 updates the pointer to the first-level translation table from the

value in bits [31:14] of the written value. Bits [13:0] Should Be Zero.

You can use the following instructions to access the TTBR:

MRC p15, 0, <Rd>, c2, c0, 0; read TTBR

MCR p15, 0, <Rd>, c2, c0, 0; write TTBR

Programmer’s Model

The CRm and Opcode_2 fields Should Be Zero when writing to c2.

Figure 2-6 shows the format of the Translation Table Base Register.

31 14 13 0

Translation table base

UNP/SBZ

Figure 2-6 TTBR format

2.3.4 Domain Access Control Register c3

Register c3 is the Domain Access Control Register consisting of 16 two-bit fields as

shown in Figure 2-7 on page 2-18.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 2-17

Page 46

Programmer’s Model

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

D15

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Figure 2-7 Register c3 format

Each two-bit field defines the access permissions for one of the 16 domains (D15-D0)

(see Table 2-14).

Reading from c3 returns the value of the Domain Access Control Register.

Writing to c3 writes the value of the Domain Access Control Register.

Table 2-14 Domain access control defines

Value Meaning Description

00 No access Any access generates a domain fault.

01 Client Accesses are checked against the access permission bits in

the section or page descriptor.

10 Reserved Reserved. Currently behaves like the no access mode.

11 Manager Accesses are not checked against the access permission

bits so a permission fault cannot be generated.

You can use the following instructions to access the Domain Access Control Register:

MRC p15, 0, <Rd>, c3, c0, 0 ; read domain access permissions

MCR p15, 0, <Rd>, c3, c0, 0 ; write domain access permissions

2.3.5 Register c4

Accessing (reading or writing) this register causes Unpredictable behavior.

2.3.6 Fault Status Registers c5

Register c5 accesses the Fault Status Registers (FSRs). The FSRs contain the source of

the last instruction or data fault. The instruction-side FSR is intended for debug

purposes only. The FSR is updated for alignment faults, and external aborts that occur

while the MMU is disabled.

2-18 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 47

Programmer’s Model

The FSR accessed is determined by the value of the Opcode_2 field:

Opcode_2 = 0 Data Fault Status Register (DFSR).

Opcode_2 = 1 Instruction Fault Status Register (IFSR).

The fault type encoding is listed in Table 3-9 on page 3-22.

You can access the FSRs using the following instructions:

MRC p15, 0, <Rd>, c5, c0, 0 ;read DFSR

MCR p15, 0, <Rd>, c5, c0, 0 ;write DFSR

MRC p15, 0, <Rd>, c5, c0, 1 ;read IFSR

MCR p15, 0, <Rd>, c5, c0, 1 ;write IFSR

The format of the Fault Status Register is shown in Figure 2-8.

31 9 8 7 4 3 0

UNP/SBZ

Table 2-15 shows the bit field descriptions for the FSR.

Table 2-15 FSR bit field descriptions

Bits Description

[31:9] UNP/SBZP.

[8] Always reads as zero. Writes ignored.

[7:4] Specifies which of the 16 domains (D15-D0) was being

accessed when a data fault occurred.

[3:0] Type of fault generated (see Table 2-16 on page 2-20).

0 Domain Status

Figure 2-8 FSR format

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 2-19

Page 48

Programmer’s Model

Table 2-16 shows the encodings used for the status field in the FSR, and if the Domain

field contains valid information. See Fault address and fault status registers on

page 3-21 for details of MMU aborts.

Table 2-16 FSR status field encoding

Priority Source Size Status Domain

Highest Alignment - b00x1 Invalid

Lowest External abort Section or page b10x0 Invalid

2.3.7 Fault Address Register c6

Register c6 accesses the Fault Address Register (FAR). The FAR contains the Modified

Virtual Address of the access being attempted when a Data Abort occurred. The FAR is

only updated for Data Aborts, not for Prefetch Aborts. The FAR is updated for

alignment faults, and external aborts that occur while the MMU is disabled.

You can use the following instructions to access the FAR:

MRC p15, 0, <Rd>, c6, c0, 0 ; read FAR

MCR p15, 0, <Rd>, c6, c0, 0 ; write FAR

Writing c6 sets the FAR to the value of the data written. This is useful for a debugger to

restore the value of the FAR to a previous state.

External abort on translation First level

Second level

Translation Section

Page

Domain Section

Page

Permission Section

Page

b1100

b1110

b0101

b0111

b1001

b1011

b1101

b1111

Invalid

Valid

Invalid

Valid

Valid

Valid

Valid

Valid

The CRm and Opcode_2 fields Should Be Zero when reading or writing CP15 c6.

2.3.8 Cache Operations Register c7

Register c7 controls the caches and the write buffer. The function of each cache

operation is selected by the Opcode_2 and CRm fields in the MCR instruction used to

write to CP15 c7. Writing other Opcode_2 or CRm values is Unpredictable.

2-20 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

Page 49

Programmer’s Model

Reading from CP15 c7 is Unpredictable, with the exception of the two test and clean

operations (see Table 2-18 on page 2-22 and Test and clean operations on page 2-24).

You can use the following instruction to write to c7:

MCR p15, <Opcode_1>, <Rd>, <CRn>, <CRm>, <Opcode_2>

The cache functions, and a description of each function, provided by this register are

listed in Table 2-17.

Table 2-17 Function descriptions register c7

Function Description

Invalidate cache Invalidates all cache data, including any dirty data.

Invalidate single entry using

either index or modified virtual

address

Clean single data entry using

either index or modified virtual

address

Clean and invalidate single

data entry using either index or

modified virtual address

Test and clean DCache Tests a number of cache lines, and cleans one of them if any

Test, clean, and invalidate

DCache

Invalidates a single cache line, discarding any dirty data.

Writes the specified DCache line to main memory if the

line is marked valid and dirty. The line is marked as not

dirty. The valid bit is unchanged.

Writes the specified DCache line to main memory if the

line is marked valid and dirty. The line is marked not valid.

are dirty. Returns the overall dirty state of the cache in bit

30. See Test and clean operations on page 2-24.

As for test and clean, except that when the entire cache has

been tested and cleaned, it is invalidated. See Test and clean

operations on page 2-24.

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 2-21

Page 50

Programmer’s Model

Table 2-17 Function descriptions register c7 (continued)

Function Description

Prefetch ICache line Performs an ICache lookup of the specified modified

virtual address. If the cache misses, and the region is

cachable, a linefill is performed.

Drain write buffer This instruction acts as an explicit memory barrier. It drains

the contents of the write buffers of all memory stores

occurring in program order before this instruction is

completed. No instructions occurring in program order

after this instruction are executed until it completes. This

can be used when timing of specific stores to the level two

memory system has to be controlled (for example, when a

store to an interrupt acknowledge location has to complete

before interrupts are enabled).

Wait for interrupt This instruction drains the contents of the write buffers,

puts the processor into a low-power state, and stops it from

executing further instructions until an interrupt (or debug

request) occurs. When an interrupt does occur, the MCR

instruction completes and the IRQ or FIQ handler is entered

as normal. The return link in R14_irq or R14_fiq contains

the address of the MCR instruction plus eight, so that the

typical instruction used for interrupt return (

PC,R14,#4

) returns to the instruction following the MCR.

SUBS

Table 2-18 lists the cache operation functions and the associated data and instruction