Arcam DV-88 Service Manual

Service Manual

DV88

DiVA DV88 DVD Player

+ Progressive Scan

Issue 2.0

ARCAM

Contents List

!

Contents list

!

Circuit description

!

Frequently asked questions issue 1

!

Software release notes 1.1 to 1.76

!

Progressive scan upgrade instructions

!

Service guide

!

Circuit diagrams

!

Component overlays

!

Circuit board parts list

!

General assembly parts list

Circuit Descriptions

L875 DSP Circuit

Summary

This board is used in the DV88 and DV27 DVD players. It

can be considered to be the central digital core of the

player, and is based around the Zoran Vaddis III DVD

decoder IC. A Siemens C161 microcontroller is used as

the system CPU and software runs on this which controls

the whole syst em. A video D AC is al so pr esent , a s well as

an ATAPI bridge device.

The board interfaces with the display board, the DVD

drive, and the AV board.

Overview

The heart of t he syst em is t he Zora n Vaddi s III IC, which

receives a data stream on its AV interface. The chip has 2

separate DSPs, one for audio and one for video. The

MPEG video/ audio decoding and Dolby digital audio

decoding are performed in these DSPs as well as other

post processing on audio and video, OSD generation,

decryption of DVD and other fu nctions.

The vaddis is controlled by the system CPU via its host

bus interface.

The system uses an ATAPI type DVD drive.

With the AV interface the Vaddis AV input comes directly

from the dri ve, a nd the d rive i s c ontroll ed fro m th e s ystem

CPU via an SSC bus (standard synchronous cont rol).

The design was modified to use the ATAPI standard by

the inclusion of the ATAPI bridge chip. This has an

ATAPI interface to the drive, and an SSC interface to the

CPU. A data stream is provided which interfaces to the

Vaddis AV input.

On the output s ide of the system, t he digital audi o output

from the Vaddis is passed to the AV board in I2S format.

The video output from the Vaddis is in the form of a

digital 8 bit parallel bus, with 27MHz clock, containing

multiplexed chroma and luma data. H and V

synchronisation is performed by the use of embedded sync

patterns in the data. This type of bus is a standard interface

known as BT-656 . This bus connects to the video DAC, an

Analog Devices ADV7172. This does PAL/NTSC

encoding and D-A conversion, and gives out 6 channels of

analogue vid eo. These a re com posit e, S-Vid eo, and 3 li nes

that are switchable YUV/RGB. All video outputs are

passed to the AV board where they are filtered and

buffered before going to th e outside world.

Circuit Description

Refer to L875 circ u it d iag r am s

Sheet 1 - Top level

This is the top level of the schematic and shows how the

sheets link together plus some of the board interfaces.

CN8 provides a serial port which may be connected to a

PC via an RS232 transceiver, for debugging purposes.

CN6 is the interface to the front panel. A 4 wire serial

interface communicates with the VFD driver chip, which

drives th e display, sc ans the butt ons and drives t he LEDs

on the front panel. This interface consists of FPDIN (serial

data from panel), FPSEL (chip select), FPCLK (serial

clock) and FPDOUT (serial data to front panel).

IRIRQ is the signal from the IR remote receiver on the

front panel, driven by an open collector circuit. This is

because that line also goes to the progressive scan board in

the DV27, which has the remote bus input on it.

CN1 is the power input. +5V and +3.3V rails are provided.

The Vaddis and its SDRAM operate on 3.3V, everything

else runs on +5V.

CN5 is th e aud i o c onn ect or t o th e AV bo ard . Digi ta l au di o

in I2S and SPDIF formats are passed to the AV board from

here, as well as a number of control signals:

FSEL0..1 Selects 1 of 4 audio cl o ck fr e quencies

MD, MC, ML8716_L, ML_8716_R, ML_8716_X 5 wire

SPI bus to configure audio DACs

GAIN_SCALING HDCD gain scaling signal.

The audio master clock also comes on to the board here. It

is generated on the AV board and fed to the DSP board to

synchronise the audio, of which more la ter.

CN2 and CN3 are not fitted. Th ey are the AV and host

interface for the AV type drive that the system was

originally designed to use.

Sheet 2 - CPU

The system CP U, U3 , i s a Siemen s C1 61 16 bit ROM-les s

microcontroller ru nning at 16MHz.

ROM and RAM a re external to the mic ro, so we have a

CPU bus with 19 bit s of address and 16 bits of data.

The ROM memory is provided by U4 and U5 which

contain the lower and upper 8 bits of program memory

respectively. These are 28SF040 4Mbit (512K x 8)

FLASH EEPROMs. These must be programmed and fitted

in their sockets before the board can be tested. Once in

place they can be re-programmed in system, and the

software has a feature where new software can be

uploaded from a CD. It is important to note that these

devices are re-programmable.

The system R AM is provided by U6 and 7 which contain

the lower and upper 8 bit s of memory respectivel y. These

are 1 Mbit (128K x 8) devices, making 256KByte memory

altogether.

U12 is an 8 bit wide latch that provides a few extra control

output lines - these bei ng a 5 wire serial control interfac e

for the audio DACs, a reset sign al for the AV drive (not

used), and ‘16/9' which is used on the SCART status lin e.

U1 is a power on reset generat or, t his resets t he mic ro, a nd

the micro has an output RSTOUT which provides the

signal RESET. Thi s goes to many devices on this b oard

and the AV board and progressive sca n board.

U2 is a serial EEPROM, provi ding non-volat ile storage of

setup data. All the parameters from the setup menu are

stored here, as well as bookmarks and the region code.

The resistor packs RP1-3, are important pullup/pulldown

resistors which configure the mode of the micro on power

up.

The resistors R2 and R12-15 are provided so we may

configure the board for different devices. All must be

fitted except R1 2 an d R1 5 fo r no r m al co nf ig uration.

Sheet 3 - Vaddis DVD decoder

This sheet shows the Vaddis DVD decod er IC, U8, and i ts

associated components.

Going back to th e block diagram, various bus interfac es

were mention ed. These can be seen on the schematic as

follows:

The AV interface

This is used for carrying a udi o/ video d ata from th e ATAPI

bridge to the Va ddis. The following lines are used.

DVDDAT[0:7] 8 bit parallel data

DVDSTRB Strobe signal

DVDSOS Start of sector indicator

DVDVALID Valid data indicator

DVDREQ Request signal (Vaddis out put)

DVDERR is not actua lly used i n t he ATAPI c onfigu ration

we are using.

The HOST bus interface

The CPU uses this to control the Vaddis, it carries

information both to and from the micro.

HD[0..7] The lower 8 bits of the system data bus

HA[1..4] Lower 4 bits of system address bus

HWR- Write strobe

HRD- Read strobe

MPGCS- Chip select

MPEGIRQ-Interrupt line generated by Vaddis

Digital Video bus

The 8 bit bus YUV[0:7], with CLK27 provides the BT-656

type parallel digital video bus. The 27MHz clock is

provided on 2 different lines. CLK27 is used for the video

DAC (and also goes to the ATAPI chip). CLK27PS is used

for the progressive scan board.

Digital Audio

The audio output of the Vaddis is given out on the

following signals

SPDIF-I34 IEC 958 SPDIF output

ASDAT0 Serial data for Left and right

ASDAT1 Serial data for Lsurround,

ASDAT2 Serial data for Centre, sub

ALRCLK Wordclock

ABCLK Bit clock

Audio/Video clocks

Special note s hou ld b e mad e of th e a u di o a nd vi d eo cloc k s

in the system, there are separate asynchronous clocks used

for video and audio. The video runs on the system 27MHz

clock, which is generated by the Vaddis in conjunction

with the crystal Y2.

The audio clock is generated on the AV board and this is

totally asynchronous with respect to the 27MHz clock.

This is slightly unusual, since most DVD players derive

the audio clock from the video clock vi a a phase locked

loop

The Vaddis has a PLL which generates the audio clock,

but we don’t use it because it has horrendous jitter.

Instead, we bypass the Vaddis PLL and configure

AMCLK as an input. Our clock source is on the AV board

and this is a very low jitter oscillator.

The Vaddis maintains AV sync by dropping or repeating 1

frame of video to re-synchronise the streams when they

start to get out of sync. In practice this happens very rarely

because the 2 clocks are very accurate so the difference in

frequency will be very small. It is important to note that

without the audio clock present, no audio or video material

can be played.

CD-DSP interface

(CDERR, CDFRM, CDD AT, CDCLK.)

The Vaddis chip has a CD-DSP interface designed to

connect to DVD drives wit h th i s type of i nt erface for C Ds.

These signals are tracked on the board but they are not

used. The data path for CDs is exactly the same as for

DVDs.

Reset and standby signals

The signal MPGRST- is an active low signal that the

micro uses to reset the Vaddis and ATAP I b r idge chip.

The signal MPGSTBY- is an active low signal that the

micro uses to put the Vaddis in a low power mode while

the player is in standby.

SDRAM

The Vaddis requires some memory for video and audio

decoding and processing. This is provided by a 16MBit

synchronous DRAM (512K x 16 bit x 2 banks).

The board is arranged to allow 2 SDRAMs, but at present

we only use one. U11 is fitted while U10 is not fitted. The

Vaddis interfaces directly to the SDRAM with no other

device being involved.

PSU Synchronisation

An interesting featu re of the Arca m DVD p layer i s th at th e

switch mode supply on the PSU is synchronised to the

audio sampling frequency. This is done to reduce the

switch mode n oise on th e audio ou tput. Th e PSU will free

run on its own , when tested, but when conn ected to the

DSP board it will loc k to th e audi o word cloc k. Th e signa l

ALRCLK is buffered by U14 to provide the signal

LRCK_PSU which goes to the PSU.

Sheet 4 - Video DAC

This sheet shows the video encoder/DAC and output

buffers.

U9 is an Analog Devices ADV7172, which does

PAL/NTSC encoding and has 6 DACs providing all our

video outputs.

It takes its input from the BT-656 video bus YUV[0..7],

this bus is clocked by CLK27 (27MHz). No H/V sync

signals are r equired since th e H and V synchronisati on is

done with embe dded sync patterns in the data.

The chip h as its operating paramet er s loaded by the system

CPU via the I2C bus.

There are 6 analogue outputs from U9. These are

composite PAL/NTSC, S-Video, and 3 lines that are

configurable (via setup menu) to be YUV or RGB. The

DACs have current outputs, so R16-21 have been chosen

to give the required output level voltage, in conjunction

with R22/24 and R23/25 which program the DAC current

outputs.

All channels are buffered by op-amps U13,16,17. These

have a gain of +2, and drive out to the AV board through a

source impedance of 75R. The AV board has filtering and

another buffer stage.

There are 2 control signals that also go to the AV board

video section.

ENABLE_AV Used for SCART status signal. High

when player is not in standby

16/9 Used for SCART status signal. High wh en 16:9

TV type has been selected in setup menu.

Digital Video output

Connector CN4 provides a digital video output. This is

used in the DV27 only, for connection to the progressive

scan board.

YUV[0..7] are present on this connector along with clock

CLK27PS.

The system res et signal RES ET- is provided, and the I2C

bus for control of devic es on the progressive scan board.

The signal IRIRQ i s con n ec ted to p ick up th e outp ut of t h e

remote bus circuit which is on the progressive scan board.

This is an open collector signal which can be driven from

either the front panel or th e r emote bus inpu t.

Sheet 5 - ATAPI Bridge and interface

U18 is a Zoran ZR36701 ATAP I to AV port bridge.

It interfaces with the system CPU via the SSC bus, made

up of the following signals:

SSC_SCLK Clock (input to ZR36701)

SSC_MTSR Data input (CPU to ZR36701)

SSC_MRST Data output (ZR36701 to CPU)

SSC_ATN- Port ready signal (output from

ZR36701)

DRV_IRQ- Interrupt request generated by

ZR36701

The chip also receives MPGRST- to reset it from th e C PU.

The system video clock CLK27 is connected to generate

timing signals.

The chip has an interface with the Vaddis referred to as the

AV interface. See the section on the Vaddis for a

description.

The ZR36701 acts as a bridge between the SSC and AV

interfaces on on e side, and th e ATAPI drive on t he other.

The ATAPI interface of the chip connects to the DVD

drive via 40 way IDC connector CN10.

Signal descrip tions:

ATCRESET-Active low reset generated by ZR36701 to

DD[0..15] Bidirectional data bus

DA[0..2] Address lines - output from ZR36701

CS0-,CS1- Chip selects - output from ZR36701 –

make up part of ATAPI address

INTRQ Interrupt request from drive to ZR36701

DIOW- Writ e s trobe - output from ZR367 01

DIOR- Read strobe - out put from ZR36701

IORDY Device ready signal from drive

Board Specifications

Power Supply:

+5V +/- 5% at 280mA nom i nal

3.3V +/-5% at 400mA nominal.

Video output levels:

Composite: 700mV nominal (in PAL) black-peak white

into 75R

S-Video: Y 700mV nominal (in PAL) black-peak white (in

PAL) into 75R

S-Sideo: C 885mV pk-pk n ominal (in PAL) into 75R

Component Y: 700mV nominal (in PAL) black to peak

white into 75R.

Component U: 700mV pk-pk nominal for 100% colour

bars, into 75R.

Component V: 700mV pk-pk nominal for 100% colour

bars, into 75R.

L877 Circuit

The PSU consists of 4 function blocks.

These are :

1. Mains to DC block

2. -19V5 supply.

3. PSU Sync Cicuit.

4. Switch Mode PSU .

The Mains to DC Block.

The mains to DC Block provides an unregulated Isolated

DC Voltage from the mains supply.

The Mains Transformer TX1 (which is now toroida l - for

reduced induced hum) has dual 115V primaries which are

connected in series for 230V op eration and in par allel for

115 V operation by the rear panel operated slide switch

SW2. F1 and F2 provide fusing for each primary winding

and the switch ing is arranged to obviate the req uirement

for different fuses for 115V and 230V operation. For a

given output power the current requirements for 115V

operation are twice that for 230V operation. This

requirements is met by having the fuses in parallel for

115V operation and having only F2 in circuit for 230V

operation.

The VDRs (Voltage Dependent Resistors) VDR1 and

VDR2 ensur e that the fuses will b low in the even t of the

ATAPI drive

rear panel switch being set for 115V and 230V being

applied. It is likely that the VDRs will fail short in such

circumstances and will then also require replacement.

C1 and C2 are Y capacitors which form an EMC

suppression network to common mode signals with

common mode choke L1. Connector SK6 provides

connection f or the analogue windings to t he AV PCB. SK7

optionally allows a further transformer to be added to

provide the analogue supply in a more expensive model. In

such a model SK6 will then not be used and the additional

transformer secondary will be plugged directly into the

AV PCB.

The mains transformer TX1 is specified to provide 25V

DC at 195V Input and maximum load across C3 and give

+/- 14.5V DC with 200mA on each rail when rectified on

The AV PCB.

The main DC supply (-38V_UR) is formed by DBR1 and

C3. L2 and C4 provi de EMC suppression to prevent the

current pulses drawn by the switching supply from

generating EMC interference via the mains lead

(Conducted emissions) .

Note that the m ain DC supply -3 8V is a negat ive supply.

This allows the -19V5 supply for the display to be

generated from it and allows the switching PSU to have a

beneficial topology.

The mains transformer is designed to blow input fuses F1

and F2 in th e event of a s hort across t he main output and

the analogue supply to the AV_PCB is fused on the

AV_PCB.

The -19V5 supply

This is simply formed by and emitter follower TR1 and

zener diode DZ1. R1 provides a couple of milliamps

through DZ1. DZ1 then forms a 20V reference voltage

which biases TR1 base thereby fixing TR1 emitter 0.6V

above it to provide around -19.4V . C8 provides some noise

filtering.

PSU Sync Circuit.

The PSU is required to be synchronised to a 32KHz,

44KHz, 48KHz and 96KHz clocks.

The sync cct provides a divide by 2cct for the 96KHz

signal. The supply is then fed with a 32KHz, 44KHz and

48KHz clock.

The sync cct is formed around the non-retriggerable

monostable IC1. IC1A is set to have a time constant of

which slight ly exceeds the period of the fastest allo wable

clock (48KHz)

and thus if a slower clock is applied the output appearing

on Q is simply the inpu t pulse train. A faster pulse t rain

has every other leading edge inhibited since the nonretrigger time exceeds the period. Thus the divide by two

occurs. The second non-retriggerable produces a pulse of

near fixed duration. The width of the pulse was set to

move the falling edge of the sync pulse away from the

falling edge of the gate drive signal in the Switching PSU.

In this way the n oise glitches associat ed with the falling

edge of the sync pulse do not cause mis triggering of the

PWM in the switching PSU. The Q output (pin 5) of IC1 is

a square wave signal. This is coupled and level shifted by

differentiating network C12 and R4 to the -38V rail. The

time constant C12, R4 is chosen so that only the rising and

falling edges of the output of IC1 appears across R4 as

positive and negative going spikes. The positive going

spike is add ed to the oscillato r r amp by D3.

Switch Mode PSU.

The PSU is formed around IC2 and TX2. The topology is

uncommon but it is basically a flyback supply with the

added complication that the primary of the transformer is

made to provide the +12V supply during the off time of

the mosfet. In this way the efficiency of the supply is

extremely high since all of the energy stored in the

transformer leakage inductance which is normally clamped

and dissipat ed is dumped into the 12V su pply and u sed to

power the DVD. Hence the stran ge arrangement of the 38V rail et c.

Control chip IC2 provides gate drive to M1. This power

mosfet connects the primary of TX1 across the -38V

supply. Note that the primary is shown on the circuit

diagram as two windings connected in series. The series

arrangemen t is to minimis e leakage indu ctance and to do

this one of the wind ings i s wound on the TX firs t, then the

secondaries are wound on and then the other primary is

then wound on last. This arrangement of windings where

the secondaries are sandwiched between two half

primaries significantly reduces the undesirable leakage

inductance.

The primary can thus be considered to be a single winding

which starts on pin 6 and ends on pin 3.

When this winding is applied across the supply the current

ramps up at a rate given by Vpri/Lpri amps per second.

Because of the p olarity of the tra nsformer wind ings all of

the secondary side diodes D5, D6, D7 and the +12V diode

D4 will be reverse biased. At some point the control cct

will decide to turn off the mosfet. When an inductor (in

this case the primary of TX1) has been charged up. (I.e.

the current ha s ramped up to some value or other and the

flux density has increased) then when the flow of current

is interrup ted by the m osfet t he volt age ac ross t he win di ng

reverses so as to allow the flux to return to decay.

When the volta ge across the p rimary win ding reverses the

diodes to th e ou tp ut s a re a ll for war d b i a sed and th e c u rren t

which was stored in the primary ramps down into the

output capacitors through the coupled secondary windings.

At this point the drain of the power mosfet M1 which had

previously been near -38V will fly back above the DGND

0V net. The t ransformer is desi gned so that when the 5V

and 3V3 outputs are at their nominal voltage then the

mosfet drain and primary will fly around 13V above

DGND and so produc e around 12V aft er the for ward drop

of D4 across C21. At th e end of the switching cycle thi s

behaviour is repeated.

The apparently complicated arrangements of the

secondaries f or the +3 V3 and +5V w indings is due to the

fact that the +3 V3 output is derived from a tap on the 5V

winding. The 3V3 winding thus has both of the +5V and

+3vV3 output current flowing in it. For this reason it needs

to be rated for a much higher curren t. The +3V3 winding

part is thus composed of two windin g in parallel a s shown

in the schematic symbol. The winding which produces the

4V3 output is a floating winding. Whereas the +3V3, +5V

and +12V are all develop with respect to DGND.

The switching frequency is dictated by an RC network R9,

C14, R10. These components combine with an internal

oscillator circuit which function as follows. The voltage

reference VREF produces a steady 5V reference. C14

charges through R9 (neglecting the presence of R10

temporarily). When the voltage on the RC pin (pin4)

exceeds a threshold then a mosfet internal to IC2 shorts

C14 and the cycle is repeated. In this way a ramp

waveform appears on the RC pin at the switching

frequency of t he PSU. When the Volt age on C10 exc eeds

the RC threshold the cap is discharged and the cycle

begins and th e PSU switching mosfet is turned ON. The

function of R10 is to allow an externally applied spike to

be superimposed on the RC pin voltage. The external spike

is generated by the sync cct. By adding a spike of a few

hundred milli volt a mp li tud e t o th e RC ra mp th e c ircu it c an

be forced to b egin a new c ycle at th e instant of the spike

since this pu shes the RC ramp voltage ab ove the requi red

threshold.

If the spike i s added at a fixed fr equency the P SU will be

effectively synchronised to this externally applied clock as required.

The oscillator is set to free run at a frequency below the

minimum sync frequency. In this sys tem the free running

frequency is set to around 25KHz. The minimum sync

frequency being 32KHz and maximum frequency is

48KHz. Component tolerances will give a sp read of free

running frequency but the upper limit with all tolerances

stacked worst case will be less than 32KHz.

As described the RC ramp switches the power mosfet ON

at the beginning of each switch cycle. The mechanism

which switches it OFF again near the middle of the cycle and thus sets the switching mosfet pulse width will now be

described.

The about volt age is controlled by varying the pulse wi dth.

In this design both the +3V3 and +5V supplies are

monitored. This is because in a multiple output switch

mode supply only the controlled output is accurately

maintained at the correct voltage (with a tolerance of

around 1%). The u nc ont rolled ou tpu t s may va r y b y arou nd

+8% max over full line and load variation.

In this design both the +3V3 and +5V outputs are required

to have good regula tion (<5%) so th e feedb ack is arran ged

so that rath er than having s ay +5V at 1 % and +3V3 at s ay

8% we actually end up with +3V3 and +5V at around 3%

tolerance. In fact the control loops is actually monitoring

the average voltage on +3V3 and +5V a nd regulating this.

The voltage of both supplies is monitored by transistor

TR2. The collector current of which is equal to the emitter

current as set by R5, R6 (neglecting base current). The

emitter resistors are scaled so that each monitored output

contributes 50% of the emitter current to TR2.

In IC2 an internal error amplifier has its positive input tied

to a 2V5 reference. The negative input of this error

amplifier is connected across series network R7, R22

which monitors the collector current of TR2. The error

amplifier ch anges th e pulse widt h of th e PSU by swingi ng

its output. In the general style of feedback systems the

error amplifier swings its output to make the voltage

difference b et ween i t s i np ut s = zero. I. e. t h e volt a ge on t h e

VFB (pin 2) of IC2 is maintained at 2.5V which in turn

sets the current through R22+R7 which in turn sets the

output voltages on +3V3 and +5V.

Internal to IC2 th e output of the volta ge error amplifi er is

actually compared with the output of another amplifier

which looks across primary current sense resistor R14. The

voltage across R14 is filtered by network R13, C18 to

remove the narrow leading edge spike caused by the

leakage inductance of TX2. When the voltage at the output

of the current s ense amplifier exceeds the volt age at the

output of the volta ge error a mp li fi er then th e power mos fet

is switched off. This will be around 1/3 duty cycle for an

input voltage of 36V on C4.

This mode of operation is called current mode control and

has a number of ad vantages over th e more obviou s PWM

method of comparing the output of the voltage error

amplifier with a ramp waveform and switching the mosfet

off when the r amp volta ge exceed s the volt age on t he E/ A

output - i.e. a conventional PWM approach. The current

feedback method has instantaneous response to input

voltage variation since lower input voltage will

automatically force the ramp waveform on R14 (from Vin

across Lpri of TX2) to be more shallow which will

instant ly f orce a longer mosfet On-time. By contrast the

conventional PWM method would require an error in the

output voltage t o occur before the m osfet ON-time cou ld

be increased.

In addition we get pulse by pulse current limiting for free

since the c hip cont ai n s a s i mple c c t wh ich tu rn s th e mo sfet

off if the current sense input voltage exceeds 1V

irrespective of what the error a mplifier is doing. Thus a

short circuit on the output of the supply will cause the

supply to power limi t and the ou tput voltages o f all of the

supplies to fall which should pr event catastrophic failure.

The mosfet is d riven from the output of th e IC through a

22R resistor. This resistor value is chosen to be

compromise between small value for rapid turn ON and

turn -OFF of M1 and high value for soft turn ON a nd low

EMC.

IC2 is powered through the network R11, DZ2, C16, C17.

This network provides a 10V supply for the controller with

values calcu lated to m aintain regulation at mini mum input

line voltage (=195Vac when set to 230Vac). The IC draws

approximately 20mA in normal operation.

Network R8, C15 are feedback loop compensation

components. The connection is actually between the

internal E/A output node and the negative input of the E/A.

C13 provides decoupling for the voltage reference.

The thee main outputs (+3V3, +5V, +12V) have small

value induct ors i nsert ed in seri es wit h th e outp uts (L3, L4,

L5). These provide excellent attenuation of switching

voltage spikes (in combination with the following

capacitor s) in an a tt empt t o k eep s the n o is e on th e su pp li es

as low as possible. Similarly the series networks R15, C19

= 1K +1nF; R17, C25; R18, C30; R19, C36 are snubbing

networks which are also used to limit switching noise

spikes.

The 4V3 output is semi-regulated by the simple emitter

follower / zener network TR3, DZ3.

This arrangemen t reduces the output voltage va riation to

well within the required range. Fuse F5 is for current

limiting b ecause the wire on the 4V3 su pply is only ra ted

for low currents and a short cct on this output would cause

high current to flow in the winding which would otherwise

overheat the transformer.

Output Voltage Specification

The specification for the PSU over fu ll range of input

voltages / load currents.

Supply tolerance Min V Nom V Max V

% V V V

3V3 5 3.135 3.3 3.465

5V 5 4.75 5 5.25

12V 10 10.8 12 13.2

4V3 5 4.085 4.3 4.515

19V5 5 18.525 19.5 20.475

Voltage across C3

Nominal Tol min nom max

V % V V V

V (C3) 27.5 5 26.13 27.50 28.88

Free running frequency

Nominal Tol Min Nom Max

%

KHz KHz KHz KHz

Frequency 27 10 24.30 27.00 29.70

L878 AV Circuit

Summary

This board is used in the DV27 and DV88 DVD players. It

takes the outputs of the DSP board and produces all the

video and audio outputs of the system (the exception being

the progressive s can output on the DV27 , which is on a

separate card).

The board features 2 mono DACs for stereo analogue

audio, an audio clock oscillator, data re-clocking, and

video buffers. There is also a p ower supply circuit for the

audio section and separate regulat o rs for sensitive cloc k

supplies.

A key feature of the design is that it is ‘DVD-Audio

ready’. The DACs and audio clock are capable of

supporting various sample rates up to 192kHz, and there

are expansion connectors present to allow an additional

audio DAC board to be fitted. This will handle the extra 4

channels of surround audio (This is a requirement for

DVD-Audio since no digital interface is allowed to

connect to ext er nal processo r s).

The DV27 and DV88 DVD-Video players ca n therefore b e

migrated in th e fu tu re to s upp ort DVD-Aud i o. Th is will b e

done by replacing the existing DSP board for one that

supports DVD-audio, and adding a 2

Overview

The audio power supply circuit ta kes an AC feed from the

main PSU and provides DC power rails for the DACs and

output buffer stage.

The clock circuit provides a selectable clock frequency

that can be 4 different frequencies. There is a clock

distribution circuit in here that feeds clocks to the DACs,

to the re-clocking circuit, the DSP board (for

synchronisation), and to an additional DAC board (not

fitted at present).

The re-clocking circuit accepts an I2S format audio signals

from the DSP board and an SPDIF signal. These are relatched to th e local clock to reduce ji tter. The re-clocked

I2S is passed on to the DACs, and the re-clocked SPDIF

goes on to the coaxial output buffer and optical output.

The DAC circuit provid es a stereo analogue audio out put

on phonos, this is also connected to the SCART AV

output. The DACs are operated under software control,

this is by an SPI bus from the DSP board.

On the video side, 6 channels of analogue video are

received from the DSP board. These are filtered and

buffered before going to the outside world. The video

signals consist of composite, S-video and 3 lines that are

switchable YUV/RGB. These 3 lines go to phono

connectors (for YUV) and the SCART (for RGB). The

player setup menu has to be set appropriately for one or

the other.

The SCART output also has some status signals to control

TVs, these are generated from control lin es from the DSP

board.

nd

DAC board.

Circuit Description

Refer to L878 circ u it d iag r am s

Sheet 1 - Top level

This sheet is the top level of the schematic showing how

the other sheets fit together, an d some of the interfac es on

the board.

SK1 is the audio interface with the DS P board.

Signal descrip tions:

CK256FS_DSP Audio master clock to DSP board

XMUTE Mute signal from DSP board

ADIN I2S audio data for L, R

AD2IN I2S aud io data for LS, RS (used on

AD3IN I2S audio data for C , SUB (used on

nd

2

DAC board)

nd

DAC board)

2

BCK_IN I2S a udio bit clock

LRCK_IN I2S audio word clock

SPDIF_IN SPDIF audio from DSP board

FSEL1..0 Control lines to select 1 of 4

frequencies of audio master clock

NRESET Power on reset signal from DSP

board, active low.

MD SPI data to configure audio DACs

MC SPI clock to configure audio DACs

ML_8716_L SPI load signal to configure left

DAC

ML_8716_R SPI load signal to configure right

DAC

ML_8716_X SPI load signal to configure

surround DACs (on 2

nd

DAC board)

GAIN HDCD gain scaling signa l, high for

HDCD x2 gain

SK3 connects to the 2

nd

The 2

DAC board can then pick up the signals it needs.

SK11 is also an expansion connector for this 2

nd

DAC board when this is fitted.

nd

DAC

board. This connector is for some of the power supplies it

will need.

Sheet 2 - Analogue power

This sheet shows the analogue audio power supply, and

also the regulators that are used for sensitive digital

supplies and the muting circuit.

AC power comes in on SK4. In the DV88 player this

comes from a winding on the transformer on the PSU

board. On the DV27, it will come fro m a separa te t orroida l

(for surround channels of DVD-

transformer (as in the FMJ CD23).

D2,3,4 and 10, with capacitors C1, C3 form a bridge

rectifier to generate unregulated DC supplies +UR and UR. These are the regulated down to +12V and -12V by

Z1 and Z4 respectively. The resulting rails +12VA and 12VA are used by the output buffer stage.

The +12V rail is used to supply the DAC supply regulators

Z2 and Z3. These provide separate supplies for the 2 mono

DACs, +5V_DAC_L and +5V_DAC_R.

SK5 is where all the power arrives fo r digit al circui try and

video. +12V is used by the muting relay and the SCART

status circuit, and a lso feeds 2 x 5V regula tors, Z9 and Z5.

Z9 produces +5V_CLOCK1 which is used by the clock

oscillator. Z5 produces +5V_CLOCK2 which is used by

the clock divider and buffer.

+5V also comes in on SK5, this is used by other digital

circuitry, and is used to derive +5V_VID via inductor L1.

+5V_VID powers the video section.

Z6 is a Toshiba TA317P muting chip, as used in other

products. This controls the muting relay RLY2. Z6 will

mute the output in several ways. Firstly, it arranges to

mute for about 2.5 seconds after power is applied.

Secondly, it mutes immediately if the mains is

disconnected. This is initiated by the AC sense signal from

D5. Finally, it can also mute when the signal XMUTE is

taken high. This is controlled by the system CPU so the

software can mute if required.

Sheet 3 - Re-clocking

This sheet sh ows the re-clockin g latches Z7, Z8 an d Z28.

These are clocked by CK256FS_RCK, and simply re-latch

the digital si gnals from the DSP boa rd. The SPDIF signal

has been given its own latch chip rather than share with

another to avoid any interference from the SPDIF on to the

I2S lines.

The re-clock ed I2S si gnals a re split so that ea ch DAC ha s

its own set of signals.

Sheet 4 - Clocks

This sheet sh ows the audio ma ster clock ci rcuit. 2 colpits

oscillators are provided with crystal frequencies of

24.576MHz and 22.5792MHz. Only one of these is

enabled at any time, this is determined by the state of

control line FSEL0. If FSEL0 is low the 22.5792MHz

oscillator will b e on , if i t is hi gh th e 24. 576MH z osci llator

will be on.

The oscillator output may then be divided by 2 by Z10A.

Control line FSEL1 is used to select the divided or nondivided version by controlling the output enable of Z14C

and Z14D. When selecting the non-divided version, we

clear Z10A for good measure to avoid noise.

Thus, 4 different clock frequencies can be selected by

FSEL1..0

FSEL1..0 Frequency Relationship to Fs Typical use

0 11.2896 44.1K x 256 CD audio

1 12.288 48K x 256 DVD-Video,

VCD

2 22.5792 88.2 x 256

DVD-Audio

(or 176.4 x 128)

3 24.576 96K x 256

DVD-Audio

(or 192 x 128)

The resulting signal is buffered before distribution by Z21

and Z14A. There are 5 clock signals distributed:

CK256FS_RCK For re-clocking circuit

CK256FS_DAC_L For left DAC

CK256FS_DAC_R For right DAC

CK256FS_DSP For DSP board

CK256FS_EXT For 2

nd

DAC board

Audio)

Sheet 5 - Audio DACs

This sheet sh ows the audi o DACs and out put buffer s tage.

Z17 and Z18 are Wolfson WM8716 audio DACs. These

are stereo p arts that can be operated in a m o no mode. They

are configured via software so that Z17 provides the left

channel and Z18 provides the right channel.

The DACs are configured individually by having separate

load signals on the SPI bus. This is required because one

DAC has to be told to be the left DAC, and one has to be

the right. The addi tiona l DACs on the 2

nd

DAC board also

have their own load signal as they wil l be used in stereo

mode.

The DAC outputs are differential. These outputs are

filtered by t h e 2

nd

order butterworth filters wit h di fferent ia l

inputs. Z19A and its associated components filter the left

channel, and Z20A and associated components filter the

right channel .

Following the filters are amplifiers with switchable gain.

Z19B amplifies the left channel and Z20B amplifies the

right chann el. For norma l use th ese have a gain of -1 . For

HDCD they will have a ga in of -2. The gain switching is

accomplished by analogue switch Z11 which switches in

additional resistors. The signal GAIN controls the switch.

It is high for HDCD x2 gai n. The stereo analogue ou tput

goes out as 2 st ereo pairs on SK6. It also go es off to the

SCART AV out put - SCART_L, SCART_R.

Sheet 6 - Video filters and buffers

On this sheet there are 6 ch annels of filt ering and buffers

for the video signals. If we consider the signal path for

SVID_Y, C113, L3, C119, and C107 form an elliptical

filter, and R1 provides 75R termination. Z23B is an opamp with a gain of +2, C93/C31 provide AC coupling and

R104 is the 75R sou rce termination. This same circui t is

duplicated for all the other channels. The CVBS output has

2 source terminators, so that the SCART and composite

outputs can both be used simultaneously.

Sheet 7 - Video outputs and SPDIF outputs

This sheet shows all the video output connectors, the

SCART status circuit and the SPDIF output.

S-Video goes out on SK8, Composite and YUV

component go out on SK7, and the SCART output is on

SK9.

The SCART sta tus circuit is a pi ece of analogue ci rcuitry

that takes 2 control lines from the DSP board, and

generates 2 status signals for the SCART output.

ENABLE_AV is a control line from the DSP board that is

high (3V) whenever the player is not in standby.

16/9 is another control line from the DSP board. This is set

high (5V) to indicate 16:9 anamorphic material. At present

this is implemented by setting it high when 16:9 TV type

is selected in the setup menu.

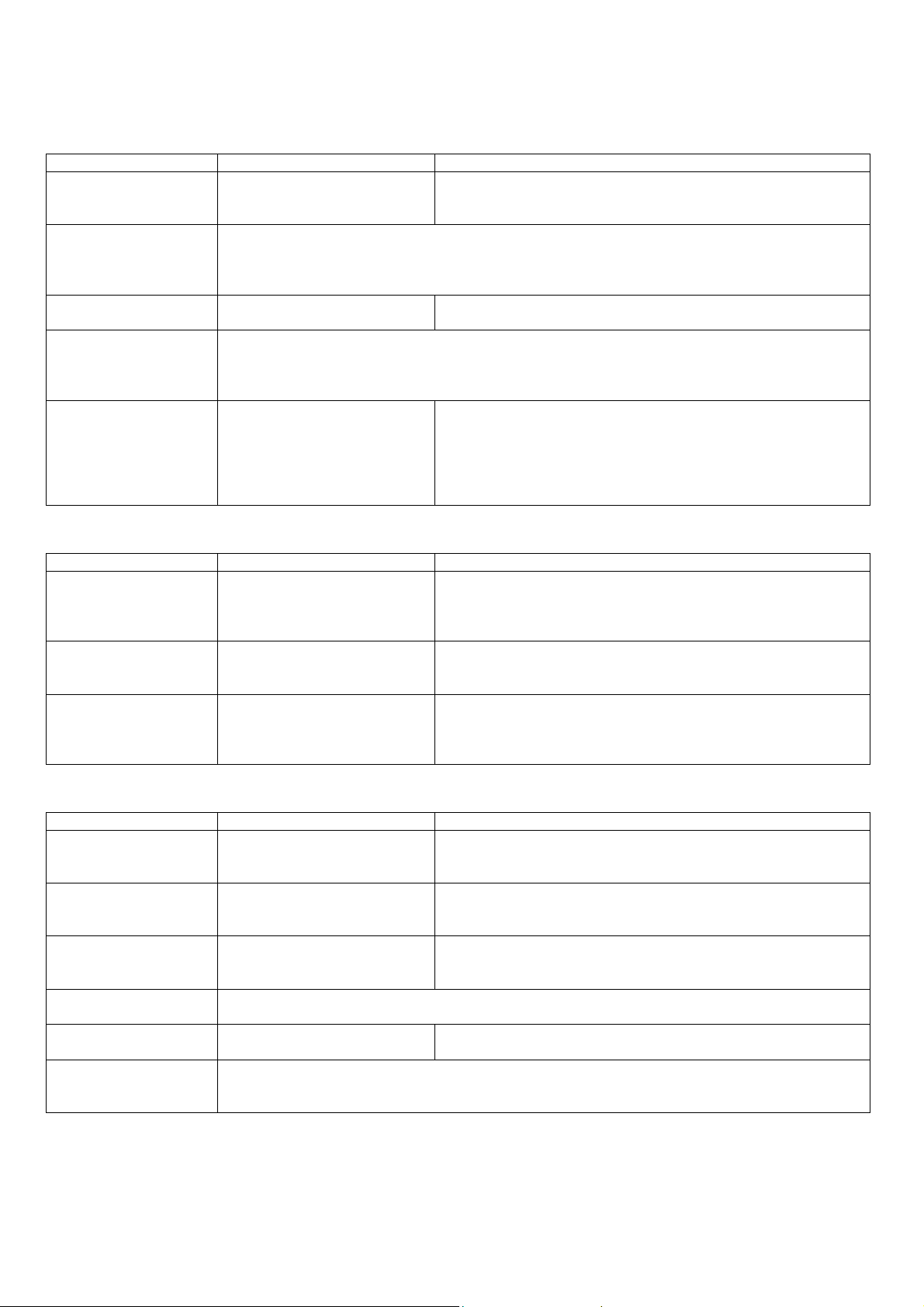

The output 0/6/12 is designed so that it is 0V when the

player is in standby, or 6V when playing 16:9 material, or

12V when playing 4:3 material.

The output AV_CTL is simply ENABLE_AV after an

emitter follower.

The spec for these outputs is as follows, typical

measuremen ts are given vs the spec:

ENABLE

_AV

0 0 0V 0-2V 0V 0-0.4V

1 0 0V

0 1 6.3V 2-9.5V 2.8V 1-3V

1 1 10.6V 9.5-

The SPDIF output is shown a t t h e b ottom of t he p a ge. Z2 6

is used to buffer the signal and 3 gates are used an parallel

in order to provi de sufficient drive. The r esistor values of

R7,8,11 and R71 ha ve been ch osen such that th e outp ut is

attenuated to the correct level, and also to provide 75R

output impedance. T1 is an isolating transformer with a

turns ratio of 1:1.

Z25 is a TOSLINK optical transmitter. This is a 6Mbit./s

part, so operation at 96kHz sampling rate is not guaranteed

(requires 12Mb/s).

Specifications

Analogue Audio

Output level: 2.2V rms for 0dB signa l +/ - 0.1 V

Frequency response 20Hz to 20kHz (+0.1, -0.5 dB)

THD+N <0.005% for 1kHz 0dB signal,

S/N >90dB at 1kHz 0dB, unweighted

Digital Audio

To IEC 958.

Amplitude: 500mV +/- 20% pk- p k in to 75R

Video

Composite: 700mV nominal (in PAL) black-peak white

into 75R

16:9 0/6/12 (spec) AV_

CTL

2.8V 1-3V

12V

measured 22Hz - 22kHz, unweighted

(spec)

S-Sideo: C 885mV pk-pk n ominal (in PAL) into 75R

Component Y: 700mV n ominal (in PAL) black to peak white

into 75R.

Component U: 700mV pk-pk nominal for 100% colour bars,

into 75R.

Component V: 700mV pk-pk nominal for 100% colour bars,

into 75R.

L886 Display Circuit

Summary

This board is used in the DV88 DVD player. It contains the

front panel VFD display, buttons, LEDs and remote IR receiver.

The board for the FMJ player (DV27) will be electrically the

same, but with a different PCB layout, since the 2 players are

mechanically d ifferent in this area.

Circuit description

Z1 is a Rohm BU2872AK VFD driver IC. It has 4 wire serial

interface with the system CPU, comprising the following

signals:

SO Data out (from Rohm chip to CPU)

SI Data in (from CPU to Rohm chip)

CS Chip select (driven by CPU)

SCK Serial clock (driven by CPU)

All the interaction with the system CPU is via this bus, with the

exception of the remote IR data, which has its own interface.

The Rohm chip drives the VFD display via SEG1..15 and G1..7.

It also has some other functions.

LEDs: The ch ip has 4 outputs to drive LEDs L1..4 . These are

used to drive the 2 front panel LEDs, HDCD and On/standby,

the latter is a bi-colour LED that is green to indicate on, red to

indicate standby. L2 and L3 are used to control the VKK

switching circuit.

Button scanning: The rohm chip also scans the front panel

buttons. The buttons form a matrix which is scanned by the

segment driver lines S3..6. The resulting matrix is read on inputs

K2,3,4 on the c hip.

Filament supply bias: The filament voltage F1/F2, is supplied as

a floating 4V3 DC supply. This is biased to the correct level by

zener diode D5, so that F1 is 5V6 above grid voltage VKK.

VKK is nominally -19.5 V, therefor F1 is normally -13V9, and

F2 is normally -9V6.

VKK switching ci rcuit: The Roh m chi p has a n unfortu nat e fault

in that it does not initiali se its display R AM on power up. This

results in random patterns being displayed momentarily on

power up. To fix this, it was necessary to include the VKK

switching circuit comprising Z2, Q5, Q6 and associated

components. D type latch Z2A is arranged so as to always

power up in a cleared state, by the inclusion of R13/C7 which

clear it on power up. The D and CLK inputs of the latch are

controlled by the L3 and L4 outputs of the Rohm chip, this

allows the s ystem softwar e to set or clear the la tch as required.

The latch outp ut c ontrols t ran si st or Q6 whi ch swi tch es th e V KK

supply voltage to the rohm chip. By inhibiting this supply until

it is required, we ensure the display always powers up blank,

and we switch it on only when we have initialised it correctly,

avoiding the random characters.

Remote IR recei ver: RX1 i s an IR recei ver module. Th e output

of this is converted to an open collector type signal by Q3/Q4.

This is required because the DV27 FMJ player will feature a

remote bus input, which will simply be wire-OR’d with this to

provide remote control from th e remote bus.

S-Video: Y 700mV nominal (in PAL) black-peak white (in

PAL) into 75R

F

SH8827FAQ, Issue 1

23425

requently Asked Questions

about your ARCAM DVD player…

Introduction

The ARCAM customer services team is avail able to help you should you experience problems with your DVD player. There are a

number of questions, however, that are asked very frequentl y. To save you the bother of having to call us or your dealer in these

instances, we have compiled this list to help you out.

Please note that this list is in addition to the “Troubleshooting” guide be found in the back of the handbook.

Obtaining the player software version and region numbers

Before contacting ARCAM customer services with a question, it is useful to have t he software version and player region numbers

available. This information is displa yed in the top-left corner of the screen when the player is first switched on (or brought out of

stand-by). The informa tion is shown for approximately two seconds; the top number is the software version, the lower number is the

ARCAM shipping region that the player is set to (not to be confused with DVD region).

Problems with remote controls

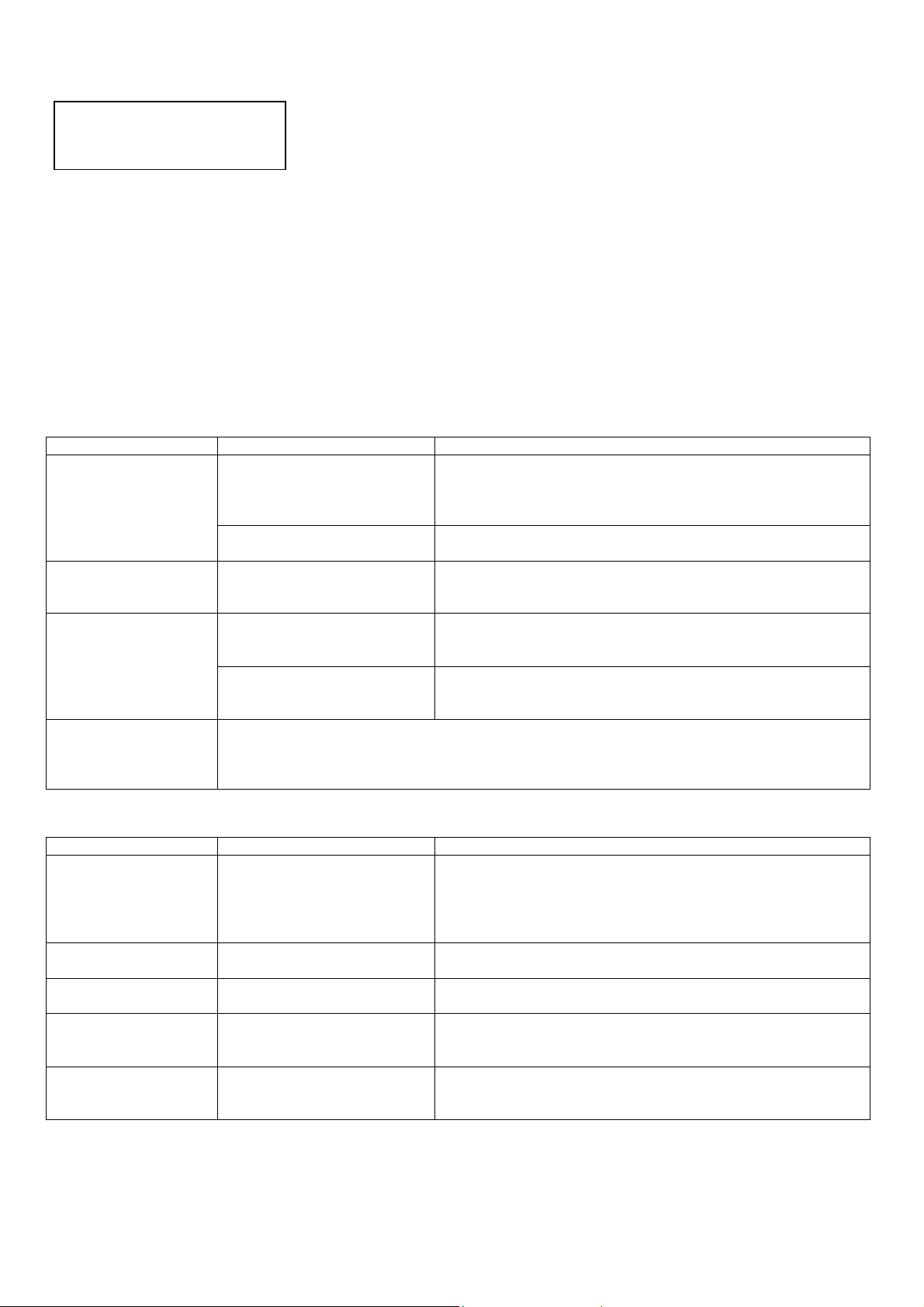

Problem Possible cause Solution

The supplied remote

control is not working.

The player does not

respond to an ARCAM

learning remote control.

The player does not

respond to a nonARCAM learning remote

control.

I need discrete on/off

codes (or a complete

code list) for use with my

learning remote.

The remote control is configured

to control a CD player, not the

DV88/27.

The batteries are not installed

correctly, or are flat.

The remote control has not been

programmed correctly.

The remote control has not been

programmed to control your

ARCAM DVD player.

The remote control does not

support “RC5” commands

correctly.

The system code for the DVD player is 25. The on/off codes are:

On = 123 (hex. 0x7b)

Off = 124 (hex. 0x7c )

A complete list of cod es c an be fo u nd on our we bs ite at www.arcam.co . u k

Press the “DVD/CD” button on the top left corner of the remote

control until the “DVD” light is illuminated. (Note that the light will

switch off again after a few s econds, but the remote control will

remain in the selected mode.)

Check battery compartment and reinstall batteries if necessary.

Reprogram the remote control.

If this fails, contact ARCAM customer services for further

assistance.

Reprogram the remote control. If programming from the supplied

(ARCAM) remote control, ensure that the ARCAM remote control is

configured to DV D and not to CD (see above).

This is a fault with th e le arni ng r em o t e cont r ol. However, conta ct

your dealer or ARCAM customer services to receive a free software

upgrade for your DVD player that fixes this problem.

Problems with video output

Problem Possible cause Solution

Picture is “jerky” when

playing region 1 discs.

No progressi ve video

output (DV27/DV88P).

No progressi ve video

output (DV88).

“Flashing green bars”

down both sides of the

screen with some films.

The picture freezes for a

moment approximately

half way through a film.

This occurs when NTSC discs

(such as those from the USA)

are played in a machine where

the output is set to “PAL” (such

as those sold in Europe).

A PAL disc (such as those sold

in Europe) is being played.

There is no progressive video

board fitted to your machine.

This has been not iced in earlier

versions of the software (version

1.6 or earlier).

This is caused by the player

changing layers on a two-layer

disc.

Enter the “Setup” menu and change the “TV system” setting to

“Auto” (see your user guide).

The player cannot output progressive video from a PAL source. To

enjoy progressive video output, NTSC source discs must be played.

Contact ARCAM customer services for details on upgrading your

player.

Contact your dealer or ARCAM customer services to receive a free

software upgrade for your DVD player that fixes this problem.

There is no fault.

23425

Problem Possible cause Solution

The picture freezes for a

moment at random points

in a film.

Can the composite /

Svideo outputs be used at

the same time as the

progressive output?

The “Zoom” feature does

not work.

“Black bars” are shown

at the top and bott om of

the sc reen.

The “Pluge” test cannot

be performed.

Frequently Asked Questions about your ARCAM DVD player…

Some versions of the software

controlling the disc drive are

reported to cause this problem.

It is possible to use the interlaced outputs at the same time as the progressive output (providing a

progressive scan board is fitted to the player). The most important restriction is that the interlaced

component and the SCART outputs cannot be used at the same time.

The “Zoom” feature does not

work with all di scs .

This can occur when a “Wide screen” film is viewed on a 4:3 format television.

Even with a 16:9 format television, “black bars” may still be visible. This is because the DVD being

viewed, although “Wide screen”, is not in 16:9 format. Many films are in 1:2.35 format, which will not

fill completely a 16:9 screen.

Prior to versio n 1 .75 of the

player software, it was not

possible to perform the “Pluge”

test.

Contact your dealer or ARCAM customer services to receive a free

software upgrade for your DVD player that fixes this problem.

There is no fault.

Contact your dealer or ARCAM customer services to receive a free

software upgrade for your DVD player (version 1.75 or later).

The “Below Black” menu item can be found at the bottom of the

second page of the set-up menu. When performing the pluge test,

this item should be set to “Pass Pluge”; at all other times, this item

should be set to “Normal” (otherwise video corruption may occur).

Problems with audio output

Problem Possible cause Solution

External digital decoder

does not decode the first

2 seconds of audio from

a CD/DVD.

On the analogue outputs,

the left (or right) channel

is on both outputs.

“Pops” or “crackles” are

heard through the amplifier when the player is

first switched on.

Some digital decoder models do

not lock quickly enough onto the

digital signal output by the DVD

player.

The analogue outputs have been

configured so that one channe l is

put out through both outputs.

The audio frequency selection

lines in the DVD player are not

being initialised correctly.

This is a fault with the digital decoder. However , contact your dealer

or ARCAM customer services to receive a free software upgrade for

your DVD player that w ill usually fix this problem (version 1.75 or

later).

Software versi on 1.75, or later:

On the third page of the “Set-up” menu, change the “Analog Out”

item to “Normal”.

Contact your dealer or ARCAM customer services for a free

software upgrade that will fix this problem (version 1.75 or later).

Problems with disc play-back and front-panel display

Problem Possible cause Solution

Player loads disc but will

not play, or play-back

halts unexpectedly.

Some MP3 discs/files

cannot be pla yed.

The number of tracks

displayed for a CD is 1

too many.

The player takes a long

time to identify a CD.

The front-panel display

is not illuminated.

The disc drive generates

more noise when a DVD

is being played.

There is a fault in the

manufacturing of the disc.

There are some restrictions on

the type of MP3 files that the

DV88/27 can play.

The CD contains a data track (it

is an “enhanced” CD).

Since this is a DVD player (primarily), it checks for discs in the following order: DVDs, SVCDs, VCDs,

CDs. Therefore it takes longer to identify a CD than any other disc type.

The front-panel display has been

switched off.

When playing DVDs, the drive spins significantly faster than when CDs are being played. A result of

this is that extra noise may be generated under certain circumstances, typically when disc menus are

being displayed. Drive noise level normally drops significantly when play-back of the film itself begins.

Contact ARCAM customer services for a list of discs known to

cause problems. Some of the problems can be solved with a free

software upgrade for your player.

The files must be recorded with a sample rate of 44.1KHz.

The bit-rate must be between 64Kb/s and 192Kb/s . Variable bit-rate

is not supported.

The DV88/27 is designed to mute the audio output if a data track is

encountered. This means that your equipment will not be damaged

by playing these discs.

The front panel supports 3 different levels of illumination. Press the

“DISP” button on the remote control to select your preferred level.

L817SW release notes

Software release notes for v1.76

The changes that differentiate versions 1.75 and 1.76 of the DV88/27 software:

•

The DTS code has been fixed.

Version 1.75 of the software will not play disks with a DTS sound track.

Software release notes for v1.75

The changes that differentiate versions 1.74 and 1.75 of the DV88/27 software:

•

Pluge (below black) menu item.

Until now, it has not been possible to perform a “pluge” test using the

DV88/27. A "Below Black" menu item has been added (to the bottom of

menu two), which has the options “Normal”, for normal viewing of material,

and “Pass Pluge” for when the pluge test is being performed.

•

FSEL lines now initialised.

The FSEL lines were not being initialised quickly enou gh previousl y, which

could lead to pops or crackles when the pla yer was first switched on. This is

now fixed.

•

Toggle-bit in remote codes.

The dependence on the toggle bit in our RC5 remote codes has been removed.

This means that the unit should be controllable using crappy learning remotes.

•

"LOAD" brings the player out of standby.

Pressing the "LOAD" button on the front panel when the player is in standby

mode brings the player out of standby and opens the draw.

•

CD skip-back works at 1 second.

It had been noted that the skip-back when a CD is being played did not work if

pressed at exactly 1-second into a track. This is now fixed.

•

Single channel mono now available on analogue outputs.

Some VCDs have a different language on the left and right channels. A menu

option has been added (“Analog output”, page 3) that allows the selection of

the left or right channel only (as mono output).

to the analogue output regardless of the disk type.

•

Quicker initiation of digital output.

Previously, the AVR100/200 did not have time to synchronise with the digital

output before the audio starting, meaning that the first 2-seconds of audio ma y

have been lost. The digital output is now started 2-seconds before the audio

when CDs are played.

•

CR9000 support.

The support for the CR9000 learning remote has changed.

The “arrow” keys must b e repro grammed t o emit “arrows”, not t he co mmands

shown on the keys (such as “stop”, “pause”), as previously.

•

Clock output enable on progressive scan board.

The clock output has been enabled on the progressive scan board. This may

cause some boards to start working that previously did not.

•

Player must be reset after the self-test has been run.

After the self-test has been run, the player will accept no further input until it

has been reset.

Note that this setting applies

Software release notes for v1.74

The changes that differentiate versions 1.73 and 1.74 of the DV88/27 software:

•

Fault in the player self-test corrected.

•

Discrete on/off remote codes added

For users with learning remote controls, discrete codes for on and off are

available (on = 123 (0x7b), off = 124 (0x7c)).

Software release notes for v1.73

The changes that differentiate versions 1.72 and 1.73 of the DV88/27 software:

•

File “atapife.c” reverted to version used in 1.4 to reduce reliability problems.

(This fixes “The Mask of Zorro” problem.)

Software release notes for v1.72

The changes that differentiate versions 1.71 and 1.72 of the DV88/27 software:

•

Block read count set to 8.

(An attempt to reduce the number of audio/video dropouts).

DV27 machines for sale require this version of software (or later).

Software release notes for v1.71

The changes that differentiate versions 1.7 and 1.71 of the DV88/27 software:

•

“LOAD” button on the front panel works when in DVD menus.

The draw can be opened when in a DVD menu.

This version of software (or later) is acceptable for in-house DV27 machines.

Software release notes for v1.7

The changes that differentiate versions 1.6 and 1.7 of the DV88/27 software:

•

Download countdown implemented and download speed improved.

•

CD playback: rewind through track boundaries possible; fast forward when in

repeat mode works correctly (playback restarts from the track beginning); fast

forward when not in repeat mode starts playback from the beginning of the

next track.

•

Progressive scan code added to main version (this code issue will detect a

progressive scan board and initialise it).

•

"USE_TOY_STORY_FIX" flag added to Makefile. The "Toy Story" fix code

can be added for customers particularly wanting that behaviour, but is not

included by default.

•

Front-Panel keys can now be used to navigate around DVD menus. PLAY =

"OK", STOP = "DOWN", PAUSE = "UP", SKIPL/REWIND = "LEFT",

SKIPR/FORWARD = "RIGHT".

•

OSD Language support added, accessed through the "OSD Lang" option in

menu 3. Supported languages are English, French, Spanish and German.

•

Block read count set to 31.

(An attempt to reduce the number of audio/video dropouts).

Software release notes for v1.6

The changes that differentiate versions 1.5 and 1.6 of the DV88/27 software:

•

Remote control fault found in issue 1.5 fixed.

•

CD rewind through track boundaries possible.

Software release notes for v1.5

The changes that differentiate versions 1.4 and 1.5 of the DV88/27 software:

•

Problems playing "Toy Story" and "Fantasia" bonus disks fixed.

This version of the software will play the “Toy Story” and “Fantasia” bonus

disks without problem, but may give problems with other disks instead.

NOTE: issue 1.5 may give problems with the remote control.

Software release notes for v1.4SEp

This is a pre-release version of 1.4 on a single machine for a friend of Steve

Reichert. It is functionally the same as issue 1.4. This version was not released

via an ECO.

Software release notes for v1.4

The changes that differentiate versions 1.3 and 1.4 of the DV88/27 software:

•

New splash screen introduced.

•

Digital output when playing disks with MPEG audio encoding has been

disabled. All MPEG disks output PCM, even when "bitstream" is selected.

•

"Robbie Williams" out-takes sound problem fixed.

•

Screen-saver does not activate during software download.

•

Screen-saver starts after two minutes (previously three minutes).

•

Chapter skip-back fixed.

Software release notes for v1.3SEf

This is a special edition sent to a single dealer in France in order to evaluate

the French language support. This versio n was not released via an ECO and

should not appear on any production player.

Software release notes for v1.3SEi

This is a special edition sent to a single dealer in Italy in order to evaluate the

Italian language support. This version was not released via an ECO and should

not appear on any production player.

Software release notes for v1.3SEp

This is a special edition sent to the DVD compliancy labs in Belgium, in order

to test that the MPEG audio encoding problem released in version 1.4 is

performed correctly. This version was not releas ed via an ECO and should not

appear on any production player.

Software release notes for v1.3SEs

This is a special edition sent to a single dealer in Spain in order to evaluate the

Spanish language support. This version was not released via an ECO and

should not appear on any production player.

Software release notes for v1.3:

The changes that differentiate versions 1.2 and 1.3 of the DV88/27 software:

•

Software download fails if the disk cannot be read - previously it was assumed

that the download had occurred correctly. Introduction of test for DVD8.bak.

•

Flag CDDSP_VCD is defined in the makefile.

•

Outline of progressive scan code added.

•

Selftest display changed, with tests for progressive scan components added.

•

Addition of French language support (not yet enabled for the user).

•

Highlights removed from OSD text.

•

"Below black" output disabled (to fix Bug's life playback problem).

NOTE: issue 1.3 may give problems with rewinding CDs through a track boundary.

Software release notes for v1.2:

The changes that differentiate versions 1.1 and 1.2 of the DV88/27 software:

•

Correction of title highlight placements when running NTSC => PAL disks.

•

Default subtitle setting changed from AUTO to OFF.

•

Default digital output changed from STEREO PCM to BITSTREAM.

Software release notes for v1.1:

The changes that differentiate versions 1.0 and 1.1 of the DV88/27 software:

•

Bookmarking is implemented so that the bookmarks are stored after the disk is

removed from the player, and restored when the disk is re-introduced. Up to

100 disks can be stored, each with up to 3 bookmarks.

•

The 'Play' button now causes playback to occur when the unit has been in 'step'

mode.

•

The aspect ratio of the material being played is detected and the SCART

output line is set accordingly. (Note that this is only effective when the player

has been set to 16x9 playback.)

•

Implement WSS on line 23 to indicate aspect ratio 4:3, 4:3 with 16:9 letterbox,

or 16:9 anamorphic.

•

Correction of menu highlight placements when running NTSC => PAL disks.

ARCAM

DV88 Progressive Scan Upgrade Instructions

CAUTION

THE ENCLOSED PRINTED CIRCUIT BOARD IS STATIC SENSITIVE AND PRECAUTIONS

MUST BE TAKEN TO ENSURE THAT IT IS NOT DAMAGED BY STATIC CHARGES. A

PROPERLY GROUNDED WRIST STRAP IS RECOMMENDED.

THIS PROCEDURE IS ONLY TO BE CARRIED OUT BY A SUITABLY QUALIFIED

TECHNICIAN. DELICATE SOLDERING IS REQUIRED.

1. Player software

The DVD player must have software version 1.74 or above in order to support progressive scan. Check

the player software version which is displayed on the TV screen momentarily after power up. There are

2 numbers displayed one above the other. The software version is shown at the top. Ignore the other

number. If the version is 1.74 or above then you do not need to update the soft ware, so ignore the rest

of this section. If it is below 1.74 then use the supplied software update disc to updat e the software.

There are actually 2 discs provided - one for the player software and one for the drive firmware. Only

the player software needs to be updated to support progressive scan, but you mig ht as well update the

drive firmware while you are at it.

Updating drive firmware

Follow this procedure exactly:

1.Turn the power on.

2.Wait for the ‘no disc’ message to appear on the display.

3.Press the LOAD button to open the tray.

4.Put the DVS firmware CD in the tray.

5.Press the LOAD button to close the tray. The firmware will now load from the CD into RAM. This

takes about 30 seconds.

6.Wait until the tray opens. When it does, take the CD out of the tray. The flash memory will now be

erased and the new firmware will be loaded from RAM into the flash ROM. This will take a further 30

seconds approximately.

7.Wait until the tray closes. This signals that the flash update is complete.

8.Switch the power off for 5 seconds and then on again to reboot the player.

Updating player software

Follow this procedure exactly:

1.Turn the power on.

2.Wait for the ‘no disc’ message to appear on the display.

3.Press the LOAD button to open the tray.

4.Put the DV88 software CD in the tray.

5.Press the LOAD button to close the tray. The player software will now load from the CD into RAM.

This usually takes about 5 minutes but may take up to half an hour. You m ay see corruption of the TV

picture during this time. This is normal.

6.Wait until the tray opens. When the tray opens, take the CD out of the tray. The flash memory will

now be erased and the new software will be loaded from RAM into the flash ROM. It will take about

one minute.

7.Wait until the tray closes. This signals that the flash update is complete. There is no need to reboot.

The software version should be shown on the TV screen m om entar ily every time the player is

powered up.

The DVD player will now have the required software to support the progressive scan board.

2. Fitting the progressive scan board

Note: When handling the PCB and working on the unit, ensure anti static precautions are taken.

Ensure the power lead is removed from the IEC inlet at the rear of the unit.

Remove the lid by removing the screws attaching the lid to the rear panel (T10 TORX driver required),

and the 2 screws each side that attach the lid to the chassis (T15 TORX driver required). The lid slides

out to the rear.

Remove 2 of the screws from the DSP board. The DSP board is the rectangular board that is fitted in

the centre of the unit along side the DVD drive. The 2 screws that need to be removed are the 2

towards the rear of the unit. A T10 TORX driver will be required for this. Now fit the 2 x 30mm hex

pillars in place of the 2 screws. A 5mm hex driver will be required for this. These pillars are used to

support the progressive scan PCB.

Remove the vinyl blanking gasket that is stuck to the outside of the rear panel covering the holes for the

progressive scan board. This blanking gasket is located above the SCART connector. If the player does

not have a blanking gasket because there are no holes to cover, contact Ar cam as you will need a new

rear panel.

Take the smaller vinyl blanking gasket that is supplied with the upgrade kit, remove the backing and

adhere it to the outside of the rear panel so that it covers the hole labelled ‘VGA’.

Fit the 3 round black plastic blanking plugs in the 3 holes in the rear panel labelled ‘C/S’, V/S’ and ‘HSYNC’. Push them into the holes from the outside.

You should be left with 3 holes in the middle labelled ‘Pr/R’, ‘Y/G’ and ‘Pb/B’. There should also be hole

labelled ‘REMOTE IN’ left uncovered.

Remove the progressive scan board from its bag and fit it into the DVD player. The 3 phono connectors

will fit in the 3 holes in the rear panel labelled ‘Pr/R’, ‘Y/G’ and ‘Pb/B’. The jack socket will fit in the hole

labelled ‘REMOTE IN’. The 2 mounting holes at the rear should line up with the 2 pillars you have just

fitted. Do not change the settings of the 8 way switch on the board. It should be set with switch 6 on

and all others off.

Attach the progressive scan board to the rear panel using the self tapping T10 TORX screws provided.

The number of screws required here will depend on the version of rear panel fitted. The latest version

of panel will have holes that allow 5 screws to be fitted to attach the board to the rear panel - 2 into the

phono connectors and 3 into the screening can. Earlier rear panels have holes only for 2 scr ews which

will screw into the connectors.

Attach the progressive scan board to the 2 hex pillars using the 2 x 6m m M3 T10 TORX screws.

3. Fitting the cables

The board should now be in position and the next task is to fit the cables.

Fit the 22 way flex foil between CN4 on the DSP board and SK1 on the progressive scan board. Ensure

that it is fitted with the contact surfaces facing the correct way - on the progressive scan board the

contact surfaces of the cable will face the rear of the unit.

Fit the 8 way cable between SK2 on the progressive scan board and SK8 on the power supply board.

Check the silk screen on the DSP board to identify the issue. If it is an issue 3 boar d or above, then the

remaining 4 way cable is fitted between SK3 on the progressive scan board and CN11 on the DSP

board. If however the board is below issue 3, then some highly delicate soldering work will be called for.

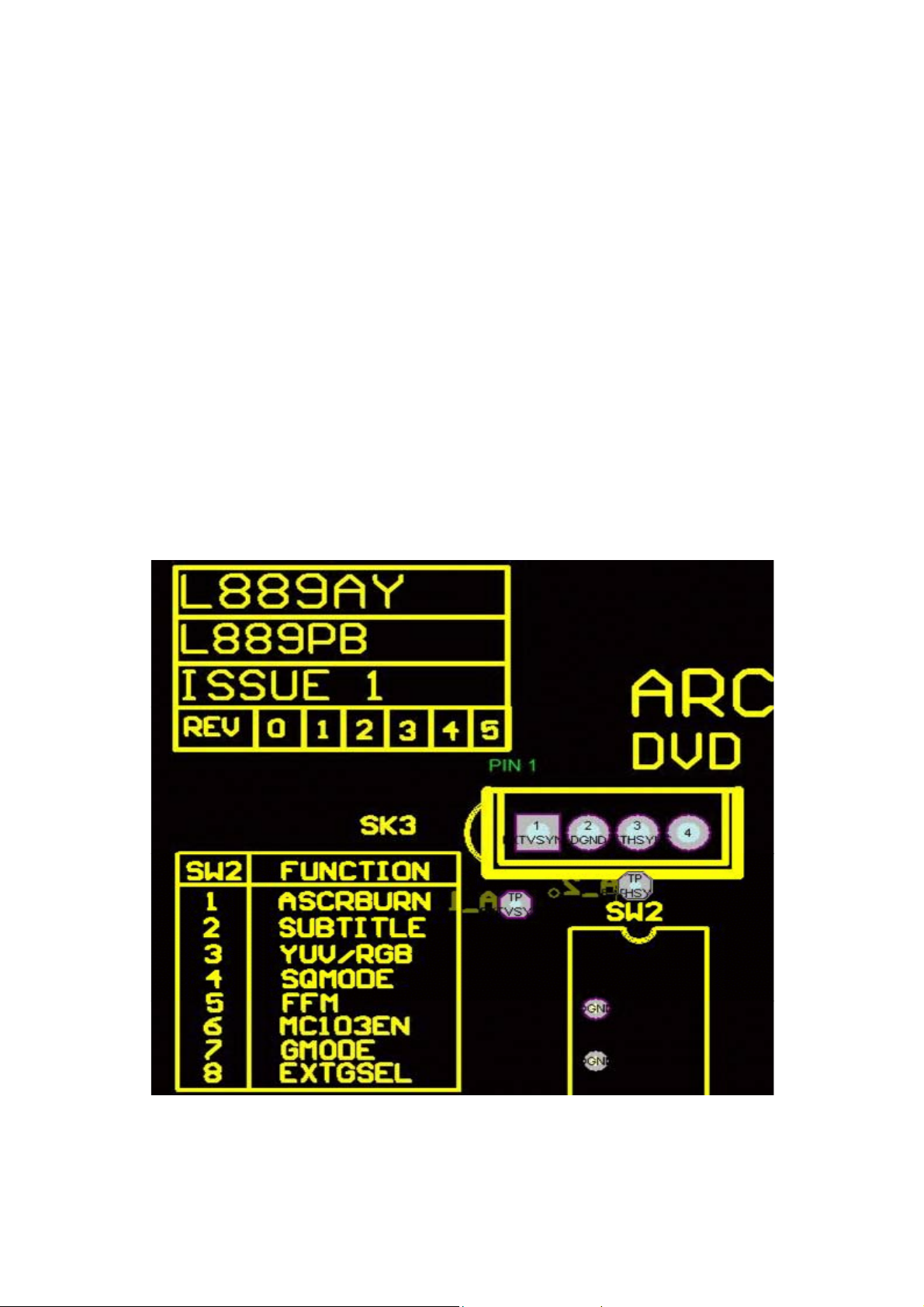

4. Soldering the 4 way cable to the DSP board (for DSP boards below issue 3 only)

Take the 4 way cable supplied in the upgrade kit and cut one of the connect or s off close to the

connector.

Plug the remaining connector into SK3 on the progressive scan board.

Make a careful mental note about which wire is pin 1 on the connector . Pin 1 is identified by a circle just

visible on the silk screen. It is the pin closest to the ‘SK3' legend on the silk screen (see diagram 1)

You will need to solder 3 of the wires to points on the DSP board. These points are located near the

bottom left corner of the Zoran Vaddis III IC (the upper right corner of the chip when viewed from the

front of the unit). Diagram 2 shows the vias to connect to.

Pin 1 V Sync Connect to via shown in diagram 2

Pin 2 GND Connect to one end of C19 (or the via near it) as shown in diagram 2

Pin 3 H Sync Connect to via shown in diagram 2

Pin 4 Not connected.

Diagram 1 - Pin numbers on 4 way connector SK3 on progressive scan board

Loading...

Loading...